**Calhoun: The NPS Institutional Archive**

Theses and Dissertations

Thesis Collection

1990-06

# Evaluation of ferroelectric materials for memory applications

Josefson, Carl Elof

Monterey, California: Naval Postgraduate School

http://hdl.handle.net/10945/27767

Calhoun is a project of the Dudley Knox Library at NPS, furthering the precepts and goals of open government and government transparency. All information contained herein has been approved for release by the NPS Public Affairs Officer.

Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

# NAVAL POSTGRADUATE SCHOOL Monterey, California

THESIS

EVALUATION OF FERROELECTRIC MATERIALS FOR MEMORY APPLICATIONS

by

Carl Elof Josefson

June 1990

Thesis Advisor:

R. Panholzer

Approved for public release; distribution is unlimited.

| REPORT DOCUMENTATION PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                      |                           | Form Approved<br>OMB No. 0704-0188                      |                                                                |                                             |              |                            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------|---------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------|--------------|----------------------------|

| 1a. REPORT SECURITY CLASSIFICATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                      |                           | 1b. RESTRICTIVE MARKINGS                                |                                                                |                                             |              |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ssified              |                           |                                                         | <u> </u>                                                       |                                             |              |                            |

| 2a. SECURITY C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | LASSIFICATIO         | N AUTHORITY               |                                                         |                                                                | I/AVAILABILITY O                            |              |                            |

| 2b. DECLASSIFICATION / DOWNGRADING SCHEDULE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |                           | Approved for public release; distribution is unlimited. |                                                                |                                             |              |                            |

| 4. PERFORMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ORGANIZAT            | ION REPORT NUMBE          | R(S)                                                    | 5. MONITORING                                                  | 5. MONITORING ORGANIZATION REPORT NUMBER(S) |              |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |                           |                                                         |                                                                |                                             |              |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                    | ORGANIZATION  uate School | Ca. OFFICE SYMBOL (If applicable) 39                    | 7a. NAME OF MONITORING ORGANIZATION  Naval Postgraduate School |                                             |              |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |                           | 39                                                      |                                                                |                                             |              | 1001                       |

| 6c. ADDRESS (C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                      |                           |                                                         |                                                                | ty, State, and ZIP                          |              |                            |

| Monte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | erey, CA             | 93943-500                 | 0                                                       | Monterey, CA 93943-5000                                        |                                             |              |                            |

| 8a. NAME OF F<br>ORGANIZAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | UNDING / SPO<br>TION | PNSORING                  | 8b. OFFICE SYMBOL<br>(If applicable)                    | 9. PROCUREMENT INSTRUMENT IDENTIFICATION NUMBER                |                                             |              |                            |

| 8c. ADDRESS (C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ity, State, and      | I ZIP Code)               |                                                         | 10. SOURCE OF                                                  | FUNDING NUMBER                              | RS           |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | •                    |                           |                                                         | PROGRAM<br>- ELEMENT NO.                                       | PROJECT<br>NO.                              | TASK<br>NO.  | WORK UNIT<br>ACCESSION NO. |

| 11. TITLE (Inclu                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | de Security C        | (secification)            |                                                         | <u></u>                                                        | <u> </u>                                    | 1            |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                    |                           | tric Material                                           | ls for Memo                                                    | ory Applic                                  | ations       |                            |

| 12. PERSONAL<br>Carl                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AUTHOR(S)<br>E. Jose | fson                      |                                                         | ···                                                            |                                             |              |                            |

| 13a. TYPE OF R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | REPORT               | 13b. TIME CO              |                                                         | 14. DATE OF REPO                                               | RT (Year, Month,                            | Day) 15.     | PAGE COUNT                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | s Thesi              | <del></del>               | TO                                                      | 1990 Ju                                                        |                                             |              | 97                         |

| 16. SUPPLEMEN<br>and do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      |                           | ws expressed<br>ficial policy                           |                                                                |                                             |              | of the author then of      |

| Defense                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                      | U.S. Gover                |                                                         |                                                                | <b>-</b>                                    | <del>-</del> |                            |

| 17.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | GROUP                |                           | 18. SUBJECT TERMS (                                     |                                                                | -                                           | =            | -                          |

| FIELD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GROUP                | SUB-GROUP                 | Ferroelectri                                            | .c, nonvola                                                    | tile memo                                   | ry, ra       | diation hard               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |                           |                                                         |                                                                |                                             |              |                            |

| 19. ABSTRACT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | (Continue on         | reverse if necessary      | and identify by block n                                 | umber)                                                         |                                             | ·            |                            |

| Ferroelectric materials have wide application in areas such as piezoelectric transducers, pyroelectric detectors, and electro-optics, and now thin-film ferroelectric materials are being integrated with conventional semiconductor processes to produce memory devices. Memories based on this technology potentially offer nonvolatile data storage and extended readwrite endurance in comparison with EEPROMS, without speed or power penalties. These memories are also radiation hard. Considerable interest in ferroelectric memory exists in the Department of Defense (DOD) because of these characteristics. However, several problems remain unsolved and no memory devices have been produced as yet. The physical mechanisms (as they are understood) are discussed, the claims made for the technology are examined, and the potential roadblocks, such as: cycle dependent fatigue, time dependent degradation of memory retention, and fabrication roblems are evaluated.  20. DISTRIBUTION/AVAILABILITY OF ABSTRACT DISCUSSIFICATION Unclassified |                      |                           |                                                         |                                                                |                                             |              |                            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |                           | PT. DTIC USERS                                          |                                                                | III 1 e a<br>Include Area Code              | 1 220 05     | FICE SYMBOL                |

| 22a. NAME OF RESPONSIBLE INDIVIDUAL  R. Panholzer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |                           | (408)64                                                 |                                                                | 4                                           | 2Pz          |                            |

| DD 50rm 147                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |                           |                                                         | · · · · · · · · · · · · · · · · · · ·                          | <del></del>                                 |              |                            |

Approved for public release; distribution is unlimited.

### Evaluation of Ferroelectric Materials for Memory Applications

by

Carl Elof Josefson Commander, United States Navy B.S., United States Naval Academy, 1971

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL FNGINEERING

from the

NAVAL POSTGRADUATE SCHOOL June 1990

| Author:        |                                                        |

|----------------|--------------------------------------------------------|

| _              | Carl Flof Josefson                                     |

|                |                                                        |

| Approved By: _ |                                                        |

|                | R. Panholzer, Thesis Advisor                           |

|                |                                                        |

|                |                                                        |

|                | J. R. Neighbours, Second Reader                        |

|                |                                                        |

|                | John P. Powers, Chairman, Department of Electrical and |

|                | Computer Engineering                                   |

#### **ABSTRACT**

The technical literature on ferroelectric materials and memory devices was reviewed to evaluate the potential for ferroelectric data storage systems in military applications. This thesis discusses the physical mechanisms and examines the claims made for the technology. The potential roadblocks, such as cycle dependent fatigue, time dependent degradation of memory retention, and fabrication problems are evaluated in terms of the impact on memory devices. This thesis describes the proposed designs and weighs their relative advantages. There are numerous applications for ferroelectric memories as the obstacles to full production are eliminated. A joint NPS/industry space evaluation of engineering prototype devices outlined will provide qualification data for applications requiring radiation tolerance.

| 1                         | Access                             | ion for            |         |

|---------------------------|------------------------------------|--------------------|---------|

|                           | NTIS<br>DTIC 1<br>Unanno<br>Justii | <b>CAB</b>         |         |

|                           |                                    | ibution<br>labilit | / Codes |

| OUALITY<br>INSPECTED<br>3 | Dist                               | Spec               | and/or  |

# TABLE OF CONTENTS

| I.   | INT                                                 | RODUCTION                                         | 1  |  |  |

|------|-----------------------------------------------------|---------------------------------------------------|----|--|--|

|      | A.                                                  | FERROELECTRIC MATERIALS                           | 1  |  |  |

|      | В.                                                  | PREVIOUS RESEARCH                                 | 2  |  |  |

|      | C.                                                  | ADVANTAGES OF FERROELECTRIC MATERIALS             | 3  |  |  |

| II.  | BASIC PHYSICAL MECHANISM IN FERROELECTRIC MATERIALS |                                                   |    |  |  |

|      | A.                                                  | DEFINITION OF FERROELECTRICITY                    | 5  |  |  |

|      | В.                                                  | CHARACTERISTICS OF FERROELECTRIC MATERIALS        | 5  |  |  |

|      |                                                     | 1. Crystal Structure                              | 6  |  |  |

|      |                                                     | 2. Polarization                                   | 8  |  |  |

|      |                                                     | 3. Other Properties of Ferroelectric Materials    | 14 |  |  |

|      | D.                                                  | DESIGN AND ENVIRONMENTAL INFLUENCES               | 15 |  |  |

|      |                                                     | 1. Electric Field/Film Thickness                  | 15 |  |  |

|      |                                                     | 2. Temperature                                    | 17 |  |  |

|      | ~r .                                                | 3. Radiation Effects                              | 19 |  |  |

|      |                                                     | 4. Grain Size                                     | 23 |  |  |

|      |                                                     | 5. Selection of Materials for Memory Applications | 23 |  |  |

| III. | DEC                                                 | GRADATION MECHANISMS IN FERROELECTRIC MATERIALS   | 25 |  |  |

|      | Α.                                                  | AGING                                             | 26 |  |  |

|      | В.                                                  | FATIGUE                                           | 32 |  |  |

|      | C.                                                  | WAITING TIME                                      | 36 |  |  |

|      | D.                                                  | EFFECTS ON DEVICE PERFORMANCE                     | 37 |  |  |

| IV.  | FAF                                                 | BRICATION OF FERROELECTRIC MEMORY DEVICES         | 30 |  |  |

|      | A.  | THIN-FILM DEPOSITION METHODS                 | 39        |

|------|-----|----------------------------------------------|-----------|

|      |     | 1. Physical Vapor Deposition                 | 40        |

|      |     | 2. Chemical Methods                          | 12        |

|      | В.  | DEVICE PATTERNING/ETCHING                    | 45        |

|      | C.  | ELECTRODE MATERIALS                          | 46        |

|      | D.  | TESTING STANDARDS                            | <b>47</b> |

|      |     | 1. Materials Characterization                | 48        |

|      |     | 2. Device Characterization                   | 50        |

| V.   | FER | ROELECTRIC RANDOM ACCESS MEMORY (RAM) DESIGN | 52        |

|      | A.  | GENERIC TWO-TRANSISTOR DESIGN                | 52        |

|      | B.  | DIFFERENTIAL-READ CELL                       | 54        |

|      | C.  | "SHADOW" RAM                                 | 56        |

|      | D.  | FERROELECTRIC FET                            | 57        |

|      | E.  | OTHER MEMORY DESIGN CONCEPTS                 | 58        |

|      |     | 1. Bipolar Memory                            | 58        |

|      |     | 2. Latch                                     | 59        |

|      |     | 3. Optical Read                              | 59        |

|      |     | 4. Non-destructive Read Out (NDRO)           | 60        |

|      | F.  | NON-MEMORY DRAM APPLICATIONS                 | 63        |

| VI.  | FER | RROELECTRIC MEMORY APPLICATIONS              | 64        |

|      | A.  | NONVOLATILE MEMORY REPLACEMENT               | 64        |

|      | B.  | RADIATION HARD APPLICATIONS                  | 67        |

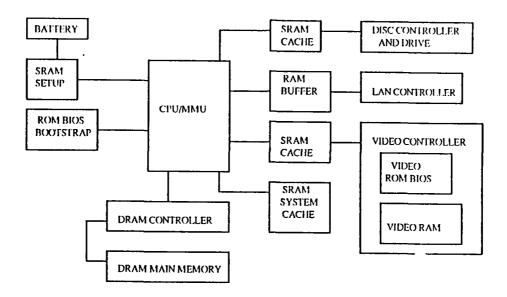

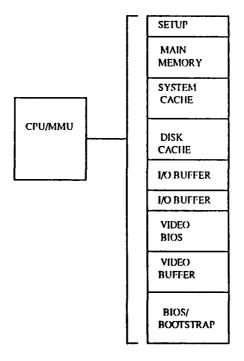

|      | C.  | ARCHITECTURE SIMPLIFICATION                  | 69        |

| VII. | SUM | MARY/CONCLUSIONS                             | 71        |

| APPENDIX A: NAVAL POSTGRADUATE SCHOOL SATELLITE ON-ORBIT |      |

|----------------------------------------------------------|------|

| MEMORY EXPERIMENT                                        | . 75 |

| LIST OF REFERENCES                                       | . 80 |

| DISTRIBUTION LIST                                        | . 87 |

# LIST OF FIGURES

| Figure 1.  | Polarization versus Applied Electric Field                        | 2  |

|------------|-------------------------------------------------------------------|----|

| Figure 2.  | ABO3 Unit Cell                                                    | 7  |

| Figure 3.  | Linear Dielectric and Ferroelectric Capacitive Response Curve     | 9  |

| Figure 4.  | Sawyer-Tower Circuit                                              | 10 |

| Figure 5.  | Switching Current versus Time for a Ferroelectric Capacitor       | 11 |

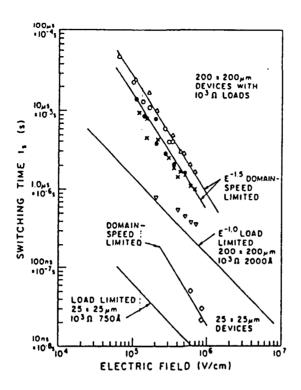

| Figure 6.  | Switching Time versus Applied Electric Field                      | 13 |

| Figure 7.  | Switching Time versus Cell Size, External Resistance, and Applied |    |

|            | Electric Field                                                    | 14 |

| Figure 8.  | Dielectric Permittivity versus Temperature                        | 15 |

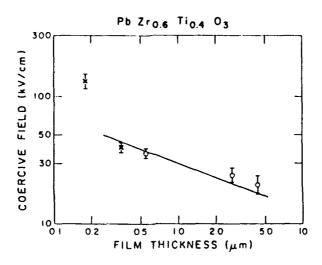

| Figure 9.  | Coercive Field versus Film Thickness                              | 17 |

| Figure 10. | Remanent Polarization versus Temperature                          | 18 |

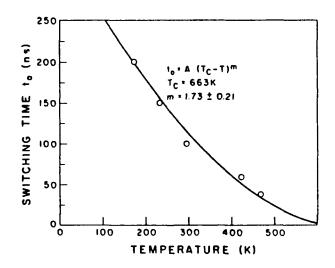

| Figure 11. | Switching Time versus Temperature                                 | 18 |

| Figure 12. | Aging Effects on the Hyteresis Loop                               | 26 |

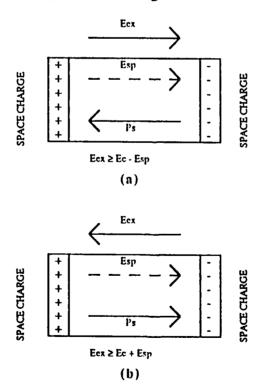

| Figure 13. | Space Charge Field                                                | 28 |

| Figure 14. | Space Charge Field versus Time                                    | 29 |

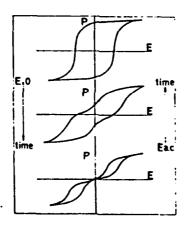

| Figure 15. | Switching Time versus Direction of Applied Electric Field         | 30 |

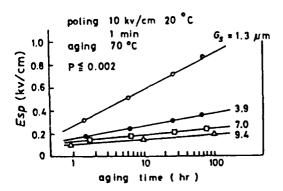

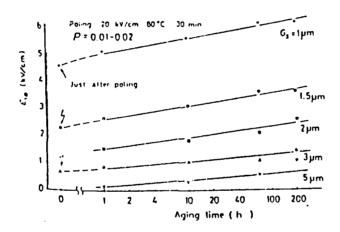

| Figure 16. | Aging Rate versus Grain Size                                      | 31 |

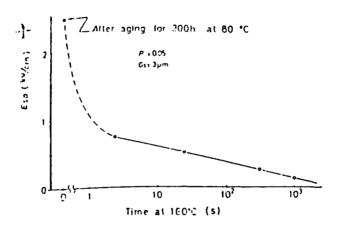

| Figure 17. | De-aging Effect of Temperature                                    | 32 |

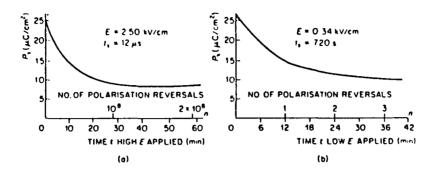

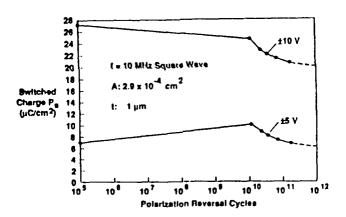

| Figure 18. | Fatigue Characteristics versus Electric Field                     | 36 |

| Figure 19. | Endurance with Sol-gel Deposition                                 | 45 |

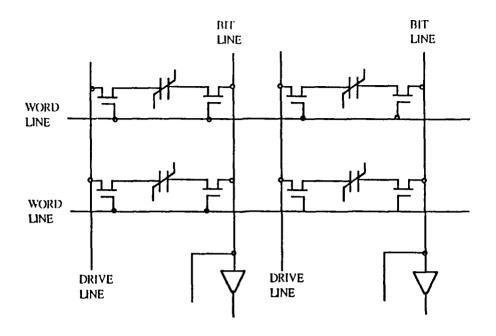

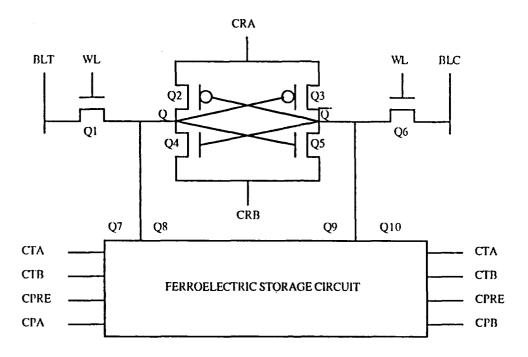

| Figure 20. | Two-Transistor Memory Cell                                        | 53 |

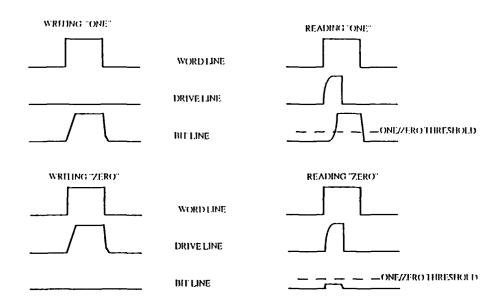

| Figure 21. | Read/Write Operation                                              | 54 |

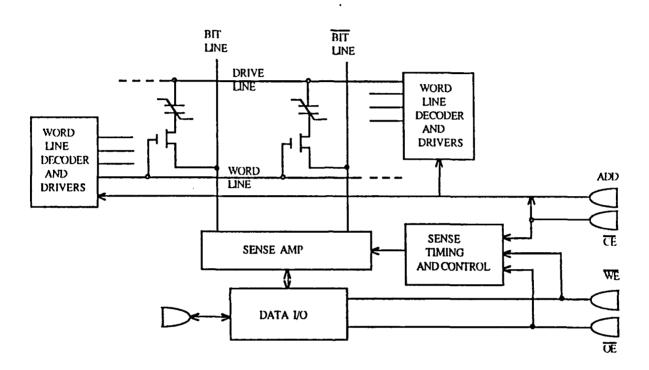

| Figure 22. | Differential Read Memory Cell                                     | 55 |

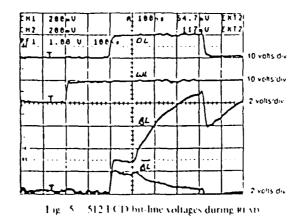

| Figure 23. | Output Voltages                                        | . 56 |

|------------|--------------------------------------------------------|------|

| Figure 24. | FRAM Cell Schematic                                    | 57   |

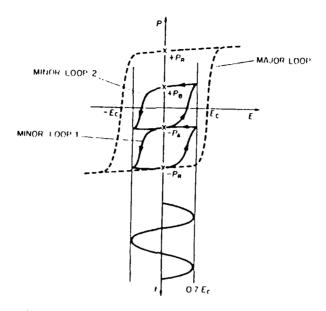

| Figure 25. | Minor Hysteresis Loop                                  | 61   |

| Figure 26. | Current Computer Memory Architecture                   | .70  |

| Figure 27. | Computer Memory Architecture with Ferroelectric Memory | . 70 |

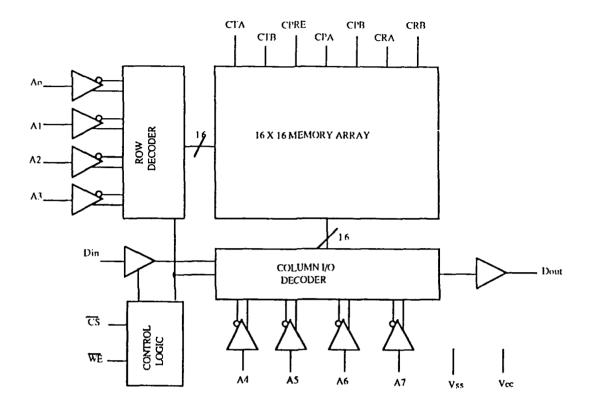

| Figure 28. | FMx 801 Memory Cell Block Diagram                      | .77  |

#### **ACKNOWLEDGEMENTS**

I want to take this opportunity to give my thanks to Prof. Panholzer for his support, guidance, and enthusiasm through the busy two years working on this project.

I also wish to thank my parents, Elof and Thora Josefson for instilling in me an interest in new ideas and the stubbornness to work at a worthwhile effort.

Most of all, I wish to thank my wife Jean, who has sustained me throughout this effort. Without her invaluable understanding, encouragement, and confidence I would not have made it.

#### I. INTRODUCTION

An exciting new memory technology, using ferroelectric materials, offers the potential for the "ideal" semiconductor memory. This new technology has a tantalizing array of capabilities: nonvolatility, radiation-hardness, low power, increased density, and high speed. With the read/write speeds and operating life predicted by its advocates, ferroelectric memories will be stiff competition for EPROMs and EEPROMs, and further development could bring their cost-per-bit down and performance up until they are direct competition for DRAMs [Ref. 1: p. 12]. In the longer term, by providing nonvolatility without sacrificing performance, ferroelectric memories could replace several currently used memory devices, thus greatly simplifying system architectures.

#### A. FERROELECTRIC MATERIALS

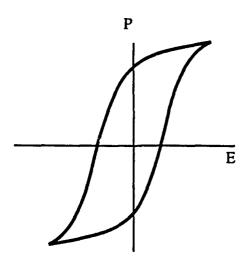

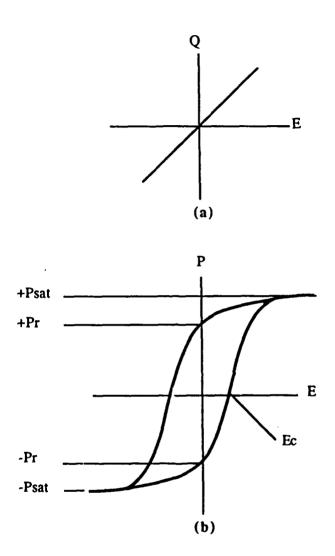

This new memory concept exploits a unique characteristic of ferroelectric materials, the ability to store binary data in the state of the material itself. Under the influence of an external electric field ferroelectric materials exhibit a spontaneous electric polarization which remains after the electric field is removed. Reversal of the electric field causes polarization in the opposite direction. A plot of the polarization P versus applied field E, as shown in Figure 1, results in a characteristic hysteresis curve analogous to ferromagnetic hysteresis. In fact, the name "ferroelectrics" is derived from this analogy, although none of the materials of current interest are ferrous. Ferroelectric materials can thus be modeled as bistable capacitors with two distinct polarization thresholds. The significant detail is that no external electric field or current is required to maintain the polarization; a finite value of polarization exists at zero applied field and will remain until switched by an applied electric field. The memory devices under development use this bistable polarization of ferroelectric

materials to store binary data. The state of polarization is read by measuring displacement current versus direction of applied electric field. The characteristics of ferroelectric materials are well known, but have not previously been exploited for memory applications because of limitations in thin film deposition and memory design.

Figure 1. Polarization versus Applied Electric Field

#### **B. PREVIOUS RESEARCH**

This is not the first time the potential of ferroelectric materials for memory applications has been recognized. Over twenty years ago there were several corporate and university programs attempting to exploit the ferroelectric effect to produce a memory device. These earlier efforts focused on thick-film or bulk ferroelectrics, which required external electric fields in excess of 40 v, well above semiconductor voltage requirements. These thick-films were also very slow to switch polarization states, making them uncompetitive with existing technologies. Additionally, the coercive voltage for most ferroelectrics is not well defined, but depends both on the level of the field and the duration of application, which made the historical approach to design of a ferroelectric memory susceptible to "half select" or

integration problems [Ref. 2: p. 65]. Also, in many ferroelectrics previously tested, it is difficult to detect the polarization reversal. Most significantly for current design efforts, many ferroelectric materials exhibited polarization-reversal-dependent material degradation (fatigue) and data retention problems, such as time-dependent signal loss (aging) and a tendency to return to a previous state after polarization, which even today have not been completely eliminated.

These and other problems, apparently inherent in the materials being evaluated, led to the termination of research efforts. IBM, as a typical example, ended its effort in 1973 because of seemingly insurmountable difficulties with read/write cycle material degradation and retention of data [Ref. 3: p. 2]. Ferroelectrics have proven to be practical in other areas, such as piezoelectric transducers, pyroelectric detectors, and electro-optics, but ferroelectric memories are still under development.

In the past fifteen years much progress has been made in the fabrication of thin-film materials, and recent breakthroughs might bring ferroelectric memories into commercial reality. Most of the memory devices under development are based on conventional CMOS circuitry and will be completely compatible with existing designs and fabrication procedures. At the present time several companies (McDonnell-Douglas, Raytheon, Westinghouse, National Semiconductor, Ramtron, TRW, and Harris, among others) are engaged in developing memories based on ferroelectric materials. The reason for this interest is clear; the potential applications of a nonvolatile semiconductor memory device require no great imagination.

#### C. ADVANTAGES OF FERROELECTRIC MATERIALS

In addition to non-volatility, ferroelectric memories offer other advantages as well: radiation hardness, low power, high bit density, high speed, and compatibility with silicon (Si) and gallium arsenide (GaAs) fabrication.

Since the polarization state is not affected by radiation, the ferroelectric memory is inherently radiation-hard. Gamma radiation, high energy particles, or neutrons must physically displace ions in the crystal lattice to impact the polarization state. Ferroelectric materials have exhibited tolerance of more than  $5x10^6$  rad (Si) of high-energy x-rays/cm<sup>2</sup> with a dose rate  $10^{11}$  rad/cm<sup>2</sup>s, and  $10^{14}$  1-Mev neutrons/cm<sup>2</sup> without performance degradation [Ref. 4: p. 1400]. Basically, the radiation hardness of a ferroelectric memory device is determined by the hardness of the underlying control circuitry.

The potential for higher bit densities results from the relatively large signal, or charge density differential between the switched and unswitched state, available for the read process. The charge density differential for Lead-Zirconate-Titanate (PZT) films is approximately 8-15  $\mu$ C/cm<sup>2</sup> [Ref. 3: p. 6, Ref. 5: p. 31, Ref. 6: p. 213], which is more than 100 times that of DRAMS, with a typical 0.1  $\mu$ C/cm<sup>2</sup> charge. This allows higher bit densities since the ferroelectric capacitors can potentially be made much smaller than DRAM cells.

Ferroelectric materials also promise low power and high speed. Ferroelectric memories are voltage driven (magnetic materials are current driven) which allows the use of high impedance, low power circuitry. Compared with EEPROMs, with millisecond write times, ferroelectric memories have achieved write times of 20-60 nanoseconds [Ref. 3: p. 7, Ref. 7: p. 220, Ref. 8: p. 130, Ref. 9: p. 1440, Ref. 10: p. 5470] and have the potential for more speed [Ref. 6: p. 213, Ref. 11: p. 211, Ref. 12: p.1, Ref. 13], which will make them competitive with DRAMs. They also promise extended read/write endurance with  $10^{12}$  read/write cycles [Ref. 3: p.67, Ref. 5: p. 31, Ref. 11: p. 213, Ref. 12: p. 3], while EEFROMs typically wear out after  $10^5$  cycles [Ref. 14: p. 32].

# II. BASIC PHYSICAL MECHANISM IN FERROELECTRIC MATERIALS

#### A. DEFINITION OF FERROELECTRICITY

Before continuing with discussions of applications, definitions for important parameters of ferroelectric materials will be developed and the physical mechanisms of these materials explored. The fundamental characteristic of ferroelectric materials, which differentiates them from the larger class of dielectric materials, is a spontaneous electric polarization (measured as charge per unit area) that can be reoriented by the application of an external electric field [ Ref. 15: p. 9].

#### **B. CHARACTERISTICS OF FERROELECTRIC MATERIALS**

All dielectric materials exhibit a polarization when an external electric field is applied, but it is not permanent; when the electric field is removed, the polarization disappears. Those dielectric materials whose crystal structure lacks a center of symmetry can exhibit piezoelectricity; that is, application of mechanical stress will induce an electric charge and, inversely, application of an electric field will produce proportional strain. A smaller subgroup of these piezoelectric materials have a unique polar axis in the unstrained condition, that is, the unit cells are aligned such that the dipole moments produce a finite and permanent polarization. The resultant electric dipole moment changes in magnitude when the material is uniformly heated or cooled, generating an electric charge at the surface of the material as the polarization changes. This effect is termed pyroelectricity. All ferroelectrics are both piezoelectric and pyroelectric, but they are unique in that they

possess a spontaneous polarization which can be reversed with the application of an external electric field.

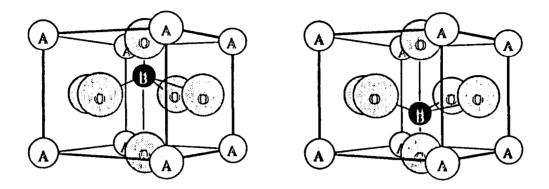

#### 1. Crystal Structure

This reversible polarization is the result of the structure of the ferroelectric atom. Figure 2 is a representation of the unit cell of an ABO<sub>3</sub> perovskite, typical of most of the ferroelectric materials of interest. The A cation at the corners of the unit cell has a large atomic radius, while the B cation is relatively small. The oxygen atoms positioned at the face centers have the largest atomic radius. In a ferroelectric material the structure is polar, usually tetragonal, orthorhombic, or rhombohedral [Ref. 16: p.17]. More of the materials of interest for memory applications are tetragonal, with the exception of potassium nitrate (KNO<sub>3</sub>). With tetgragonal structure, a cubic cell is stretched along one axis and shrunk along the two others. The longer axis is referred as the a axis and the shorter are called the c axes. The asymmetric position of the B ion, resulting from a difference between the center of positive and the center of negative charge, gives the unit cell its electric dipole. The external charge resulting from the dipole is the polarization, expressed in  $\mu$ C/cm<sup>2</sup>. It can be seen from the figure how the new polarization of the cell is "locked in" by the attractive-repulsive forces in the unit cell until an external field moves the B ion either from the lower to the upper position or vice versa. In lead zirconate titanate (PZT), the A ions are primarily lead, with some of the lead replaced by zirconium, and the B ions are titanium. Ferroelectric materials are characteristically formed from ions with certain valance relations and atomic size ratios and it is possible to generate a list of candidate materials with specific characteristics using these two criteria [Ref. 17].

Figure 2. ABO<sub>3</sub> Unit Cell

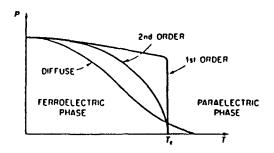

The switchability of polarization implies that the energy "hump" between directional states is relatively low. It further implies that the nonpolar state is only slightly less stable, so increasing the temperature will cause the material to become nonpolar [Ref. 16: pp. 11-12]. In fact, ferroelectric materials have a particular temperature at which there is a transformation to a nonpolar (cubic) structure and the spontaneous polarization disappears. This transformation temperature is called the Curie point (T<sub>c</sub>); above the Curie point the material is said to be in a paraelectric phase. In the paraelectric phase, the dielectric permittivity follows Curie-Weiss behavior; that is, the dielectric permittivity is inversely proportional to the difference between the temperature of the material and the Curie temperature

$$K = C/(T - T_c) \tag{1}$$

where K is the relative dielectric constant, C is the Curie constant, and  $T_c$  is the Curie temperature. [Ref. 16: p. 13] There is generally a substantial discontinuity of the electrical, optical, mechanical and thermal properties of a ferroelectric material near  $T_c$ . In PZT  $T_c$  is

approximately 360°C and it exceeds 250°C in the other materials of interest for memory applications.

#### 2. Polarization

As a sample of ferroelectric material is brought from the high-temperature paraelectric state through  $T_{\rm C}$  to the ferroelectric state, it develops the polar, or asymmetric crystal lattice, structure. This polar structure displaces the ionic and electronic charges within the unit cell, resulting in a microscopic electric dipole moment. In ferroelectric materials, the unit cells cooperatively align parallel with neighboring cells within a region called a domain, a homogeneous region where there is a common orientation of the dipole, resulting in a uniform spontaneous polarization. Since separate domains are randomly polarized, the electric dipole moments will tend to cancel each other and there may be no net macroscopic polarization.

To achieve a macroscopic polarization of the ferroelectric material so there is a net remanent polarization, it is "poled". Poling is the application of a dc electric field to reorient the polar axis of the domains in a common direction [Ref. 15: p. 13]. Since the field required to reorient the domains is usually a minimum at  $T_c$ , poling is commonly accomplished by cooling through  $T_c$  with an applied electric field. Poling at relatively high temperatures is recommended to improve the fatigue resistance of the sample [Ref. 3: p. 3]. The magnitude and duration of poling required varies from material to material.

As previously noted, the unique characteristic of a ferroelectric material is the polarization response of the material to an applied electric field. After the poling electric field is removed, the material will retain a net polarization which is defined as the remanent polarization  $(P_r)$ . When a voltage is applied in the opposite direction, the polarization will switch directions to the opposite sign. The reversal of an electric field applied to a linear

dielectric results in the response curve of Figure 3a, while the distinctive hysteresis loop characteristic of ferroelectric materials under the same conditions is shown in Figure 3b.

Figure 3. Linear Dielectric and Ferroelectric Capacitive Response Curve (After Ref. 15)

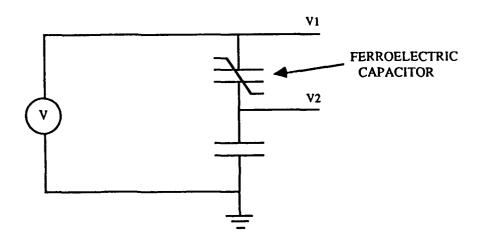

Measurement of the polarization response versus applied electric field can be done using a Sawyer-Tower circuit as shown in Figure 4 [Ref. 18: p. 270]. A large integrating capacitor is placed in series with the sample so that most of the voltage drop in the circuit is across the sample. Thus, V1 is a close approximation of the voltage across the ferroelectric

sample, and V2 is proportional to the charge (q) flowing through the material. The polarization (P) in  $\mu$ C/cm<sup>2</sup> is calculated from

$$P = q/A \tag{2}$$

where A is the electroded area of the ferroelectric material. The polarization can reach values as high as 500  $\mu$ C/cm<sup>2</sup>, although it is more typically 10-38  $\mu$ C/cm<sup>2</sup> for the materials of interest for memory applications [Ref. 19: p.122]. The electric field (E) is calculated from

$$E = V/d (3)$$

where d is the thickness of the sample [Ref. 20: p.3].

Figure 4. Sawyer-Tower Circuit (After Ref. 18)

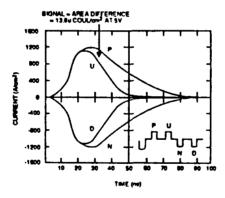

A ferroelectric memory capacitor is written to by the application of an electric field which orients all the dipoles in a common direction. To "read" the device, an electric field is again applied to the capacitor. If the dipoles are in the direction of the applied field, a current pulse corresponding to the charging current of the capacitor is generated. This current can be considered proportional to the linear dielectric of the capacitor. If, however,

the dipoles are oriented in the opposite direction, a larger current pulse forms, consisting of the capacitor charging current and the switching current caused by the switch in polarity of the dipoles. The "read" operation in most memory designs under consideration involves detecting the difference between the two output signals to determine whether a "one" or a "zero" was stored. It is important to note that when the "read" operation requires polarization reversal, it is destructive; the data must be rewritten to the memory cell following the "read". Figure 5 shows the current response as a function of time for each of the four read situations: negative voltage pulse followed by a positive voltage pulse (P), two consecutive positive pulses (U), positive pulse followed by negative pulse (N), and two consecutive negative pulses (D). The difference between P and U, or N and D, is the signal charge, and is  $13.8 \,\mu\text{C/cm}^2$  in this example [Ref. 6: p. 213]. This large signal makes the technology highly scalable; a  $1\times1 \,\mu\text{m}$  capacitor will provide approximately 200 mv differential in-line voltage.

Figure 5. Switching Current versus Time for a Ferroelectric Capacitor (From Ref. 6)

This hysteresis loop response of polarization to the applied electric field defines three parameters which are useful for the classification of ferroelectrics: remanent polarization (previously defined), coercive field, and saturation polarization. These parameters are also labeled on Figure 3b.

The electric field required to reverse the polarity from +Pr to zero is defined as the coercive field ( $E_c$ ). For memory applications the coercive field is the digital switching voltage of the memory cell. As an electric field larger than  $E_c$  is applied, the polarization will continue to increase (although at a slower rate) until all domains are aligned in the new direction; at this point the P versus E curve becomes linear. Extrapolation of the linear extreme of the plot is defined as the saturation polarization ( $P_{sat}$ ). For typical measurement of  $P_{sat}$ , the polarization at 3\* $E_c$  is used.[Ref. 20: p. 39]

The hysteresis loop is generally symmetrical about the origin ( $+E_c = -E_c$ ,  $+P_r = -P_r$ ). However, mechanical clamping, doping, radiation treatment [Ref. 20: p. 40], and space charge shielding [Ref. 21: p. 1242] can cause asymmetry or distortion of the loop. The loop parameters are functions of the dimensions and treatment of the specimen, temperature, pressure, type of electrodes, magnitude and frequency of the applied switching field, and the material's electrical and thermal history [Ref. 20: p. 40, Ref. 22: p. 3]. Generally, higher frequencies and temperatures decrease the values of  $P_r$  and  $P_{sat}$ . The coercive field increases as a function of the rate of polarization reversal [ Ref. 15: p. 14].

The actual mechanism of polarization reorientation is a sequential process which begins with the nucleation, or reorientation, of small regions. After these regions, usually near the surface, reach a critical size, their growth rate becomes approximately exponential. The time to reach the critical size is termed nucleation time and is on the order of one nanosecond for barium titanate (BaTiO<sub>3</sub>) and KNO<sub>3</sub>. [Ref. 11: p. 209]

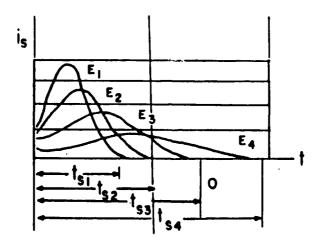

The sequence continues with the growth of domains in the direction of the applied field. These domains can usually be considered to grow at the speed of sound in solids, or approximately one km/sec in the materials of interest. Thus, for a one micron film, the

forward growth time is comparable to the nucleation time. The process of switching is complete when the needle-like domains begin to spread laterally until the entire sample has switched to the opposite polarization. In most ferroelectrics, the time for lateral growth is the dominant factor in switching time and is strongly affected by the applied electric field; larger fields reduce the switching time (Figure 6) [Ref. 15: p. 14]. The circuitry used and the size of the cell also influence the switching speed, with smaller size and lower load resistances decreasing switching time. In KN0<sub>3</sub> the switching times vary between 11 nsec and 10 µsec, depending on the applied field, external circuit, and cell size as shown in Figure 7 [Ref. 11: p. 211].

Figure 6. Switching Time versus Applied Electric Field  $(E_1>E_2>E_3>E_4)$  (From Ref. 15)

Figure 7. Switching Time versus Cell Size, External Resistance, and Applied Electric Field (From Ref. 11)

#### 3. Other Properties of Ferroelectric Materials

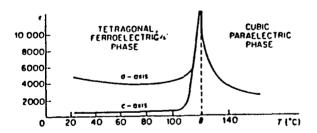

Another distinction shared by ferroelectric materials is the possession of anomalously high values for dielectric permittivity,  $\varepsilon$ . Ferroelectric materials have values of  $\varepsilon$  in the range of 100-20,000, much higher than the values of 1-10 normally associated with nonpolar dielectrics [Ref. 16: p. 8, Ref. 20: p. 360, Ref. 23: p. 266]. This is commonly referred to as the dielectric constant, but since it is not constant, but a function of both electric field and temperature in ferroelectric materials, dielectric permittivity is more appropriate. The dielectric permittivity is a nonlinear function of the electric field and is nearly proportional to the slope of the P-E curve [Ref. 24: p. 19]. The curves in Figure 8 illustrate the typical temperature dependency for ferroelectrics, with a large discontinuity at the Curie point, above which the dielectric permittivity conforms with the Curie-Weiss Law [Ref. 20: p. 36, fig. 3.1]. It should also be noted that the dielectric permittivity is

different for each axis of the basic crystal structure [Ref. 20: p. 36]. The dielectric permittivity is also a function of material composition and structure, frequency of the applied electric field, and time. The capacitance of the ferroelectric capacitor is calculated from

$$C = \varepsilon_r \, \varepsilon_o \, A/d \tag{4}$$

where C is the capacitance in Farads,  $\varepsilon_r$  is the relative permittivity,  $\varepsilon_0$  is the permittivity of free space, A is the area of the capacitor, and d is the distance between plates. As shown in equation (4), the capacitance is a function of the dielectric permittivity. Since most memory sense circuits are based on the Sawyer-Tower circuit, the capacitance of the ferroelectric memory capacitor must be fixed relative to the sense capacitor. Thus, a ferroelectric material used for memory applications must have a dielectric permittivity that is relatively stable over a wide range of temperatures.

Figure 8. Dielectric Permittivity versus Temperature (From Ref. 20)

#### D. DESIGN AND ENVIRONMENTAL INFLUENCES

#### 1. Electric Field/Film Thickness

Remanent polarization, switching speed, aging, and fatigue are all dependent on the external electric field applied to the ferroelectric memory capacitor. Since the applied electric field is a function of the circuit voltage (which is fixed if the device is to be compatible with existing logic levels) and film thickness, as shown in equation (3), the parameters listed above are also functions of film thickness. With larger applied electric fields remanent polarization, switching speed, and aging rate increase [Ref. 25: p. 569, Ref. 26: p. 170, Ref. 27: p. 4]. However, larger applied fields appear to reduce the rate of fatigue, although from the published data it is difficult to determine if the fatigue rate actually decreases, or if the larger field, by increasing the remanent polarization, is masking the effect of fatigue [Ref. 3: p. 6]. If the initial remanent polarization is large enough to provide sufficient aging margin, a larger field will give improved speed performance and greater readable signal.

Independent of the expected relationship between applied voltage, film thickness, and resulting electric field, film thickness influences the dielectric permittivity, remanent polarization, and coercive field [Ref. 28: p. 2717, Ref. 29: p. 788]. Figure 9 shows a plot of the coercive field versus film thickness for KNO<sub>3</sub> [ Ref. 26: p. 168]. The dependencies of E<sub>c</sub> and switching speed on film thickness support theories of three-dimensional domain switching, where the lateral domain wall velocities are the rate-limiting factor in polarization switching [ Ref. 26: p. 170].

Figure 9. Coercive Field versus Film Thickness (From Ref. 29)

The effects of electric field and film thickness are competing factors in the design of an integrated memory cell. Faster operation requires thinner films, but, as the film thickness is reduced, E<sub>c</sub> increases. Since the device operating voltage is fixed by standard semiconductor voltages, the increase in E<sub>c</sub> sets a minimum thickness of 100-400 nm for KNO<sub>3</sub> [Ref. 11: p. 209, Ref. 25: p. 569].

#### 2. Temperature

As previously mentioned, the properties of ferroelectric materials are functions of temperature. This includes the remanent polarization of the material, one of the critical parameters for memory applications, which decreases as temperature increases until the Curie temperature is reached. The reduction is relatively gradual at lower temperatures, but becomes more dramatic as the Curie temperature is approached, at which point the material enters the paraelectric phase and the material loses its capability to switch polarization and retain a set state (Figure 10) [Ref. 20: p. 40]. For memory applications this temperature dependence must be considered in the design process when establishing the required minimum levels of initial remanent polarization. This dependence on

temperature also limits the materials useful for memory applications to those with Curie temperatures significantly above the maximum military specification of 125°C.

Figure 10. Remanent Polarization versus Temperature (1 om Ref. 20)

Switching time is also a function of temperature. As temperature increases toward  $T_c$ , the switching speed of the material increases. Switching time extrapolates to zero as the temperature goes to  $T_c$  [Ref. 29: p. 790]. Figure 11 shows this relationship for PZT thin-films [Ref. 29: p. 790, Fig. 6].

Figure 11. Switching Time versus Temperature (From Ref. 29)

Increased temperature while cycling polarization states can also act as an aging and fatigue accelerator. Operation of a ferroelectric capacitor at high temperature--above

approximately 85° C--increases the effect of polarization cycling and reduces the signal retention time by increasing the aging rate [Ref 27: p.4]. Increased temperature also increases the nonswitching response, which further complicates sensing the stored state in memory applications since the switched and unswitched signal are usually compared in a complementary fashion [Ref. 27: p. 4, Ref. 29: p. 790]. The increased nonswitching response is probably due to domain wall contribution to ε [Ref. 29: p. 790]. This acceleration begins at approximately 85° C and grows as temperature increases. The effect on data retention at the high end of the military operating range (125°C) can be significant, and must be considered in memory cell design and establishing retention/fatigue specifications.

#### 3. Radiation Effects

Ferroelectric materials are extremely tolerant of radiation exposure. The function of the material as a memory relies on the "permanence" of the polarization and its ability to switch states with an applied electric field, and neither the polarization nor the switchability of the material is easily affected by low doses of radiation. For example, BaTiO<sub>3</sub> was exposed to up to  $10^{12}$  neutrons/cm<sup>2</sup> with no effect on the ferroelectric properties of the material. Exposure to a greater flux of  $10^{13} \cdot 10^{16}$  neutrons/cm<sup>2</sup> caused reduction in the coercive field and remanent polarization, while  $10^{17} - 10^{20}$  neutrons/cm<sup>2</sup> caused continued degradation of the material until samples subjected to doses above  $10^{20}$  neutrons/cm<sup>2</sup> lost all ferroelectric properties [Ref. 16: p. 90, Ref. 30: p. 116]. Other tests have shown that exposure to x-ray, gamma-ray, neutrons, and electrons can also produce asymmetries in the hysteresis loop and structural changes in the material, but that relatively high levels of exposure are required [Ref. 20: p. 39-40].