**Calhoun: The NPS Institutional Archive**

Theses and Dissertations

**Thesis Collection**

1991-09

# A technique for predictable real-time execution in the AN/UYS-2 parallel signal processing architecture

Little, Brian S.

Monterey, California. Naval Postgraduate School

http://hdl.handle.net/10945/26805

Calhoun is a project of the Dudley Knox Library at NPS, furthering the precepts and goals of open government and government transparency. All information contained herein has been approved for release by the NPS Public Affairs Officer.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

http://www.nps.edu/library

#### UNCLASSIFIED

SECURITY CLASSIFICATION OF THIS PAGE

•

| REPORT DOCUMENTATION PAGE                                                          |                                                                                                                           |                                                                     |                                                                                                        |                                                                                                                                                                                                     |                                                                                                                                           |                                                                                                            |                                                        |                                                              |                                                                                                    |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 1a. REPORT<br>UNCLASSI                                                             | SECURITY CLASS                                                                                                            | IFICATIC                                                            | N                                                                                                      | •                                                                                                                                                                                                   | 1b. RESTRICTIVE MARKINGS                                                                                                                  |                                                                                                            |                                                        |                                                              |                                                                                                    |

| 2a. SECURIT                                                                        | Y CLASSIFICATIO                                                                                                           | NAUTH                                                               | ORITY                                                                                                  |                                                                                                                                                                                                     | 3. DISTRIBUTION/AVAILABILITY OF REPORT                                                                                                    |                                                                                                            |                                                        |                                                              |                                                                                                    |

| 2b. DECLASSIFICATION/DOWNGRADING SCHEDULE                                          |                                                                                                                           |                                                                     |                                                                                                        | LE                                                                                                                                                                                                  | Approved for publ                                                                                                                         | lic release; distrib                                                                                       | ation is                                               | unlimited                                                    | 1.                                                                                                 |

| 4. PERFORM                                                                         | ING ORGANIZAT                                                                                                             | ION REP                                                             | ORTNUMBE                                                                                               | R(S) NPS EC-92-002                                                                                                                                                                                  | 5. MONITORING O                                                                                                                           | RGANIZATION REI                                                                                            | PORTN                                                  | JMBER(S                                                      | )                                                                                                  |

| 6a. NAME OF PERFORMING ORGANIZATION<br>Naval Postgraduate School                   |                                                                                                                           |                                                                     |                                                                                                        | 6b. OFFICE SYMBOL<br>(If applicable)<br>33                                                                                                                                                          | If applicable) Naval Postgraduate School                                                                                                  |                                                                                                            |                                                        |                                                              |                                                                                                    |

| 6c. ADDRES                                                                         | S (City, State, and                                                                                                       | d ZIP Co                                                            | ie)                                                                                                    | Į                                                                                                                                                                                                   | 7b. ADDRESS (City                                                                                                                         | , State, and ZIP Co                                                                                        | de)                                                    |                                                              |                                                                                                    |

|                                                                                    | CA 93943-5000                                                                                                             |                                                                     |                                                                                                        |                                                                                                                                                                                                     | Monterey, CA 93                                                                                                                           |                                                                                                            |                                                        |                                                              |                                                                                                    |

|                                                                                    |                                                                                                                           |                                                                     |                                                                                                        |                                                                                                                                                                                                     |                                                                                                                                           |                                                                                                            |                                                        |                                                              |                                                                                                    |

|                                                                                    | DF FUNDING/SPOI                                                                                                           |                                                                     | -                                                                                                      | 8b. OFFICE SYMBOL<br>(If applicable)PMS-412                                                                                                                                                         | 9. PROCUREMENT                                                                                                                            | INSTRUMENT IDE                                                                                             | NTIFICA                                                | TION NU                                                      | MBER                                                                                               |

| 8c. ADDRES                                                                         | S (City, State, and                                                                                                       | d ZIP Co                                                            | te)                                                                                                    | <u></u>                                                                                                                                                                                             | 10. SOURCE OF FU                                                                                                                          | NDING NUMBERS                                                                                              |                                                        |                                                              |                                                                                                    |

|                                                                                    |                                                                                                                           |                                                                     |                                                                                                        |                                                                                                                                                                                                     | Program Element No.                                                                                                                       | Project No.                                                                                                | Tas                                                    | k No.                                                        | Work Unit Accession<br>Number                                                                      |

| (U) A TECH<br>ARCHITEC                                                             | -                                                                                                                         | REDICA                                                              | TABLE REA                                                                                              | L-TIME EXECUTION I                                                                                                                                                                                  | N THE AN/UYS-2 I                                                                                                                          | PARALLEL SIGN                                                                                              | AL PRO                                                 | )CESSIN                                                      | G                                                                                                  |

| 13a, TYPE O                                                                        | FREPORT                                                                                                                   |                                                                     | 13b. TIME C                                                                                            | OVERED                                                                                                                                                                                              | 14. DATE OF REPOR                                                                                                                         | T (vear, month, da                                                                                         | v) 1                                                   | 5. PAGE                                                      | COUNT                                                                                              |

| Master's Th                                                                        |                                                                                                                           |                                                                     | From                                                                                                   |                                                                                                                                                                                                     | 911201                                                                                                                                    |                                                                                                            |                                                        | 141                                                          |                                                                                                    |

|                                                                                    |                                                                                                                           |                                                                     | e those of the                                                                                         | author and do not reflec                                                                                                                                                                            | t the official policy o                                                                                                                   | or position of the D                                                                                       | epartm                                                 | ent of De                                                    | fense or the U.S.                                                                                  |

| 17. COSATI                                                                         | CODES                                                                                                                     |                                                                     |                                                                                                        | 18. SUBJECT TERMS (co                                                                                                                                                                               | ntinue on reverse if                                                                                                                      | f necessary and ide                                                                                        | ntify by                                               | block nu                                                     | imber)                                                                                             |

| FIELD                                                                              | GROUP                                                                                                                     | SU                                                                  | GROUP                                                                                                  | AN/UYS-2, Data-flow                                                                                                                                                                                 |                                                                                                                                           |                                                                                                            | lology, S                                              | Signal Pro                                                   | ocessing,                                                                                          |

|                                                                                    |                                                                                                                           |                                                                     |                                                                                                        | Scheduling, Large-gra                                                                                                                                                                               | in Data-flow Archit                                                                                                                       | ectures                                                                                                    |                                                        |                                                              | 1                                                                                                  |

| 19 495784                                                                          |                                                                                                                           |                                                                     | f 04/04/2012                                                                                           | I<br>nd identify by block num                                                                                                                                                                       | harl                                                                                                                                      |                                                                                                            |                                                        |                                                              |                                                                                                    |

| The AN/UY<br>Methodolog<br>allocation m<br>time overhe<br>analysis to<br>Improveme | S-2 provides the<br>ry (PGM), which<br>nechanism that s<br>ead, it is difficult<br>exploit the period<br>nt in performanc | Navy w<br>represen<br>upports<br>to predic<br>lic arriv<br>e of the | ith a state of<br>hts specific ta<br>large-grain of<br>t if a given P<br>al of data and<br>machine whe | the art Digital Signal Pr<br>sks as nodes in a graph.<br>lata-flow processing. Wh<br>GM will meet the applic<br>d a priori knowledge of th<br>in the PGM graphs are re<br>ch when there is a high c | ocessor. The AN/U'<br>It utilizes a simple l<br>nile the mechanism<br>ation requirements.<br>are amount of compu-<br>patructured using th | First-Come-First-<br>is robust, easy to i<br>. Therefore, an ap<br>tation and commu<br>is approach, called | Served (<br>mpleme<br>proach (<br>nication<br>i Revolv | FCFS) ru<br>ent, and ru<br>hat uses<br>overhea<br>ving Cylir | n-time resource<br>esults in low run-<br>compile-time<br>d is investigated.<br>nder scheduling, is |

| 20. DISTRIB                                                                        | UTION/AVAILABI                                                                                                            | LITY OF                                                             | ABSTRACT                                                                                               |                                                                                                                                                                                                     | 21. ABSTRACT SEC                                                                                                                          | URITY CLASSIFICA                                                                                           |                                                        | 78(                                                          | 06                                                                                                 |

|                                                                                    | SIFIED/UNLIMITED                                                                                                          |                                                                     | E AS REPORT                                                                                            | DTIC USERS                                                                                                                                                                                          | UNCLASSIFIED                                                                                                                              |                                                                                                            |                                                        |                                                              |                                                                                                    |

| 22a. NAME<br>Shridhar St                                                           | OF RESPONSIBLE<br>nukla                                                                                                   | INDIVIC                                                             | UAL                                                                                                    | •                                                                                                                                                                                                   | 22b. TELEPHONE (1<br>408-646-2764                                                                                                         | Include Area code                                                                                          | )                                                      |                                                              | SH                                                                                                 |

| DD FORM                                                                            | 1473, 84 MAI                                                                                                              | R                                                                   |                                                                                                        | 83 APR edition may<br>All other edit                                                                                                                                                                |                                                                                                                                           | sted <u>SECU</u>                                                                                           |                                                        | ASSIFICA                                                     | TION OF THIS PAGE                                                                                  |

Approved for public release; distribution is unlimited.

A Technique for Predictable Real-Time Execution in the AN/UYS-2 Parallel Signal Processing Architecture

by

Brian S. Little Lieutenant, United States Navy B.S.E., University of Florida

Submitted in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

#### ABSTRACT

The AN/UYS-2 provides the Navy with a state of the art Digital Signal Processor. The AN/UYS-2 is programmed utilizing the Processing Graph Methodology (PGM), which represents specific tasks as nodes in a graph. It utilizes a simple First-Come-First-Served (FCFS) run-time resource allocation mechanism that supports large-grain data flow processing. While the mechanism is robust, easy to implement, and results in low runtime overhead, it is difficult to predict if a given PGM will meet the application requirements. Therefore, an approach that uses compile-time analysis to exploit the periodic arrival of data and a priori knowledge of the amount of computation and communication overhead is investigated. Improvement in performance of the machine when the PGM graphs are restructured using this approach, called Revolving Cylinder scheduling, is observed; and it is found to be effective when there is a high communication overhead or when the PGM nodes are of uniform size.

# The 715 C. 1

# TABLE OF CONTENTS

| I. | INTRO | DUC  | CTION                            | ••    |       |       |         | . 1 |

|----|-------|------|----------------------------------|-------|-------|-------|---------|-----|

| •  | Α.    | BAG  | CKGROUND                         | • •   |       | • • • | • • • • | 2   |

|    |       | 1.   | AN/UYS-2 Design Theory           | •••   | • • • | • • • | • • • • | . 2 |

|    |       | 2.   | AN/UYS-2 Design Problems         | •••   |       |       | • • • • | . 4 |

|    | B.    | OBJ  | ECTIVES                          | • •   | • • • | • • • |         | . 5 |

|    | C.    | TH   | ESIS ORGANIZATION                | ••    |       | •••   |         | 5   |

|    |       |      |                                  | -     |       |       |         |     |

| п. | ARCH  | HITE | CTURE AND PROGRAMMING OF THE AN/ | UYS   | -2.   | • • • |         | . 7 |

|    | Α.    | ARG  | CHITECTURE                       | • •   |       | • • • |         | 7   |

|    |       | 1.   | Modularity                       | ••    |       | • • • |         | 8   |

|    |       |      | a. The Scheduler                 | • •   | •••   | • • • | • • •   | 10  |

|    |       |      | b. The Global Memories           | • •   | •••   | • • • | • • •   | 10  |

|    |       |      | c. The Arithmetic Processors     | • •   | • • • | • • • | • • •   | 11  |

|    |       |      | d. The Input/Output Processors   | • •   | •••   | • • • |         | 12  |

|    |       |      | e. The Input Signal Conditioner  | • • • |       | •••   | • • •   | 12  |

|    |       | 2.   | Cohesiveness                     | • • • | • • • | • • • |         | 12  |

|    |       |      | a. Control Buses                 |       |       |       | • • •   | 13  |

|     |     | b. Data Transfer Network 13               | 3 |

|-----|-----|-------------------------------------------|---|

|     |     | c. Command Program Processor              | 3 |

|     | В.  | Programming 14                            | 4 |

|     |     | 1. Graphical Interface 14                 | 4 |

|     |     | 2. Graph to Program Conversion 15         | 5 |

|     |     |                                           |   |

| ш.  | SCH | EDULING OF PGM. ON THE AN/UYS-2 17        | 7 |

|     | А.  | SIGNAL PROCESSING REQUIREMENTS            | 7 |

|     |     | 1. Desirable Characteristics In Execution | 8 |

|     |     | 2. Resource Allocation                    | 8 |

|     | В.  | FIRST-COME-FIRST-SERVED SCHEDULING        | 0 |

|     |     | 1. Advantages 21                          | 1 |

|     |     | 2. Disadvantages 21                       | 1 |

|     |     | 3. A Simple Example                       | 2 |

|     | C.  | REVOLVING CYLINDER SCHEDULING             | 3 |

|     |     | 1. Implementation                         | 5 |

|     |     | 2. Advantages                             | 8 |

|     |     | 3. Disadvantages 29                       | Ð |

|     |     | 4. A Simple Example                       | 9 |

|     |     |                                           |   |

| ſV. | THE | SIMULATOR                                 | 1 |

|     | Α.  | IMPLEMENTATION                            | 1 |

|     |     |                                           |   |

.

|    |      | 1.  | Communications                   | 34 |

|----|------|-----|----------------------------------|----|

|    |      | 2.  | Major Resource Elements          | 37 |

|    |      |     | a. The Input/Output Processor    | 37 |

|    |      |     | b. The Global Memories           | 38 |

|    |      |     | c. The Scheduler                 | 39 |

|    |      |     | d. The Arithmetic Processors     | 40 |

|    | B.   | TH  | E LANGUAGE - C++                 | 41 |

|    | C.   | USE | ER INTERFACE                     | 42 |

|    | D.   | LIM | ITATIONS OF THE SIMULATOR        | 43 |

|    |      |     |                                  |    |

| V. | PERF | ORN | IANCE EVALUATION                 | 44 |

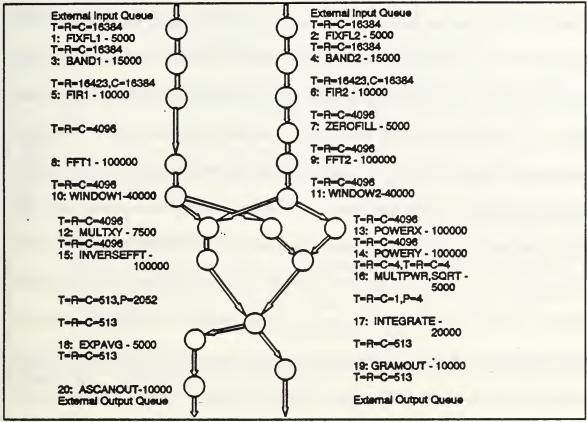

|    | Α.   | CO  | RRELATOR APPLICATION             | 44 |

|    |      | 1.  | Description                      | 44 |

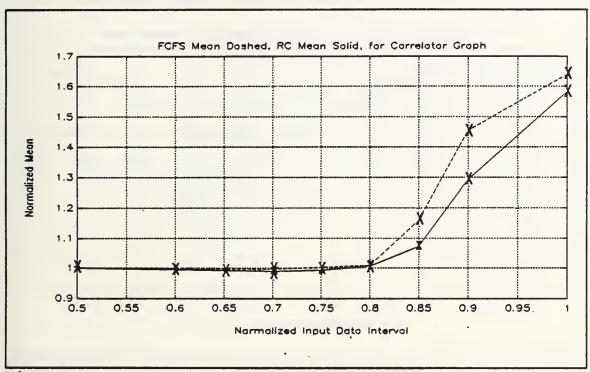

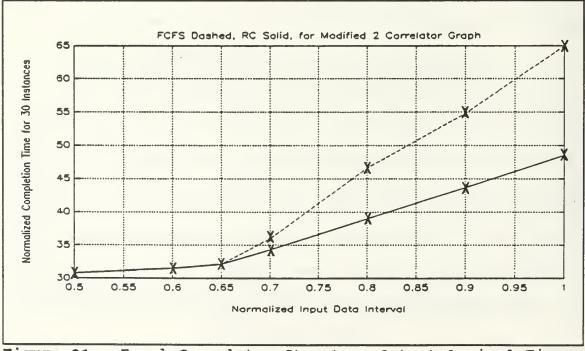

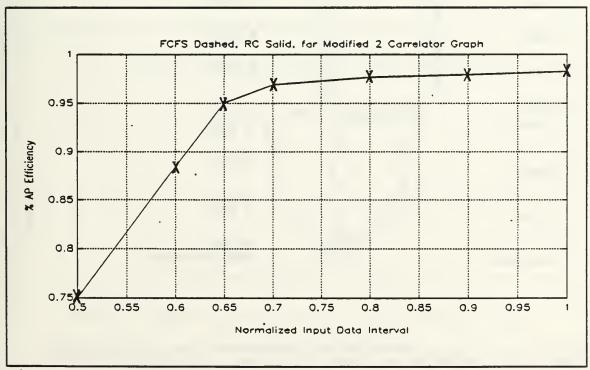

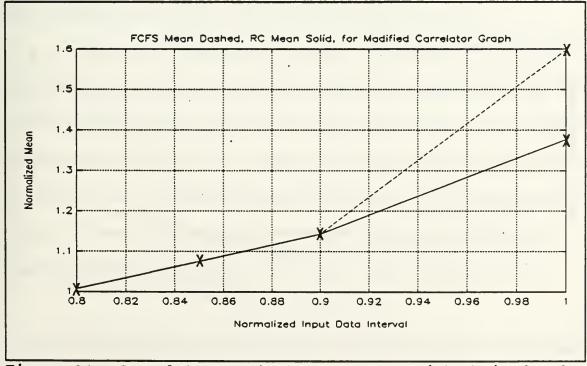

|    |      | 2.  | Output and Interpretation        | 45 |

|    | B.   | CO  | RRELATOR WITH UNIFORM NODE SIZES | 49 |

|    |      | 1.  | Description                      | 49 |

|    |      | 2.  | Output and Interpretation        | 50 |

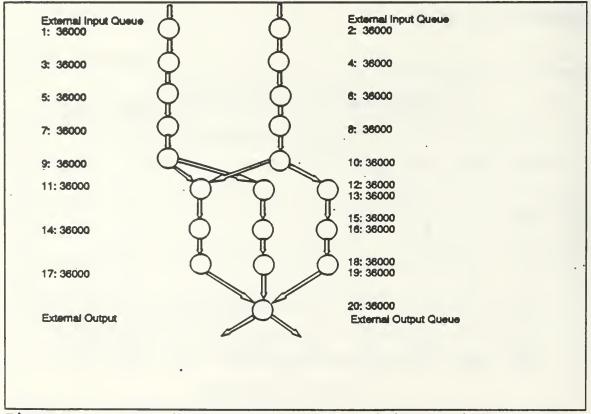

|    | C.   | CO  | RRELATOR WITH CHAINED NODES      | 54 |

|    |      | 1.  | Description                      | 54 |

|    |      | 2.  | Output and Interpretation        | 55 |

|    | D.   | FFI | APPLICATION                      | 58 |

|    |      | 1.  | Description                      | 58 |

|     |      | 2.   | Out   | put ar | nd Interpretation                       | • • | • • • |       | 60 |

|-----|------|------|-------|--------|-----------------------------------------|-----|-------|-------|----|

| VI. | CON  | ICLU | ISIOI | NS     |                                         | • • | •••   |       | 65 |

|     | Α.   | SUC  | CCES  | S OF   | THE RC APPROACH                         | ••  | •••   |       | 65 |

|     |      | 1.   | Con   | nmun   | ication Intensive                       | ••  | •••   |       | 65 |

|     |      | 2.   | Nor   | ı-Com  | munication Intensive                    | • • | •••   |       | 65 |

|     | B.   | IMI  | PROV  | /ING   | RC                                      | • • | • • • |       | 66 |

|     | C.   | PRO  | OPOS  | ED F   | RESEARCH                                | ••  | •••   |       | 67 |

|     |      | 1.   | Har   | dware  | Modifications                           | ••  | •••   |       | 67 |

|     |      |      | a.    | Syst   | olic Array Processor                    | ••  | •••   |       | 67 |

|     |      |      | b.    | Ope    | n Architecture                          | ••  | • • • |       | 67 |

|     |      | 2.   | Soft  | ware   | Modifications                           | • • | • • • |       | 67 |

|     |      |      | a.    | User   | r Friendly Processing Graph Methodology | ••  | • • • |       | 68 |

|     |      |      | b.    | Thro   | oughput Enhancements                    | ••  | •••   |       | 68 |

|     |      |      |       | (1)    | Node Chaining                           | • • | • • • |       | 68 |

|     |      |      |       | (2)    | Scheduling                              | ••  | •••   |       | 68 |

|     |      |      |       | (3)    | Fault Tolerance                         | ••• | • • • |       | 69 |

|     |      |      |       |        |                                         |     |       |       |    |

| APF | PEND | IX A | : RE  | EVOL   | VING CYLINDER CODE                      | ••  | •••   | • • • | 70 |

|     |      |      |       |        |                                         |     |       |       |    |

| APP | PEND | IX B | : PC  | IM R   | EPRESENTATION CODE                      | ••  | • • • | • • • | 87 |

vii

| APPENDIX C: MAIN SIMULATOR CODE         | 90  |

|-----------------------------------------|-----|

| APPENDIX D: INPUT/OUTPUT PROCESSOR CODE | 93  |

| APPENDIX E: GLOBAL MEMORY CODE          | 96  |

| APPENDIX F: SCHEDULER CODE              | 99  |

| APPENDIX G: ARITHMETIC PROCESSOR CODE   | 107 |

| APPENDIX H: INTER-COMMUNICATION CODE    | 113 |

| APPENDIX I: RESULT GENERATION CODE      | 115 |

| LIST OF REFERENCES                      | 120 |

| INITIAL DISTRIBUTION LIST               | 124 |

# LIST OF TABLES

| Table I:   | FUNCTIONAL ELEMENT REQUIREMENTS                    | 9  |

|------------|----------------------------------------------------|----|

| Table II:  | EXECUTION OF 36 CYCLES UTILIZING FCFS SCHEDULING . | 24 |

| Table III: | RC ASSIGNMENT SCHEDULE FOR SAMPLE PGM GRAPH        | 30 |

## LIST OF FIGURES

| Figure 1:  | The AN/UYS-2 Architecture                           | 9  |

|------------|-----------------------------------------------------|----|

| Figure 2:  | A Sample PGM Graph                                  | 15 |

| Figure 3:  | Converted PGM Program                               | 16 |

| Figure 4:  | A Simple PGM Graph                                  | 23 |

| Figure 5:  | An Algorithm to Perform RC Assignment               | 26 |

| Figure 6:  | An Algorithm to Assign Dependencies                 | 27 |

| Figure 7:  | A Possible Restructured PGM                         | 27 |

| Figure 8:  | Graphical Input Format for the Simulator            | 32 |

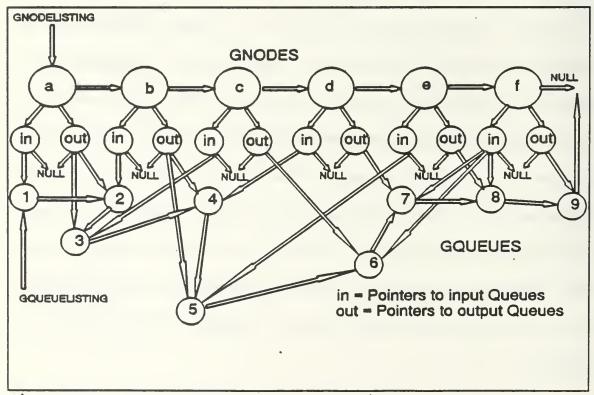

| Figure 9:  | Data Structure Representation of a PGM Graph        | 32 |

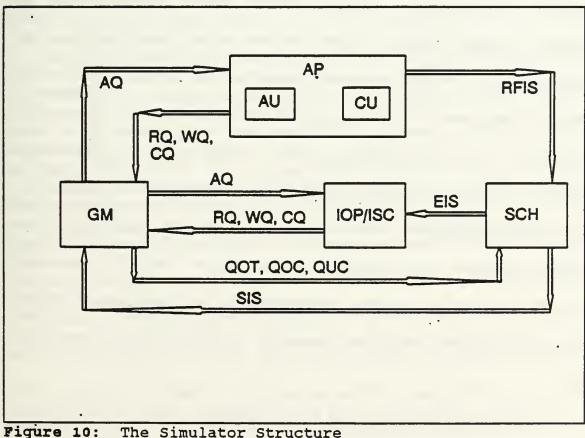

| Figure 10: | The Simulator Structure                             | 33 |

| Figure 11: | Graphical Description of Correlator Application     | 45 |

| Figure 12: | Correlator Graph Mean                               | 47 |

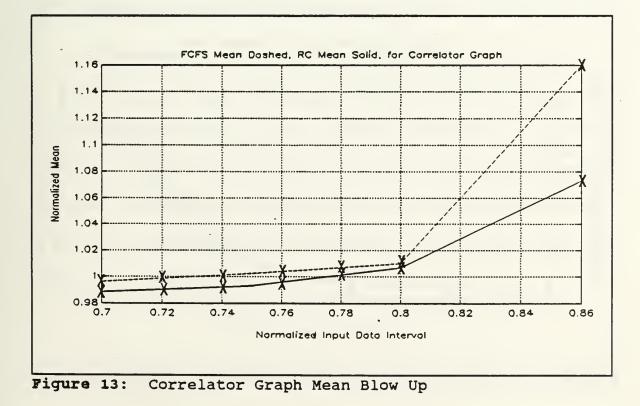

| Figure 13: | Correlator Graph Mean Blow Up                       | 47 |

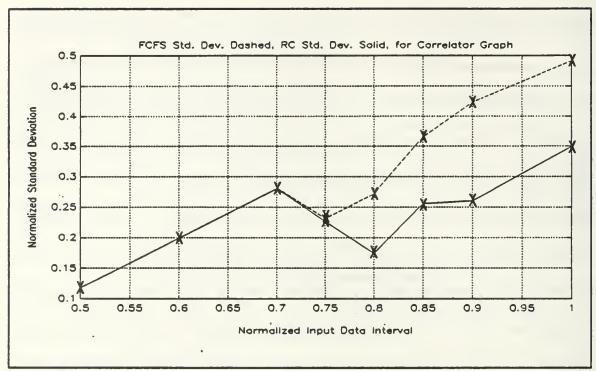

| Figure 14: | Correlator Graph Standard Deviation                 | 48 |

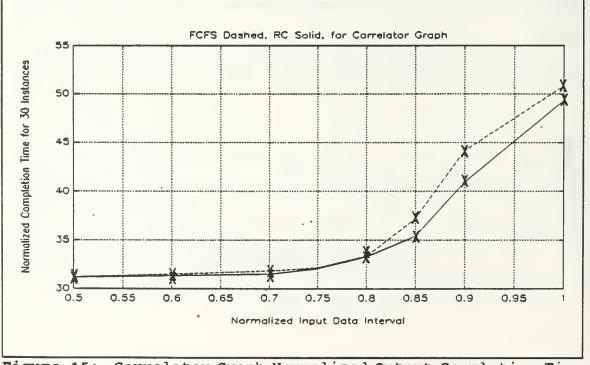

| Figure 15: | Correlator Graph Normalized Output Completion Time  | 48 |

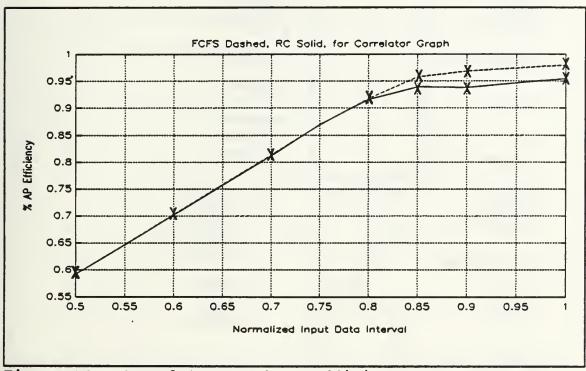

| Figure 16: | Correlator Graph AP Efficiency                      | 49 |

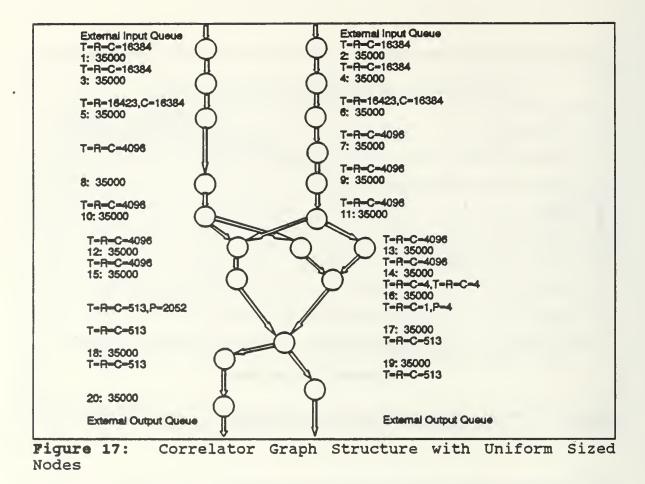

| Figure 17: | Correlator Graph Structure with Uniform Sized Nodes | 50 |

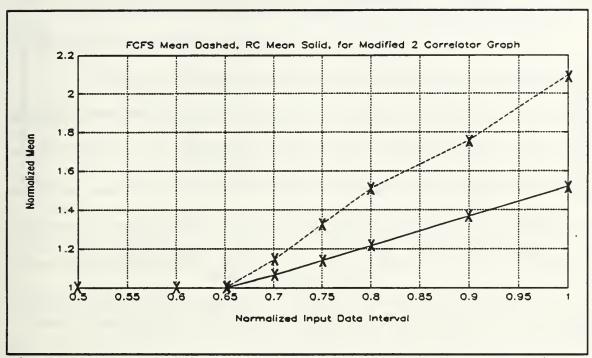

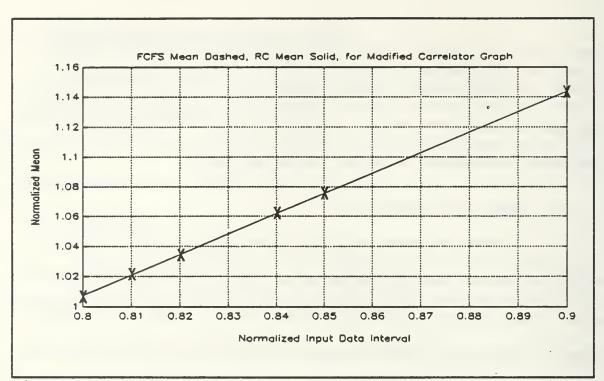

| Figure 18: | Correlator Structure Means for Equal Node Times     | 51 |

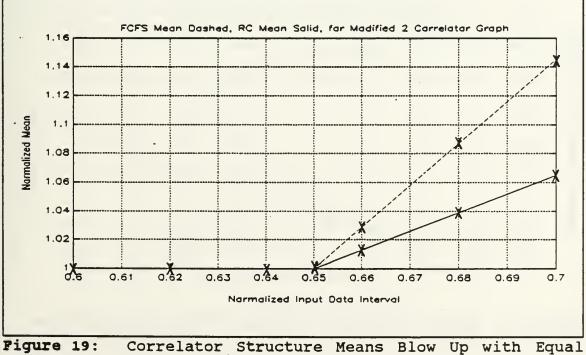

| Figure 19: | Correlator Structure Means Blow Up with Equal Times | 51 |

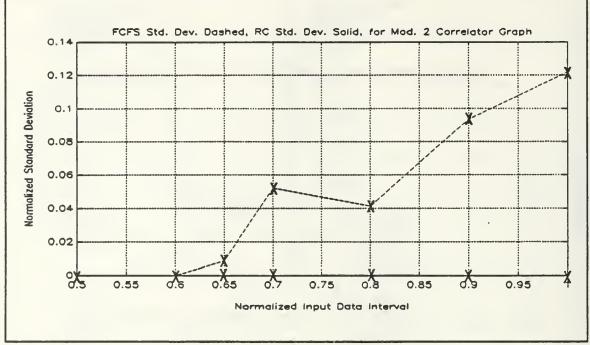

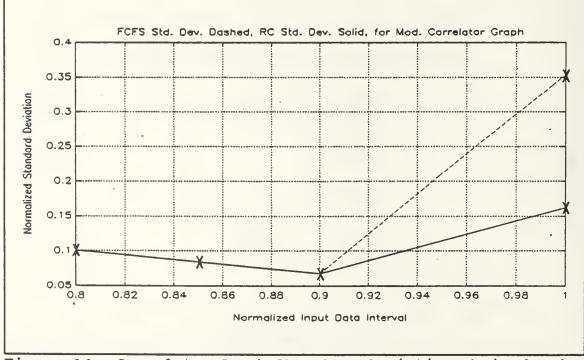

| Figure 20: Correlator Structure Deviation with Equal Times    | 52 |

|---------------------------------------------------------------|----|

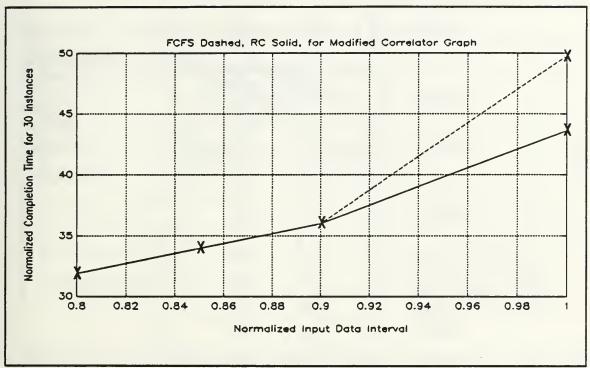

| Figure 21: Equal Correlator Structure Output Arrival Times    | 52 |

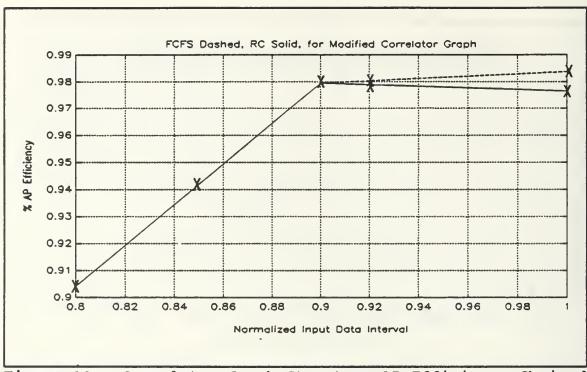

| Figure 22: AP Efficiency for Correlator Structure Equal Times | 53 |

| Figure 23: Correlator Graph Structure with Chained Nodes      | 54 |

| Figure 24: Correlator Graph Structure Mean with Chained Nodes | 55 |

| Figure 25: Correlator Graph Structure Mean Blow Up Chained    | 56 |

| Figure 26: Correlator Graph Structure Deviation Chained Nodes | 56 |

| Figure 27: Correlator Graph Structure Output Times Chained    | 57 |

| Figure 28: Correlator Graph Structure AP Efficiency Chained   | 58 |

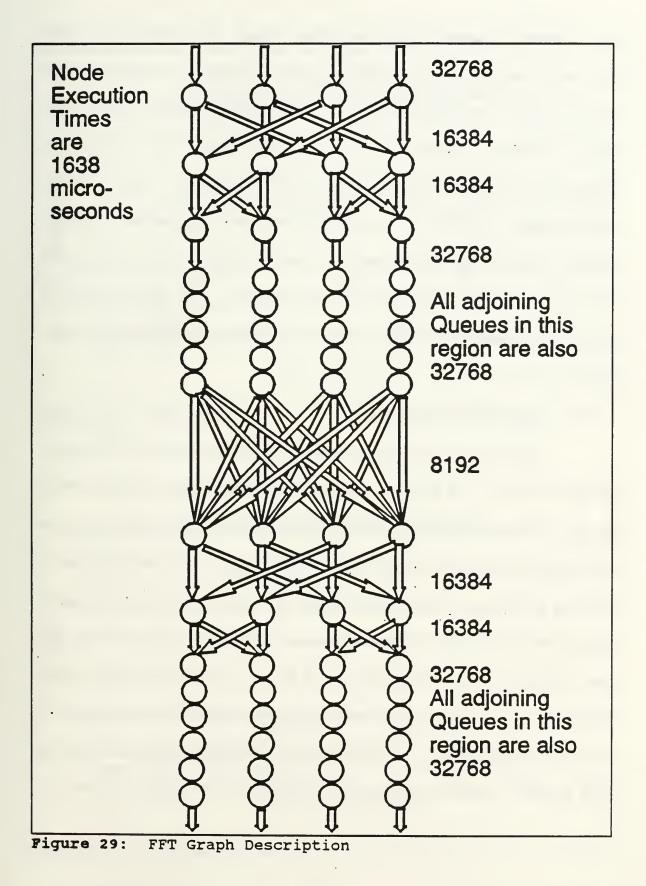

| Figure 29: FFT Graph Description                              | 59 |

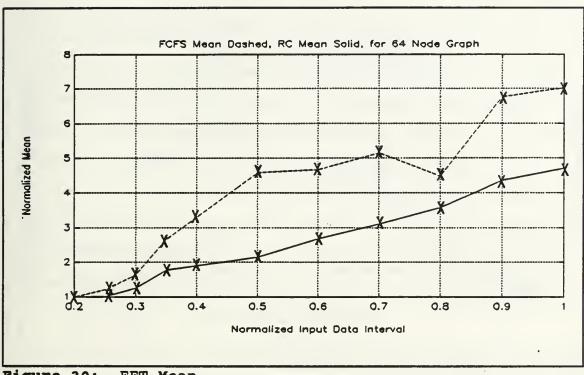

| Figure 30: FFT Mean                                           | 61 |

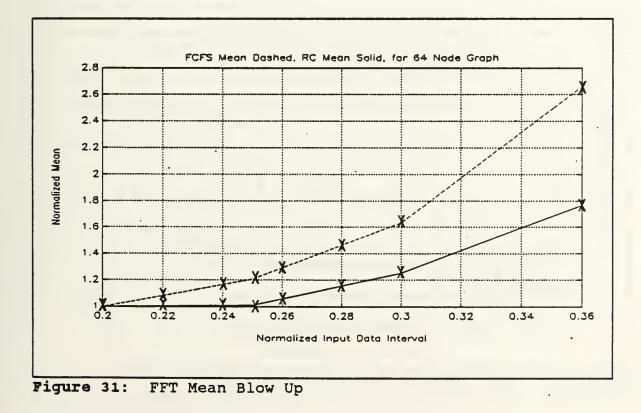

| Figure 31: FFT Mean Blow Up                                   | 61 |

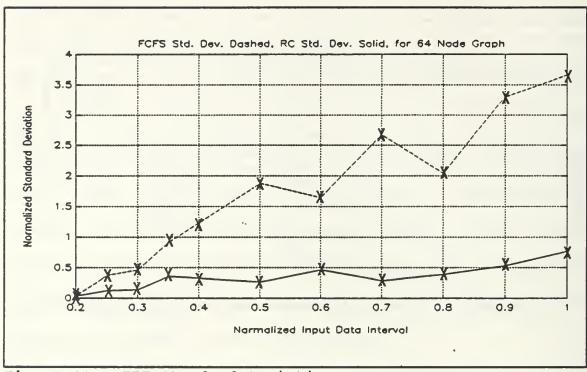

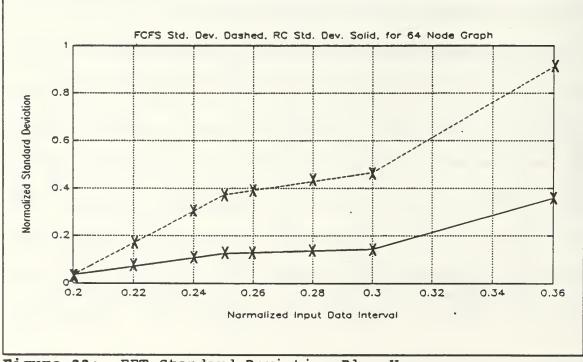

| Figure 32: FFT Standard Deviation                             | 62 |

| Figure 33: FFT Standard Deviation Blow Up                     | 62 |

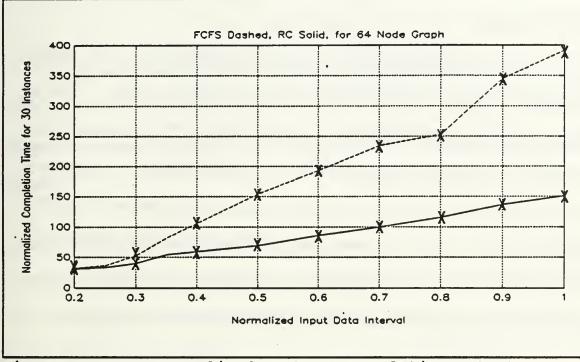

| Figure 34: FFT Normalized Instance Completion Output          | 63 |

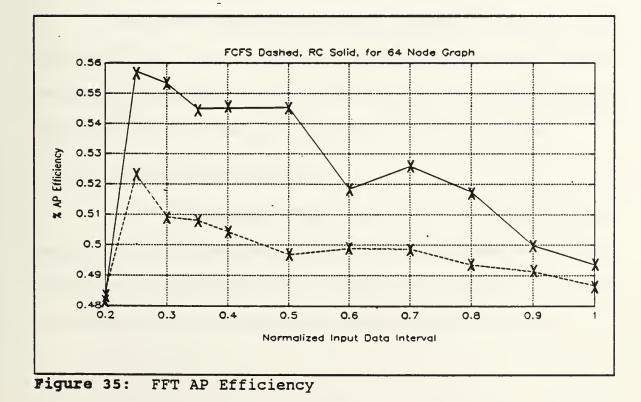

| Figure 35: FFT AP Efficiency                                  | 63 |

.

# LIST OF SYMBOLS

| DSP   | - | Digital Signal Processing                          |

|-------|---|----------------------------------------------------|

| SEM   | - | Standard Electronic Module                         |

| FE    | - | Functional Element                                 |

| SCH   | - | Scheduler                                          |

| AP    | - | Arithmetic Processor                               |

| GM    | - | Global Memory                                      |

| IOP   | - | Input/Output Processor                             |

| ISC   | - | Input Signal Conditioner                           |

| CBUS  | - | Control Bus                                        |

| DTN   | - | Data Transfer Network                              |

| PE    | - | Physical Element                                   |

| PGM   | - | Processing Graph Methodology                       |

| AU    | - | Arithmetic Unit                                    |

| CU    |   | Control Unit                                       |

| CPP   | - | Command Program Processor                          |

| FCFS  | - | First Come First Served                            |

| RC    | - | Revolving Cylinder                                 |

| ASCII | - | American Standard Code for Information Interchange |

| WQ    | - | Write Queue                                        |

.

| QOT  | - | Queue Over Threshold         |

|------|---|------------------------------|

| QOC  | - | Queue Over Capacity          |

| QUC  | • | Queue Under Capacity         |

| EIS  | - | Execute Instruction Stream   |

| SIS  | - | Send Instruction Stream      |

| AIS  | - | Accept Instruction Stream    |

| RQ   | - | Read Queue                   |

| AQ   | - | Accept Queue                 |

| RFIS | - | Ready For Instruction Stream |

| CQ   |   | Consume Queue                |

| FFT  | - | Fast Fourier Transform       |

| 2-D  | - | Two Dimensional              |

| 1-D  |   | One Dimensional              |

٠

xiii

•

• • • •

#### ACKNOWLEDGEMENTS

I would like to thank my advisor, Shridhar Shukla, for all of his assistance and contributions throughout the duration of this project. In addition, I would like to express my deepest gratitude to my wife, Joan. Her understanding and patience throughout the long computer nights were invaluable. Without her, none of this would have been possible.

#### I. INTRODUCTION

Since the advent of radar before World War II, the success of modern warfare has depended on the ability of a system to process "... electronic signals to detect, localize, attack, and counter increasingly sophisticated threats." [RICE 90, pp. 1-2] The more sophisticated the system, the more complex the signal processing requirements. Not only does the complexity depend on the number of operations to be performed, but also on the time interval available for completion [BELLANGER 84, pp. 3]. Within the realm of modern warfare, milliseconds can be the difference between survival or death. The ability to quickly interpret and disseminate incoming target data provides the user a discernible edge during today's modern warfare.

No longer does the Navy need to rely upon electro-mechanical processors. The development of data transducers and the advent of multi-processors allow electrical signals to be processed in real time using digital methods [BELLANGER 84, pp. 4-5]. But, if digital signal processing machines are to operate in real time, they must operate at a rate which is closely related to the sampling frequency of the signals.

The AN/UYS-2 Enhanced Modular Signal Processor is utilized in many different signal processing applications, from the acoustic system on a P3-C "Orion" aircraft to the BSY-2 Sonar Suite on the SSN-21 "Seawolf" class submarine. Although different configurations are possible, the search mission drives the envelope of the processing system. The United States' Navy's signal processing requirements have been increasing

since the advent of electronics conception in the early part of the twentieth century and "... are expected to increase tenfold within the next ten years." [RICE 90, pp. 2]

The AN/UYS-2 is meant to provide the United States' Navy with a standard, programmable, modular, multi-processor capable of meeting the digital signal processing requirements into the twenty-first century. Yet, modifications will be required if it is to maintain its goal.

#### A. BACKGROUND

The innovation of new weapon platforms, led by Autonomous Underwater Vehicles and Remotely Piloted Vehicles, and the advancement of weapon technology requires an intelligent stand-alone programmable multi-processor.

"To achieve high performance in a processor specialized for signal processing, the need to depart from the simplicity of von Neumann computer architectures is axiomatic." [LEE 87, pp. 24]

#### 1. AN/UYS-2 Design Theory

Parallel computations that exist in signal processing can be naturally represented as data-flow graphs. The data-flow approach was first presented by Karp, and it has since been expanded by many including Dennis and Watson [KARP 66, pp. 1390-1411, DENNIS 80, pp. 48-56, WATSON 82, pp. 51-57]. These graphs not only describe the dependencies between different parts of the computation required in an application, but also provide built-in scheduling and synchronization.

While data-flow techniques have been applied to digital signal processing since its earliest days, Navy sensor systems have continued to employ a control-flow method until the AN/UYS series development during the 1980's [LEE 90, pp. 333, RICE 90, pp. 2]. Time-line control, in which a single control signal generates program execution and provides the output, characterizes a control-flow architecture. Multi-thread control flow architectures are achievable by use of more than one control signal, though it is difficult to develop programs that mold themselves to this simplified structure.

Data-flow representation of digital signal processing algorithms provides a natural exploitation of concurrence [LEE 90, pp. 333]. Typical data-flow algorithms execute a task based upon the availability of input data and machine resources, thereby enabling the data to exist only between its production and consumption and eliminating the need for a distinct program counter [RICE 90, pp. 2].

A distinction must be made between *large-grain* and *fine-grain* data-flow architectures. *Fine-grain* architectures have their uses in Very Large Scale Integration as documented by Koren, Silberman, and Dennis [DENNIS 80, pp. 48-56, KOREN 83, pp. 335-337]. But, the use of *fine-grain* data-flow within the modular design of the AN/UYS-2 would produce unreasonable communication overheads. Therefore, the AN/UYS-2 is built around the *large-grain* data-flow architecture approach. Due to the generality of the data-flow paradigm, it can be used to specify and exploit the parallelism at the instruction level as well as at the task level [BROBST 87, pp. 40-45, SAWKAR 83, pp. 344]. The theoretical foundation for consistency of such representations has been well studied by Lee, Karp, and Miller [LEE 87, pp. 24-35, KARP 66, pp. 1390-1411].

The focus of this work is on task-level parallelism in such applications expressed using data-flow graphs. Such computations are also classified as *pipelined function-parallel computations* and *synchronous data-flow computations* [LEE 87, pp. 24-35]. However, the machine must provide mechanisms to manage the data that flows through the graph and to capture the intrinsic scheduling and synchronization.

The AN/UYS-2 utilizes a distributed run-time operating system which implements a hybrid control-flow/data-flow architecture by utilizing the data-flow technique at the task level and the control-flow approach at the elementary processing level [POPS 89, pp. 2-9, RICE 90, pp. 2]. This helps to minimize the communication costs involved while providing efficient elementary level execution.

#### 2. AN/UYS-2 Design Problems

The mechanisms involved in managing graph data flow, intrinsic scheduling, and synchronization, typically operating at run-time, result in overheads that lead to suboptimal performance.

The non-deterministic (first-come-first-served) scheduling strategy used by the AN/UYS-2 will not be able to maintain throughput with the rapidly increasing data-flow graph bandwidth.

Increasing sensor system complexity compounded by decreasing allowable reaction time is likely to degrade the AN/UYS-2 capabilities considerably.

#### **B.** OBJECTIVES

Since the AN/UYS-2 utilizes a non-real-time strategy to schedule the application's nodes to free processors, this thesis investigates a robust, compile-time technique that supports a simple run-time mechanism to improve throughput and predictability in the AN/UYS-2 architecture including:

- Investigation of Digital Signal Processing (DSP) requirements

- Development of a compile-time algorithm for graph restructuring

- Design and implementation of an AN/UYS-2 software simulator

- Performance evaluation and comparison of the existing and proposed scheduling algorithms [POPS 90, pp. 6-3].

A compile-time approach is possible in DSP due to the tremendous amount of information that is known about each task. It simplifies the application developer's task and results in no change to the run-time mechanism.

#### C. THESIS ORGANIZATION

Chapter II describes the architecture of the AN/UYS-2 in detail and discusses the program interface. The modular design and actual components are elaborated. Chapter III studies the requirements of signal processing applications, examines the current AN/UYS-2 scheduling strategy, and proposes a deterministic scheduling approach. C++ code for the deterministic algorithm is provided. A simple graph is scheduled as an example. Chapter IV describes the simulator constructed for this thesis and its limitations. Background information and simulator specifics, including coding techniques, are also provided. Chapter V analyzes the performance of the non-deterministic and

deterministic algorithms by utilizing two key signal processing examples. Chapter VI provides a summary of the overall work, and gives recommendations for future expansion and improvement.

#### **II. ARCHITECTURE AND PROGRAMMING OF THE AN/UYS-2**

This chapter describes the architecture of the AN/UYS-2 in detail and discusses how the AN/UYS-2 is programmed to achieve its desired results. The data-flow principle is examined from the view point of the modular components.

#### A. ARCHITECTURE

Different DSP applications have specific processing requirements. The Navy's diverse operating environment, stringent operational tempo, and sundry weapon platforms contribute heavily towards the requirement for a modular based design. In addition, specific reliability criteria required in today's weapon systems are easier to implement and maintain in a modular system. Within the last twenty years, "... substantial reductions in the cost of digital computation have occurred accompanied by an improvement in performance, speed, memory capacity, and ease of programming ..." making modular design even more attractive [BEAUCHAMP 79, pp. iv]. Rapidly changing hardware technology and DSP requirements are easier to implement in a modular design. The AN/UYS-2 architecture provides for many modular machine configurations, tailoring itself to a set application, while maintaining a cohesiveness and implementation ease as an overall system. [POPS 90, pp. 2-6].

The AN/UYS-2 comes packaged in two Standard Electronic Module (SEM) type implementations which enable the unit to be configured for either ship based or aircraft mounting. The standard SEM "B" cabinet format and the smaller SEM "E" format which

optimizes the unit with regards to size and weight, making it ideal for aircraft dissemination. Within each SEM class, the AN/UYS-2's components are constructed on very high speed integrated circuit cards. Specific hardware implementation is documented by Rice. [RICE 90, pp. 4-7]

#### 1. Modularity

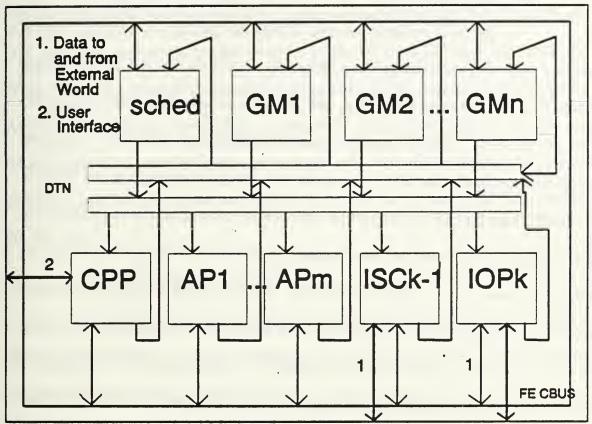

The AN/UYS-2's modular design is based on six functional element (FE) types: the Scheduler (SCH), the Arithmetic Processors (AP's), the Global Memories (GM's), the Input/Output Processors (IOP's), the Command Program Processor (CPP), and the Input Signal Conditioner's (ISC's); and two data paths: the Control Bus (CBUS) and the Data Transfer Network (DTN) as shown in Figure 1. These six FE types can be fused into any combination as long as the requirements specified in Table I are maintained, thereby enabling the AN/UYS-2 to be tailored to a specific application [APPLIC 90, pp. 2-3]. Each FE performs certain system tasks. The AN/UYS-2 layout enables the incorporation of new FE's into the modular structure as long as the communication interface to the DTN and CBUS remains constant.

These modular FE's perform parallel computation by associating "... each step of the algorithm with a node of a directed graph." [KARP 66, pp. 1390] As data for these nodes becomes available, each node must be scheduled to execute on an AP. This is accomplished by the scheduler. The actual programming approach is discussed later in this chapter.

Figure 1: The AN/UYS-2 Architecture

#### Table I: FUNCTIONAL ELEMENT REQUIREMENTS

|                 | Minimum | Maximum            |

|-----------------|---------|--------------------|

| Number of AP's  | 1       | 59 - IOP's - ISC's |

| Number of GM's  | 1       | 30                 |

| Number of SCH's | 1       | 1                  |

| Number of IOP's | 1 OR    | 59 - AP's - ISC's  |

| Number of ISC's | 1       | 59 - AP's - ISC's  |

| Number of CPP's | 1       | 1                  |

| Total Number    | 5       | 63                 |

#### a. The Scheduler

The SCH performs the node scheduling operation of matching a ready node to a free AP by maintaining four tables: the ready-node list, the free processing element (PE) list, the node status table, and the queue-to-node table [RICE 90, pp. 4, POPS 90, pp. 6-3]. The SCH receives queue information from the GM's. As queues exceed threshold levels, the GM's send queue over threshold messages to the SCH via the CBUS. Since the SCH also receives AP availability information via the CBUS, when all of a graph node's queues are over threshold, it then attempts to match free AP's to ready graph nodes. If a match is successful, and that graph node is not currently executing, scheduling data is sent to the GM's in the form of a message via the Control Bus (CBUS); and the database tables are updated to reflect the match. If a match is unsuccessful, the node status table and ready node list are updated to indicate the new ready node. When an AP indicates to the SCH that it is Ready For Instruction Stream (RFIS), the SCH checks the ready node list for nodes ready to execute and assigns one to the now available AP. [POPS 90, pp. 6-3]

#### b. The Global Memories

The GM provides the data storage for the AN/UYS-2 and executes memory management primitive functions. Each Processing Graph Methodology (PGM) queue, discussed later in this Chapter, is allocated to a GM for storage, and that GM maintains that queue's state information. Queue state information consists of read, produce, consume, and threshold quantities, queue size, and a queue identification number. When a queue exceeds threshold or capacity values, or returns under threshold,

the GM's notify the SCH via the CBUS. Upon receiving instructions from the SCH, the GM's send the appropriate *execute* messages to the AP's and IOP's via the CBUS and DTN. The GM's maintain the control variables and node information necessary for the AP's to execute the node successfully. After the AP has completed node breakdown and informed the GM, the GM consumes the input data involved by freeing the storage previously used by those queues and notifies the SCH of the current queue level. [POPS 90, pp. 7-9]

#### c. The Arithmetic Processors

After the SCH sends the node *execute* instruction to the GM's, the GM's relay the information, by another message via the CBUS, to an AP. The AP then executes the actual signal processing primitives. The message from the GM's contains all of the required information for the AP to read the necessary queue data from the GM's (set-up), execute the designated primitives, and write the output queue data back to the GM's (breakdown). The AP's consist of an Arithmetic Unit (AU) and a Control Unit (CU); consequently, three nodes can be associated with an AP at any one time:

- The first node being setup within the CU

- The next node executing within the AU

- The third node performing breakdown within the CU.

When the AP has completed execution of its current node and setup of its next node, it notifies the SCH via the CBUS that it is ready to process the following node. The ability of the CU to concurrently perform setup and breakdown on distinct nodes and to notify the SCH without the AU's knowledge helps to increase the concurrence involved with

minimum loss of through-put due to the non-availability of resources. [RICE 90, pp. 5, POPS 90, pp. 9-8]

#### d. The Input/Output Processors

The IOP's provide for raw digitized sensor data input and processed data output from the AN/UYS-2 by buffering and formatting the input and output data to synchronize the different external device data rates with the internal network. Upon arrival of sufficient external data as determined by input buffer size, the IOP's dispatch the input data to the GM queues after an amount specified by the application programmer is received. The IOP's receive the output data from the GM's and redirect it to the external world. [POPS 90, pp. 8-1]

#### e. The Input Signal Conditioner

In addition to performing the same functions as the IOP's, the ISC's perform signal conditioning operations to reduce input data bandwidth and generates output for sensor control. The ISC's are capable of performing analog-to-digital conversions during the input/output process. [POPS 90, pp. 10-1]

#### 2. Cohesiveness

Despite the modularity of the AN/UYS-2, key elements of its structure mold it into a cohesive unit. The cohesiveness is built around the ability of the modules to communicate and interact with each other. The communication among FE's occurs over the Data Transfer Network and Control Buses. All interaction between the user and the AN/UYS-2 occurs in the Command Program Processor.

#### a. Control Buses

The FE built-in-test control bus (BITCBUS) provides a means with which the Command Program Processor (CPP) can test the AN/UYS-2 system, and the CBUS provides the main means by which the modular FE's communicate short messages of data-flow control information [RICE 90, pp. 5].

#### b. Data Transfer Network

The DTN provides for up to 16 simultaneous, asynchronous, unidirectional 32-bit data transfers among FE's by continuously polling the data sources. When a source requests a transfer to a destination that is not already receiving data, the DTN path is established and the transfer conducted. Possible DTN configurations include 2, 4, 8, or 16 input and output ports; each port can have up to four further disseminations. [POPS 90, pp. 4-1]

#### c. Command Program Processor

The CPP provides the glue that holds the entire AN/UYS-2 architecture together. The CPP acts as the overall control unit for the AN/UYS-2 by performing the following functions:

- Data-flow graph management

- Tactical interface

- Input/output configuration control

- System performance monitoring [POPS 90, pp. 5-1].

#### **B.** Programming

New programming methodologies are required for data-flow architectures because data-flow computers depart from conventional architectures [DENNIS 83, pp. 331]. The AN/UYS-2 is programmed using the Enhanced Modular Signal Processor Common Operational Support Software, which refers to the implementation of the PGM on the AN/UYS-2 [POPS 90, pp. 2-8, ECOS 89, pp. 1-35].

#### 1. Graphical Interface

The PGM yields a convenient means of writing application software without concern for the specific architecture of the machine on which it would run [PGMTUT 90, pp. 1-1]. The PGM provides the application programmer with a high level graph oriented language, provides a method of translating these graphs into load modules that the AN/UYS-2 can recognize, and furnishes a run-time support environment which expands graph realizations and manages execution of graph instances [APPLIC 90, pp. 2-5].

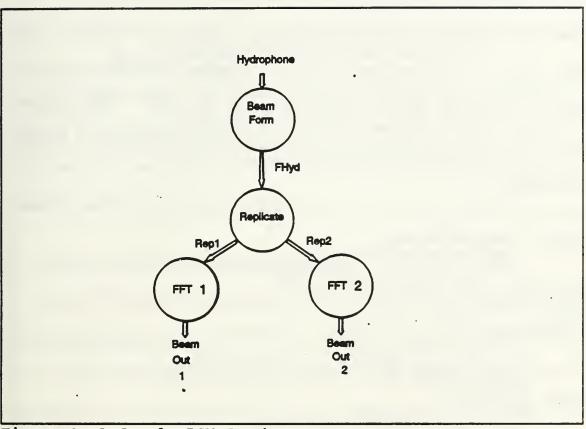

A PGM application consists of a *directed*, *acyclic* graph with nodes representing large grain computations called *primitives*, which are chosen from a selfcontained library of signal processing functions. A simple example PGM appears in Figure 2. The edges of the graph represent queues which receive data from the source primitive and supply data to the destination primitive. Conversion of the PGM description into a executable data-flow graph entails only specifying the read, produce, consume, and threshold values. The AN/UYS-2 is designed to run several signal processing applications simultaneously. Therefore, several instances of multiple PGM's

Figure 2: A Sample PGM Graph

may be running at the same time. The graph is loaded into the AN/UYS-2 by the CPP prior to graph initialization.

#### 2. Graph to Program Conversion

Since the AN/UYS-2 is unable to recognize the PGM graph directly as shown previously in Figure 2, the graph must be converted to a *key-word* program. This conversion is typically performed by machine utilizing the guidelines supplied in the Application Programmer User Manual [APPLIC 90, pp. all]. A possible program for the graph of Figure 2 appears in Figure 3. The node primitives that appear within the nodes are documented in the primitive library [PRIMLIB 90, pp. all]. The name of the graph is specified along with its external input and output queues. Constants are then initialized followed by a description of all queues and nodes. A queue is described by a name followed by a ":" and a type name. A node is completely described by a name, primitive, input queues "prim\_in", and output queues "prim\_out." The constructed program is then loaded into the AN/UYS-2 and executed by the CPP following the data-flow paradigm.

```

%graph (SamplePGMGraph

INPUTQ=Hydrophone : fixed(1)

OUTPUTQ=BeamOut1,BeamOut2 : int)

%GIP scan : int initialize to 4096

%Queue (FHyd : dfloat)

%Queue ([1..2]Rep : dfloat)

%Node (BeamForm

primitive=BFR FREO

prim in=scan, Hydrophone threshold=scan

prim out=FHyd)

%Node (Replicate

primitive=DFC REP

prim in=1,2,FHyd threshold=1

prim out=[1..2]Rep)

%Node (FFT1

primitive=FFT_CR

prim in=scan, [1]Rep threshold=scan

prim out=BeamOut1)

%Node (FFT2

primitive=FFT CR

prim in=scan, [2] Rep threshold=scan

prim out=BeamOut2)

%endgraph

```

```

Figure 3: Converted PGM Program

```

#### III. SCHEDULING OF PGM ON THE AN/UYS-2

This chapter diagrams the specific scheduling of PGM on the AN/UYS-2 by examining the signal processing requirements and the methods of resource allocation. The current First-Come-First-Served (FCFS) implementation and the proposed *real-time* scheduling algorithm are examined in detail.

#### A. SIGNAL PROCESSING REQUIREMENTS

Due to DSP's concurrency and high throughput requirements, large-grain data-flow programming models can be used effectively to exploit the intrinsic parallelism [PARHI 88, pp. 178]. General data-flow processing requires a direct hardware implementation of the data-flow paradigm [GURD 85, pp. 34-52, BROBST 87, pp. 40-45]. This results in unmanageable overheads. However, for specific classes of applications, such as signal processing, data-flow can be managed very efficiently at the macro level to obtain significant performance improvement. This is due to the ability of representing digital signal processing applications as synchronous data-flow graphs [LEE 87, pp. 24].

Executing data-flow descriptions of DSP's applications on parallel processors requires decisions about allocation, ordering, and data movement. In the AN/UYS-2 context, allocation refers to the assignment of PGM nodes to resources. GM's and AP's constitute the majority of the resources. Ordering relates the node assignment and execution sequence on these resources. Data movement reflects the method and amount of data internally transferred in between executions. Since large-grain data-flow architectures inherently possess a high decision making overhead, the data-flow principle must be allowed to take effect in order to capture the concurrency and minimize the decision making overhead. Synchronous applications assist in limiting this overhead. The three properties of these applications that make this possible are availability of *a priori*, knowledge of the amount of data produced and consumed, known function execution times, and negligible use of conditionals and recursion. [LEE 87, pp. 25-31]

## 1. Desirable Characteristics In Execution

In real-time signal processing applications, the principle requirements are predictability and performance as measured by throughput. An additional characteristic imposed by the AN/UYS-2 is on-line reconfiguration. Since the AN/UYS-2 is a dataflow architecture, this predictability is critical in Navy sensor systems. Given the nondeterminism of large-grain data-flow model and a set number of available resources for computational assignment, how can deterministic, rate-optimal through-put be guaranteed? While this question has spawned complete design environments like *Gabriel*, designed by Lee, the answer undoubtedly lies in resource allocation [LEE 89, pp. 333-335]. Efficient resource allocation and low communications overhead lead to the high through-put, deterministic output required by DSP.

## 2. Resource Allocation

Resource allocation forms the basis of the system designer's dilemma. Based on how a graph node and arc attributes are used at compile time and how much control information is generated to aid the run-time mechanisms, data-flow scheduling

implementations can be classified over a spectrum that ranges from *fully-dynamic* through *fully-static*. Although allocation can be *fully-dynamic*, *self-timed*, *static*, or *fully-static*, typical designs utilize a combination of these allocation methods. *Fully-dynamic* allocation performs all scheduling of nodes at run time based on the readiness of inputs. In *self-timed* allocation systems, the compiler determines the order of node execution and allocates resources, but the firing is determined at run-time by data arrival. *Static* node allocation involves the assignment of a node to a processor, but the order of execution is left up to the run time scheduler based on the node's inputs. In *fully-static* allocation, the compiler determines the exact firing time, assignment, and ordering of nodes based on that node's predicted behavior. [LEE 90, pp. 333-334]

Quasistatic scheduling methods are based on ordering memory accesses by blending the static and self-timed methods into a hybrid solution that supports Von Neumann Architectures without the need for specifically designed data-flow machines. Quasistatic scheduling maintains the ordering of nodes on processors while preserving the ordering of accesses to other shared system resources. Since quasistatic scheduling incorporates self-timed methods, node execution time can vary without affecting the results. Lee et al. have proposed utilizing hardware semaphore to overcome the high communication overheads generated by quasistatic methods [LEE 90, pp. 334-338].

Many different processor allocation schemes have been proposed that are inadequate for actual data-flow systems [DAVIS 79, pp. 1079-1086, ARVIND 80, pp. 7-14, MUNDELL 81, pp. 156-157]. Systems like *Gabriel*, characterized by Lee, utilize compile time static resource assignment and work well on sequential data-flow graphs,

whose very nature enables nodes to be scheduled at compile time rather than run time, relying on the graph structure for enforcement. Periodic Admissible Parallel Schedule (PAPS), also proposed by Lee, assumes sequential data-flow and establishes precedence links between nodes in the graph and synchronizes these links at every graph instance [LEE 87, pp. 25-28]. *Quasistatic* methods ensure run time enforcement by utilizing dynamic control [LEE 87, pp. 25-28]. While algorithms proposed by Ho and Irani maintain concurrency, they do not guarantee deterministic throughput [HO 83].

As mentioned previously, the AN/UYS-2 possesses several sets of resources: the AP's, GM's, IOP's, ISC's, DTN, and CBUS. IOP's and ISC's are hardwired into a certain configuration for the external world. GM's are allocated at compile time when the graph is initiated, and are assigned based solely on the graph queue structure with all input queues associated with a node being assigned to the same GM if possible. AP's are allocated to execute specific graph nodes by the scheduler as they become ready on a first-come-first-served basis at run time. The DTN and CBUS are configured and hardwired for its specific structure during assembly, but individual messages are not allocated to it until run time. [POPS 90, pp. 3-8]

## B. FIRST-COME-FIRST-SERVED SCHEDULING

The simple nature of the SCH is motivated by the requirements that it should not be a bottleneck, that it should maintain a high and balanced AP utilization, that it should incorporate multiple applications simply, and that it should behave well during reconfiguration. The SCH implements First-Come-First-Served (FCFS) scheduling by

maintaining a database consisting of PGM graph node and AP information. Available AP's are matched with ready nodes on a continuing basis, interrupted only by user reconfiguration of the system. If the SCH is unable to execute a match, either due to no free AP's or no ready nodes, then the SCH maintains a free AP list and a ready node list. The SCH matches the elements from the lists together in the same FCFS manner as they become available.

#### 1. Advantages

The simplicity of FCFS scheduling earns it the designation as the most attractive scheduling algorithm. The FCFS scheduling algorithm's low *run-time* overhead costs also lends itself to the AN/UYS-2. This simple algorithm ensures close to the maximum possible AP utilization since nodes are sent to AP's as soon as they become available.

#### 2. Disadvantages

The major disadvantage within the AN/UYS-2 scheduling arises from unpredictability in EMSP output arrival. The dynamic assignment of AP's to ready nodes suffers from the following intrinsic disadvantage when data arrives periodically from the external world. The nodes that depend only upon the receipt of external data get ready for execution, and therefore enter the ready list at a rate which is independent of the other nodes. If the graph latency is longer than the data arrival period, nodes in the lower portion of the graph get ready after nodes in the upper portion. Since the machine follows a FCFS node to AP assignment strategy, the top nodes execute at a higher rate

than the nodes lower down in the graph. The lower graph nodes' execution will catch up only as the upper nodes' output queues exceed capacity and prevent the top nodes from entering the ready list. As a result, processed output data arrives unpredictably leading to the possibility of intolerable delays and insufficient buffer space especially under high loads. This non-uniformity in output arrival arises because the task-level dataflow mechanism does not allow any mechanism to control the input nodes [SHUKLA 91, pp. 222-231]. It will be present when the resource allocation at all stages of the parallel machine is not coupled to the input data arrival and has been observed due to FCFS scheduling [SHUKLA 91, pp. 222-231].

### 3. A Simple Example

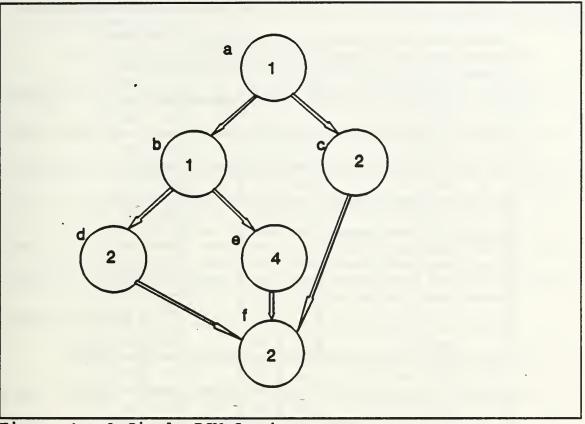

The PGM graph shown in Figure 4, a simple graph with six nodes whose AP execution time are shown inside the vertices, can be used to demonstrate FCFS scheduling. For simplicity, we neglect the set-up and break-down times associated with each node. Consider that an AN/UYS-2 with two AP's, each of which has a processing speed of one unit, should be able to attain a maximum data rate and start a new graph instance every:

$$\frac{TotalExecutionTime}{Number of AP's} = \frac{12}{2} = 6Cycles.$$

(1)

Assume, for simplicity of explanation, that data arrives at this exact rate. A possible resulting order of execution utilizing FCFS scheduling is documented in Table II. The non-uniformity that exists in the instance completion times is inherently obvious in this table by examining the clock cycles for node "f." It should be noted that this is only one

Figure 4: A Simple PGM Graph

possible FCFS scheduling order. Different orders are possible due to set-up and breakdown delays affecting the node arrival order at the SCH.

# C. REVOLVING CYLINDER SCHEDULING

While the simple dispatcher works quite well as a run-time mechanism, it does not yield easily to compile-time analysis. This technique restructures the graphical application description by performing compile-time analysis of the application execution profile. Given a graph, it is possible to systematically determine whether it can be mapped on a certain number of AP's while satisfying the required data rates. It can be proved that the graph can be scheduled (ignoring overheads) such that the consecutive graph instances are

| Table II: EXECUTION | OF 36 | CYCLES | UTILIZING | FCFS | SCHEDULING |

|---------------------|-------|--------|-----------|------|------------|

|---------------------|-------|--------|-----------|------|------------|

| Cycle | AP1 | AP2 | Cycle | AP1 | AP2        | Cycle | AP1 | AP2        |

|-------|-----|-----|-------|-----|------------|-------|-----|------------|

| 1     | a1  | L   | 13    | b3  | e2         | 25    | e4  | b5         |

| 2     | b1  | c1  | 14    | d3  | <b>c</b> 3 | 26    | c5  | e5         |

| 3     | dl  | c1  | 15    | d3  | <b>c</b> 3 | 27    | c5  | e5         |

| 4     | dl  | el  | 16    | e3  | f2         | 28    | d5  | e5         |

| 5     | L   | el  | 17    | e3  | f2         | 29    | d5  | e5         |

| 6     | a2  | e1  | 18    | e3  | a4         | 30    | f5  | f4         |

| 7     | b2  | el  | 19    | e3  | b4         | 31    | f5  | f4         |

| 8     | c2  | f1  | 20    | f3  | d4         | 32    | a6  | L          |

| 9     | C2  | f1  | 21    | f3  | d4         | 33    | C6  | b6         |

| 10    | d2  | e2  | 22    | e4  | C4         | 34    | C6  | <b>e</b> 6 |

| 11    | d2  | e2  | 23    | e4  | C4         | 35    | d6  | e6         |

| 12    | a3  | e2  | 24    | e4  | a5         | 36    | d6  | <b>e</b> 6 |

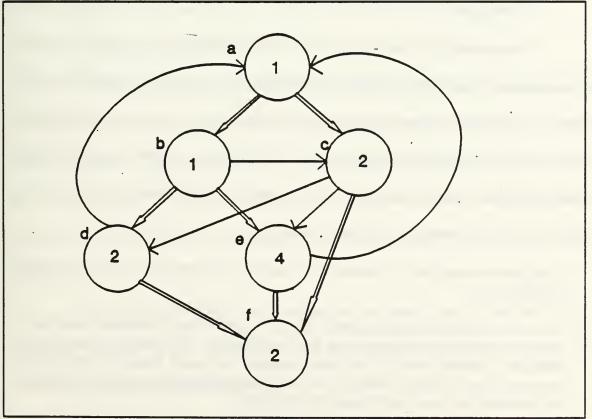

separated by a time equal to the *total execution time* of the PGM divided by the number of AP's. Since the AP's will be fully utilized, this time corresponds to the maximum throughput rate. The key idea in the Revolving Cylinder (RC) assignment is that inserting delays in the PGM can produce a graph with better throughput. The idea behind RC scheduling can be traced back to algorithms for overlapping complex operations on pipelined processors [RAU 82, pp. 131-139, SHUKLA 91, pp. 222-231].

## 1. Implementation

RC scheduling recommends when a graph node should be scheduled, but choosing the AP to schedule it on is left to the run-time dispatcher. This enables the actual scheduling to remain *dynamic*. Assume that there is a cylinder whose circumference is the sum of all of the nodes' execution times divided by the number of AP's in the AN/UYS-2 structure. The idea is to schedule the graph such that it wraps around the cylinder, thereby causing its end to meet its beginning. The separation of beginning from end has the effect of a *divide-by-circumference* counter every time the beginning meets the end.

Each slot in the cylinder is of width equal to the smallest size node in the graph. For each node in the graph, starting with the top and working towards the bottom, attempt to schedule the node at its earliest start time. If it can not be inserted at that time, delay the start time by the width of a slot and repeat until it can be inserted. Adjust the earliest start time of all descendants of that node and repeat the above sequence with the next node as the top node in the graph. This ensures that maximum cylinder usage will result when the cylinder is filled by these algorithms shown in Figure 5.

Once all nodes have been inserted into the cylinder and the cylinder is full, assign dependencies to the nodes based upon their location in the cylinder. For each entry relegated to an AP in the cylinder, if there are other nodes assigned to the same AP with the same index and the node higher up in the cylinder is not an ancestor of the other, then create a dependency from the higher node to the lower. This algorithm is shown in Figure 6. Figure 7 shows a possible restructuring resulting from these

```

procedure Assign RC(G,P); /*G is a directed acyclic graph*/

/*P is the number of AP's*/

q ← topological sort(G);/*O(e), q is a queue*/

for all nodes ni

est(n_i) \leftarrow 0;

/*est is the earliest start time*/

circumference \leftarrow 0;

for all nodes n;

circumference \leftarrow circumference + w(n_i);

/*w(n_i) is the size of the node n_i * \bar{/}

circumference + [(circumference/P)];

while q is not empty

temp \leftarrow remove top(q);

if sufficient space available in cylinder

t + schedule_node(temp, est(temp), cylinder);

for all descendants of temp

est(descendent) + max(est(descendent), t + w(temp);

else

cylinder - increase cylsize(cylinder,circumference,w)

end(if)

end(while)

headofdepqs + create deps(cylinder,circumference,w);