**Calhoun: The NPS Institutional Archive**

Theses and Dissertations

Thesis Collection

2000-06

Implementation of a fault tolerant computing testbed: a tool for the analysis of hardware and software fault handling techniques

Summers, David C.

Monterey, California. Naval Postgraduate School

Calhoun is a project of the Dudley Knox Library at NPS, furthering the precepts and goals of open government and government transparency. All information contained herein has been approved for release by the NPS Public Affairs Officer.

Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943 NPS ARCHIVE 2000.06 SUMMERS, D. DUDLEY KNOX LIBRARY

NAVE POSTGRADUATE SCHOOL

MONTEREY CA 93943-5101

# NAVAL POSTGRADUATE SCHOOL Monterey, California

# **THESIS**

IMPLEMENTATION OF A FAULT TOLERANT COMPUTING TESTBED:

A TOOL FOR THE ANALYSIS OF HARDWARE AND SOFTWARE FAULT HANDLING TECHNIQUES

by David C. Summers

June 2000

Thesis Co-advisors:

Alan A. Ross Herschel H. Loomis

Approved for public release; distribution is unlimited.

# REPORT DOCUMENTATION PAGE

Form Approved

OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington DC 20503.

2. REPORT DATE 1. AGENCY USE ONLY (Leave blank) 3. REPORT TYPE AND DATES COVERED June 2000 Master's Thesis 4. TITLE AND SUBTITLE 5. FUNDING NUMBERS Implementation of a Fault Tolerant Computing Testbed: A Tool for the Analysis of Hardware and Software Fault Handling Techniques 6. AUTHOR(S) Summers, David C. 8. PERFORMING 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) ORGANIZATION REPORT Naval Postgraduate School NUMBER Monterey, CA 93943-5000 9. SPONSORING / MONITORING AGENCY NAME(S) AND ADDRESS(ES) 10. SPONSORING / MONITORING AGENCY REPORT NUMBER

#### 11. SUPPLEMENTARY NOTES

The views expressed in this thesis are those of the author and do not reflect the official policy or position of the Department of Defense or the U.S. Government.

12a. DISTRIBUTION / AVAILABILITY STATEMENT

12b. DISTRIBUTION CODE

Approved for public release; distribution is unlimited.

#### 13. ABSTRACT (maximum 200 words)

With spacecraft designs placing more emphasis on reduced cost, faster design time, and higher performance, it is easy to understand why more commercial-off-the-shelf (COTS) devices are being used in space based applications. The COTS devices offer spacecraft designers shorter design-to-orbit times, lower system costs, orders of magnitude better performance, and a much better software availability than their radiation hardened (radhard) counterparts. The major drawback to using COTS devices in space is their increased susceptibility to the effects of radiation, single event upsets (SEUs) in particular.

This thesis will focus on the implementation of a fault tolerant computer system. The hardware design presented here has two different benefits. First, the system can act as a software testbed, which allows testing of software fault tolerant techniques in the presence of radiation induced SEUs. This allows the testing of the software algorithms in the environment they were designed to operate in without the expense of being placed in orbit. Additionally, the design can be used as a hybrid fault tolerant computer system. By combining the masking ability of the hardware with supporting software, the system can mask out and reset processor errors in real time. The design layout will be presented using OrCAD® schematics.

| 14. SUBJECT TERMS Fault Tolerant Computing, Triple Modular Redundancy (TMR), Commercial-Off-The-Shelf (COTS) Devices, Single Event Upsets (SEU) |                                                             |                                                      |                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------|-------------------------------------|

|                                                                                                                                                 |                                                             |                                                      | 16. PRICE CODE                      |

| 17. SECURITY CLASSIFICATION OF REPORT Unclassified                                                                                              | 18. SECURITY CLASSIFICATION OF<br>THIS PAGE<br>Unclassified | 19. SECURITY CLASSIFICATION OF ABSTRACT Unclassified | 20. LIMITATION<br>OF ABSTRACT<br>UL |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. 239-18

# Approved for public release; distribution is unlimited

# IMPLEMENTATION OF A FAULT TOLERANT COMPUTING TESTBED: A TOOL FOR THE ANALYSIS OF HARDWARE AND SOFTWARE FAULT HANDLING TECHNIQUES

David C. Summers Captain, United States Marine Corps B.S., Texas A&M University, 1995

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

NAVAL POSTGRADUATE SCHOOL June 2000

#### **ABSTRACT**

With spacecraft designs placing more emphasis on reduced cost, faster design time, and higher performance, it is easy to understand why more commercial-off-the-shelf (COTS) devices are being used in space based applications. The COTS devices offer spacecraft designers shorter design-to-orbit times, lower system costs, orders of magnitude better performance, and a much better software availability than their radiation hardened (radhard) counterparts. The major drawback to using COTS devices in space is their increased susceptibility to the effects of radiation, single event upsets (SEUs) in particular.

This thesis will focus on the implementation of a fault tolerant computer system. The hardware design presented here has two different benefits. First, the system can act as a software testbed, which allows testing of software fault tolerant techniques in the presence of radiation induced SEUs. This allows the testing of the software algorithms in the environment they were designed to operate in without the expense of being placed in orbit. Additionally, the design can be used as a hybrid fault tolerant computer system. By combining the masking ability of the hardware with supporting software, the system can mask out and reset processor errors in real time. The design layout will be presented using OrCAD® schematics.

V

34.00 ft

# TABLE OF CONTENTS

| I.   | INTR | ODUCTION                                       | 1         |

|------|------|------------------------------------------------|-----------|

|      | A.   | THE SPACE ENVIRONMENT                          | 2         |

|      |      | 1. Vacuum                                      | 2         |

|      |      | 2. Meteoroids                                  | 3         |

|      |      | 3. Temperature                                 | 3         |

|      |      | 4. Radiation                                   | 4         |

|      | В.   | SINGLE EVENT EFFECTS (SEE)                     | 5         |

|      |      | 1. Single Event Latchup (SEL)                  | 6         |

|      |      | 2. Single Event Transient (SET)                | 6         |

|      |      | 3. Single Event Upsets (SEU)                   | 7         |

|      | C.   | COMMERCIAL-OFF-THE-SHELF VS. RADIATION HARDENI | ΞD        |

|      |      | DEVICES                                        | 7         |

|      |      | 1. Cutting Edge Technology                     | 8         |

|      |      | 2. Faster Design-to-Orbit Time                 | 8         |

|      |      | 3. Reduced Cost                                | 8         |

|      | D.   | PURPOSE                                        | 9         |

|      | E.   | THESIS ORGANIZATION                            | 10        |

| II.  | BACK | GROUND                                         | 11        |

|      | A.   | REDUNDANCY                                     |           |

|      |      | 1. Software Redundancy                         | 11        |

|      |      | 2. Information Redundancy                      | 12        |

|      |      | 3. Time Redundancy                             | 13        |

|      |      | 4. Hardware Redundancy                         | 13        |

|      |      | 5. TMR Implementations                         |           |

|      | В.   | SOFTWARE VS HARDWARE REDUNDANCY                | <b>16</b> |

|      | C.   | TMR MICROPROCESSOR DESIGN                      | <b>17</b> |

|      |      | 1. Processor Selection                         | 17        |

|      |      | 2. Hardware Design                             | 18        |

|      |      | 3. Software Design                             | 20        |

| III. | HARD | OWARE DESIGN SPACE                             | 23        |

|      |      |                                                | 23        |

|      |      | 1. Evaluation Board                            | 24        |

|      |      | 2. Space Flight Board                          | 25        |

|      |      | 3. Accelerator Testing                         | 25        |

|      | В.   | SYSTEM OVERVIEW                                | 26        |

|      | C.   | SYSTEM SUPPORT ELEMENTS                        | 29        |

|      |      | 1. Discrete Components                         | 29        |

|      |      | 2. Timing Interface                            | 29        |

|      |      | a) CPU Oscillator                              | 30        |

|     |           |      | b) UART Oscillator                           | 31 |

|-----|-----------|------|----------------------------------------------|----|

|     |           |      | c) Buffer/Driver Logic                       | 32 |

|     |           | 3.   | Reset System                                 | 33 |

|     |           | 4.   | Mode Select                                  | 35 |

|     |           | 5.   | Test Connectors                              | 37 |

|     | D.        | MIC  | ROPROCESSOR AND ADDRESS LATCH                | 38 |

|     |           | 1.   | Microprocessor                               | 38 |

|     |           | 2.   | Address Latch                                |    |

|     | E.        | MEN  | MORY SPACE                                   | 39 |

|     |           | 1.   | R3081 Memory Space                           | 39 |

|     |           | 2.   | PROM                                         |    |

|     |           | 3.   | SRAM                                         |    |

|     |           |      | a) Size                                      |    |

|     |           |      | b) Memory Segments                           |    |

|     |           | 4.   | Input/Output (I/O)                           |    |

|     |           |      | a) Interface Type                            |    |

|     |           |      | b) I/O Interface Implementation              |    |

|     | F.        | FIFO | O INTERFACE                                  |    |

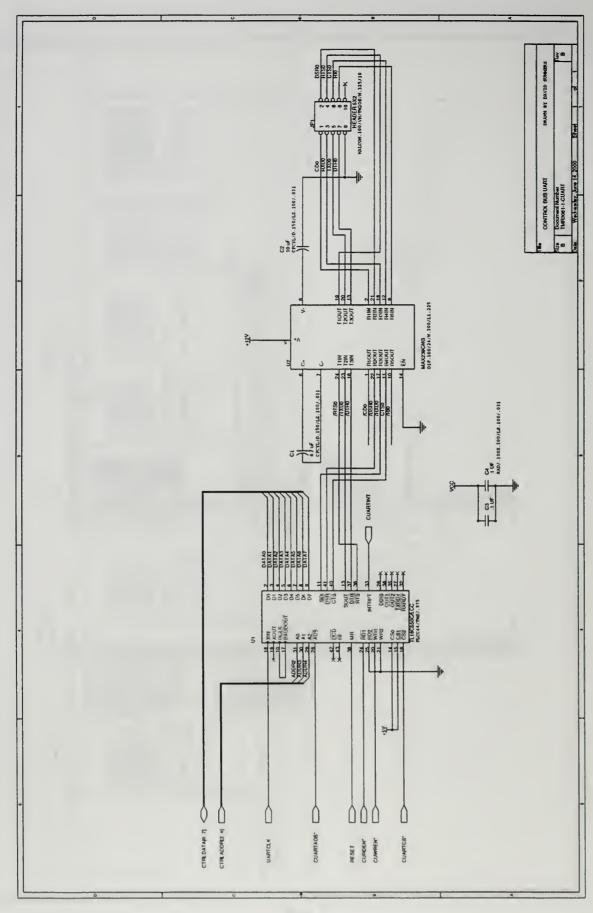

|     | ~ *       | 1.   | Control Bus Design                           |    |

|     |           | 2.   | FIFO Selection                               |    |

|     |           |      |                                              |    |

| IV. |           |      | MABLE LOGIC DESIGN                           |    |

|     | <b>A.</b> |      | DESIGN                                       |    |

|     |           | 1.   | Memory Controller PLD                        |    |

|     |           |      | a) Counter                                   |    |

|     |           |      | b) Cycle End (CYCEND*)                       |    |

|     |           |      | c) Read Buffer Clock Enable (RDCEN*)         |    |

|     |           |      | d) Acknowledge (ACK*)                        |    |

|     |           |      | e) Bus Error (BUSERR*)                       |    |

|     |           |      | f) Voter Interrupt (VOTINT*)                 |    |

|     |           | 2.   | Memory Enable PLD                            |    |

|     |           |      | a) Read Enable (RDEN*)                       |    |

|     |           |      | b) Write Enables                             |    |

|     |           |      | c) Data Enables                              |    |

|     |           |      | d) Synchronous Resets                        |    |

|     | В.        | FPG  | A DESIGN                                     |    |

|     |           | 1.   | FPGA Selection                               |    |

|     |           | 2.   | Address Voter, Memory Decoder, and Timer FPG |    |

|     |           |      | a) Address Voter                             |    |

|     |           |      | b) Memory Decoder                            |    |

|     |           |      | c) Timer                                     | 72 |

|     |           |      | ,                                            |    |

|     |           | 3.   | Control and Data Voter FPGA                  |    |

|     |           | 3.   | Control and Data Voter FPGA                  |    |

|     |           | 3.   | Control and Data Voter FPGA                  |    |

|      |           | 4.    | System Controller FPGA                             | 81  |

|------|-----------|-------|----------------------------------------------------|-----|

|      |           |       | a) Interrupt Enable (INTEN*)                       | 82  |

|      |           |       | b) Control UART (CUART) Initialization             | 83  |

|      |           |       | c) FIFO Data Collection                            | 84  |

|      |           |       | d) FIFO Data Transfer                              | 87  |

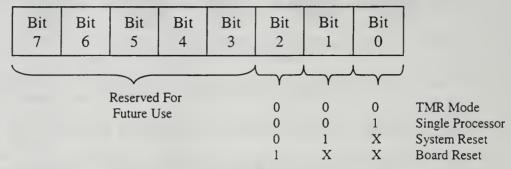

|      |           |       | e) TMR Mode Control                                | 93  |

|      | C.        | DET   | TAILED SYSTEM TIMING ANALYSIS                      | 94  |

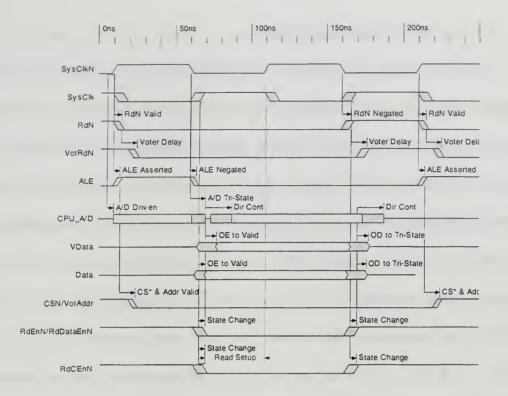

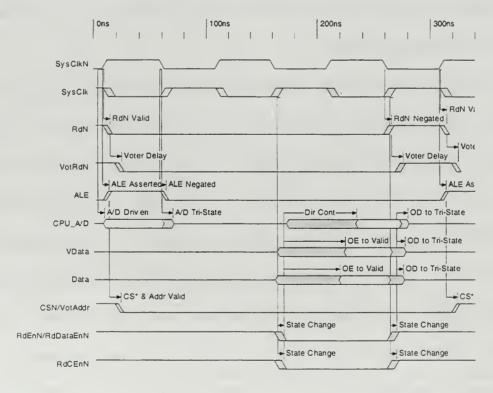

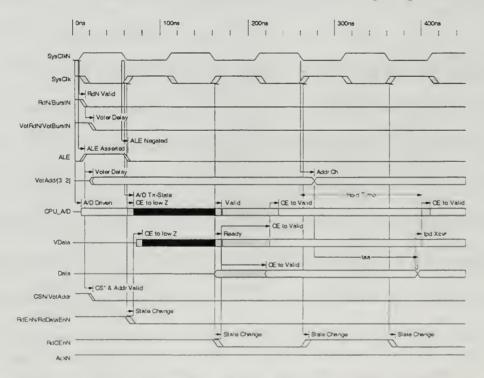

|      |           | 1.    | Single Word Read Cycles                            | 95  |

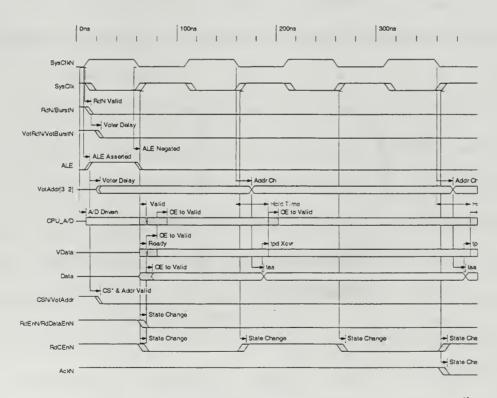

|      |           | 2.    | Quad-Word Read Cycles                              | 98  |

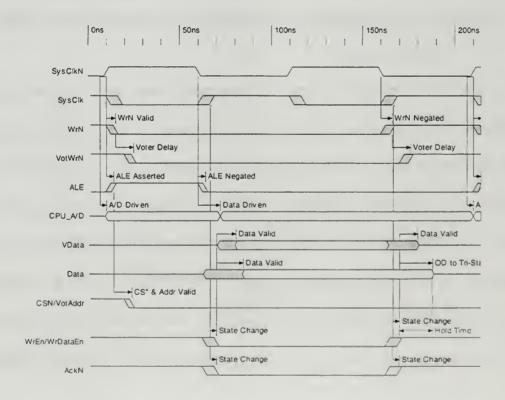

|      |           | 3.    | Write Cycles                                       |     |

| V.   | MA        | NUFAC | CTURING AND DESIGN REVIEW                          | 103 |

|      | <b>A.</b> | PCB   | FABRICATION                                        | 103 |

|      | В.        | WH    | ITE WIRES                                          | 105 |

| VI.  | CON       | CLUS  | IONS AND FOLLOW-ON RESEARCH                        | 109 |

|      | A.        | CON   | NCLUSIONS                                          | 109 |

|      | В.        | FOL   | LOW-ON RESEARCH                                    | 110 |

|      |           | 1.    | Completion of TMR Implementation                   | 111 |

|      |           | 2.    | Radiation Testing                                  | 112 |

|      |           | 3.    | Conversion to Space Flight Board                   |     |

|      |           | 4.    | Application to a State-of-the-Art (SOTA) Processor | 113 |

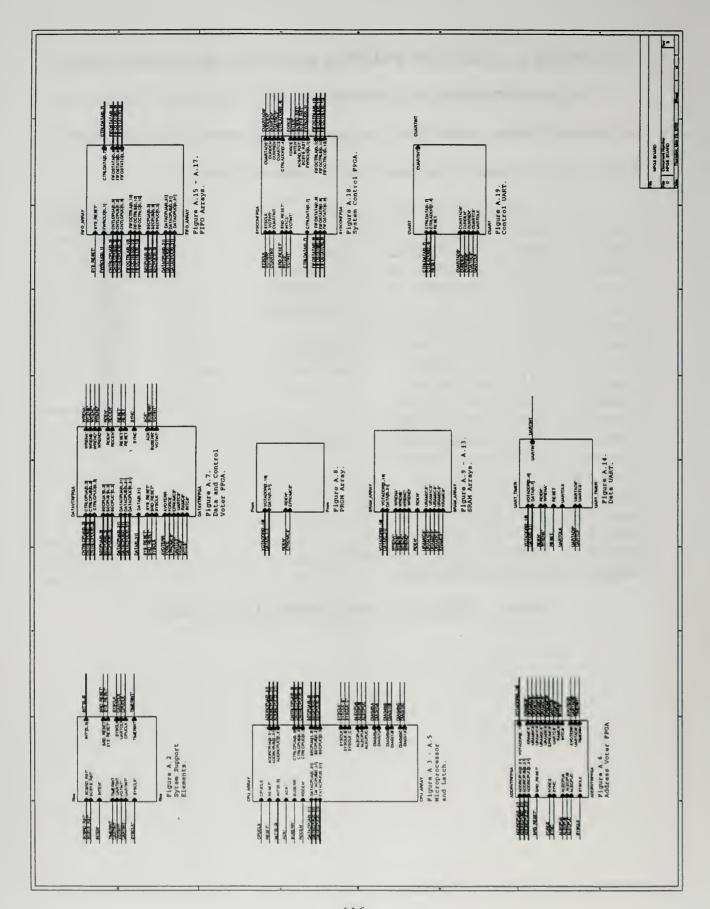

| APP  | ENDIX     | A. TN | MR IMPLEMENTATION ORCAD SCHEMATICS                 | 115 |

| APPI | ENDIX     | B. W  | INCUPL FILES                                       | 135 |

|      | 1.        |       | MORY CONTROL PLD PROGRAM FILE                      |     |

|      | 2.        | ME    | MORY CONTROL PLD SIMULATION OUTPUT FILE            | 139 |

|      | 3.        | MEN   | MORY ENABLE PLD PROGRAM FILE                       | 141 |

|      | 4.        | MEN   | MORY ENABLE PLD SIMULATION FILE                    | 144 |

| APPI | ENDIX     | C. XI | LINX FOUNDATION DESIGNS                            | 145 |

|      | 1.        | ADD   | ORESS VOTER FPGA                                   | 145 |

|      | 2.        | DAT   | TA AND CONTROL VOTER FPGA                          | 153 |

| LIST | OF R      | EFERE | ENCES                                              | 163 |

| INIT | TALD      | ISTRI | RUTION LIST                                        | 167 |

THIS PAGE INTENTIONALLY LEFT BLANK

# TABLE OF FIGURES

| Figure 2.1. 3-1 | Bit Majority Voter Logic Diagram. After Ref. [7]              | 14 |

|-----------------|---------------------------------------------------------------|----|

| Figure 2.2. Ba  | sic TMR Circuit Implementation. After Ref. [7]                | 15 |

| Figure 2.3. Tri | iplicated TMR Voters. After Ref. [7]                          | 16 |

| Figure 2.4. Sin | mple R3081 Board Design. After Ref. [11]                      | 19 |

|                 | AR R3081 Board Design. From Ref. [9]                          |    |

|                 | IR FIFO Interface. From Ref. [9]                              |    |

| _               | AR R3081 Block Diagram                                        |    |

| Figure 3.2. Tin | ming Interface                                                | 30 |

| Figure 3.2. Tin | ming Interface                                                | 30 |

| Figure 3.3. TN  | AR Reset System                                               | 34 |

| Figure 3.4. Int | errupt/Mode Logic                                             | 36 |

| Figure 3.5. Vii | rtual to Physical Address Translation. From Ref. [10]         | 40 |

|                 | s/UART/Line Driver Interconnections. From Ref. [22]           |    |

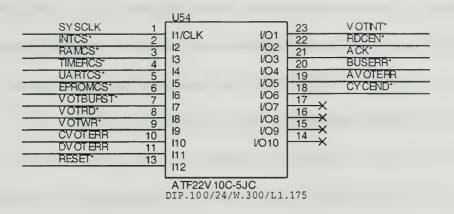

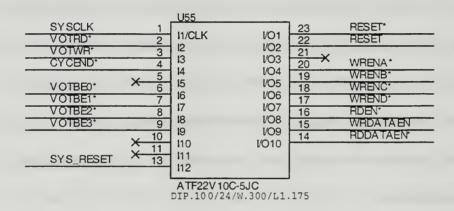

| Figure 4.1. Pro | ogrammable Logic Device Identifier                            | 53 |

| Figure 4.2. Me  | emory Controller PLD                                          | 57 |

| Figure 4.3. Me  | emory Enable PLD                                              | 62 |

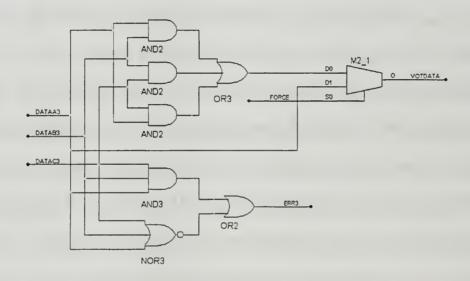

| Figure 4.4. 3-I | Bit Majority Voter/Error Detector                             | 70 |

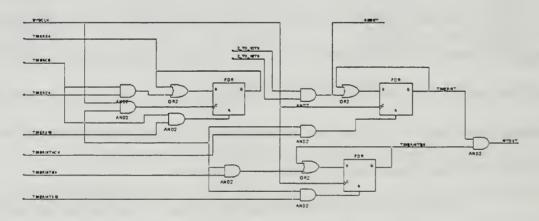

| Figure 4.5. Tir | mer Enable/Disable/Interrupt Design                           | 74 |

| Figure 4.6. Tra | ansceiver Logic Design                                        | 78 |

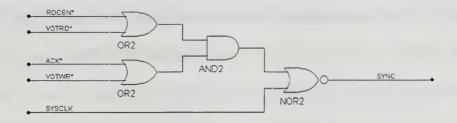

| Figure 4.7. SY  | 'NC Signal Design                                             | 81 |

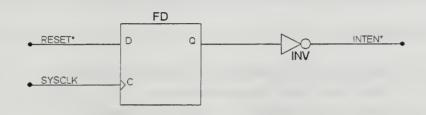

| Figure 4.8. IN  | TEN* Signal Design                                            | 83 |

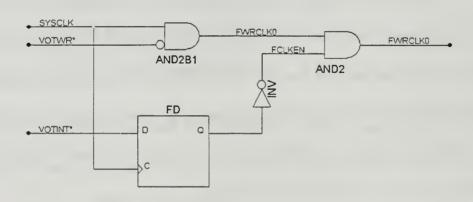

| Figure 4.9. FW  | VRCLK0 Signal Design                                          | 86 |

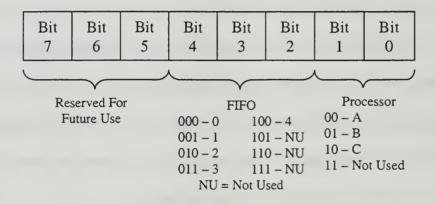

|                 | leader Byte Design                                            |    |

| Figure 4.11. D  | ata Transfer FSM Design                                       | 89 |

| Figure 4.12. Pr | rocessor Select FSM                                           | 90 |

| Figure 4.13. F. | IFO Select FSM Design                                         | 91 |

| Figure 4.14. B  | yte Select FSM Design                                         | 93 |

| Figure 4.15. T. | MR Mode Select Register Design                                | 94 |

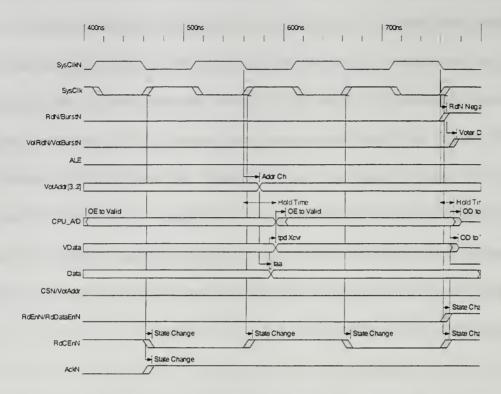

| Figure 4.16. Z  | ero Wait State Read Timing Diagram                            | 97 |

|                 | ingle Wait State Read Timing Diagram                          |    |

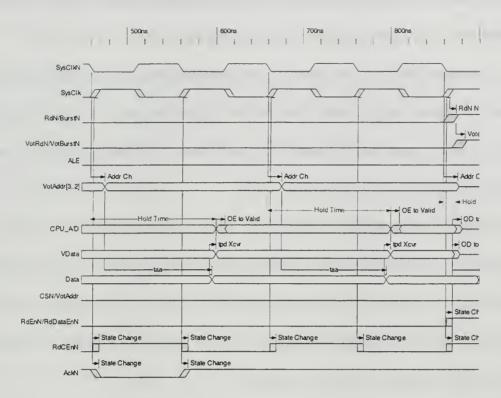

|                 | ero Wait State Quaded Word Read Timing Diagram (1st Half)     |    |

|                 | ero Wait State Quaded Word Read Timing Diagram (2nd Half) 1   |    |

|                 | ingle Wait State Quaded Word Read Timing Diagram (1st Half) 1 |    |

|                 | ingle Wait State Quaded Word Read Timing Diagram (2nd Half) 1 |    |

|                 | ero Wait State Write Timing Diagram1                          |    |

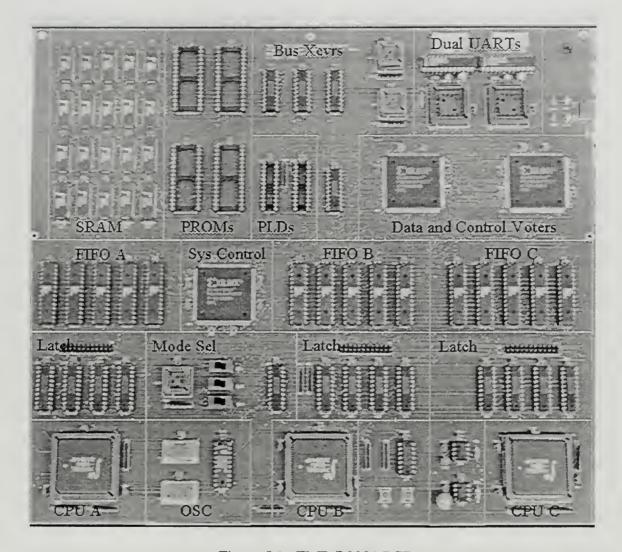

|                 | 1R R3081 PCB1                                                 |    |

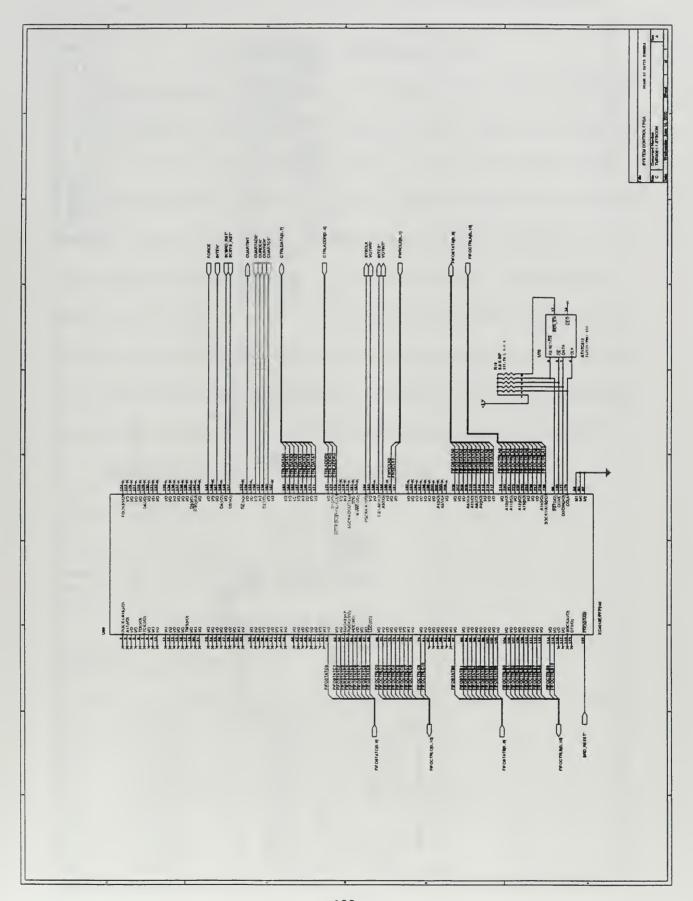

|                 | MR R3081 Top Level Schematic                                  |    |

|                 | stem Support Elements Schematic                               |    |

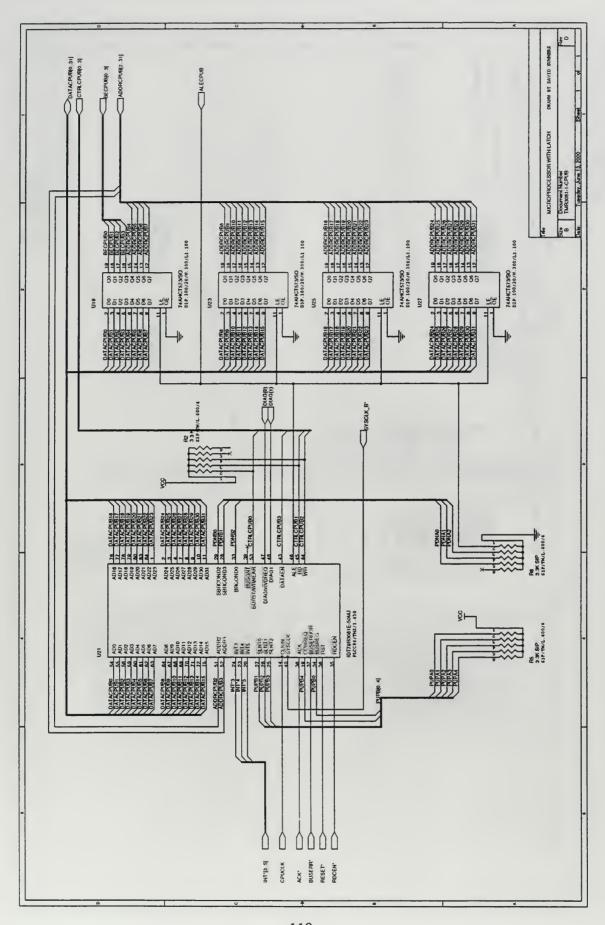

|                 | PU A Microprocessor and Latch Schematic                       |    |

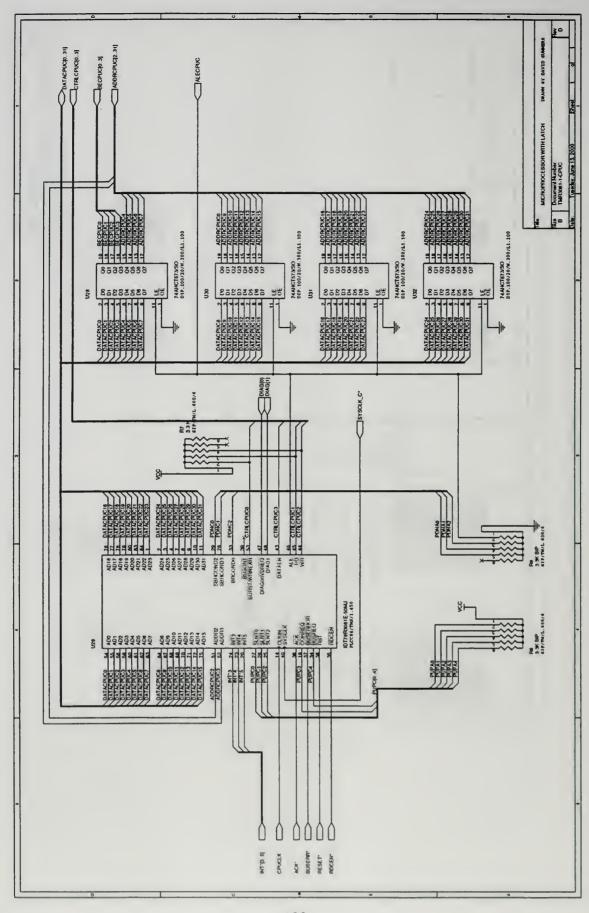

| _               | PU B Microprocessor and Latch Schematic                       |    |

| Figure A.5. CI  | PU C Microprocessor and Latch Schematic                       | 20 |

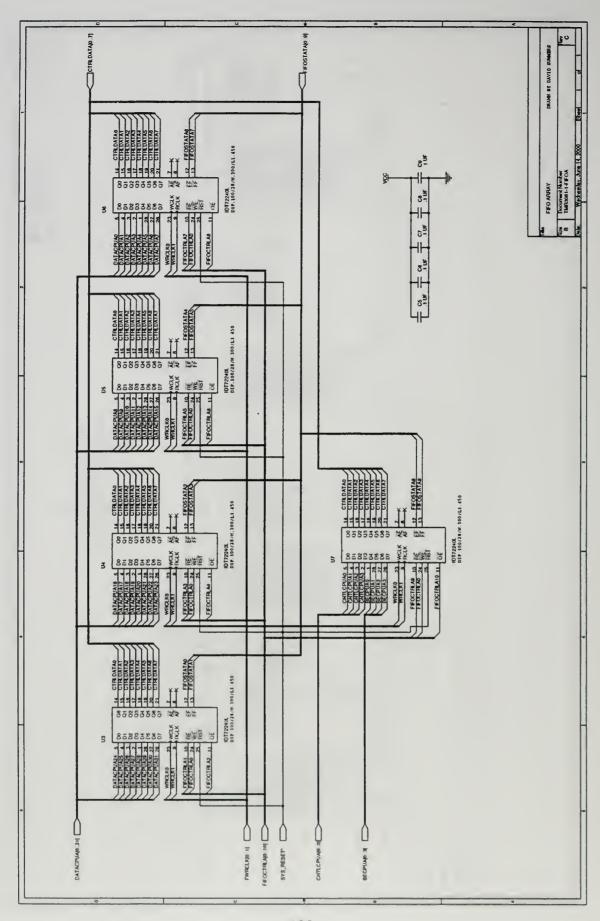

| Figure A.6. Address Voter FPGA Schematic                    | . 121 |

|-------------------------------------------------------------|-------|

| Figure A.7. Data and Control Voter FPGA Schematic           | 122   |

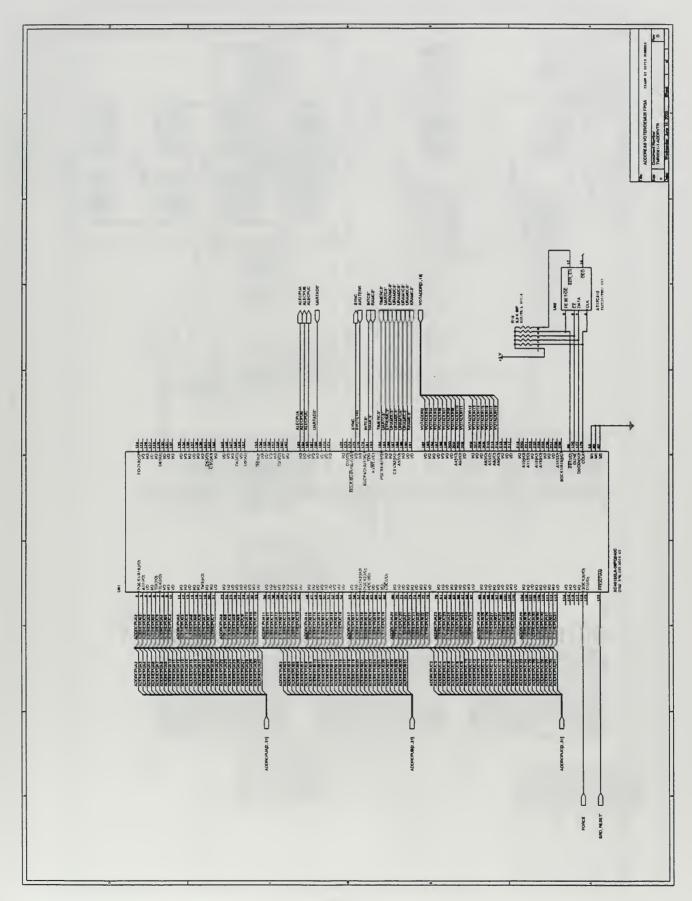

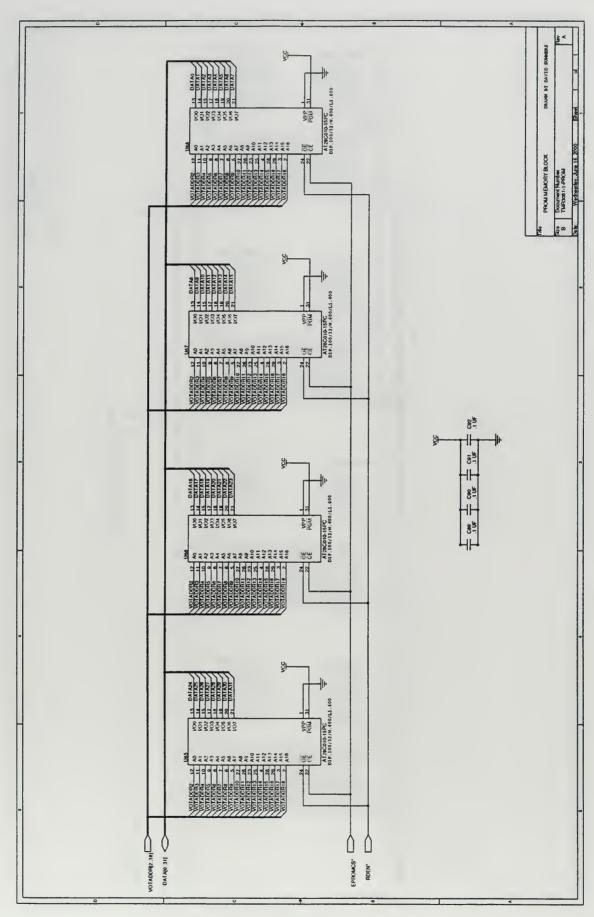

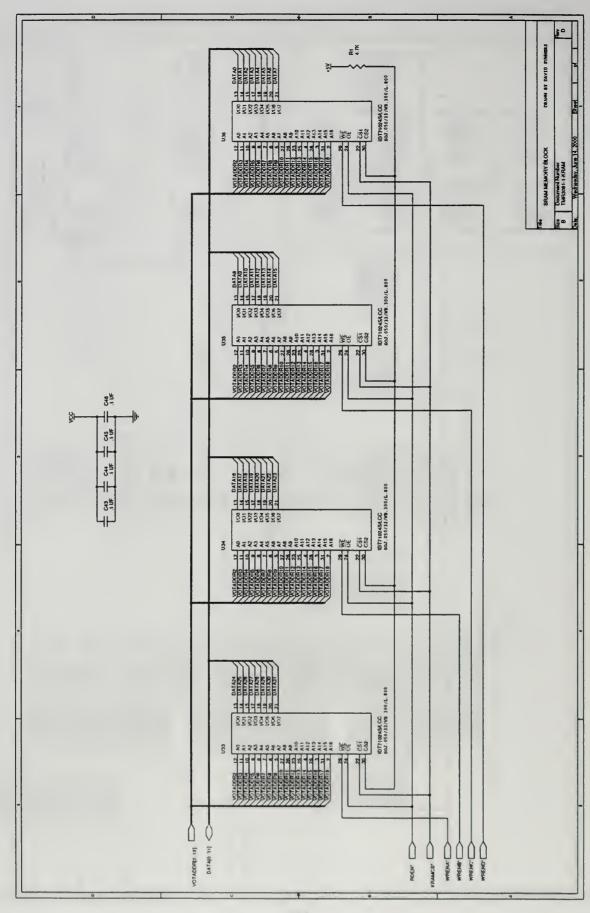

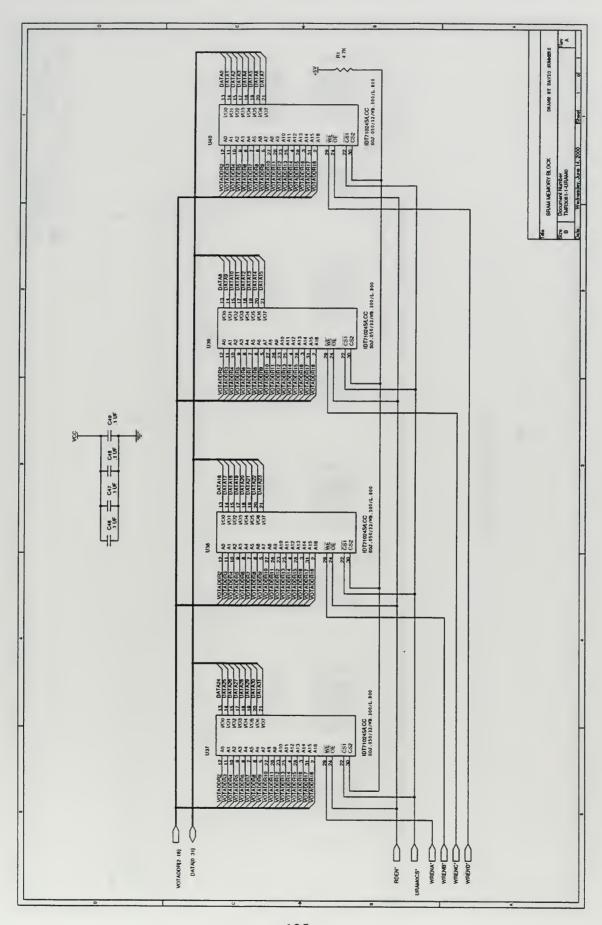

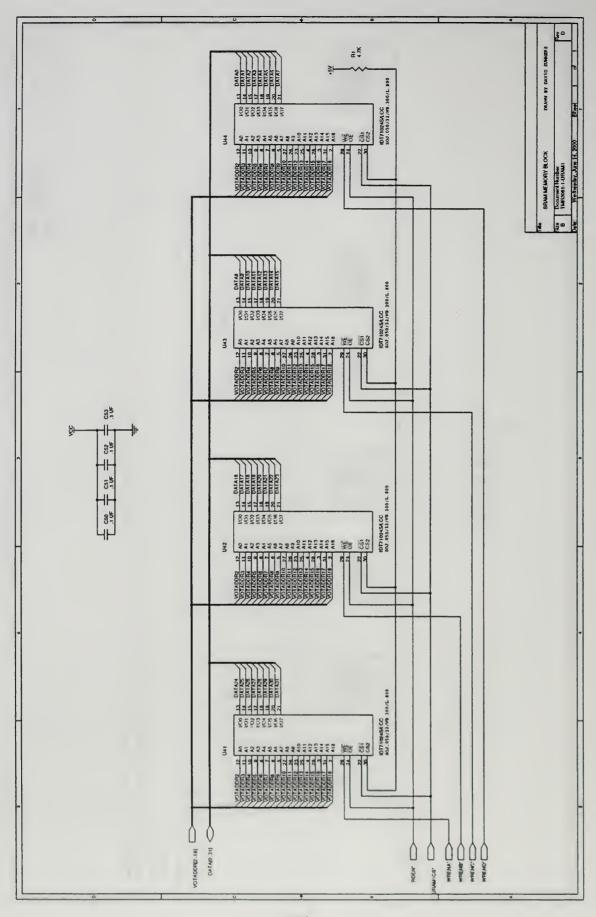

| Figure A.8. PROM Array Schematic                            |       |

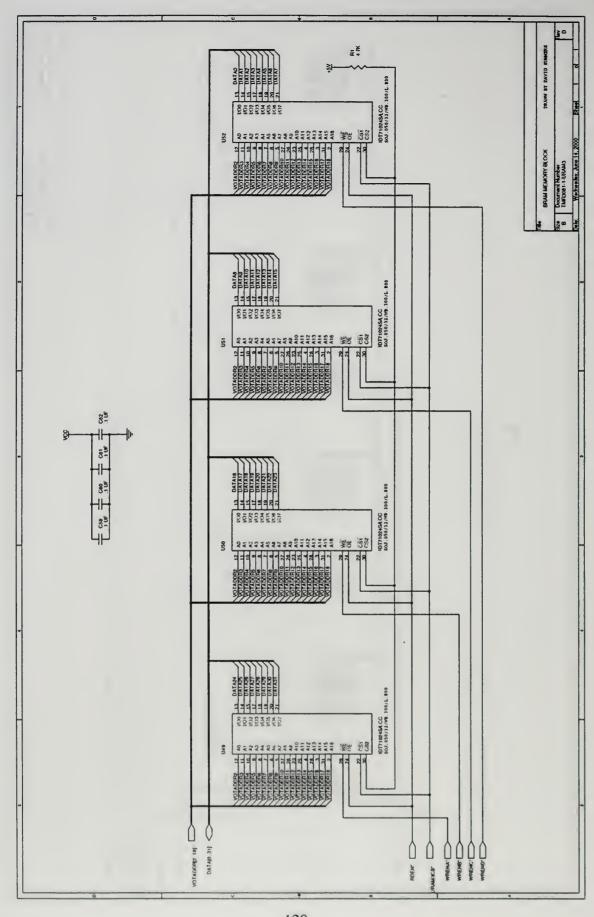

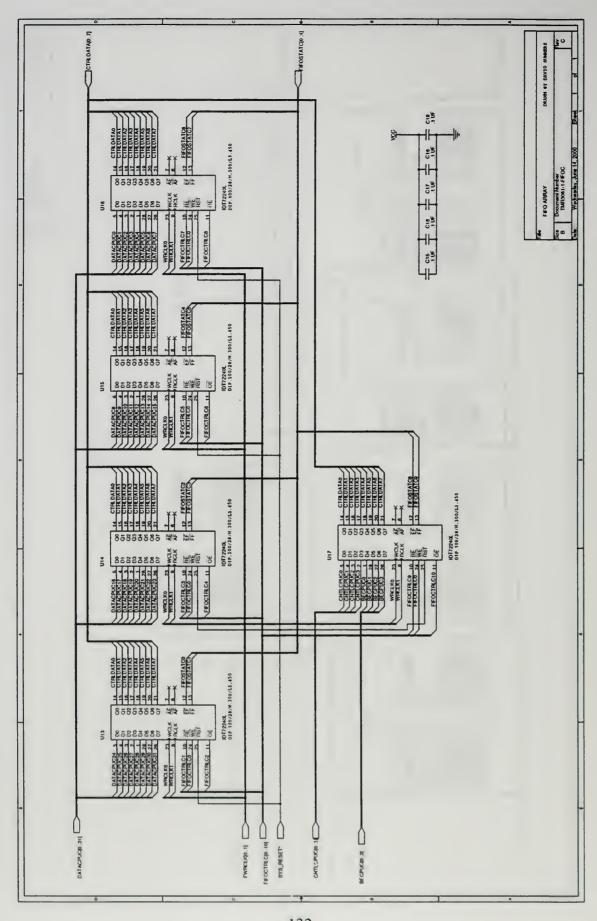

| Figure A.9. KRAM Array Schematic                            | 124   |

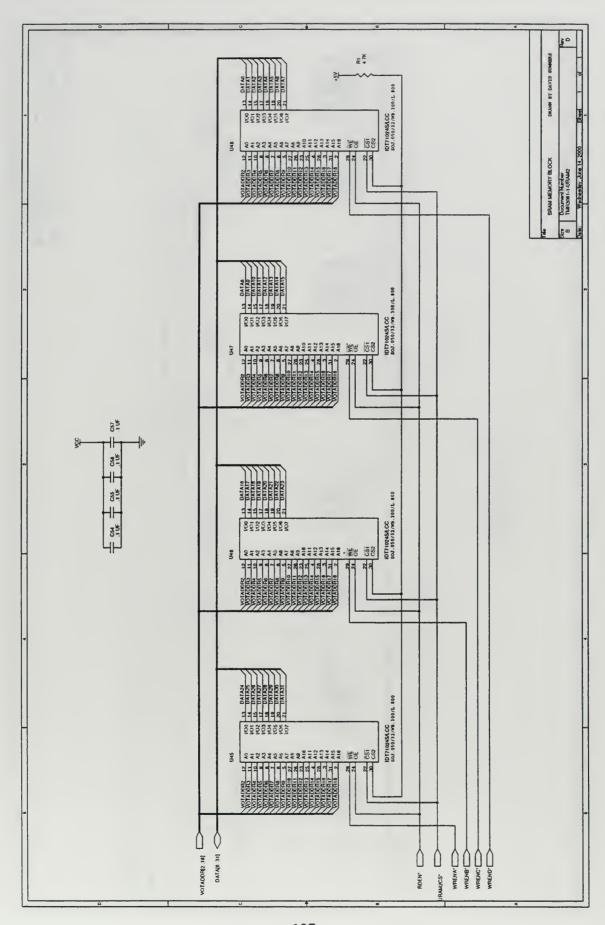

| Figure A.10. URAM0 Array Schematic                          | 125   |

| Figure A.11. URAM1 Array Schematic                          | 126   |

| Figure A.12. URAM2 Array Schematic                          | 127   |

| Figure A.13. URAM3 Array Schematic                          | 128   |

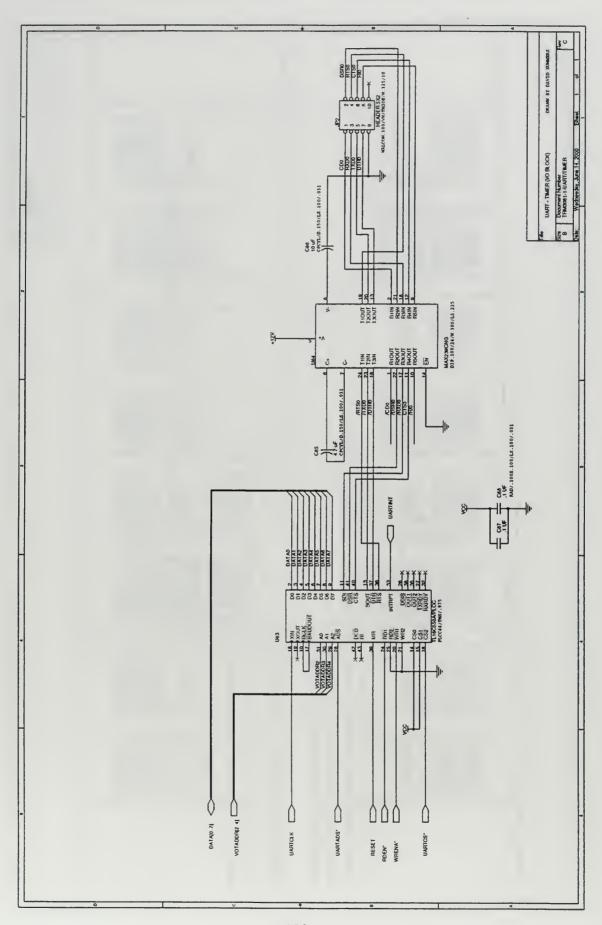

| Figure A.14. Data UART Schematic                            | 129   |

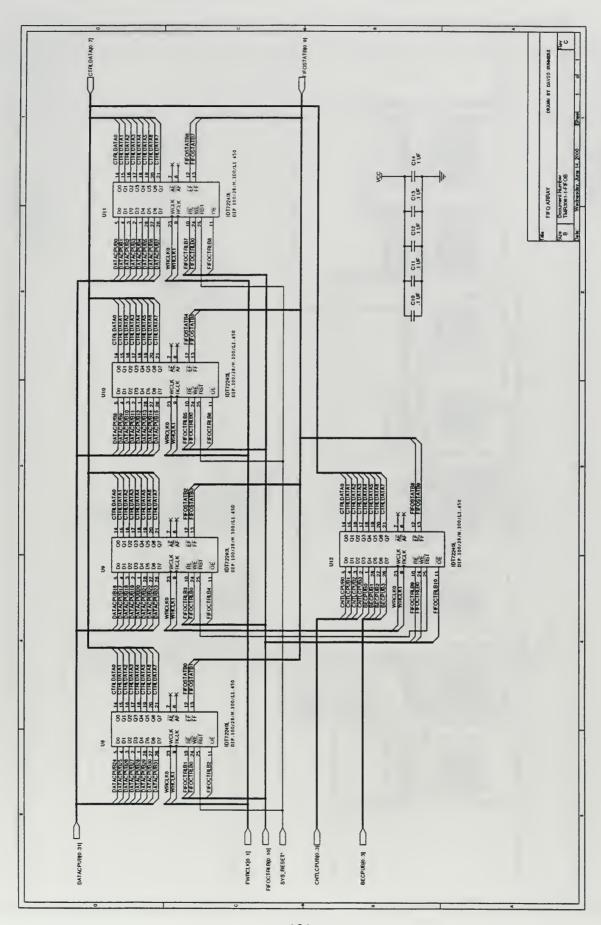

| Figure A.15. CPU A FIFO Array Schematic                     | 130   |

| Figure A.16. CPU B FIFO Array Schematic                     | 131   |

| Figure A.17. CPU C FIFO Array Schematic                     | 132   |

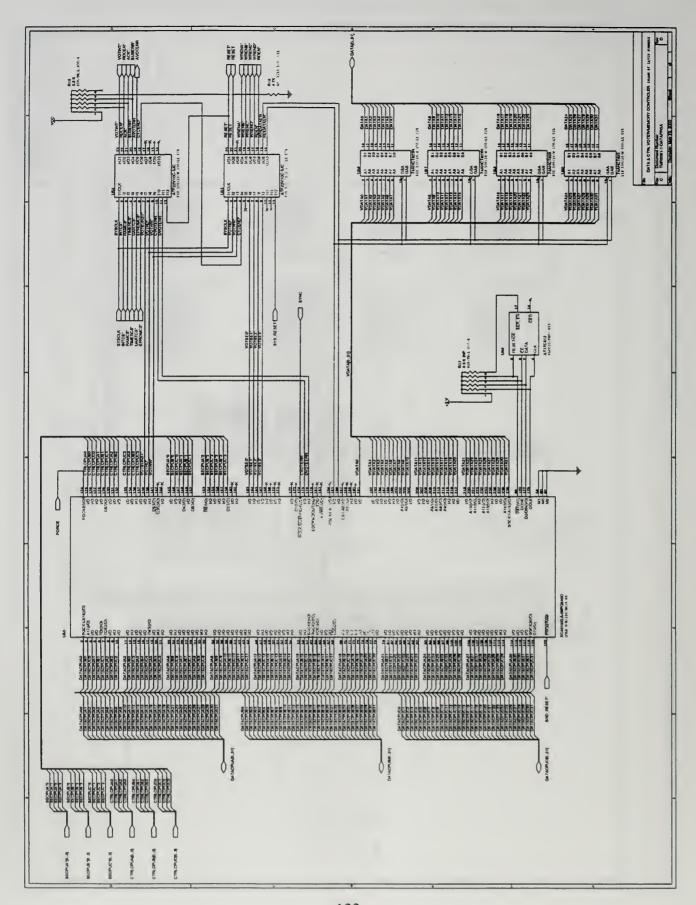

| Figure A.18. System Control FPGA Schematic                  | 133   |

| Figure A.19. Control UART Schematic                         | 134   |

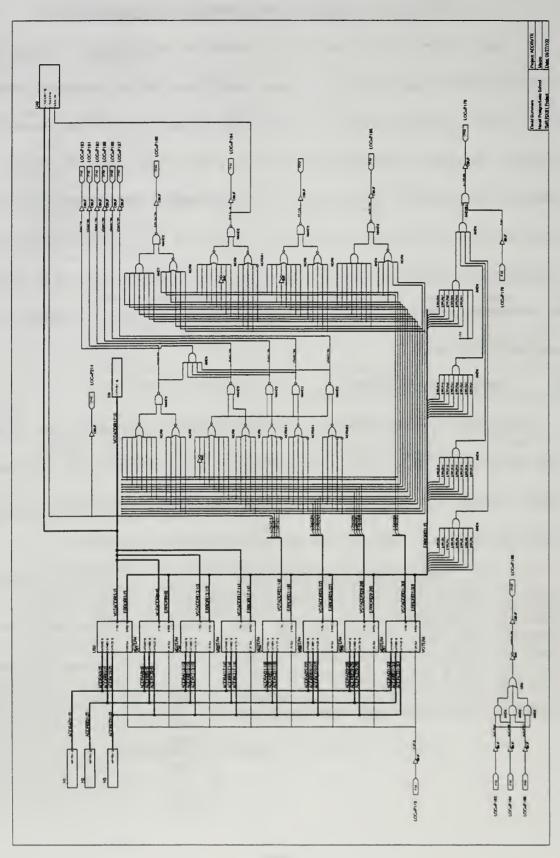

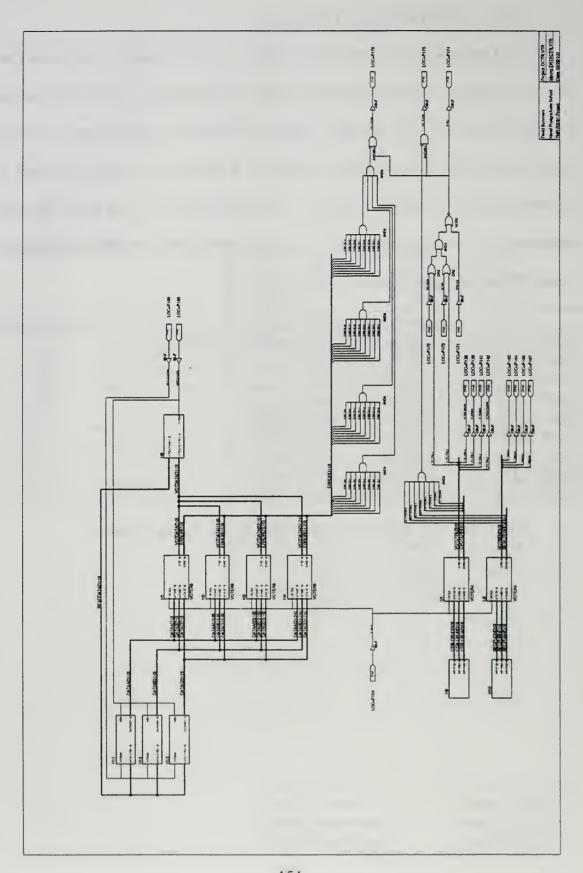

| Figure C.1. Address Voter FPGA Top Level Schematic          | 146   |

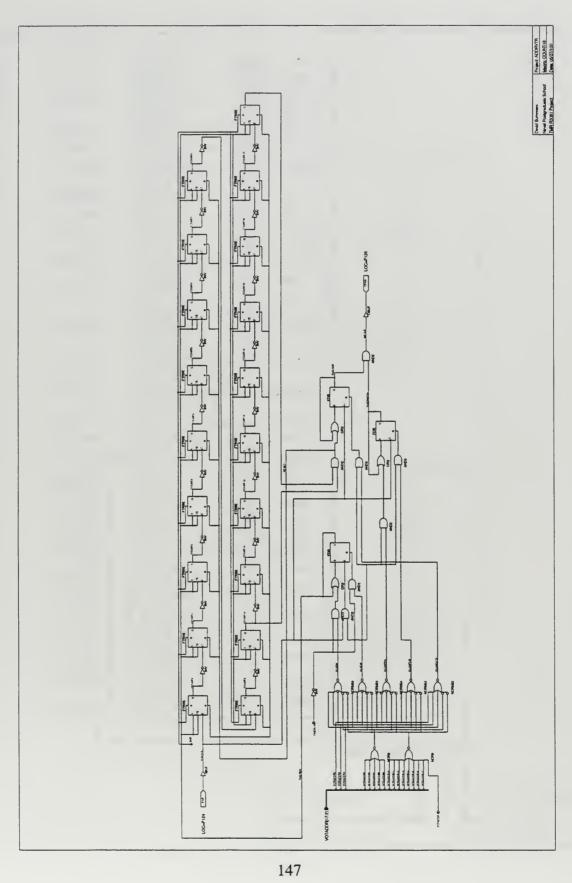

| Figure C.2. 18-Bit Counter                                  | 147   |

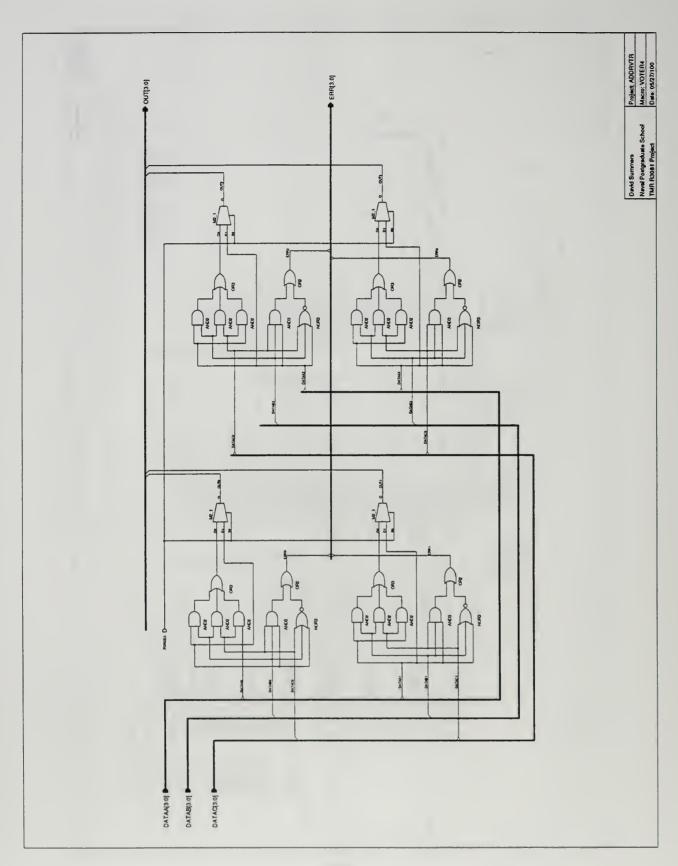

| Figure C.3. 4-Bit Wide 3-Bit Majority Voter                 | 148   |

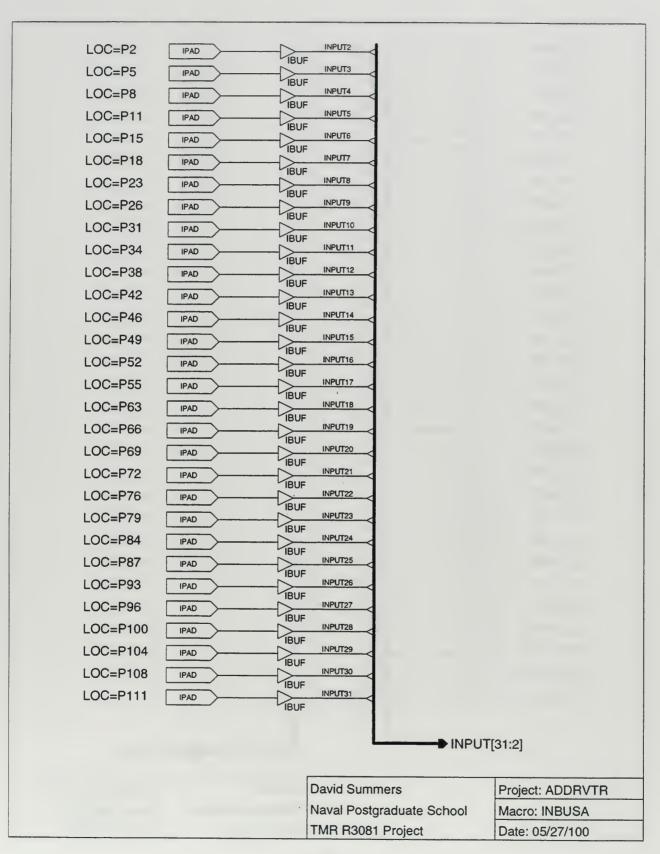

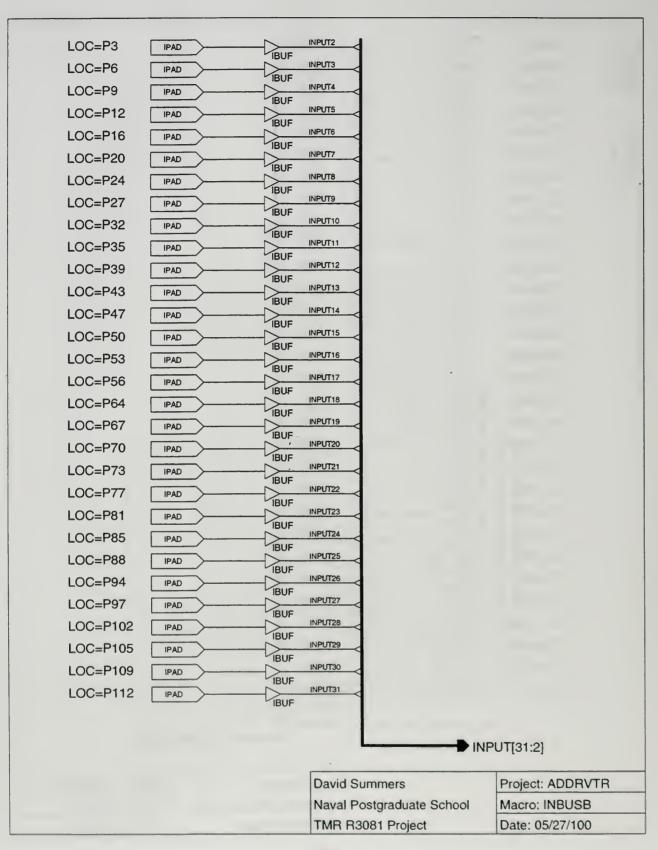

| Figure C.4. CPU A Address Bus Input Specification           | 149   |

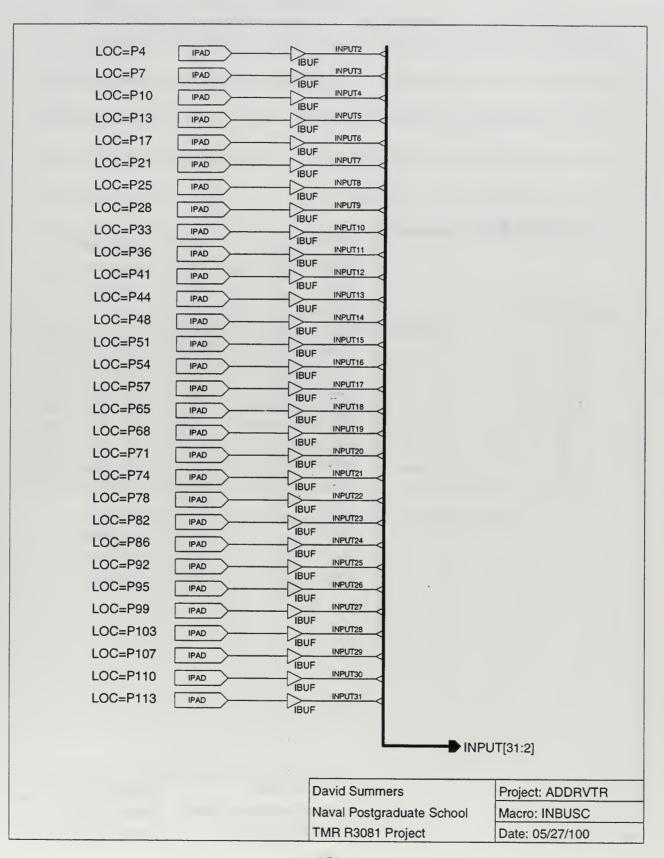

| Figure C.5. CPU B Address Bus Input Specification           | 150   |

| Figure C.6. CPU C Address Bus Input Specification           | 151   |

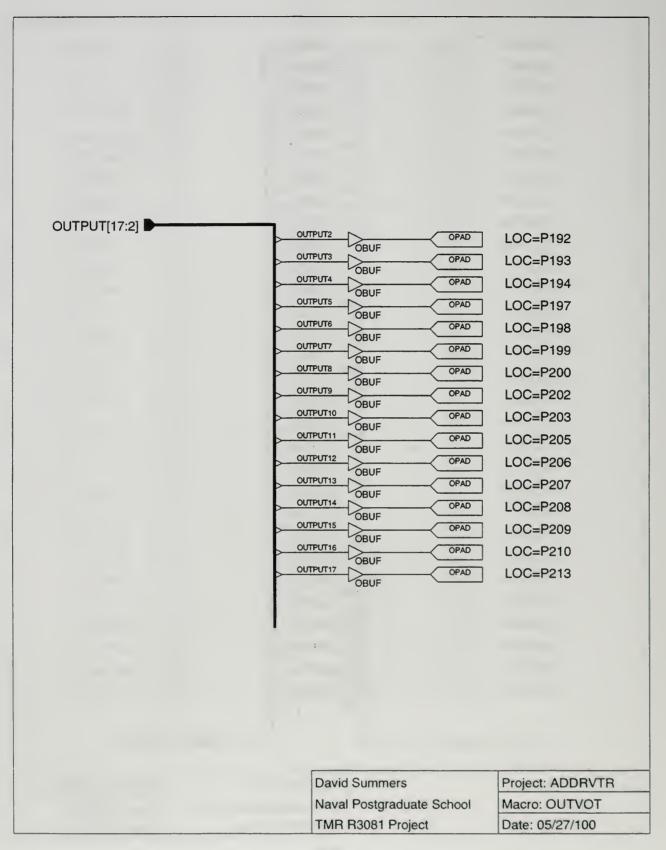

| Figure C.7. Voted Address Bus Output Specification          |       |

| Figure C.8. Data and Control Voter FPGA Top Level Schematic | 154   |

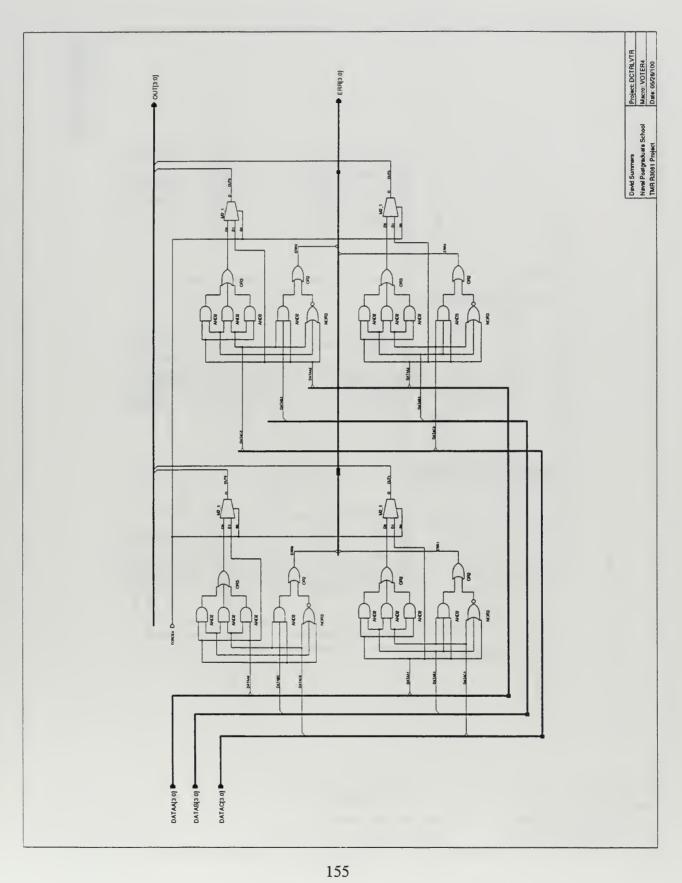

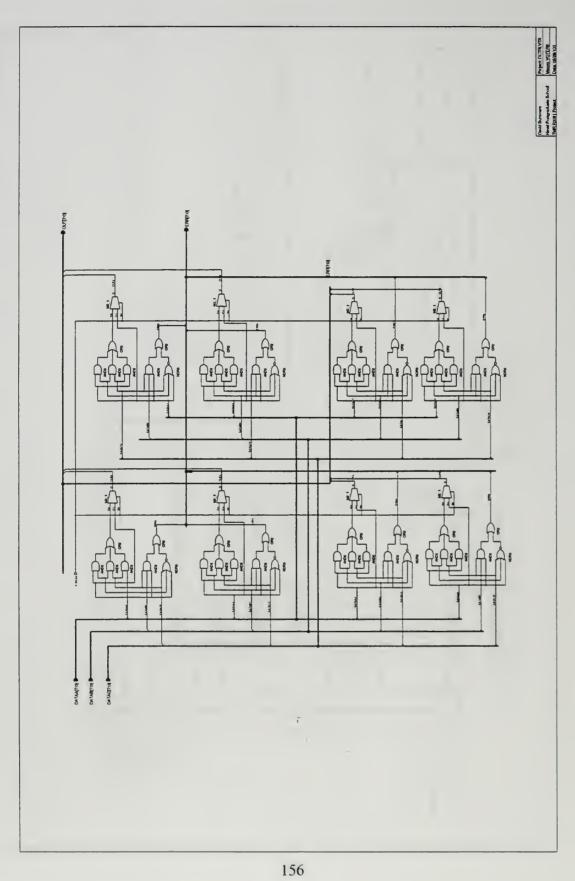

| Figure C.9. 4-Bit Wide 3-Bit Majority Voter                 |       |

| Figure C.10. 8-Bit Wide 3-Bit Majority Voter                | 156   |

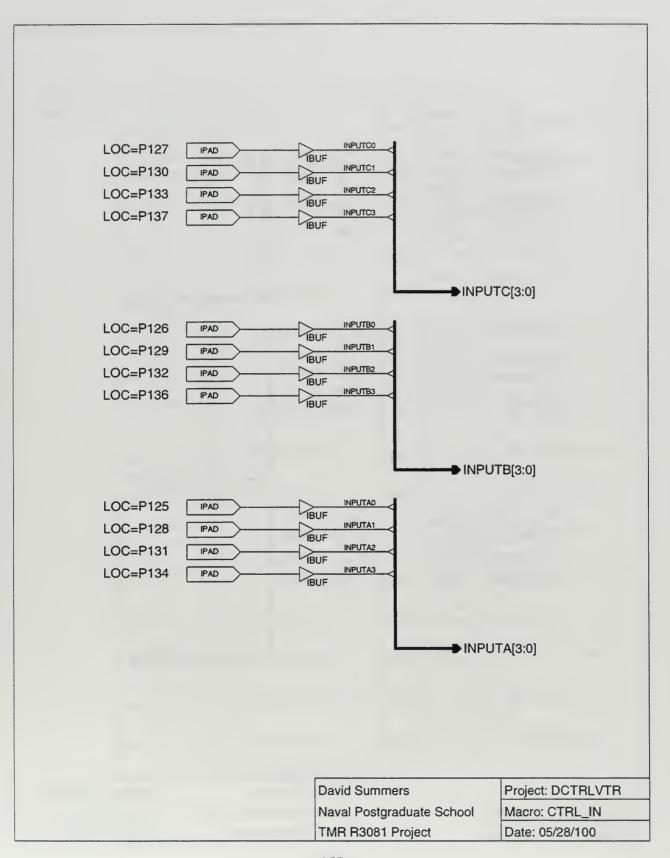

| Figure C.11. Control Bus Input Specification                | 157   |

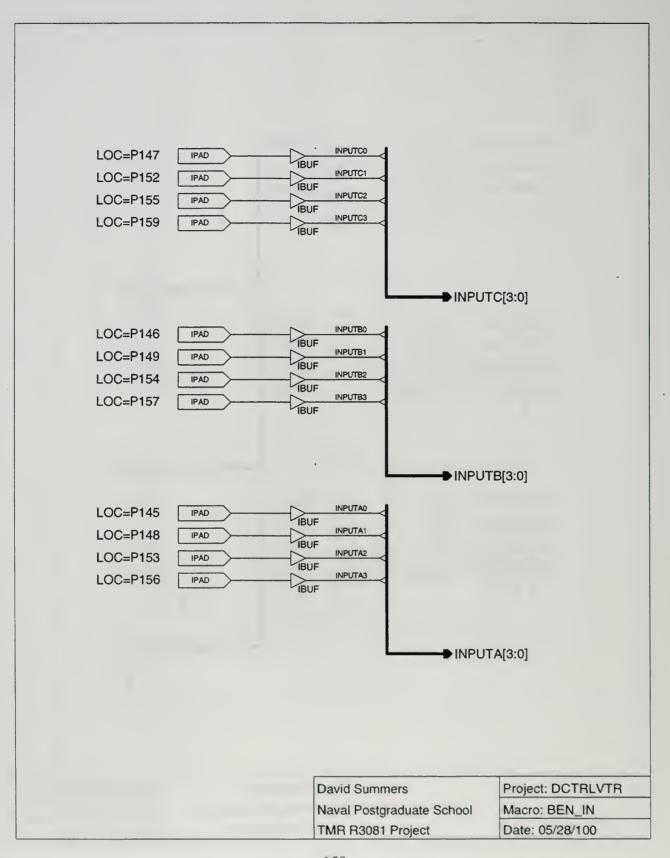

| Figure C.12. Byte Enable Bus Input Specification            | 158   |

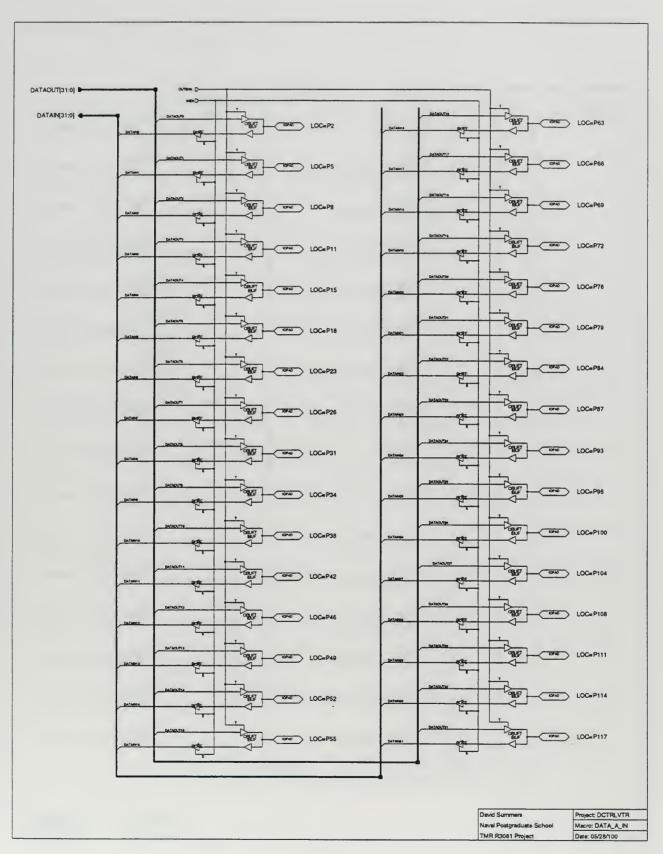

| Figure C.13. CPU A Data Bus Input Specification             | 159   |

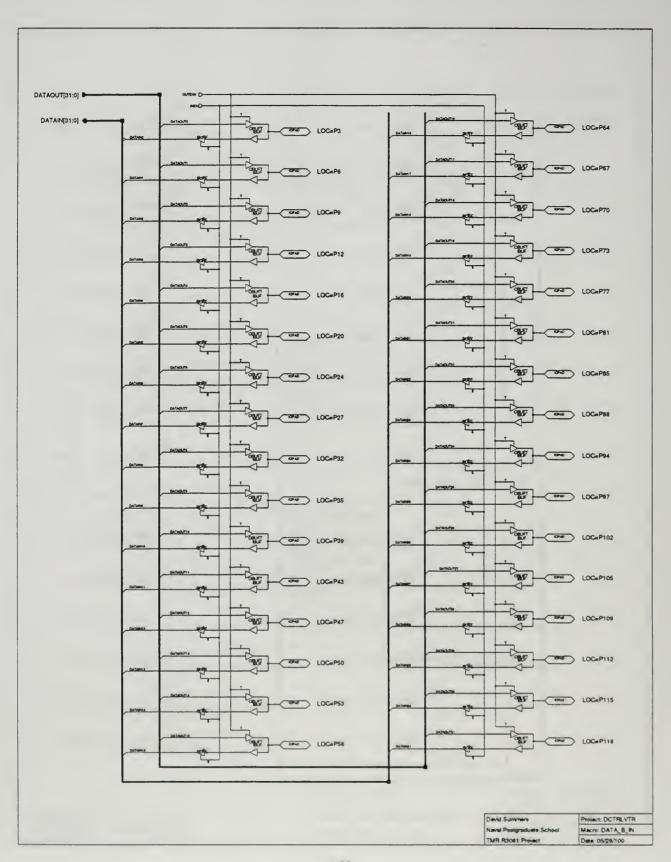

| Figure C.14. CPU B Data Bus Input Specification             |       |

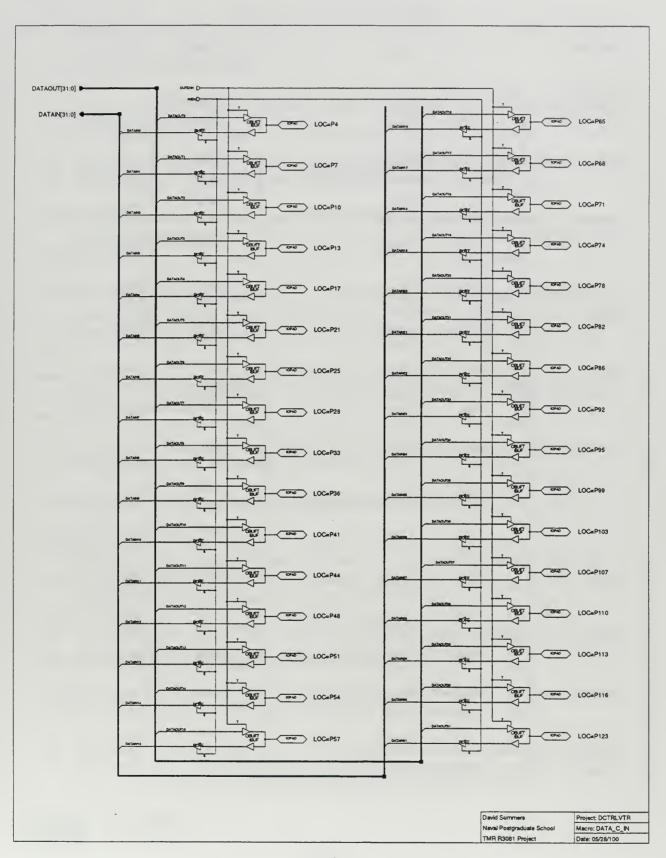

| Figure C.15. CPU C Data Bus Input Specification             | 161   |

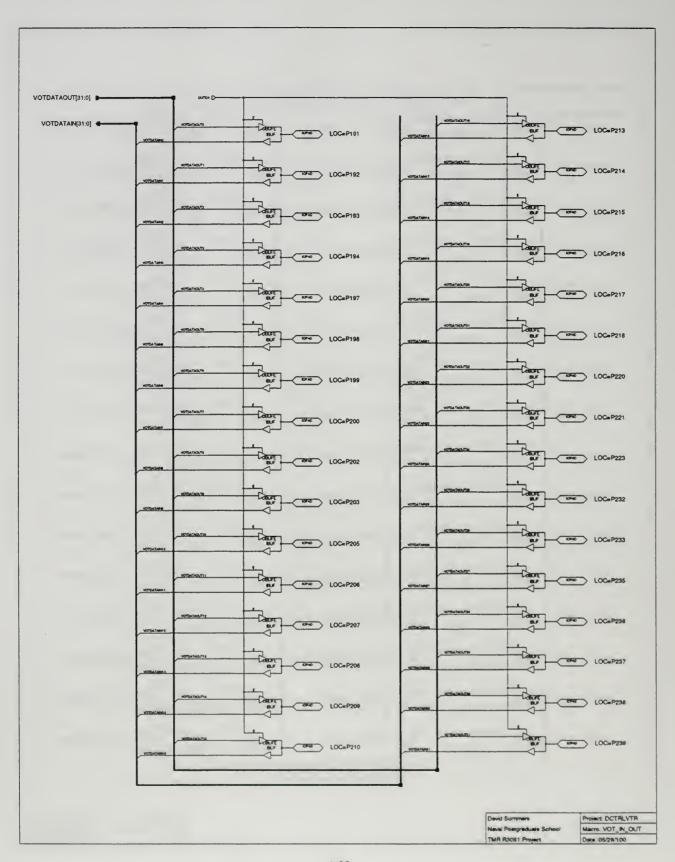

| Figure C.16. Voted Data Bus Output Specification            | 162   |

# LIST OF TABLES

| Table 2.1. 3-Bit Majority Voter Truth Table              | 14  |

|----------------------------------------------------------|-----|

| Table 3.1. Mode Selectable Features. From Ref. [10]      | 35  |

| Table 3.2. R3081 Internal Registers                      | 46  |

| Table 4.1. Write Enable Assertion Table                  | 64  |

| Table 4.2. Chip Select Memory Map                        | 72  |

| Table 4.3. Memory Mapped Timer Modes                     | 74  |

| Table 5.1. Table of White Wires and Cuts                 | 106 |

| Table A.1. TMR R3081 System Schematics By Page Number    | 115 |

| Table C.1. Address Voter Figures By Page Number          | 145 |

| Table C.2. Data and Control Voter Figures By Page Number | 153 |

THIS PAGE INTENTIONALLY LEFT BLANK

#### **ACKNOWLEDGMENTS**

The author would like to take this opportunity to thank all the people who provided the support and assistance that made this work possible.

First of all, to my family, Sandra, Courtney, and Kristen Summers: Without your unwavering support throughout this endeavor, its completion would not have been possible.

To Captain Kim Whitehouse and Susan Groening: Your software expertise provided great insight to the hardware/software interface requirements in this project. Additionally, your friendships provided the nucleus of a team that I am proud to have worked with. It is very unfortunate that the LED did not make it into the design!

To Jim Craybill: Your willingness to share your technical expertise in OrCAD and WinCUPL went beyond the call of duty. Additionally, your efforts in producing the PCB are greatly appreciated.

To Professor Alan Ross and Professor Herschel Loomis: Your guidance, patience and tutelage were instrumental in the completion of this portion of the project.

THIS PAGE INTENTIONALLY LEFT BLANK

#### I. INTRODUCTION

The decline of Department of Defense (DOD) funding of research into radiation hardening and reliability of microelectronics since the end of the Cold War has had serious impact on the price and availability of these parts. This, coupled with reductions in the space budget, has spacecraft designers looking for alternative ways to implement reliable systems with reduced cost, faster design time, and higher performance. One alternative is the use of commercial-off-the-shelf (COTS) devices in place of radiation hardened devices. COTS devices offer spacecraft designers shorter design-to-orbit times, lower system costs, orders of magnitude better performance, and a much better software availability than their radiation hardened (radhard) counterparts. The major drawback to using COTS devices in space is their increased susceptibility to the effects of radiation, both total dose and single event upsets (SEUs).

This thesis will present the implementation of a fault tolerant computer system. The hardware design presented here has two different benefits. First, the system can act as a software testbed, which enables the testing of software fault tolerant techniques in the presence of radiation induced SEUs. This allows the testing of the software algorithms in the environment they were designed to operate in without the expense of being placed in orbit. Additionally, the design can be used as a hybrid fault tolerant computer system. By combining the masking ability of the hardware with supporting software, the system can mask out and reset single processor errors with small cost in time. Both of these concepts will be discussed further in the body of the thesis.

#### A. THE SPACE ENVIRONMENT

The most important aspect to the designer of an electronic system is its function. Another vital interest to the system designer is the environment the system is going to operate in. If the environment is going to be space, then there are many factors that must be taken into account. The uninformed might think space is a benign environment, but that can not be farther from the truth. The vacuum, temperature extremes, debris, and radiation all interact with the system in one way or another and special efforts must be taken to account for their negative side effects.

#### 1. Vacuum

As you move away from the Earth's surface, the number of particles per unit volume continues to decrease. Starting at roughly 10<sup>18</sup> particles per cubic centimeter (cm³) on the surface of the Earth, this number decreases drastically as you increase in altitude. The average particle density from 600 to 1200 miles is only about 100 particles per cm³. Additionally, as with the particle density, the pressure associated with an altitude decreases as you move away from the surface of the Earth. While the pressure is near 760 millimeters of mercury (mmHg) at the surface of the earth, it is only about 10<sup>-12</sup> to 10<sup>-16</sup> mmHg past 1200 miles. These low pressures are sometimes referred to as hard vacuum. [Ref. 1]

One phenomena caused by the hard vacuum of space is called outgassing.

Outgassing occurs when a material actually loses mass because molecular gasses trapped inside or on the surface of the material at ground level are pulled out and away by the vacuum of space. A byproduct of outgassing is the cold weld. In the atmosphere, metal

surfaces have a thin layer of the molecular gas, which acts as a lubricant when two surfaces are in contact. When the vacuum removes the gas, the metal surfaces are allowed to touch and they will bond together. This issue is one to be dealt with by a materials scientist. The solution to this problem usually relies on the selection of appropriate materials to minimize the effects of the vacuum. [Ref. 1]

#### 2. Meteoroids

Meteoroids and orbital debris pose a risk to satellites. Although there are a large number of meteoroids and space dust near the Earth, most are fairly small and do not pose a large risk of catastrophic damage to a satellite. There have been a couple of satellites that have mysteriously quit working and the conjecture is that the failure might be due to damage caused by impact with meteoroids. With this in mind, the system should be designed to deal with the higher probability of micrometeoroid strikes, where only a small portion of the system is damaged. One option is to design the system using redundancy, a concept that will be explored later in this chapter. [Ref. 1]

### 3. Temperature

The Earth's atmosphere and the mass of the planet keep the ambient temperatures within a fairly moderate range at the surface of the planet. That can not be said of the space environment. Careful considerations with respect to thermal radiation must be taken into account when designing systems for space application. The skin of a spacecraft exposed to the sun will rise to a very high temperature while the shaded side falls to an extremely low temperature. This causes a very high temperature difference across the space vehicle. With that in mind, microelectronic devices used in systems

designed for space must function correctly over a much larger temperature range than required within the Earth's atmosphere. [Ref. 1]

#### 4. Radiation

Radiation is the emission or propagation of waves or particles. It is the key element of the space environment that our design is taking into consideration. High-energy charged particles can cause damage or disruptions, which are discussed later in the chapter, in microelectronic devices. These particles are either ions or photons. Ions, except for the neutron, have both a charge and mass associated with them. There are basically four types of ions: electrons, neutrons, light, and heavy. Light ions have a very low mass, such as protons, which are hydrogen atoms with the electron missing, and alpha particles, which are helium atoms with both the electrons stripped off. Heavy ions are any element heavier than helium with one or more electrons missing. Unlike ions, photons have neither mass nor charge. They are just very short wavelengths of light, such as X-rays and gamma rays. [Ref. 2]

There are several contributors to the radiation effects near the Earth. The largest contributor to a device's total dose is from particles trapped in the Earth's geomagnetic field. These trapped particles make up an area known as the Van Allen Belts. Any satellite in orbit is subject to effects from the Van Allen Belts. Another contributor is solar particles. Due to the high temperatures of the sun, many particles have enough energy to escape the sun's gravity. Those particles continuously flow across the Earth in what is called the Solar Wind. The sun continually moves through cycles of solar activity, where a single cycle takes approximately eleven years to complete. Another

source of radiation is galactic cosmic rays. These are heavy ions produced by events, such as exploding stars, outside our solar system. [Ref. 2]

When radiation interacts with microelectronic devices, it is either absorbed into or passes through the semiconductor leaving a path of ionization. The radiation has four major different types of effects on the semiconductor: Total Dose Effects, Dose Rate Effects, Displacement Damage, and Single Event Effects (SEEs). [Ref. 2]

Total Dose Effects are device failures caused by the lifetime sum of radiation absorbed by the device. Similarly, Dose Rate Effects are where the device fails to function at a particular radiation rate, or number of particles per unit of time. Displacement Damage deals with nuclear interactions between the particle and the semiconductor. The radiation changes the nuclear makeup of crystal atoms within the semiconductor, which leads to device failure. [Ref. 2] Finally, SEEs are the effects of charged particles changing the state of transistors in the circuit. SEEs are the radiation effect we are most interested in and are discussed in greater detail in the following section.

#### B. SINGLE EVENT EFFECTS (SEE)

The main difference between SEEs and the radiation effects discussed in the last section is that SEEs are not necessarily destructive in nature. SEEs are caused when an ionized particle deposits enough charge to cause transistors to change state in a device. In most cases, the transistor only changes state long enough for the charge to be absorbed back into the system and then resumes its original state. The transistor's state change can lead to latchup in parasitic transistors, be purely transient, or be latched into a storage

element. These three main types of SEE in Complimentary Metal Oxide Semiconductors (CMOS), which is currently the most popular type of circuit implementation for microelectronic devices, are discussed in the following sections. [Ref. 2]

#### 1. Single Event Latchup (SEL)

When CMOS field effect transistors are fabricated near each other on a single chip, one of the unwanted byproducts is a pair of vertical bipolar junction transistors. An SEL is caused when a charged particle passes close enough to this circuit to bias the two parasitic transistors on. This creates a very low impedance path to ground, which has two possible outcomes. If the current drawn through the parasitic transistors generates more heat than the device can dissipate, it will be destroyed. Even if the device can dissipate the heat, the large amount of current drawn through the parasitic transistors prevents the remainder of the circuit from operating correctly, which is a non-destructive SEL. The normal manifestation of a non-destructive SEL is that of a hung system, which requires a system reset for recovery. [Ref. 3]

## 2. Single Event Transient (SET)

Single Event Transients are unexpected, short duration changes in the output value of a combinational logic circuit due to the influence of a charged particle. SETs are not detrimental to the system. They only adversely effect the system if the pulse change is near the clocking edge and is long enough to meet the setup and hold times of the next storage unit in the cascade of stages. If the SET meets these criteria, then it manifests itself as a single event upset (SEU). [Ref. 4]

#### 3. Single Event Upsets (SEU)

An SEU is any unwanted value change in a memory cell, whether it be a latch, register, or cache cell, that is caused by charge introduced into the circuit by radiation. In microprocessors, SEUs are usually categorized into one of two error types: program flow errors and data errors. Program flow errors are errors that occur in the program counter (PC), control logic, or any other register that deals with the state of the processor. Data errors are usually confined to the registers and data cache. These two types of errors are not necessarily exclusive. A data error could occur in a register that is later used as a jump address. When the PC jumps to the address held in that register it is in the wrong location and begins to execute incorrect code. [Ref. 4]

# C. COMMERCIAL-OFF-THE-SHELF VS. RADIATION HARDENED DEVICES

The radiation effects discussed in the previous sections, with the exception of SETs and SEUs, are destructive in nature. The main way of reducing their effects is by using radiation hardened (radhard) devices or providing shielding. A radhard device is one that is specifically designed to be able to withstand higher amounts of radiation than standard commercial parts.

In a direct comparison of commercial-off-the-shelf (COTS) parts to radhard parts, the first question someone is bound to ask is 'why would we use non-hardened parts in such a harsh environment?' This section gives some insight into the answer of that question.

#### 1. Cutting Edge Technology

As alluded to in the introduction, companies developing and marketing radhard devices are on the decline. Without DOD budget support for research into this area, there is not sufficient demand from commercial sector customers to motivate companies to sink large sums of money into research on these devices. For those reasons, the technology of radhard devices is lagging behind state of the art technology by up to two or more generations. As an example, a state of the art processor, the 600 MHz Intel Pentium III, AMD K-6 II, or a RISC design, depending on your preferences, is available off the commercial shelf. The nearest competitor on the radiation hardened shelf would be a 66 MHz 486 processor. This is a whole order of magnitude difference in processor capability. [Ref. 5]

## 2. Faster Design-to-Orbit Time

Because many manufacturers of radhard devices offer them as a secondary market, many do not readily stock the parts. This causes a delay in the design and test phase of the project. With a move to COTS devices, the order delay is completely erased. Most of these devices are available from multiple vendors, which gives the designer even more leverage in selecting a vendor. Additionally, data on radiation testing for many devices is now becoming available to help the designer make an informed decision on the correct part to use based on the environment it is to be placed in. [Ref. 5]

#### 3. Reduced Cost

Profit or lack thereof is one of the main reasons companies have moved away from the manufacture of radiation hardened devices. The low demand for these devices

keeps the price hundreds of times higher than the commercial models for several different reasons. Since radiation hardened devices employ different techniques in their design to reduce the susceptibility to effects from ionized particles, they tend to be larger than the non-hardened devices. This lowers the number that will fit on the wafer in the first place and increases the probability that the devices will have defects. The reduction in yield can be attributed to two main factors. The first is the higher probability of defects in each device mentioned before and the second is from the limited number of runs of the fabrication process. Because yield normally increases with the number of production runs and radhard devices account for a small number of fabrication runs, radhard devices normally do not show large improvements in yield. Since the demand for commercial devices is much higher, the manufacturer can adjust the fabrication process over a large number of runs to increase the yield, which results in lower cost to the consumer. [Ref. 2]

#### D. PURPOSE

The goal of this research is the implementation of a fault tolerant computer system using COTS microprocessors that is able to accurately compute in the presence of radiation induced SEUs. This research specifically concentrates on the ability of the system to detect and mark or correct SEUs in a microprocessor in real time. This work does not address error detection and correction (EDAC) of memory systems, which has been previously researched [Ref. 6] and is a topic left for future inclusion.

There are two major benefits from this study. First, the system can act as a fault tolerant software testbed. The processor is monitored for an SEU. When one is detected, a time stamp is generated and the Operating System is observed in its handling of the

error. This allows the testing of the software algorithms in the environment they were designed to operate in without the expense of being placed in orbit.

The system can also be used as a hybrid fault tolerant computer system. In this use, the processor is also monitored for an SEU. When one is detected, the faulty data is corrected in the processor and it continues to execute its instructions from the corrected data. A major advance in this implementation is the ease with which the error can be corrected. The normal mode from previous research in these types of systems has been to just reset the processor when an SEU was detected, effectively loosing all computations done up to the time of the SEU.

#### E. THESIS ORGANIZATION

The organization of this thesis follows closely to the design approach used in developing the system. Chapter I has been a brief introduction into the environment that the system will be operating in. Chapter II is background material on research that set the foundation for this design. Chapter III presents the hardware design of the system and points out changes from the previous design. Chapter IV contains the design of the programmable elements of the system, which include the Voter Modules and the System and Memory Controllers. Chapter V presents the steps that were taken to have the printed circuit board fabricated and the design review that was conducted after the board was manufactured. Chapter VI presents the conclusions developed during this research and discusses topics for follow-on work.

#### II. BACKGROUND

The study of fault tolerant computing systems has been going on for many years. In fact, many early analog computer systems were designed with duplicate processing units because of their propensity to have errors. The EDVAC computer, which was designed in 1949, had duplicate Arithmetic Logic Units (ALUs) that continued to compute as long as their results agreed. As computer systems moved further into the digital era and became more reliable, fault tolerant designs took a back seat to designs that improved performance and speed. When computers started to perform critical tasks in systems, designers had to once again focus on fault tolerance. [Ref. 7]

The purpose of this chapter is to provide the reader a brief background for this project and the key issues that make it important. The chapter starts by describing the general concept of redundancy and focuses in on the design from which this system was implemented.

#### A. REDUNDANCY

The fundamental concept for implementing fault tolerance is redundancy. In its most basic form, redundancy is the addition of resources beyond those required by the system for normal operation to achieve reliability, availability, or safety. There are four different kinds of redundancy that can be implemented in a system. They are software, information, time, and hardware redundancy, each of which is discussed below. [Ref. 7]

## 1. Software Redundancy

One of the key attributes of software redundancy is that it requires a minimal amount of additional hardware to support it. Three typical software redundancy

techniques are consistency checks, capability checks, and n-version programming. Consistency checks use a-priori knowledge of the data set to check it to ensure that it is consistent with the expected values. Capability checks will test functional units of the system to ensure they are in working order. While both of these methods are software tests of hardware, n-version programming is a software test of software. Different programmers code different versions of the same function. All of the versions are executed and their results compared to ensure that all the results are the same. [Ref. 7]

# 2. Information Redundancy

Information redundancy provides additional bits along with the data to allow for checking that the correct values are received at the destination. The additional information can be small enough to allow error detection or robust enough to allow multiple bit corrections. Two good examples of information redundancy are the parity bit and the Hamming Code. The parity bit is a single bit appended to the data set that allows for error detection. Parity can either be even or odd. If even parity is selected, the number of ones in the data set and the parity bit should add up to an even number. If odd parity is selected, the ones should add up to an odd number. If they do not, there is an error in the information. The limit of the parity bit is its inability to determine which bit is in error. The Hamming Code appends multiple bits to the data set, which allows for error detection and correction by pointing out the faulty bit. The additional bits appended by the Hamming Code are actually weighted parity bits. By determining which Hamming Code bits are in error, the faulty data bit can be determined and corrected. [Ref. 7]

#### 3. Time Redundancy

One of the costs associated with all forms of redundancy is the large overhead. This overhead can be paid in the form of additional hardware, weight, and power consumption. In some cases, these assets are not available for trade. When that happens, another form of fault tolerance must be found. In systems where speed is not a critical issue, time redundancy can be used. The premise behind time redundancy is that the same calculations can be performed serially multiple times and the outputs compared to check for errors. This requires the system to save the state before the calculation, perform the calculation and save it, make a context switch back to the beginning of the calculation, perform it again, and then compare the results of the two different calculations. [Ref. 7]

#### 4. Hardware Redundancy

When you mention redundancy to people, hardware redundancy is typically the first thing that enters their mind. This form of redundancy is regaining popularity as the cost for replicating hardware is getting less and less expensive. There are basically three forms of hardware redundancy: passive, dynamic, and hybrid. Passive redundancy uses fault masking to keep the fault from propagating out of the current process. This is implemented using multiple modules and voting hardware. It does not require any actions from the system or operator. Dynamic redundancy monitors the outputs of the modules looking for faulty units. When one is detected, the system removes the faulty unit from the system and replaces it with a good one if it is available. The hybrid approach uses portions of both the passive and dynamic approaches. [Ref. 7]

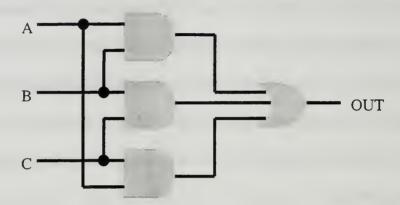

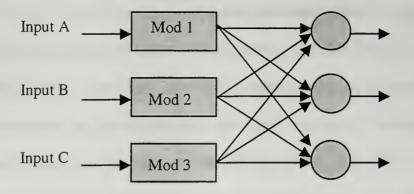

A subset of passive hardware redundancy is the Triple Modular Redundant (TMR) system. As the name implies, the TMR system takes the outputs of three replicated modules and compares them in a voting unit. The voting unit passes the most common input to the output, essentially masking out any single fault. The heart of a TMR system, the voting unit, and its truth table are shown below in Figure 2.1 and Table 2.1.

Figure 2.1. 3-Bit Majority Voter Logic Diagram. After Ref. [7]

| A   | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

|-----|---|---|---|---|---|---|---|---|

| В   | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| С   | 0 | 1 | 0 | 1 | 0 | 1 | 0 | 1 |

| OUT | 0 | 0 | 0 | 1 | 0 | 1 | 1 | 1 |

Table 2.1. 3-Bit Majority Voter Truth Table

The table shows that anytime two or more inputs have the same logic value, either a zero or one, then that value is propagated to the output. This system can also be extended to an N input model. As N gets larger, the logic required to realize the circuit and the added levels of delay get prohibitively large. Typically N is held to three or five.

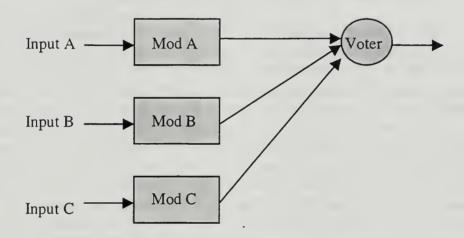

### 5. TMR Implementations

As stated before, by placing the three modules in parallel and voting their outputs, a TMR circuit can be implemented. The basic TMR circuit is shown below in Figure 2.2. The inputs and output of the modules do not have to be single values. There can be X inputs and Y outputs associated with each module. All that needs to be done is place Y single bit voters in parallel connected such that they vote each of the respective Y outputs.

Figure 2.2. Basic TMR Circuit Implementation. After Ref. [7]

The single voter on the output of the TMR system is a single point of failure. That is, if the voter fails and generates or propagates an error, then the error will be propagated throughout the circuit. This could become a major problem in cascaded circuits. To solve this problem, the voters at the end of each stage can also be triplicated. [Ref. 7] An example of this is shown in Figure 2.3.

Figure 2.3. Triplicated TMR Voters. After Ref. [7]

### B. SOFTWARE VS HARDWARE REDUNDANCY

The technology associated with very large-scale integrated circuit (VLSI) design has advanced at a phenomenal pace. Systems that used to be produced as multiple chip designs are now compacted into systems on a chip. Much of the current hardware design emphasis is placed on reducing the transistor size in order to increase the capability and decrease communication times within the chip. Since the communication times between chips in a system has not progressed at the same rate as internal communication, the addition of logic layers between the processor and its peripherals would require the system bus clock to operate at a reduced frequency. Because of this, general trends have moved the reliability issue to software.

When using software fault tolerant techniques, as in Checkpointing, the software must run the same segment of code a minimum of two times. If the results of the first two runs match, the processor can continue where it left off after it has saved its internal state. If the results do not match, the processor must run the code segment an additional time to try to determine which of the first two runs were correct and then save the correct

internal state. This occupies over half of the processor's execution cycles in context switching and rerunning code. [Ref. 8]

The option being investigated in this research is a move back to hardware redundancy. By applying the TMR technique discussed earlier to the microprocessor, the outputs of the processors can be combined through a voter. If an error occurs in one of the processors the voter will mask it out and the bus cycle will complete normally. The two good processors will then reset the errant processor to their good state and then all three processors will continue executing the program.

A direct comparison of the two options is very difficult. Although the TMR design looks like it can save over half the time required to perform a function, it can not operate at the same clock speed that the Checkpoint model can. The TMR system has to place additional logic between the processor and the memory space to perform the voting operation, which decreases the maximum clock speed at which the processor can operate.

# C. TMR MICROPROCESSOR DESIGN

The framework for the system implemented in this work was originally designed and simulated using Verilog by Lieutenant John C. Payne, Jr., USN, as a Fault Tolerant Computing Testbed. The remainder of this section is a brief synopsis of his TMR Testbed Design. For a more detailed explanation, please see Ref. [9].

### 1. Processor Selection

Lt. Payne began his design with the logical step of selecting a microprocessor. In his selection process he took into account such factors a COTS vs. Radhard, CISC vs. RISC, size, pinout, power, bus width, memory size, speed, and multiple chip vs. single

chip implementations. His research led him to select the MIPS R3081 RISController produced by Integrated Device Technologies (IDT). This device was selected over AMD's AM29000 and AM29050; IBM and Motorola's PowerPC 603e, 604e, and 750; and IDT's R36100, R4650, and R5000. A detailed description of the R3081 can be found in Ref. [10].

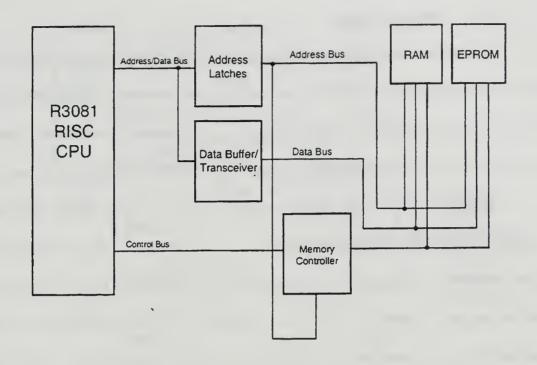

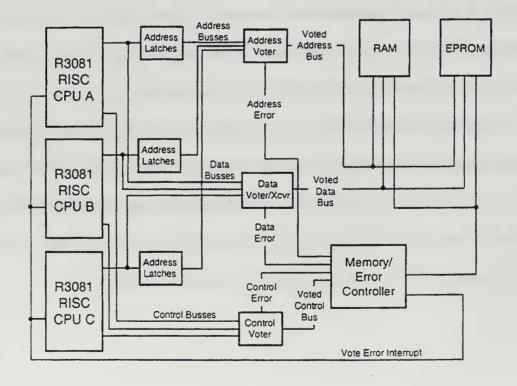

# 2. Hardware Design

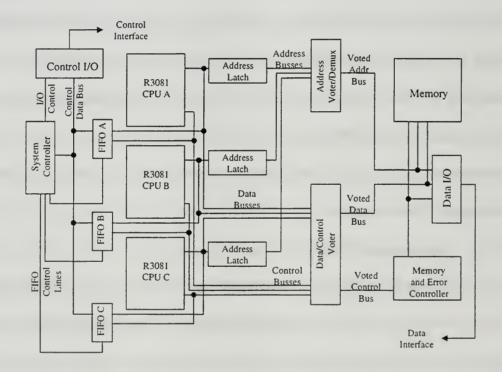

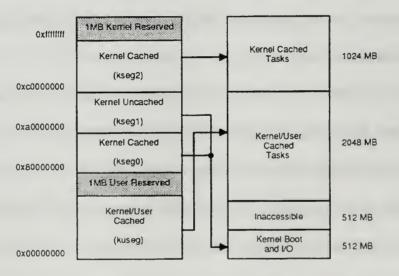

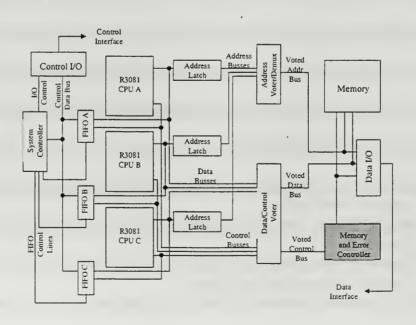

With the processor selected, the next step was to integrate all the peripheral components required for the R3081 to function as a TMR computer system. For comparison purposes, a block diagram of a single processor system and a TMR system are provided on the following page in Figure 2.4 and Figure 2.5, respectively.

From comparison of Figures 2.4 and 2.5, the architecture of the TMR implementation has relatively few changes from the single processor design. The major additions are CPU B and CPU C along with the Address, Data, and Control Voters.

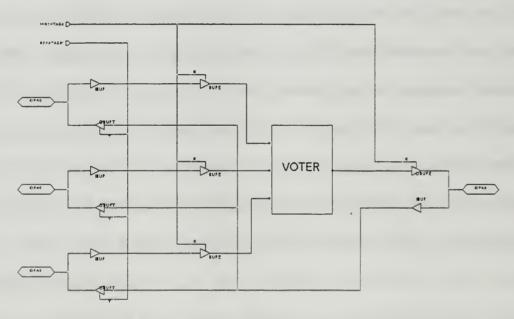

The processors are connected in such a way that the Operating System acts as if there is only one processor in the system. The processors are kept in lock step from boot up by executing the same instructions in parallel. The processors Address, Data, and Control busses are then routed to their respective voters. The voters perform a majority vote on the signals and pass them on to the Memory Space and Memory Controller as in a single processor system. If an error is detected in a voter, the Memory Controller generates an interrupt. [Ref. 9]

Figure 2.4. Simple R3081 Board Design. After Ref. [11]

Figure 2.5. TMR R3081 Board Design. From Ref. [9]

## 3. Software Design

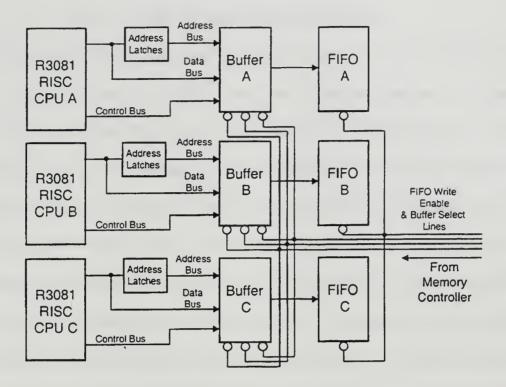

The voters allow the fault generated in one of the processors to be masked out and the bus cycle to complete correctly, but that does not completely remedy the situation. The processor that had the error is now out of synchronization with the other two processors. That is where the software design of the Interrupt Handler comes into play.

When a voter detects a miss compare on its inputs, it signals the Memory Controller, which asserts an interrupt input to the processors. The Interrupt Handler resets the invalid processor in a very simplistic way. It starts by saving the processor's internal registers to memory. Since all three processors will be executing the instructions, the Data Voter will mask out the invalid data from the corrupted CPU. The Interrupt Handler then reloads the processors internal registers from memory. This puts the corrupted processor back into synchronization with the other two processors. The Interrupt Handler then acknowledges the interrupt and returns from the exception. The processors then continue execution with the next instruction.

In order to determine which processor was corrupted, the internal registers of each processor must be examined. The data must be captured prior to being voted or the error is lost. By placing First-In-First-Out (FIFO) Registers on the address, control, and data busses between the processors and voter, each processors internal state can be captured in its corresponding FIFO. The arrangement is shown below in Figure 2.6.

Figure 2.6. TMR FIFO Interface. From Ref. [9]

Lt. Payne's design and simulations prove the fundamental concept of a working TMR R3081 system. The next logical step is to implement the system in hardware. The next two chapters examine the transition of this design from simulation to hardware. Chapter III presents the hardware implementation, while Chapter IV presents the programmable logic synthesis. Because of hardware limitations and additional system requirements, the transition is not a one-to-one process.

THIS PAGE INTENTIONALLY LEFT BLANK

### III. HARDWARE DESIGN SPACE

The process of designing a complicated electronic system is very seldom linear in nature. That is, the system originally conceived is seldom designed, simulated, implemented, and manufactured without changes. Many factors affect the process as the design matures, which can cause changes in areas of the design that were once thought to be complete. This results in feedback loops in the design process. This design has not been an exception to these effects. It has gone through several revisions in the implementation and manufacturing phases due to feedback from several different factors, including changes in requirements and parts availability. This chapter presents the final hardware implementation and explains design changes where major deviations from the simulation model were required.

### A. DESIGN PARAMETERS

As discussed in Chapter I, the most important aspect of the system the designer must be familiar with is its function. Chapter II presented a simulated design by Lt. John Payne, Jr. [Ref. 9] that fulfilled all the functional requirements, but focused primarily on validating the concept of TMR using the IDT R3081 microprocessor. The next step in the design process is the hardware implementation. This implementation was developed by making modifications to Lt. Payne's design and using three general functional applications: use as an Evaluation Board, easy adaptation to a space flight board, and the ability to be tested in a particle accelerator.

#### 1. Evaluation Board

The evaluation board design parameter adds value by introducing flexibility and visibility to the design. For flexibility, socketed parts and programmable logic are used. By using socketed parts instead of parts that must be soldered to the printed circuit board (PCB), the designer enables the user to quickly and easily exchange integrated circuit (IC) chips. This allows easier replacement of damaged parts and requires fewer vias when routing traces on the PCB layout, when compared to surface mount devices. Upgrades to the system can also be easily incorporated if the new IC chip is pin compatible with the old one. The most common use of this advantage would be upgrading to faster parts.

Using programmable logic to interface the processors and the peripherals is another tool the system designer can use to increase flexibility. Unless the same manufacturer builds the processor and peripheral, there is normally a requirement for additional logic to be placed between the two components to allow them to function together properly. The additional logic is usually referred to as "glue logic." By using a programmable device to perform the glue-logic function, the system can easily be expanded to incorporate system updates and changes.

Since evaluation boards are normally used to investigate new concepts, it is important to be able to capture data from as many internal signal lines as possible. Today's PCBs are normally fabricated using multi-layer designs, making it difficult to capture signals residing on internal routes. Connecting the essential signals to a test connector, which makes them visible to the user, can alleviate this problem.

### 2. Space Flight Board

Although it may seem that designing the initial implementation of a system with such a futuristic goal would increase the complexity of the design, in this case it actually narrowed the scope on many of the part choices. The premise of this design parameter was to focus on parts, other than the microprocessor, that were available in both commercial and rad-hard versions or parts that showed a reduced susceptibility to SEUs. The pin compatibility and exact functionality between the commercial and rad-hard versions of devices reduces the process of upgrading to a flight ready board to a simple IC exchange with minor modifications to the timing parameters of the glue logic. As for parts showing reduced susceptibilities to SEUs, different technologies used to implement devices can have drastic differences in their SEU susceptibility, such as in the case of static or dynamic RAM. When these choices were available, the technology offering the lower susceptibility was used.

# 3. Accelerator Testing

One of the key functions of this system is its ability to test fault-tolerant software. In order to achieve that function, the user must be able to operate the system in a particle beam, which places added requirements on the implementation of the system. First, the system must be able to communicate with the host interface over distances of fifty feet, due to the shielding and physical layout of the testing facilities. Because heavy ion testing requires the system to be placed in a vacuum chamber, the device must be able to physically fit within the chamber and be reset remotely. The remote reset allows the user to recover a "hung" system without having to bring the chamber back to local pressure,

reset the system, and then reapply the vacuum, which wastes expensive chamber/facility time.

### B. SYSTEM OVERVIEW

The final block diagram for the TMR R3081 system as implemented is shown in Figure 3-1. Compared to the simulated system depicted in Figures 2-5 and 2-6, there are several differences. This section will discuss those differences.

Figure 3.1. TMR R3081 Block Diagram

The most important difference between the two designs is the addition of a System Controller to the implementation, since the Verilog® design suite acted as the

System Controller during simulation. For the implementation, an FPGA was selected to perform the System Controller function. Its design is explained in Chapter IV.

The other main design change is concerned with the I/O interface. Since the scope of the design in Ref. [9] did not require the loading and running of user programs, an interface to provide that functionality was not included. Additionally, the simulation used a System Interface module to read out the collected FIFO data. Although the System Interface was expected to be a laptop or similar system, its interface was simulated using a 104 bit wide interface, which could not be directly implemented into hardware. This left a wide latitude in the implementation of the I/O interface. For reasons discussed below, a dual-port interface was selected.

Although this thesis focuses on hardware implementation, two other major efforts on this project were going on in parallel. Captain Kim Whitehouse, USMC, and Lieutenant Susan Greoning, USN, conducted research into the selection of an operating system for the TMR R3081 and the design of a Human Computer Interface (HCI). Their research garnered the selection of VxWorks as a real-time operating system and the design of a user interface for a software testbed which is presented in Ref. [12]. The important aspect of the close association of the hardware and software designers is the ability to effectively integrate the two designs, which is why several hardware design decisions are based on the software interface requirements.

The functionality of the HCI plays a significant role in determining the design of the I/O interface. The HCI controls the TMR's mode of operation, provides for a remote reset, enables the user to download and run programs, and also provides a path for data

collected in the FIFOs to be returned for analysis. Serious consideration was given to the use of a single communications port for this interface. Difficulties arose in the design when trying to implement the remote reset function with a single port. Because the CPUs control the transfer of data in a single port device, a "hung" system would not be able to reset because it could not respond to the reset signal at the port. In order to achieve this function a second port, controlled by the System Controller, was added to the implementation.

With the decision made to use two ports, the next step was to determine what functionality was associated with each port. To help distinguish the two ports, which were depicted back in Figure 3.1, the processor-controlled port was named the Data Port and the System Controller controlled port was named the Control Port. Since the ability to download and run programs does not require interface with the System Controller, it was left on the Data Port. In order to free the processors from the overhead associated with transmitting the large FIFO data blocks and to provide the System Controller with direct access to control and resets, these functions were assigned to the Control Port. This separation lets the user interact with the downloaded program through the Data Port and interact with the TMR hardware through the System Controller on the Control Port.

Now that the major changes in the implementation from the simulation have been presented, the rest of the chapter discusses the individual pieces of the design. Section C presents the design and implementation of the system support elements that were not required during the simulation phase. The microprocessor and address latch selection is

then addressed in Section D. The design of the Memory Space and its components follows in Section E. Finally, Section F presents the design of the FIFO buffer interface.

### C. SYSTEM SUPPORT ELEMENTS

The detailed analysis of the TMR implementation starts with the system support elements. These portions of the system are critical to the systems functionality, setup, and testing, but are seldom included in simulations. One of the benefits of simulation is the ability to only include the required portions of the system. The implementation must account for all the elements that must be added to support the main system that were not included in the simulation, such as pull-up and pull-down resistors, decoupling capacitors, clocking and reset systems, mode select, and test connectors.

# 1. Discrete Components

One important change from a simulation environment to a hardware implementation is the inclusion of the discrete resistors and capacitors used in the circuits. When control signal lines are driven by devices that can tri-state their outputs pull-up or pull-down resistors are required to maintain the signal line at a known value. This prevents the device from misinterpreting the driver going into the high impedance state as an active signal. Additionally, decoupling capacitors are required to reduce the power fluctuations seen on the voltage bus during switching and to keep AC noise off the DC bus.

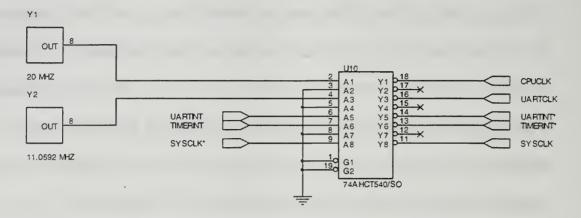

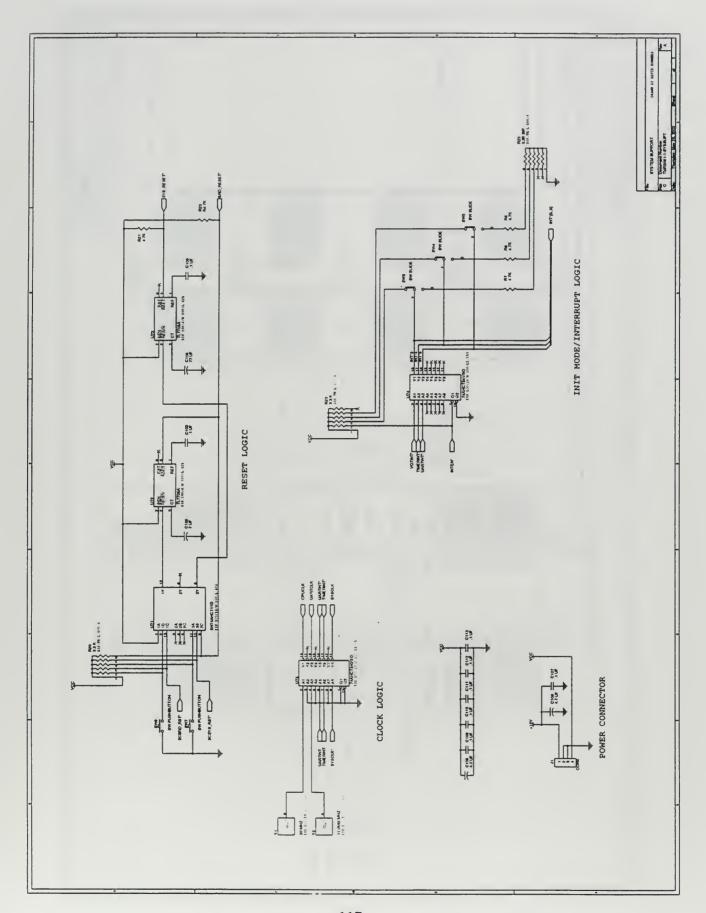

# 2. Timing Interface

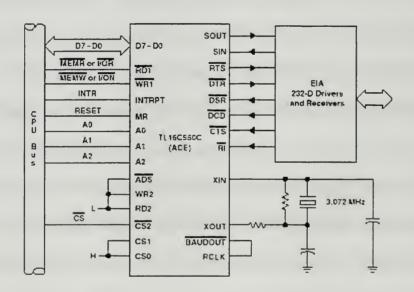

The Timing Interface consists of two different clocking systems, one for the CPUs and one for the two universal asynchronous receiver transmitters (UARTs), which are

used to transmit data through the Data and Control Ports. The schematic for the Timing Interface is given in Figure 3.2. The two oscillators and the buffer/driver are all socketed to allow the user to easily change the oscillator frequency or the buffer/driver chip. The frequency selections and buffer/driver logic selections are discussed below.

Figure 3.2. Timing Interface

### a) CPU Oscillator

For reasons discussed later, the 50 MHz model of the microprocessor was selected for this implementation. Ref. [13] requires the ClkIn signal, or CPU clock, to have a period between 40 ns and 50 ns, which translates to between 20 MHz and 25 MHz. This is because the 50 MHz R3081 is restricted to the 1x Clock Mode, where the ClkIn signal is passed to an internal clock doubler and converted to a double frequency clock for signals internal to the processor. The CPU oscillator selected for this implementation was the 20 MHz model, which provided a slightly longer clock period to account for the added propagation delays of the Voter FPGAs.

### b) UART Oscillator

The UART Oscillator provides a reference input to the two UARTs that is used to generate the clock signals that control the serial communications between two terminals. For the two devices to communicate, their UARTs must be set up to transfer and receive data at the same rates. In order to accomplish this, the UARTs provide an internal register that can be loaded with a divisor to generate any baud rate equal to or lower than the reference signal. The divisor is usually used to generate one of the industry standard baud rates, such as 38.4, 57.6, or 115.2 kbps. This allows the user flexibility when selecting the interface frequency.

The design goal was to provide the highest data transfer rate possible within the constraints of the I/O interface. Higher data transfer rates reduce the transfer time required for user programs and CPU FIFO contents. The original oscillator frequency selected was 16 MHz, which is the maximum allowed oscillator input to the UART. This frequency allows the UART to transmit at its maximum rate of 1Mbps. Unfortunately, other system constraints discussed in the I/O portion of the Memory Space section of this chapter could not support the maximum transfer rate.

Since the maximum baud rate could not be supported, an attempt was made to maximize the number of standard baud rates the system could support. This led to the use of an 11.0592 MHz oscillator. This frequency allows for standard baud rate generation up to 115.2 kbaud, which is the maximum transfer rate currently supported by the HCI serial port.

## c) Buffer/Driver Logic

The main purpose of the Buffer/Driver chip is to buffer the low power oscillator signals into output signals strong enough to drive the CPU and UART clock inputs. The CPUCLK signal that emerges from the buffer/driver is the timing reference signal used by the CPUs. Since the input signal to the buffer from the oscillator is not referenced by any other component, the phase and delay of the buffered signal compared to the oscillator signal does not matter. The same applies to the UARTCLK, since its frequency only needs to be matched to the device it is communicating with.

Most buffer/drivers come in packages of eight. In order to minimize the chip count, other uses of vacant glue logic chips were considered. In this case, three additional buffers could be used if the buffer/driver inverted its inputs. Two interrupt signals, UARTINT and TIMERINT, are generated by their respective devices in positive logic and the buffer/driver inverts them to the negative logic required by the CPUs. Additionally, the SYSCLK\* signal generated by the CPUs as a reference signal for bus interface transactions is inverted by the buffer/driver to get the SYSCLK signal used by the memory controller state machines out of phase from the CPU reference clock. This allows the memory controller to meet the setup and hold times required by the CPU for read and write cycles without adding additional wait states beyond those required by memory access times.

There is a very large pool of inverting buffer/drivers to choose from. The design goal used in the selection of the buffer/driver was a CMOS implementation with less than 12 ns propagation delay. The CMOS implementation reduces the static power

dissipated by the device, which is also one of the major considerations when selecting parts for a space flight board. The restriction on the propagation delay was needed to ensure the Read Clock Enable and Acknowledge signals reached the CPUs soon enough to meet the required setup times. The Texas Instruments (TI) 74AHCT540 was selected because it met these requirements [Ref. 14]. Chapter IV will present a detailed analysis of these timing signals.

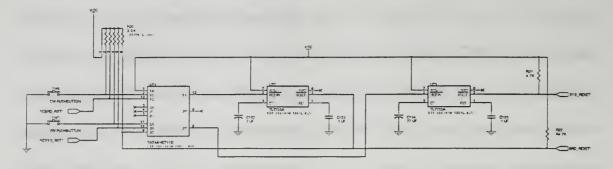

### 3. Reset System

Most computer systems have a single level reset circuit that is activated when power is turned on or by a push button switch. The TMR implementation uses a two level reset system that can be activated three different ways: power on, remotely, or by push button switch. The Reset System design evolved from the system requirement of being remotely reset and the use of serially programmed FPGAs. The main reason a two level reset was implemented was to allow the system to be reset without having the delay associated with reprogramming the FPGAs. A schematic diagram of the Reset System is shown in Figure 3.3.

When power is initially applied to the system, the Supply-Voltage Supervisors (SVSs) sense the level of the supply voltage. When the supply voltage crosses a point near 3.6 V, their RESET outputs go active and the timer function is initiated, as long as the RESIN\* input is not active. The timer function is determined by  $t_d = 1.3 \times 10^4 * C_t$ , where  $t_d$  is the delay time and  $C_t$  is the total capacitance in the timer circuit. [Ref. 15]

Figure 3.3. TMR Reset System

The first SVS, U72, uses a 7 µF capacitor in its timer circuit to hold the BRD\_RESET\* output low for 91 ms. The reset pulse allows the FPGAs to recognize the reset signal and setup for their initialization. The BRD\_RESET\* signal is also routed back to one of the inputs of a 3-input AND gate. The AND gate combines the three input signals to the second SVS, U73. This feedback prevents the timer of the second SVS from starting until the first timer has finished. The FPGAs use the time delay provided by the second SVS, 1 second using a 77 µF capacitor, to load the serial configuration data from their PROMs and to initialize. The one-second delay for loading clearly meets the 200 µs pulse required by the processor [Ref. 10]. If the two step approach were not used, the processors would attempt to make memory accesses through the FPGA vote logic, but no signals would pass through the FPGA because all the inputs and outputs of the FPGA are in a high impedance state during initialization.

After the power on reset (POR) is completed and the board is operating, there are two levels of reset the user can initiate. The first is a Board Level Reset. This reset goes through the complete POR routine. The second level of reset is a System Level Reset. It does not reset the FPGAs, but resets all the remaining devices in the system.

Each level of reset has two methods of activation. The first method is through a normally open push button switch. Since the switch is normally open, the input to the AND gate used by the switch must be pulled-up to Vcc. When either switch is closed, an active low signal is applied to the respective AND gate, which causes the appropriate RESIN\* input to go active. The second method is initiated remotely by the HCI. The HCI can send a new control word to the Control Register in the System Controller, which is described in Chapter IV. The System Controller drives the SCBRD\_RST\* and SCSYS\_RST\* inputs to the reset logic. When the System Controller activates one of these inputs, the appropriate level reset is initiated remotely.

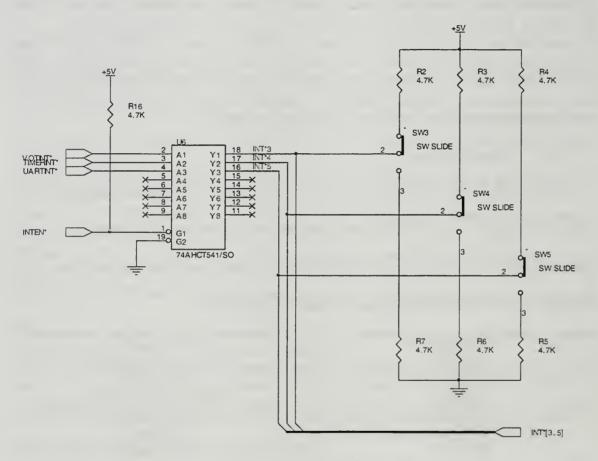

### 4. Mode Select

The IDT R3081 processors have several features that are selected during system reset. The signals used to select these features are latched into the processor off the Interrupt bus by the rising edge of RESET\*. The input signals and the functions they select are given on the following page in Table 3.1. [Ref. 10]

| Interrupt Pin | Mode Feature        |  |  |

|---------------|---------------------|--|--|

| INT(5)*       | CoherentDMAEn*      |  |  |

| INT(4)*       | 1xClockEn*          |  |  |

| INT(3)*       | Half-frequency Bus* |  |  |

| SINT(2)*      | DblockRefill        |  |  |

| SINT(1)*      | Tri-State*          |  |  |

| SINT(0)*      | BigEndian           |  |  |

Table 3.1. Mode Selectable Features. From Ref. [10]

Since the Interrupt bus must provide both the Reset Vector and the Interrupt signals, a system to multiplex the two signals had to be designed. A tri-statable non-inverting buffer/driver was used to select between the two signals. The Interrupt bus is

routed through the buffer. During reset the buffer is held in the tri-state mode, effectively blocking the interrupt signals. This allows the signals selected by pull-up and pull-down resistors to be latched into the processor. After the reset is complete, the System Controller activates the INTEN\* signal, which allows the interrupt signals to drive the processor interrupt inputs. A schematic of this system is shown in Figure 3.4.

Figure 3.4. Interrupt/Mode Logic

The three synchronous interrupt inputs, SINT\*[0..2], are hardwired to Vcc, since there was no need for the user to change them. They are hardwired to select Big Endianess, not Tri-stated, and Data Block Refill. Since VxWorks requires Big Endian functionality [Ref. 12], this mode selection was hardwired. Since there is no need to Tri-

State the processors outputs until another reset, essentially disabling the processor, this input was tied inactive. Additionally, the Data Block Refill signal was asserted to make the processor handle both data and address cache misses in exactly the same manner, as quad word reads.

The remaining interrupt inputs, INT\*[3..5], can be selected by the user at reset. This enables different functionality if the 50 MHz processors are swapped out for a slower frequency model. Since the 50 MHz R3081 is restricted to a one times clock input and half frequency bus operation, the Half-frequencyBus\* and 1xClockEn\* inputs, INT(3)\* and INT(4)\* are asserted during reset. Additionally, the Coherent DMA Enable is not asserted on INT(5)\* because the implementation does not use DMA.

#### 5. Test Connectors

Test connectors were designed into the schematic to allow for ease of troubleshooting. The initial design had connectors on each bus of the system. They were between each processor and the voter FPGAs, the voter FPGAs and the memory system, the FIFOs and the System Controller, and one collecting up all the control signals. Unfortunately, the Orcad tool used by the contractor to convert the schematics to a PCB Layout could not support the large number of pins in the system. The majority of the test connectors had to be pulled from the design. Only the connectors between the FIFOs and the System Controller remain in the implementation. For troubleshooting, chip clips will have to be used to extract the signals from the board.

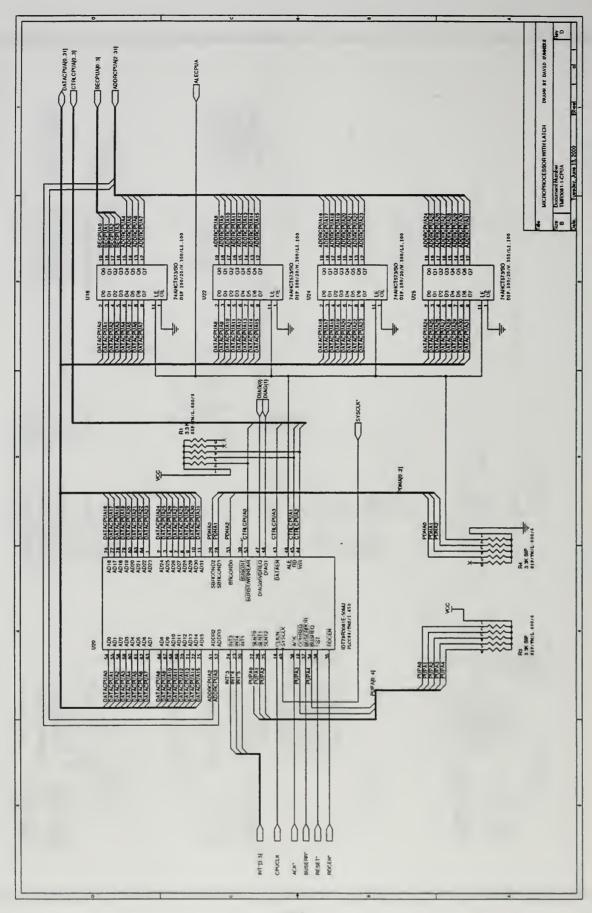

### D. MICROPROCESSOR AND ADDRESS LATCH

Although the system requires the support elements to function correctly, the key element in the system is the microprocessor. In the case of the TMR system, it is actually the three parallel microprocessors. This section discusses the model selection of the R3081 microprocessor. Since the hardware is being presented as it is grouped in the schematics, the address latches are also discussed here. The schematic diagrams of the three microprocessor/address latch pairs along with the rest of the system are given in Appendix A.

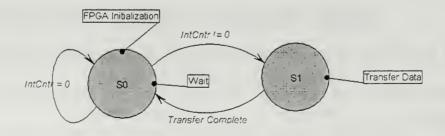

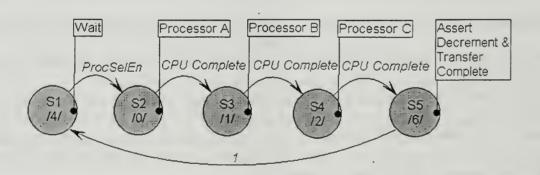

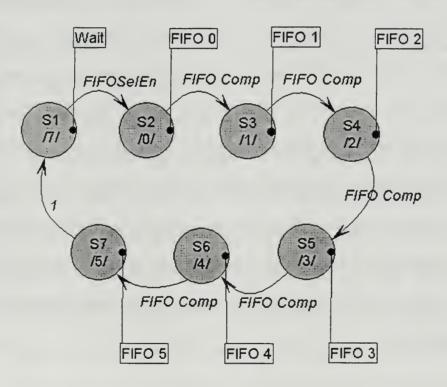

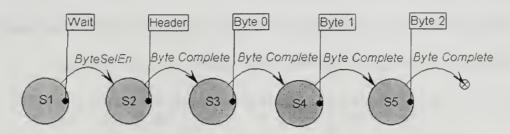

# 1. Microprocessor