**Calhoun: The NPS Institutional Archive**

Theses and Dissertations

Thesis Collection

2003-12

# Benchmarking and analysis of the SRC-6E reconfigurable computing system

Macklin, Kendrick R.

Monterey, California. Naval Postgraduate School

http://hdl.handle.net/10945/6170

Calhoun is a project of the Dudley Knox Library at NPS, furthering the precepts and goals of open government and government transparency. All information contained herein has been approved for release by the NPS Public Affairs Officer.

> Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

# NAVAL POSTGRADUATE SCHOOL

MONTEREY, CALIFORNIA

# THESIS

# BENCHMARKING AND ANALYSIS OF THE SRC-6E RECONFIGURABLE COMPUTING SYSTEM

by

Kendrick R. Macklin

December 2003

Thesis Advisor: Douglas Fouts Co-Advisor: Theodore Lewis

Approved for public release; distribution is unlimited

#### REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington DC 20503.

- 1. AGENCY USE ONLY (Leave blank)

- 2. REPORT DATE December 2003

- 3. REPORT TYPE AND DATES COVERED Master's Thesis

- 4. TITLE AND SUBTITLE: Benchmarking and Analysis of the 5. FUNDING NUMBERS SRC-6E Reconfigurable Computing System

- 6. AUTHOR(S) Kendrick R. Macklin

- 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) Naval Postgraduate School Monterey, CA 93943-5000

- 8. PERFORMING ORGANIZATION REPORT NUMBER

- 9. SPONSORING /MONITORING AGENCY NAME(S) AND ADDRESS(ES) N/A

- 10. SPONSORING/MONITORING AGENCY REPORT NUMBER

- 11. SUPPLEMENTARY NOTES The views expressed in this thesis are those of the author and do not reflect the official policy or position of the Department of Defense or the U.S. Government.

#### DISTRIBUTION / AVAILABILITY STATEMENT Approved for public release; distribution is unlimited

#### 13. ABSTRACT (maximum 200 words)

This thesis evaluates the usefulness of the SRC-6E reconfigurable computing system for a radar signal processing application and documents the process of creating and importing VHDL code to configure the user definable logic on the SRC-6E. A false-target radar-imaging algorithm was chosen and implemented on the SRC-6E. Data from alternative computational approaches to the same problem are compared to determine the effectiveness of SRC-6E solution. The results show that the implementation of the algorithm does not provide an effective solution when executed on the SRC-6E. An evaluation of the SRC-6E difficulty of use is conducted, including a discussion of required skills, experience and development times. The algorithm test code and collected data are included as appendices.

| 14. SUBJECT TERMS Benchmark, Reconfigurab Target Synthesis | 15. NUMBER OF PAGES 149 |                   |                |  |  |  |

|------------------------------------------------------------|-------------------------|-------------------|----------------|--|--|--|

|                                                            | 16. PRICE CODE          |                   |                |  |  |  |

| 17. SECURITY                                               | 18. SECURITY            | 19. SECURITY      | 20. LIMITATION |  |  |  |

| CLASSIFICATION OF                                          | CLASSIFICATION OF THIS  | CLASSIFICATION OF | OF ABSTRACT    |  |  |  |

| REPORT                                                     | PAGE                    | ABSTRACT          |                |  |  |  |

| Unclassified                                               | Unclassified            | Unclassified      | UL             |  |  |  |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. 239-18

## Approved for public release; distribution is unlimited

# BENCHMARKING AND ANALYSIS OF THE SRC-6E RECONFIGURABLE COMPUTING SYSTEM

Kendrick R. Macklin Lieutenant, United States Naval Reserve B.S., San Diego State University, 1997

Submitted in partial fulfillment of the requirements for the degree of

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

from the

# NAVAL POSTGRADUATE SCHOOL December 2003

Author: Kendrick R. Macklin

Approved by: Douglas Fouts

Thesis Advisor

Ted Lewis Co-Advisor

John P. Powers

Chairman

Department of Computer and Electrical

Engineering

#### ABSTRACT

This thesis evaluates the usefulness of the SRC-6E reconfigurable computing system for a radar signal processing application and documents the process of creating and importing VHDL code to configure the user definable logic on the SRC-6E. A false-target radar-imaging algorithm was chosen and implemented on the SRC-6E. Data from alternative computational approaches to the same problem are compared to determine the effectiveness of SRC-6E solution. The results show that the implementation of the algorithm does not provide an effective solution when executed on the SRC-6E. An evaluation of the SRC-6E difficulty of use is conducted, including a discussion of required skills, experience and development times. The algorithm test code and collected data are included as appendices.

# TABLE OF CONTENTS

| I.   | INTRO | ODUCTION                                            |

|------|-------|-----------------------------------------------------|

|      | A.    | PURPOSE1                                            |

|      | B.    | FALSE TARGET RADAR IMAGING ALGORITHM                |

|      | C.    | FALSE-TARGET RADAR-IMAGING CHIP DESIGN              |

|      | D.    | FALSE-TARGET RADAR-IMAGING PROGRAM DESIGN5          |

|      | E.    | REMAINING CHAPTER OUTLINE                           |

|      |       |                                                     |

| II.  |       | 6E ARCHITECTURE AND SOFTWARE ENVIRONMENT9           |

|      | A.    | INTRODUCTION9                                       |

|      | в.    | SRC-6E HARDWARE OVERVIEW9                           |

|      | C.    | SOFTWARE ENVIRONMENT11                              |

|      |       | 1. Operating System11                               |

|      |       | 2. Programming Environment11                        |

|      | D.    | MAJOR DOCUMENTATION12                               |

|      |       | 1. SRC-6E C Programming Environment Guide12         |

|      |       | 2. SRC-6E Fortran Programming Environment Guide .12 |

|      |       | 3. SRC-6E MAP Hardware Guide12                      |

|      |       | 4. SRC-6E MAP Macro Developers Guide12              |

|      |       | 5. Macro Data Sheet Library13                       |

| TTT. | DEVE  | LOPMENT AND TESTING IN VHDL WITH ALDEC ACTIVE-HDL   |

|      |       |                                                     |

|      | A.    | INTRODUCTION                                        |

|      | в.    | FUNCTIONAL BLOCKS                                   |

|      | _,    | 1. D-Type Flip Flops                                |

|      |       | 2. Adders                                           |

|      |       | 3. Look-Up Table (LUT)                              |

|      |       | 4. Control Logic Block (CLB)                        |

|      |       | 5. Gain Shifter                                     |

|      |       | 6. One Range Bin                                    |

|      |       | 7. Two Range Bins                                   |

|      |       | 8. Four Range Bins                                  |

|      |       | -                                                   |

| IV.  | PORT  | ING THE VHDL CODE TO THE SRC-6E19                   |

|      | A.    | INTRODUCTION19                                      |

|      | B.    | THE SRC-6E FILE TYPES19                             |

|      |       | 1info                                               |

|      |       | 2box19                                              |

|      |       | 3mc                                                 |

|      |       | 4c                                                  |

|      |       | 5. makefile                                         |

|      |       | 6vhd                                                |

|      |       | 7. Other Types                                      |

|       | C.     | CODE DEVELOPMENT21                             |

|-------|--------|------------------------------------------------|

|       |        | 1. Version 1.021                               |

|       |        | 2. Version 1.1                                 |

|       |        | 3. Version 1.2                                 |

|       |        | 4. Version 2.022                               |

|       |        | 5. Version 2.1                                 |

|       |        | 6. Version 2.2                                 |

|       |        | 7. Version 2.3                                 |

|       |        | 8. Version 2.4                                 |

|       |        | 9. Version 2.524                               |

|       |        | 10. Version 3.025                              |

|       | D.     | SYNTHESIZABLITY25                              |

|       |        | 1. Gain Shifter Changes25                      |

|       |        | 2. LUT Changes                                 |

|       | E.     | TIMING FAILURES26                              |

|       |        | 1. Single 8-bit CLAH                           |

|       |        | 2. Three 4-bit CLAH                            |

|       |        | 3. Two 4-bit and one 8-bit CLAH                |

|       | F.     | MEMORY ALLOCATION CHANGES28                    |

| V.    | ר א תו | COLLECTION AND TIMING ANALYSIS                 |

| v •   | A.     | INTRODUCTION                                   |

|       | в.     | BENCHMARK TEST PLATFORMS                       |

|       | ь.     | 1. C Program Executed on a Windows-based       |

|       |        | Machine                                        |

|       |        | 2. C Program Executed on the SRC-6E            |

|       |        | 3. VHDL Code on the SRC-6E MAP                 |

|       | c.     | TIMING DATA COLLECTION METHOD                  |

|       | D.     | TIMING DATA ANALYSIS                           |

|       | υ.     | 1. Methods                                     |

|       |        | 2. Results                                     |

|       |        | 3. Conclusions                                 |

|       |        | 5. Conclusions                                 |

| VI.   | CONCI  | LUSIONS                                        |

|       | A.     | INTRODUCTION39                                 |

|       | B.     | DIFFICULTY OF USE39                            |

|       |        | 1. Necessary Skills39                          |

|       |        | 2. Experience Level                            |

|       |        | 3. Development Time40                          |

|       | C.     | APPROPRIATENESS OF THIS ALGORITHM40            |

|       | D.     | RECOMMENDATIONS FOR FUTURE WORK40              |

|       |        | 1. Develop Implementation of More Range Bins40 |

|       |        | 2. Develop a More User-Friendly Programming    |

|       |        | Environment41                                  |

|       |        | 3. Testing Other Applications41                |

| APPEI | NDTX 2 | A                                              |

|       | -      | СПТО СТМ С 43                                  |

| APPEN     | 1DIX | EB                                           |

|-----------|------|----------------------------------------------|

|           | A.   | D-TYPE FLIP FLOP51                           |

|           | B.   | 5-BIT REGISTER51                             |

|           | C.   | 8-BIT REGISTER52                             |

|           | D.   | 13-BIT REGISTER53                            |

|           | E.   | 17-BIT REGISTER54                            |

|           | F.   | FULL ADDER55                                 |

|           | G.   | FULL ADDER WITH OVERFLOW SIGNAL55            |

|           | H.   | 5-BIT ADDER                                  |

|           | I.   | 16-BIT ADDER WITH OVERFLOW SIGNAL            |

|           | J.   | LUT                                          |

|           | K.   | CONTROL LOGIC BLOCK                          |

|           | L.   | SHIFTER                                      |

|           | М.   | ONE RANGE BIN60                              |

|           | N.   | TWO RANGE BINS63                             |

|           | 0.   | FOUR RANGE BINS64                            |

| APPEN     | DIX  | C                                            |

|           | Α.   | MACRO VHDL FILE                              |

|           | в.   | MAKEFILE84                                   |

|           | c.   | MACRO INFO FILE85                            |

|           | D.   | MACRO BLACKBOX FILE86                        |

|           | E.   | C DRIVER PROGRAM86                           |

|           | F.   | MAP CODE FILE92                              |

|           | G.   | SAMPLE PHASE SAMPLE INPUT FILE93             |

|           | H.   | SAMPLE RANGE BIN GAIN INPUT FILE93           |

|           | I.   | SAMPLE SCREEN OUTPUT94                       |

|           | J.   | SAMPLE OUTPUT DATA FILE94                    |

|           | K.   | SAMPLE RANGE BIN PHASE ROTATION INPUT FILE95 |

| APPEN     | хтаг | D                                            |

| 711 I III | A.   | SRC-6E MACRO DATA97                          |

|           | в.   | SRC-6E C PROGRAM DATA                        |

|           | c.   | WINDOWS C PROGRAM DATA                       |

| LIST      |      | REFERENCES                                   |

|           | _    |                                              |

| LLINT     | LAL  | DISTRIBUTION LIST127                         |

## LIST OF FIGURES

| Figure | 1. | False Target Radar Imaging Algorithm Usage2         |

|--------|----|-----------------------------------------------------|

| Figure | 2. | False Target Radar Image Chip Signal Flow3          |

|        |    | Internal Design of the Control Logic                |

|        |    | Signal Flow for Four Cascaded Range Bins6           |

| _      |    | SRC-6E System Diagram (After Ref. 2.)               |

| _      |    | MAP Interface Block Diagram (From Ref. 2.)10        |

| _      |    | 16-bit Adder Versions                               |

| _      |    | Comparison of Average Total Time33                  |

| _      |    | Semi-Log Comparison of Average Total Time34         |

|        |    | . Comparison of Average Time per Sample35           |

| _      |    | . Semi-Log Comparison of Average Time per Sample 36 |

| _      |    | . Comparison of Average Time per Sample             |

# LIST OF TABLES

| Table 1. | False-Target Radar-Imaging Program Example  | e Using     |

|----------|---------------------------------------------|-------------|

|          | Four Range Bins                             | . <b></b> 6 |

| Table 2. | Gain Shifter Operational Data (After Ref. 9 | .)17        |

#### ACKNOWLEDGEMENTS

I would like to thank Professor Russ Duren, formerly of the Naval Postgraduate School, but now at Baylor University, for donating his personal time and expertise to help me debug my code on several occasions. Without his assistance, the focus of this thesis would have been how I could not make the algorithm work on this computer as opposed to a presentation of benchmarks and results.

I would also like to acknowledge David Caliga of SRC Computers, Inc. for providing personal assistance in helping me to understand and use the SRC-6E computer. His help went well beyond what I would normally expect from that required by a technical support contract by personally debugging my code on several occasions.

#### EXECUTIVE SUMMARY

The purpose of this research was to evaluate the performance, correctness, and ease of use of the SRC-6E reconfigurable computing system built by SRC Computers, Inc., and also to aid in establishing a broad base of knowledge on what types of applications are appropriate for implementation on this type of machine. To this end, it was necessary to first choose a readily available yet suitably complex algorithm for implementation on the SRC-6E. The algorithm chosen was based on a custom chip design previously developed by a faculty/student research team at the Naval Postgraduate School which creates false target radar images. A C language program, written by Professor Douglas Fouts, was also available to use as a standard for comparing the accuracy of results throughout the research.

Reconfigurable computing is defined as "the capability of reprogramming hardware to execute logic that is designed and optimized for a specific user's algorithms" [1]. The SRC-6E reconfigurable computer is a Linux-based system consisting of two independent sides labeled A and B which each contain motherboards holding dual Intel P3 Xeon 1-GHz processors, 1.5 gigabytes of memory, and a SNAP interface card. The SNAP card is a custom interface card which plugs into a motherboard DIMM memory slot and provides connections to the MAP board which is located in a third section of the A single MAP board consists of two independent system. MAPs. MAP, a registered trademark of SRC Computers, Inc., is the name for the custom hardware. Each MAP consists of three Xilinx Virtex-II-series XC2V6000 FPGAs and 24 megabytes of memory. One of the FPGAs is reserved for "control

logic" while the other two, available for user programs, are called "user logic". The memory is split into six equal banks, labeled A through F, of 4 megabytes each. The user FPGAs are connected to a fixed 100-MHz clock.

Code written in the hardware description languages

Verilog and/or VHDL can be ported for use on the SRC-6E

with only minor changes. Several support files are required to make the code target the user logic. These files

primarily describe the interfaces to the code. The algorithm selected for the research described here was written

in VHDL and converted for use on the SRC-6E.

In order to evaluate the effectiveness of the SRC-6E, timing data was collected from several sources. data source was the executable created on the SRC-6E which utilizes the reconfigurable user logic. The second data source was a C program which performs the same functionality as the VHDL code. This code was compiled and executed on a 3-GHz Pentium 4 system, utilizing 2 gigabytes of DIMM memory and the Windows XP Professional operating system. The third data source was the same C program running on the 1-GHz Xeon processor on the Linux based SRC-6E (but not using the MAP). Several input data sets were created for testing. Each individual input data value consists of a 5bit number, written as two hexadecimal digits, which represent an intercepted radar signal. Data sets containing 32, 64, 128, 256, 512, 1024, 2048, 4096, 8192, 16284, 32786, 65536, 131072, 262144, and 500000 data values were used. Five timing runs were conducted for each data set on all three data sources.

The timing data shows the SRC-6E MAP execution time is extremely fast, even for very large data set sizes. However, the total execution time for the SRC-6E VHDL macro takes considerably longer than all other benchmark sources. The extra time represents delays in the system to prepare and transfer the data in and out of the MAP which cause the SRC-6E execution time to be longer for all input set sizes, initially by an order of magnitude.

As input set size is increased the timing results begin to converge. The overhead in the SRC VHDL macro clearly dominates the results for smaller sample set sizes. However, for larger sample set sizes, the overhead time is amortized over the total time to be nearly insignificant. Presumably, the SRC macro total execution time would eventually meet the other benchmark platforms if the sample set size could be further increased. However, this is not possible with the current macro design due to the memory design of the SRC-6E hardware.

Programming the SRC-6E to use user-defined macros requires knowledge of high-level programming languages, hardware description languages, hardware component design, and synthesizability. Relatively few people possess all of these skills to use the system effectively without first receiving significant training. However, programming the system using only high-level languages of C or Fortran is possible which widens the potential user base to many more people. More research needs to be performed to determine if either method produces more effective solutions.

The SRC-6E has a relatively steep learning curve.

There are a few examples in the documentation and a very

small body of work in place using the system. The errors generated by the system during development are not intuitive and cannot be solved without previous experience with solving the same errors. There are no development tools in place to assist novice users in programming the system.

More research is required to see how much experience on the system is required to prevent and or recognize these types of errors quickly.

The development time to implement solutions on this system appears to be high, primarily due to the steep learning curve and lack of development tools. More research must be performed to quantify the development time and see how it improves once a group of experienced repeat users is grown. No research has yet been performed with large projects, employing multiple programmers, to see if the total project time can be reduced effectively.

Since it is pipelined and supports parallel processing, the chosen implementation of the false-target radarimaging algorithm appears to be one that would benefit from a reconfigurable computer. However, the current implementation has been shown to lack the necessary parallelism required to fully utilize the hardware and make it effective. Without increases in the memory size allocated for the user logic, the implementation on the SRC-6E is not an effective solution in terms of development time, processing time, or cost-effectiveness.

#### I. INTRODUCTION

#### A. PURPOSE

The purpose of this research was to evaluate the performance, correctness, and ease of use of the SRC-6E reconfigurable computing system built by SRC Computers, Inc., and also to aid in establishing a broad base of knowledge on what types of applications are appropriate for implementation on this type of machine. To this end, it was necessary to first choose a readily available yet suitably complex algorithm for implementation on the SRC-6E. rithm chosen was based on a custom chip design previously developed by a faculty/student research team at the Naval Postgraduate School which creates false target radar images. A C language program, written by Professor Douglas Fouts, was also available to use as a standard for comparing the accuracy of results throughout the research. This chapter discusses the basics of the false radar imaging algorithm, use of the chip design and C program in the research and gives an overview of the major steps required to implement and test the algorithm using the SRC-6E.

#### B. FALSE TARGET RADAR IMAGING ALGORITHM

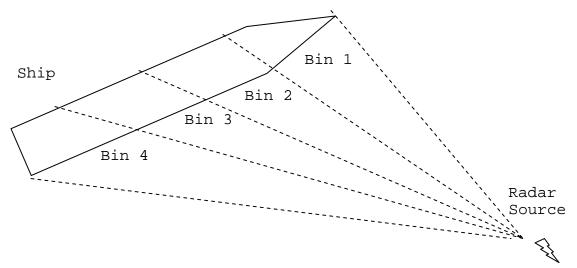

The algorithm works by splitting a false target image into several range bins, as shown in Figure 1, where a ship is split into four range bins. Each range bin represents a portion of the vessel based on the distance from the radar source. Greater resolution can be achieved by having a greater number of range bins for a given false target. It can be observed from the geometry that the radar-signal travel distance is different for each range bin.

Figure 1. False Target Radar Imaging Algorithm Usage

Based on knowledge of a ship's radar image, an operator can set phase rotation and gain constants for each range bin. The algorithm begins with the interception and sampling of an interrogating radar pulse. The sample phase is then rotated by adding a rotation constant to it. Next, the sine and cosine are calculated. The gain is then applied to the results by multiplying by a gain value. The results of each range bin are then summed up to produce a radar reflection signal at a given time. With proper use, the ship can be made to appear in a false position, be of a different type of target, or to appear to be traveling with other ships.

### C. FALSE-TARGET RADAR-IMAGING CHIP DESIGN

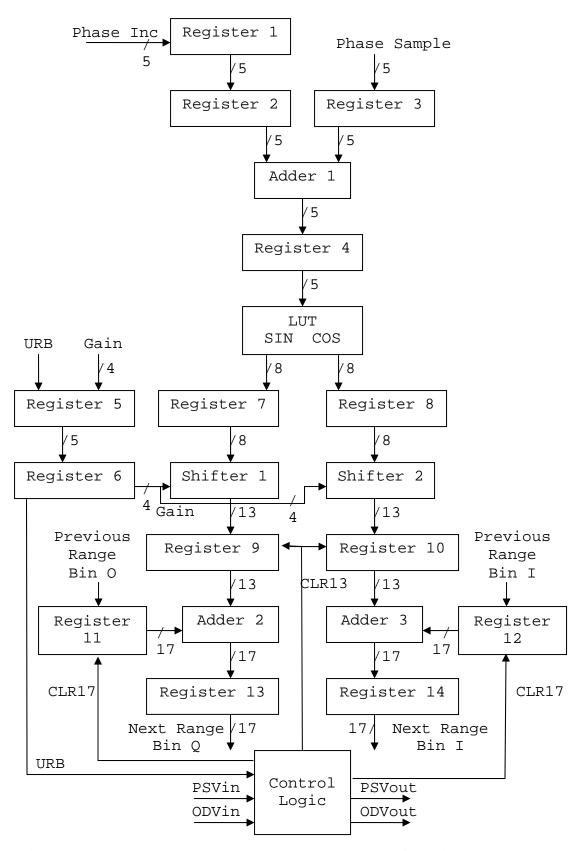

The false-target radar-imaging chip consists of a 6-stage pipeline which performs all necessary functions to create a false radar reflection for a single range bin. Figure 2 shows the signal flow through the slightly simplified version as was implemented during the research.

Figure 2. False Target Radar Image Chip Signal Flow

The basic steps of the algorithm are performed as follows:

- 1. The phase sample enters into register 3.

- 2. The phase rotation value enters into register 1, is then loaded into register 2, and is then added to the phase sample at adder 1. The results are then loaded into register 4.

- 3. The contents of register 4 enter the lookup table (LUT) and Sine and Cosine results are calculated. The remainder of the pipeline is split into two identical portions for each data result. The following steps outline the path for the Sine result.

- 4. The gain value enters at register 5, is then loaded to register 6, and proceeds to shifter 1 where it controls how the contents of register 7 are shifted before they proceed to register 9. This accomplishes modulo-2 multiplication.

- 5. The result from a preceding range bin enters at register 11 and is added to the contents of register 9 in adder 2 before proceeding to register 13.

- 6. The contents of register 13 are now available as output Q if this is the last range bin in the series or are sent to register 11 of a following range bin.

The control logic block receives signals URB (use range bin), PSVin (phase sample valid input), and ODVin (output data valid input). These signals are used to create the

CLR13 (clear 13-bit register), CLR17 (clear 17-bit register), PSVout (phase sample valid output), and ODVout (output data valid output).

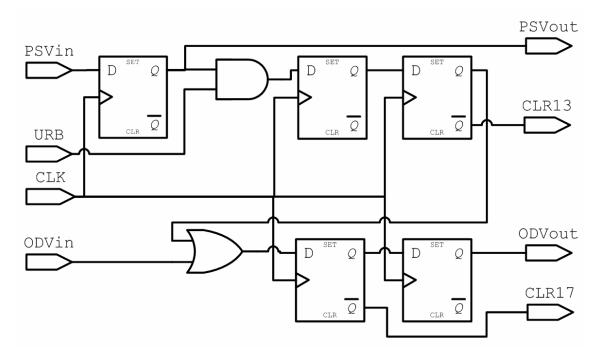

The internal design of the control logic is shown in Figure 3. The CLR13 and CLR17 signals are used to clear the register contents at the appropriate time in the pipelines when they do not contain valid data. This occurs during pipeline startup and shutdown. The PSVout signal is present to show the DRFM signal is valid. The ODVout sig-

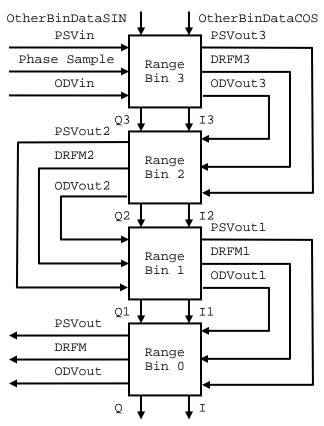

nal is present to show that outputs Q and I contain valid data. The URB signal is present to allow the operator to disable a range bin. Figure 4 shows the signal flow when four range bins are connected together.

Figure 3. Internal Design of the Control Logic

#### D. FALSE-TARGET RADAR-IMAGING PROGRAM DESIGN

The false-target radar-imaging program was written in the C language. It performs the same arithmetic calculations as the false radar imaging chip but uses nested loop iterative structures instead of pipelines. While the chip requires a separate pipeline for each range bin, the program simply adds additional length to the appropriate arrays, trading off memory utilization for computational logic. Table 1 shows how the results of each of four range bins with an input of N samples are placed into the two dimensional array created by the program. Each row of the table is then summed up to produce the false target radar signal results.

Figure 4. Signal Flow for Four Cascaded Range Bins

| Bin 0      | Bin 1        | Bin 2        | Bin 3        |

|------------|--------------|--------------|--------------|

| Sample 1   | 0            | 0            | 0            |

| Results    |              |              |              |

| Sample 2   | Sample 1     | 0            | 0            |

| Results    | Results      |              |              |

| Sample 3   | Sample 2     | Sample 1     | 0            |

| Results    | Results      | Results      |              |

| Sample 4   | Sample 3     | Sample 2     | Sample 1     |

| Results    | Results      | Results      | Results      |

| •••        | •••          | •••          | •••          |

| Sample $N$ | Sample $N-1$ | Sample $N-2$ | Sample $N-3$ |

| Results    | Results      | Results      | Results      |

| 0          | Sample $N$   | Sample $N-1$ | Sample $N-2$ |

|            | Results      | Results      | Results      |

| 0          | 0            | Sample N     | Sample $N-1$ |

|            |              | Results      | Results      |

| 0          | 0            | 0            | Sample $N$   |

|            |              |              | Results      |

Table 1. False-Target Radar-Imaging Program Example Using Four Range Bins

The program was used as both a trusted source for results to test the research against as well as used in the timing comparisons discussed in Chapter V. The full code for the program can be viewed in Appendix A.

### E. REMAINING CHAPTER OUTLINE

The following outlines the remaining chapters which roughly follow the major steps that were taken throughout the research:

- Chapter II discusses the SRC-6E architecture, programming environment, and documentation.

- Chapter III discusses programming the chip design using VHDL.

- Chapter IV discusses porting the VHDL code to SRC-6E environment

- Chapter V presents the data collection methods and analysis.

- Chapter VI provides conclusions and future work recommendations.

- Appendix A contains the modified C program originally written by Professor Douglas Fouts which was used a standard for output correctness and as a source of timing data.

- Appendix B contains the final version of the VHDL code that was tested before porting to the SRC-6E.

- Appendix C contains the final version of the files used on the SRC-6E, including sample input and output.

- Appendix D contains all of the timing data collected during the research.

### II. SRC-6E ARCHITECTURE AND SOFTWARE ENVIRONMENT

#### A. INTRODUCTION

This chapter provides a brief overview of the hard-ware, software, and documentation, of the SRC-6E reconfigurable computing system. Reconfigurable computing is defined as "the capability of reprogramming hardware to execute logic that is designed and optimized for a specific user's algorithms" [1].

#### B. SRC-6E HARDWARE OVERVIEW

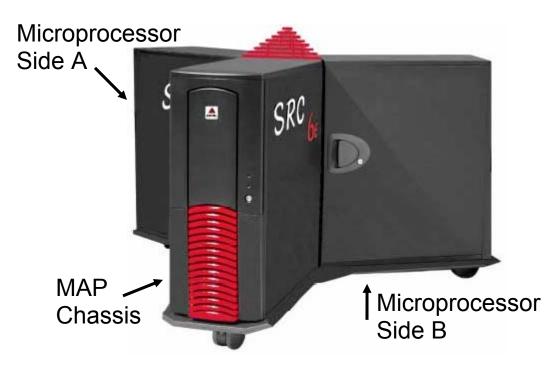

The SRC-6E computer consists of two independent Linux computers (labeled A and B) and a MAP board, (see Figure 5).

Figure 5. SRC-6E System Diagram (After Ref. 2.)

MAP, a registered trademark of SRC Computers, Inc., is the name of the custom reconfigurable hardware. Each independent Linux computer contains a motherboard holding dual In-

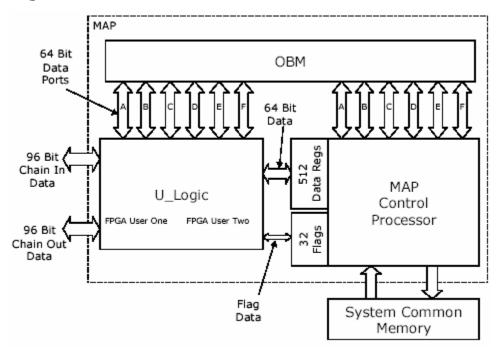

tel P3 Xeon 1-GHz processors, 1.5 gigabytes of memory, and a SNAP interface card. The SNAP card is a custom interface card which plugs into a motherboard DIMM memory slot and provides connections to the MAP board which is located in the MAP Chassis. A single MAP board consists of two independent MAPs. A block diagram of a single MAP is shown in Figure 6. A MAP consists of three Xilinx Virtex-II-series XC2V6000 FPGAs and 24 megabytes of memory (labeled OBM on Figure 6).

Figure 6. MAP Interface Block Diagram (From Ref. 2.)

One of the FPGAs is reserved for "control logic" while the other two, available for user programs, are called "user logic". The OBM memory is split into six equal banks, labeled A through F, of 4 megabytes each. The user FPGAs are connected to a fixed 100-MHz clock, which seems overly restrictive. According to Xilinx product specification sheets, the Virtex-II-series FPGAs can ran at clock speeds as low as 1 MHz and upwards of 400 MHz [3]. Programmer

control of the clock speed on the SRC-6E would make the system more flexible. Each MAP also has a chain port which can be used for direct I/O to the user logic, but was not used during this research.

### C. SOFTWARE ENVIRONMENT

#### 1. Operating System

The operating system for the SRC-6E is Red Hat Linux, which has been augmented with custom drivers and libraries to support the MAP and SNAP hardware. The built-in graphical text editor in Linux is called GEdit. Programmers experienced with UNIX can use the standard line type text editors such as VI if they choose. Both contain the minimal functionality required of a text editor to write the required files for the SRC-6E.

### 2. Programming Environment

The programming environment for the SRC-6E is called Carte. Carte allows a user to write code in a high level language, either C or Fortran, that directly targets the user programmable FPGAs in the MAP. In addition, users can write their own "macros" using the hardware definition languages Verilog and/or VHDL. At compile time, all user code and macros are linked together into a single executable file. Carte includes standard compilers for the Intel microprocessors as well as custom MAP compilers for both Fortran and C. Synplify Pro software by Synplicity, Inc. is used for FPGA place and routing. This program normally runs under Windows version but is executed in the Linux environment using a Windows emulator called Wine.

Since Carte relies on the built-in Linux editors, the SRC-6E programming environment does not have any of the modern features a programmer expects from editors available

in products such as Microsoft's Visual C++ or Borland's J-Builder. Lack of syntax and error checking in the programming environment is a serious drawback when using this system. Some error messagess are produced at compile time, but they are cryptic at best, especially for someone not used to the Linux environment. There are several file types which must interact during the compile process, as will be discussed in Chapter IV. The intricate details of these files can be quite confusing and it is often difficult to identify which file contains the problem based on the error messages given at compile time. Rudimentary checking of these files within a custom editor would greatly improve the entire programming process.

#### D. MAJOR DOCUMENTATION

The documents discussed here come with the SRC-6E to aid in its programming.

#### 1. SRC-6E C Programming Environment Guide

Driver code must be developed to create the interface to the user logic. This document describes how to write this code using the C language [4].

## 2. SRC-6E Fortran Programming Environment Guide

Similar to the C Programming Environment Guide, this document describes how to write similar code using the Fortran language [5].

#### 3. SRC-6E MAP Hardware Guide

This document contains hardware implementation specifics of the MAP which are well below the level required for users to successfully program the SRC-6E [2].

#### 4. SRC-6E MAP Macro Developers Guide

This document discusses general information on the use of the Macro Data Sheet Library, including naming conventions, interfaces, fanout and combinatorial delays [6].

## 5. Macro Data Sheet Library

The library contains data sheets for all macros developed by SRC for the SRC-6E. A list of all currently supported macros is available in a technical note, Ref. 7. The macros can be used like regular function calls in the chosen programming environment language (C or Fortran). The macros include all basic math and logic functions currently supported by the environment. There are also several support macros which include, among others, various macros for combining and splitting data structures.

This chapter provided an overview of the hardware, software and documentation of the SRC-6E computer. The next chapter will discuss development and testing of the VHDL code used in the research.

THIS PAGE INTENTIONALLY LEFT BLANK

# III. DEVELOPMENT AND TESTING IN VHDL WITH ALDEC ACTIVE-HDL 5.2

#### A. INTRODUCTION

This chapter describes the development of the false-target radar-imaging macro in VHDL before it was ported to the SRC-6E environment. This portion of the research was performed before receipt of the SRC-6E system or any training on the system was received. As a result, the macro that was originally developed contained the correct functionality but was not optimized for the SRC-6E environment. Development of the macro was performed in a Windows XP environment using Aldec Active-HDL 5.2 software.

#### B. FUNCTIONAL BLOCKS

The False-Target Radar-Imaging chip was implemented directly into VHDL by direct programming of the code. Each component of the design was created using separate functional blocks of VHDL code. Several of the basic building blocks of code were taken from Ref. 8 and modified as necessary. The code for this section can be viewed in Appendix A.

# 1. D-Type Flip Flops

The six pipeline stages required registers, which were implemented as D-type Flip Flops. Single-bit registers were designed that are loaded on the rising clock edge and have both enable and clear input signals. The 5-, 8-, 13-, and 17-bit registers required for the designed were created by instancing multiple copies of the single-bit registers.

#### Adders

A single-bit full adder was coded using the design of Ref. 8. The 5- and 16-bit adders required for the design were created by instancing multiple copies of the single-

bit adder. A simple ripple carry design was used at this point in the research. Chapter IV will discuss why this was later modified with carry look-ahead circuitry. For the 16-bit adder, a special final single-bit stage was developed to propagate an overflow signal if generated by previous range bin stages.

## 3. Look-Up Table (LUT)

The LUT was originally developed starting with a design from Ref. 7, but was later heavily modified. The LUT takes a single 5-bit input and performs simultaneous lookups using data from both sine and cosine tables. The output of the LUT is two 8-bit values, one each for sine and cosine. The initial design had the correct functionality but was later modified after porting to the SRC-6E. The required modifications will be discussed in Chapter IV.

# 4. Control Logic Block (CLB)

The CLB was created by instancing several of the flip flops with some basic logic functions to create the design shown in Figure 3.

## 5. Gain Shifter

The shifter takes a 4-bit control input and shifts the 8 bits of input data into a 13-bit output. The shifter is designed to provide a maximum gain multiplication of 1024. However, applying this to an 8-bit input results in an 18-bit output with more dynamic range than is necessary [9]. Therefore, the least significant 5 bits are truncated to create a 13-bit output. Table 2 shows how the control bits affect the shift and the resulting resolution of the output.

| Control<br>Code | Multiplication<br>Factor | Size of<br>Shift | Sin/Cosine Wave<br>Resolution |

|-----------------|--------------------------|------------------|-------------------------------|

| 0               | 1                        | 0                | 3                             |

| 1               | 2                        | 1                | 4                             |

| 2               | 4                        | 2                | 5                             |

| 3               | 8                        | 3                | 6                             |

| 4               | 8                        | 3                | 6                             |

| 5               | 16                       | 4                | 7                             |

| 6               | 32                       | 5                | 8                             |

| 7               | 64                       | 6                | 8                             |

| 8               | 16                       | 4                | 7                             |

| 9               | 32                       | 5                | 8                             |

| 10              | 64                       | 6                | 8                             |

| 11              | 128                      | 7                | 8                             |

| 12              | 128                      | 7                | 8                             |

| 13              | 256                      | 8                | 8                             |

| 14              | 512                      | 9                | 8                             |

| 15              | 1024                     | 10               | 8                             |

Table 2. Gain Shifter Operational Data (After Ref. 9.)

Because the input data could be negative, it was also necessary to preserve the sign bit by copying it as necessary to the upper bits in the output. The original version of this code used a case statement and some simple math to determine which bits were shifted where. The version ran correctly in the Aldec simulation software, but required

modification when porting to the hardware, which will be discussed further in Chapter IV.

## 6. One Range Bin

A single range bin was created by instancing the above parts and creating an appropriate interface. The code was tested by comparing the output to the C program run on the same data set. After some minor error correction to the lookup table entries, the code was incorrectly deemed to be correct. Additional testing later conducted with two range bins yielded additional errors in the CLB that were not found in the single range bin tests.

# 7. Two Range Bins

A system with two range bins was then created by instancing two of the single range bins previously tested. Tests run on the same data sets with the C program yielded errors. As previously mentioned, problems were eventually discovered with the timing within the CLB. These problems were not identified while testing the single-range-bin since the CLB primarily creates signals to handle the interaction between multiple range bins. After correction of the errors, the output was deemed to be correct.

## 8. Four Range Bins

Finally, a system with four range bins was created by instancing four of the single range bins with an appropriate interface. The signal flow of four range bins is shown in Figure 4. The code worked properly the first time. It was this version of the code that was initially ported to the SRC-6E.

This chapter discussed VHDL code development. The next chapter will discuss porting the code to the SRC-6E.

## IV. PORTING THE VHDL CODE TO THE SRC-6E

#### A. INTRODUCTION

This chapter discusses the porting of the VHDL code to the SRC-6E and the required support files. Also discussed are changes that were required to the original code to make it compatible with the SRC-6E.

## B. THE SRC-6E FILE TYPES

The process of writing code to target the user logic requires several file types. To import a user macro from either VHDL or Verilog, five files must be created: .info, .box, .mc, .c, and the makefile. Using only the last three, one can write code that targets the user logic without using a user defined macro. Examples of these file types can be viewed in Appendix C, which contains the final versions of all the files used.

# 1. .info

This file type is required whenever a user macro is used. It contains the following information:

- Macro name

- Macro type stateful, external, and pipelined

- Latency a number stating how many clock cycles before valid output is generated by the macro.

- List of inputs and outputs

The file type ".info" is a naming convention and is not required. Any filename can be used as long as it matches that listed in the makefile.

# 2. .box

This is another file type that is required only when using a user-defined macro. It is a Verilog style description of the input and output variables of the macro. The Verilog description is necessary for both VHDL and Verilog

macros. As with the .info type, the .box name is only by convention.

#### 3. .mc

This file type is C code written to target the user logic. All code in this file will be implemented in hardware along with the user macro. Using this file type, it is possible to write code for the hardware using only the high-level language C without using any user-defined macros defined with a hardware description language.

## 4. .c

This file type is regular C code which provides the interface between the operating system and the hardware code defined in the .mc file. Code implemented in this file is executed on the Xeon processors.

## 5. makefile

This file is used by the command "make" when all the files are compiled and linked. It contains all of the file names and paths used, as well as the desired final executable name. Compiler flags and options can also be stated in this file.

#### 6. .vhd

This file type is for VHDL macro files. In general, it is safest to merge multiple files into one. However, it is possible to build with separate files as long as they are listed in the proper order in the makefile. The compiler appears to be single pass so the files must be in the order they are used, with the lowest order file listed first.

### 7. Other Types

Two other file types can be used by users programming the user logic: .f, which is a Fortran file, and .v, which

is a Verilog file. These file types were not used during this research.

#### C. CODE DEVELOPMENT

Porting of the macro code began with creation of the required support files previously mentioned. Although the files are relatively small, creating them was non-trivial as there were no previous examples using VHDL macros. The process was a painful series of trial and error, particularly with the required contents of the .info and .box files. The code went through ten major revisions, with three major versions, over a period of about six months.

### 1. Version 1.0

The single-range-bin VHDL code was imported to the SRC-6E and all code modules were merged into a single .vhd file. The required support files were first generated using some unrelated examples in the C Programming Guide and a lot of guessing. The SRC data packing macros called combine and split were used to pack and unpack the data in the .mc file into two memory banks for input and one for output. Much trial and error was attempted on this version, but it would never make to create an executable.

#### 2. Version 1.1

After discussion with SRC technical support, some new changes were tested. The .info and .box file format questions were mostly resolved in this version. The order of declarations within the .vhd file was changed to make the main macro appear as the top level to the compiler. The gain shifter code was modified to make it synthesizable. This version compiled to executable but caused unexplainable segmentation faults when run.

## 3. Version 1.2

In order to isolate the faults in this version, empty macros were made in VHDL consisting of only the interface information. After determining the problem was in the support files, the original VHDL macro was restored. Problems were isolated with misuse of the SRC packing macros and various other syntax errors. After much further work and testing, this version created a working executable which produced the proper output expected for a single range bin on a 32 sample size input.

## 4. Version 2.0

Encouraged by the success, a new version was created which attempted to implement four range bins. The SRC packing macros were not used in this implementation because they could not combine vectors shorter than 8 bits without wasting the remaining space. The VHDL macro uses 1-, 4-, 5-, and 17-bit signals. These odd sizes could not be efficiently combined with the pre-built macros and all packing of data was implemented in the C program, combining all input into two 64-bit words using a series of shifting and logic with masks. The VHDL macro interface was also modified to support the changes. This version created a working executable; however, some of the output data was incorrect.

## 5. Version 2.1

In order to help identify where the problems were, the output format was modified in the .c program to display the outputs of all four range bins. After several changes, the code began hanging when executed during the call to the MAP function. On recommendation of the SRC technicians, the method in which the array sizes were calculated was modified to ensure the arrays were properly padded and aligned

on 32-bit memory boundaries as required. The changes resolved the hanging problem but the output data was still incorrect.

#### 6. Version 2.2

At this point, the researchers were stumped and searching for any possible reasons why the output data was wrong. The majority of the output was correct. generated several correct values followed by a single incorrect value. The remaining output was correct up until a certain point before the end of the data where it all went Exploring all possibilities, it was discovered that bad. the macro was failing the timing requirements to run within the 100-MHz clock. No errors or warnings were produced by the SRC environment to state this. The timing results are created along with many other files during the make process. For example, running the make process on Version 3.0 of this research generates 54 files split over 3 directories. Locating useful debugging information within these many files can be a chore. How the timing failures were resolved will be discussed later, but they ended up not being the problem.

#### 7. Version 2.3

In order to troubleshoot the corrupt data problem, the 16-bit adder code was removed, which allowed the direct output of each of the four range bins to appear in the output. The data generated by each of the range bins showed the same general format of being mostly correct but all going bad after a certain point. Much attention was turned to the control logic at this point to see if it was the culprit but no errors could be found. To help isolate the problem, the current version of the VHDL code was exported back to the Windows environment and it produced the correct

output. At this point, the SRC-6E was incorrectly suspected to have either a software or hardware bug, possibly in the memory transfers. The software environment has a useful debugging mode called MAPTRACE which can be used to view the data before and after it is sent to the MAP. Observations of the file generated by MAPTRACE showed that the data was being passed to and received by the MAP correctly.

## 8. Version 2.4

This version still had the 16-bit adder removed. Minor changes to the LUT and gain shifter were implemented in this version to ensure that they were fully synthesizable but they did not affect the output. Troubleshooting with this version did not solve the problem but helped narrow the focus to the interface. Upon close examination of the interfaces it was noted that there were differences between the Windows version and the SRC version as to the way the data was packed in the SRC version. After exporting the packed data to the Windows version, the code produced the same identical faulty output as the SRC version. Since the two versions both produced the same identical output, it was determined that the problem had to be with the interface and input data.

#### 9. Version 2.5

After closer inspection of the interface and the method used to pass in data, it was observed that the gain and phase shift signals were not being applied properly. This was an operational problem as the macro code was correct. Modifying how the signals were applied fixed the problem with the faulty outputs. At this point, the code was producing correct output and data collection was started on various sized data sets. While collecting the

data, it was noted that a segmentation fault would occur above certain array sizes.

#### 10. Version 3.0

After discussion with SRC technical support, the code was modified to use a dynamic array allocation method which will be discussed later. The memory usage changes corrected the problem. All extra unnecessary output was also removed in this version. This final version was used to collect the data and is shown in Appendix C.

#### D. SYNTHESIZABLITY

Synthesizability is a style of hardware description language programming which allows the available layout tools to properly convert the code for hardware implementation on an FPGA. During the design of the code, the Aldec software was only used to simulate the VHDL code. Therefore, it only tested the code for functionality and did not consider if the code could actually be implemented in hardware. Two of the original code blocks, the gain shifter and LUT, required modification once ported to the SRC-6E so the layout tool could define them in hardware. The root cause of this was inexperience with both the VHDL language and the concept of synthesizability.

## 1. Gain Shifter Changes

The gain shifter went through two changes. Initially, the code was defined such that some of the variable bit widths were defined at run-time. This worked fine during emulation but could not be implemented in hardware. To make it work the code was written with a "case" statement that outlined specifically every possibility at runtime. Implementing this in hardware requires redundant logic and decoders to choose which portions to use during run time. Later, the code was streamlined again to remove an unneces-

sary function call which provided some savings in the final hardware definition. The function call, which converted data types from bit\_vector to integer, also had an unnecessary variable length defined at run-time. When removing the variability, it was determined that the entire function was not required and the "case" statement was modified to incorporate the function's results directly.

# 2. LUT Changes

The same function call that was made in the Gain Shifter was also used in the LUT. Although this code worked properly, even with the variable length at runtime, the function call was unnecessary and similar methods were used to remove it from the code entirely. The removal resulted in a small space savings on the FPGA.

## E. TIMING FAILURES

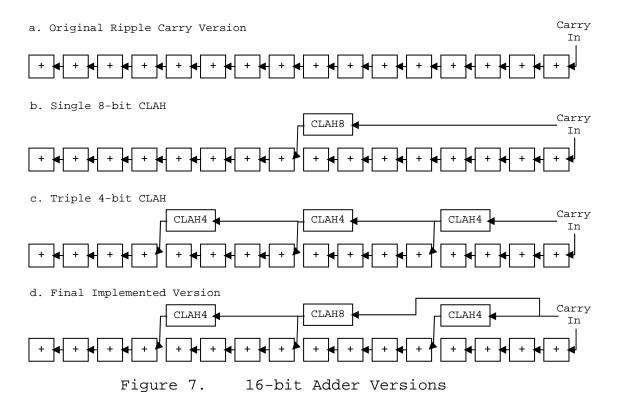

While debugging the code to determine the cause of some faulty output on the SRC-6E, it was noted that the macro was failing timing requirements for implementation with the 100-MHz clock. The worst path through the logic was reported to be in the portion of the pipeline that contained the 16-bit adder and that it exceeded the required time by 4.310 ns. The cause of the poor timing was that the 16-bit adder was initially implemented with a simple design using ripple carry propagation, shown in Figure 7a.

Several alternative designs were tested using carry look-ahead (CLAH) circuits to bring the delay time within that required for the 100-MHz clock. Of note, these modifications did not affect the output in any way and were not the solution to the problem being investigated at the time. The problem being investigated involved passing in improper input. Despite the fact that the timing was failing, the circuits were still working properly, demonstrating that there was possibly some error within the timing calculations or more likely that there was additional padding engineered within the design.

## 1. Single 8-bit CLAH

A single 8-bit CLAH circuit was designed and placed in the center of the carry chain, which effectively splits the chain in half as shown in Figure 7b. This improved the time by almost 3 ns, but the circuit still failed timing by 1.615 ns.

## 2. Three 4-bit CLAH

A 4-bit CLAH circuit was designed and placed at three points in the carry chain. The circuit chained groups of four carries to each other, as shown in Figure 7c. This design slightly improved the timing but was still inadequate.

## 3. Two 4-bit and one 8-bit CLAH

Finally, combinations of 4-bit and 8-bit CLAH circuits were used, which effectively split the 16 carries into four pieces, as shown in Figure 7d. Initially, this design only improved the timing slightly which remained about 1.2 ns over what was required. Coincidentally, at the time of this testing, an upgrade to the Carte software was released, version 1.5. Remaking the same design after the upgrade created a result that was 0.401 ns under time. The reason why the new version of the software caused the timing improvement remains a mystery. No further modifications were made after this point.

## F. MEMORY ALLOCATION CHANGES

Data passed into the MAP must be properly declared and aligned. There are two methods to accomplish this. The first method attempted used the SRC function "addr32." This method uses fixed sized arrays declared at compile time. The addr32 method worked fine up to fixed size arrays of 166,581 but caused segmentation faults when exceeding this value. A trial and error approach was used to determine the exact value at which the segmentation faults began. The number 166,582 has no apparent meaning when related to array sizes and is a very unusual number to fail on. Communication with SRC Computers, Inc. could not re-

solve why this occurs. However, using the second available method with the "cache\_alligned\_allocate" function allowed the array sizes to be declared correctly. This method uses run-time allocation to declare the proper array sizes and was tested successfully up to array sizes of 500,000 64-bit elements. Based on 4 megabytes of memory per bank, the theoretical limit is 524,288 64-bit values, but this upper limit was not tested.

This chapter discussed the necessary changes required to port the VHDL code to the SRC-6E environment. The next chapter will discuss benchmarking the SRC-6E, including data collection and analysis.

THIS PAGE INTENTIONALLY LEFT BLANK

#### V. DATA COLLECTION AND TIMING ANALYSIS

#### A. INTRODUCTION

This chapter discusses the benchmarks and methods used for collection of data and its analysis during the research.

## B. BENCHMARK TEST PLATFORMS

## C Program Executed on a Windows-based Machine

The C program shown in Appendix A was compiled and executed on a 3-GHz Pentium 4 processor system with 2 gigabytes of RAM running the Windows XP Professional operating system. The primary reason for this benchmark was to draw a comparison for cost-effectiveness between the high-cost special purpose SRC-6E system and a modern, off-the-shelf, general purpose computer.

# 2. C Program Executed on the SRC-6E

The same C program was compiled and run directly on the SRC-6E without using any of the custom hardware. Therefore, the data collected is based on the Linux operating system running on a 1-GHz Xeon 3 processor with 1.5 gigabytes of RAM. Although the system contains dual processors, only one thread is created while running the code and therefore it is believed that only one processor is utilized during the test. The primary reason for this benchmark was to test if the algorithm itself is suitable for implementation on the user-logic.

#### 3. VHDL Code on the SRC-6E MAP

The VHDL user macro and support files (shown in Appendix C) were built and executed on the SRC-6E MAP. Two timing data results were collected from each of the runs, the total run time for the entire execution and the time of

execution on the MAP only. The two timing data results compare overhead time to actual execution on the MAP.

#### C. TIMING DATA COLLECTION METHOD

The input data sets were composed to represent a stream of intercepted radar samples. Each data item consists of two hexadecimal characters representing a five-bit intercepted radar sample. The 32-sample-size data set is shown in Appendix C, which represents the decimal numbers 0 to 31 in order. All other-sized sample sets were created by duplicating and repeating the same 32 samples in order. By doubling each previous sample set size the following set sizes were created: 32, 64, 128, 256, 512, 1,024, 2,048, 4,096, 8,192, 16,284, 32,786, 65,536, 131,072, and 262,144. The final set size of 500,000 was chosen as a convenient, large value that was close to the upper array size restriction allowed by the four megabytes of memory per bank on the SRC-6E.

Data from all test platforms were collected in order of increasing input set size. All raw data used in the timing analysis can be observed in Appendix D. The timing data was collected by running five consecutive runs of each input data set on each of the three benchmark platforms. The data for the Windows XP system were collected after a fresh reboot with all unnecessary programs closed. It should be noted that observation of the system usage during execution of the code showed that the processor and memory were not fully utilized. The reasons why the processor did not appear to be fully used and the methods Windows uses to measure performance are unknown. The SRC-6E system data were collected by running the executables on side A when no other users were using the system.

# D. TIMING DATA ANALYSIS

#### 1. Methods

The timing data are displayed in two types of graphs. The first is the average total time each test platform takes for each data set. The average is taken of the five data points for each input set size. The second is the average time per sample for each input set. First, the average is taken over the five data points and then it is divided by the input set size. All graphs are connected with straight line approximations between data points.

# 2. Results

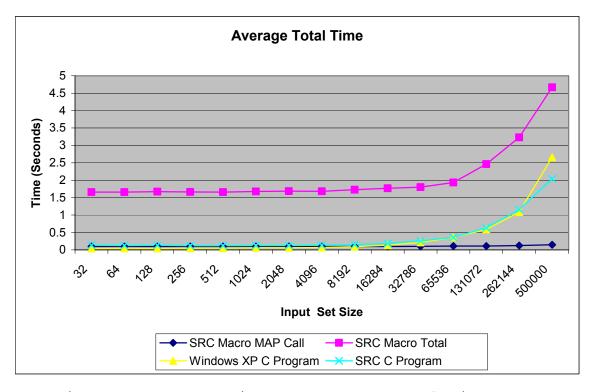

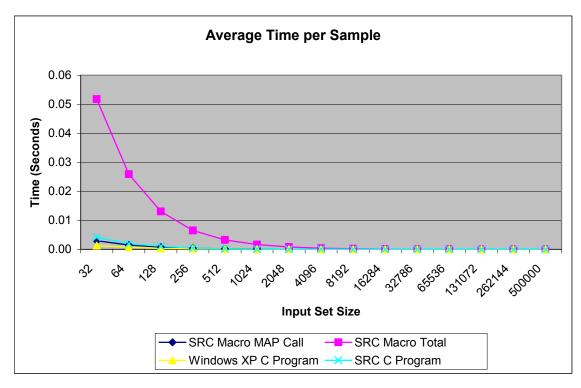

Figure 8 shows the average total time vs. input set size for each of the four timing result sets.

Figure 8. Comparison of Average Total Time

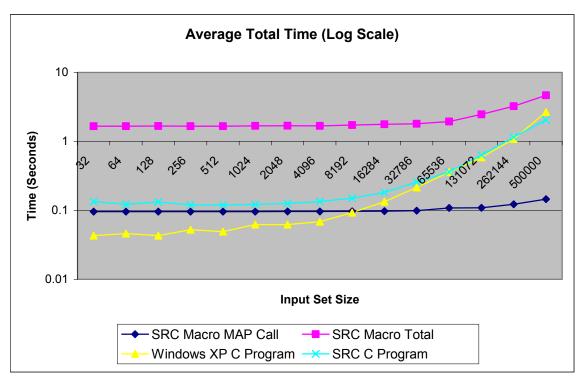

Figure 9 shows the same data displayed on a semi-log scale for better clarity in the lower sample set size region.

All four curves are fairly constant up to the 16,284 sample

size. This result shows that, for small data set sizes, the overhead times inherent in the systems are much greater than the calculation times. We consider overhead to be all the data file read/write operations and memory accesses required to prepare the data for calculations. The SRC Macro MAP Call curve clearly shows the calculation time is insignificant compared to the total processing time.

Figure 9. Semi-Log Comparison of Average Total Time

The SRC Macro MAP Call curve also shows the MAP execution time is extremely fast, even for very large data set sizes. However, the SRC Macro Total curve shows the total execution time for the VHDL macro takes considerably longer. The extra time represents delays in the system to prepare and transfer the data in and out of the MAP which cause the SRC execution time to be longer for all input set sizes, initially by an order of magnitude.

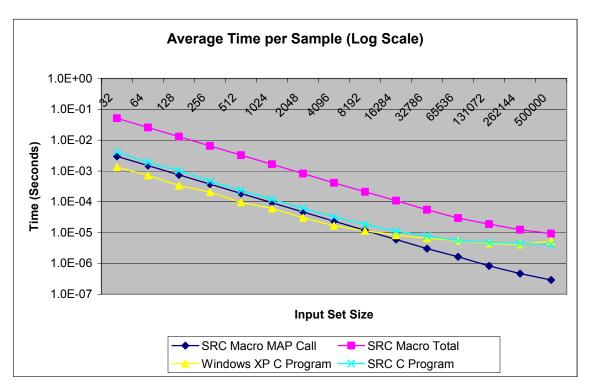

As the input set size is increased, we see the curves begin to converge. Figure 10 shows a comparison of the average time per sample. Figure 11 shows the same data on a semilog scale.

Figure 10. Comparison of Average Time per Sample

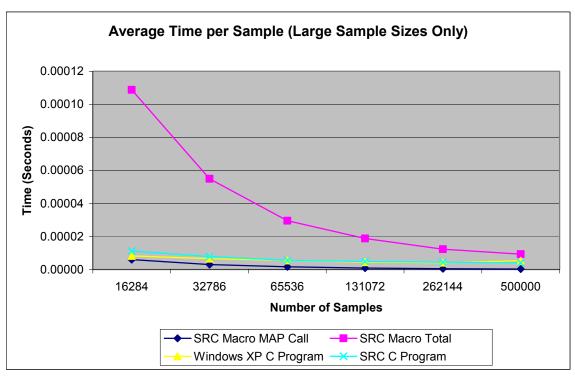

The overhead in the SRC Macro clearly dominates the graphs for smaller sample set sizes. However, for larger sample set sizes, the overhead time is amortized over the total time to be nearly insignificant. Figure 12 shows only the upper sample set size data to magnify the differences. The SRC Macro Total time is approaching the other curves and presumably would eventually meet them if the sample set size could be further increased. However, this is not possible with the current macro design due to the memory design of the SRC-6E hardware.

Figure 11. Semi-Log Comparison of Average Time per Sample

Figure 12. Comparison of Average Time per Sample

## 3. Conclusions

The design of the VHDL macro running on the SRC-6E suffers from excessive overhead which makes it less efficient than the C program which performs the same calculations. Due to the memory size available to the user logic on the SRC-6E, the sample set size cannot be increased large enough to make the VHDL macro run efficiently. The calculation time on the SRC user logic is extremely fast but this is irrelevant if a method cannot be developed to reduce the overhead.

The C program running on Windows is faster at low sample set sizes due to the raw processing power of the faster clocked Pentium 4. However, the slower Linux based SRC system catches up for larger sample set sizes and even appears to surpass the Pentium at the 500,000 sample set size. It appears that the Linux operating system is more efficient than Windows for this particular algorithm on the SRC-6E. However, the much greater cost of the SRC-6E does not make it a cost-effective solution for this algorithm.

This chapter discussed benchmarking the SRC-6E, including collection of data and analysis, and drew conclusions on the results. The next chapter draws conclusions on the SRC-6E, including difficulty of use and appropriateness for the chosen algorithm. Recommendations for future work are also presented.

THIS PAGE INTENTIONALLY LEFT BLANK

#### VI. CONCLUSIONS

#### A. INTRODUCTION

This chapter draws conclusions on the difficulty of use of the SRC-6E, appropriateness of the chosen algorithm for application on the SRC-6E, and gives recommendations for future work.

#### B. DIFFICULTY OF USE

#### 1. Necessary Skills

Programming the SRC-6E to use user-defined macros requires knowledge of high-level programming languages, hardware description languages, hardware component design, and synthesizability. Relatively few people possess all of these skills to use the system effectively without first receiving significant training. However, programming the system using only high-level languages of C or Fortran is possible which widens the potential user base to many more people. Much more research needs to be performed to determine if either method produces more effective solutions.

## 2. Experience Level

The SRC-6E has a relatively steep learning curve. There are a few examples in the documentation and a very small body of work in place using the system. The errors generated by the system during development are not intuitive and cannot be solved without previous experience with solving the same errors. The SRC support staff are very helpful in solving specific code problems but are not forthcoming in the reasons or methods used to resolve them. There are no development tools in place to assist novice users in programming the system. More research is required to see how much experience on the system is required to prevent and or recognize these types of errors quickly.

# 3. Development Time

The development time to implement solutions on this system appears to be high, primarily due to the steep learning curve and lack of development tools. This research represents approximately one year of part-time work by a single, previously inexperienced person, of which about half the time was working with the SRC-6E. It should be noted that many delays were present in the research that would not occur on a second attempt at testing the system, for example, scheduling user training and initial delivery of the system. More research must be performed to further quantify the development time and see how it improves once a group of experienced repeat users is grown. No research has yet been performed with large projects, employing multiple programmers, to see if the total project time can be reduced effectively.

#### C. APPROPRIATENESS OF THIS ALGORITHM

The chosen implementation of the false target radar imaging algorithm appears to be one that would benefit from a reconfigurable computer because it is pipelined and supports parallel processing. However, implementation of the design with four or less range bins has been shown to lack the necessary parallelism required to fully utilize the hardware and make it effective. Without increases in the memory size allocated for the user logic, implementation of four range bins on the SRC-6E is not an effective solution in terms of development time, processing time, or costeffectiveness.

#### D. RECOMMENDATIONS FOR FUTURE WORK

# Develop Implementation of More Range Bins.

The algorithm is not parallel enough with four or less range bins to make implementing it on the SRC-6E architec-

ture an effective solution. Expanding the interface to instantiate and deliver data to more range bins at once may show a more drastic increase in performance versus other computing methods. Rough estimates of FPGA usage show that 16 range bins should fit in the user logic area. However, rebuilding the interface to support this could be a challenge with the limited bandwidth provided by six 64-bit arrays.

# Develop a More User-Friendly Programming Environment.

As previously discussed, the SRC-6E lacks a custom code editing environment with modern features such as real time syntax checking. Automated generation of some of the support files could also be implemented. Project wizards could be created that ask a few questions and then create the skeletons of the support files for the project. Changes to one file that affect another could be automatically corrected or at a minimum generate warnings.

# 3. Testing Other Applications.

The knowledge base of what types of applications do or do not work efficiently on this system is very small. Many more algorithms need to be tested on the system. Programming the same algorithm with both the high level language method and the user macro method would also provide information on which produces better results for different types of algorithms. Cost and timing comparison to modern, readily available computers should continue to be made.

THIS PAGE INTENTIONALLY LEFT BLANK

#### APPENDIX A

This appendix contains the C code written by Professor Douglas Fouts that was used as a standard for output correctness and as a source of timing data. Slight modifications were made to provide for timing result output and increased sample sizes. The version presented was used on both the SRC-6E and the Windows XP platforms for timing analysis with no modifications.

# A. CHIP2\_SIM.C

```

/* Simulate the DIS-512 chip. */

/* Compile Command */

/* cc Chip2 Sim.c -lm */

/* Range bin phase increment data must be in the file phzinc.txt. */

/* Range bin amplitude scaling data must be in the file ampscal.txt. */

/* Pulse phase samples must be in the file phzsamp.txt. */

/* Output results are put into the file IandQout.txt */

/* Global Included Files */

#include <stdio.h>

#include <math.h>

#include <time.h>

/* Global Defines */

#define rangebins 4 /* Number of range bins. */

#define phzsamps 500000 /* Maximum number of phase samples. */

/* Global Data Structures */

bin. */

ampscaldat[rangebins], /* Stores amplitude scaling factors for

each range bin. */

results for each phase sample */

Qpartres[phzsamps + rangebins][rangebins],

/* in each

range bin. */

sintab[32], costab[32],    /* Sin and Cos lookup tables. */

/* Used to count number of samples read in from

file phzsamp.txt. */

```

```

/* Read in phase increment values for each range bin, */

/* and store the results in the array phzincdat.

rdphzinc()

/* Local Variables */

FILE *filepnt;

int rbcnt;

/* Open the input file phzinc.txt. */

if ((filepnt = fopen("phzinc.txt", "r")) == NULL)

fprintf(stderr, "\n\nTERMINAL FAULT: File phzinc.txt not

found.\n\n";

/* For each range bin. */

for (rbcnt = 0; rbcnt < rangebins; rbcnt++)</pre>

increment value. */

} /* end of for loop */

/* Close input file. */

fclose(filepnt);

/* End of function rdphzinc. */

/* Read in amplitude scaling values for each range bin, */

/* and store result in array ampscaldata.

rdampscal()

/* Local Variables */

FILE *filepnt;

int rbcnt, inptampdat, tstampdat;

/* Open the input file ampscal.txt. */

if ((filepnt = fopen("ampscal.txt", "r")) == NULL)

fprintf(stderr, "\n\nTERMINAL FAULT: File ampscal.txt not

found.\n\n");

/* Read in amplitude scaling values for each range bin. */

for (rbcnt = 0; rbcnt < rangebins; rbcnt++)</pre>

fscanf(filepnt, "%x", &inptampdat);

ampscaldat[rbcnt] = 0x00000001 & inptampdat;

```

```

tstampdat = 0x00000001 & (inptampdat >> 1);

if (tstampdat == 1)

ampscaldat[rbcnt] = ampscaldat[rbcnt] + 2;

tstampdat = 0x00000001 & (inptampdat >> 2);

if (tstampdat == 1)

ampscaldat[rbcnt] = ampscaldat[rbcnt] + 3;

tstampdat = 0x00000001 & (inptampdat >> 3);

if (tstampdat == 1)

ampscaldat[rbcnt] = ampscaldat[rbcnt] + 4;

/* Close input file. */

fclose(filepnt);

/* End of function rdampscal. */

/* Initialize the global storage arrays. */

initarrays()

/* Local Variables */

int sampnum, rbnum;

/* Initialize the partial result array. */

for (sampnum = 0; sampnum < phzsamps; sampnum++)</pre>

for (rbnum = 0; rbnum < rangebins; rbnum++)</pre>

Ipartres[sampnum + rbnum][rbnum] = 0;

Qpartres[sampnum + rbnum][rbnum] = 0;

}

/* Initialize the sin table. */

sintab[0] = 0x000000000;

sintab[1] = 0x00000019;

sintab[2] = 0x00000031;

sintab[3] = 0x00000047;

sintab[4] = 0x0000005A;

sintab[5] = 0x0000006A;

sintab[6] = 0x00000075;

sintab[7] = 0x0000007D;

sintab[8] = 0x0000007F;

```

```

sintab[9] = 0x0000007D;

sintab[10] = 0x00000075;

sintab[11] = 0x0000006A;

sintab[12] = 0x0000005A;

sintab[13] = 0x00000047;

sintab[14] = 0x00000031;

sintab[15] = 0x00000019;

sintab[16] = 0x000000000;

sintab[17] = 0xFFFFFFE7;

sintab[18] = 0xFFFFFFCF;

sintab[19] = 0xFFFFFB9;

sintab[20] = 0xFFFFFFA6;

sintab[21] = 0xFFFFFF96;

sintab[22] = 0xFFFFFF8B;

sintab[23] = 0xFFFFFF83;

sintab[24] = 0xFFFFFF81;

sintab[25] = 0xFFFFFF83;

sintab[26] = 0xFFFFFF8B;

sintab[27] = 0xFFFFFF96;

sintab[28] = 0xFFFFFFA6;

sintab[29] = 0xFFFFFFB9;

sintab[30] = 0xFFFFFFCF;

sintab[31] = 0xFFFFFFE7;

/* Initialize the cos table. */

costab[0] = 0x0000007F;

costab[1] = 0x0000007D;

costab[2] = 0x00000075;

costab[3] = 0x0000006A;

costab[4] = 0x0000005A;

costab[5] = 0x00000047;

costab[6] = 0x00000031;

costab[7] = 0x00000019;

costab[8] = 0x00000000;

costab[9] = 0xFFFFFFE7;

costab[10] = 0xFFFFFFCF;

costab[11] = 0xFFFFFFB9;

costab[12] = 0xFFFFFFA6;

```

```

costab[13] = 0xFFFFFF96;

costab[14] = 0xFFFFFF8B;

costab[15] = 0xFFFFFF83;

costab[16] = 0xFFFFFF81;

costab[17] = 0xFFFFFF83;

costab[18] = 0xFFFFFF8B;

costab[19] = 0xFFFFFF96;

costab[20] = 0xFFFFFFA6;

costab[21] = 0xFFFFFFB9;

costab[22] = 0xFFFFFFCF;

costab[23] = 0xFFFFFFE7;

costab[24] = 0x000000000;

costab[25] = 0x00000019;

costab[26] = 0x00000031;

costab[27] = 0x00000047;

costab[28] = 0x0000005A;

costab[29] = 0x0000006A;

costab[30] = 0x00000075;

costab[31] = 0x0000007D;

/* End of function initarrays. */

/* Read in pulse phase samples and calculate partial */

* /

/* results for each range bin and store result in

/* the arrays Ipartres and Qpartres.

* /

rdphzsamp()

/* Local Variables */

FILE *filepnt;

int phzdat, phzaddout, ILUTOut, QLUTOut, IGainOut, QGainOut, rbcnt;

/* Open the input file phzsamp.txt. */

if ((filepnt = fopen("phzsamp.txt", "r")) == NULL)

fprintf(stderr, "\n\nTERMINAL FAULT: File phzsamp.txt not

found.\n\n");

/* Process each phase sample in the file phzsamp.txt. */

numofsamps = 0;

while (fscanf(filepnt, "%x", &phzdat) != EOF)

{

```

```

/* Process the new phase sample in each range bin and store the

result. */

for (rbcnt = 0; rbcnt < rangebins; rbcnt++)</pre>

/* Increment the phase. */

phzaddout = phzdat + phzincdat[rbcnt];

phzaddout = phzaddout & 0x0000001F;

/* Calculate I for each range bin and store the result. */

ILUTOut = costab[phzaddout];

IGainOut = ILUTOut << ampscaldat[rbcnt];</pre>

if (IGainOut >= 0)

IGainOut = IGainOut >> 5;

else

IGainOut = (IGainOut >> 5) | 0xffffE000;

IGainOut = IGainOut & 0x0000FFFF;

Ipartres[numofsamps + rbcnt][rbcnt] = IGainOut;

/* Calculate Q for each range bin and store the result. */

QLUTOut = sintab[phzaddout];

QGainOut = QLUTOut << ampscaldat[rbcnt];</pre>

if (QGainOut >= 0)

QGainOut = QGainOut >> 5;

else

QGainOut = (QGainOut >> 5) | 0xFFFFE000;

OGainOut = OGainOut & 0x0000FFFF;

Qpartres[numofsamps + rbcnt][rbcnt] = QGainOut;

/* Increment the number of phase samples counter. */