**Calhoun: The NPS Institutional Archive**

Theses and Dissertations

Thesis Collection

2009-09

# Development of the phase synchronization circuit for wirelessly distributed digital phased array

Tsai, Yen-Chang

Monterey, California: Naval Postgraduate School

http://hdl.handle.net/10945/4611

Calhoun is a project of the Dudley Knox Library at NPS, furthering the precepts and goals of open government and government transparency. All information contained herein has been approved for release by the NPS Public Affairs Officer.

Dudley Knox Library / Naval Postgraduate School 411 Dyer Road / 1 University Circle Monterey, California USA 93943

## NAVAL POSTGRADUATE SCHOOL

**MONTEREY, CALIFORNIA**

## **THESIS**

## DEVELOPMENT OF THE PHASE SYNCHRONIZATION CIRCUIT FOR WIRELESSLY DISTRIBUTED DIGITAL PHASED ARRAY

by

Tsai, Yen-Chang

September 2009

Thesis Advisor: David C. Jenn

Second Readers: Robert D. Broadston

Jiheon Ryu

Approved for public release; distribution is unlimited

#### REPORT DOCUMENTATION PAGE

Form Approved OMB No. 0704-0188

Public reporting burden for this collection of information is estimated to average 1 hour per response, including the time for reviewing instruction, searching existing data sources, gathering and maintaining the data needed, and completing and reviewing the collection of information. Send comments regarding this burden estimate or any other aspect of this collection of information, including suggestions for reducing this burden, to Washington headquarters Services, Directorate for Information Operations and Reports, 1215 Jefferson Davis Highway, Suite 1204, Arlington, VA 22202-4302, and to the Office of Management and Budget, Paperwork Reduction Project (0704-0188) Washington DC 20503.

| 22202-4302, and to the Office of Management and Budget, Faperwork Reduction Floject (0/04-0188) Washington DC 20303.          |                                      |                                                   |                                              |

|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------|----------------------------------------------|

| 1. AGENCY USE ONLY (Leave blank)                                                                                              | <b>2. REPORT DATE</b> September 2009 | 3. RE                                             | PORT TYPE AND DATES COVERED  Master's Thesis |

| <b>4. TITLE AND SUBTITLE</b> Development of the Phase Synchronization Circuit for Wirelessly Distributed Digital Phased Array |                                      | 5. FUNDING NUMBERS                                |                                              |

| 6. AUTHOR(S) Tsai, Yen-Chang                                                                                                  |                                      |                                                   |                                              |

| 7. PERFORMING ORGANIZATION NAME(S) AND ADDRESS(ES) Naval Postgraduate School Monterey, CA 93943-5000                          |                                      |                                                   | 8. PERFORMING ORGANIZATION<br>REPORT NUMBER  |

| 9. SPONSORING /MONITORING AGENCY NAME(S) AND ADDRESS(ES) N/A                                                                  |                                      | 10. SPONSORING/MONITORING<br>AGENCY REPORT NUMBER |                                              |

11. SUPPLEMENTARY NOTES The views expressed in this thesis are those of the author and do not reflect the official policy or position of the Department of Defense or the U.S. Government.

12a, DISTRIBUTION / AVAILABILITY STATEMENT Approved for public release; distribution is unlimited

12b. DISTRIBUTION CODE

#### 13. ABSTRACT (maximum 200 words)

The Wirelessly Distributed Digital Phased Array (WDDPA) is an ongoing research program at the Naval Postgraduate School (NPS) which has numerous possible applications in radar and communication systems. The WDDPA incorporates many array elements randomly or nonuniformly in the environment or on a platform. Array elements are synchronized and controlled over a wireless channel. Compared to conventional phased array systems, its advantages are adaptability, survivability and flexibility.

Phase synchronization is a critical component of the WDDPA development. The common phase reference is vital to steer the beam and control the radiation pattern for the phased array system. The objective of this paper is to improve the WDDPA synchronization operation. Previous hardware and software architectures were replaced or modified to improve the accuracy and speed of the phase synchronization.

A series of experiments, first for hardwired channels, then for wireless channels, were conducted successfully to verify the synchronization operation for two elements. Several problems with the circuit were diagnosed and then addressed. The overall performance of the improved synchronization circuit for the demonstration array was satisfactory, allowing phases to be synchronized within 20° wirelessly. The architecture for the potential successor of the synchronization circuit is introduced. It is more flexible and robust than the current circuit and thus more desirable for future applications of the WDDPA.

| <b>14. SUBJECT TERMS</b> Radar, Distributed array, Phased Array, Phase Synchronization, Digital Radar, Digital Beamforming (DBF), Wireless Beamforming, Wireless Network Sensor, Aperstructure, Opportunistic Array, LabVIEW, Ballistic Missile Defense (BMD), CG(X), DDG-1000, Network-Centric Warfare (NCW), UAV, Modulator, Demodulator, Filter, Transmit/ Receive (T/R) Module, Leakage Cancellation |                        |                   | 15. NUMBER OF PAGES |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------|---------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                          |                        |                   | 16. PRICE CODE      |

|                                                                                                                                                                                                                                                                                                                                                                                                          |                        |                   |                     |

| 17. SECURITY                                                                                                                                                                                                                                                                                                                                                                                             | 18. SECURITY           | 19. SECURITY      | 20. LIMITATION OF   |

| CLASSIFICATION OF                                                                                                                                                                                                                                                                                                                                                                                        | CLASSIFICATION OF THIS | CLASSIFICATION OF | ABSTRACT            |

| REPORT                                                                                                                                                                                                                                                                                                                                                                                                   | PAGE                   | ABSTRACT          |                     |

| Unclassified                                                                                                                                                                                                                                                                                                                                                                                             | Unclassified           | Unclassified      | UU                  |

NSN 7540-01-280-5500

Standard Form 298 (Rev. 2-89) Prescribed by ANSI Std. 239-18 THIS PAGE INTENTIONALLY LEFT BLANK

#### Approved for public release; distribution is unlimited

## DEVELOPMENT OF THE PHASE SYNCHRONIZATION CIRCUIT FOR WIRELESSLY DISTRIBUTED DIGITAL PHASED ARRAY

Tsai, Yen-Chang Lieutenant, Republic of China Navy B, Chinese Naval Academy, 2001 B.M.S, National Cheng Kung University, 2001

Submitted in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE IN ELECTRONIC WARFARE SYSTEMS ENGINEERING

from the

#### NAVAL POSTGRADUATE SCHOOL September 2009

Author: Tsai, Yen-Chang

Approved by: David C. Jenn

Thesis Advisor

Robert D. Broadston

Second Reader

Jiheon Ryu Second Reader

Dan C. Boger

Chairman, Information Sciences Department

THIS PAGE INTENTIONALLY LEFT BLANK

#### **ABSTRACT**

The Wirelessly Distributed Digital Phased Array (WDDPA) is an ongoing research program at the Naval Postgraduate School (NPS) which has numerous possible applications in radar and communication systems. The WDDPA incorporates many array elements randomly or nonuniformly in the environment or on a platform. Array elements are synchronized and controlled over a wireless channel. Compared to conventional phased array systems, its advantages are adaptability, survivability and flexibility.

Phase synchronization is a critical component of the WDDPA development. The common phase reference is vital to steer the beam and control the radiation pattern for the phased array system. The objective of this paper is to improve the WDDPA synchronization operation. Previous hardware and software architectures were replaced or modified to improve the accuracy and speed of the phase synchronization.

A series of experiments, first for hardwired channels, then for wireless channels, were conducted successfully to verify the synchronization operation for two elements. Several problems with the circuit were diagnosed and then addressed. The overall performance of the improved synchronization circuit for the demonstration array was satisfactory, allowing phases to be synchronized within 20° wirelessly. The architecture for the potential successor of the synchronization circuit is introduced. It is more flexible and robust than the current circuit and thus more desirable for future applications of the WDDPA.

THIS PAGE INTENTIONALLY LEFT BLANK

## TABLE OF CONTENTS

| I.   | INT       | RODUCTION                                               | 1  |

|------|-----------|---------------------------------------------------------|----|

|      | A.        | BACKGROUND                                              | 1  |

|      |           | 1. Forward-deployed Ballistic Missile Defense and CG(X) | 4  |

|      |           | 2. Network-centric Warfare and Unmanned Vehicles        | 7  |

|      | В.        | WDDPA ARCHITECTURE AND SYNCHRONIZATION                  |    |

|      | C.        | PROBLEM STATEMENT AND THESIS OBJECTIVE                  | 11 |

|      | D.        | SCOPE AND ORGANIZATION                                  | 11 |

| II.  | WD        | DPA ARCHITECTURE                                        |    |

|      | <b>A.</b> | DISTRIBUTED ARRAY CONCEPT AND OPERATION                 |    |

|      |           | 1. Element Factor                                       |    |

|      |           | 2. Array Factor                                         |    |

|      |           | 3. Total Array Pattern                                  |    |

|      |           | 4. Directivity                                          |    |

|      |           | 5. Radar Range Equation                                 |    |

|      |           | 6. Signal-to-noise Ratio                                | 18 |

|      | В.        | WIRELESS BEAMFORMING CONCEPT                            |    |

|      |           | 1. Digital Beamforming                                  | 19 |

|      |           | 2. Wireless Network Requirement                         | 20 |

|      | <b>C.</b> | WDDPA DEMONSTRATION OVERVIEW                            | 22 |

|      |           | 1. Central Controller                                   | 24 |

|      |           | 2. T/R Module                                           | 25 |

|      |           | 3. LO System                                            | 26 |

|      |           | 4. Wireless Communication Network                       | 27 |

|      | D.        | WDDPA SYNCHRONIZATION PROCESS                           |    |

|      |           | 1. Synchronization Operation and Concept                | 28 |

|      |           | 2. Previous NI LabVIEW FPGA                             | 30 |

|      |           | 3. New Module Hardware                                  |    |

|      |           | a. Implementation of Single PXI Controller              | 33 |

|      |           | b. Agilent Power Sensor U2001A                          |    |

|      |           | c. Vaunix Technology LSG-402 Signal Generator           | 38 |

|      |           | d. Baseband Differential Instrumentation Amplifier      | 38 |

|      |           | e. LabVIEW Software Program Modification                | 39 |

|      | <b>E.</b> | NEW DEMONSTRATION SETUP                                 |    |

|      | F.        | SUMMARY                                                 | 41 |

| III. | WIF       | RED SYNCHRONIZATION TESTING                             |    |

|      | <b>A.</b> | BACKGROUND                                              |    |

|      | В.        | SINGLE-ELEMENT TESTING                                  |    |

|      |           | 1. Module Components                                    |    |

|      |           | 2. LO Signal Power Measurements                         |    |

|      |           | 3. Diagnostic Test                                      |    |

|      | <b>C</b>  | ALTERNATIVES INVESTIGATION                              | 50 |

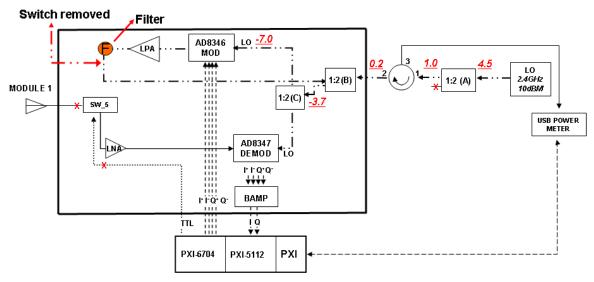

|      |           | 1. Removal of LPA                                      | 50           |

|------|-----------|--------------------------------------------------------|--------------|

|      |           | 2. Implementation of Isolator                          | 51           |

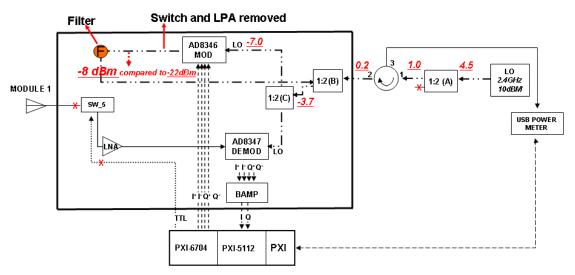

|      |           | 3. Removal of Switch                                   |              |

|      |           | 4. Implementation of Filter                            | 53           |

|      |           | a. Investigation of MFC-13944 Filter                   | 53           |

|      |           | b. Module Testing with MFC-13944 Filter                | 56           |

|      |           | 5. Summary                                             |              |

|      | D.        | VALIDATION OF NEW SYNCHRONIZATION CIRCUIT              | 60           |

|      |           | 1. Testing with Coaxial Cable                          | 60           |

|      |           | 2. Testing with 3 dB Quadrature Coupler                | 63           |

|      |           | 3. Testing with Phase Shifter                          |              |

|      |           | 4. Summary                                             |              |

|      | <b>E.</b> | TWO-ELEMENT SYNCHRONIZATION TESTING                    |              |

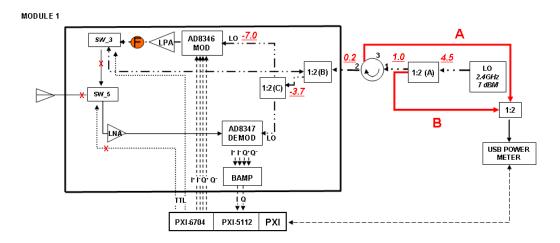

|      |           | 1. LO Power Leakage                                    |              |

|      |           | 2. Analysis of LO Power Balance                        |              |

|      |           | 3. Validation of LO Power Balance                      |              |

|      |           | 4. Two-element Testing                                 |              |

|      | F.        | SUMMARY                                                | . <b>7</b> 7 |

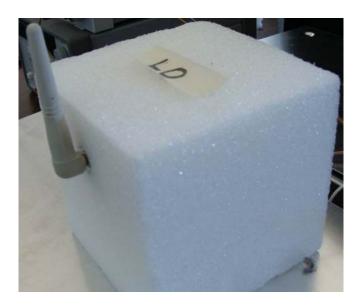

| IV.  | DEV       | ELOPMENT OF WIRELESS SYNCHRONIZATION                   | 79           |

|      | <b>A.</b> | BACKGROUND                                             |              |

|      | В.        | WIRELESS SYNCHRONIZATION DEMONSTRATION                 |              |

|      |           | 1. Investigation of Free Space Propagation Loss        |              |

|      |           | 2. Demonstration of Wireless Synchronization Operation |              |

|      | <b>C.</b> | ANALYSIS                                               |              |

|      |           | 1. LO Power Leakage                                    | 86           |

|      |           | 2. Spurious Signals                                    |              |

|      | D.        | IMPROVEMENT IN SYNCHRONIZATION OPERATION               |              |

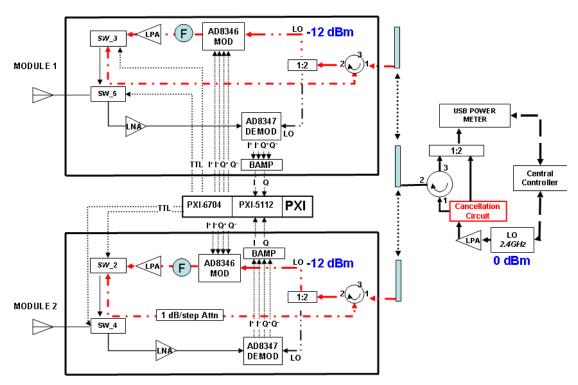

|      |           | 1. Leakage Power Cancellation Circuit                  |              |

|      |           | 2. Implementation of the LPA                           |              |

|      | E.        | THE MODIFIED TWO-ELEMENT WIRELESS TESTING              | 93           |

|      | F.        | SUMMARY                                                | 96           |

| V.   | CON       | CLUSION AND RECOMMENDATIONS                            | 99           |

| ٧.   | A.        | CONCLUSIONS                                            | •••••        |

|      | В.        | RECOMMENDATIONS FOR FUTURE WORK                        |              |

|      | D.        | 1. New Architecture of Phase Synchronization           |              |

|      |           | 2. Developing LabVIEW Program                          |              |

|      |           | • 0                                                    |              |

|      | ENDIX     |                                                        |              |

| LIST | OF RI     | EFERENCES                                              | 105          |

| INIT | ית וגוי   | CTDIRITION LIST                                        | 100          |

## LIST OF FIGURES

| Figure 1.  | CG-54 with AN/SPY-1 radar highlighted (From [4])                          | 1  |

|------------|---------------------------------------------------------------------------|----|

| Figure 2.  | (a) Analog BFN and (b) WDDPA(From [5])                                    |    |

| Figure 3.  | BMDS structure (From [7])                                                 |    |

| Figure 4.  | Artist's concept of DDG–1000 (From [13])                                  |    |

| Figure 5.  | CAD model of DDG-1000 with 1200 distributed arrays (From [14])            |    |

| Figure 6.  | Predator and Global Hawk (From [18])                                      |    |

| Figure 7.  | Configuration of wireless sensor network with mini UAVs highlighted       |    |

| _          | (From [20])                                                               |    |

| Figure 8.  | WDDPA system architecture implemented on a ship's hull with a single      |    |

|            | element highlighted (From [5])                                            | 9  |

| Figure 9.  | Spherical coordinate system referenced to DDG-1000 CAD model (From        |    |

|            | [3])                                                                      | 15 |

| Figure 10. | Distributed array operation configuration (From [3])                      | 16 |

| Figure 11. | Generic DBF architecture (From [3])                                       | 19 |

| Figure 12. | Configuration of WDDPA elements embedded in DDG-1000's hull (After        |    |

|            | [29])                                                                     |    |

| Figure 13. | WDDPA demonstration array configuration (From [21])                       | 24 |

| Figure 14. | Simplified configuration of T/R module (From [23])                        | 25 |

| Figure 15. | Simplified "brute force" schematic phase synchronization with the switch  |    |

|            | highlighted (From [23]).                                                  | 29 |

| Figure 16. | Illustration of the WDDPA phase comparison algorithm with the             |    |

|            | minimum highlighted                                                       | 30 |

| Figure 17. | Original synchronization diagram for two modules with LabVIEW FPGA        |    |

|            | system highlighted (From [32])                                            | 31 |

| Figure 18. | The detailed element module diagram of previously implemented             |    |

|            | LabVIEW FPGA system (From [21])                                           |    |

| Figure 19. | Schematic model of the LabVIEW software interface (From [31])             |    |

| Figure 20. | New schematic model of the LabVIEW software interface (After [31])        |    |

| Figure 21. | NI PXIe–1062Q 8–slot PXI Express Chassis (From [35])                      |    |

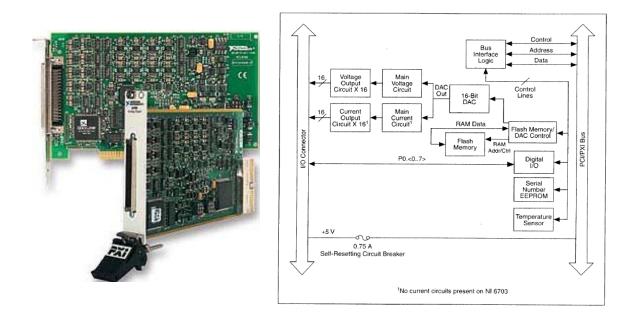

| Figure 22. | NI PXI-6704 analog/digital output module (From [36])                      |    |

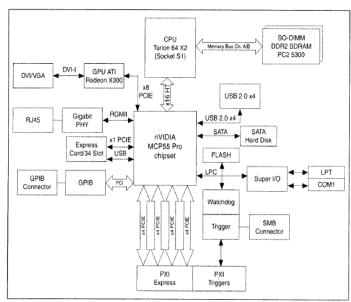

| Figure 23. | NI PXIe–8130 embedded controller (From [38])                              |    |

| Figure 24. | U2001A USB power sensor (From [39])                                       |    |

| Figure 25. | Lab Brick LSG–402 (From [40])                                             | 38 |

| Figure 26. | The differential amplifier board marked as DD1 placed above an AD 8347    |    |

|            | demodulator                                                               | 39 |

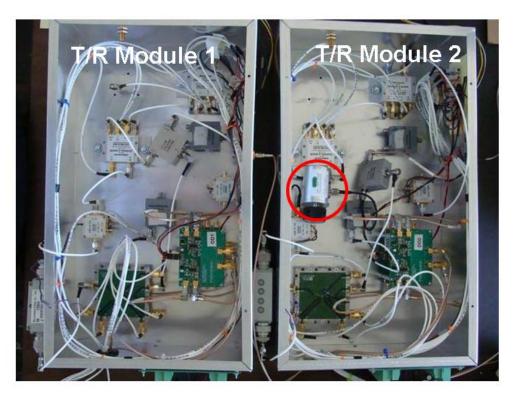

| Figure 27. | The final configuration of two T/R modules with the single PXI controller |    |

|            | highlighted                                                               |    |

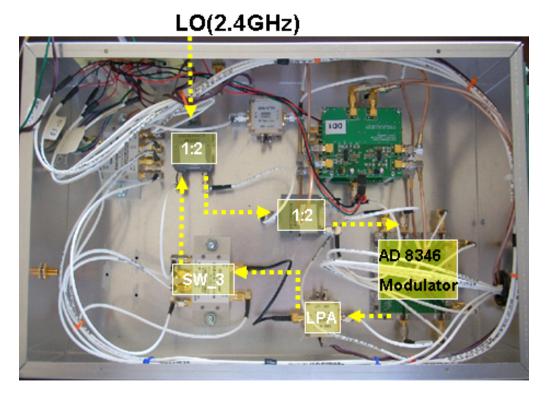

| Figure 28. | The metal box accommodating original hardware components                  | 44 |

| Figure 29. | Highlighted LO signal passing through the synchronization circuit in a    |    |

|            |                                                                           | 46 |

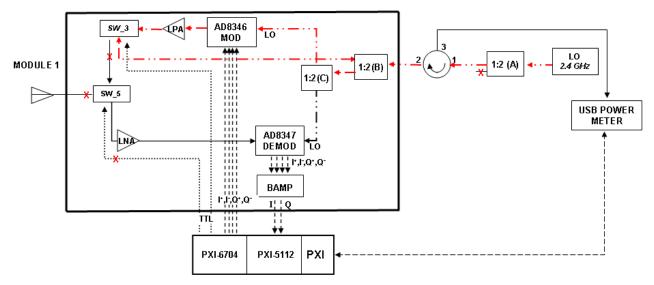

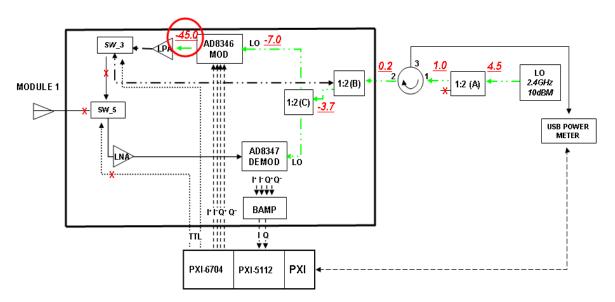

| Figure 30. | The illustration diagram of single T/R module with LO signal highlighted  | 47 |

| Figure 31. | Measurements of LO signal power level in T/R module 1 with the LO               | 40  |

|------------|---------------------------------------------------------------------------------|-----|

| T' 00      | output power highlighted (power is in dBm)                                      | .48 |

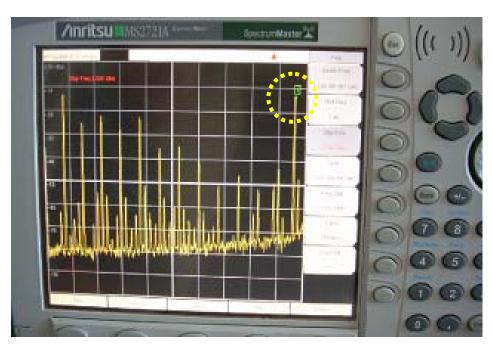

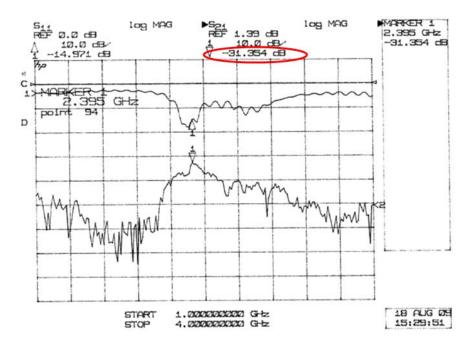

| Figure 32. | Numerous spurs occurring in the AD 8346 modulator board with 2.4 GHz            | 40  |

| Eigung 22  | LO signal highlighted                                                           | .49 |

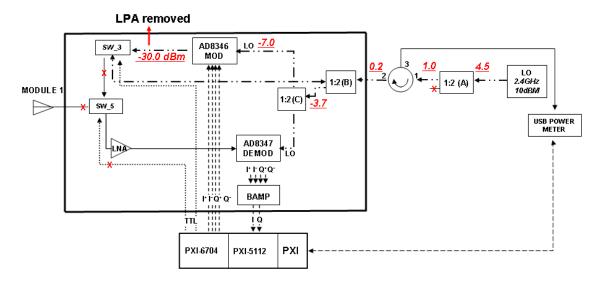

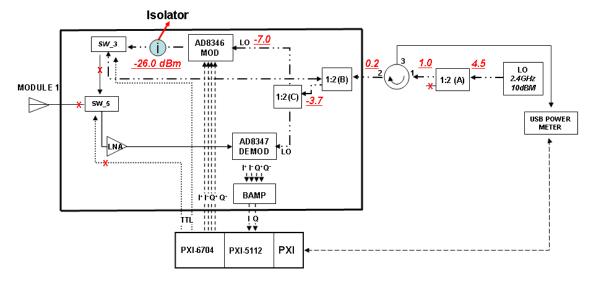

| Figure 33. | Measurement of LO signal power level in T/R module 1 without LPA (power in dBm) | 51  |

| Figure 34. | An isolator is inserted at the location of the LPA                              |     |

| Figure 34. | Measurement of LO signal power level in T/R module 1 with isolator              | .31 |

| riguic 33. | implemented (power in dBm)                                                      | 52  |

| Figure 36. | Measurement of LO signal power level in T/R module 1 with the switch            |     |

| rigure 30. | and LPA removed (power in dBm)                                                  |     |

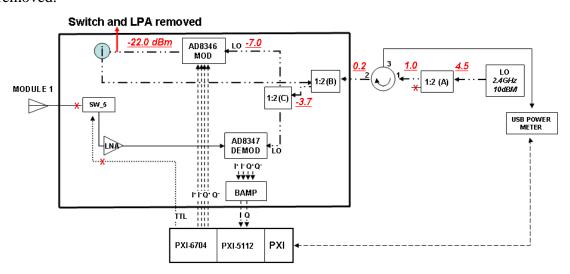

| Figure 37. | Model 13944 full band bandpass filter (From [44])                               |     |

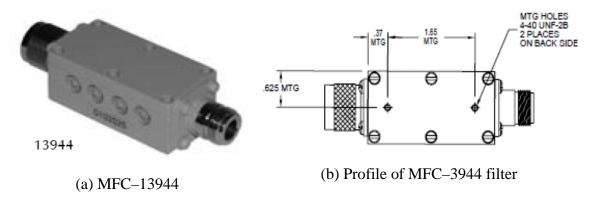

| Figure 38. | Filter 1 performance with the 3 dB bandwidth and rejection highlighted          |     |

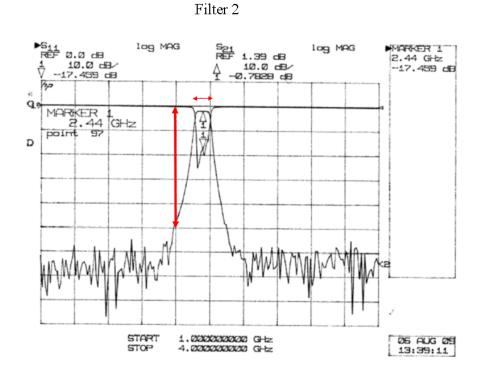

| Figure 39. | Filter 2 performance with the 3 dB bandwidth and rejection highlighted          |     |

| Figure 40. | Measurement of LO signal power level in T/R module 1 with MFC–13944             | .55 |

| rigure 40. | implemented                                                                     | 56  |

| Figure 41. | Measurement of LO signal power level in T/R module 1 with MFC–13944             |     |

| 118010 111 | and LPA implemented                                                             | 57  |

| Figure 42. | The returned LO signal A and the reference signal B highlighted (power in       |     |

| 118010 .2. | dBm)                                                                            | .58 |

| Figure 43. | The result of the synchronization process of the filter-implemented T/R         |     |

| 8          | module 1 with the minimum power level highlighted                               | .59 |

| Figure 44. | Application of a regular coaxial cable in the synchronization testing           |     |

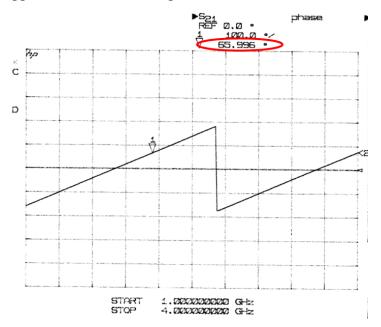

| Figure 45. | The phase of the coaxial cable                                                  |     |

| Figure 46. | The phase reference without the coaxial cable                                   |     |

| Figure 47. | The shifted phase with the implementation of the coaxial cable                  |     |

| Figure 48. | Anaren 3 dB quadrature coupler with the phase of the two ports                  |     |

| C          | highlighted                                                                     |     |

| Figure 49. | The phase difference between two ports of the 3 dB quadrature coupler           |     |

| Figure 50. | Application of a 3 dB quadrature coupler in the synchronization testing         |     |

| C          | with 0° port connected                                                          | .64 |

| Figure 51. | The shifted phase of the 3 dB coupler implemented circuit with the nulls        |     |

| 8          | highlighted                                                                     | .65 |

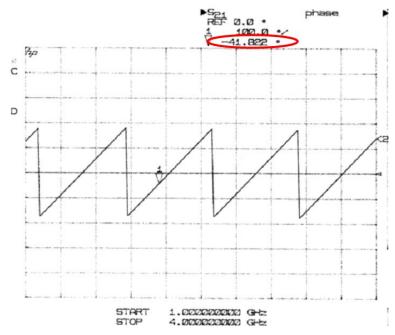

| Figure 52. | Two mechanical phase shifters in pairs (From [22])                              |     |

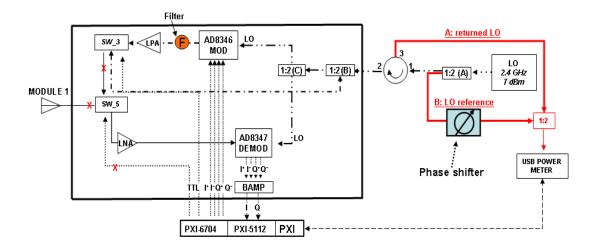

| Figure 53. | Application of the phase shifter in the synchronization testing                 |     |

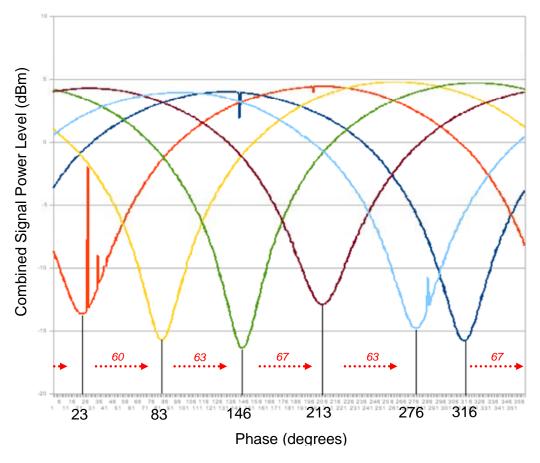

| Figure 54. | Phase shifted by implementing the mechanical phase shifter                      |     |

| Figure 55. | Illustration of possible LO power leakage occurred in the setup of the T/R      |     |

| 118010 001 | module                                                                          | .70 |

| Figure 56. | A typical distortion of the shape of the combined LO power level                |     |

| Figure 57. | The comparison of the circuit before and after implementing 8 dB                |     |

| 8          | attenuation                                                                     | .72 |

| Figure 58. | Phase shift after implementing 3 dB quadrature coupler                          |     |

| Figure 59. | Phase shift after six complete turns of the phase shifter                       |     |

| Figure 60. | Configuration of T/R module with the 1 dB/step variable attenuator              |     |

| J          | highlighted                                                                     | .75 |

| Figure 61.  | The 1 dB/step variable attenuator implemented in T/R module 2                     | .75  |

|-------------|-----------------------------------------------------------------------------------|------|

| Figure 62.  | Configuration of two-element testing setup                                        | .76  |

| Figure 63.  | Phase shifted by operating beamforming control of the master element              | .77  |

| Figure 64.  | The stubby antenna implemented in the wireless synchronization testing            | .80  |

| Figure 65.  | The system loss of two stubby antennas placed 50 cm apart                         | .80  |

| Figure 66.  | Configuration of attenuation implemented in the route of the wired LO             | 01   |

| Eigung 67   | distribution                                                                      | .01  |

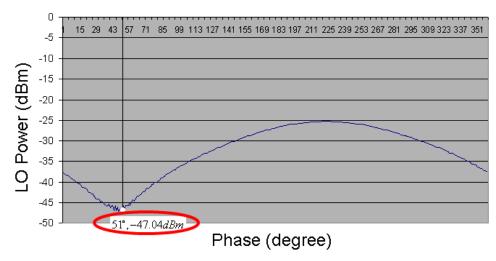

| Figure 67.  | The curve of the 30 dB attenuator implemented in the circuit with the null        | 02   |

| Eigung 60   | highlighted                                                                       |      |

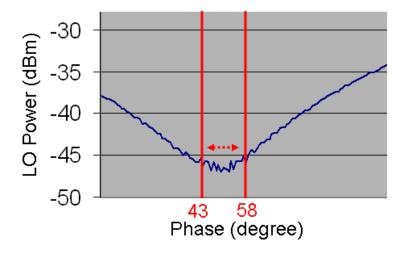

| Figure 68.  | The null region of the 30 dB attenuator implemented                               | .82  |

| Figure 69.  | The curve of the 40 dB attenuator implemented with the obscure region highlighted | .83  |

| Figure 70.  | The estimation of the null with 10 points moving average line highlighted         | .83  |

| Figure 71.  | The simplified WDDPA diagram of the wireless synchronization                      |      |

| υ           | operation                                                                         | .84  |

| Figure 72.  | The power curves of the phase of the master element set at 0, 90, 180 and         |      |

| 8           | 270 degrees                                                                       | .85  |

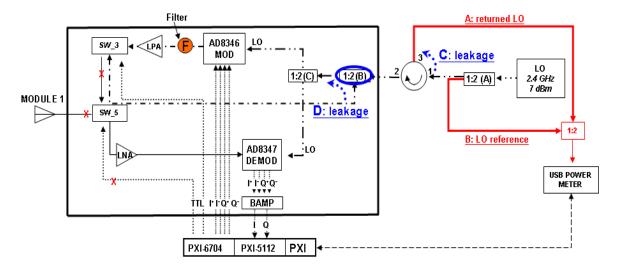

| Figure 73.  | Illustration of LO power leakage occurring in the wireless synchronization        |      |

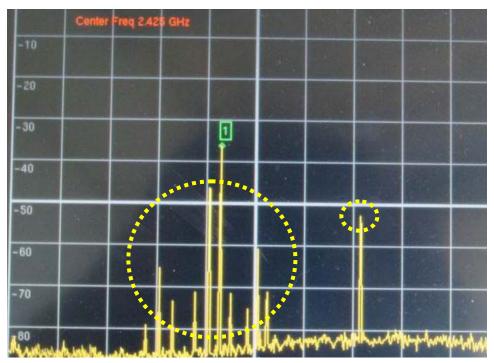

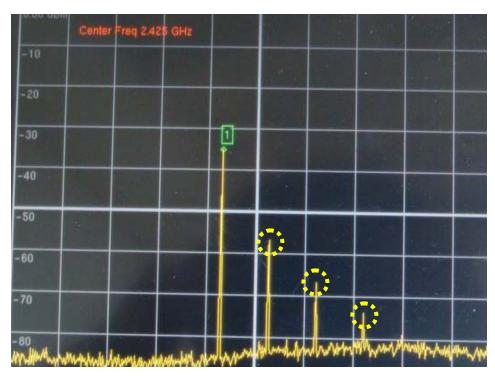

| 8           | setup                                                                             | .86  |

| Figure 74.  | The highlighted spurs                                                             |      |

| Figure 75.  | The different type of spurs                                                       |      |

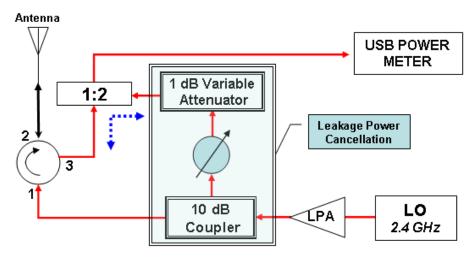

| Figure 76.  | Diagram of the leakage power cancellation circuit                                 |      |

| Figure 77.  | The appearance of the implemented leakage power cancellation circuit              |      |

| Figure 78.  | Two main factors affecting the leakage signal: (a) antenna mismatch and           |      |

| υ           | (b) reflection from outside environment                                           | .91  |

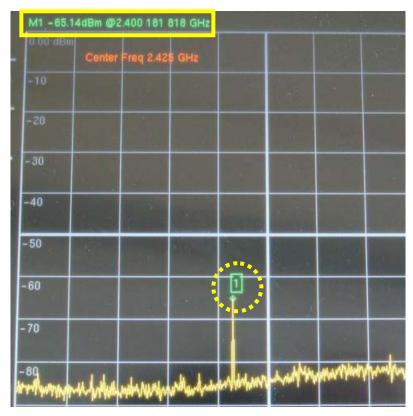

| Figure 79.  | The reduced leakage signals with power level of -65 dBm highlighted               |      |

| Figure 80.  | The improved two-element WDDPA demonstration array                                |      |

| Figure 81.  | The curves of the phase of the T/R module 2 fixed at 0, 90 and 270                | ., - |

| 8           | degrees                                                                           | .94  |

| Figure 82.  | The curves of the phase of the T/R module 2 fixed at 0, 90, 135 and 330           | .,   |

| 8           | degrees                                                                           | .95  |

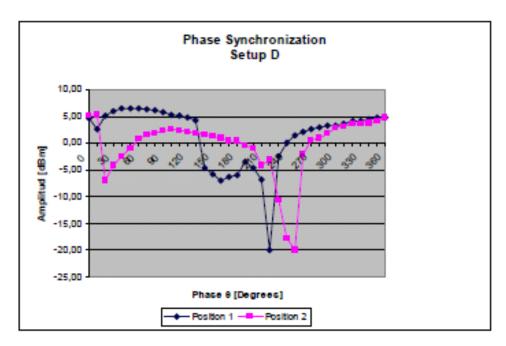

| Figure 83.  | The distorted power curves of the setup D in [21] (From [21])                     |      |

| Figure 84.  | The distorted curves of the phase synchronization testing in [22] (From           |      |

| -0          | [22])                                                                             | .97  |

| Figure 85.  | The new architecture of the WDDPA phase synchronization with the                  | ,    |

| 1 18010 00. | individual LO source highlighted (From [32])                                      | 100  |

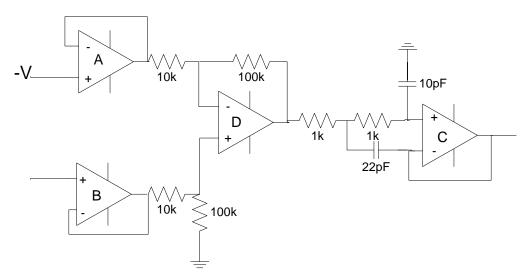

| Figure 86.  | The functional schematic of the BAMP.                                             |      |

| -0          |                                                                                   |      |

THIS PAGE INTENTIONALLY LEFT BLANK

## LIST OF TABLES

| Table 1. | A summary of the wireless network requirement for WDDPA (After [15])  | .21 |

|----------|-----------------------------------------------------------------------|-----|

| Table 2. | NI PXI-5112 Specifications (After [37])                               | .36 |

| Table 3. | Components deployed in T/R module (After [22])                        | .45 |

| Table 4. | AD 8346 specifications (From [41])                                    | 47  |

| Table 5. | MFC-13944 filter specification (From [45])                            | .54 |

| Table 6. | Modulator RF output power comparison of two setups (with and without  |     |

|          | LPA present)                                                          | .57 |

| Table 7. | The summarized phase shifting error by applying the phase shifter (in |     |

|          | degrees)                                                              | .67 |

| Table 8. | The summarized test results (in degrees)                              | .95 |

|          |                                                                       |     |

THIS PAGE INTENTIONALLY LEFT BLANK

#### LIST OF ACRONYMS AND ABBREVIATIONS

ADC analog-to-digital convertor

BAMP baseband differential instrumentation amplifier

BMD ballistic missile defense

BFN beamforming network

CG(X) capital multi-mission surface cruiser

COTS commercial-off-the-shelf

cRIO compact reconfigurable input/output

DAC digital-to-analog convertor

DBF digital beamforming

EWR early warning radar

FOV field of view

FPGA floating point gate array

ICBM intercontinental ballistic missile

IF intermediate frequency

LNA low noise amplifier

LO local oscillator

LOS line-of-sight

LPA low power amplifier

NCW network-centric warfare

NI National Instruments

NPS Naval Postgraduate School

PA power amplifier

PCI peripheral component interconnect

RRE radar range equation

RX receive

SNR signal-to-noise ratio

TTL transistor-transistor logic

TX transmit

UAV unmanned aerial vehicle

UV unmanned vehicle

WDDPA wirelessly distributed digital phased array

WiMAX Worldwide Interoperability for Microwave Access

WLAN wireless local area network

#### **ACKNOWLEDGMENTS**

I would like to express my great gratitude to the Republic of China (Taiwan) Navy for providing me with this terrific opportunity to study at the Naval Postgraduate School for 30 months. This excellent educational institution has not only given me knowledge, but has opened a window for me to see a different world. Being with family in the gorgeous Monterey Bay area is especially wonderful after a five-year sea tour in the Taiwan Strait.

To Professor David Jenn: I would like to thank you for your clear instruction and great patience. During this research process, you always guided me in the right direction, as the lighthouse guides the sailor. Whenever I needed help, you were always there. Thank you, sir.

Many thanks to Mr. Robert Broadston. As the Microwave Laboratory Director, you always do your best to help the students. Without your invaluable support, many technical problems could not have been solved. Thank you, Bob.

Special thanks to Mr. Jiheon Ryu, an outstanding experienced microwave engineer from Korea. With your company in the lab, working on microwave equipment became much more interesting to me. Thanks, Jiheon.

I have to thank all my family in Taiwan. During these months, you always selflessly supported me with all your love, encouragement, even when Typhoon Morokot was striking Taiwan. Thank you all for everything.

I cannot end without thanking my dear wife and best friend, Yichun Kuo (Laney). With your love and support, we have been able to enjoy a great family life in America. With your cleverness and independence, Yangyang and Lele have been growing up happily and healthily during our time here. Thank you, darling.

THIS PAGE INTENTIONALLY LEFT BLANK

#### I. INTRODUCTION

#### A. BACKGROUND

The initial application of phased array antennas in military sensor systems can be traced back to the late 1930s [1]. Since the 1960s, electronically steered phased arrays, such as the well-known U.S. Navy AN/SPY-1 phased array radar shown in Figure 1, have been employed in some of the more demanding military combat systems [2]. Up to now, the phased array has been considered the mainstream antenna architecture of high performance sensor or communication systems, especially for radar [3]. It is applied widely in systems at sea, on land, in the air and even in outer space.

A phased array has numerous advantages over traditional antennas. The most prominent point in radar applications is that beam-steering is controlled electronically by applying phase shifters and switches instead of positioning the antenna mechanically. The prompt and precise beam switching for phased array radars yields versatile and superior capabilities, e.g., the ability to perform search and multiple target tracking simultaneously. This provides radar the flexibility and adaptability to conduct various functions for different missions and battle environments.

Figure 1. CG–54 with AN/SPY–1 radar highlighted (From [4])

Along with those advantages, the phased array has inherent disadvantages and limitations, such as cumbersome physical size, heavy weight and complicated beamforming network (BFN) architecture. A complicated hardwired beamforming system means high cost, high volume and weight, and low survivability. The large physical size usually results in low stealth, low flexibility and high maintenance requirements.

By riding on the superior advances of commercial wireless communication technology and computer processing capabilities of the past decade, it is now possible to minimize many of the disadvantages of phased array sensors. Additionally, the improvement becomes necessary and vital for success in the modern battlefield. The wirelessly distributed digital phased array (WDDPA) will be a potential system designed to integrate modern technologies to meet the needs of next-generation sensor or communication systems.

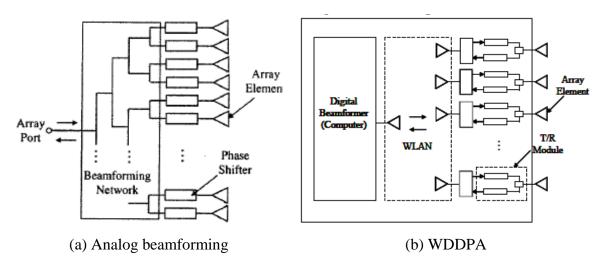

Figure 2 shows the simplified configurations of the BFN of a conventional phased array system and a WDDPA. Conventional phased array systems are composed of a great number of array elements, which might be dipoles or slots, and the individual element is usually controlled by its own phase shifter. The antenna port is connected to the individual array element by a network of transmission lines and power dividers, i.e., the BFN. On transmit (TX), the encoded baseband message or radar waveform is upconverted to the operating frequency then transmitted via the antenna after amplification. On receive (RX), the signal is received via the antenna, amplified, down-converted, and then the encoded message or radar waveform is recovered [5].

Figure 2. (a) Analog BFN and (b) WDDPA(From [5])

For the WDDPA, each element has an individual T/R module that is a combined transmitter and receiver. Every T/R module is controlled by the digital beamformer via a wireless channel. As Figure 2 (b) shows, the need for the hardwired microwave circuitry of the analog BFN is eliminated in the WDDPA, improving the survivability of the overall system compared to a hardwired BFN. The other critical advantage that comes with the elimination of circuitry is that the system is capable of operating over a wider frequency band, increasing its versatility.

Another prominent feature of the WDDPA is that, because of the wireless architecture, the system array elements are able to be distributed randomly or nonuniformly in the environment or on platforms. This leads to a low-profile system with ultimate flexibility that can be integrated into the platform. WDDPA makes the whole system much less detectable to enemy sensors and its distributed nature makes it almost impossible to give WDDPA a single "deadly hit."

The following two examples clearly illustrate WDDPA applications in the field. The first is the ship-based distributed array radar for ballistic missile defense and the second is distributed beam-forming by a swarm of unmanned vehicles.

#### 1. Forward-deployed Ballistic Missile Defense and CG(X)

On April 5, 2009, North Korea launched a three-stage rocket carrying a claimed experimental communications satellite which flew over Japan and fell into the Pacific Ocean after traveling 3,230 kilometers [6]. The launch was believed to be a part of the testing of Taepodong–2 intercontinental ballistic missiles (ICBMs). It not only caused tension in Pacific Rim nations but also drew renewed worldwide attention to recent U.S. Ballistic Missile Defense System (BMDS) developments. The sea-based BMDS, also known as forward-deployed BMDS, is the key component of the U.S. integrated BMD, as shown in Figure 3. This is because it is extremely difficult to counter sea-based BMDS due to surface combatants' mobility at sea. The advance of sea-based BMDS can certainly add strength to the overall BMDS.

Figure 3. BMDS structure (From [7])

The sea-based BMDS now employs modified combat systems on several U.S. Navy Aegis cruisers and destroyers in order to provide needed but limited BMD capability in their remaining years of service. The proposed FY2010 defense budget requests a total of \$1,859.5 million for the modification, which is approximately

\$260 million for each implemented surface combatant [8]. Although generous budgets are spent, the modification *is not to* intercept ICBMs or ballistic missiles inside the atmosphere, during either their initial boost phase of flight or their final (terminal) phase of flight [9].

The U.S.'s future capital multi-mission surface cruiser, the CG(X), is designed to be provided with the initial operational capability to be a highly capable BMD platform. It is set for service in 2019 [10]. A descendant of the DDG–1000 originally expected to be commissioned in 2014 (Figure 4), CG(X) was supposed to adopt a similar hull design and newly developed concepts of combat systems. Recent discussions [10]–[12] showed that in order to carry out additional BMD missions other than DDG–1000, it will be necessary to accommodate the powerful advanced S-band radar in the CG(X). However, under the conventional phased array architecture and corresponding power requirements, this kind of BMD radar requires a much larger ship size: about 22,000 to 24,000 tons displacement compared to the 14,500 tons of a DDG–1000 [10]–[11].

Figure 4. Artist's concept of DDG– 1000 (From [13])

The price of the added BMD capability is an estimated \$4 billion for each CG(X), much more than the \$3 billion procurement cost of the controversial DDG-1000 [10]–

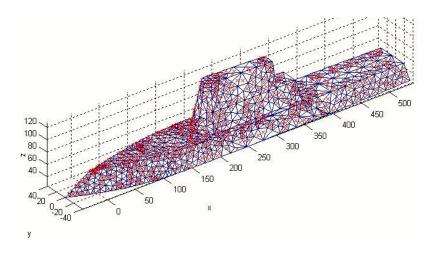

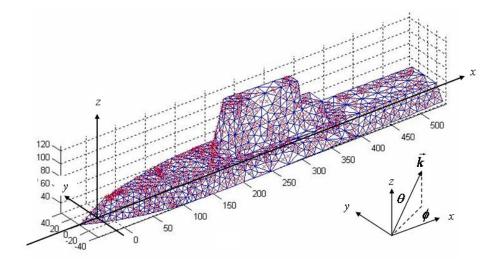

[11]. References [14] and [15] have investigated whether it is possible to equip the DDG–1000 with adequate early warning radar (EWR) operating at 300 MHz employing a WDDPA structure. EWR is a secondary radar operating in conjunction with the primary S-band radar.

The most prominent feature of this kind of EWR is a digital phased array radar with thousands of integrated ship-wide opportunistic array elements as shown in Figure 5. Elements are placed at available open areas over the entire ship's structure. Low-profile patch antennas can be integrated into the ship's structure, meeting the requirement of enhanced stealth. The cost associated with bulky ship size can also be reduced dramatically without sacrificing required BMD capability. The opportunistic array in the context of EWR can detect and track targets over 1000 km due to its high angular resolution capability, which is provided by a very narrow beamwidth (on the order of 0.005 radians) [14].

Implementing such array architecture on the CG(X) has the potential to fulfill the U.S. Navy's BMD mission at a relatively lower cost by performing exo-atmospheric surveillance, tracking and preliminary discrimination. This relieves the primary radar of the burden of BMD.

Figure 5. CAD model of DDG–1000 with 1200 distributed arrays (From [14])

#### 2. Network-centric Warfare and Unmanned Vehicles

Network-centric warfare (NCW) is recognized as the cornerstone of military transformation occurring in the world today [16]. It has changed the military not only in operation's concepts, but also in weapon systems. Unmanned vehicles (UVs) implemented with WDDPA could be a great means to advance the spirit of NCW.

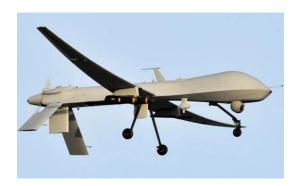

UVs, especially the unmanned aerial vehicles (UAVs), are widely used in the battlefield for surveillance and reconnaissance. During Operation Iraqi Freedom, 16 Predator and 1 Global Hawk (shown in Figure 6) were deployed in operation for thousands of hours [17]. They were all remotely controllable via satellite links from command centers in the continental United States, decreasing personnel casualties dramatically.

Figure 6. Predator and Global Hawk (From [18])

Most current UAVs, however, do not have high-resolution recognition or detection capabilities in the battlefield because they are large and must fly at relatively high altitudes, which degrades video resolution. The cost issue also prohibits widespread deployment [19].

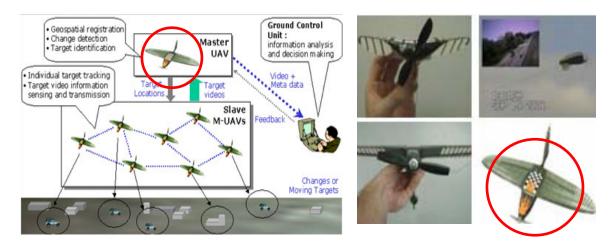

With the combined concept of WDDPA and NCW, a distribution of numerous mini UAVs that are equipped with individual T/R elements could be an improvement over those limitations. Among the deployed mini UAVs, one is assigned to be the master UAV and the others are the slave UAVs. Via the wireless network, the master UAV is in charge of transmitting the acquired information to the control unit and synchronizing

slave UAVs in order to perform coherent operation. A robust and cost-effective sensor network like this is able to carry out the surveillance or intelligence mission in a hot zone (Figure 7).

One advantage is that the cost will be much lower than larger systems, such as the Global Hawk or Predator. For a MQ-1B Predator, the cost is approximately \$10 million, whereas a mini UAV cost can be less than \$1,000 [19]-[20]. Secondly, with WDDPA architecture, UAVs work with coherent operation and are able to fly at much lower altitudes, which can lead to higher resolution recognition capabilities. Lastly, countermeasures for this sensor network will be very difficult in practice, because of their small size. The WDDPA network is relatively insensitive to a small number of UAV losses, increasing its survivability.

Figure 7. Configuration of wireless sensor network with mini UAVs highlighted (From [20])

#### B. WDDPA ARCHITECTURE AND SYNCHRONIZATION

The development and evolution of different aspects of WDDPA have been contributed by several Naval Postgraduate School (NPS) researchers. Several technological challenges still need to be solved in order to bring WDDPA into practice.

Phase and time synchronization are recognized as vital issues of WDDPA development. Efficient operation relies on the capability to synchronize numerous elements wirelessly in order to perform coherent processing.

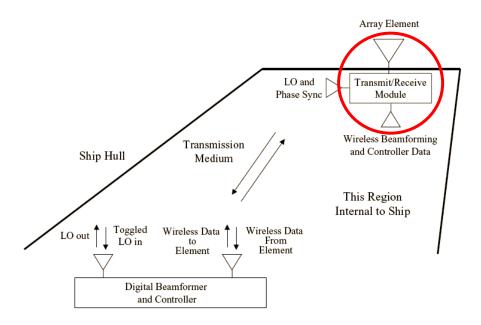

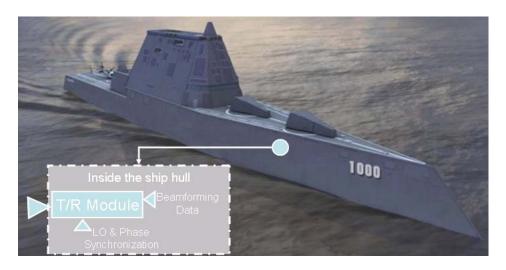

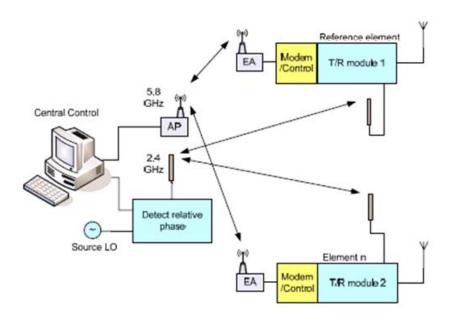

Figure 8 shows that the architecture of a WDDPA system implemented on a ship's hull, illustrating the concept of phase synchronization. Thousands of T/R modules, considered a self-standing array element, are randomly distributed over the superstructure and hull. The system is composed of the central digital controller that communicates wirelessly with all the array elements. The central digital controller computes the beamcontrol data and radar waveform parameters and transmits them to the elements wirelessly. The local oscillator (LO) and synchronization signals are transmitted to the elements wirelessly [15].

Figure 8. WDDPA system architecture implemented on a ship's hull with a single element highlighted (From [5])

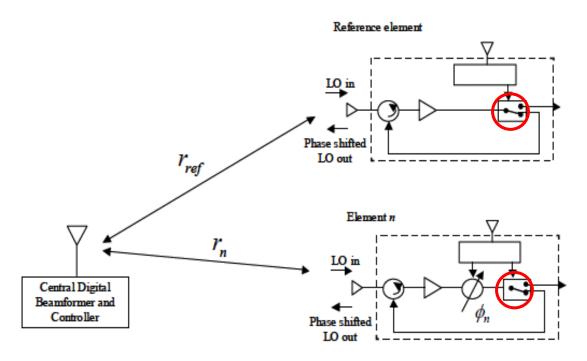

One of the elements is assigned to be the master element, providing its phase information back to the central controller as the reference, while the others are slave elements. In normal conditions, the system is supposed to perform coherent processing of all elements. Periodically, in order to keep all the elements coherent, the central controller

needs to measure phase difference between the master and slave elements. It achieves this goal by executing a synchronization process. The controller sends out the synchronization signal (i.e., beacon) to each element in sequence to synchronize all the slave elements. An active phase synchronization technique is applied to compensate for element dynamic position and propagation channel changes.

Loke [15] first examined possible approaches to dynamically synchronize the elements to a common frequency and then proposed a "brute force" method that has a convenient and simple hardware setup. He also addressed the possible problem of synchronizing modules on a ship which has deforming surfaces and concluded that no correction is needed when operating in the VHF/UHF frequency bands, because the ship deformation is relatively smaller compared to the wavelength.

Grahn [21] applied Loke's proposal of the "brute force" method to design and implement a synchronization circuit composed of commercial-off-the-shelf (COTS) microwave hardware into existing T/R modules. He then examined several configurations of synchronization circuits in wired and wireless structures, trying to validate the previous proposed concept of phase synchronization. Finally, he found a problem that caused unsatisfactory performance. He suggested that the power leakage caused by low isolation of the circulator or the power divider in the synchronization circuit was affecting the performance.

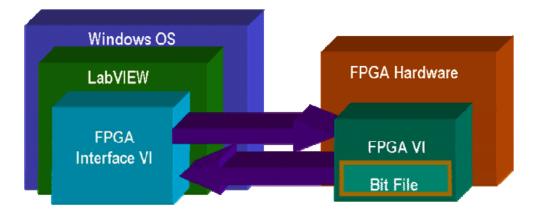

Djerf and Tornazakis [22] developed a LabVIEW control and processing program that handles all the functions within a floating point gate array (FPGA) structure. They also verified all the components in a two-element setup with integrated synchronization circuits. Furthermore, they designed several different synchronization circuits to investigate the problem reported by Grahn. In the end, they proposed that the simple synchronization circuit would not perform adequately with realistic devices because the peaks and nulls of the voltage waveform were always distorted and shifted, resulting in inaccurate phase compensation results. The inability to control signal levels to the LO ports of the modulators and demodulators was also a problem.

#### C. PROBLEM STATEMENT AND THESIS OBJECTIVE

Grahn, Djerf, and Tornazakis had met very similar problems in that the combined LO returned signal power level curves were distorted, which caused the *null* (minimum) of the waveform to be shifted and destroyed. Accordingly, the master was not able to provide an adequate reference to all the elements through the synchronization process. They have proposed some possible errors, such as LO leakage, leakage caused by low isolation of the circulator in the synchronization circuit, and poor performance of the low power amplifier (LPA).

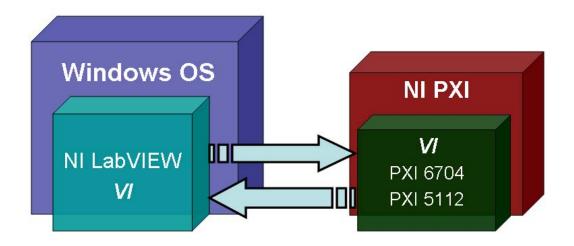

The objective of this paper is to resolve the problem and verify the operation of the synchronization circuit. The same "brute force" synchronization algorithm is still applied for its unique advantage of convenience. Next, some parts of the hardware and software architectures are modified to improve the accuracy and speed of the phase synchronization. The FPGAs are no longer used in hardware and new components were investigated and applied to provide more processing capability and faster sampling speed. As for software, LabVIEW is still used but is modified substantially because of the change in hardware.

Furthermore, once the problem is resolved, the wireless synchronization process will be validated in order to carry on the development of WDDPA. Several different synchronization circuit configurations are implemented to examine the tradeoffs between proposed ideas. The power budget of the overall synchronization circuit is also discussed.

#### D. SCOPE AND ORGANIZATION

Chapter II discusses the architecture of the WDDPA system. The previous synchronization concept and wireless communication network requirements are summarized. Then, the present hardware components and software architectures are addressed. Finally, the revised two-element WDDPA configuration is introduced.

Chapter III examines and verifies the implementation of the new setup of synchronization circuits with the wired LO source. The comparisons between results of current and previous setups are discussed. A comprehensive analysis of the performance of the synchronization process is addressed.

Chapter IV investigates the synchronization process through the wireless network. The demonstration of transmission and reception between two T/R modules is completed and compared to Grahn's result. Several methods to improve the overall system performance are examined in a series of experiments. The analysis of wireless synchronization process is then presented.

Chapter V summarizes the work and offers suggestions for future research in WDDPA phase synchronization.

#### II. WDDPA ARCHITECTURE

#### A. DISTRIBUTED ARRAY CONCEPT AND OPERATION

The core concept of the WDDPA is to incorporate digital wireless beamforming architecture into the structure of a distributed phased array. Conventional phased array antennas are usually periodic arrays composed of multiple single-element antennas spatially distributed in two or three dimensions, based on a needed functionality. Compared to a conventional periodic array, a distributed array has several unique characteristics, and the conventional array formulas must be re-examined for the purpose of WDDPA development.

Basic array antenna and radar performance parameters have been presented in numerous textbooks (see, for example, [23]). The basic equations for array patterns, directivity and radar range equations are re-examined in order to clarify the overall WDDPA system performance.

#### 1. Element Factor

The element factor is the normalized radiation pattern of individual elements in the array. Typically, the field of view (FOV) of a single element is wide and its directivity or gain should be relatively low. With the contribution of all array elements, the radiation pattern of a phased array can achieve very directive and high gain. However, when array elements are distributed in different environments from conventional setups, not every element can illuminate the target due to obstruction of platform superstructures or other environmental factors. Therefore, while the target is not in the FOV of an element, it does not contribute to the array pattern [3]. The element factor is expressed as:

$$EF_n = \begin{cases} \left| \hat{n}_n \bullet \hat{r} \right|, \ \hat{n}_n \bullet \hat{r} > 0 \\ 0, \text{ otherwise} \end{cases}$$

(1)

where

$EF_n$  = element factor of the  $n^{th}$  element.

$\hat{n}_n$  = vector normal to the surface of the  $n^{th}$  element.

$\hat{r}$  = vector in observation direction

Equation (1) defines a general cosine type of pattern.

#### 2. Array Factor

Array factor is the normalized radiation pattern of the array composed of multiple individual elements. The DDG–1000 model in Figure 9 is used to illustrate the spherical coordinate system reference. A general form for the three-dimensional array factor with elements located at  $(x_n, y_n, z_n)$ , n = 1, 2, 3, ..., N is [3], [14]

$$AF(\theta,\phi) = \sum_{n=1}^{N} A_n e^{+j\psi_n} e^{+j\psi_s} e^{+j\bar{k}\cdot\bar{r}_n}$$

(2)

where

$A_n e^{+j\psi_n}$  = complex coefficient of the  $n^{th}$  element that accounts for sidelobe control and corrections for all hardware nonidealities including synchronization

$\psi_s$  = beam scanning phase weights

$$= -k \left[ \left( \sin \theta_s \cos \phi_s \right) x_n + \left( \sin \theta_s \sin \phi_s \right) y_n + \left( \cos \theta_s \right) z_n \right]$$

$(\theta_s, \phi_s)$  = scan angle as defined by the coordinate system in Figure 9

$$\vec{k}$$

=  $k(\hat{x}\sin\theta\cos\phi + \hat{y}\sin\theta\sin\phi + \hat{z}\cos\theta)$

$$k = \frac{2\pi}{\lambda}$$

$\lambda$  = the wavelength

$(x_n, y_n, z_n)$  = location of element n

$\vec{r}_n$  = position vector from the array origin to element n

$$= \hat{x}x_n + \hat{y}y_n + \hat{z}z_n$$

Figure 9. Spherical coordinate system referenced to DDG–1000 CAD model (From [3])

#### 3. Total Array Pattern

The transmitting and receiving array pattern can be computed from the element locations and orientations. The pattern factor  $F(\theta,\phi)$  is the product of element factor  $EF_n(\theta,\phi)$  and array factor  $AF(\theta,\phi)$ , combining Equations (1) and (2) [3]:

$$F(\theta,\phi) = \sum_{n=1}^{N} A_n e^{+j\psi_n} e^{+j\psi_s} e^{+j\bar{k}\cdot\bar{p}_n} EF_n(\theta,\phi)$$

(3)

#### 4. Directivity

Directivity is the maximum value of the directive gain. It is one important characteristic in the description of the antenna performance. The directive gain can be defined in terms of the normalized pattern factor  $F_{\text{norm}}(\theta,\phi)$  [3]:

$$D(\theta,\phi) = \frac{4\pi}{\int\limits_{0}^{2\pi} \int\limits_{0}^{2\pi} \frac{\left|F\left(\theta,\phi\right)\right|^{2}}{\left|F_{\text{max}}\right|^{2}} \sin\theta d\theta d\phi} = \frac{4\pi}{\int\limits_{0}^{2\pi} \int\limits_{0}^{2\pi} \left|F_{\text{norm}}\left(\theta,\phi\right)\right|^{2} \sin\theta d\theta d\phi}$$

(4)

Directivity is the maximum value of the directive gain without any loss occurring in the array. When loss occurs, the gain is equal to the directivity multiplied by the efficiency [3]:

$$G(\theta, \phi) = \eta D(\theta, \phi) = \frac{4\pi A_e}{\lambda^2} |F_{\text{norm}}(\theta, \phi)|^2$$

(5)

where

$\eta$  = the antenna efficiency,  $0 \le \eta \le 1$

$A_{\rho}$  = the array effective area

# 5. Radar Range Equation

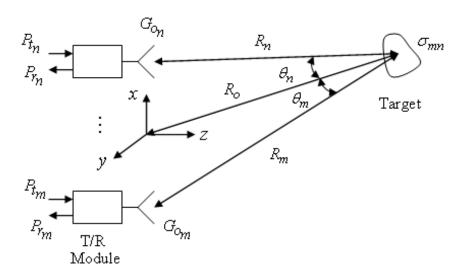

Reference [3] customizes the radar range equation (RRE) for a distributed array to include the various phase shifts of the received power for wireless beamforming application. Figure 10 shows an arbitrary number of array elements distributed relatively close to each other compared to the range to the target.

Figure 10. Distributed array operation configuration (From [3])

Therefore, the deviation of the aspect angles between individual elements is so small that it can be neglected, and the range from each element to the target is considered approximately the same. Additionally, in this model, all element characteristics are identical, which means equal transmit power, equal antenna effective area, and equal antenna gain. After substitution and reduction from the conventional RRE, and including phase shifts in the receive channels in the distributed array, the received power at element m yields:

$$\overline{P_{r_m}} = \frac{\overline{P_t} G_o^2 \sigma \lambda^2}{\left(4\pi\right)^3 R_o^4} \left| \sum_{n=1}^N \left(1\right) \right|^2 = \frac{\left(N\overline{P_t}\right) \left(NG_o\right) G_o \sigma \lambda^2}{\left(4\pi\right)^3 R_o^4}$$

(6)

where

$\overline{P_t}$  = the time-averaged power transmitted by each element =  $\overline{P_{t_m}}$  =  $\overline{P_{t_n}}$

$G_o$  = the antenna gain of each element =  $G_{o_n} = G_{o_n}$

$\sigma$  = radar cross section of the target

$\lambda$  = wavelength

$R_o$  = the path distance from the array origin (phase reference

$= R_n = R_m$

N = the total number of elements

In this simplified RRE,  $\overline{P_{r_m}}$  is considered as the minimum detectable signal power at element m, hence  $R_o$  can be obtained if all the other variables are known. The derived formula clearly shows that for N-elements in a coherent distributed array system, the total transmit power is  $N\overline{P_t}$  and the overall antenna gain is  $NG_o$ . The range  $R_o$  is in proportion to the square root of the number of element N, if other variables stay the same.

#### 6. Signal-to-noise Ratio

Signal-to-noise ratio (SNR) is one of the vital measures for a radar system. It is obtained from the RRE, in which  $\overline{P_{r_m}}$  is the power received by a single element m. The equation derived by the thermal noise power for an individual element in the array is  $N_o = k_B T_S B$ :

$$\left(\frac{S}{N_o}\right)_m = \frac{\overline{P_{r_m}}}{N_o} = \frac{G_{o_m} \lambda^2}{\left(4\pi\right)^3 k_B T_S B} \left| \sum_{n=1}^N \frac{\sqrt{\overline{P_{t_n}} G_{o_n} \sigma_{mn}}}{R_n R_m} \exp\left\{-j2kR_o\right\} \right|^2$$

(7)

where

$k_B$  = Boltzman's constant (operated with a matched input and load)

$= 1.38 \times 10^{-23} \text{ J/K}$

$T_s$  = the system noise temperature (degrees Kelvin)

*B* = the system bandwidth (hertz)

If there are identical N elements in the distributed array system, using coherent integration yields signal amplitude multiplied by N. The associated power of coherent performance is proportional to  $N^2$  [3]. The thermal noise in the system is considered as uncorrelated Gaussian white noise, which indicates that the total noise power in the array is additive. This also leads the total noise power to be N times the noise power in the single element. The array SNR is then improved by a factor of N:

$$\left(\frac{S}{N_o}\right)_{array} = N\left(\frac{S}{N_o}\right)_1 \tag{8}$$

#### B. WIRELESS BEAMFORMING CONCEPT

As previously stated, the core concept of WDDPA is to incorporate digital wireless beamforming into the architecture of a distributed phased array. The two major separate aspects here are the distributed array and wireless beamforming. Distributed

array related concepts and formulas were reviewed in the last section. This section reviews the concepts of wireless networking and digital beamforming (DBF).

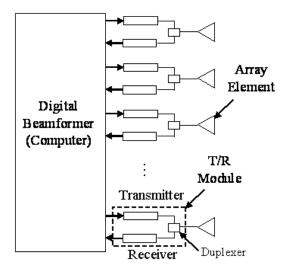

# 1. Digital Beamforming

The general DBF architecture is shown in the Figure 11. In this architecture each element is composed of a transmitter and receiver. The transmitter consists of a baseband waveform generator, modulator and power amplifier (PA). The receiver is composed of a low noise amplifier (LNA), demodulator, and analog-to-digital convertor (ADC). On TX, the waveform is generated from the information provided by the central digital beamformer, and sent to the array element. The waveform is generated at each element and then transmitted simultaneously. On RX, the returned signal is received by the element, amplified, down-converted, sampled and passed to the computer.

Note that the phase reference is required to be distributed in the array system to ensure that all of the LO signals of the deployed elements perform coherent processing, i.e., phase synchronization.

Figure 11. Generic DBF architecture (From [3])

Reference [3] implements the phase shift factor  $\psi_n$  into the element weight  $W_n$  for beamforming:

$$W_n = A_n \exp[-jk(x_n u_s + y_n v_s + z_n w_s) + j\psi_n]$$

(9)

and the corresponding array factor  $F(\theta, \phi)$  becomes:

$$F(\theta, \phi) = \sum_{n=1}^{N} W_n \exp\left[jk\left(x_n u + y_n v + z_n w\right)\right]$$

(10)

where

$$W_n$$

=  $A_n e^{j\psi_n} e^{j\psi_s}$  = element weight for beamforming

$(u, v, w)$  = direction cosines of the observation point

=  $(\sin\theta\cos\phi, \sin\theta\sin\phi, \cos\theta)$

$(u_s, v_s, w_s)$  = direction cosines for scan angle

=  $(\sin\theta_s\cos\phi_s, \sin\theta_s\sin\phi_s, \cos\theta_s)$

In the beamforming process, the element weight  $W_n$  is sent to the modulator on TX. On RX the central controller applies the element weight to the received signal from the demodulator and then computes the array factor.

# 2. Wireless Network Requirement

Potentially thousands of elements can be implemented in the WDDPA system. The weight and complexity of routing data and transmission lines to all elements are difficult. Wireless communication is another critical technology for the BFN. Figure 2 (b) shows a WDDPA configuration where all the self-standing T/R modules are required to continuously communicate with the central controller wirelessly, including beamforming signals, synchronization signals, element phase weights, and digitized received signals. A distributed phased array employing wireless beamforming requires a very high data rate.

Reference [15] examined the wireless network requirements of the distributed array as shown in Table 1. On TX, a total of eight bits of data are required in the setup. They are composed of waveform control, synchronization, and phase weight data. The needed TX data rate is not challenging for modern commercial wireless hardware.

| TX/RX | Wireless Data Description | Source             | Data Ra                              | ate   |

|-------|---------------------------|--------------------|--------------------------------------|-------|

| TX    | Waveform Control          | Central Controller | 2 b/s                                |       |

|       | Synchronization           | Central Controller | 2 b/s                                | 8 b/s |

|       | Phase Weights             | Central Controller | 4 b/s                                |       |

| RX    | Digitized Received Signal | Array Element      | 100 MS/s (sampling rate)<br>1.6 Gb/s |       |

Table 1. A summary of the wireless network requirement for WDDPA (After [15])

On RX, a high data rate is needed because the performance of the ADC affects the resolution of the received digitized signal [3]. The sampling rate of the ADC must meet the Nyquist condition, which is at least twice the intermediate frequency (IF) bandwidth (in a super heterodyne receiver) or twice the baseband frequency (in a homodyne system). The approximate data rate requirement is given by [24]:

$$R_b = N_c \times N_b \times R_s \tag{11}$$

where

$R_h$  = data rate

$N_c$  = data channels per array element

$N_b$  = ADC bits of resolution

$R_s$  = ADC sampling rate (samples per second)

Therefore, if a two-channel ADC is simultaneously sampled with 100 MS/s for each element and the resolution is eight bits, then for each element in the wireless

network, the required data rate is approximately  $R_b = 2 \times 8 \times 100$  MS/s = 1.6 Gb/s. For an N-element full-scale array, the total required data rate is 1.6N Gb/s. Furthermore, if deformations of a platform or complex non line-of-sight (LOS) environments are taken into consideration, a much higher data rate is required.

Currently, the most commonly used wireless local area network (WLAN) is based on the IEEE 802.11 standard. Some of its variants, such as IEEE 802.11a (5 GHz) and IEEE 802.11g (2.4 GHz) standards, offer a peak data rate 54 Mb/s. Obviously, 54 Mb/s would not be sufficient for a full-scale developed WDDPA according to Equation (11).

With each generation of technology, wireless data rates have increased significantly [25]. For example, IEEE 802.16 is another series of wireless broadband standards that is hugely successful both in universal spread of users and commercial interests of IEEE 802.11 applied in WLANs. The IEEE 802.16e, adopted in the well-known broadband wireless access (WiMAX) technology, standardizes networking between various fixed access points and mobile devices. Originated in 2005, it provides data rates up to 70 Mb/s [26]. In late 2006, IEEE 802.16m was proposed by the IEEE 802.16 working group. In early 2009, it was reported that the new standard will push data rates up to 100 Mb/s for mobile application and 1 Gb/s for fixed application [25]–[27] in order to offer an advanced air interface to meet future cellular layer requirements. Stimulus from the commercial market during the fast advance of wireless communication technology will benefit WDDPA.

To handle the high data rate, hybrid optical and wireless configurations are also possible. Fiber optic links could be used for remote parts of the ship, with short-range wireless networks used for clusters of nearby elements. Currently, fiber optic links are capable of data rates greater than 40 Gb/s [28].

#### C. WDDPA DEMONSTRATION OVERVIEW

Up to now, the demonstration of the WDDPA has mainly been from the perspective of the ship-based distributed array radar. This is illustrated by the EWR implemented on the DDG-1000 (Figure 12). Several researchers [12]-[17] have

examined whether the EWR employing a WDDPA structure is capable of carrying out the mission of a secondary BMD radar. This section reviews the system as currently conceived.

Figure 12. Configuration of WDDPA elements embedded in DDG–1000's hull (After [29])

The opportunistic array is assumed to operate at 300 MHz in the VHF/UHF band. In the context of EWR, it is expected to detect and track targets at ranges over 1000 km, which affects the number of elements implemented. The system's high angular resolution capability is provided by the narrow radar beamwidth. Tong [14] did extensive system simulations of radar performance. Validation of the critical concepts, such as synchronization, was required; therefore, a simplified system was built for the purpose of validation and verification. This was done at 2.4 GHz to take advantage of the COTS microwave hardware and other needed components. COTS hardware was also used for wireless communication devices and the central controller in the demonstration array.

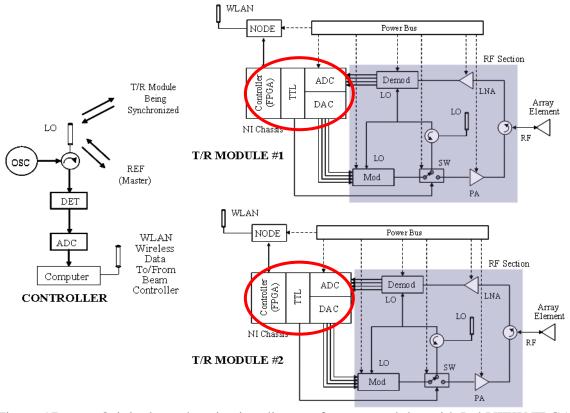

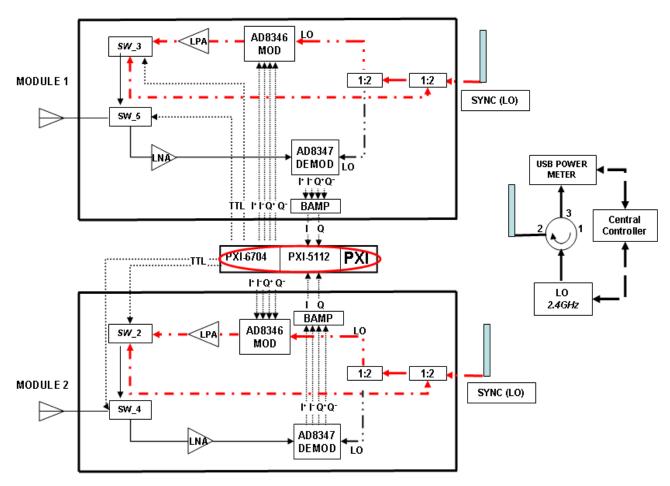

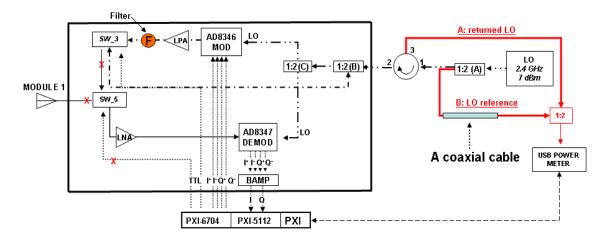

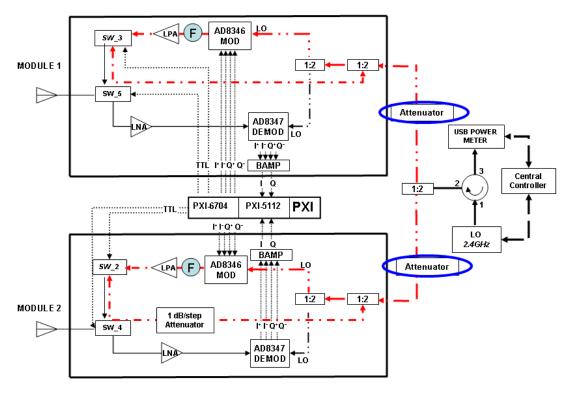

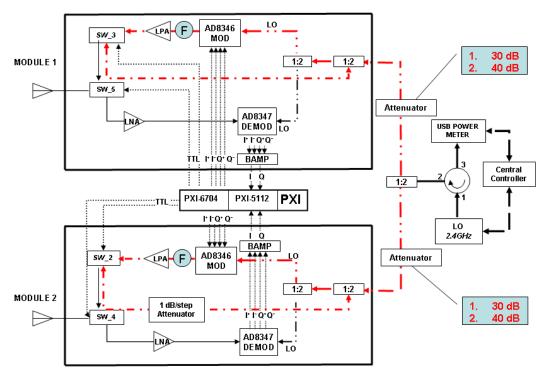

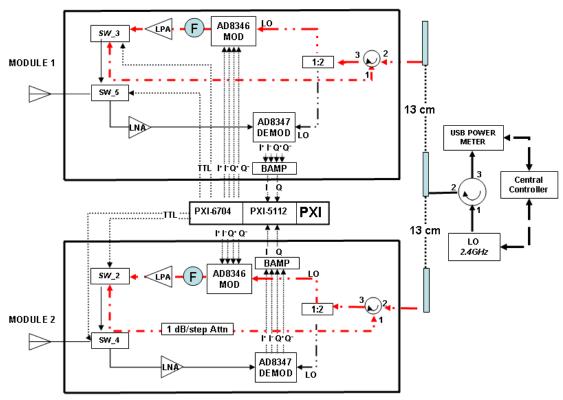

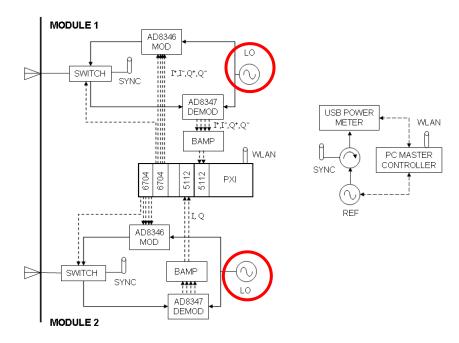

Four major subsystems make up the WDDPA demonstration array as shown in Figure 13: (1) Central Controller, (2) T/R Module, (3) LO System, and (4) Wireless Communication Network. Each was developed and tested, and improvements were made based on the testing outcomes.

Figure 13. WDDPA demonstration array configuration (From [21])

#### 1. Central Controller

The central controller acts as the "brain" of the overall WDDPA system, as shown in Figure 13. It is basically a computer installed with the required application software. LabVIEW 8.6, from National Instruments, was selected for the demonstration array. It controls data flow and synchronization, and also plays the role of a digital beamformer. For a full-scale WDDPA system, the central controller must be capable of generating the beamforming control data, as well as rapidly processing received digitized signal data for all the elements. Meanwhile, it must be able to monitor every element's operation for the purpose of optimizing system performance.

For the small demonstration array, the basic needed function of the central controller is to offer the operator an interface to input control signals to the T/R modules and manage the data transfer between a small number of T/R modules (two elements in the present setup). One of the main tasks for the controller is performing the synchronization process. In order to maintain the coherence, the central controller has the

capability to detect the phase difference between two T/R modules. Then, the master element is assigned to provide its phase information as the reference for the slave elements.

# 2. T/R Module

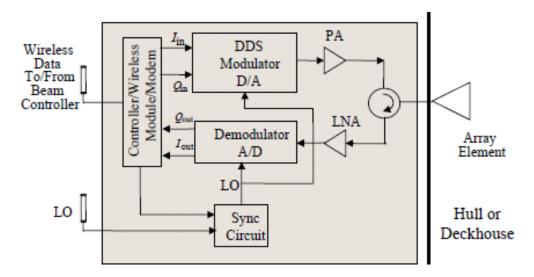

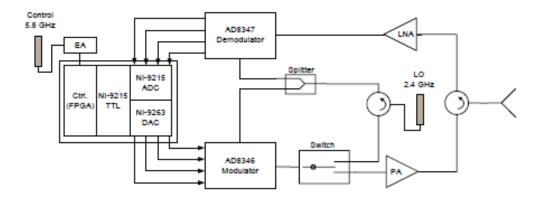

In the WDDPA architecture, as shown in Figure 13, the system is composed of numerous self standing T/R modules, which are capable of transmitting the assigned signals, receiving returned signals, and communicating with the central controller wirelessly. Each T/R module integrates a local controller and a LO antenna, and is equipped with an antenna for TX and RX of the radar signal. A simplified T/R module is shown in Figure 14.

Figure 14. Simplified configuration of T/R module (From [23])

In the WDDPA development process, a functional demonstration T/R module using various COTS microwave components has been improved in several iterations. Improvements include the performance of the modulator and demodulator, the development of the synchronization circuit, and the control of power levels in the system. The present functionality and configuration of the T/R module is as follows:

The central controller sends the beamforming control information generated from the operator's inputs to each T/R module's local controller over a wireless network. The

Analog Devices AD 8346 modulator requires five inputs, which are the LO, and differential in-phase and quadrature-phase voltages (LO, IP, IN, QP and QN).

The quadrature-phase voltages from the baseband waveform are up-converted by the modulator board. After amplification, the needed waveform is transmitted. All the elements are required to perform in coherent operation, which means all the transmissions occur simultaneously.

On RX, the received echo signal is amplified by a LNA before the demodulator (Analog Devices AD 8347) mixes the LO and incoming signals. Then the demodulator produces four differential outputs i.e., IP, IN, QP and QN. A differential input instrumentation amplifier (more details in the Appendix) is applied in the most recent setup to convert four channels into two channels (I and Q). After sampling, the samples are sent back to the central controller via the wireless network. The signal processing and beamforming are executed by the central controller.

# 3. LO System

The LO concept shown in Figures 13 and 14 distributes a LO signal (2.4 GHz for the demonstration array) wirelessly to all elements in the system. Each implemented element is equipped with a dedicated LO antenna. The received LO from the master controller is used as the local oscillator signal, eliminating the requirement for a signal source at every element.

To optimize system performance, each element has to be synchronized to a common phase and time reference. The central controller executes the synchronization process. The phase of the distributed LO signal in the master element is assigned as a reference to all of the slave elements. The central controller calculates the phase differences between master and slave elements, and then compensates for the difference in the processing. Therefore, the system is synchronized and coherent operation is ensured.

Note that this approach also compensates for any phase difference in the LO transmission channel between the central controller and elements. The process must be

repeated often enough to maintain adequate synchronization, with the frequency determined by the stability of the equipment and propagation channels between the controller and elements.

#### 4. Wireless Communication Network

The WDDPA concept is based on up to thousands of distributed elements implemented randomly or non-uniformly in the environment or on platforms. Therefore, a conventional wired data transfer system is not realistic. The wireless architecture makes the WDDPA feasible.

All the communications between the central controller and numerous elements are accomplished via a robust wireless network which functions as the "nerve" of the overall WDDPA system. In the wireless network, each element behaves as a node on the network. By taking advantage of modern commercial wireless communication technology, constructing an efficient and cost-effective demonstration array of the network is achievable.

In the present two-element configuration, the wireless network for communication between the central controller and elements is the IEEE 802.11a standard. The operation frequency is 5.8 GHz, as shown in Figure 13, in order to prevent possible interferences with the LO system (2.4 GHz). The wireless access point (WAP) is connected to the central controller. For each element in the WDDPA demonstration array structure, the local controller is connected to an antenna which acts as an access point to the central controller.

Noris [30] addresses the WDDPA wireless network challenges and possible solutions in more depth.

#### D. WDDPA SYNCHRONIZATION PROCESS

# 1. Synchronization Operation and Concept

The common phase reference is extremely crucial in order to steer the beam and control the radiation pattern simultaneously for any phased array system. A phased array system is composed of numerous elements, whereby the radiation pattern is determined by controlling the phase shifts of individual elements. The phase information is always relative to a common reference. The objective of this paper is to improve the WDDPA phase synchronization operation.

The "brute force" synchronization technique, a systematic phase adjustment of each element, was proposed and then applied in the WDDPA by Loke [15]. The major advantages of this technique are its simplicity and regularity.

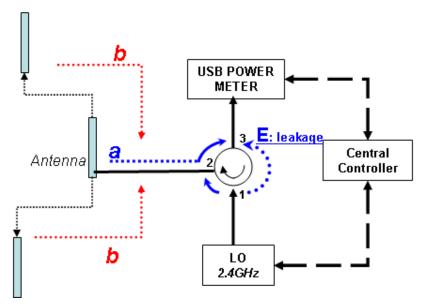

Figure 15 demonstrates the simplified "brute force" phase synchronization process. The dashed block represents an element, and needed synchronization hardware components are incorporated in each element. The "brute force" synchronization is applied one element at a time. The first element to be synchronized (the slave) is chosen, and the central controller sends out the signal to execute the phase synchronization process. The selected slave element is then in the synchronization mode and the switch (circled) is positioned for the synchronization operation. The LO signal is passed through the synchronization circuit, which is composed of circulators, power dividers, a PA, and a phase shifter. Then the modified LO signal is sent back and compared to the signal of a specific master element reference at the central controller.

Figure 15. Simplified "brute force" schematic phase synchronization with the switch highlighted (From [23]).

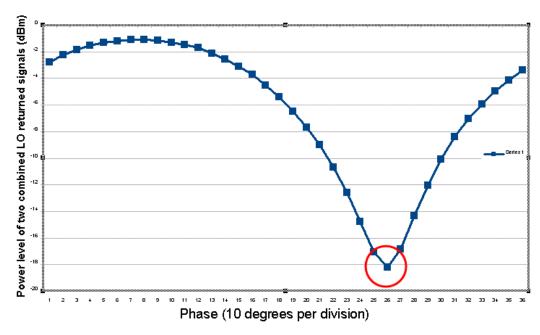

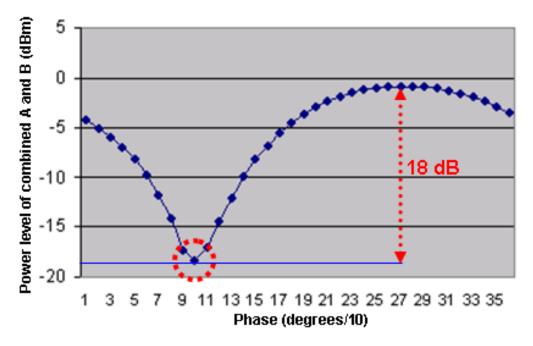

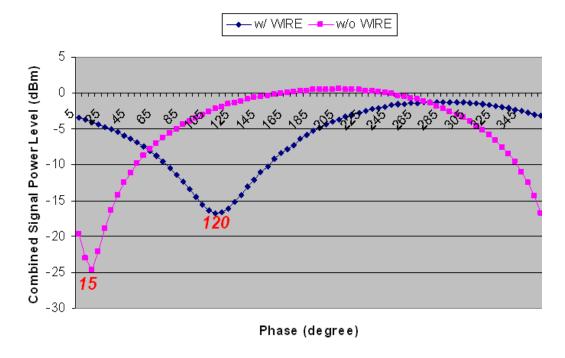

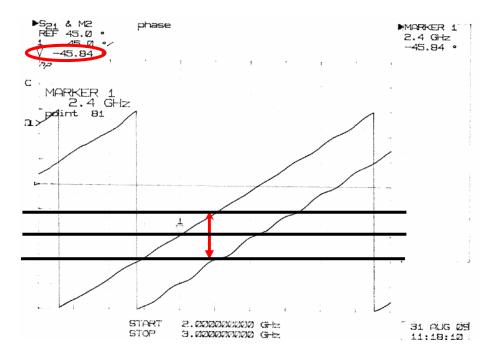

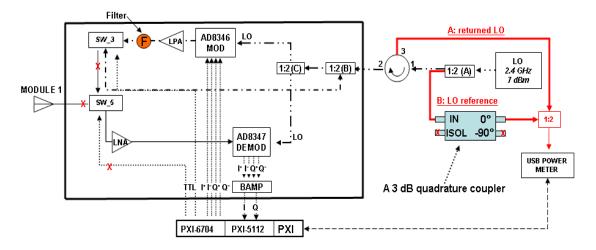

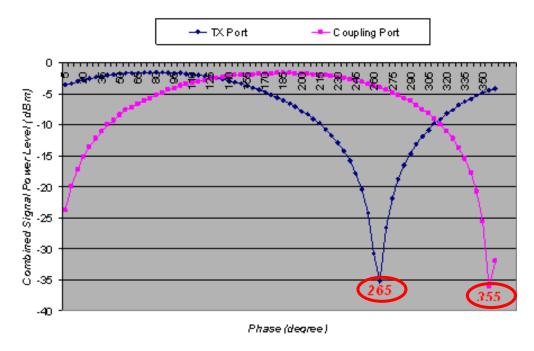

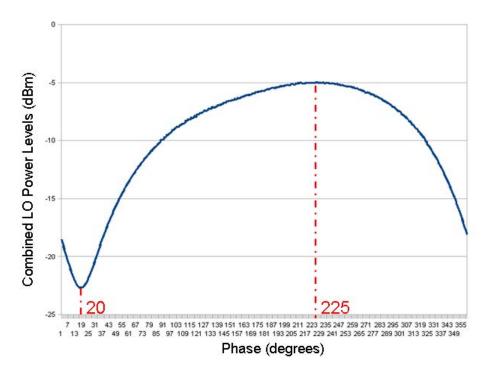

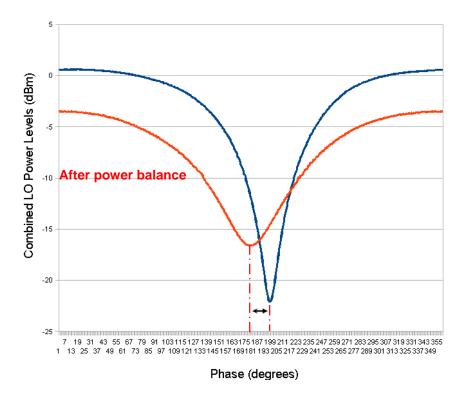

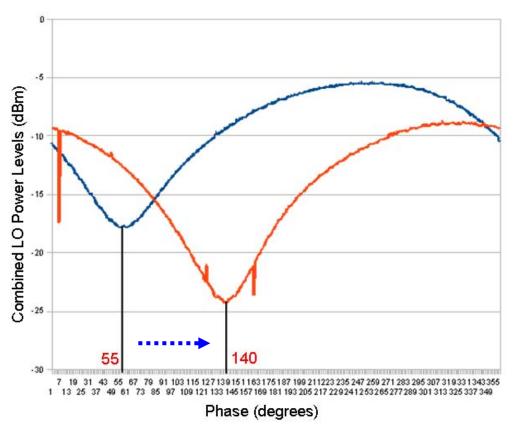

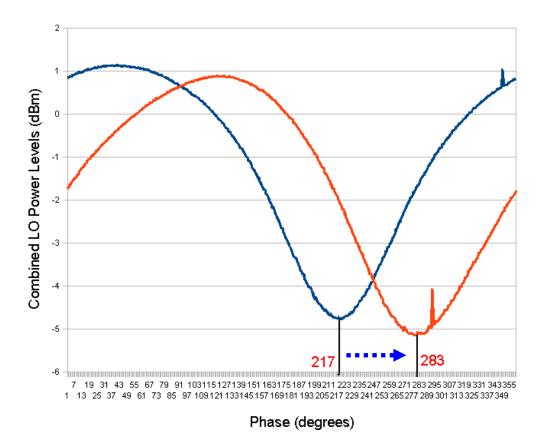

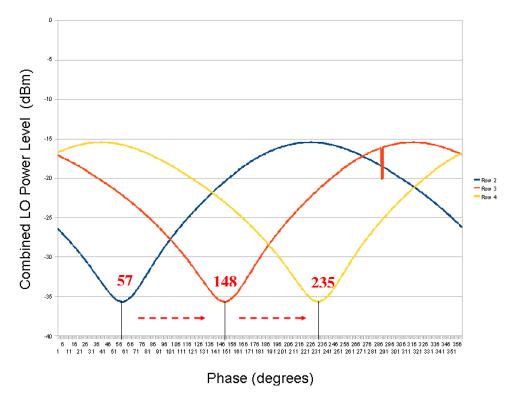

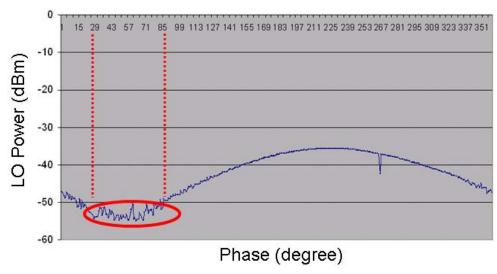

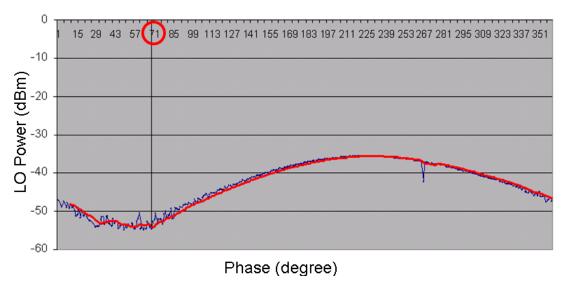

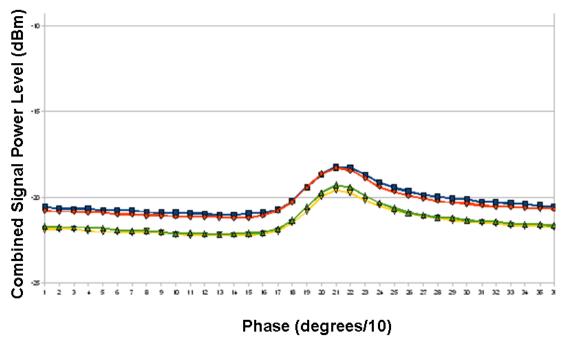

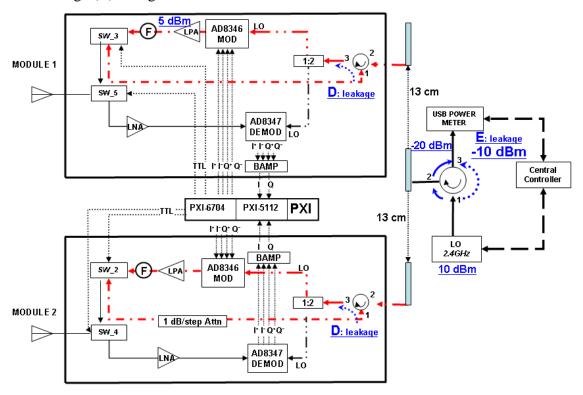

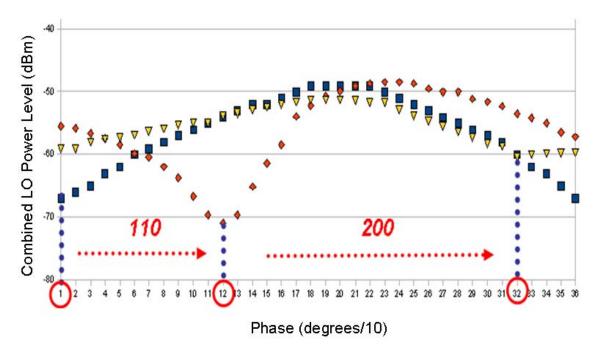

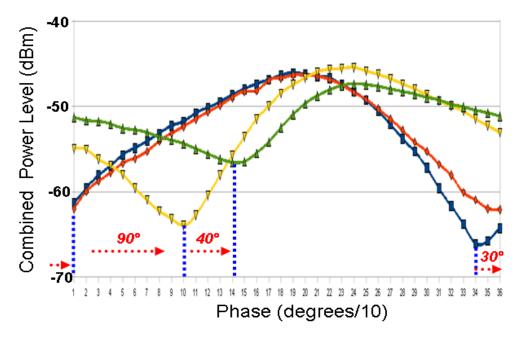

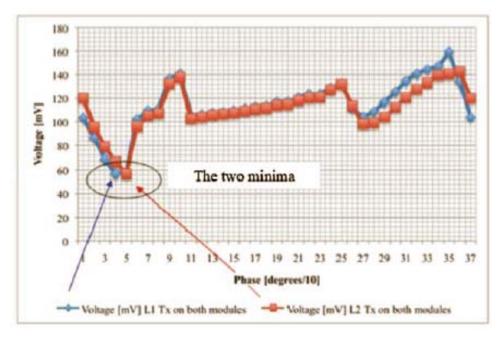

The central controller runs a phase comparison algorithm, combining the master's reference signal and a returned LO signal from the slave. The process is repeated by stepping through 360 degrees of phase at the slave. The power sensor enables the central controller to display the graph of phase difference versus combined signal power level as shown in Figure 16. It is relatively easy to detect the minimum in comparison to the maximum.