## ABSTRACT

### COMPUTER SCIENCE

FOWLER, CHANTICE B.S., SPELMAN COLLEGE, 1992 M.S., CLARK ATLANTA UNIVERSITY, 1994

### THE COMPUTER SCIENCE GRADUATE RECORD EXAM TUTORIAL COURSEWARE

Advisor: Dr. Kenneth Perry

Thesis dated May, 1994

The design and development of Computer Science Graduate Record Examination Tutorial Software will be discussed. The courseware reviews Computer Design, File Structures, Data Structures, and Discrete Math to thoroughly prepare students for the exam. A demonstration of the software is included on diskette.

## THE COMPUTER SCIENCE GRADUATE RECORD EXAM TUTORIAL COURSEWARE

A THESIS

SUBMITTED TO THE FACULTY OF CLARK ATLANTA UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF MASTER OF SCIENCE

BY

CHANTICE M. FOWLER

DEPARTMENT OF COMPUTER & INFORMATION SCIENCE

.

.

ATLANTA, GA

MAY 1994

R= VIII T= 103

#### ACKNOWLEDGEMENTS

.

This entire tutorial courseware project and thesis would not be possible had it not been for the encouragement, support, dedication, patience, insight, and expertise of my advisor, Dr. Kenneth Perry. To him I say, "Thank You!!" The Atlanta University Center's Computer Science & Engineering Programs would definitely reign as the best in the country if all the professors were as nearly dedicated and hardworking as he. Clark Atlanta University did not make any mistakes when they gave him tenure.

Let me acknowledge Clayton Collie who contributed the report on File Structures. In addition, Byron Roberson, Janice Barlow, Katina McKinney, and Courtney Smith programmed the cache demonstration used within the CS-GRE Tutorial Courseware.

Special thanks are given to the National Science Foundation for funding my entire graduate studies education. This project would not have been possible had it not been for their financial support.

Finally, let me thank Clark Atlanta University for being one exceptional university.

ii

## TABLE OF CONTENTS

| ACKNOWLI | EDGEMENTS | 5.    | • •  | •    | •   | •   | • • | •   | •   | ٠   | ٠   | ٠   | •   | •   | •   |    | • | ٠ | ii   |

|----------|-----------|-------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|---|---|------|

| LIST OF  | ILLUSTR   | ATION | is . | •    | •   | •   | • • | •   |     | •   | ٠   | •   | ٠   | •   | •   | •  | • | • | vi   |

| LIST OF  | TABLES    | • •   |      | •    | •   | •   | • • | •   | •   | •   | •   | ٠   | •   | •   | •   | •  | • | • | viii |

|          |           |       |      |      |     |     |     |     |     |     |     |     |     |     |     |    |   |   |      |

| CHAPTER  | 1         |       |      |      |     |     |     |     |     |     |     |     |     |     |     |    |   |   |      |

| INTRODUC | CTION .   | • •   | • •  | •    | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •  | • | • | 1    |

|          |           |       |      |      |     |     |     |     |     |     |     |     |     |     |     |    |   |   |      |

| CHAPTER  | 2         |       |      |      |     |     |     |     |     |     |     |     |     |     |     |    |   |   |      |

| STUDENT  | COMPUTER  | R SCI | ENC  | CΕ   |     |     |     |     |     |     |     |     |     |     |     |    |   |   |      |

| GRADUATI | E RECORD  | EXAM  | I TE | EST  | RE  | SU  | LTS | 5.  | ٠   |     | •   | •   | •   | •   | •   | •  | • | • | 4    |

|          |           |       |      |      |     |     |     |     |     |     |     |     |     |     |     |    |   |   |      |

| CHAPTER  | 3         |       |      |      |     |     |     |     |     |     |     |     |     |     |     |    |   |   |      |

| PROGRAM  | DESIGN    | • •   | • •  | •    | •   | •   | •   |     | •   | •   | •   | •   | •   | •   | •   | •  | • | • | 17   |

| Ma       | in Menu   | ••    | • •  | •    | •   | •   | •   |     | •   | •   | •   | •   | •   | •   | •   | •  | • | • | 19   |

| A.       | Computer  | r Des | igr  | ı.   | •   | •   | •   |     | •   | •   | •   | •   | •   | •   | •   | •  | • | • | 25   |

|          | A.1.      | Intr  | odu  | ict  | ion | L   | •   |     | •   | •   | •   | •   | •   | •   | •   | •  | • | • | 25   |

|          | A.2.      | IAS   | Con  | nput | ter |     | •   |     | •   | •   | •   | ٠   | •   | •   | •   | •  | ٠ | • | 26   |

|          | A.3.      | Mode  | rn   | Cor  | mpu | ite | rs  |     | •   | •   | •   | ٠   | •   | •   | •   | •  | • | • | 26   |

|          | A.4.      | CPU   | •    |      | •   | •   | •   |     | • • | •   | •   | ٠   | •   | ٠   | ٠   | •  | • | • | 29   |

|          | A.5.      | Memo  | ry   | Sya  | ste | ems |     |     | •   | •   | •   | ٠   | •   | •   | •   | •  | • | • | 33   |

|          | A.6.      | Micr  | oir  | nst: | ruc | ti  | on  | Se  | qu  | en  | ciı | ng  | •   | •   | •   | •  | • | • | 55   |

|          | A.7.      | Bool  | .ear | n A  | lge | bra | a   | (Sv | vit | ch: | ing | g J | Alç | gel | ora | a) | • | • | 56   |

| в.       | File St   | ruct  | ure  | es   | •   | •   | •   |     | •   | •   | •   | •   | •   | •   | •   | •  | • | • | 58   |

|          | B.1.      | Sequ  | ent  | ia   | 1 F | 'il | e ( | Org | jan | iza | at: | io  | n   | •   | •   | •  | • |   | 58   |

|    | в.2.    | Rando   | m Fi | le   | Or    | :ga | ni  | za  | ti  | on | l   | •   | •   | •  | •  | •  | •   | • | 58 |

|----|---------|---------|------|------|-------|-----|-----|-----|-----|----|-----|-----|-----|----|----|----|-----|---|----|

|    | в.3.    | Index   | ed S | lequ | ıer   | nti | al  | F   | il  | е  | Or  | ga  | ni  | za | ti | on |     | • | 59 |

|    | B.4.    | Multi   | key  | Fi:  | le    | Or  | ga  | ni  | za  | ti | on  |     | •   | •  | •  | •  | •   | • | 59 |

|    | в.5.    | Block   | ing  | •    | •     | •   | •   | •   | •   | •  | •   | •   | •   | •  | •  | •  | •   | • | 60 |

|    | B.6.    | Buffe   | ring | • 1  | •     | •   | •   | •   | •   | •  | •   | •   | •   | •  | •  | •  | •   | • | 61 |

|    | в.7.    | File a  | Stor | age  | e I   | )ev | ric | es  |     | •  | •   | •   | •   | •  | •  | •  | •   | • | 61 |

|    | в.8.    | Timin   | g of | A    | cce   | ess | M   | et  | ho  | ds | 6   | •   | •   | •  | •  | •  | •   | • | 62 |

|    | в.9.    | Recor   | d Ke | eys  | •     | •   | •   | •   | •   | •  | •   | •   | ٠   | •  | ٠  | ٠  | •   | • | 64 |

|    | в.10.   | Hash    | ing  | •    | •     | •   | •   | •   | •   | •  | •   | •   | •   | •  | •  | •  | •   | • | 64 |

|    | B.11.   | Tree    | s.   | •    | •     | •   | ·   | •   | •   | •  | •   | •   | •   | •  | •  | •  | •   | • | 68 |

| c. | Data St | ructu   | res  |      | •     | •   | •   | •   | •   | •  | •   | •   | •   | •  | •  | •  | •   | • | 71 |

|    | C.1.    | Array   |      | •    | •     | •   | •   | •   | •   | •  | •   | •   | •   | •  | •  | •  | •   | • | 71 |

|    | C.2.    | Linke   | d Li | st   | •     | •   | •   | •   | •   | •  | •   | •   | •   | •  | ٠  | •  | • • | • | 71 |

|    | C.3.    | Stack   | s.   | •    | •     |     | •   | •   | •   | •  | •   | •   | •   |    | •  |    | •   | • | 72 |

|    | C.4.    | Queue   | s.   | •    | •     | •   | •   | •   | •   | •  | •   | •   | •   | •  | •  | •  | •   | • | 73 |

|    | C.5.    | Trees   |      | •    | •     | •   | •   | •   |     | •  | •   | •   |     | •  | •  | •  | •   | • | 74 |

|    | C.6.    | Measu   | ring | ra   | Pr    | cog | ra  | m ' | S   | Pe | erf | or  | ma  | nc | e  | •  | •   | • | 75 |

|    | C.7.    | Algor   | ithm | ı Cl | har   | cac | te  | ri  | st  | ic | s   |     |     | •  | •  | •  | •   | • | 76 |

|    | C.8.    | Alloc   | atic | on d | of    | St  | or  | ag  | e   | Sp | ac  | e   | •   |    | •  | •  |     |   | 77 |

|    | C.9.    | Progr   | am P | er   | for   | ma  | nc  | e   | Im  | pr | ov  | ren | ien | ts | 6  | •  | •   | • | 77 |

|    | C.10.2  | An Ex   | pla  | nat  | io    | n   | 0   | f   | t   | he | 9   | Q   | ue  | st | io | ns |     | æ |    |

|    | 1       | Answer  | s.   | •    |       | •   |     |     |     | •  |     |     |     |    | •  | •  |     | • | 78 |

| D. | Discret | te Mati | hema | ti   | cs    | (S  | Set | Г   | 'he | 01 | :y) |     |     | •  |    | •  |     | • | 80 |

|    | D.1.    |         |      |      |       |     |     |     |     |    |     |     |     |    |    |    |     |   | 80 |

|    | D.2.    | _       |      |      |       |     |     |     |     |    |     |     |     |    |    |    |     | • | 86 |

|    | D.3.    | -       |      |      |       |     | -   |     |     |    |     |     |     |    |    |    |     | • | 88 |

|    |         |         |      |      | - 3 - |     | -   | -   | -   | -  | -   | 7   | -   | -  | -  | -  | -   |   |    |

| E. Summary                     | ٠ | ٠ | • | • | • |   | ٠ | • | • | • | • | ٠ | 88  |

|--------------------------------|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| CHAPTER 4                      |   |   |   |   |   |   |   |   |   |   |   |   |     |

| CONCLUSIONS & FUTURE WORK      | • | • | ٠ | ٠ | • | • | ٠ | • | ٠ | • | ٠ | • | 90  |

| APPENDIX A                     |   |   |   |   |   |   |   |   |   |   |   |   |     |

| THE CS-GRE TUTORIAL COURSEWARE | • | • | • |   |   |   | • | • |   | • |   | • | 102 |

|                                |   |   |   |   |   |   |   |   |   |   |   |   |     |

| SELECTED BIBLIOGRAPHY          | • | • | • | • |   | • | • |   | • |   |   | • | 103 |

• .

## LIST OF ILLUSTRATIONS

| Figure |                                                                                         | Page |

|--------|-----------------------------------------------------------------------------------------|------|

| 2-1.   | Computer Science GRE Evaluation Results for All<br>Students                             | 9    |

| 2-2.   | Computer Science GRE Evaluation Results for CAU<br>Undergraduate Students               | 10   |

| 2-3.   | Computer Science GRE Evaluation Results for CAU<br>Graduate Students                    | 11   |

| 2-4.   | Computer Science GRE Evaluation Results for CAU<br>Graduate Students from CAU           | 12   |

| 2-5.   | Computer Science GRE Evaluation Results for CAU<br>Graduate Students from Other Schools | 13   |

| 2-6.   | Structure Diagram                                                                       | 15   |

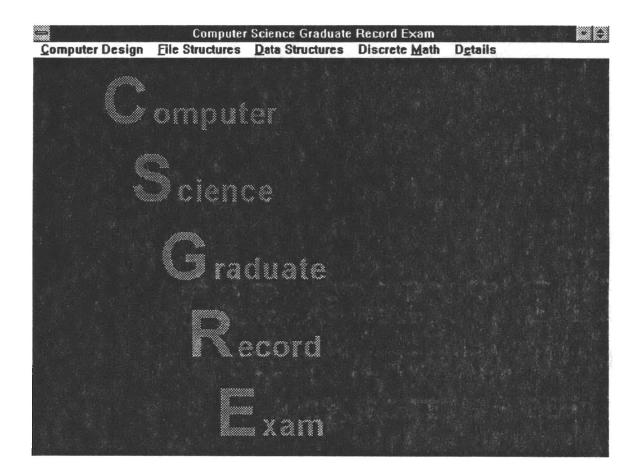

| 3-1.   | CS-GRE Tutorial Courseware Main Menu Screen                                             | 19   |

| 3-2.   | CS-GRE Tutorial Courseware Computer Design<br>Screen                                    | 20   |

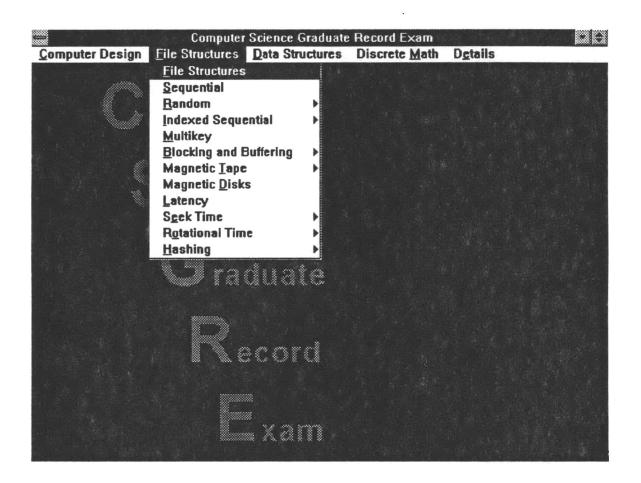

| 3-3.   | CS-GRE Tutorial Courseware File Structures<br>Screen                                    | 21   |

| 3-4.   | CS-GRE Tutorial Courseware Data Structures<br>Screen                                    | 22   |

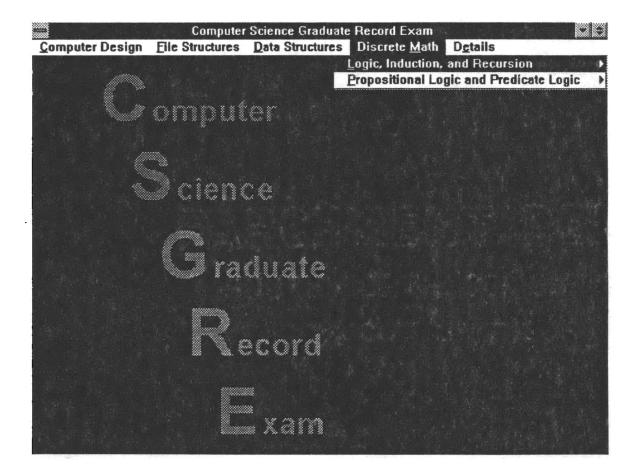

| 3-5.   | CS-GRE Tutorial Courseware Discrete Math Screen                                         | 23   |

| 3-6.   | CS-GRE Tutorial Courseware Details Screen                                               | 24   |

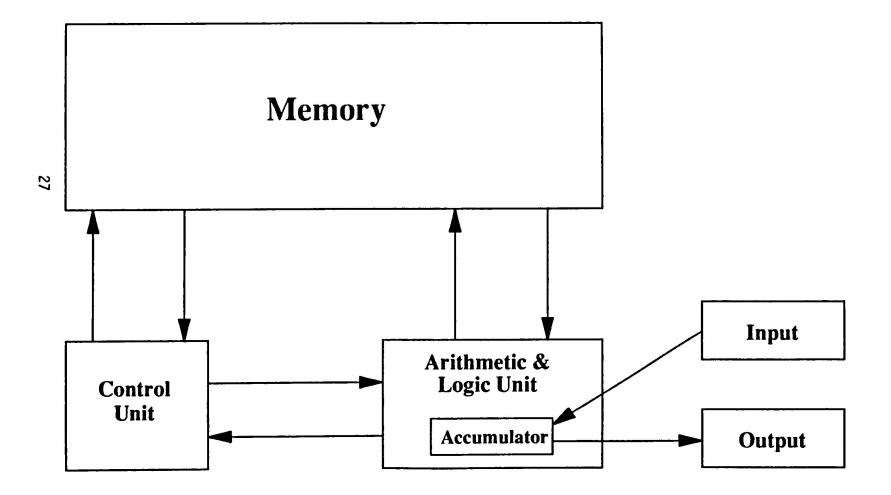

| 3-7.   | The Original von Neumann Machine                                                        | 27   |

| 3-8.   | Basic Computer Organization                                                             | 28   |

| 3-9.   | Memory Hierarchy                                                                        | 34   |

| 3-10.  | Memory Represented By Array M of Size N                                                 | 38   |

| 3-11. | The Moving of Pages Between Auxiliary & Primary          |

|-------|----------------------------------------------------------|

|       | Memory                                                   |

| 3-12. | The CS-GRE Tutorial Courseware Diagram 1 43              |

| 3-13. | The CS-GRE Tutorial Courseware Diagram 2 44              |

| 3-14. | The CS-GRE Tutorial Courseware Diagram 3 47              |

| 3-15. | The CS-GRE Tutorial Courseware Diagram 4 49              |

| 3-16. | The CS-GRE Tutorial Courseware Diagram 5 51              |

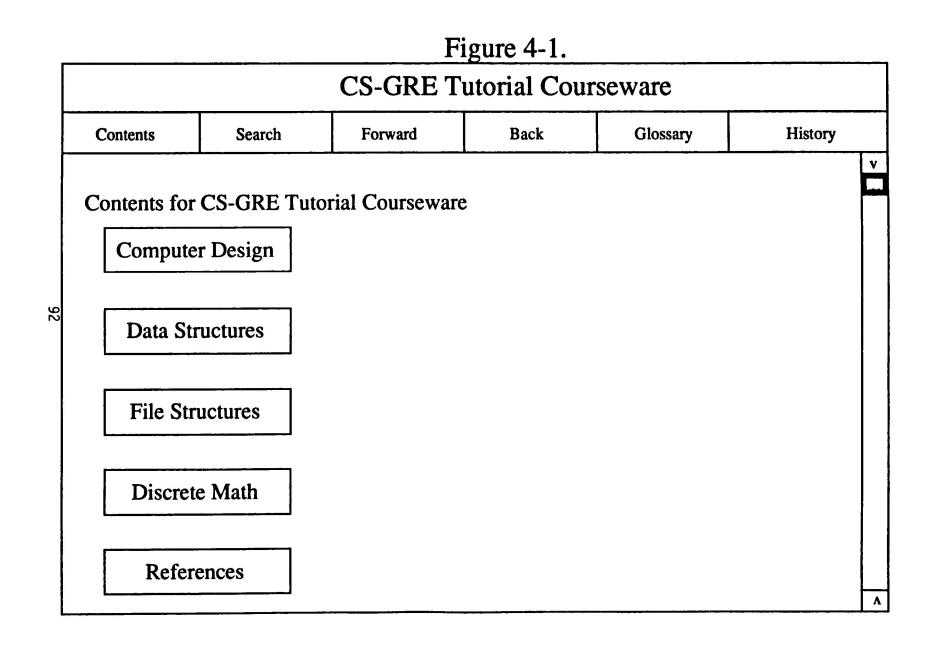

| 4-1.  | CS-GRE Tutorial Courseware Menu Selections 92            |

| 4-2.  | CS-GRE Tutorial Courseware Computer Design<br>Selections |

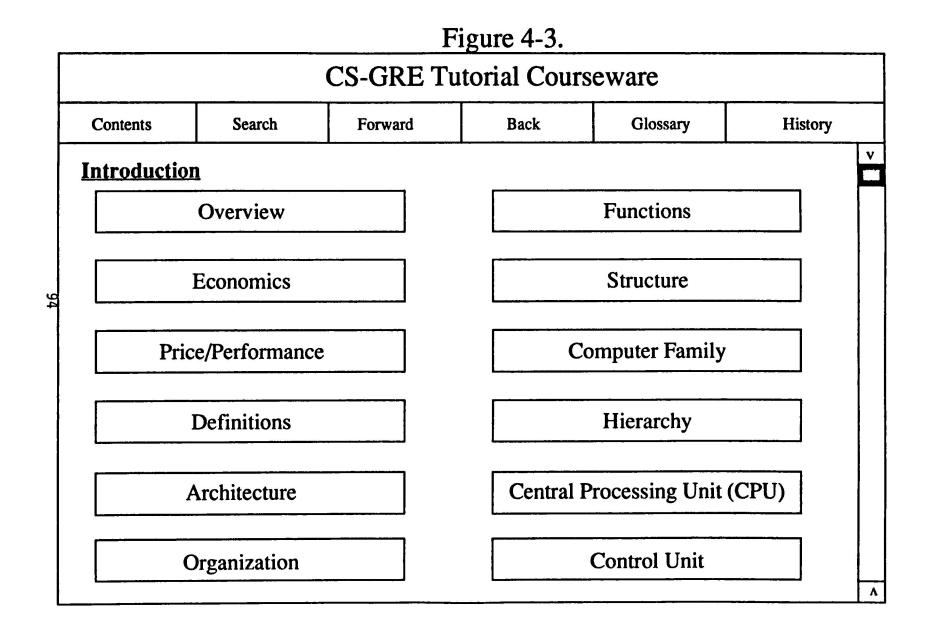

| 4-3.  | CS-GRE Tutorial Courseware Introduction<br>Selections    |

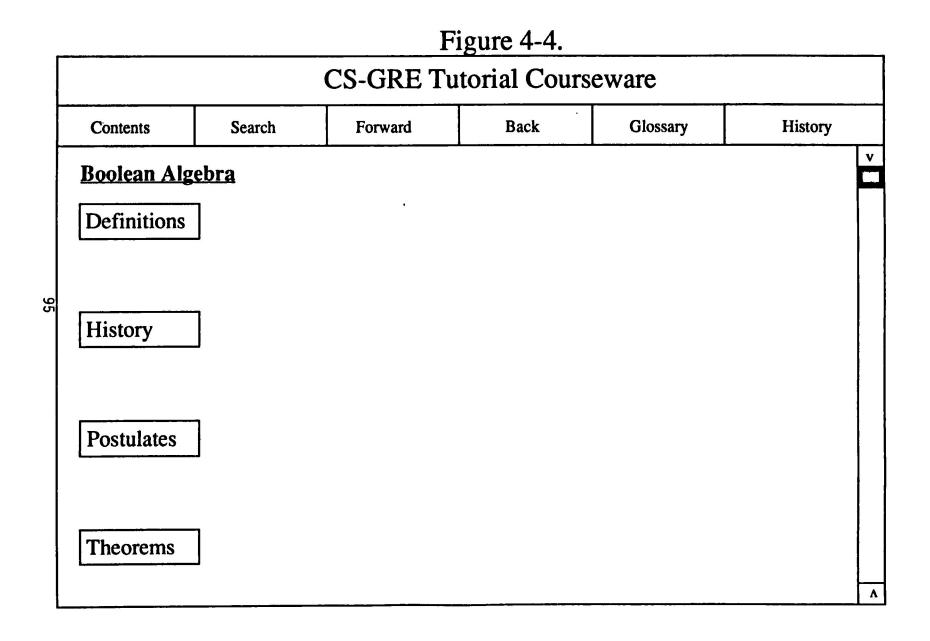

| 4-4.  | CS-GRE Tutorial Courseware Introduction<br>Selections    |

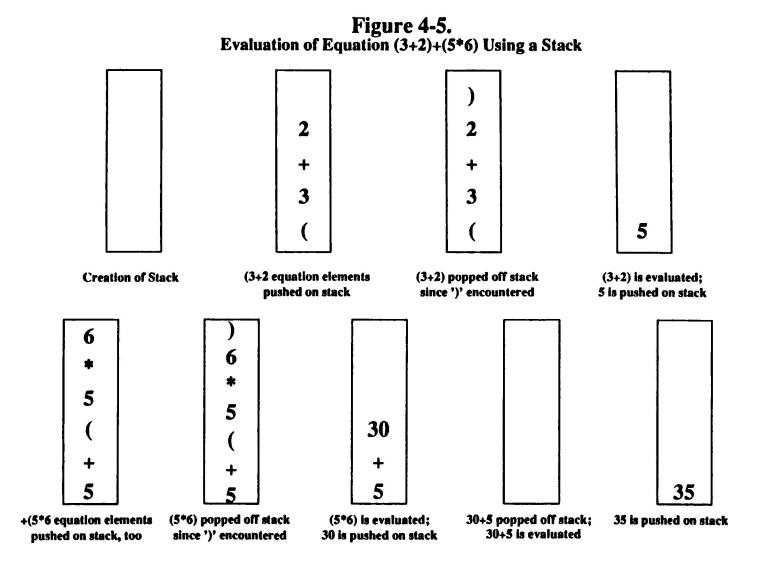

| 4-5.  | CS-GRE Tutorial Courseware Introduction<br>Selections    |

## LIST OF TABLES

| Table |          |         |     |            |          |        | Page |

|-------|----------|---------|-----|------------|----------|--------|------|

| 2-1.  | Computer | Science | GRE | Evaluation | Results  |        | 6    |

| 2-1.  | Computer | Science | GRE | Evaluation | Results, | cont'd | . 7  |

•

## CHAPTER 1

## INTRODUCTION

This thesis presents the design and implementation of interactive courseware for the Computer Science Graduate Record Examination (CS-GRE). The motivation for the courseware arose after Dr. Kenneth Perry administered the Computer Science GRE to Clark Atlanta University (CAU) students. They did not perform as well as expected. The test results are in Chapter 2. The software provides tutorial information on four subject areas: Computer Design, File Structures, and Discrete Mathematics. Structures, Data feedback indicates the CS-GRE tutorial using Initial interactive multi-media modalities to present many basic computer science concepts does help in preparing students for the GRE Computer Science Exam.

The tutorial courseware began as a group project. We tested 17 CAU students on a previously given Computer Science GRE for questions numbered 1 through 39; and, the students did not perform very well. A group of students who needed to prepare for the actual GRE Computer Science Exam realized there was no commercially-available tutorial software for this particular exam. Amazing, since there are other software

packages on the market for other GRE subject exams. After all, computer science is the discipline upon which software originates.

Consequently, this thesis was initiated after one student realized the need for the tutorial courseware based on the CAU students test scores and decided to make one. After analyzing previous CS-GRE exams and several meetings with my advisor, Dr. Kenneth Perry, we decided on the computer science subjects to be included in the package: Data Structures & Algorithm Analysis, Computer Organization, File Structures, Operating Systems & Computer Architecture, Discrete Mathematics, and A large percentage of the Computer Science GRE Pascal. questions cover material taught within these particular I prepared in-depth summaries of many important subjects. concepts reviewed within each course. Clayton Collie, another Clark Atlanta University (CAU) graduate student, contributed the report on File Structures.

I designed the courseware structure and programmed the computer interface using an event-driven software package, Microsoft Visual Basic, which is an application programmers interface language for Microsoft Windows environments. (An executable copy of the software is included in Appendix A.) The software is currently available to students in the CIS Computer Lab. One objective of the tutorial courseware is to target the largest install base which is the personal computer market and provide the software at an affordable price for

students.

Chapter 2 presents and analyzes the Computer Science GRE score results when 17 CAU students took the sample exam. Chapter 3 introduces the design philosophy used to develop this tutorial courseware, gives a detailed description of the software design, and discusses its features. Chapter 4 provides a list of potential future enhancements for the next version and concludes the tutorial courseware thesis.

## CHAPTER 2 STUDENT COMPUTER SCIENCE GRADUATE RECORD EXAM TEST RESULTS

This chapter provides an extensive discussion of the CAU student CS-GRE test results. Based on the results, the CS-GRE tutorial courseware was created to increase our students' test scores. The courseware reviews information most often asked within the Computer Science Graduate Record Examination.

An actual Computer Science Graduate Record Examination (GRE) was administered to 17 Clark Atlanta University (CAU) students in the spring of 1993. Dr. Kenneth Perry, a CAU Computer Science professor, officiated the exam. There is a total number of 80 questions within the Computer Science GRE, and the exam is given over a 4 hour time period. However, the CAU students were only required to answer questions 1-39 due to the time factor of 2 hours. The CAU students comprised both graduates and undergraduates.

The graduate students represented a diverse group in terms of their different ages, interests, occupations, work experience, undergraduate majors, and undergraduate colleges. Most of the graduate students came from other schools. The undergraduate colleges they attended were among Tennessee

State University, Spelman College, Rensselaer, and Clark Atlanta University. Their undergraduate majors varied from Computer Science and Management Information Systems to Physics. Their current graduate grade point averages had to be above 3.0 since they remained in excellent standing with CAU's Computer & Information Systems Department. The range of ages is from 22 years to 37 years.

There were two graduate students who attended CAU as undergraduates. Their undergraduate majors were Physics and Computer Science. Their undergraduate college grade point averages were 3.0 and 3.9, respectively. Both students earned high school grade point averages above 3.5.

The undergraduates also represented a diverse group. Several students were Computer Information Systems majors, while others were Computer Science majors. Their classifications were either junior or senior. Their current college grade point averages ranged from 2.77 to 3.75. In reference to their high school statistics, their grade point averages ranged from 2.7 to 3.8. Their SAT scores ranged from 790 to 1080.

Given the diverse group of students taking the exam, the results were very revealing. The evaluation results may be viewed in Table 2-1. The rows list the number of the specific exam questions from 1 to 39. The columns give the assigned student identification numbers from 1 to 17. The average of all the students' scores was approximately 38% correct, 34%

# Table 2-1.Computer Science GREEvaluation Results

Assigned Student ID Number

|          |    | 10015 | III U I | Juuu |   | <u>/ 1 1 U I</u> | IIII |   |   |   |    |    |    |    |    |    |    |    |

|----------|----|-------|---------|------|---|------------------|------|---|---|---|----|----|----|----|----|----|----|----|

|          |    | 1     | 2       | 3    | 4 | 5                | 6    | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 |

|          | 1  | R     | R       | R    | R | R                | W    | R | R | R | R  | R  | R  | R  | R  | R  | R. | R  |

|          | 2  | w     | W       | W    | R | N                | N    | N | R | W | R  | R  | R  | R  | R  | R  | R  | R  |

|          | 3  | w     | N       | W    | N | W                | w    | R | W | W | R  | W  | W  | R  | R  | W  | W  | R  |

|          | 4  | R     | W       | R    | N | W                | W    | W | R | W | R  | N  | R  | R  | R  | R  | W  | R  |

|          | 5  | W     | R       | W    | R | ₩                | w    | R | R | R | ¥  | W  | R  | ĸ  | R  | R  | R  | R  |

|          | 6  | W     | W       | W    | W | W                | R    | W | R | W | W  | R  | W  | R  | W  | R  | W  | R  |

| Number   | 7  | R     | R       | W    | W | W                | W    | R | R | W | R  | R  | W  | W  | R  | R  | R  | R  |

| nb       | 8  | R     | R       | *    | R | R                | W    | N | R | N | W  | W  | ¥  | W  | W  | ¥  | N  | R  |

| Iul      | 9  | W     | W       | W    | N | W                | W    | N | R | W | R  | R  | W  | R  | R  | R  | W  | ¥  |

| 10. 1111 | 10 | N     | R       | W    | N | R                | N    | N | R | R | R  | W  | W  | N  | N  | W  | W. | R  |

| 0        | 11 | R     | W       | W    | N | R                | R    | W | W | R | R  | R  | W  | R  | R  | R  | R  | R  |

| Question | 12 | N     | N       | W    | N | N                | N    | W | W | W | N  | N  | N  | N  | N  | N  | N  | N  |

| ne       | 13 | W     | W       | ¥    | R | N                | W    | W | R | W | R  | W  | W  | R  | W  | W  | W  | N  |

| 0        | 14 | N     | N       | ¥    | N | W                | W    | N | R | N | N  | N  | Ŵ  | R  | N  | R  | R  | R  |

|          | 15 | *     | W       | W    | W | N                | N    | W | R | W | N  | N  | R  | R  | R  | W  | R  | Ŕ  |

|          | 16 | W     | R       | ₩    | R | N                | W    | R | R | W | R  | R  | R  | R  | R  | R, | R  | R  |

|          | 17 | R     | R       | R    | W | R                | W    | R | R | R | R  | R  | R  | R  | R  | R  | R  | R  |

|          | 18 | R     | R       | N    | R | R                | N    | N | W | R | N  | W  | R  | R  | R  | R  | R  | N  |

|          | 19 | N     | W       | W    | N | W                | W    | W | R | W | N  | N  | W  | W  | N  | W  | N  | R  |

|          | 20 | w     | N       | W    | N | N                | W    | w | R | w | N  | N  | w  | R  | R  | W  | R  | R  |

R = Correct

W = Incorrect

N = Never Seen

σ

# Table 2-1.Computer Science GREEvaluation Results, cont'd.

**Assigned Student ID Number**

| 1        |    | 1 | 2 | 3     | 4 | 5 | 6 | 7 | 8                 | 9 | 10 | 11 | 12 | 13 | 14                 | 15 | 16 | 17 |

|----------|----|---|---|-------|---|---|---|---|-------------------|---|----|----|----|----|--------------------|----|----|----|

|          | 21 | N | N | w     | N | w | w | w | w                 | w | N  | N  | N  | w  | N                  | W  | w  | R  |

|          | 22 | N | R | w     | N | N | N | N | R                 | W | w  | N  | w  | W  | w                  | W  | w  | R  |

|          | 23 | N | N | W     | N | R | W | W | ĸ                 | W | R  | N  | W  | R  | N                  | R  | R  | R  |

|          | 24 | N | R | R     | N | W | N | W | W                 | R | N  | N  | R  | R  | W                  | W  | W  | R  |

| -        | 25 | w | W | R     | W | R | W | R | R                 | R | N  | N  | W  | N  | W                  | R  | R  | R  |

| pel      | 26 | N | W | W     | N | W | N | W | R                 | W | R  | w  | W  | N  | N                  | w  | W  | R  |

| E        | 27 | N | N | w     | N | N | N | N | W                 | W | N  | N  | N  | W  | N                  | N  | W  | R  |

| Number   | 28 | R | R | W     | R | R | R | W | R                 | R | R  | W  | Ř  | R  | N                  | R  | R  | R  |

|          | 29 | R | N | W     | R | N | N | N | R                 | R | N  | N  | W  | R  | N                  | ·N | W  | R  |

| IOL      | 30 | N | N | w     | R | w | N | N | R                 | W | R  | N  | N  | W  | N                  | W  | W  | R  |

| Question | 31 | R | R | R     | R | М | R | N | R                 | W | R  | W  | W  | R  | W                  | W  | w  | R  |

| ne       | 32 | N | N | R     | N | N | N | N | R                 | N | N  | W  | W  | R  | W                  | W  | W  | N  |

| 0        | 33 | R | N | N     | W | W | W | W | R                 | W | W  | W  | W  | R  | N                  | W  | W  | N  |

|          | 34 | R | N | N     | W | W | W | W | R                 | W | w  | W  | R  | R  | N                  | ·R | N  | R  |

|          | 35 | N | N | w     | R | W | N | N | R                 | W | R  | N  | N  | R  | R                  | W  | W  | R  |

|          | 36 | N | W | W     | N | N | N | N | R                 | W | R  | R  | W  | R  | W                  | w  | W  | R  |

|          | 37 | W | W | W     | R | N | N | N | R                 | W | R  | N  | R  | N  | N                  | N  | W  | N  |

|          | 38 | N | N | N     | N | R | N | W | R                 | R | N  | N  | N  | N  | N                  | N  | N  | N  |

|          | 39 | R | N | N     | N | N | N | W | R                 | R | N  | N  | W  | W  | W                  | N  | N  | R  |

|          |    |   |   | Corre |   |   |   |   | / = Inc<br>otal W |   |    |    |    |    | ever Se<br>N = 188 |    |    |    |

incorrect, and 28% of the material had never been seen before.

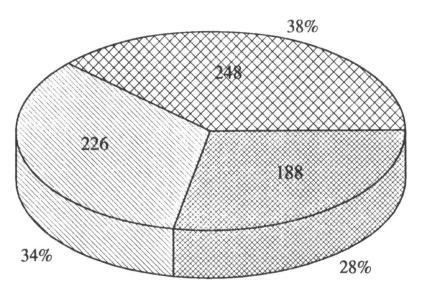

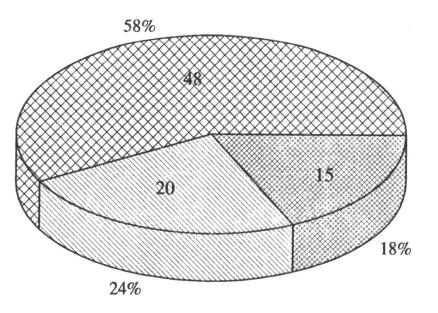

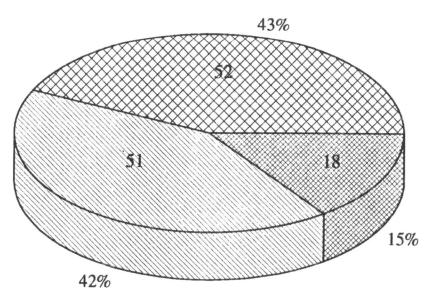

To be exact, 248 answers were correct, 226 were incorrect, and 188 were unknown meaning the material was unfamiliar. Please view Figure 2-1 for a table representation of the approximate percentages. These figures are rather surprising and disappointing.

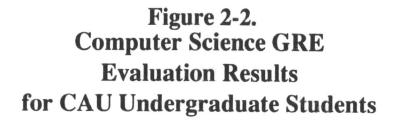

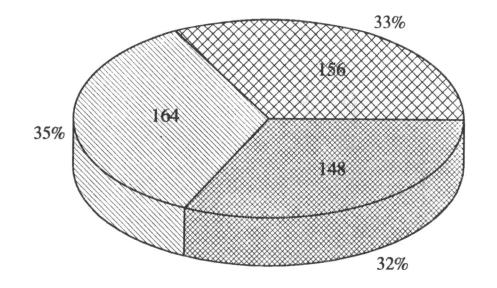

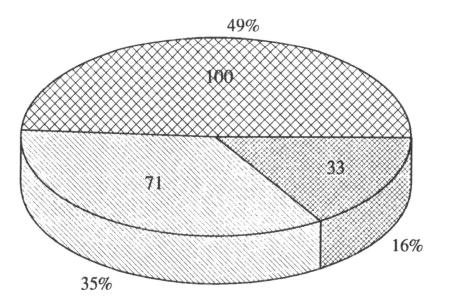

The CAU undergraduates answered 156 correct, 164 incorrect, and 148 unknown. The respective percentages of 33%, 35%, and 32% may be seen in Figure 2-2. The graduates did perform better than the undergraduates. Figure 2-3 lists the graduate students' performance as a whole. The five graduates together scored 100 correct, 71 incorrect, and 33 unknown. The respective percentages are 49%, 35%, 16%. The two graduate students who attended CAU as undergraduates scored 48 correct, 20 incorrect, and 15 unknown. The percentages for these scores are 58%, 24%, and 18%, respectively, and are shown in Figure 2-4. The three graduates who attended colleges other than CAU scored 52 correct, 51 incorrect, and 18 unknown. Figure 2-5 gives the percentages for these scores of 43% correct, 42% incorrect, and 15% unknown.

These scores prove our students as a whole do not perform very well on the Computer Science GRE. As a result of this discovery, something has to be done to improve the scores of our students, and I am the person who wanted to make a difference to raise our test scores and performance.

Figure 2-1. Computer Science GRE Evaluation Results for All Students

🖾 # Correct 🖾 # Incorrect 🖾 # Never Seen

Figure 2-3. Computer Science GRE Evaluation Results for CAU Graduate Students

🖾 # Correct 🖾 # Incorrect 🖾 # Never Seen

Figure 2-4. Computer Science GRE Evaluation Results for CAU Graduate Students from CAU

🖾 # Correct 🖾 # Incorrect 🖾 # Never Seen

# Figure 2-5. Computer Science GRE Evaluation Results for CAU Graduate Students from Other Schools

🖾 # Correct 🖾 # Incorrect 🖾 # Never Seen

The poor performance may be attributed to the exam covering material which is not being reviewed thoroughly within a classroom environment. The incorrect answers and the unfamiliar material are evidence the exam analyzes material which is either difficult or foreign to the students. In order for the students to perform well, this unfamiliar and difficult material must be thoroughly reviewed during preparation for the Computer Science GRE. The CS-GRE tutorial courseware is developed to cover the unfamiliar subject matter and to improve students' scores.

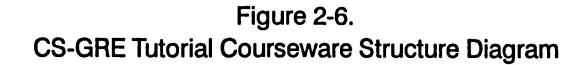

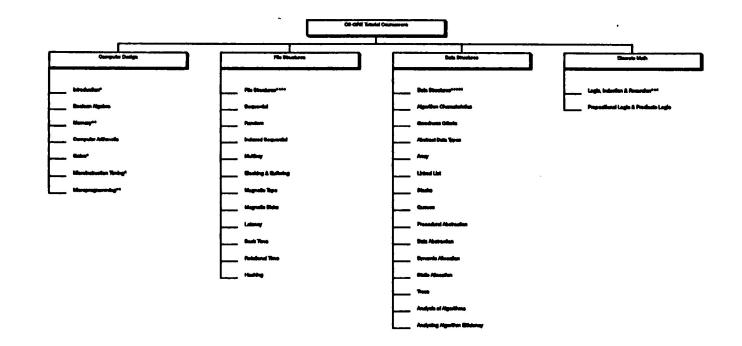

After reviewing the GRE, we identified six courses from which most of the information originates. These six courses include Data Structures & Algorithm Analysis, Computer Organization, File Structures, Operating Systems & Architecture, Pascal, and Discrete Mathematics. Five courses are reviewed in the package within four modules. Pascal is the sixth course not yet included; but, it is being developed as a fifth module. The four modules implemented include Computer Design, File Structures, Data Structures, and Discrete Mathematics.

The structure diagram for the modules may be seen in Figure 2-6. Each topic provides narrative information within a window. One asterisk (\*) indicates a diagram accompanies the narrative. Two asterisks (\*\*) indicate animation or a demonstration is shown. Three asterisks (\*\*\*) show where a future diagram may be included in the next version. Four

asterisks (\*\*\*\*) indicate where future animation or video may be demonstrated. Five asterisks (\*\*\*\*\*) show where future sound may be added.

The next chapter on Program Design reviews the material included in the tutorial courseware. All four modules, Computer Design, File Structures, Data Structures, and Discrete Math, are reviewed.

.

## CHAPTER 3 PROGRAM DESIGN

This chapter discusses the design philosophy used in creating the tutorial courseware and gives a detailed description of the software design features. The material presented familiarizes the reader with Computer Organization, Operating Systems & Architecture, File Structures, Data Structures & Algorithm Analysis, and Discrete Mathematics courses taught within a university's computer science degree program.

The CS-GRE tutorial is divided into five main headings: Computer Design, File Structures, Data Structures, Discrete Math, and References. The software is designed using a hierarchical menu structure which includes submenus that can be nested up to six levels deep. This organizational structure within the tutorial software is used to present an overview of computer science in a clear, concise manner with related topics grouped together.

The software provides the user a general overview of computer science. The package lays a basic foundation to prepare a student for the Computer Science GRE Subject Exam

and increase our students' test scores.

In addition, the tutorial is intuitively designed to be simple and easy to use. The user may use either the mouse or the keyboard to review the tutorial. The menu items' windows may appear by either selecting the desired item with the mouse, or typing in a specific underlined letter from the menu items' title as a hotkey.

Visual Basic was chosen as the application programming tool because 1) our objective is to develop low-cost software for the largest installed base which is the PC market; 2) we want the software to run under Microsoft Windows since it is such a common computing environment; 3) Visual Basic is the fastest and easiest way to develop Windows applications; and 4) Visual Basic is the Applications Programmer Interface Language for all future Windows releases including Windows NT and greater.

The structure of the screens displayed in the tutorial is described.

## <u>Main Menu</u>

The Main Menu is displayed in Figure 3-1. The menu headings with the CS-GRE background screen are shown.

The Computer Design section includes the following menu items as shown in Figure 3-2. Several items are thoroughly discussed within this document.

| Computer Design                            |        | Science Graduate<br>Data Structures | D <u>c</u> tails |  |

|--------------------------------------------|--------|-------------------------------------|------------------|--|

| Introduction                               |        |                                     |                  |  |

| <u>B</u> oolean Algebra<br>M <u>e</u> mory |        |                                     |                  |  |

| <u>Computer</u> Arithme                    | etic 🕨 | Cr All                              |                  |  |

| Gates                                      |        |                                     |                  |  |

| Instruction Set                            | _      |                                     |                  |  |

| MicroInstruction<br>Microprogrammir        |        |                                     |                  |  |

| Register File                              |        |                                     |                  |  |

| yon Neuman Arch                            |        |                                     |                  |  |

|                                            | Gra    | duate                               |                  |  |

|                                            | Re     | cord                                |                  |  |

|                                            |        | . xam                               |                  |  |

## File Structures

The File Structures section is shown in Figure 3-3 and discussed below in section B.

The Data Structures menu in Figure 3-4 illustrates the following topics within the menu that pertain to this subject.

## Discrete Math

In Figure 3-5, this Discrete Math menu shows the two subjects into which the topic is divided. Logic, induction, and recursion are discussed in the first topic. Propositional logic and predicate logic represent the second topic.

## Details

The Details menu in Figure 3-6 presents the author and references sections. The tutorial author is given in About CS-GRE. The references section lists all actual references used to gather the information in this tutorial.

| -                      | Computer        | Science Graduate | Record Exam           | ing di ditagok nyang di 💽                                     |   |

|------------------------|-----------------|------------------|-----------------------|---------------------------------------------------------------|---|

| <u>Computer Design</u> | Eile Structures | Data Structures  | Discrete <u>M</u> ath | D <u>e</u> tails<br><u>A</u> bout CS-GRE<br><u>References</u> |   |

|                        | omput           | ar               |                       |                                                               | 4 |

|                        | Dciena          | :e               |                       |                                                               |   |

|                        | Gra             | duate            |                       |                                                               |   |

|                        | Re              | ecord            |                       |                                                               |   |

|                        |                 | *<br>•<br>• xam  |                       |                                                               |   |

### A. Computer Design

This section presents an overview of the von Neumann machine, modern computers, the central processing unit, memory systems, microinstruction sequencing, and Boolean algebra. The modern computers and memory systems discussion includes diagrams which enable the reader to understand the organization of a computer, several memory types, and different cache schemes. Several questions and answers are given to demonstrate a variety of caching strategies. The discussion gives the reader a general understanding of computer organization and operating system architecture.

## A.1. Introduction

The four basic functions of a computer are: data processing, data storage, data movement, and control. A computer includes a set of instructions that when used together as a group allows the user to perform any conceivable data-processing task. This allows the use of computers in many fields whether the user plans to develop applications, perform research, design models, or manipulate records. Therefore, computers include an ample number of instructions to move data to and from memory; perform arithmetic and logic instructions; provide instructions for checking status information which enables the computer to render decisionmaking capabilities; and, perform input and output operations. General-purpose computers contain high-speed primary memory,

auxiliary memory, a central processing unit (CPU), and an input/output (I/O) system.

## A.2. IAS Computer

John von Neumann built the Princeton's Institute of Advanced Studies (IAS) computer modeled after the Electronic Discrete Variable Automatic Computer (EDVAC) in the early 1950's. The IAS computer is referred to as a von Neumann machine and is still the basis for digital computers today. An important feature is that the program and data are represented in digital form in the computer's memory instead of the antiquated system of using large numbers of switches and cables to program a computer.

The IAS computer in Figure 3-7 contains five parts as follows: the memory, the ALU, the program control unit, and the input and output equipment. Properties of a von Neumann architecture include the storage of data and instructions in a single read-write memory; and, the contents of this memory are addressable by location, without regard to the type of data contained therein. Execution occurs in a sequential fashion from one instruction to the next, unless explicitly modified.

## A.3. Modern Computers

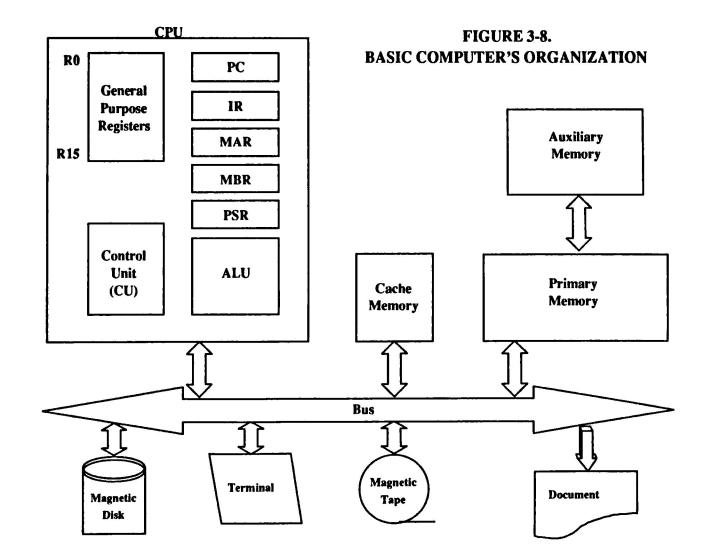

There are four main structural components to a computer: the central processing unit (CPU), main memory, input/output (I/O), and the system interconnections. Figure 3-8 presents a basic computer's organization. The CPU controls the

## FIGURE 3-7. THE ORIGINAL VON NEUMAN MACHINE

operation of the computer and performs its data processing functions. Main memory stores data. Input/output moves data between the computer and its external environment. The system interconnection provides some mechanism which supplies communication among the CPU, main memory, and I/O.

#### A.4. CPU

The CPU or central processing unit shown in Figure 3-8 is the section of a computer which handles the interpretation and execution of the programming instructions. The CPU consists of four major structural units: the ALU, the control unit, registers, and the CPU interconnections. The arithmetic and logic unit (ALU) performs the computer's data processing functions. The control unit controls the operation of the CPU. Registers provide storage internal to the CPU. CPU interconnections provide communication between the control unit, ALU, and registers. The CPU contains the arithmetic and logical unit (ALU), control unit (CU), instruction register (IR), memory address register (MAR), memory buffer register (MBR), program counter (PC), general purpose registers, buses, and program status register (PSR).

#### A.4.a. ALU

The ALU contains electronic circuits which receive and operate on the data. The ALU exercises the basic arithmetic operations of addition, subtraction, shift operation, and logical operations, i.e. AND, OR, and COMPLEMENT. The ALU typically consists of a binary adder and binary shifter. The

adder inputs two binary numbers and produces a binary sum for output. The shifter changes the position of the bits either to the left or to the right. The shifter and the adder can be used together to execute multiplication. Complimentary addition is used to perform subtraction. Division is achieved by repeated subtraction and shifting.

#### A.4.b. Control Unit

The control unit (CU) manages the flow of data between all other devices. It also translates the operations represented by the program instructions. Furthermore, the CU sends signals to the devices which perform these operations. The CU directs both the flow of instructions and data to and from memory. The flow of both the instructions and data to memory is termed the store cycle; and, the flow of both from memory to various devices is defined as the fetch cycle or read cycle.

Before program execution begins, the PC must receive the memory address of the first instruction to be executed. The CU then continues program execution, or rather evaluates instruction execution cycles. An instruction execution cycle begins with the read cycle of an instruction. The cycle ends when a result is obtained. As the instruction is moved or copied from primary memory, the CU interprets the instruction. During this interpretation, the CU transmits the appropriate signals to the various devices necessary for processing the instruction. Also, the CU sends the necessary data to be used

in the instruction to the ALU. Upon completion of the operation, the CU directs the result from the ALU into the appropriate memory cell or processor register.

#### A.4.b.1. Processor Registers

Instructions for moving data to and from memory are essential. Most information in a computer is stored in memory while the computations are done in the CPU and stored in the processor registers. The system must have the capability of moving data between memory and the processor registers if the system is to be fully effective and useful.

A CPU instruction cycle performs several different operations. The cycle first fetches the next instruction from memory and places it in the instruction register. The program counter changes to hold the address of the next instruction to be executed. The instruction is decoded. Data is fetched from memory if necessary. The instruction is executed, and the results are stored. Then, the CU returns to the first step and repeats the process until all instructions have been executed.

#### A.4.b.2. IR, MAR, & MBR

The instruction register (IR) is the register within the CPU which holds the current instruction. The memory address register (MAR) holds an address of an instruction or data to be read or written; while, the memory buffer register (MBR) stores the instruction or data.

#### A.4.c. Program Counter

The program counter (PC) is designated as a special register which contains the address of the next instruction to be executed. As the instruction is retrieved from memory and placed in a special register within the CPU, the PC is updated. The PC is incremented by a number equivalent to the length of the instruction in bytes. The number of bytes required to store the instruction in memory is the length of the instruction.

Since memory is a linear array, the PC normally stores the address of the next sequential instruction to be executed. An exception arises when the current instruction is a branch or transfer of control instruction. In this situation, the CPU discerns the instruction to be executed is not the next sequential instruction. Therefore, the PC is updated to store the branch address for the next instruction to be executed. A.4.d. General Purpose Registers

General purpose registers supply local, high-speed storage for the processor. Registers function as discrete storage cells of some fixed length. Registers receive, hold, and transfer data as well as store addresses, but their primary use is to hold data temporarily. The advantage to using registers is that data can be processed more quickly than by accessing main memory.

#### A.4.e. Program Status Registers

Program status registers (PSRs) contain status information which report the current state of the program in

execution. There are one or more PSRs within the CPU. PSRs provide information about the results obtained from instruction execution by using condition codes.

Almost every instruction execution records some information in the condition code. The condition code is just one type of status information. On the basis of this information, the programmer decides which actions to take next. Condition codes supply the following information: the result is zero, the result is negative, the result is positive, the result is out-of-range (overflow), and whether the arithmetic operations use "carry-out" or "borrow-into."

#### A.5. Memory Systems

This section presents an overview of memory systems including memory hierarchy, locality of reference, address space, primary memory, auxiliary memory, virtual memory, and cache memory. Cache memory includes a discussion on associative cache, direct-mapped cache, and set-associative cache. Five questions are given which represent several caching strategies.

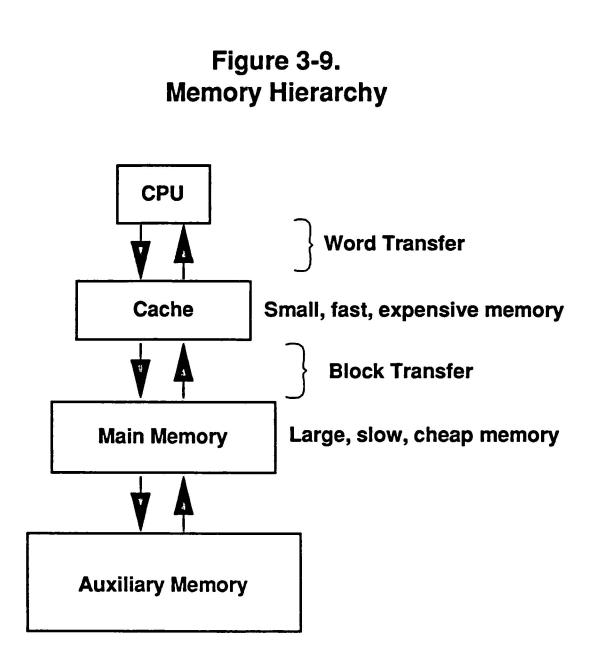

#### A.5.a. Memory Hierarchy

Whereas a virtual memory system shifts data between auxiliary memory and primary memory, cache organization moves data between primary memory and the CPU. Thus, each memory type involves a different level in the memory hierarchy system. Figure 3-9 displays the memory hierarchy. Within the computer memory hierarchy, programs and data are first stored

in auxiliary memory. The cache holds those most heavily used parts of the program and data, while the auxiliary memory stores those parts the CPU is not presently handling. As a result, the CPU commands direct access to both cache and primary memory but not to auxiliary memory.

#### A.5.b. Locality of Reference

Locality of reference means references to memory at any given time interval tend to be confined within a few localized memory cells. Locality of reference occurs since a typical computer program flows sequentially from top to bottom, encountering frequent program loops and procedure calls. Upon a program loop's execution, the CPU repeatedly refers to the set of instructions which form the loop. Every time a procedure is called, its own set of instructions must be moved from memory. The main idea is that when a word is referenced, it is brought from the large, slow memory into the cache. Therefore, the next time it is needed, it will be retrieved quickly. Loops and procedures then localize references to memory. References to data stored in primary memory also tend to be localized.

#### A.5.c. Address Space

During the execution of the program, each address the CPU references undergoes address mapping. This mapping transforms a virtual address into a physical address. The virtual address only demonstrates meaning in reference to the page's domain, whereas the physical address functions as the memory

cell's actual address. A programmer evaluates a virtual address. The set of all virtual addresses completes the address space. An address in primary memory designates a location or physical address. The entire set of such locations specifies memory space. Therefore, the address space is the set of addresses programs generate as they reference instructions and data. The memory space is characterized by the actual primary memory locations directly addressable for processing.

#### A.5.d. Primary Memory

Primary memory or main memory consists of two state components which can represent two measurable, distinct states. The binary numbering system of 0 and 1 is used to represent its two states. The binary digit symbol 0 represents one state, while 1 represents the other. Portions of a program or data are only brought into primary memory as they are needed for program execution. Primary memory performs at high speed and forms two organizational features: 1) each memory cell is the same size and, 2) each cell is uniquely referenced by its very own numeric address. A memory cell contains an address to indicate the cell's relative position in reference to some known position. The contents of the cell represent a numeric value or an alphanumeric character stored in a particular memory cell. These contents may be changed or used in an operation.

A.5.e. Auxiliary Memory

Auxiliary memory devices are used for backup storage. The most common auxiliary memory devices are magnetic disks, magnetic drums, and magnetic tapes. This particular kind of memory does not communicate directly with the CPU. Instead, information is moved to primary memory from which the CPU obtains the necessary instructions and data. Please review a basic computer's organization in Figure 3-8. Only programs and data the processor currently uses reside in primary memory. All other information is stored in auxiliary memory and is then transferred to primary memory on demand.

Figure 3-10 illustrates a memory model where the memory is represented by an array M of size N. The illustration shows the employment of addresses to reference memory cells. Each element within the array pertains to one memory cell. The cell size, N, varies according to the specifications the computer manufacturer chooses. The specifications must meet the needs of the program application for which the computer is to be used. Each index addresses a particular memory cell in array M. Any memory cell may be referenced when the index is switched to a specific value. With this method, the memory cell allows the placement of new data or the copying of old data.

#### A.5.f. Virtual Memory

The idea of executing a program while only a portion of the program remains in the primary memory is referred to as virtual memory. Virtual memory streamlines memory space since

## FIGURE 3-10. MEMORY REPRESENTED BY ARRAY M OF SIZE N

| •     | Address<br>each cell equals<br>the index of<br>the cell | To obtain<br>contents |

|-------|---------------------------------------------------------|-----------------------|

| M0    | 0                                                       | M(0)                  |

| M1    | 1                                                       | M(1)                  |

| M2    | 2                                                       | M(2)                  |

| Mi    | i                                                       | M(i)                  |

| M N-1 | N-1                                                     | M (N-1)               |

the user constructs a program with memory space equal to the combined sizes of the auxiliary and primary memory. The virtual memory system contains both hardware and software necessary to implement and manage virtual memory.

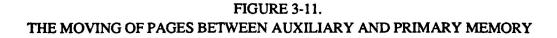

When a program is submitted for execution, the virtual memory system divides the program into equal parts or pages. Please review Figure 3-11 for the moving of pages between auxiliary and primary memory diagram. The pages are transferred between the primary and auxiliary memories. When program execution begins, the program's first page is moved into the first available primary memory block. A block of memory is a group of contiguous memory cells equivalent to the size of a page. During the program's execution, the virtual system transfers the next page to the same block of the primary memory from the auxiliary memory whenever the program's next page is required. The same method is followed for the program's necessary data. Primary memory contains separate blocks of information for both the program and its data.

#### A.5.g. Cache Memory

Cache memory is a fast memory where the active portions of the program and data are placed to reduce the average memory access time. As a result, the program's total execution time is reduced. Cache memory is situated between the CPU and the primary memory. Figure 3-8 shows the location of cache memory. This kind of memory possesses an access time

less than the primary memory access time by an average factor of five to ten. Leading as the fastest memory device in the memory hierarchy and approaching the speed of CPU devices, the use of cache memory has many advantages.

The fundamental idea of cache organization is to keep the most frequently accessed instructions and data in the fastest memory. Although the cache remains just a small fraction of primary memory's size, many memory requests are transmitted to the fast cache memory due to locality of reference.

The cache is examined whenever the CPU needs to access memory. If the CPU discovers the necessary instructions or data in the cache, the instructions or data are passed to the necessary device which made the request. However, if the instructions are not found, primary memory will then be accessed. A block of instructions or data containing the requested information is now transferred to the cache memory. This process ensures most future references to memory will find the required information within the fast cache memory. The hit ratio is determined by the percentage of hits of the memory references finding the requested information within the cache.

#### A.5.g.1. Different Cache Organizations

There are three different types of cache organizations: associative cache, direct-mapped cache, and set-associative cache. Associative cache and direct-mapped cache specify two different kinds of organization, while set-associative cache

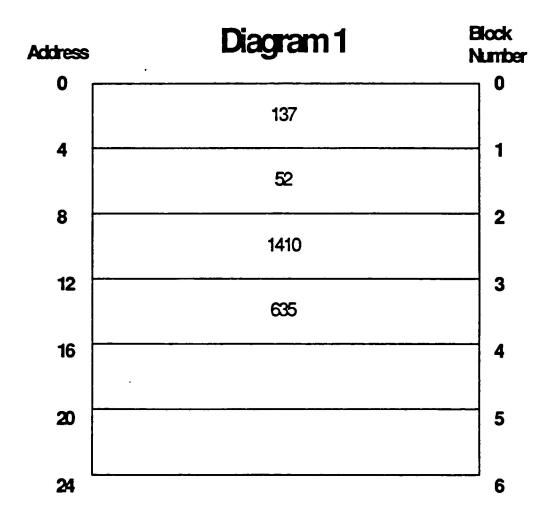

is a combination of the other two. For all three types, the memory is assumed to be  $2^m$  bytes. Please see Figure 3-12. The memory is divided into sequential blocks of b bytes equaling a total of  $2^m/b$  blocks. Each block contains an address representing some multiple of b. The block size, b, is usually a power of two.

The associative and direct-mapped caches have their own advantages and disadvantages. The direct-mapped cache is less complex, cheaper to build, and has a faster access time because the appropriate slot being found by indexing into the cache uses a portion of the address as the index. The associative cache supplies a higher hit ratio for any given number of slots.

A.5.g.1a. Associative Cache.

The associative cache consists of a number of slots or lines. Each slot or line contains one block and its block number along with a bit telling whether or not that slot is currently in use. In an associative cache, the order of the entries is random. When the system is reset, all the valid bits are set to zero which indicates there are not any valid cache entries. Figure 3-12 shows primary memory with  $2^{24}$  bytes partitioned into  $2^{22}$  4-byte blocks. The primary memory diagram contains the actual value of words which are used in an executing program. The values 137, 52, 1410, and 635 are random numbers chosen to represent the word values.

Figure 3-13 provides a diagram of an associative cache.

FIGURE 3-12. MEMORY WITH 4-BYTE BLOCKS.

.

## Diagram 2

### FIGURE 3-13. Associative Cache with 1024 Lines

| Valid          | Block Number | Value       |       |

|----------------|--------------|-------------|-------|

| 1              | 0            | 137         |       |

| 1              | 600          | 2131        |       |

| 1              | 2            | 1410        |       |

| 0              |              |             | 1 K   |

| 1              | 160218       | 290380      | Lines |

| 0              |              |             |       |

| _              |              |             | =     |

|                | <u> </u>     |             | ₩     |

| <b>→</b> 1 bit |              | → 32 bits → |       |

If the first program instruction references the 32-bit word at address 0, the microprogram will check all entries of the associative cache in search of an occupied entry containing block number 0. When the cache controller fails to find the entry, it will send a bus request to fetch word 0 from the primary memory. The word 0 is fetched from primary memory at address 0, and the controller then generates a valid entry for block number 0 which will contain the contents of word 0 within the cache. The associative cache diagram contains all words which have been referenced for execution of the program's instructions. The block numbers 0, 600, 2, and 160218 are random block numbers chosen to reference the program's instructions. The values 137, 2131, 1410, and 290380 are randomly chosen values for the words used to execute the program. If a word is needed again, it is then taken from the cache which eliminates the need for a bus operation.

When more cache entries are marked as occupied or valid, the entire program and its data will eventually appear in the cache. Since the program will be running at high speed at this particular point, there will not be any need to make any memory references over the bus. At some specific point, the cache becomes full; and, an old entry will have to be removed to create space for a new one.

The associative cache is distinguished from other types since each slot contains a block number and its entry. When

a memory address is presented, the microprogram computes the associative block number and finds the block number in the cache. To prevent a linear search from being done, the associative cache uses special hardware which compares every entry to a given block number simultaneously as opposed to exercising a microprogram loop. This hardware causes the associative cache to be quite expensive.

#### A.5.g.1b. Direct-Mapped Cache

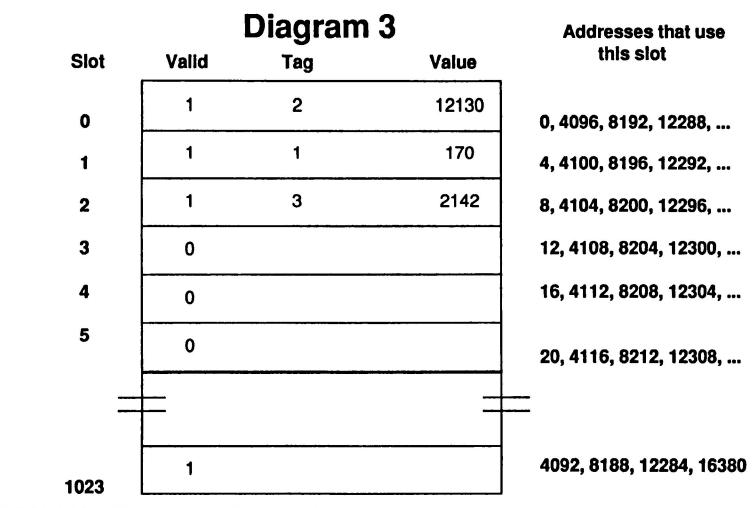

Conversely, the direct-mapped cache was created to reduce the cost accompanying associative cache memory. Direct-mapped cache prevents a search from being done by moving each block in a slot whose slot number can be easily calculated from the block number. The slot number is the block number modulo the number of slots. Figure 3-14 shows a pictorial representation of this example. With 4-byte word blocks and 1024 slots, the slot number for the word at address A is (A/4) modulo 1024. So the words at 0, 4096, 8192, etc. would map onto slot 0, while the words at 4, 4100, 8196, etc. would map onto slot 1.

This eliminates the problem of searching every slot number, but direct-mapped caches must reveal which of the many words mapped into a given slot are currently occupying that particular slot location. One may be able to tell by placing part of the address in the cache within the tag field. The tag field is the part of the address which cannot be computed from the slot number.

Let us consider another example, suppose you have an

FIGURE 3-14. A Direct-Mapped Cache with 1024 Slots of 4 bytes each

instruction at address 8192 which moves the word at 4100 to Within Figure 3-14, 1024 blocks have been created 12296. using the total block numbers modulo the cache size. The block number corresponding to 8192 is computed by dividing 8192 by 4 which equals 2048. The 12 bit binary representation for 2048 in binary form is 100000000000. The slot number is computed by taking 2048 modulo 1024 which equals 0. This is the same as using the low-order 10 bits of 2048. The upper 12 bits contain a 2, which becomes the tag. The block number for 4100 is computed by dividing 4100 by 4 which equals 1025. The 12 bit binary representation for 1025 is 01000000001. The slot number is 1 since 1025 modulo 1024 equals 1; and, the low-order 10 bits contain 1. The upper 12 bits of 1025 contain a 1; the tag then equals 1. The block number for 12296 is calculated by dividing 12296 by 4 which equals 3074. The 12 bit binary representation for 3074 is 11000000010. The slot number equals 2 since 3074 modulo 1024 is 2; and, the low-order 10 bits holds a 2. The upper 12 bits equal 3 which becomes the tag value. Figure 3-14 displays the cache after the evaluation of all three addresses.

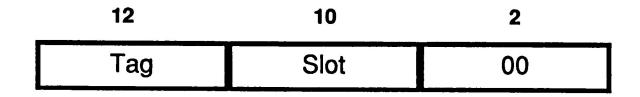

Please view Figure 3-15 to fully understand how the address is divided. The low-order two bits are always set to 0 since the cache works with whole blocks; and, these bits are multiples of the block size. In this example, the block size is 4 bytes; the slot number is 10 bits; and, the tag is 12 bits. For maximum efficiency, hardware should be built which

# **Diagram 4**

FIGURE 3-15.

Calculation of the slot and tag from a 24-bit address.

extracts the slot number and tag from any memory address.

Additional problems will occur since multiple blocks map into the same cache slot. If two words both have addresses which map into the same slot, the word which was processed last would occupy the cache while the word processed first would be discarded. The direct-mapped cache performance is degraded if many words are being mapped to the same slot. A.5.g.1c. Set Associative Cache

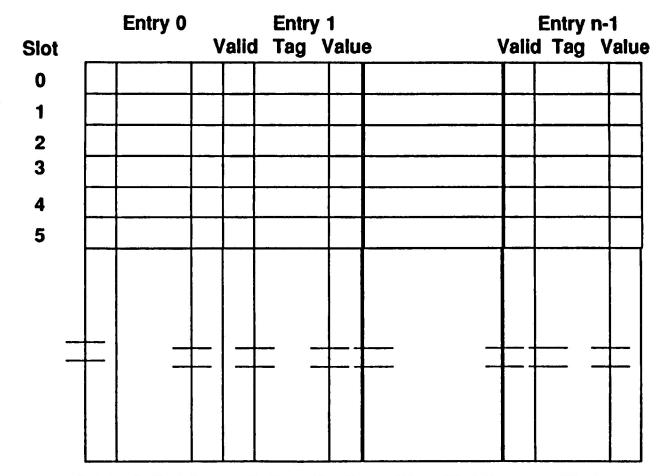

Set associative cache provides a solution to problems which arise from associative and direct-mapped cache. It offers a direct-mapped cache with multiple entries per slot. The set associative cache combines associative and directmapped caches. Please view Figure 3-16 for a pictorial If the number of slots is reduced to 1, all representation. the cache entries will be in the same slot. Therefore, they would have to be distinguished entirely by their tags since they all map into the same address. This distinction is similar to an associative cache. If n=1, then that resembles direct-mapped cache with entry one per slot. a A.5.g.2. An Explanation of the Cache Questions & Answers

The questions selected provide an illustration of different caching strategies. There are five questions within the tutorial which are actual questions taken from a previously given Computer Science GRE.

The first question asks for the major disadvantage of unpaged caches. An unpaged cache or read-ahead cache links

**Diagram 5**

FIGURE 3-16. A Set Associative Cache with n Entries per Slot.

disk domains, or fields, with the start address of the read request and proceeds for a particular length. The major disadvantage of an unpaged cache is cache domains, or fields, are permitted to hold repetitious data. A cache domain is always loaded beginning with the first address of the read request.

Yet, the recently entered data may be required for the following read requests; and, subsequent read requests may begin with data that is partially located in the cache domain. A problem arises when the request cannot be completed since only part of the data for the request is in the cache. Therefore, another cache domain must be filled from the disk which may very well lead to the storage of redundant data in the cache.

Unpaged or read-ahead caching demands a more complex algorithm for handling input and output, especially when a write request is submitted. The correct cache domain has to be found to update the file; and, then the cache domain containing unnecessary repetitious data must be removed to resolve the problem.

The second question pertains to cached and interleaved memory models. Cached and interleaved memories are methods of increasing the speed of memory access time between CPUs and slower RAM. The question asks which memory models improve performance the most, or are best suited, for which particular programs. The choices include: 1) cached memory is best

suited for small loops; 2) interleaved memory is best suited for small loops; 3) interleaved memory is best suited for large sequential code; and, 4) cached memory is best suited for large sequential code.

The answer involves choices 1 and 3. Caches are small in relation to the size of memory and a small loop would fit within a cache to decrease the accesses to slower RAM. Interleaved memory accesses RAM in parallel sequential memory blocks. Branching occurs seldom with large sequential code; therefore, each sequential piece read from slow RAM is fully utilized.

On the contrary, choices 2 and 4 are false. A small loop would cause frequent branching; and, interleaved memory would reaccess RAM without using all the previously read information from the prior read request. Large sequential code permits the access of new addresses which results in more RAM read requests and the decrease of cache performance.

Third, a memory system with the following parameters is evaluated: the cache access time,  $T_c$ , is 100 nanoseconds, and the main memory access time,  $T_m$ , is 1200 nanoseconds. If you desire effective or average memory access time less than 20% higher than cache access time, the hit ratio for the cache needs to be at least 98%.

The following formula provides an effective system access time,  $T_s$ :  $T_s = HT_c + (1-H)T_n$ . H is the hit ratio expressed from .80 to .95 up to 100. Therefore, 100H + 1200(1-H) needs

to be less than or equal to  $T_c + (.20 \times T_c)$  which equals 120 nanoseconds, or 20% more than the cache access time. Furthermore, 100H + 1200 - 1200H  $\leq$  120 and H  $\geq$  (1100  $\div$  1080) which equals .98.

The fourth question concerns cache and main memory. Assume the cache and main memory access times are 100 and 1200 nanoseconds. Some market survey denotes the average cost per bit of cache memory,  $C_c$ , is .0002 cents per bit, and the average cost per bit of main memory,  $C_m$ , equals .00001 cents per bit. The cost of a 1 megabyte memory system rounded to the nearest 10 dollars using a cache hit ratio of at least 98% would be \$230.

The hit ratio is assumed to be 98%. The optimal cache memory size is not possible to obtain. The size of the cache other than the hit ratio is affected by several other factors including the application's environment, the work load, and the design considerations involving the chip and board area.

Generally, cache sizes vary from 1K to 128K for a 1 megabyte, MB, system depending upon the desired hit ratios. Suppose the following experimental results involving the hit ratio versus the cache memory size for a 1 MB memory system occur for the application and work load being considered:

| Cache size per 1MB memory | Application hit ratio |

|---------------------------|-----------------------|

| 1K                        | .75                   |

| 32K                       | .80                   |

| 64K                       | .85                   |

| 96K                       | .90                   |

| 128K                      | .95                   |

| 196K                      | .96                   |

| 256K                      | .98                   |

According to the table, the desired 98% hit ratio requires 256K of cache memory. Therefore, the cost of a 1MB system follows:

> C = cost of main memory + cost of cache memory = (2<sup>20</sup> x 8 bits x .00001 cents/bit) + (2<sup>18</sup> x 8 bits) x (.0002 cents/bit) = \$(.00001 x 2<sup>21</sup>) + \$(.0002 x 2<sup>20</sup>) = \$20.97 + \$209.72 = \$230.69

Coincidentally, cache equals the same amount as main memory. The fifth question asks for the hit ratio of a cache if a system performs memory access at 30 nanoseconds with the cache and 150 nanoseconds without it. Suppose the cache uses a 20 nanosecond memory. The following formula calculates the memory access, M, using the hit ratio, H, the cache speed, C, and the ram speed, R: M = H × C + (1-H) × R.

> $30 = H \times 20 + (1-H) \times 150.$  30 = 20H + 150 - 150H = -130H + 150  $H = 130 \div 120 = 26 \div 24 = 13 \div 12 =$ 92% approximately.

More questions will be added as future work.

A.6. Microinstruction Sequencing

A basic ALU cycle sets up the A and B ALU input latches, gives the ALU and shifter time to do their work, and stores the results. These steps must occur in that sequence. To achieve the correct event timing, we use a four-phase clock. A four-phase clock is a clock with four subcycles.

The key events during each of the four subcycles are as follows:

- 1. Load the next microinstruction to be executed into the MIR.

- 2. Gate the registers onto the A and B buses and capture them in the A and B latches.

- 3. Now that the inputs are stable, give the ALU and shifter time to produce a stable output and load the MAR if required.

- 4. Now that the shifter output is stable, store the C bus in the scratchpad and load the MBR, if either is required.

A.7. Boolean Algebra (Switching Algebra)

In 1854, George Boole introduced a symbolic notation to handle symbolic statements that employ a binary value of either true or false. This symbolic notation was adopted by Claude Shannon to analyze logic functions and has since been known as Boolean algebra or switching algebra.

A Boolean algebra is a closed algebraic system containing a set K of two or more elements and two binary operators '+' (OR) and '&' (AND); for, every X and Y in set K, X&Y belongs to K and X+Y belongs to K. In addition, the following postulates must be satisfied:

```

P1: Existence of 1 and 0

a) X + 0 = X

X \in 1 = X

b)

P2: Commutativity

a) X + Y = Y + X

P3: Associativity

a) X + (Y + Z) = (X + Y) + Z

b)

X \& (Y \& Z) = (X \& Y) \& Z

P4: Distributivity

X + (Y \& Z) = (X + Y) \& (X + Z)

a)

X \& (Y+Z) = X \& Y + X \& Z

b)

P5: Complement

a) X + X' = 1

b) X \in X' = 0

```

SummaryX + 0 = XX + 1 = 1X & 0 = 0X & 1 = X0' = 1, 1' = 0, X'' = X

Where & denotes AND, + denotes OR and ' denotes a complement.

Two expressions are said to be equivalent if one can be replaced by the other. The "dual" of an expression is obtained by replacing each "+" in the expression by "&", each "&" by "+", each 1 by 0, and each 0 by 1. The principle of duality states that if an equation is valid in Boolean algebra, its dual is also valid.

The following theorems are useful in manipulating Boolean functions. They are traditionally used for converting Boolean functions from one form to another, deriving canonical forms, and minimizing, or reducing the complexity of, Boolean functions.

```

T1: Idempotency

a) X + X = X

b) X \& X = X

T2: Properties of 1 and 0

a) X + 1 = 1

b) X \in 0 = 0

T3: Absorption

a) X + XY = X

b) X \& (X + Y) = X

T4: Absorption

X + X'Y = X + Y

a)

X \& (X' + Y) = X \& Y

b)

DeMorgan's Laws

a) (X + Y)' = X' \in Y'

(X \in Y)' = X' + Y'

b)

```

Consensus a) XY + X'Z + YZ = XY + X'Z b) (X + Y) & (X' + Z) & (Y + Z) = (X + Y) & (X' + Z)

#### B. File Structures

File structures specify the forms in which files may be structured. These structures are processed and even organized in different ways. File processing refers to the manner in which records are processed or stored in an external file. In addition, file organization pertains to the data structures associated with organizing the data. Four common file organizations include sequential, random, indexed sequential, and multikey.

B.1. Sequential File Organization

Sequential file organization characterizes the simplest type. Sequential grouping employs the least complex process for organizing files. Files are written consecutively in sequence from beginning to end and must be accessed in the same manner. The retrieval of files adopts a LIFO (last-infirst-out) method.

#### B.2. Random File Organization

Random file organization implies a predictable relationship between the key used to identify an individual record and that record's location in an external file. A relative file illustrates a common implementation of random file organization while being available in most high-level programming languages. Once a key-position relationship is

established, the position of the record in the file is specified as a record number relative to the position of the record from the beginning of the file. Each address is computed by using the following formula: the record's address = (the relative record number x the fixed record length) + the beginning of the file.

#### B.3. Indexed Sequential File Organization

Indexed sequential file organization combines sequential access and ordering with the capabilities of random access. An indexed sequential file contains two parts. The first part stores a collection of records in contiguous locations within blocks in a relative file. The record's order is according to a key field. The second part holds an index to the file of ordered records. The index contains a hierarchical structure of record keys and relative block numbers. The blocks of records in the file are not necessarily stored in sequential order. The index indicates the order in which the blocks should be obtained to achieve sequential order by record keys. Indexed sequential file organization provides sequential access to records by the primary key order field. Random access is supplied, as well, to an individual record by the same key. Indexed sequential file organization comprises two types: the cylinder and surface indexing method, and the index and data blocks method.

#### B.4. Multikey File Organization

Multikey file organization permits access to a data file

by several different key fields. Hence, multiple key fields are recognized to retrieve a particular file. The advantage simply lies in the file's access not being restricted to only one key field.

Multiple key-file organization includes two different types. The first being inverted file organization which accesses data from a file by secondary keys. The access is achieved by using a directory of all possible attributes for each secondary key field; and, the primary key or address of all records containing those attributes. The second type is multilist file organization which uses a file to link data records with identical secondary key values to organize a multilist file. A multilist file is divided into two areas: a directory and a data record area.

The directory contains an inverted list for each secondary key field to be used in accessing the data records in the data record area. The directory also stores all possible attributes for each secondary key field and a pointer to a linked list of all records storing the attribute. The data records are organized to provide random access to the records.

#### B.5. Blocking

The smallest amount of data which can be read from or written to a secondary storage device at a time occupies a block. By blocking several components into one block, several components can be accessed at one time. This increases

efficiency by decreasing the amount of physical accesses to the file and lessening the execution time of the program accessing the file.

The amount of data transferred to or from the file during access forms the size of one block. The size cannot exceed the amount of available main memory.

#### B.6. Buffering

A buffer functions as a location in memory to serve as an intermediary between I/O devices and main memory. Double buffering is possible when both the I/O operations performed by the I/O channel and the processing operations generated by the CPU overlap in time.

Implementations are I/O bound when access time to input one buffer from the file is longer than process time. The total time to process the file cannot be reduced without reducing the file's access time. Processor-bound demonstrates processing time is longer than access time.

#### B.7. File Storage Devices

Magnetic tape represents a sequential storage device in which blocks of data are stored serially along the length of the tape and can only be accessed consecutively. Data are recorded in 9 tracks aligned parallel to the edges of the tape. Magnetic tapes are used for sequentially organized files only.

The recording density of the tape is the number of bytes of data to be stored per inch. A block of data is sometimes

called a physical record, and may contain one or more logical records. These physical records or blocks are separated by interblock gaps (IBGs) in which the tape can start and stop between I/O requests.

The following formulas involve accessing specific information from magnetic tape:

Space Calculations:

- Block Length (bytes) = Logical Record Length x Blocking Factor

- Block Length (inches) = Block Length (bytes) / Density

- Number of Blocks = Number of Records / Blocking Factor

Block Length = Block Length (bytes) / Density

Tape Length = (Number of Blocks x Block Length) + (Number of IBGs x IBG Length)

Accessing Time and Tape Calculations:

- Time to Read 1 Block = Start Time + Stop Time + Block Length (inches) / Transfer Speed

- Time to Read 1 Tape = (Time to Read 1 Block) x (Number of Blocks)

- Single Buffering: Total Time for File = (Time to Read 1 Block + Processing Time for 1 Block) x Number of Blocks

- Double Buffering: Total Time for File = (Input Time x Number of Blocks) + Processing Time for 1 Block

#### B.8. Timing of Access Methods

Brief definitions of additional terms will ensue. These terms are associated with several formulas given later. The

transfer rate is the uniform rate at which all tracks on the same disk pass under the read/write head. Rotational delay or latency pertains to the time required for the beginning of the accessed block to rotate around to the read/write head. Transfer time regards the time required for the entire block to pass under the read/write head. Minimum seek time concerns the time needed to move the access arm to an adjacent track. Maximum seek time refers to the time it takes to move from the outermost or innermost track to the farthest track.

Average seek time relates to the average of both the maximum and minimum seek times. Seek time establishes the most significant factor of the access time, while the transfer rate is the least significant factor.

Rotational time pinpoints the time it takes for a disk pack to make one revolution. Rotational delay or latency operates between zero delay and the rotational time. The following formulas involve accessing specific information from a fixed disk:

```

Access times:

Average Access Time per Block = Seek + Latency +

Transfer

For Fixed Disks with One Head per Track, the Average

Access Time = Latency + Transfer

Hard Disk Capacity:

(If Using Cylinders)

Readable Radius = (Outer Diameter - Inner Diameter)

/ 2

```

Tracks/Surface = (Readable Radius / Spacing Between Tracks ) + 1Bits/Track = Density x Circumference of Smallest Track = Density x Inner Diameter x Pi Bits/Track x Tracks/Surface Bits/Pack = х Surfaces/Pack (If Using Sectors) Bits/Sector = (Bits/Track) / (Sectors/Track) Bytes/Sector = (Bits/Sector) / (Bits/Byte) Bits/Track (Sectoring) = Bits/Byte x Bytes/Sector x Sectors/Track = Bits/Track x Tracks/Surface Bits/Pack х Surfaces/Pack

Transfer Rate = Bytes/Revolution x [(Revolutions/Minute) / (60 Seconds/Minute)]

## B.9. Record Keys

On the other hand, with direct file organization there exists a predictable relationship between the key used to identify an individual record and the record's absolute address in the external file. A relative file with space for N records contains positions with relative record numbers 0, 1, ..N-1 where the i<sup>th</sup> number has the relative record number I - 1. The key-position relationship must be a predictable relationship to ensure direct access to the record is possible once the record is stored in the relative file.

### B.10. Hashing

Hashing is the application of a function to the key of a particular record resulting in mapping a range of possible key values into a smaller range of relative addresses. The function randomly selects a relative address for a specific key value without regard to the physical sequence of records in the file. A collision occurs when the hashing function for two different keys results in the same relative address.