# Application and Evaluation of GaN Technology in High Performance DC-DC Converters

A thesis submitted to the University of Manchester for the degree of Doctor of Philosophy in the Faculty of Science and Engineering

2019

**Yichen Cai**

School of Electrical and Electronic Engineering

### Contents

| Contents                                                                         | 1  |

|----------------------------------------------------------------------------------|----|

| List of figures                                                                  | 5  |

| List of tables                                                                   | 11 |

| List of symbols                                                                  | 13 |

| List of abbreviations                                                            | 16 |

| Abstract                                                                         | 18 |

| Declaration                                                                      | 19 |

| Intellectual Property Statement                                                  | 20 |

| Acknowledgement                                                                  | 21 |

| Chapter 1                                                                        | 22 |

| Introduction                                                                     | 22 |

| 1.1 Background                                                                   | 22 |

| 1.2 Aim and objectives                                                           | 23 |

| 1.3 Thesis structure                                                             | 23 |

| Chapter 2                                                                        | 25 |

| Literature Review                                                                | 25 |

| 2.1 Introduction                                                                 | 25 |

| 2.2 Emerging device technology                                                   | 25 |

| 2.2.1 WBG material                                                               | 25 |

| 2.2.2 Off-the-shelf WBG devices                                                  | 26 |

| 2.2.3 Structure of GaN power devices                                             | 29 |

| 2.3 Characteristics of GaN HEMTs                                                 | 33 |

| 2.3.1. Switching characteristics                                                 | 33 |

| 2.3.2. PCB Design considerations                                                 | 34 |

| 2.3.3. Dynamic on-resistance                                                     | 37 |

| 2.4 Converter miniaturization and performance advance for transport applications | 43 |

| 2.4.1. On-board charger (OBC)                                            | 44 |

|--------------------------------------------------------------------------|----|

| 2.4.2. Traction drive converters                                         | 51 |

| 2.4.3. Auxiliary power module (APM)                                      | 55 |

| 2.5 High-conversion-ratio DC-DC converters                               | 60 |

| 2.5.1. Cascaded buck/boost converter                                     | 60 |

| 2.5.2. Quadratic buck/boost converter                                    | 60 |

| 2.5.3. Switched capacitor/inductor converter                             | 60 |

| 2.5.3. Coupled inductor buck/boost converter                             | 61 |

| 2.5 Summary of literature review                                         | 62 |

| Chapter 3                                                                | 64 |

| Characterization of GaN HEMT                                             | 64 |

| 3.1 Introduction                                                         | 64 |

| 3.2 Measurement of switching characteristics of GaN HEMTs                | 64 |

| 3.2.1 Theory of GaN HEMTs inductive switching                            | 64 |

| 3.2.2 Design and practical implementation of a double-pulse-test circuit | 66 |

| 3.2.3 Experimental Results and discussion                                | 70 |

| 3.2.4 Summary of the GaN HEMTs switching performance characterization    | 75 |

| 3.3 Measurement of dynamic on-state resistance of GaN HEMTs              | 75 |

| 3.3.1 Introduction                                                       | 75 |

| 3.3.2 Measurement techniques and challenges                              | 76 |

| 3.3.3 DPT test circuit                                                   | 78 |

| 3.3.4 Dynamic on-state resistance using modified DPT circuit             | 79 |

| 3.3.5 Dynamic on-state resistance using continuous operating converter   | 85 |

| 3.3.6 Dynamic on-state resistance using modified pulsed test circuit     | 89 |

| 3.3.7 Performance comparison of the original and modified test circuits  | 94 |

| 3.4 Summary                                                              | 95 |

| Chapter 4                                                                | 97 |

| GaN-Based Interleaved Switched-Capacitor Step-Down Converter             | 97 |

| 4.1 Introduction                                                         | 97 |

|                                                                          |    |

| 4.2 Topology selection and description                                 |     |

|------------------------------------------------------------------------|-----|

| 4.3 Circuit operation principle at steady-state                        |     |

| 4.4 Circuit analysis during switching transients                       | 101 |

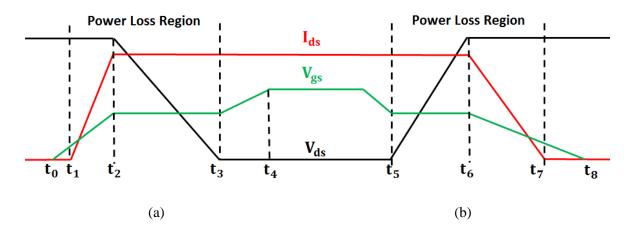

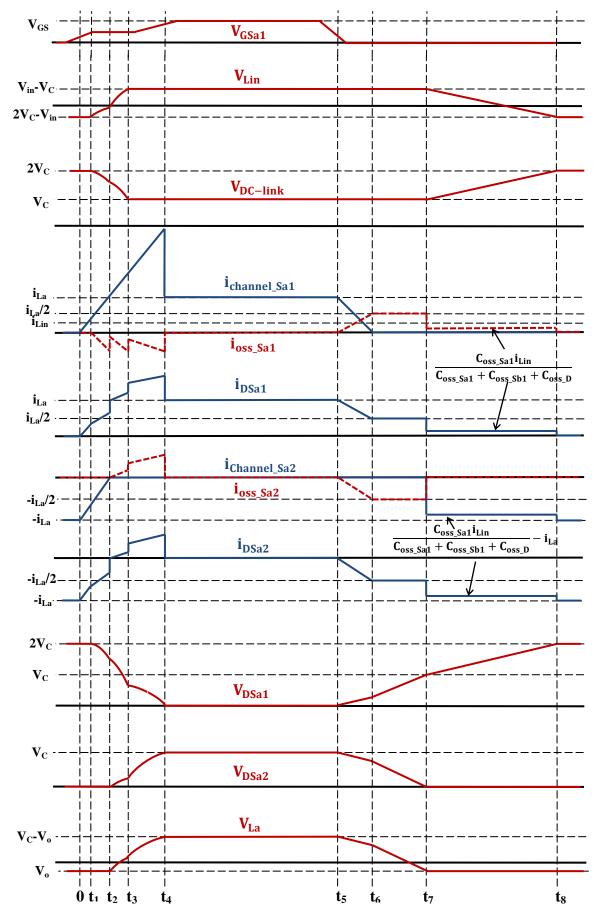

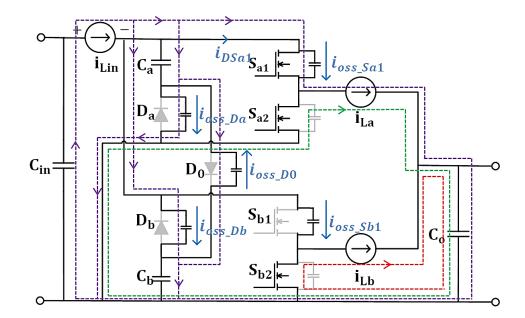

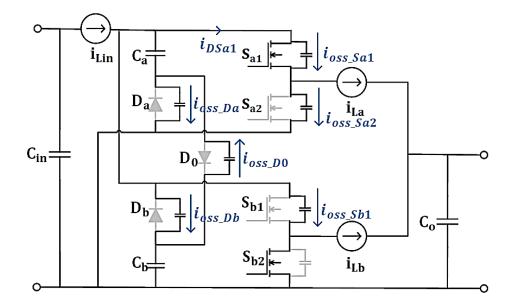

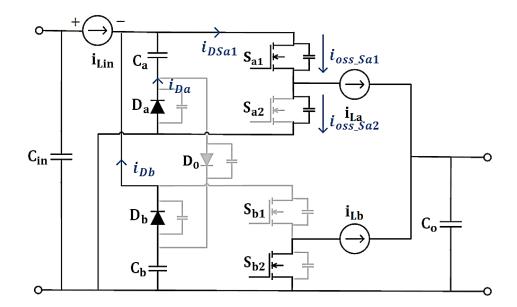

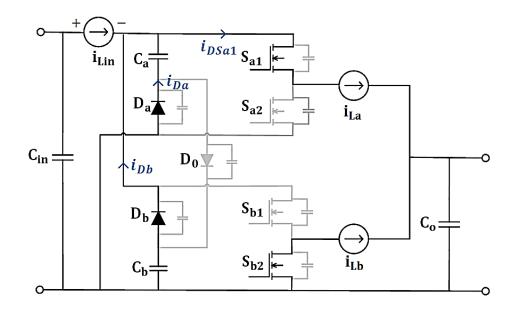

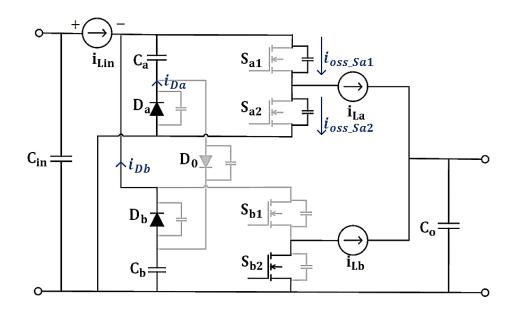

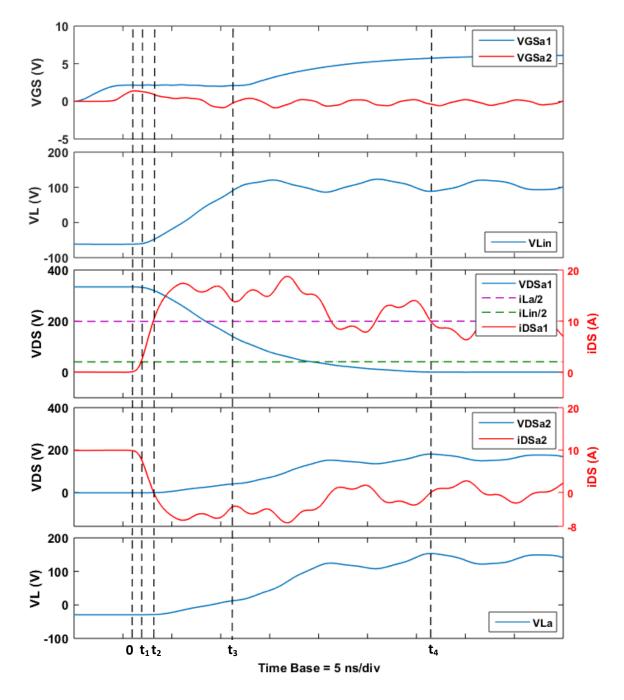

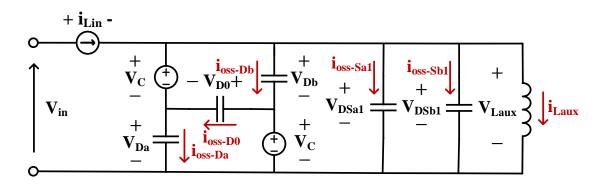

| 4.4.1 Sub-Period 0~t <sub>1</sub>                                      | 103 |

| 4.4.2 Sub-Period $t_1 \sim t_2$                                        |     |

| 4.4.3 Sub-Period $t_2 \sim t_3$                                        | 104 |

| 4.4.4 Sub-Period $t_3 \sim t_4$                                        | 105 |

| 4.4.5 Sub-Period $t_4 \sim t_5$                                        | 105 |

| 4.4.5 Sub-Period $t_5 \sim t_6$                                        | 106 |

| 4.4.5 Sub-Period $t_6 \sim t_7$                                        | 107 |

| 4.4.6 Sub-Period t <sub>7</sub> ~t <sub>8</sub>                        | 108 |

| 4.5 Converter parameter design and component selection                 |     |

| 4.6 Prototype description                                              |     |

| 4.8 Converter thermal management                                       |     |

| 4.9 Converter simulation model                                         |     |

| 4.10 Experimental results                                              |     |

| 4.11 Converter loss breakdown                                          |     |

| 4.12 Converter efficiency                                              |     |

| 4.13 Comparison with Si-based circuit                                  |     |

| 4.14 Summary                                                           |     |

| Chapter 5                                                              |     |

| Operation of the Soft-Switching Switched-Capacitor Step-Down Converter |     |

| 5.1 Introduction                                                       |     |

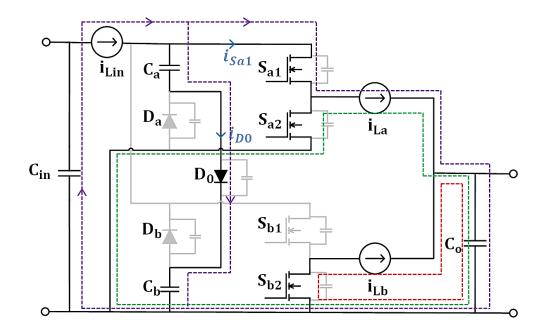

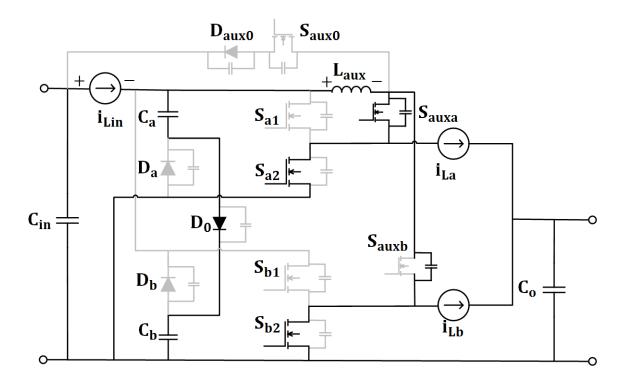

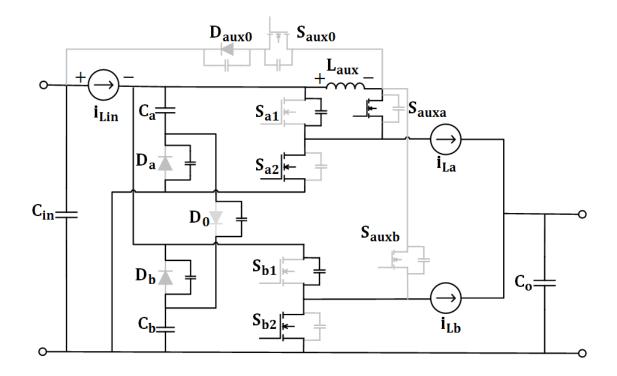

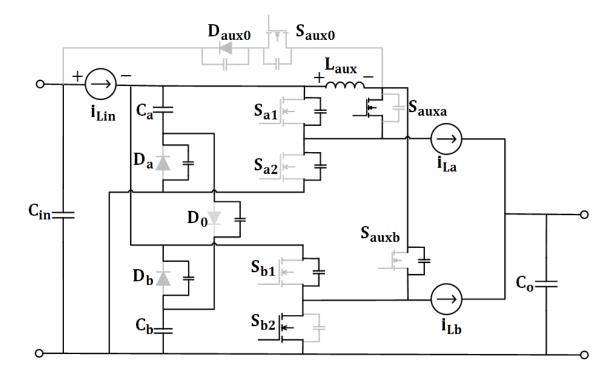

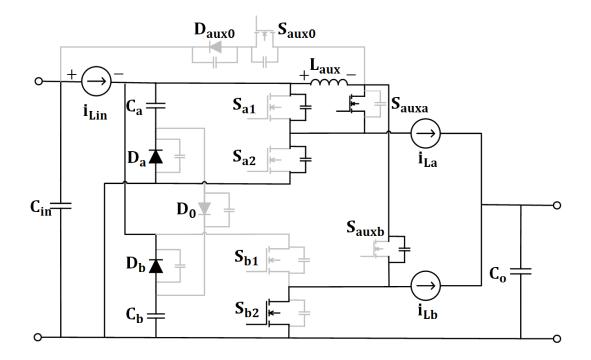

| 5.2 Circuit description                                                |     |

| 5.3 Circuit operation principle at steady-state                        |     |

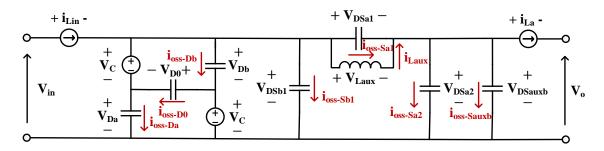

| 5.4 Circuit analysis during advance time                               |     |

| 5.4.1 Circuit operation at nominal load conditions                     |     |

| 5.4.2 Circuit operation at heavy load conditions                       | 146 |

| 5.5 Auxiliary circuit design                                           | 149 |

|                                                                        | 3   |

| 5.5.1 Control timings of auxiliary circuit                                               |  |  |

|------------------------------------------------------------------------------------------|--|--|

| 5.5.2 RC snubbers design                                                                 |  |  |

| 5.6 Converter component selection                                                        |  |  |

| 5.7 Converter prototype description                                                      |  |  |

| 5.8 Simulation results                                                                   |  |  |

| 5.9 Experimental results                                                                 |  |  |

| 5.10 Converter energy management                                                         |  |  |

| 5.11 Comparison with hard-switching converter                                            |  |  |

| 5.12 Summary                                                                             |  |  |

| Chapter 6 176                                                                            |  |  |

| Conclusions and Future Outlook                                                           |  |  |

| 6.1 Introduction                                                                         |  |  |

| 6.2 Key findings and research contributions                                              |  |  |

| 6.2.1 Switching characterization of GaN HEMTs 176                                        |  |  |

| 6.2.2 Dynamic on-state resistance characterization of GaN HEMTs 176                      |  |  |

| 6.2.3 GaN-based hard-switching interleaved switched-capacitor step-down converters 178   |  |  |

| 6.2.4 GaN-based soft-switching interleaved switched-capacitor step-down converters 179   |  |  |

| 6.3 Future outlook and research opportunities                                            |  |  |

| 6.3.1 Dynamic on-state resistance of GaN HEMT during continuous operation                |  |  |

| 6.3.2 Further tests on the hard-switching switched-capacitor step-down converter         |  |  |

| 6.3.3 Optimisation of the soft-switching switched-capacitor step-down converter          |  |  |

| 6.3.4 Advanced control for interleaved switched-capacitor step-down converters           |  |  |

| 6.3.5 Embedded design for GaN-based switched-capacitor step-down converters              |  |  |

| References                                                                               |  |  |

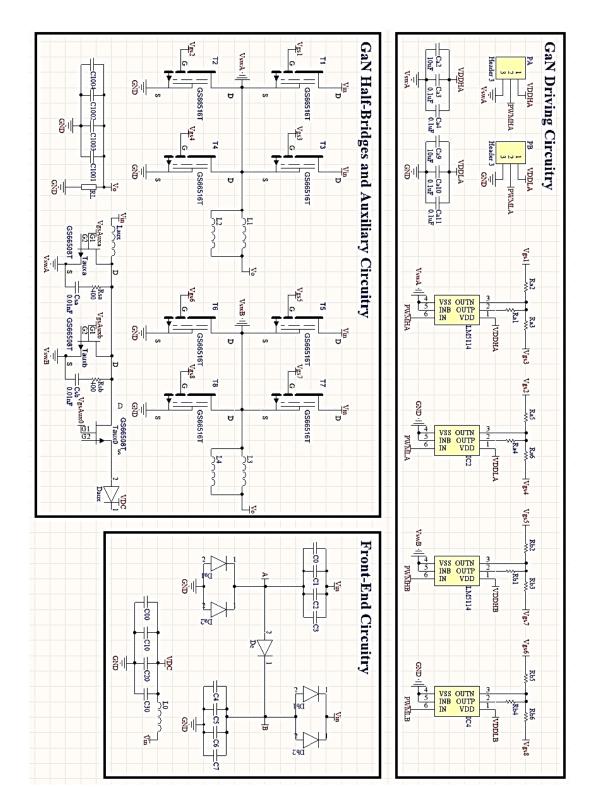

| Appendix A. Soft-switching switched-capacitor step-down converter circuit schematics 192 |  |  |

| Appendix B. Soft-switching switched-capacitor step-down converter PCB layout             |  |  |

Word count: 45,442

# List of figures

| Fig. 2.1. Specific on-resistance vs breakdown voltage for Si, SiC and GaN commercial products and the material one-dimensional limits [1]2 |

|--------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.2. Material properties comparison of Si, SiC and GaN [8]                                                                            |

| Fig. 2.3. Basic structure of GaN HEMT from EPC [33]6                                                                                       |

| Fig. 2.4. Normally-off GaN HEMT using GIT at (a) off-state and (b) on-state [34]                                                           |

| Fig. 2.5. Schematic of cascode GaN transistor [40]7                                                                                        |

| Fig. 2.6. Switching losses of the (a) 650 V/30 A and (b) 650 V/60 A GaN HEMTs [51] 9                                                       |

| Fig. 2.7. Thermal management of the (a) top-cooled and (b) bottom-cooled GaN HEMTs [51, 53]                                                |

| Fig. 2.8. The effects of high (a) di/dt and (b) dv/dt on GaN HEMTs [57, 58]                                                                |

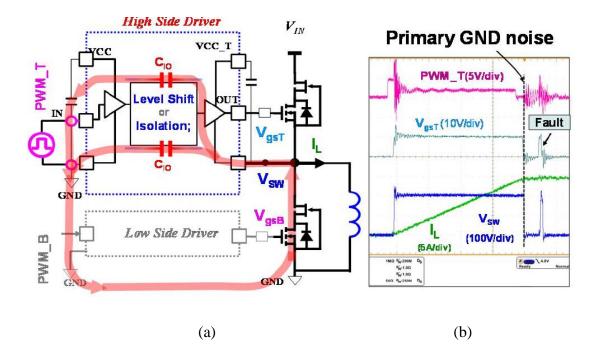

| Fig. 2.9. (a) Common mode noise mechanism due to high dv/dt and (b) its effect on the driving signals [60]                                 |

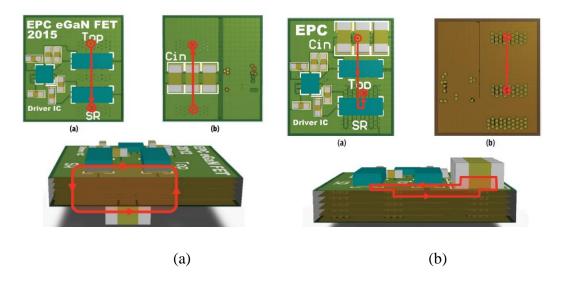

| Fig. 2.10. PCB layouts with (a) vertical loop and (a) multi-layer vertical loop [61] 13                                                    |

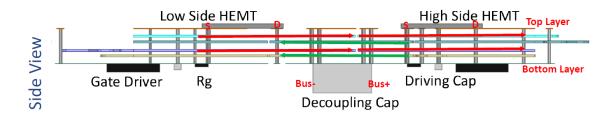

| Fig. 2.11. Multi-layer PCB layout design with flux cancelling effect [62]13                                                                |

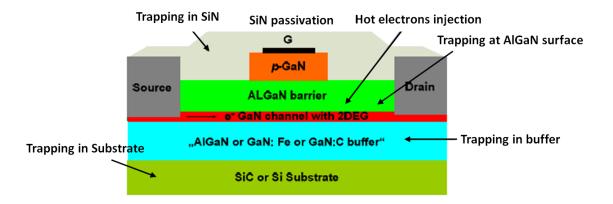

| Fig. 2.12. Trapping mechanism in GaN HEMT14                                                                                                |

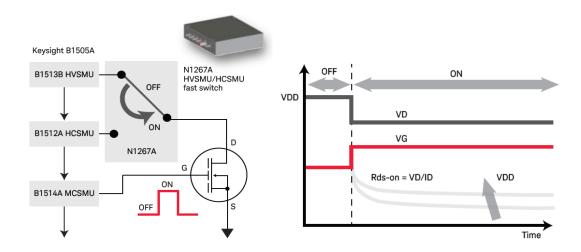

| Fig. 2.13. Circuit diagram of Keysight curve tracer B1505A [70]15                                                                          |

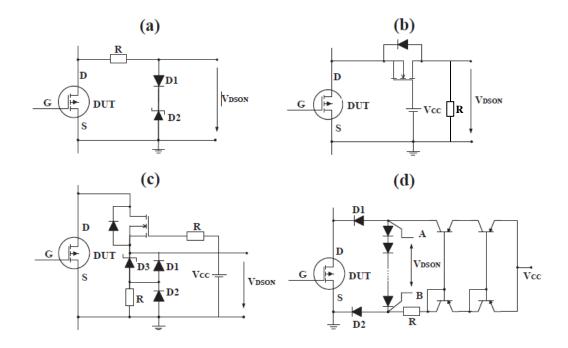

| Fig. 2.14. Clamping circuit for dynamic on-resistance measurement [71]16                                                                   |

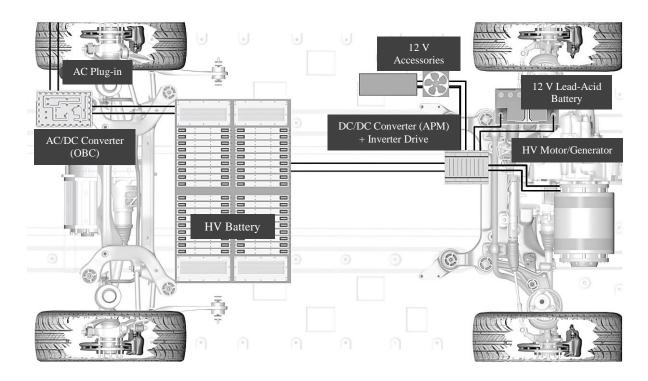

| Fig. 2.15. Powertrain of plug-in hybrid electric vehicle (PHEV) [88] 19                                                                    |

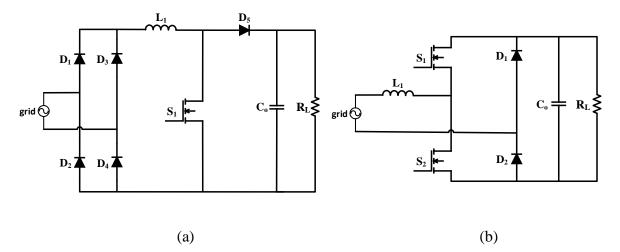

| Fig. 2.16. (a) Conventional PFC rectifier and (b) bridgeless totem pole rectifier                                                          |

| Fig. 2.17. EMI filter for (a) 100 kHz boost PFC, (b) 1 MHz single-phase boost PFC and (c)<br>1 MHz dual-phase interleaved boost PFC [99]   |

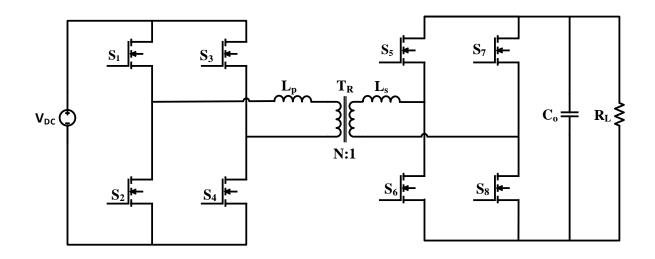

| Fig. 2.18. Circuit schematic of (a) DAB and (b) CLLC converters                                                                            |

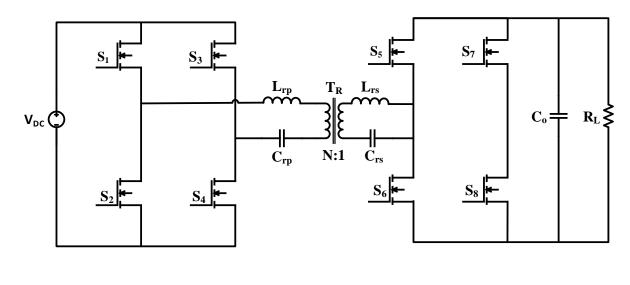

| Fig. 2.19. Circuit schematic of dual-phase boost converter                                                                                 |

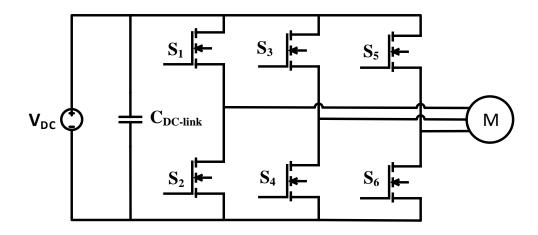

| Fig. 2.20. Circuit schematic of three-phase inverter drive                                                                                 |

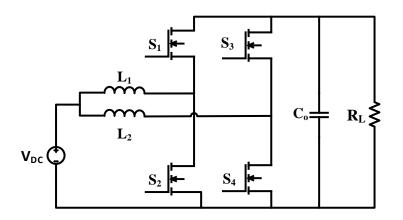

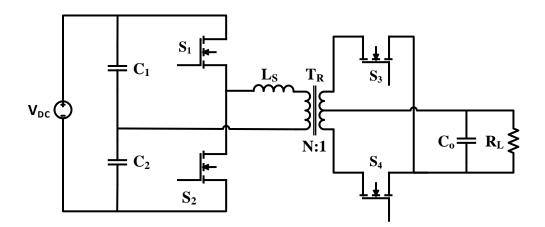

| Fig. 2.21. Circuit schematic of half-bridge center-tap DC-DC converter                                                                     |

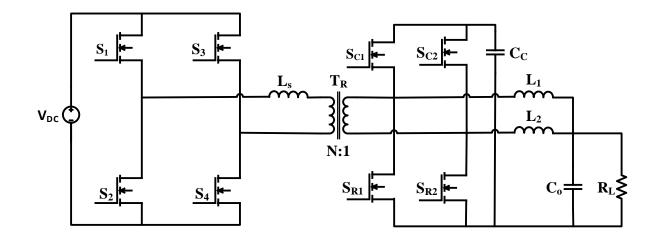

| Fig. 2.22. Circuit schematic of active clamp FBPS converter with current-doubler-rectifier                                                 |

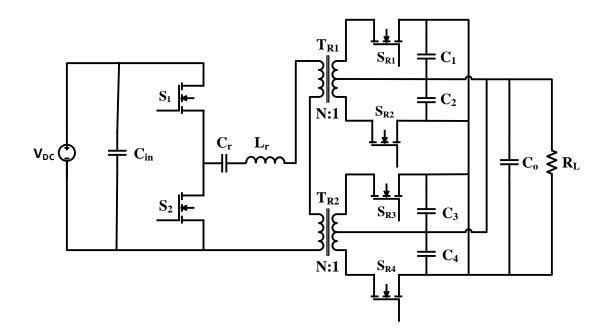

| <i>Fig. 2.23. Circuit schematic of LLC converter with integrated transformer</i>                                                           |

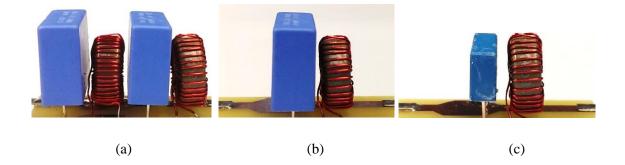

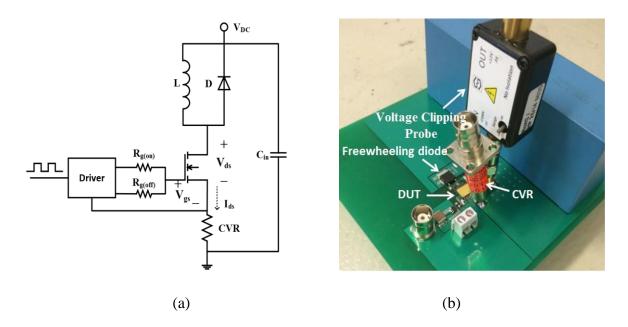

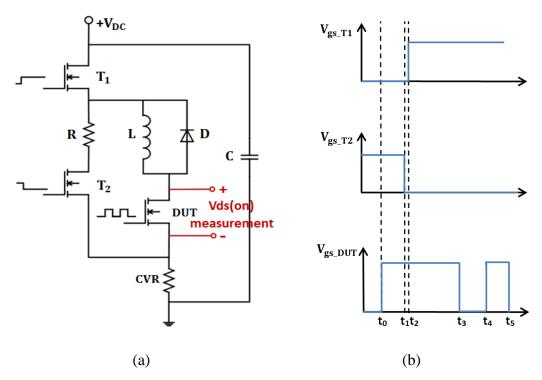

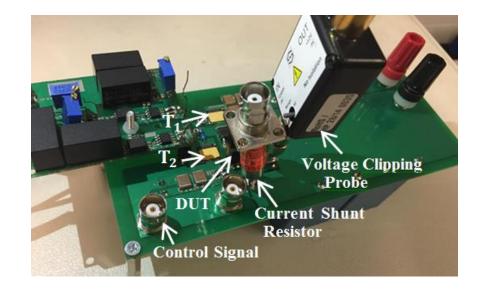

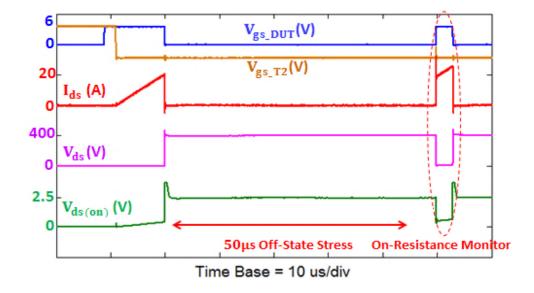

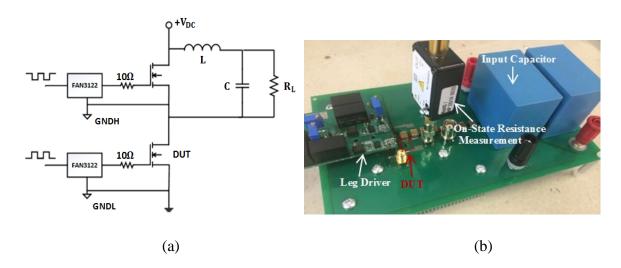

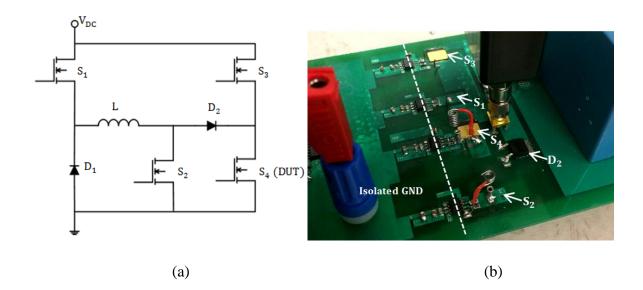

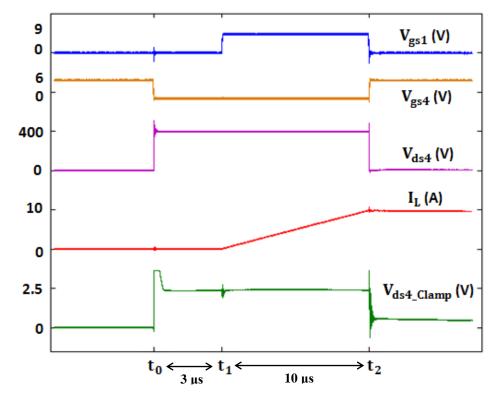

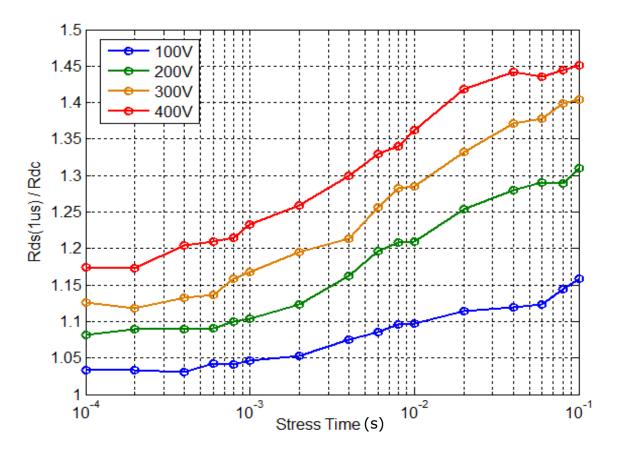

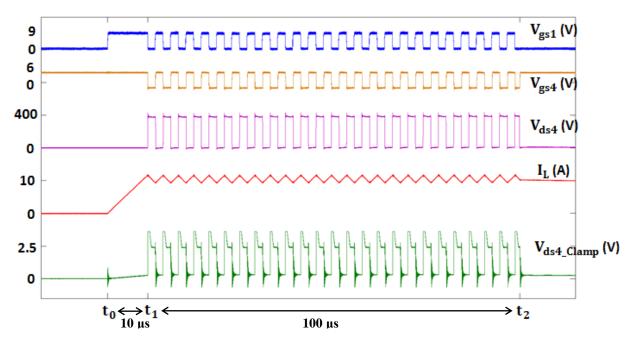

Fig. 3.20. (a) Circuit schematic and (b) practical implementation of the converter...... 22

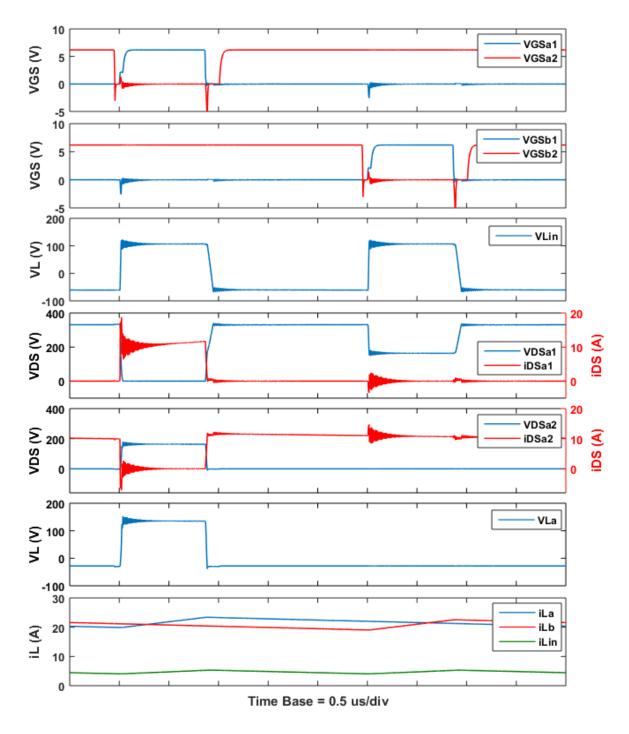

Fig. 4.2. Ideal operation waveforms of the interleaved switched-capacitor converter ...... 4

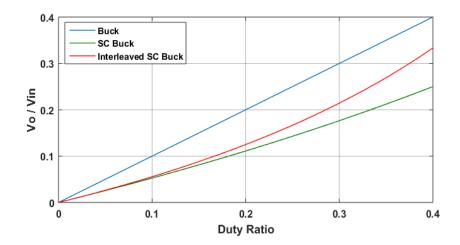

| Fig. 4.3. Conversion ratio of buck, switched-capacitor buck and interleaved switched-capacitor buck topologies                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 4.4. Converter ideal operation waveforms during switching transients                                                                                                                                                                                               |

| Fig. 4.5. Circuit operation during $0 \sim t_1$                                                                                                                                                                                                                         |

| Fig. 4.6. Circuit operation during $t_1 \sim t_2$                                                                                                                                                                                                                       |

| Fig. 4.7. Circuit operation during $t_2 \sim t_3$                                                                                                                                                                                                                       |

| Fig. 4.8. Circuit operation during $t_3 \sim t_4$                                                                                                                                                                                                                       |

| Fig. 4.9. Circuit operation during $t_4 \sim t_5$                                                                                                                                                                                                                       |

| Fig. 4.10. Circuit operation during $t_5 \sim t_6$                                                                                                                                                                                                                      |

| Fig. 4.11. Circuit operation during $t_6 \sim t_7$                                                                                                                                                                                                                      |

| Fig. 4.12. Circuit operation during $t_7 \sim t_8$                                                                                                                                                                                                                      |

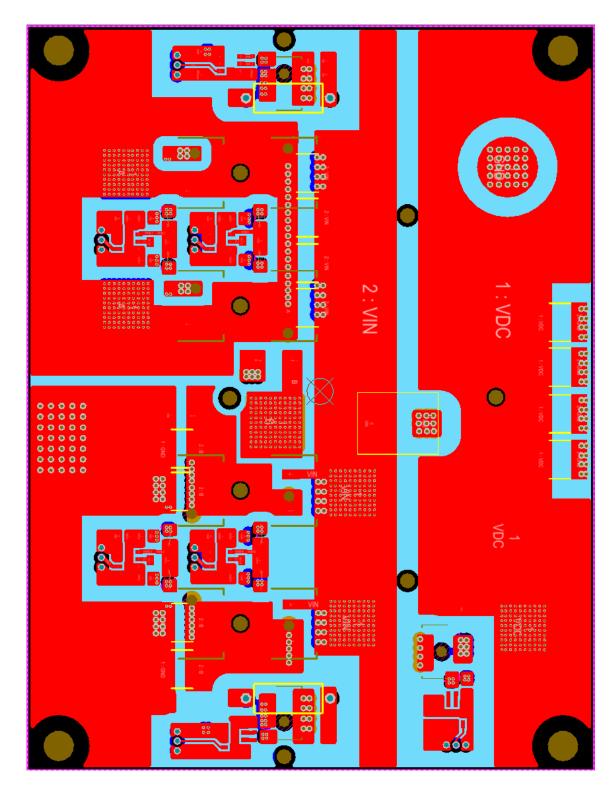

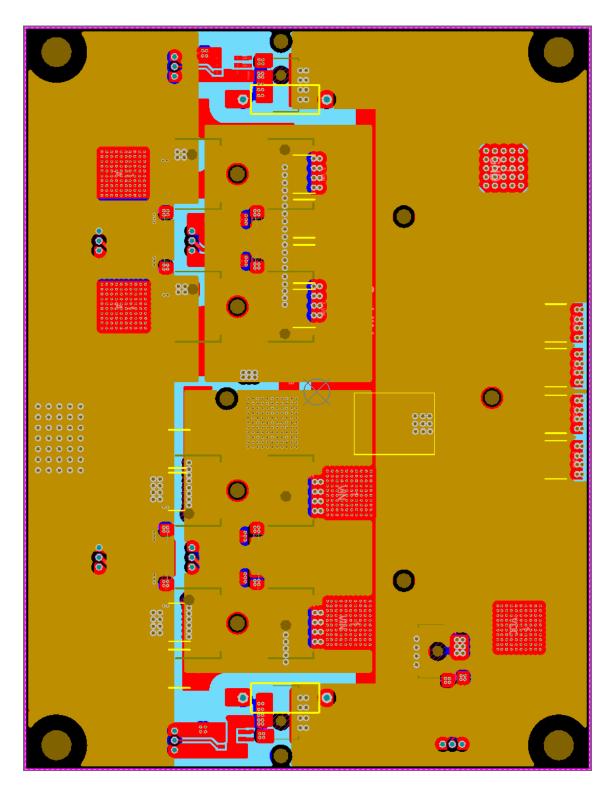

| Fig. 4.13. Main switching circuit board (a) top side (b) bottom side 16                                                                                                                                                                                                 |

| Fig. 4.14. Converter prototype17                                                                                                                                                                                                                                        |

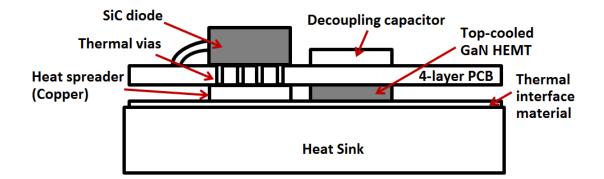

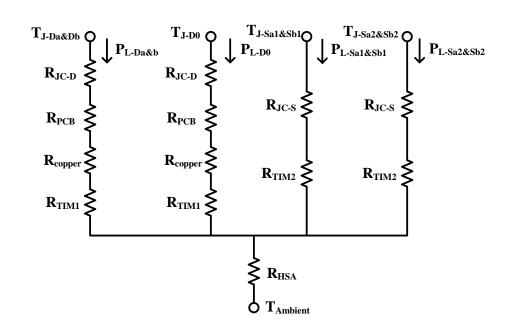

| Fig. 4.15. Cross-sectional view of the converter and thermal arrangements                                                                                                                                                                                               |

| Fig. 4.16. Converter thermal equivalent circuit                                                                                                                                                                                                                         |

| Fig. 4.17. Simulation results of the converter operating at 270-28 V, 200 kHz, 1.2 kW 20                                                                                                                                                                                |

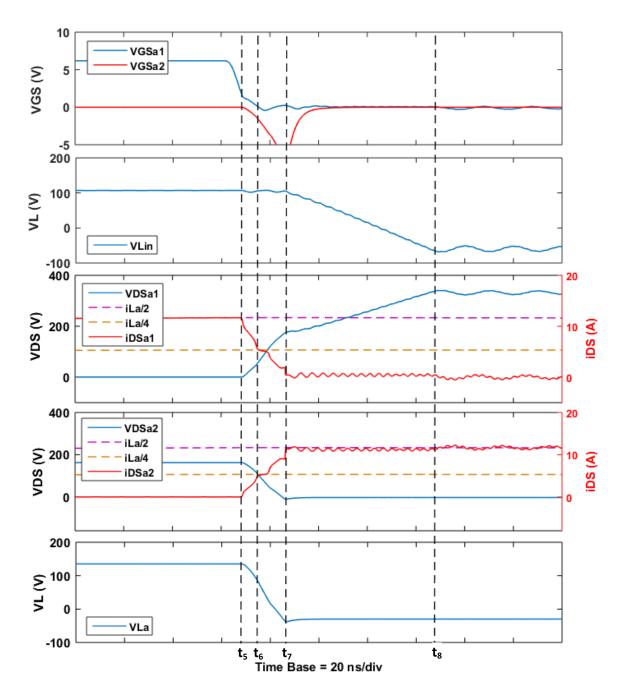

| Fig. 4.18. Simulation results during the $S_{a1}$ turn-on transient for the converter operating at 270-28 V, 200 kHz, 1.2 kW                                                                                                                                            |

| Fig. 4.19. Simulation results during the $S_{a1}$ turn-off transient for the converter operating at 270-28 V, 200 kHz, 1.2 kW                                                                                                                                           |

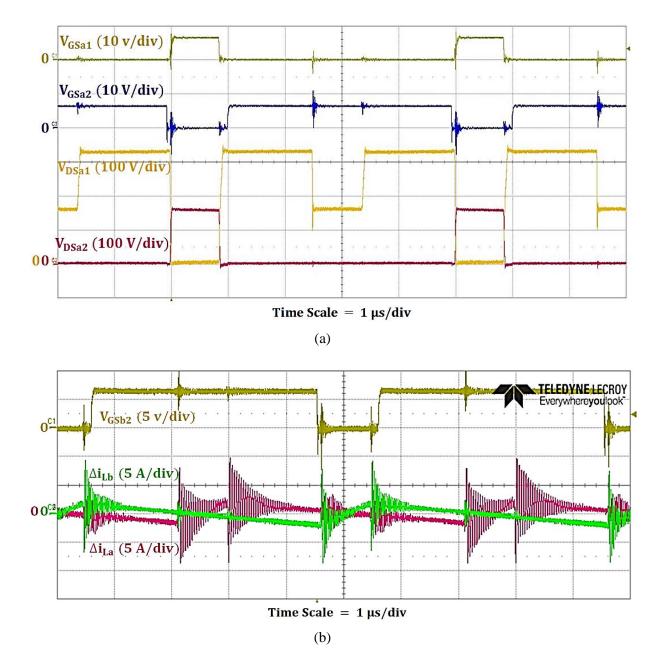

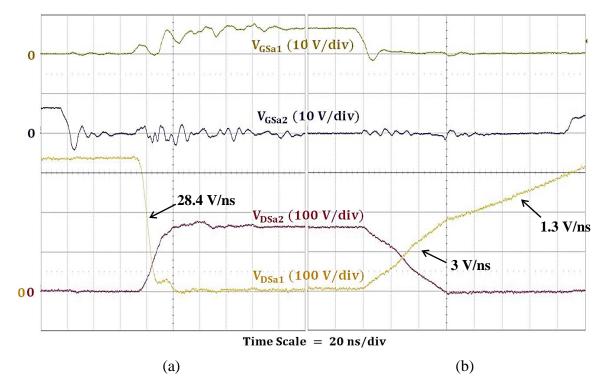

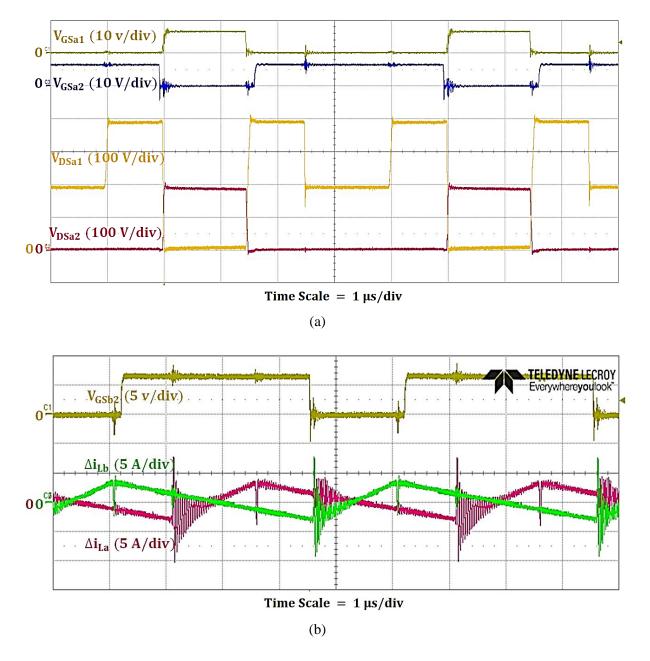

| Fig. 4.20. Experimental waveforms of (a) gate and drain-to-source voltage for $S_{a1}$ and $S_{a2}$ and (b) ripple current of output inductors for operation at $V_{in} = 270.9$ , $V_o = 27.5$ V, $f = 200$ kHz, $i_{out} = 41.4$ A, $P_{in} = 1.22$ kW and $D = 0.17$ |

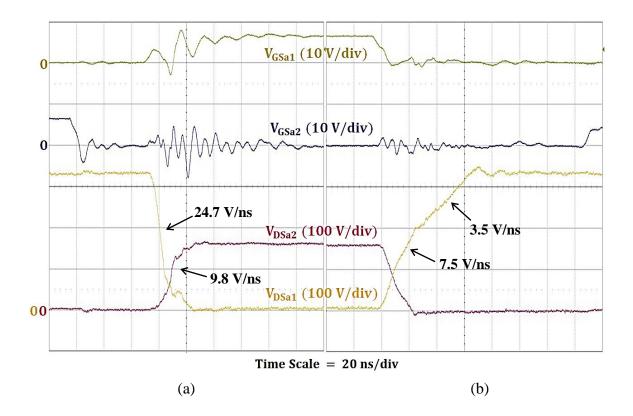

| Fig. 4.21. Experimental waveforms during switching transients for operation at $V_{in} = 270.9$ , $V_o = 27.5$ V, $f = 200$ kHz, $i_{out} = 41.4$ A, $P_{in} = 1.22$ kW and $D = 0.17$ (a) $S_{a1}$ turn-on;<br>(b) $S_{a1}$ turn-off                                   |

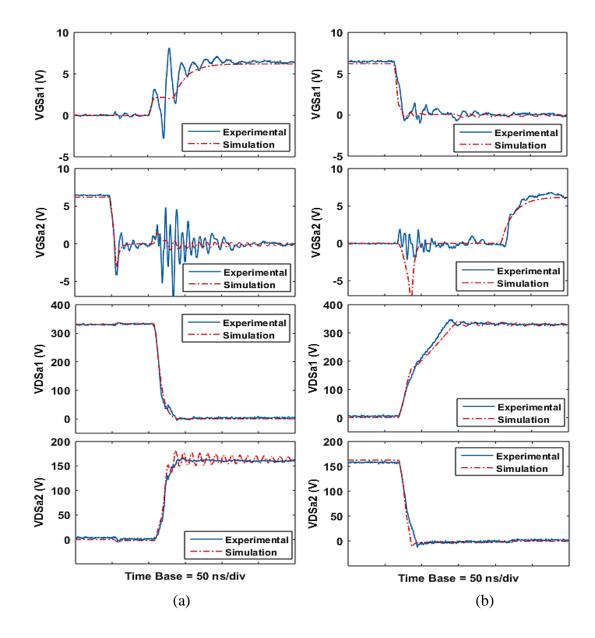

| Fig. 4.22. Comparison of experimental and simulation waveforms during (a) turn-on and (b) turn-off transients for operating at 270-28 V, 200 kHz, 1.2 kW                                                                                                                |

| Fig. 4.23. Experimental waveforms during switching transients for operation at $V_{in} = 270.9$ , $V_o = 28.5$ V, $f = 200$ kHz, $i_{out} = 11.7$ A, $P_{in} = 380$ W and $D = 0.17$ (a) $S_{a1}$ turn-on; (b) $S_{a1}$ turn-off                                        |

| 8                                                                                                                                                                                                                                                                       |

| Fig. 4.24. Experimental waveforms of (a) gate and drain-to-source voltage for $S_{a1}$ and $S_{a2}$ and (b) ripple current of output inductors for operation at $V_{in} = 270.9$ , $V_o = 56.3$ V, $f = 200$ kHz, $i_{out} = 20.5$ A, $P_{in} = 1.22$ kW and $D = 0.29$ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 4.25. Expanded experimental waveforms during $S_{a1}$ switching transients for operation<br>at $V_{in} = 270.9 V$ , $V_o = 56.3 V$ , $f = 200 kHz$ , $i_{out} = 20.5 A$ , $P_{in} = 1.22 kW$ and $D = 0.29 \dots 29$                                               |

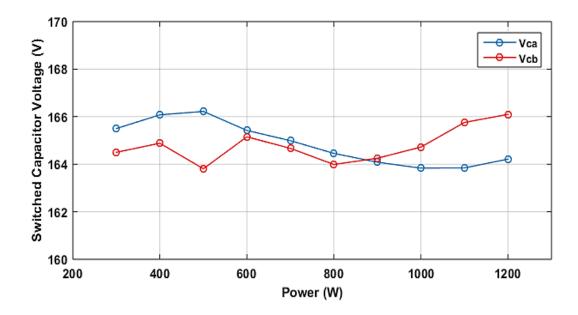

| Fig. 4.26. Voltages of switched capacitor $C_a$ and $C_b$ against load power for operation at $V_{in}=270$ V, $D=0.17$                                                                                                                                                  |

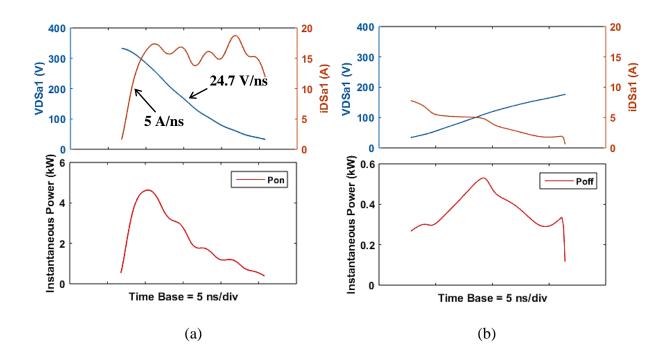

| Fig. 4.27. Top device $S_{a1}$ instantaneous power losses during (a) turn-on and (b) turn-off transients for operation at $V_{in} = 270$ V, $V_o = 27.9$ V, $f = 200$ kHz, $i_{out} = 43$ A, $P_{in} = 1.24$ kW and $D = 0.17$                                          |

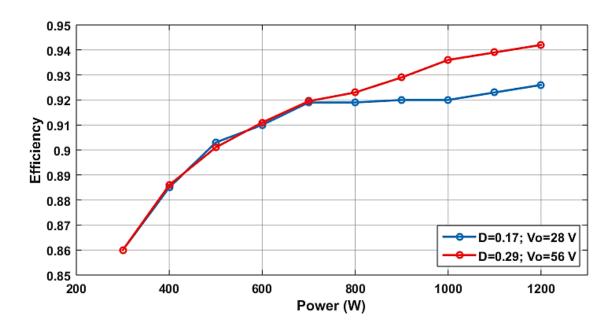

| <i>Fig. 4.28. Converter efficiency for operation at</i> $V_{in}=270$ <i>V,</i> $P_o=300\sim1.2$ <i>kW,</i> $f=200$ <i>kHz and</i> $D=0.17$ <i>and</i> $0.29$                                                                                                            |

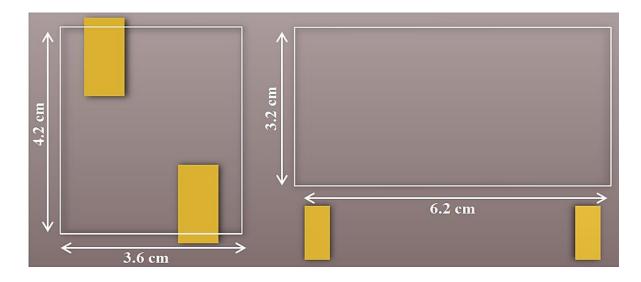

| Fig. 4.29. Footprint comparison of output inductors for AGP4233 used in the original converter (left) and IHV-60-24 used in Si-based converter (right)                                                                                                                  |

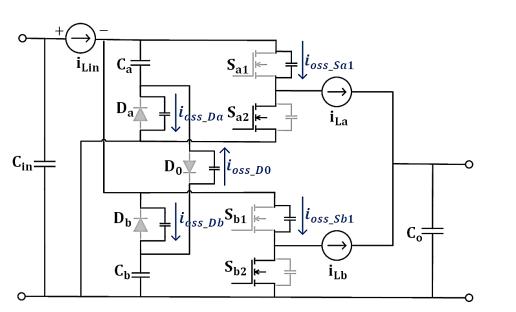

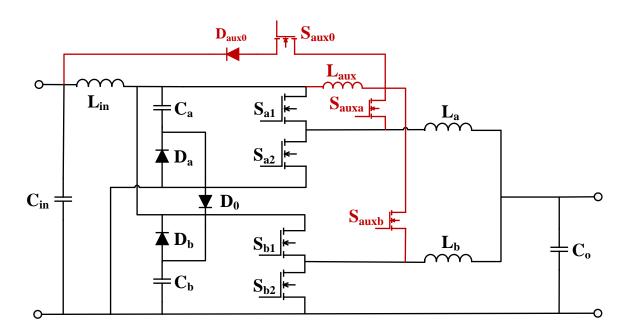

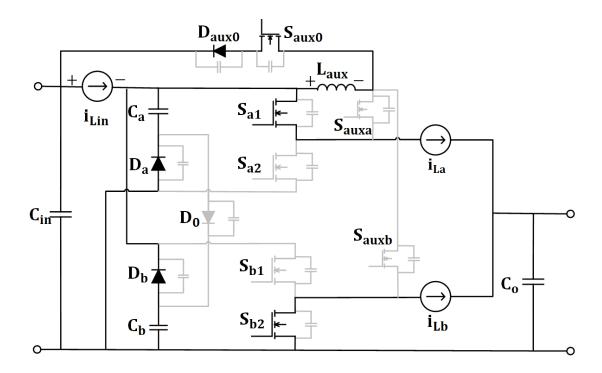

| Fig. 5.1. Interleaved soft-switching switched-capacitor step-down converter                                                                                                                                                                                             |

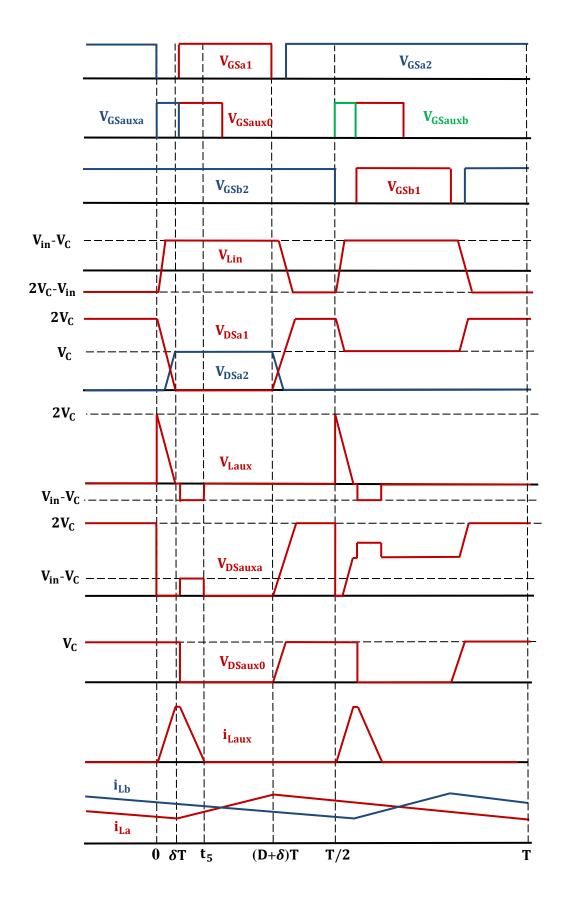

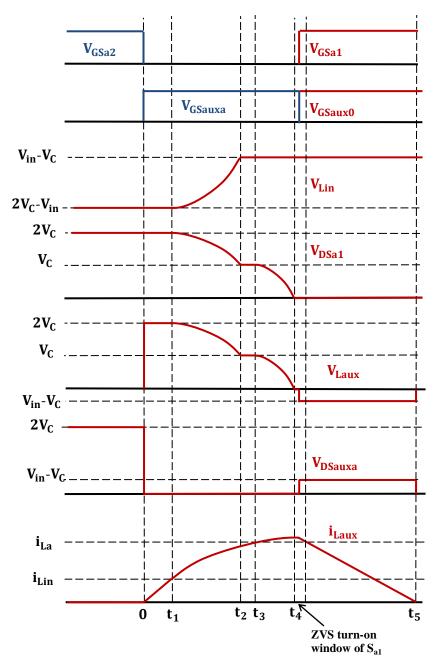

| Fig. 5.2. Ideal steady-state waveforms for D<0.5                                                                                                                                                                                                                        |

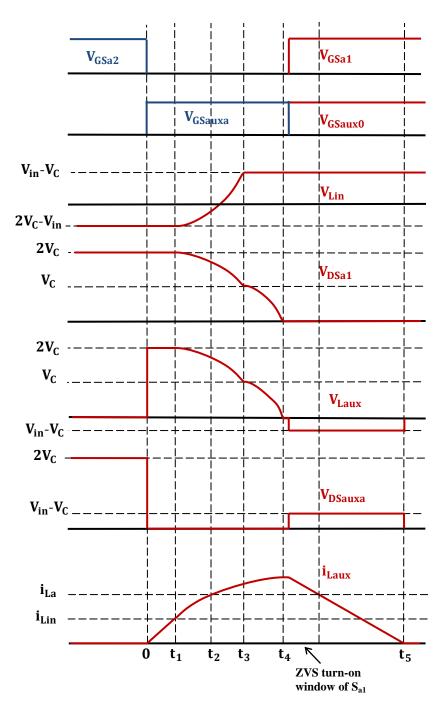

| Fig. 5.3. Expanded ideal steady-state waveforms during $0 \sim t_5$ for $D < 0.5$ at rated load conditions                                                                                                                                                              |

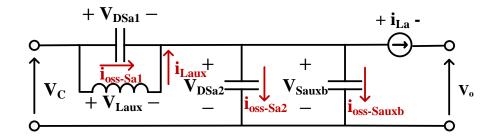

| <i>Fig. 5.4. Circuit operation during</i> $0 \sim t_1$ 6                                                                                                                                                                                                                |

| <i>Fig. 5.5. Circuit operation during</i> $t_1 \sim t_2$ <b>7</b>                                                                                                                                                                                                       |

| <i>Fig. 5.6. Simplified equivalent circuit during</i> $t_1 \sim t_2$ <b>7</b>                                                                                                                                                                                           |

| <i>Fig. 5.7. Circuit operation during</i> $t_2 \sim t_3$                                                                                                                                                                                                                |

| <i>Fig. 5.8. Simplified equivalent circuit during</i> $t_2 \sim t_3$                                                                                                                                                                                                    |

| <i>Fig. 5.9. Circuit operation during</i> $t_3 \sim t_4$                                                                                                                                                                                                                |

| Fig. 5.10. Simplified equivalent circuit during $t_3 \sim t_4$                                                                                                                                                                                                          |

| Fig. 5.11. Circuit operation during $t_4 \sim t_5$                                                                                                                                                                                                                      |

| Fig. 5.12. Ideal steady-state waveforms during $0 \sim t_5$ for D<0.5 at heavy load conditions 15                                                                                                                                                                       |

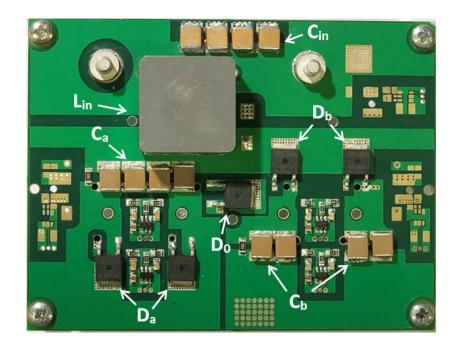

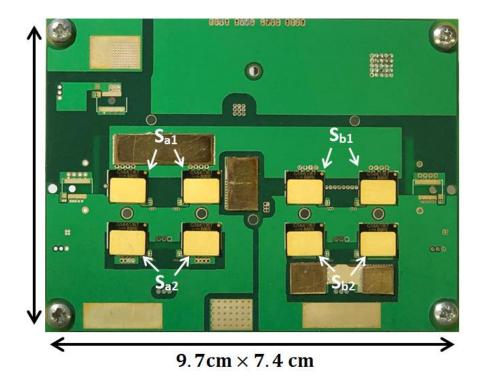

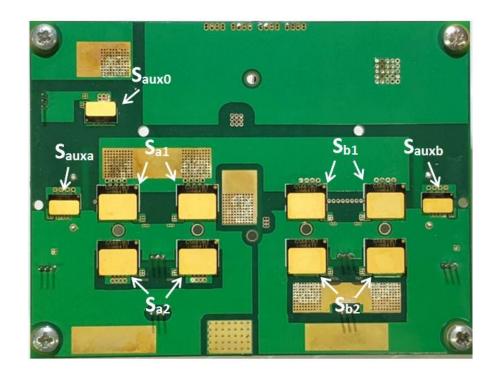

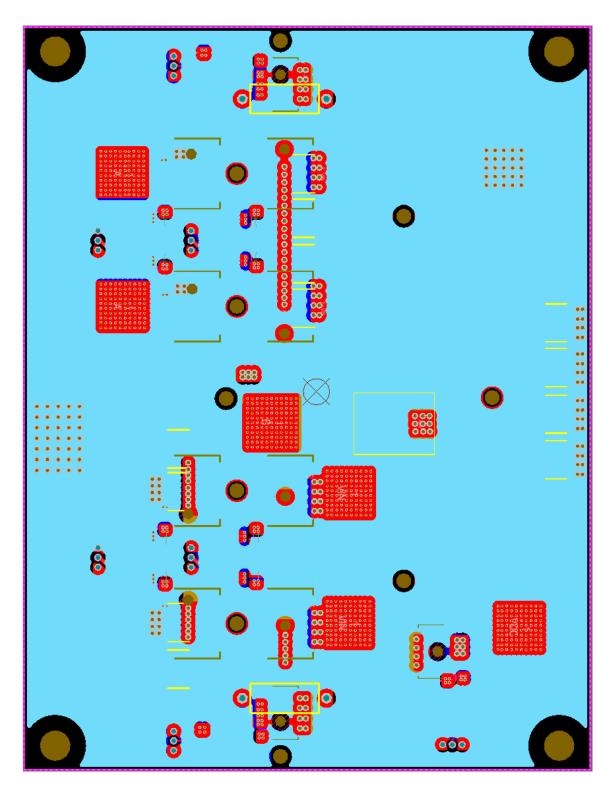

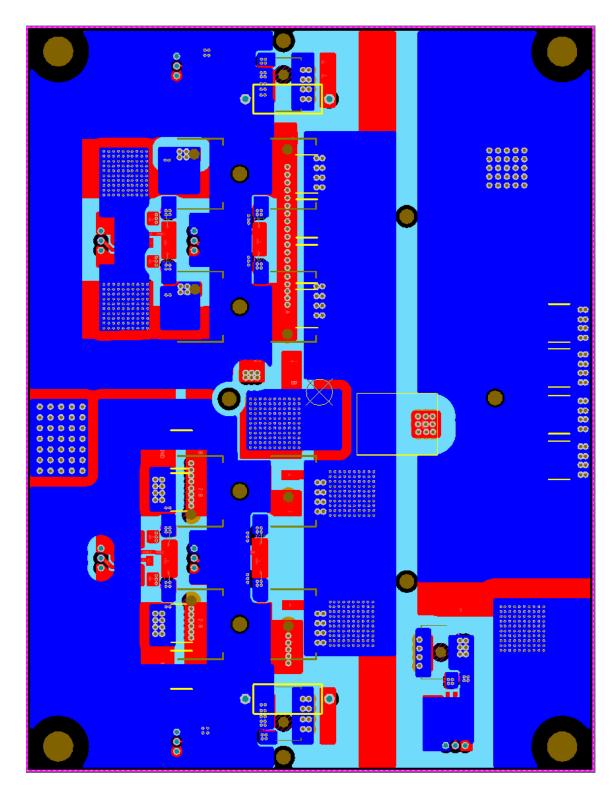

| Fig. 5.13. Main circuit board on four-layer PCB (bottom side) 20                                                                                                                                                                                                        |

| <i>Fig. 5.14. Size comparison of (a) 5 W resistor, 2 W resistor and GaN HEMT GS66508T (from top to bottom); (b) Output, input and auxiliary inductor (from left to right)</i>                                                                                           |

| <i>Fig. 5.15. Simulation results of the soft-switching converter for operation at 270-28 V, 200 kHz, 1.2 kW</i>                                                                                                                                                         |

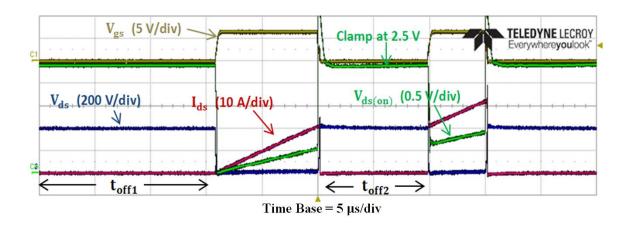

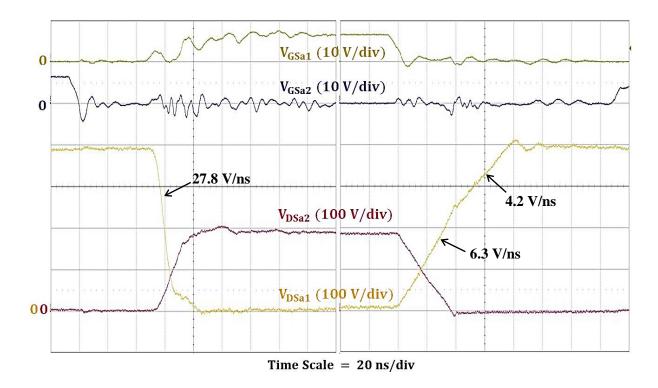

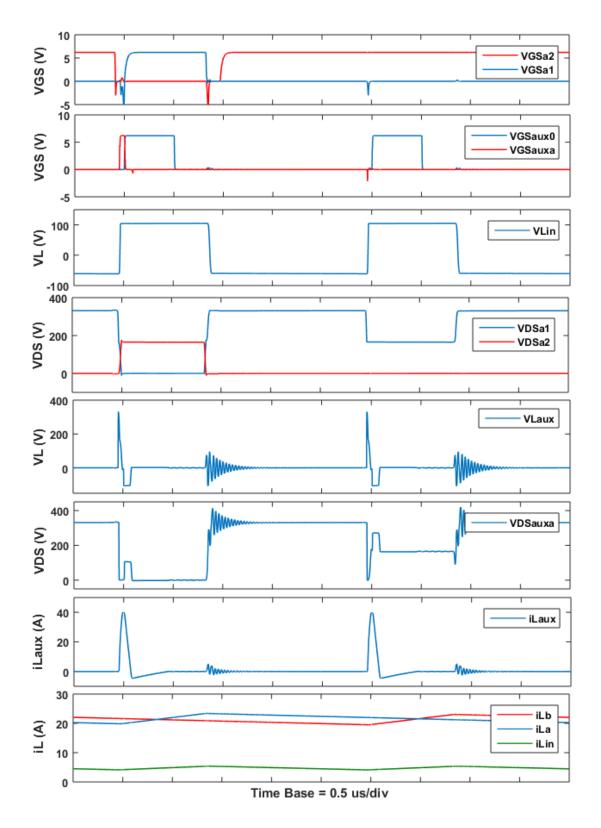

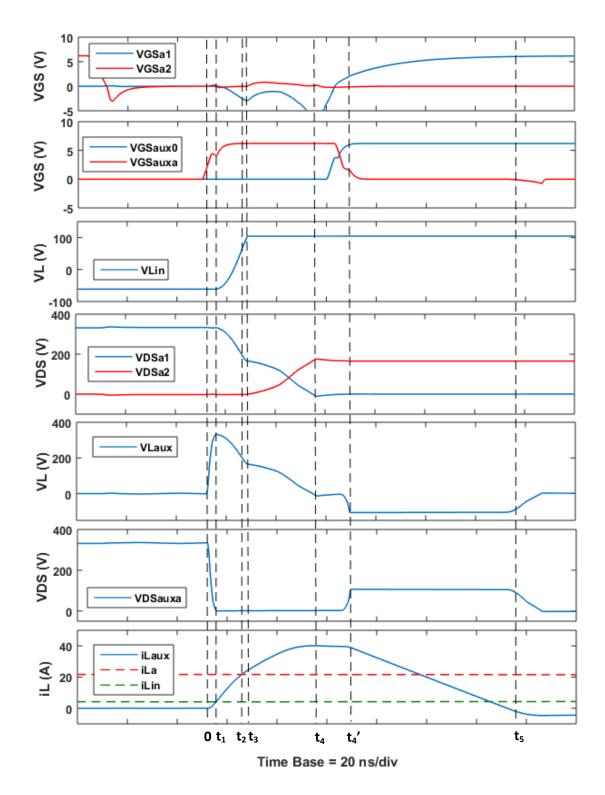

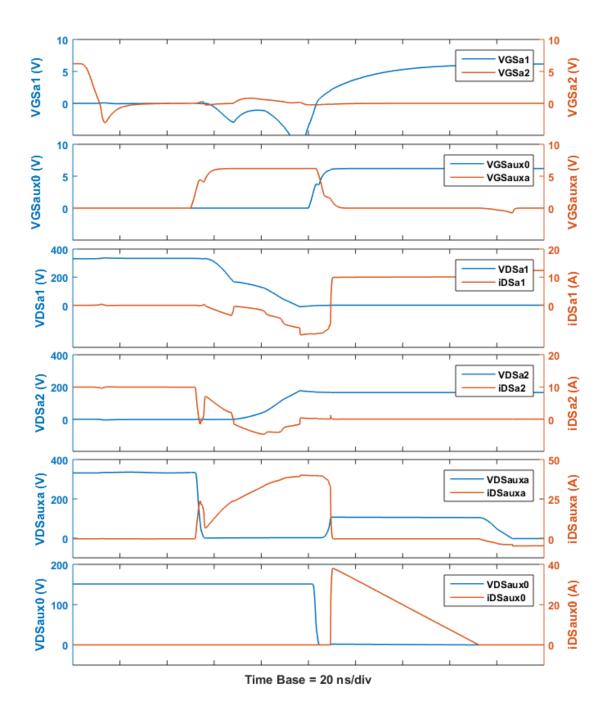

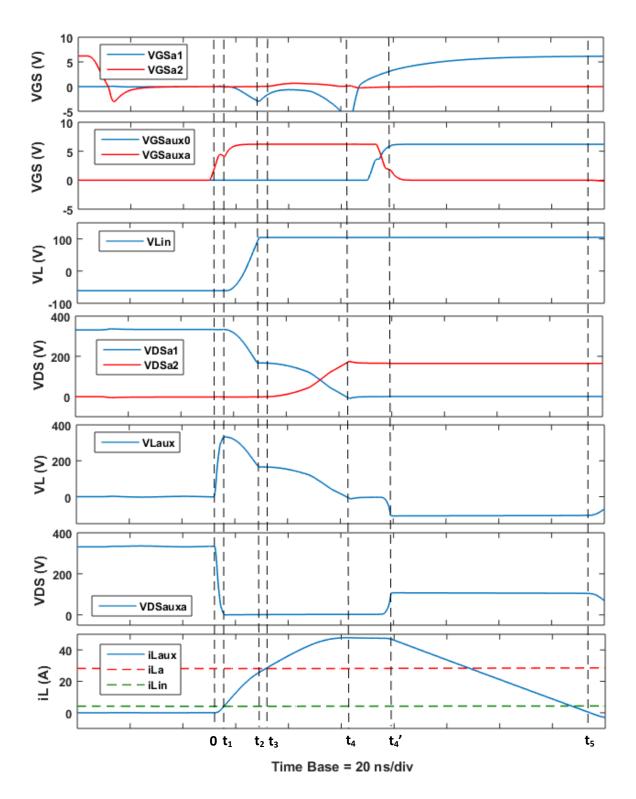

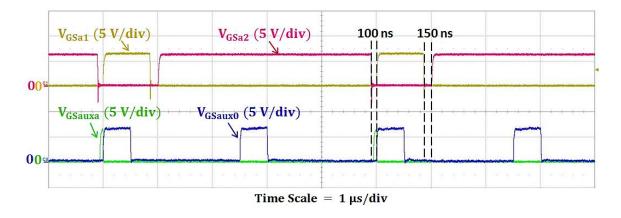

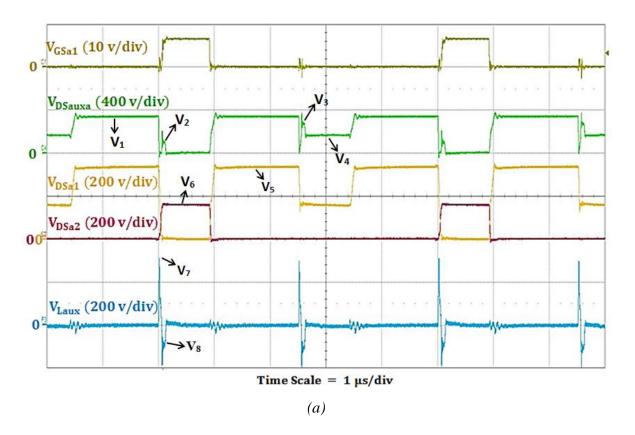

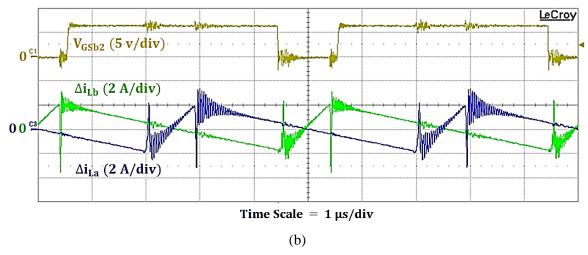

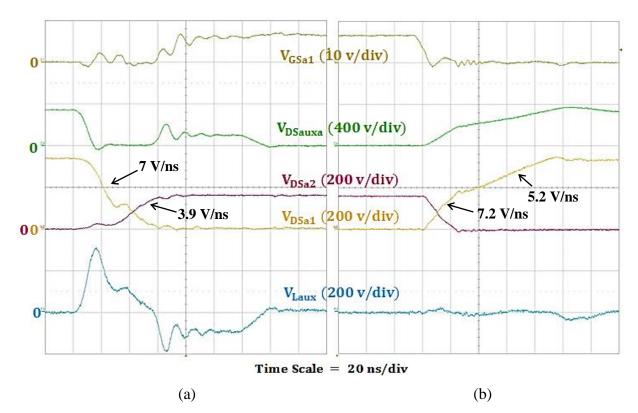

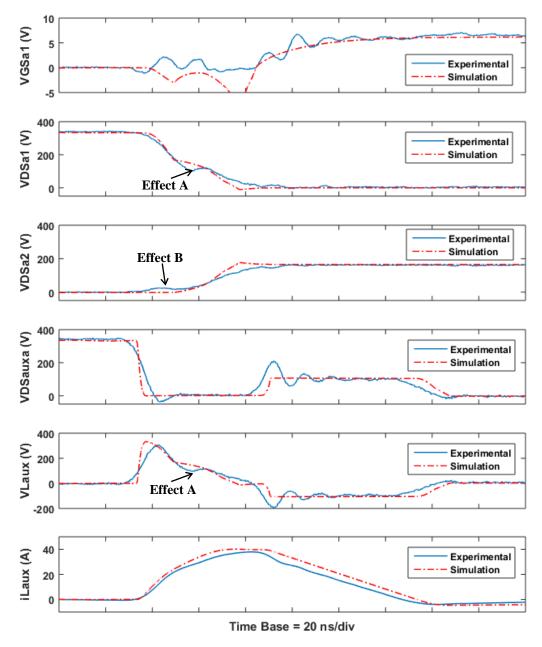

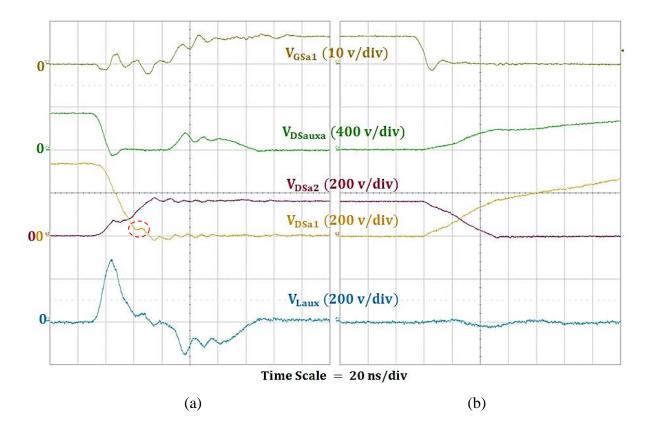

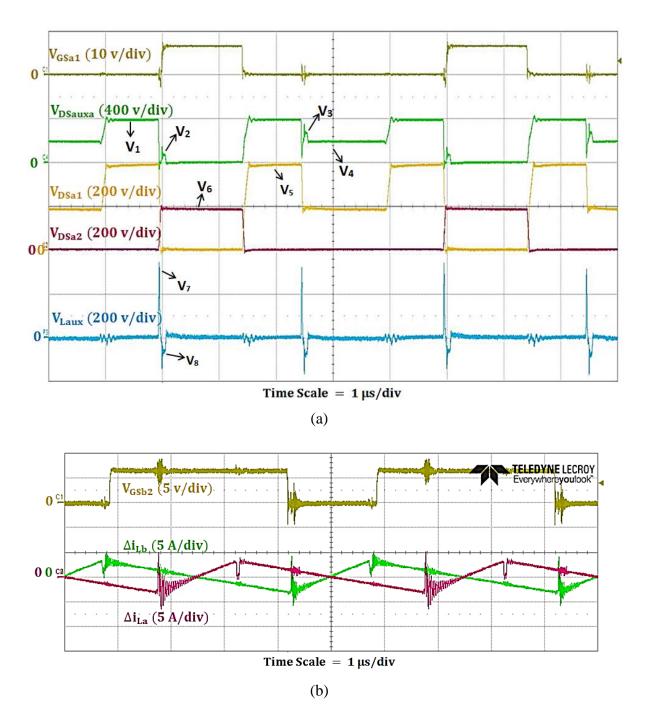

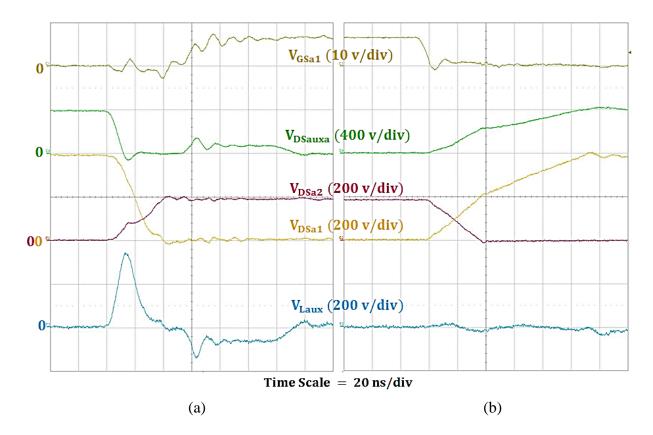

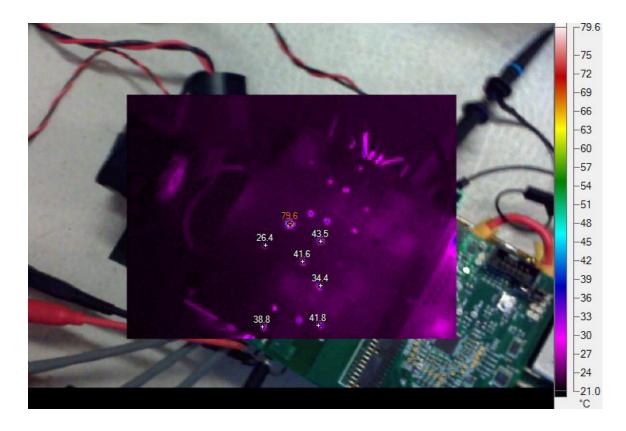

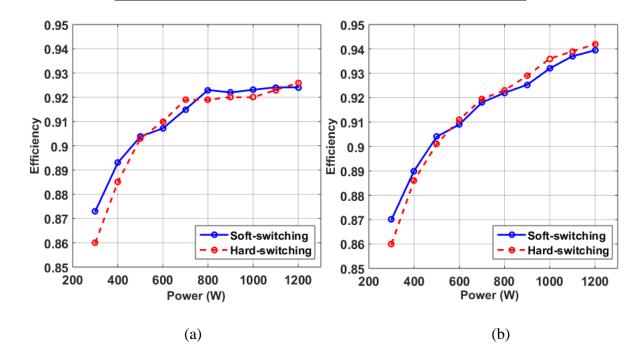

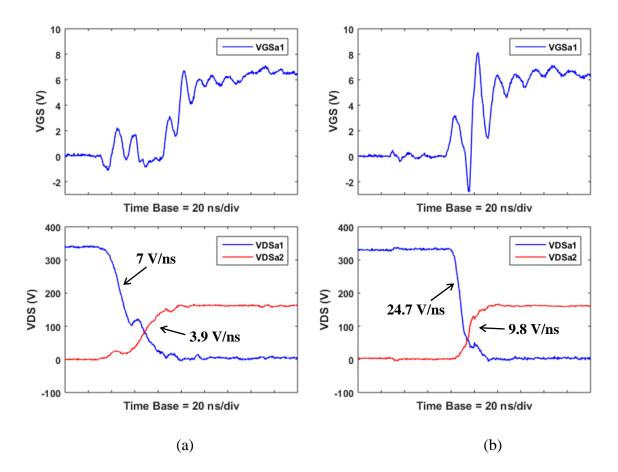

Fig. 5.16. Expanded simulation waveforms during  $0 \sim t_5$  where zero-voltage turn on of  $S_{a1}$ is achieved when operating at 270-28 V, 200 kHz, 1.2 kW...... 23 Fig. 5.17. Expanded simulation waveforms corresponding to Fig. 5.13 showing the transistor voltage and current at 270 V-28 V, 200 kHz, 1.2 kW...... 26 Fig. 5.18. Expanded simulation waveforms during  $t_0 \sim t_5$  where zero voltage turn on of  $S_{a1}$ is achieved when operating at 270-28 V, 200 kHz, 1.6 kW...... 28 Fig. 5.20. Experimental waveforms of (a) main and auxiliary transistor voltages and (b) ripple current of output inductors for  $V_{in} = 270.9$ ,  $V_o = 28.6$  V, f = 200 kHz,  $i_{out} = 39.1$  A,  $P_{in} = 1.21 \text{ kW} \text{ and } D = 0.17 \dots 30$ Fig. 5.21. Experimental waveforms during the switching transients of  $S_{a1}$  for  $V_{in} = 270.9$ ,  $V_o = 28.6 V$ , f = 200 kHz,  $i_{out} = 39.1 A$ ,  $P_{in} = 1.21 kW$  and D = 0.17 (a)  $S_{a1}$  turn-on Fig. 5.22. Comparison of experimental and simulation waveforms during  $t_0 \sim t_5$  for 270-28 Fig. 5.23. Experimental waveforms during the switching transients of  $S_{a1}$  for  $V_{in} = 270.9$ ,  $V_o = 28.3 V, f = 200 kHz, i_{out} = 14.6 A, P_{in} = 461 W and D = 0.17 (a) S_{a1}$  turn-on transient; Fig. 5.24. Experimental waveforms of (a) main and auxiliary transistor voltage and (b) ripple current of output inductors for  $V_{in} = 270.9$ ,  $V_o = 56.3$  V, f = 200 kHz,  $i_{out} = 20.2$  A,  $P_{in} = 1.21 \text{ kW} \text{ and } D = 0.29 \dots 35$ Fig. 5.25. Experimental waveforms during the switching transients of  $S_{a1}$  for  $V_{in} = 270.9$ ,  $V_o = 56.3 \text{ V}, f = 200 \text{ kHz}, i_{out} = 20.2 \text{ A}, P_{in} = 1.21 \text{ kW} and D = 0.29 (a) S_{a1} \text{ turn-on}$ Fig. 5.26. Thermal image of the prototype for operation at  $V_{in} = 270.9$ ,  $V_{out} = 28.6$  V, f =Fig. 5.27. Efficiency of hard-switching and soft-switching converter for operation at  $P_{in}$  = Fig. 5.28. Transistor gate and drain-to-source voltage when operating at 1.2 kW, 200 kHz,

### List of tables

| Table 2.1. Material Properties of Si, SiC and GaN [6]    2                                                         |

|--------------------------------------------------------------------------------------------------------------------|

| Table 2.2. Property comparison of GaN on different substrates [45]                                                 |

| Table 2.3. Dynamic $R_{ds(on)}$ contribution to the device total loss at different frequencies and load power [74] |

| Table 2.4. Main features of commercial PFCs from TI, Cree, Transphorm and GaN      Systems [87, 93-95]      22     |

| Table 2.5. WBG CLLC converter with variable frequency/DC link voltage [103]                                        |

| Table 2.6. key performance factors of the Si, SiC and GaN DAB converters [104] 27                                  |

| Table 3.1. Key parameters of candidate gate drivers    4                                                           |

| Table 3.2. Switching speed of the GaN Systems HEMT at 400 V, 40 A with different gate resistors                    |

| Table 3.3. Summary of the devices under test    18                                                                 |

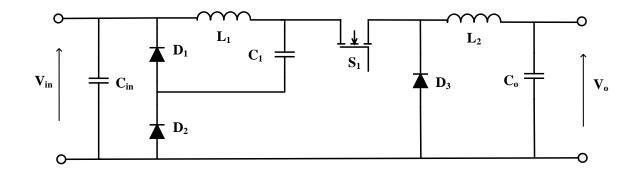

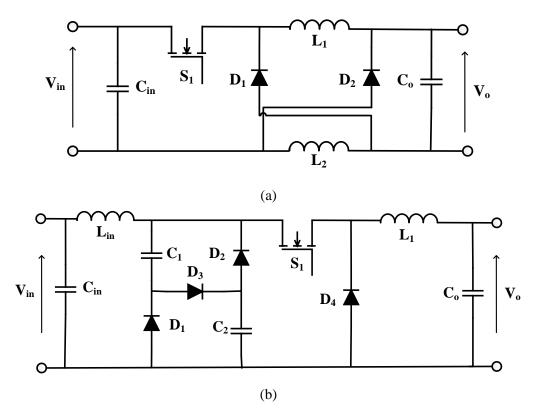

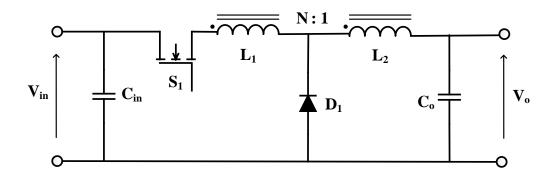

| Table 4.1. High-step-down ratio DC/DC converter topologies key features                                            |

| Table 4.2. Converter preliminary specification                                                                     |

| Table.4.3. Converter key components parameters    14                                                               |

| Table 4.4. Components thermal resistance    18                                                                     |

| Table 4.5. Circuit parasitic capacitance    19                                                                     |

| Table 4.6. Inductors winding resistance                                                                            |

| Table 4.7. Converter simulation output results    19                                                               |

| Table 4.8. Converter loss breakdown at 270-28 V, 200 kHz, 1.2 kW                                                   |

| Table 4.9. WBG-based and Si-based converter losses at 270-28 V, 200 kHz, 1.2 kW 34                                 |

| Table 4.10. Output inductor weight for the original WBG converter and Si-based converter                           |

| Table 5.1. Converter design target                                                                                 |

| Table 5.2. Circuit key parameters and design criteria                                                              |

| Table 5.3. Analytical and simulation results of key variables at 270-28 V, 200 kHz, 1.2 kW                         |

| Table 5.4. Switching conditions of main and auxiliary devices    25                                                |

| Table 5.5. Analytical and simulation results of key variables at 1.6 kW, 270 -28 V,200 kHz200 kHz |

|---------------------------------------------------------------------------------------------------|

| Table 5.6. Comparison of key voltage values between experimental and analytical results           |

|                                                                                                   |

| Table 5.7. Comparison of key voltage values between experimental and analytical results           |

|                                                                                                   |

| Table 5.8. Converter loss breakdown at 270-28 V, 200 kHz, 1.2 kW38                                |

| Table 5.9. Component case temperatures    39                                                      |

| Table 5.10. Hard-switching and soft-switching converter losses at 270-28 V, 200 kHz,1.2 kW40      |

## List of symbols

| А, В                                                     | Characteristic equation coefficients                                                            |

|----------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| A <sub>C</sub>                                           | Material contact area                                                                           |

| C <sub>in</sub>                                          | Input capacitor                                                                                 |

| Co                                                       | Output capacitor                                                                                |

| Coss_Sa1, Coss_Sa2                                       | Device output capacitance of $S_{a1}$ and $S_{a2}$                                              |

| C <sub>oss_D</sub>                                       | Sum of parasitic capacitance of $D_a$ , $D_b$ and $D_0$                                         |

| $C_a, C_b$                                               | Switched capacitors in phase a and b                                                            |

| $C_{T2}, C_{T3}, C_{T4}$                                 | Effective capacitances of soft-switching converter resonant circuits during sub-periods 2, 3, 4 |

| Cs                                                       | Snubber capacitance                                                                             |

| D                                                        | Main transistor duty ratio                                                                      |

| D <sub>a</sub> , D <sub>b</sub>                          | Switched diodes in phase $a$ and $b$                                                            |

| $D_0$                                                    | Switched diode between phase $a$ and $b$                                                        |

| D <sub>aux0</sub>                                        | Diode in the auxiliary circuit                                                                  |

| E <sub>sw</sub>                                          | Switching energy                                                                                |

| Eon, Eoff                                                | Switching energy during turn-on and turn-off                                                    |

| f                                                        | Switching frequency                                                                             |

| $\dot{i}_{in}, \dot{i}_{out}$                            | Converter input and output currents                                                             |

| i <sub>Lin</sub>                                         | Input inductor current                                                                          |

| i <sub>La</sub> , i <sub>Lb</sub>                        | Output inductor currents of phase $a$ and $b$                                                   |

| i <sub>Laux</sub>                                        | Auxiliary inductor current                                                                      |

| i <sub>ds</sub>                                          | Transistor drain current                                                                        |

| i <sub>DSa1</sub> , i <sub>DSa2</sub>                    | Drain currents of $S_{a1}$ and $S_{a2}$                                                         |

| i <sub>Channel_Sa1</sub> , i <sub>Channel_Sa2</sub>      | Channel currents of $S_{a1}$ and $S_{a2}$                                                       |

| $i_{Lin\_avg}, i_{La\_avg}, i_{Lb\_avg}$                 | DC currents of $L_{in}$ , $L_a$ and $L_b$                                                       |

| $i_{Lo\_avg}$                                            | DC current of the output inductors                                                              |

| $i_{oss\_Da}, i_{oss\_Db}, i_{oss\_D0}$                  | Parasitic capacitive currents of $D_a$ , $D_b$ and $D_0$                                        |

| $i_{oss\_Sa1}, i_{oss\_Sa2}, i_{oss\_Sb1}, i_{oss\_Sb2}$ | Parasitic capacitive currents of $S_{a1},S_{a2},S_{b1}$ and $S_{b2}$                            |

| i <sub>oss_Sauxa</sub> , i <sub>oss_Sauxb</sub>          | Parasitic capacitive currents of $S_{auxa}$ and $S_{auxb}$                                      |

| i <sub>error</sub>                                       | Quantization error in the current measurement                                                   |

| $\Delta i_{Lin}, \Delta i_{La}, \Delta i_{Lb}$           | Ripple currents of the input and output inductors                                               |

| $\Delta i_{Lo}$                                                                  | Output inductor current ripple                             |

|----------------------------------------------------------------------------------|------------------------------------------------------------|

| $\Delta i_o$                                                                     | Output capacitor current ripple                            |

| $\Delta i_{L-rms}$                                                               | RMS value of the inductor ripple current                   |

| K                                                                                | Material thermal conductivity                              |

| K <sub>dy</sub>                                                                  | Dynamic on-resistance increase coefficient                 |

| L <sub>in</sub>                                                                  | Input inductor                                             |

| $L_a, L_b$                                                                       | Output inductors of phase a and b                          |

| L <sub>aux</sub>                                                                 | Auxiliary inductor                                         |

| Ν                                                                                | Transformer/coupled inductor turns ratio                   |

| P <sub>in</sub>                                                                  | Converter input power                                      |

| Po                                                                               | Converter output power                                     |

| P <sub>sw</sub>                                                                  | Average Switching loss                                     |

| Pon, Poff                                                                        | Instantaneous power losses during turn-on and turn-off     |

| P <sub>con</sub> , P <sub>con-rev</sub>                                          | Transistor conduction and reverse conduction losses        |

| P <sub>con-D</sub>                                                               | Diode forward conduction loss                              |

| Qoss_mosfet                                                                      | Output charge of the Si MOSFET                             |

| $Q_{rr_MOSFET}, Q_{rr_diode}$                                                    | Reverse recovery charge of the Si MOSFET and diode         |

| R <sub>DC</sub>                                                                  | Inductor winding DC resistance                             |

| R <sub>AC</sub>                                                                  | Inductor winding AC resistance                             |

| R <sub>ds(on)</sub>                                                              | Transistor on-state DC resistance                          |

| R <sub>(1us)</sub>                                                               | Dynamic on-state resistance 1 µs after turn-on             |

| R <sub>S</sub>                                                                   | Snubber resistance                                         |

| R <sub>0</sub>                                                                   | Thermal resistance                                         |

| R <sub>JC-D</sub> , R <sub>JC-S</sub>                                            | Diodes and transistors junction-to-case thermal resistance |

| R <sub>PCB</sub> , R <sub>copper</sub> , R <sub>TIM1</sub> , R <sub>TIM2</sub> , | Thermal resistance of copper bar, thermal interface        |

| R <sub>HSA</sub>                                                                 | material and heatsink                                      |

| R <sub>error</sub>                                                               | Quantization error in the calculated resistance            |

| <b>S</b> <sub>1</sub> , <b>S</b> <sub>2</sub>                                    | Top and bottom device in converter leg                     |

| $S_{a1}, S_{a2}$                                                                 | Top and bottom device in leg $a$                           |

| $S_{b1}, S_{b2}$                                                                 | Top and bottom device in leg b                             |

| S <sub>auxa</sub> , S <sub>auxb</sub> , S <sub>aux0</sub>                        | Soft-switching converter auxiliary transistors             |

| t <sub>off1</sub> , t <sub>off2</sub>                                            | Transistor off-state time                                  |

|                                                                                  |                                                            |

| t <sub>0</sub> -t <sub>8</sub>                                  | Transition times of converter sub-periods                                       |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------|

| $T_1, T_2, T_3, T_4, T_5$                                       | Durations of converter sub-periods 1, 2, 3, 4, 5                                |

| Т                                                               | Switching period                                                                |

| $T_{M}$                                                         | Thickness of material                                                           |

| T <sub>sw</sub>                                                 | Switching time                                                                  |

| T <sub>con-rev</sub>                                            | Transistor reverse conduction time                                              |

| T <sub>con-D</sub>                                              | Diode conduction time                                                           |

| T <sub>DT</sub>                                                 | Dead time between the top and bottom transistors                                |

| TJ                                                              | Devices junction temperatures                                                   |

| T <sub>case</sub>                                               | Components case temperatures                                                    |

| T <sub>Ambient</sub>                                            | Ambient temperature                                                             |

| $V_{in}, V_o$                                                   | Converter input and output voltages                                             |

| V <sub>C</sub>                                                  | Switched capacitor voltage                                                      |

| $\Delta V_{Cin}, \Delta V_{Co}, \Delta V_{C}$                   | Ripple voltages of the input, output and switch capacitors                      |

| $\Delta V_{Ca}, \Delta V_{Cb}$                                  | Ripple voltages of C <sub>a</sub> and C <sub>b</sub>                            |

| $V_{\mathrm{f}}$                                                | Forward voltage drop of diodes and transistors                                  |

| $V_{GSa1}, V_{GSa2}$                                            | Gate-to-source voltage of $S_{a1}$ and $S_{a2}$                                 |

| V <sub>GSb1</sub> , V <sub>GSb2</sub>                           | Gate-to-source voltage of $S_{b1}$ and $S_{b2}$                                 |

| V <sub>GSauxa</sub> , V <sub>GSauxb</sub> , V <sub>GSaux0</sub> | Gate-to-source voltage of $S_{auxa}$ , $S_{auxb}$ and $S_{aux0}$                |

| V <sub>gs</sub>                                                 | Transistor gate-to-source voltage                                               |

| V <sub>ds</sub>                                                 | Transistor drain-to-source voltage                                              |

| V <sub>ds(on)</sub>                                             | Transistor on-state voltage                                                     |

| V <sub>DSa1</sub> , V <sub>DSa2</sub>                           | Drain-to-source voltage of $S_{a1}$ and $S_{a2}$                                |

| V <sub>Lin</sub>                                                | Input inductor voltage                                                          |

| V <sub>La</sub> , V <sub>Lb</sub>                               | Output inductor voltages of phase a and b                                       |

| V <sub>DC-link</sub>                                            | DC link voltage                                                                 |

| V <sub>oss</sub>                                                | Device output capacitor voltage                                                 |

| V <sub>1</sub> -V <sub>8</sub>                                  | Key voltage values in experimental waveforms                                    |

| V <sub>error</sub>                                              | Quantization error in the voltage measurement                                   |

| $\omega_{T2}, \omega_{T3}, \omega_{T4}$                         | Angular frequency of the converter resonant circuits during sub-periods 2, 3, 4 |

| δ                                                               | Auxiliary transistor $S_{auxa}$ and $S_{auxb}$ duty ratio                       |

| $\delta_2$                                                      | Auxiliary transistor $S_{aux0}$ duty ratio                                      |

### List of abbreviations

| 2DEG   | Two-dimensional electron gas                        |  |  |

|--------|-----------------------------------------------------|--|--|

| APM    | Auxiliary power module                              |  |  |

| BTP    | Bridgeless totem pole                               |  |  |

| BJT    | Bi-polar junction transistor                        |  |  |

| ССМ    | Continuous conduction mode                          |  |  |

| CRM    | Critical conduction mode                            |  |  |

| DCM    | Discontinuous conduction mode                       |  |  |

| DUT    | Device under test                                   |  |  |

| DPT    | Double pulse test                                   |  |  |

| DAB    | Dual active bridge                                  |  |  |

| DFM    | Design for manufacturing                            |  |  |

| EV     | Electric vehicle                                    |  |  |

| EMI    | Electromagnetic interference                        |  |  |

| FOM    | Figure of merit                                     |  |  |

| GIT    | Gate injection transistors                          |  |  |

| GaN    | Gallium Nitride                                     |  |  |

| HEMT   | High electron mobility transistor                   |  |  |

| IC     | Integrated circuit                                  |  |  |

| JFET   | Junction gate field-effect transistor               |  |  |

| MOSFET | Metal-oxide-semiconductor field-effect transistor   |  |  |

| OBC    | On-board charger                                    |  |  |

| PFC    | Power factor correction                             |  |  |

| PSFB   | Phase shift full bridge                             |  |  |

| РСВ    | Printed circuit board                               |  |  |

| PHEV   | Plug-in hybrid electric vehicle                     |  |  |

| Si     | Silicon Carbide                                     |  |  |

| SC     | Switched capacitor                                  |  |  |

| SL     | Switched inductor                                   |  |  |

| SJ     | Super junction                                      |  |  |

| SPICE  | Simulation program with integrated circuit emphasis |  |  |

| TIM    | Thermal interface material                          |  |  |

|        |                                                     |  |  |

| TI  | Texas Instruments       |

|-----|-------------------------|

| TCM | Triangular current mode |

| WBG | Wide band gap           |

| V2G | Vehicle to grid         |

| ZVS | Zero voltage switching  |

| ZCS | Zero current switching  |

### Abstract

This research has investigated the potential of emerging GaN power transistors to meet some of the power conversion challenges that are being posed by transport electrification. The switching performance, driving requirements and on-state characteristics of an example high current GaN HEMT are examined practically followed by the development and demonstration of a high-step-down-ratio DC-DC converter that includes a softswitching capability.

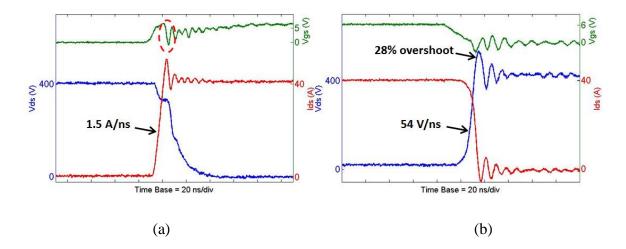

The GS66516T 650 V/60 A HEMT from GaN Systems that represents a typical GaN HEMT model, was shown to achieve a turn-on speed of 9.2 A/ns with a current overshoot of 32% and a turn-off speed of 94.7 V/ns with a voltage overshoot of 45%, resulting in a total switching loss of less than 150  $\mu$ J at 400 V, 40 A. The significance of the driver selection and parasitic component optimization were highlighted and the ultra-low turn-off loss mechanism of the GaN HEMT was identified.

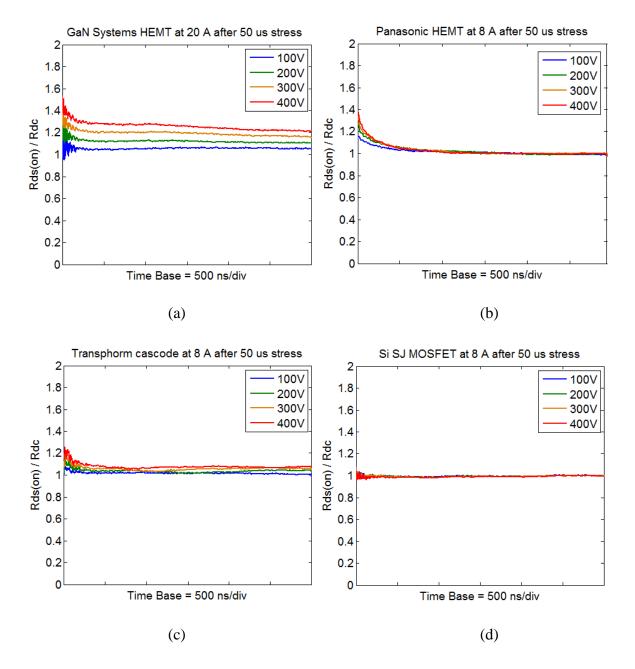

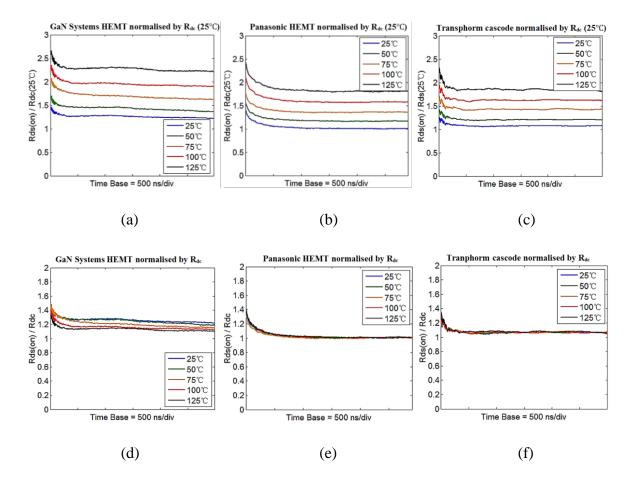

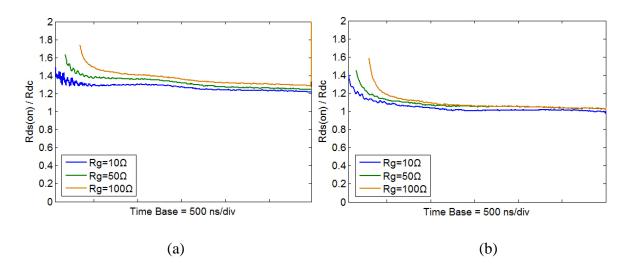

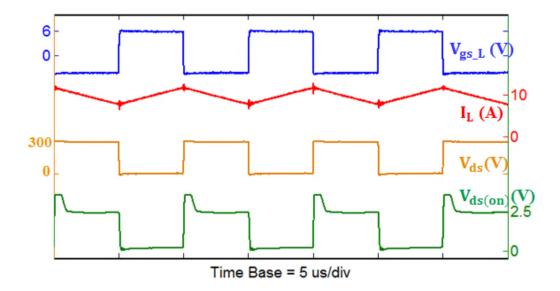

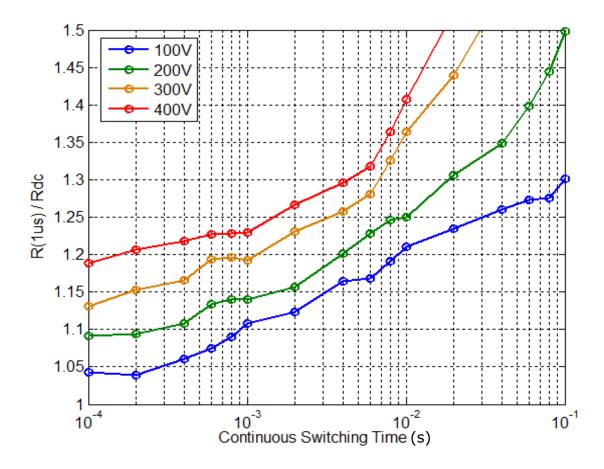

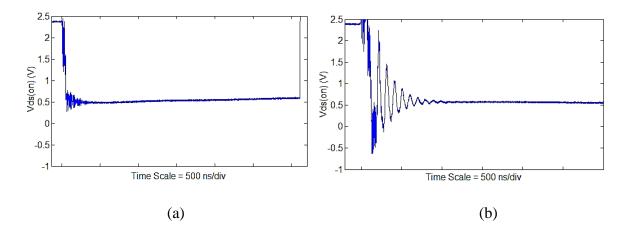

The dynamic on-state resistance of three GaN devices were measured over a range of conditions that are often encountered in converter applications. Significant variations were observed between device types. An increase in dynamic on-state resistance of 20~30% was observed for the GaN Systems device within 3 µs of turn-on after 50 µs of 400 V stress voltage. The dynamic on-state resistance was largely insensitive to temperature but depended on the switching energy. During continuous operation, an increase of 50.4% in average on-state resistance of the GaN Systems device was observed when operating at 400 V, 10 A, 400 kHz and 0.5 duty ratio.

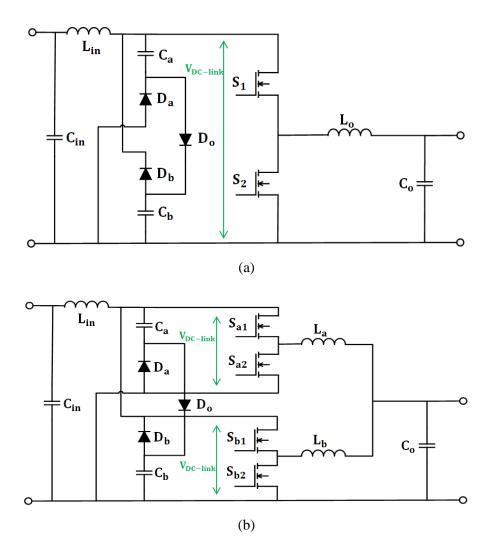

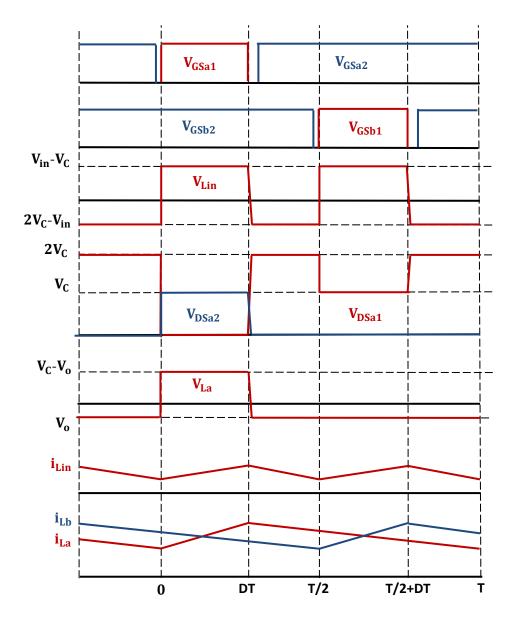

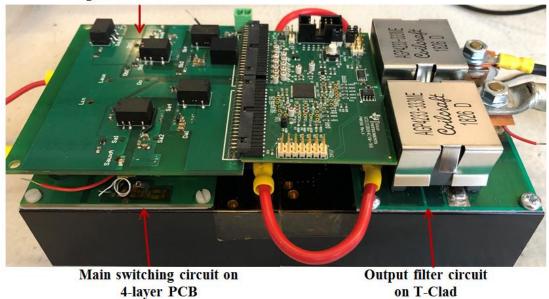

The switched-capacitor, step-down DC-DC converter topology was extended to an interleaved configuration, enabling increased output currents, and its performance was evaluated in a 270-28 V, 200 kHz, 1.2 kW prototype, paying particular attention to the switching waveforms. Furthermore, a multi-layer assembly was used to provide compact electrical and thermal connections. The efficiency of 92.6% represented a five percentage point increase over an equivalent silicon design. A soft-switching topology was then developed to control the switching losses and dv/dt levels by adding a small auxiliary circuit. The converter overall efficiency remained similar due to the introduced auxiliary losses but the converter reliability was significantly improved due to the reduced stress in the GaN transistors.

### Declaration

No portion of the work referred to in the thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

### **Intellectual Property Statement**

The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made only in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

The ownership of certain Copyright, patents, designs, trademarks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the University IP Policy (see http://documents.manchester.ac.uk/DocuInfo.aspx?DocID=24420), in any relevant Thesis restriction declarations deposited in the University Library, The University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on Presentation of Theses.

### Acknowledgement

I would like to express my gratitude to my supervisors, Professor Andrew Forsyth and Dr Rebecca Todd for their guidance and advice throughout my project study.

I would like to thank to Dr Gerardo Calderon Lopez for his suggestions and help. Many thanks to Dr Alejandro Villarruel Parra, Dr Md Rishad Ahmed, Dr Ding Wu for their help at different phases of the project. Also I am thankful to all my fellow students in the Power Conversion Group and my friends in the UK for their friendship and support.

Finally, I am deeply grateful to my parents for their unconditional love, understanding and constant support.

# **Chapter 1**

# Introduction

#### 1.1 Background

The advance of technology and the drive for more sustainable forms of energy use in the field of transportation, industrial automation, internet services, entertainment and electronic consumer goods has led to an ever-increasing demand on electrical power. Up to 2018, the electricity production in the UK had increased by 38.4% to 1473.5 TWh compared to 2010, of which 30.9% was consumed for industrial use, 35.1% for domestic use, 1.6% for transportation and 32.4% for other services [1].

The increasing use of electrical power has intensified the demand for reliable and costeffective technologies and systems to manage and convert the power according to the demands of different applications. This is producing an ever-growing range of conversion requirements in terms of voltage and current, however, achieving high efficiency and small equipment size remain important for all applications, especially for mobile and transport systems.

In addition to the increasing demands from applications, the power electronic industry is undergoing a period of revolutionary change due to the emergence of new power semiconductor technologies based on wide bandgap (WBG) materials such as silicon carbide (SiC) and gallium nitride (GaN). These materials offer the prospect of new devices with lower on-state losses, faster switching speeds, higher blocking voltages and increased junction temperatures than existing silicon devices.

Whilst these new devices offer the opportunity of making a step-change in converter performance, there are many unknowns and challenges including, the detailed characteristics of the devices, the most-effective driving techniques, the best packaging and interconnection techniques and the most suitable converter topologies. This work identified some emerging challenges for WBG-based converter applications and demonstrated the performance benefits in a GaN-based DC-DC converter case.

#### 1.2 Aim and objectives

The aim of this research was to investigate how WBG devices particularly GaN devices could enable performance improvements for power converters in some of the emerging applications in transport systems.

The first objective was to characterize the switching performance and the dynamic on-state resistance of commercial GaN HEMTs rated at 600 V/650 V. These characteristics directly link to the device switching and conduction losses in converter applications.

The second objective was to identify a suitable converter topology for potential high-stepdown-ratio DC-DC transportation applications, validate the topology in a converter prototype and demonstrate the performance boost by using WBG technology.

The third objective was to enhance the selected converter topology through the use of softswitching, and demonstrate the further improvement in the converter performance.

#### **1.3 Thesis structure**

Chapter 2 presents a review of the main publications regarding the current status of commercial WBG devices, the characteristics of GaN devices and the application of WBG devices in the hybrid and EV sector.

Chapter 3 describes the experimental characterization of commercial GaN transistors in terms of switching performance and dynamic on-state resistance, requiring the development of testing methodologies. The experimental measurements for switching speed, switching losses and dynamic on-resistance over a range of conditions are presented.

Chapter 4 describes the selection and validation of a WBG-based, high-step-down ratio, DC-DC converter topology including detailed analysis of the device switching waveforms, prototype design and performance evaluation. The superiority of the WBG-solution was assessed by comparison with a conventional Si-solution.

Chapter 5 presents the development and validation of a soft-switching technique for the high step-down-ratio DC-DC converter in Chapter 4. Detailed analysis of the circuit operation was undertaken forming a basis for prototype design. Experimental results for performance comparison with the hard-switching converter were collected and presented.

Chapter 6 presents the conclusions of the research work, its contributions and identifies further research opportunities.

# **Chapter 2**

# **Literature Review**

#### **2.1 Introduction**

This chapter introduces the emerging wide-band-gap material and power devices, including the current status and characteristics of GaN power devices, followed by a review of high-performance, high-power-density converters for transportation applications using WBG technology. Several high-conversion-ratio DC-DC converter topologies are also reviewed.

#### 2.2 Emerging device technology

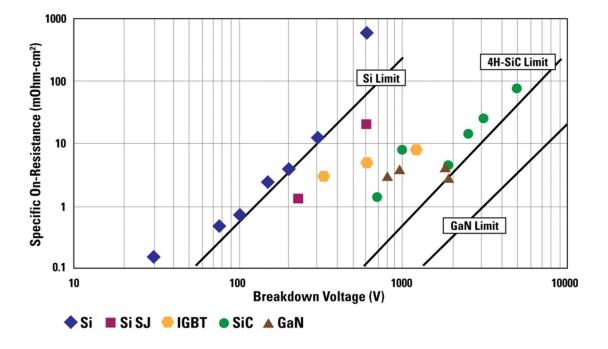

Since the 1960s power semiconductor devices have been based on silicon technology [2]. However, with incremental advances in the device design, manufacturing, fabrication and assembly processes, the performance of Si devices is approaching the theoretical limit of the material. For instance, the Infineon IPB025N10N3G 100V MOSFET has pushed the specific on-state resistance to less than 0.1  $\Omega/\text{mm}^2$ , which is almost at the theoretical limit of a one-dimensional Si device [3].

#### 2.2.1 WBG material

As alternatives, wide bandgap (WBG) materials such as SiC and GaN have emerged and drawn growing attention for power applications. The material bandgap is used to describe the energy required for an electron to jump from the top of the valence band to the bottom of the conduction band within the semiconductor. Typically, materials with bandgaps greater than that of silicon, 1 eV, are referred to as wide bandgap material [4].

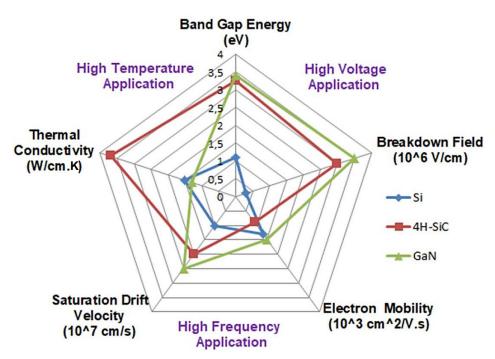

Table 2.1 and Fig. 2.1 show the material properties for Si, SiC (SiC-4H) and GaN which also include the major electrical characteristics for the corresponding semiconductor devices [5]. The wide bandgap and higher critical field of SiC and GaN material indicates that a smaller/thinner die could block a certain voltage, potentially leading to lower on-state voltage and smaller parasitic capacitances. It also means that the device has the potential of operating at higher temperature with lower leakage current [6]. The electron

mobility and electron saturation velocity influence the device on-state resistance [7]. GaN material shows the greatest potential in this aspect, which suggests that GaN-based power devices could offer the smallest on-state resistance associated with high breakdown voltage, exceeding the limits of Si and SiC material shown in Fig 2.1. These features make GaN-based devices the most promising candidate for high frequency applications, but less competitive than SiC-based devices for applications aiming at particularly high ambient temperature [8].

| -                                                  |      |        |     |

|----------------------------------------------------|------|--------|-----|

| Materials Property                                 | Si   | SiC-4H | GaN |

| Band Gap (eV)                                      | 1.1  | 3.2    | 3.4 |

| Critical Field (MV/cm)                             | 0.3  | 2.2    | 3.3 |

| Electron Mobility $(10^3 \text{ cm}^2 \text{V/s})$ | 1.45 | 0.9    | 2   |

| Electron Saturation Velocity $(10^7 \text{ cm/s})$ | 1    | 2.2    | 2.5 |

| Thermal Conductivity (W/cmK)                       | 1.5  | 3.8    | 1.3 |

Table 2.1 Material Properties of Si, SiC and GaN [5]

Fig. 2.1. Material properties comparison of Si, SiC and GaN [9]

#### 2.2.2 Off-the-shelf WBG devices

Fig. 2.2 shows the one-dimensional theoretical limit of Si, SiC and GaN, and maps the position of some commercial product samples. It can be seen that current commercial Si MOSFETs are reaching the material one-dimensional theoretical limit, whilst SiC and GaN materials have provided greater opportunity for manufacturers to fabricate devices

with smaller size and better FOM (input charge  $\times$  on-state resistance) for a given breakdown voltage [9].

Fig. 2.2. Specific on-resistance vs breakdown voltage for Si, SiC and GaN commercial products and the material one-dimensional limits [9]

A number of commercial WBG power products have been released in recent years and demonstrated very attractive electrical characteristics.

The SiC Schottky diode was the first commercialized SiC power device. The Infineon-IDW15S120 was released in 2001, which successfully extended the breakdown voltage limitation of 200 V for Si Schottky diodes to above 1 kV [10]. The SiC diode is a majority carrier device, and does not have reverse recovery phenomenon. On the other hand, a SiC diode has a higher forward voltage drop than a Si Schottky diode due to the larger band-gap energy, causing higher conduction losses. However, the forward voltage drop shows a positive temperature coefficient, making it suitable for parallel connection [11].

The SiC JFET was commercialized in 2008 by SemiSouth [12]. Although the SiC JFET is easier to implement and has a better gate oxide-semiconductor interface quality than a SiC MOSFET, the normally-on feature in the early devices made it undesirable due to fault protection issues [13]. A cascode configuration with a low-voltage normally-off Si-MOSFET can be used to address this issue. A cascode 1.2 kV SiC JFET was released in 2012 [14].

The SiC MOSFET was first introduced by Cree (Wolfspeed) in 2011 [15]. The initial concerns around the SiC MOSFET such as gate instability and junction robustness at high temperature were quickly overcome in the following years as Cree released their third generation 1.2 kV SiC MOSFET [16]. In addition, major manufactures such as Infineon, STMicroelectronics, ROHM have also developed their own 1.2 kV SiC MOSFET models since 2012 [17]. Up to now, SiC MOSFETs rated at 1.2 kV /90 A and modules rated up to 1.7 kV/225 A are commercially available [18].

Apart from the reduced die size and low parasitic capacitance, SiC MOSFETs also have compelling advantages in terms of the on-state resistance at elevated temperatures due to the wide bandgap, for example only a 20% increase in the DC resistance occurs when the junction temperature increases from 25 °C to 135 °C, whereas that of the Si MOSFET increases by 250% [13]. Also, the gate leakage current of SiC MOSFETs remains at a very low level with elevated temperature, whilst that of Si MOSFETs can increase around 100 times when the junction temperature increases from 25 °C to 135 °C to 135 °C [13]. The body diode of SiC MOSFETs normally has a forward voltage drop of around 3 V which is five times that of Si MOSFETs, however the reverse recovery time is much smaller [19].

SiC BJTs became available in 2012 from Fairchild and are currently mainly available from GeneSiC [20]. 1.2 kV/100 A discrete models and 1.2 kV/160 A modules have now been released by GeneSiC. The SiC BJT provides the lowest specific on-resistance, therefore has the smallest chip size and parasitic capacitance for a specific voltage and current. It also has no oxide layer and is capable of operating at a high junction temperature of up to 175°C [21]. However, as it is a current-controlled device, the SiC BJT tends to a have high driving loss. A current gain of 50-70 was typical in the commercial SiC BJT from Fairchild [13].

The GaN high-electron-mobility transistor (HEMT) was first introduced commercially as a depletion-mode (normally-on) transistor, and was released as an enhancement-mode (normally-off) device in 2009 [22]. The first commercial GaN switch rated at 200 V/3 A was produced by Efficient Power Conversion (EPC) in 2012 [23]. Significant progress has been made since then and a wide range of GaN HEMTs is now commercially available up to 650 V.

Some major GaN device manufacturers and their GaN devices are listed as follows.

Efficient Power Conversion Corporation (EPC) was the first company to introduce the concept and commercialize enhancement-mode GaN power transistors. The company now provides a wide range of GaN FETs (eGaN) and ICs up to 300 V. The third generation eGaN offers the conduction figure of merit of 8.5 nC ×10 m $\Omega$  [24].

Panasonic has released a series of enhancement mode 600 V GaN transistors rated up to 26 A, namely X-GaN, providing a figure of merit of 32 nC  $\times$ 70 m $\Omega$ . The company claimed that the new X-GaN products have very low gate leakage and are current-collapse-free due to an additional p-GaN plate near the drain [25].

Infineon has released 400 V and 600 V enhancement-mode GaN transistors rated at up to 31 A with a figure of merit of 4.5 nC ×70 m $\Omega$  for the 400 V device and 5.8 nC ×70 m $\Omega$  for the 600 V device [26].

Transphorm has produced a series of 600 V GaN devices in cascode configuration up to 47 A. The latest product TP65H035 offers a figure of merit of 9 nC  $\times$ 35 m $\Omega$  [27].

GaN Systems offers 100 V and 650 V GaN power transistors rated up to 60 A, which is the highest current in the market. The device has a figure of merit of 12 nC  $\times$ 25 m $\Omega$  and an ultra-low device parasitic inductance due to the special packaging technique [28].

Other manufacturers such as Cambridge Electronics, Exagan, MicrogaN, Nexperia have also been developing GaN transistors at similar or higher ratings with better performance and lower cost [29-31].

Up to now, most of the GaN manufacturers have focused their development effort on the transistors below 1 kV, as SiC MOSFETs currently dominate the market of 1.2 kV and above. However, some SiC manufacturers such as STMicroelectronics and ROHM have extended their device portfolio to 650 V/100 A, leading to competition with GaN HEMTs in the medium voltage market [32, 33]

#### 2.2.3 Structure of GaN power devices

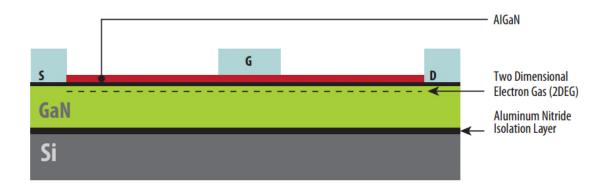

Unlike SiC or Si MOSFETs, the commercial GaN HEMTs have a lateral structure, shown in Fig. 2.3. The two-dimensional-electron-gas (2DEG) formed between the AlGaN and GaN heterostructure interface has a high concentration of electrons, providing a very low on-state resistance and high current density. To make a good ohmic contact between the electrodes and 2DEG, recess etching is conducted to allow the ohmic electrodes to pierce through the AlGaN layer creating a short circuit until all the high mobility electrons in the 2DEG layer are depleted [34]. Therefore, a negative voltage on the gate with respect to drain and source electrodes is required to deplete the electrons and turn off the device. However, the depletion-mode transistor is not well suited to many converter applications, and may cause short circuit faults during start-up or under abnormal conditions.

Fig. 2.3. Basic structure of GaN HEMT from EPC [34]

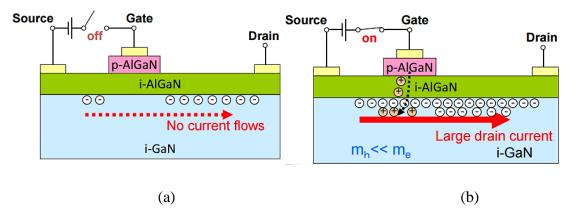

Fig. 2.4. Normally-off GaN HEMT using GIT at (a) off-state and (b) on-state [35]

To achieve normally-off behaviour, several methods have been proposed. The approach adopted by EPC and Panasonic is the GIT (gate injection transistor) technology – applying a processed gate electrode with p+ extension. As shown in Fig. 2.4 [35], at a gate-source voltage of 0V, the acceptors in the Schottky-type gate metal deplete the 2DEG of the transistor channel and no drain current flows. When the gate-source bias is higher than the threshold voltage, holes from the p-AlGaN are injected into the channel and produce a large number of electrons. The electrons then flow to the drain electrode with high mobility under the drain bias, resulting in a high drain current, whilst the holes stay around

the gate due to their low mobility. The drawback of this method is that the threshold voltage is quite low, normally around +1V (similar to the forward bias voltage of a p-n junction) [36]. Some additional process and surface treatments have been proposed to lift the threshold voltage to around +3V [37-40].

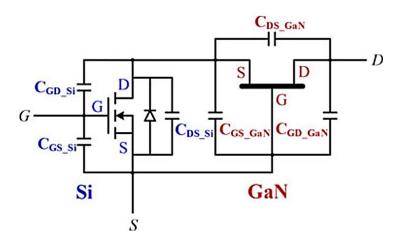

Another widely adopted approach is the cascode configuration in which a depletion mode HEMT is connected in series with a low voltage normally-off Si MOSFET, shown in Fig 2.5. Several generations of commercial cascode GaN transistors up to 600 V are currently available. As the cascode device is controlled via the Si MOSFET, it has the benefits of a robust gate with high threshold voltage and a good compatibility with common Si MOSFET driving solutions. However, the packaging of current commercial cascode GaN transistors causes relatively high parasitic inductance effects. Advanced packaging techniques such as the chip-on-chip technique are therefore in demand [41, 42]. The configuration also has disadvantages such as the mismatch of the parasitic charge between the Si MOSFET and the GaN transistor, which may lead to additional losses and reliability degradation [7, 42].

Fig. 2.5. Schematic of cascode GaN transistor [41]

Besides the normally-on nature of the basic GaN HEMT, another limitation to commercializing the technology is that large area and low cost wafers are currently not available. Therefore, unlike SiC devices that are grown on the epitaxial layer of same material, another material is normally used as the substrate for GaN devices without sacrificing too much performance. Si is the most commonly used material due to the low cost and scalability to large diameter processing. However, silicon has a relatively large lattice mismatch with GaN, which can lead to a large number of defects [43, 44]. Applying

an AlN seed layer between the epitaxial layer and the substrate is an effective solution due to the better lattice match between AlN and GaN, which also smooths the rough surfaces and crack formations [45].

Nevertheless, GaN transistors on a GaN substrate remain a long term ambition as this removes the electrical degradation caused by the dislocation (lattice mismatch) and enables the fabrication of vertical GaN transistors which should reduce the leakage current and defect density, and achieve higher breakdown voltage due to the thicker drift region. A comparison of GaN device characteristics on different substrate materials is shown in Table 2.2 [46]. NEXGEN has been researching GaN-on-GaN transistors since 2015 and plans to enter a full-scale production for bulk GaN transistors in 2019 [47].

| Device Area →<br>Carrier Wafer →   |                 | GaN<br>SiC        | GaN<br>GaN                         |

|------------------------------------|-----------------|-------------------|------------------------------------|

| Attribute                          | GaN-on-Si       | GaN-on-SiC        | GaN-on-GaN                         |

| Defect Density [cm <sup>-2</sup> ] | 10 <sup>9</sup> | 5x10 <sup>8</sup> | 10 <sup>3</sup> to 10 <sup>5</sup> |

| Lattice Mismatch [%]               | 17              | 3.5               | 0                                  |

| CTE Mismatch [%]                   | 54              | 25                | 0                                  |

| Layer Thickness [µm]               | 1-2             | 2-6               | > 40                               |

| Reliability                        | Low             | Low               | High                               |

| Device Types                       | Lateral         | Lateral           | Vertical<br>& Lateral              |

Table 2.2 Property comparison of GaN on different substrates [46]

The development of the GaN diode has attracted less interest from manufactures, mostly because the SiC diode is mature and well established in the market. Also, a GaN diode using a lateral AlGaN/GaN structure presents a worse trade-off between the turn-off characteristics and forward voltage drop compared to a SiC Schottky-barrier diode due to the high charge density of the 2DEG [48]. Most of the research on GaN diodes is focused on vertical structures, which provide higher breakdown voltage, better thermal performance, and lower charge density in the drift layer than is present in the 2DEG [49, 50]. Similar to the case with transistors, a vertical diode on bulk GaN will have lower defect density and leakage current, and the thicker drift region should increase the breakdown voltage [50]. However, Some GaN-on-Si Schottky diodes with passivation and

field plate structures have also been demonstrated to exhibit similar performance as bulk GaN-on-GaN diodes [51].

#### 2.3 Characteristics of GaN HEMTs

Due to the superior material property, GaN devices have tremendous potential for enabling high-frequency, high-performance converters. Understanding the characteristics of GaN HEMTs is crucial for exploiting the full device advantages in converter applications.

#### 2.3.1. Switching characteristics

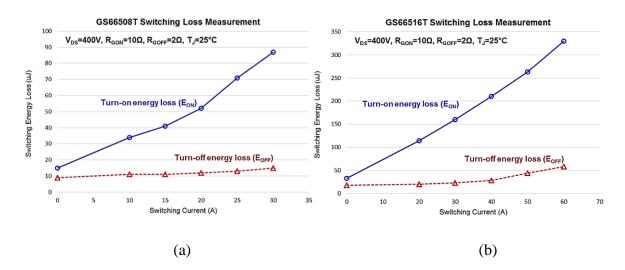

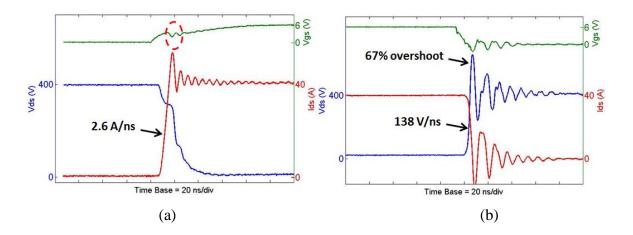

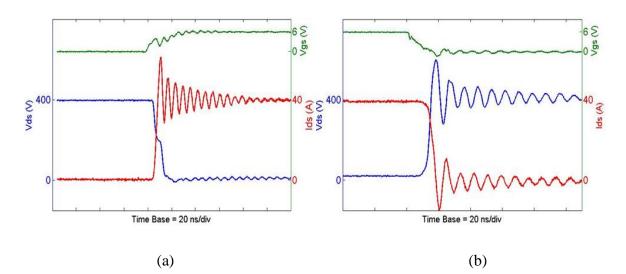

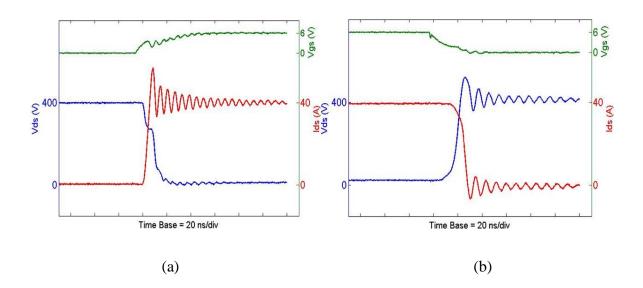

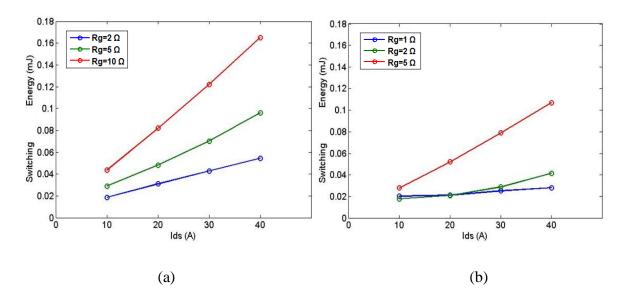

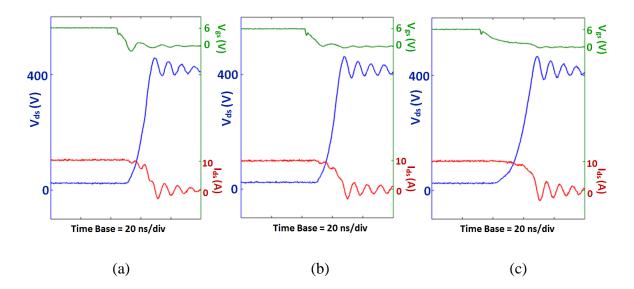

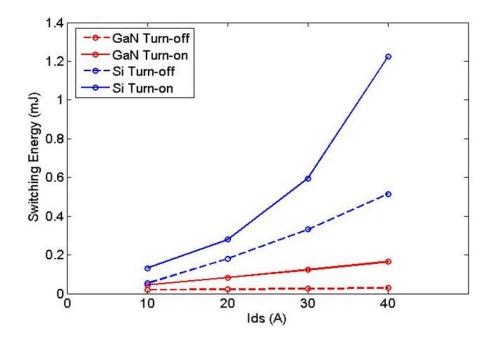

GaN Systems has presented experimental switching test results for their top-cooled 650 V/60 A and 650 V/30 A GaN HEMTs, GS66516T and GS66508T, using a double-pulse-tester (DPT) circuit and a half-bridge synchronous buck converter [52]. The switching losses of the two GaN HEMTS are shown in Fig. 2.6. The total switching loss of the GS66508T, 650 V/30 A, is only around 60  $\mu$ J at 400 V 20 A due to the very fast switching speed of 70 V/ns at turn-on and 40 V/ns at turn-off, whilst the switching loss of the GS66516T, 650 V/60 A, is less than 250  $\mu$ J at 400 V 40 A.

Fig. 2.6. Switching losses of the (a) 650 V/30 A and (b) 650 V/60 A GaN HEMTs [52]

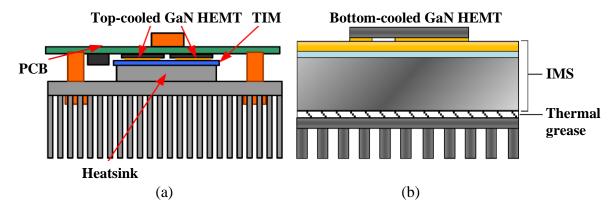

The efficiency of a 400-200 V 100 kHz buck converter using the 30 A and 60 A devices operating at 2 kW and 2.4 kW was demonstrated to be above 98.5% and the device junction temperatures were measured to be less than 75°C with foced-air cooling [52, 53]. The company also released a bottom-cooled version for the 60 A device, GS66516B, and demonstrated its performance in a 400-200 V 80 kHz buck converter using an insulated-

metal-substrate (IMS) half-bridge module. A full-load efficiency of 98.8% was achieved with a device maximum junction temperature of less than 65 °C [54]. The thermal configuration for the top-cooled device mounted on a PCB and the bottom-cooled device with an IMS board is shown in Fig. 2.7 [52, 54].

Fig. 2.7. Thermal management of the (a) top-cooled and (b) bottom-cooled GaN HEMTs [52, 54]

The switching characteristic of a 600 V/2 A vertical GaN-on-GaN chip was evaluated in [55]. A turn-on speed of 70 V/ns and turn-off speed of 33 V/ns were demonstrated when switching at 450 V 2 A, which resulted in energy losses of 8.1  $\mu$ J and 3  $\mu$ J respectively.

A 600 V/ 15 A cascode GaN transistor from Transphorm was characterized in [56]. The switching speeds during turn-on and turn-off at 400 V 10 A were measured to be 87 V/ns and 43 V/ns respectively, resulting in a total energy loss of 70.6  $\mu$ J. It was also demonstrated that replacing the upper GaN device with a SiC diode in the DPT circuit reduced the total switching loss by 21  $\mu$ J due to the smaller output charge of the freewheeling device.

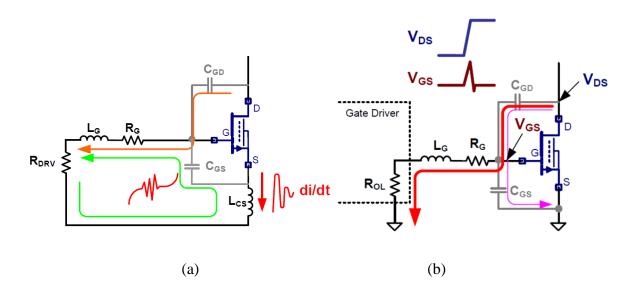

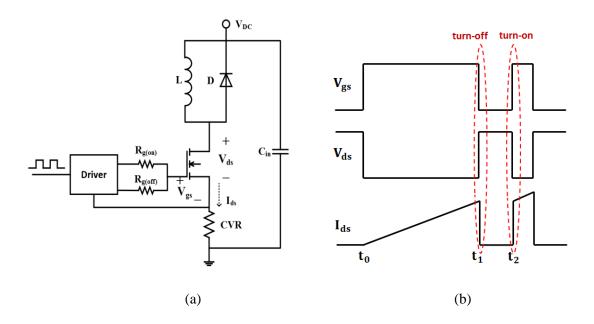

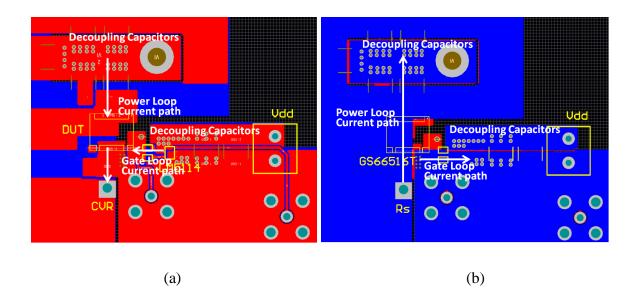

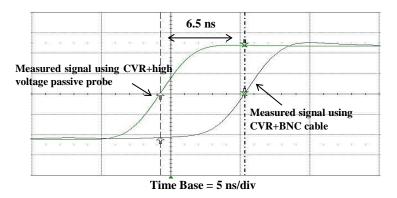

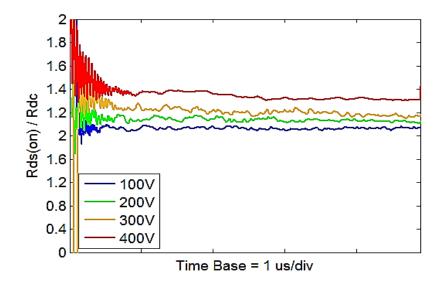

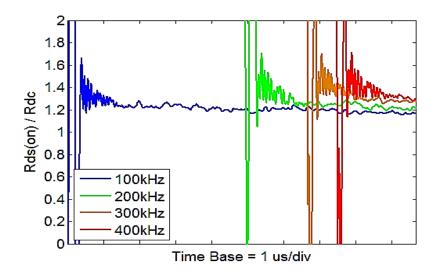

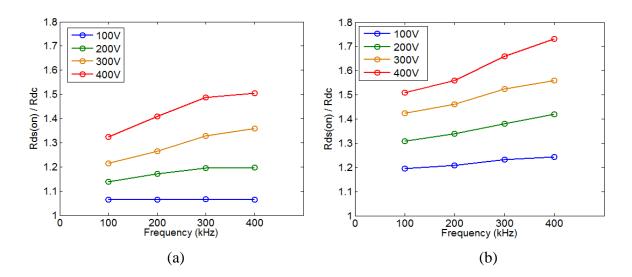

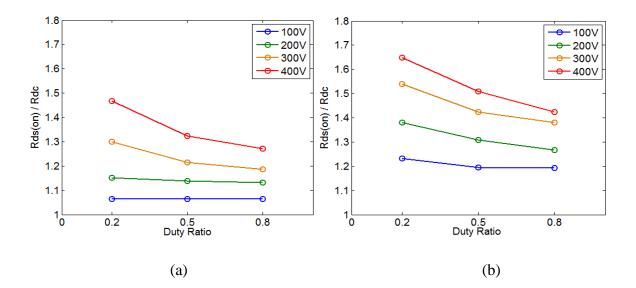

#### 2.3.2. PCB Design considerations