## Entwicklung und Charakterisierung vertikaler Double-Gate-MOS-Feldeffekttransistoren

Von der Fakultät für Mathematik, Informatik und Naturwissenschaften der Rheinisch-Westfälischen Technischen Hochschule Aachen zur Erlangung des akademischen Grades eines Doktors der Naturwissenschaften genehmigte Dissertation

vorgelegt von

Diplom-Physiker Stefan Trellenkamp

aus Viersen

Berichter: Universitätsprofessor Dr. Hans Lüth apl. Professor Dr. Siegfried Mantl

Tag der mündlichen Prüfung: 28. November 2003

Diese Dissertation ist auf den Internetseiten der Hochschulbibliothek online verfügbar.

## Berichte des Forschungszentrums Jülich; 4139

ISSN 0944-2952

Institut für Schichten und Grenzflächen

Institut 1: Halbleiterschichten und -bauelemente Jül-4139

(Diss., Aachen, RWTH, 2003)

Zu beziehen durch: Forschungszentrum Jülich Gmb<br/>H  $\cdot$  Zentralbibliothek D-52425 Jülich  $\cdot$  Bundesrepublik Deutschland

${\bf 2\!\!\! 2}$ 02461/61-5220 · Telefax: 02461/61-6103 · e-mail: zb-publikation@fz-juelich.de

## Entwicklung und Charakterisierung vertikaler Double-Gate-MOS-Feldeffekttransistoren

Kurzfassung. Planare MOS-Feldeffekttransistoren sind derzeit übliche Bauelemente in den meisten Produkten der Computerindustrie. Können diese Bauelemente nicht weiter verkleinert werden, sind neue Konzepte für alternative Transistorentwürfe vonnöten. In der vorliegenden Arbeit wird die Entwicklung vertikaler Double-Gate-Feldeffekttransistoren vorgestellt, ein Transistortyp, bei dem der p-n-p- (bzw. n-p-n-)Übergang vertikal angeordnet ist und somit der Source-Drain-Strom senkrecht zur Waferoberfläche fließt. Double-Gate-Feldeffekttransistoren zeichnen sich dadurch aus, daß ein sehr dünnes Kanalgebiet auf beiden Seiten von Gateelektroden flankiert wird, die parallel geschaltet sind. Die Symmetrie und das verminderte Bulkvolumen dieses Bauelementes versprechen ein verbessertes Skalierpotential sowie eine bessere Gatekontrolle des Kanalgebietes und damit die Unterdrückung von Kurzkanaleffekten.

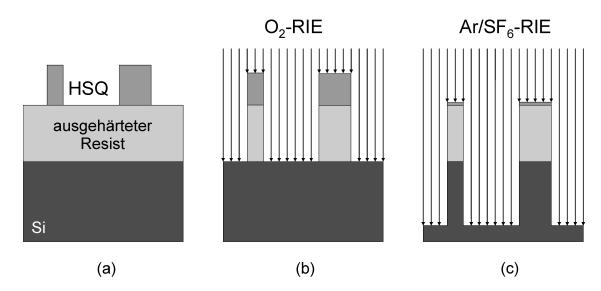

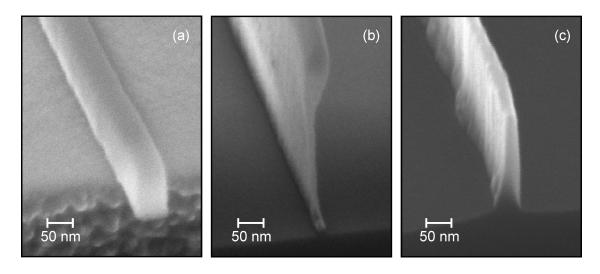

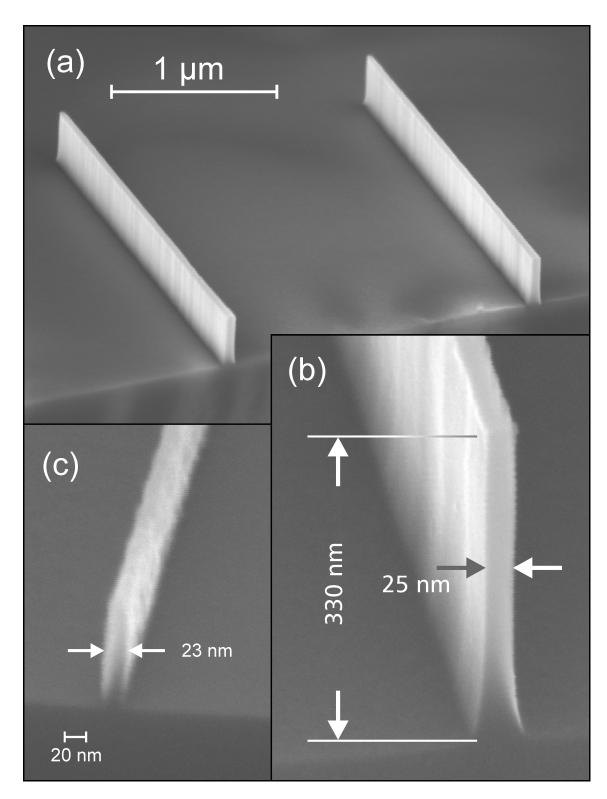

Die Nanostrukturierung des aktiven Bereichs eines vertikalen Double-Gate-Transistors ist höchst anspruchsvoll, da ca. 300 nm hohe und bis zu 30 nm schmale Siliziumstege reproduzierbar hergestellt werden müssen. Der Einsatz von Hydrogensilsesquioxan (HSQ) als hochauflösender anorganischer Elektronenstrahlresist bildet die Grundlage dieser Nanostrukturierung. In HSQ definierte Strukturen werden mittels ICP-RIE (reaktives Ionenätzen mit induktiv gekoppeltem Plasma) sehr anisotrop und mit hoher Selektivität in Silizium übertragen. 25 nm breite und 330 nm hohe Siliziumstege können so hergestellt werden.

Realisiert werden verschiedene Transistorausführungen, deren Kanallängen vor der Nanostrukturierung durch epitaktisches Wachstum dotierter Siliziumschichten oder nach der Nanostrukturierung mittels Ionenimplantation eingestellt sind.

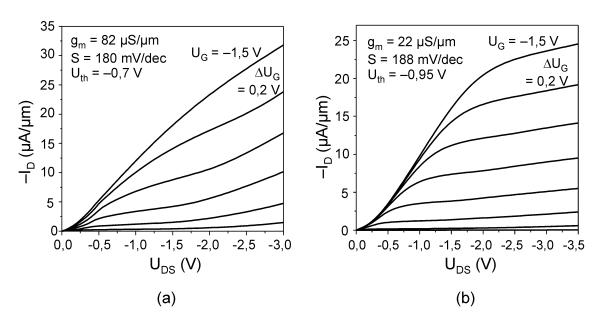

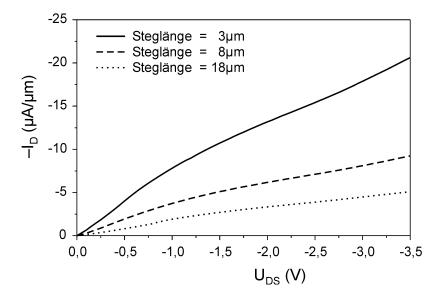

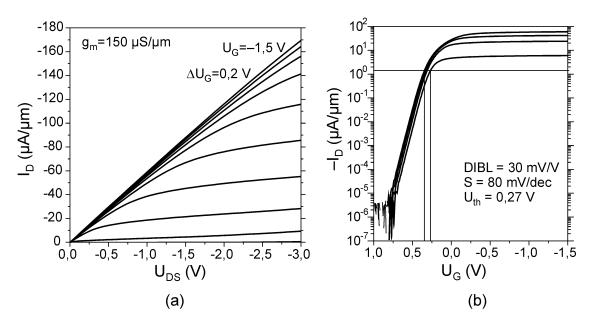

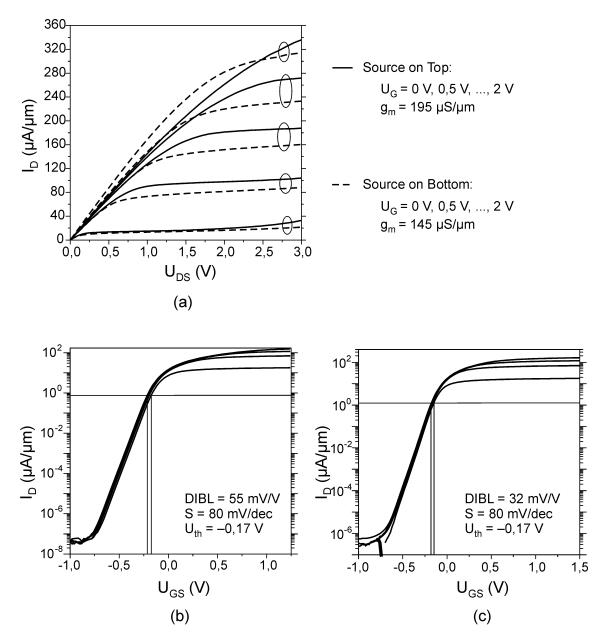

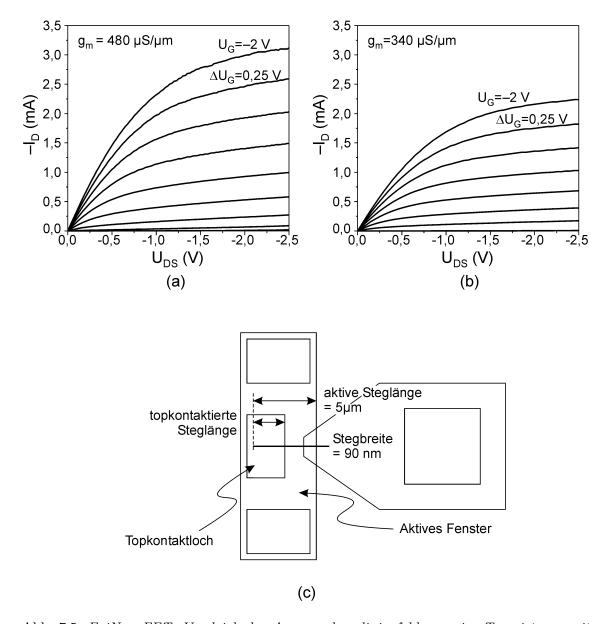

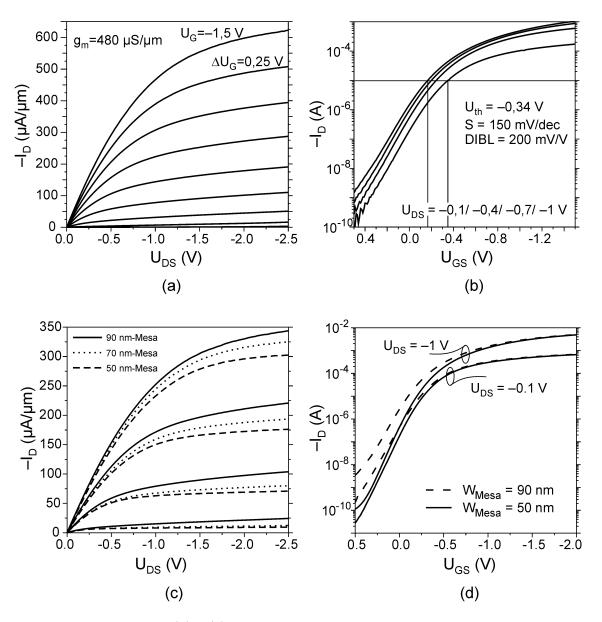

Die realisierten Transistoren weisen Source-Drain-Ströme bis zu  $380\,\mu\text{A}/\mu\text{m}$  und Steilheiten bis zu  $480\,\mu\text{S}/\mu\text{m}$  auf. Es wird gezeigt, daß sich bei Abnahme der Siliziumstegbreite das Kurzkanalverhalten verbessert.

#### Development and characterization of vertical Double-Gate-MOS-field-effect transistors

Abstract. Planar MOS-field-effect transistors are common devices today used by the computer industry. When their miniaturization reaches its limit, alternate transistor concepts become necessary. In this thesis the development of vertical Double-Gate-MOS-field-effect transistors is presented. These types of transistors have a vertically aligned p-n-p junction (or n-p-n junction, respectively). Consequently, the source-drain current flows perpendicular with respect to the surface of the wafer. A Double-Gate-field-effect transistor is characterized by a very thin channel region framed by two parallel gates. Due to the symmetry of the structure and less bulk volume better gate control and hence better short channel behavior is expected, as well as an improved scaling potential.

Nanostructuring of the transistor's active region is very challenging. Approximately 300 nm high and down to 30 nm wide silicon ridges are requisite. They can be realized using hydrogen silsesquioxane (HSQ) as inorganic high resolution resist for electron beam lithography. Structures defined in HSQ are then transferred with high anisotropy and selectivity into silicon using ICP-RIE (reactive ion etching with inductive coupled plasma). 25 nm wide and 330 nm high silicon ridges are achieved.

Different transistor layouts are realized. The channel length is defined by epitaxial growth of doped silicon layers before or by ion implantation after nanostructuring, respectively.

The transistors show source-drain currents up to  $380 \,\mu\text{A}/\mu\text{m}$  and transconductances up to  $480 \,\mu\text{S}/\mu\text{m}$ . Improved short channel behavior for decreasing width of the silicon ridges is demonstrated.

# Inhaltsverzeichnis

| 1 | Einl | Einleitung                                |    |  |

|---|------|-------------------------------------------|----|--|

| 2 | Das  | X-MOS-Projekt                             | 3  |  |

|   | 2.1  | Der Schottky-Barrieren-MOSFET             | 4  |  |

|   | 2.2  | Der NovaFET                               | 5  |  |

| 3 | Der  | MOSFET                                    | 9  |  |

|   | 3.1  | Die MOS-Struktur                          | 9  |  |

|   | 3.2  | Aufbau und Wirkungsweise                  | 12 |  |

|   | 3.3  | Strom-Spannungs-Charakteristik            | 13 |  |

|   | 3.4  | MOSFET-Skalierung                         | 16 |  |

|   | 3.5  | Kurzkanaleffekte                          | 18 |  |

|   |      | 3.5.1 $U_{th}$ -Roll-Off                  | 19 |  |

|   |      | 3.5.2 Drain-Induced Barrier Lowering      | 19 |  |

|   |      | 3.5.3 Punch-Through                       | 20 |  |

|   |      | 3.5.4 Kanallängenmodulation               | 21 |  |

|   |      | 3.5.5 Unterschwellströme                  | 21 |  |

|   | 3.6  | Neue MOSFET-Konzepte                      | 23 |  |

|   |      | 3.6.1 SOI-MOSFETs                         | 23 |  |

|   |      | 3.6.2 Double-Gate-MOSFETs                 | 24 |  |

| 4 | Verv | wendete Technologie                       | 27 |  |

|   | 4.1  | Technologien zur Strukturerzeugung        | 27 |  |

|   |      | 4.1.1 Elektronenstrahl-Lithographie       | 27 |  |

|   |      | 4.1.2 Optische Lithographie               | 29 |  |

|   |      | 4.1.3 Strukturübertragung durch RIE-Ätzen | 30 |  |

|   | 4.2  | Ionenimplantation                         | 33 |  |

|   | 4.3  | SIMS                                      | 34 |  |

|   | 4.4  | Chemisch-Mechanisches Polieren (CMP)      | 35 |  |

| 5 | Der  | NovaFET-Prozeß                            | 39 |  |

|   | 5.1  | NovaFET – ursprüngliches Layout           | 39 |  |

|   |      |                                           | 40 |  |

|   |      |                                           | 42 |  |

|   | 5.2  |                                           | 44 |  |

| R | Δhl                          | iirzungon                                    | 01   |  |  |  |  |  |

|---|------------------------------|----------------------------------------------|------|--|--|--|--|--|

|   |                              | Prozeßprotokoll EpiNovaFET                   |      |  |  |  |  |  |

|   | A.2                          | Prozeßprotokoll I-NovaFET                    |      |  |  |  |  |  |

|   | A.1                          | (ursprüngliches Layout)                      | 81   |  |  |  |  |  |

| A |                              | zeßfolgen<br>Prozeßprotokoll NovaFET         | 01   |  |  |  |  |  |

| ٨ | Dno                          | roßfolgen                                    | 81   |  |  |  |  |  |

| 8 | Zusammenfassung und Ausblick |                                              |      |  |  |  |  |  |

|   | 7.4                          | Einordnung                                   | . 73 |  |  |  |  |  |

|   | 7.3                          | EpiNovaFET                                   |      |  |  |  |  |  |

|   | 7.2                          | I-NovaFET                                    |      |  |  |  |  |  |

|   | 7.1                          | NovaFET (ursprüngliches Layout)              |      |  |  |  |  |  |

| 7 |                              | Bauelementcharakterisierung                  |      |  |  |  |  |  |

|   | 6.4                          | Strukturübertragung durch Direktätzen        | . 02 |  |  |  |  |  |

|   |                              | Strukturübertragung mit Zweilagenlack        |      |  |  |  |  |  |

|   | 6.2<br>6.3                   | Strukturdefinition mit HSQ                   |      |  |  |  |  |  |

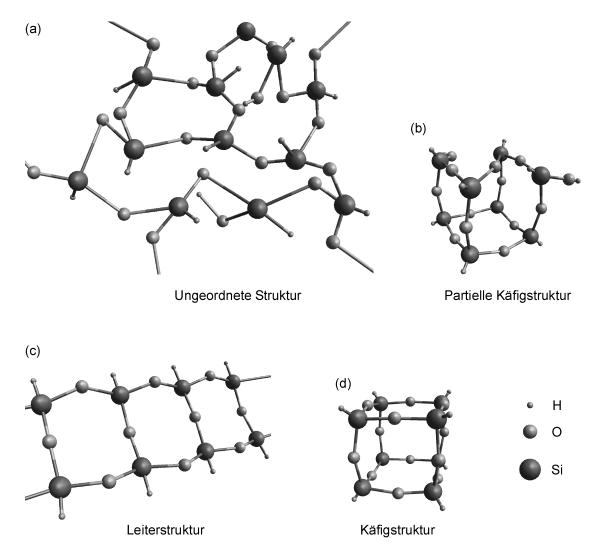

|   | 6.1                          | Eigenschaften des anorganischen Moleküls HSQ |      |  |  |  |  |  |

| 6 |                              |                                              |      |  |  |  |  |  |

|   |                              |                                              | . 54 |  |  |  |  |  |

|   |                              | 5.3.2 Schlüsselprozesse                      |      |  |  |  |  |  |

|   | 0.0                          | 5.3.1 Prozeßfolge                            |      |  |  |  |  |  |

|   | 5.3                          | EpiNovaFET                                   |      |  |  |  |  |  |

|   |                              | 5.2.2 Schlüsselprozesse                      |      |  |  |  |  |  |

|   |                              | 5.2.1 Prozesfolge                            | . 45 |  |  |  |  |  |

# Kapitel 1

# **Einleitung**

Viele Jahre schon wird das Ende der erstaunlichen Entwicklung beschworen, die 1965 von G. Moore aus einer kurzen Vergangenheit in die Zukunft projeziert [1] und zur sich selbst erfüllenden Prophezeiung wurde: "Moore's law", das für die Miniaturisierung in der Halbleiter-Technologie eine Verdopplung der Transistor-Performance und eine Vervierfachung der Transistoranzahl auf einem Chip alle drei Jahre konstatiert, gilt auch nach über 40 Jahren noch. Lange Zeit galten technologische Grenzen als limitierend, insbesondere die Auflösung der Lithographie, denn für die Skalierung galten einfache Regeln. Während die technologischen Hürden immer weiter nach hinten verschoben werden konnten, treten nun vermehrt ökonomische und physikalische Herausforderungen in den Vordergrund: Die Ökonomie entscheidet letztendlich, ob eine gefundene Lösung umgesetzt werden kann, und die Physik verhindert eine weitere Skalierung nach altem Muster. Quantenmechanische Effekte werden in einigen Jahrzehnten erst erreicht: Die Wellenlänge des Elektrons in Silizium ist 5 nm, Energiequantisierung von einigen meV tritt bei 10 nm-Strukturen auf; die ultimative Grenze ist wohl der Atomabstand im Gitter von 0,4 nm [2].

Derzeit ist das wichtigste Bauelement der Metall-Oxid-Halbleiter-Feldeffekttransistor (MOSFET); beim erfolgreichen CMOS¹-Design sind die logischen Schaltungen aus p- und n-Kanal-MOSFETs integriert aufgebaut. In Dimensionen, bei denen quantenmechanische Effekte dominieren, wird CMOS wohl schon keine Rolle mehr spielen – neue Arten wie Quantencomputer könnten bis dahin realisiert sein. Für die nächsten Jahrzehnte jedoch müssen Lösungen innerhalb von CMOS gefunden werden. Diese Entwicklung ist derzeit am Scheideweg: Die konventionelle Skalierung konnte sehr lange Zeit mit nur geringen Veränderungen wie z. B. Dotierprofile im Kanalgebiet durchgehalten werden, weiteres bloßes Verkleinern schadet aber der Performance mehr als es der Platzersparnis nutzt – man spricht allgemein von "Kurzkanalverhalten", dem es zu begegnen gilt. Neuartige, nicht klassische CMOS-Bauelemente werden derzeit untersucht, um für kommende Chipgenerationen bereit zu stehen. Als non-classical CMOS bezeichnet die ITRS-Roadmap² Transistor-Layouts wie Ultra-

$<sup>^1</sup>$  Complementary Metal-Oxide-Silicon

<sup>&</sup>lt;sup>2</sup>National Technology Roadmap for Semiconductors, von der Semiconductor Industry Association (SIA) seit 1992 regelmäßig erstellte Analyse der Halbleitertechnologie mit Ausblick auf die Erfordernisse für Chipgenerationen der nächsten 15 Jahre.

Thin Body SOI, Vertikaler Transistor, FinFET und Double-Gate-Transistor [3] (siehe auch 3.6). Welchen Weg CMOS dabei gehen wird, ist noch offen.

Einer dieser möglichen Wege ist der vertikale Double-Gate-MOSFET. Durch seinen symmetrischen Aufbau, senkrechtem Stromfluß und lithographieunabhängiger Kanallänge verspricht er gute Transistoreigenschaften und hohe Packungsdichte. Dieser Transistor war Bestandteil des Projektes "Extended Silicon MOSFET" am ISG des Forschungszentrums Jülich, seine Entwicklung und Charakterisierung Ziel dieser Arbeit.

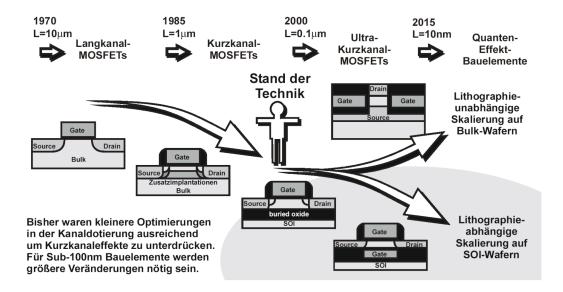

Abb. 1.1: Evolution und mögliche Weiterentwicklung des MOSFETs (aus [4]).

# Kapitel 2

# Das Projekt "Extended Silicon MOSFET"

Ausgehend von den Entwicklungen in der Technologie der Silizium-Bauelemente, setzt das Projekt "Extended Silicon MOSFET" bei den nicht-klassischen Transistormodellen ein. An einem Punkt, an dem ein Ende der bisherigen Skalierung absehbar und die Richtung für neue Konzepte noch nicht entschieden ist, gilt es verschiedene Möglichkeiten zu untersuchen:

"Übergeordnetes Ziel des Vorhabens "Extended MOSFET" ist die Erforschung, Realisierung und Charakterisierung von Feldeffekttransistoren mit Kanallängen zwischen 50 und 100 nm. Dabei sollen sowohl die Physik als auch die Technologie zur Herstellung dieser Bauelemente weiter vorangebracht werden. Solche Ultrakurzkanaltransistoren versprechen höhere Geschwindigkeit, höhere Packungsdichte und kleinere Verlustleistungen."

(aus dem Projektantrag)

Das Projekt "Extended Silicon MOSFET" bestand am Institut für Schichten und Grenzflächen (ISG 1) des Forschungszentrums Jülich von Juli 1999 bis Dezember 2002 und wurde vom HGF¹ gefördert.² Das Know-how und die Technik sind nicht zuletzt durch die Koordination des vorausgegangenen BMBF-Projektverbundes "NanoMOS" (1995–1999) durch das ISI (jetzt ISG 1) erworben worden. Im Rahmen dieses Projektes wurden vertikale MOSFETs auf der Basis selektiver Epitaxie entwickelt und realisiert [5]. Das Kanalgebiet wurde dabei mit optischer Lithographie im Mikrometerbereich definiert, die Kanallänge über die Dicke einer Epitaxieschicht eingestellt.

$<sup>^1{,}</sup>$  Hermann von Helmholtz-Gemeinschaft Deutscher Forschungszentren", Dachorganisation der fünfzehn deutschen Helmholtz-Zentren

<sup>&</sup>lt;sup>2</sup>Förderkennzeichen 01SF9933/6

Das HGF-Strategiefondprojekt eröffnete nun die Möglichkeiten, Schlüsselprozesse der modernen Siliziumtechnologie zu integrieren, wie z. B. verbesserte optische Lithographie, Chemisch-Mechanisches Polieren, Niederenergie-Ionenimplantation, RTP<sup>3</sup> und ICP-RIE.<sup>4</sup> Durch diese Investitionen und die damit verbundene Erweiterung des Reinraums konnten die für dieses Projekt gesteckten anspruchsvollen Ziele weitestgehend erreicht werden.

Das Projekt war in zwei Arbeitsbereiche unterteilt: die Realisierung von vertikalen Double-Gate-MOSFETs ("NovaFET"), in deren Rahmen die vorliegende Arbeit entstand, und die Erforschung eines selbst-assemblierten Verfahrens zur Herstellung von Nanostrukturen, die als Bausteine für laterale Schottky-Barrieren-MOSFETs (SB-MOSFETs) auf SOI-Substraten dienen (Abb. 2.1).

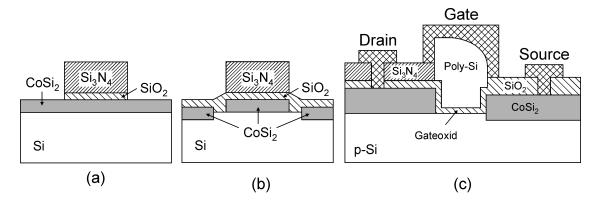

## 2.1 Der Schottky-Barrieren-MOSFET

Das selbst-assimblierte Verfahren für die Herstellung der SB-MOSFETs beruht auf der lokalen Oxidation von Silizidschichten ("LOCOSI", Local Oxidation of Silicides) [7]. Bei diesem Prozeß wird über ein elastisches Spannungsfeld, welches an den Kanten einer  $\mathrm{Si_3N_4/SiO_2}$ -Maske entsteht, die Diffusion von Kobaltatomen während der lokalen Oxidation des Silizids gesteuert, so daß sich entlang dieser Kante eine wohldefinierte Aufspaltung formt [6]. Übertragen auf  $\mathrm{CoSi_2}$ -Schichten auf ausgedünnten SOI-Substraten können mit dieser Methode homogene Auftrennungen mit Breiten bis auf 40 nm herunter erzielt werden (Abb. 2.2).

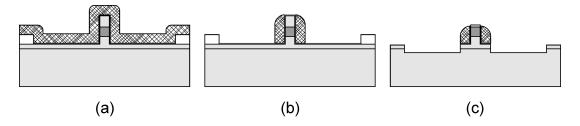

Abb. 2.1: Selbstjustierende Nanostrukturierung für laterale Schottky-Tunnel-MOSFETs. (a) Schichtsystem vor der Nanostrukturierung. (b) Bei der "rapid thermal oxidation" (RTO) reißt die CoSi<sub>2</sub>-Schicht an der Kante der Nitridmaske auf. Diese Spaltbreite, die deutlich unter 100 nm realisiert werden kann, bestimmt für den späteren Transistor die Kanallänge. (Die vertikale Verlagerung der CoSi<sub>2</sub>-Schicht ist überzeichnet.) (c) Layout des Transistors. Der Übergang CoSi<sub>2</sub> – Si ist hier ein Schottkykontakt. Vom Source zum Substrat ist dieser in Sperrichtung, nach Anlegen der Gatespannung kann die Barriere jedoch durchtunnelt werden. Der Gatekontakt wird über einen Polysiliziumspacer hergestellt.

<sup>&</sup>lt;sup>3</sup>, Rapid thermal processing"

<sup>&</sup>lt;sup>4</sup>, Inductive Coupled Plasma-Reactive Ion Etching", siehe 4.1.3.

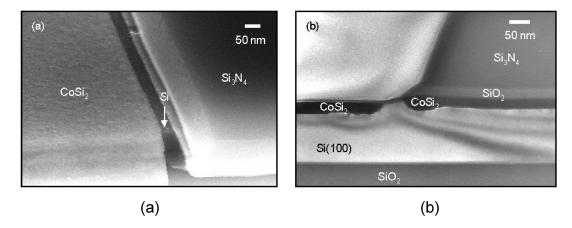

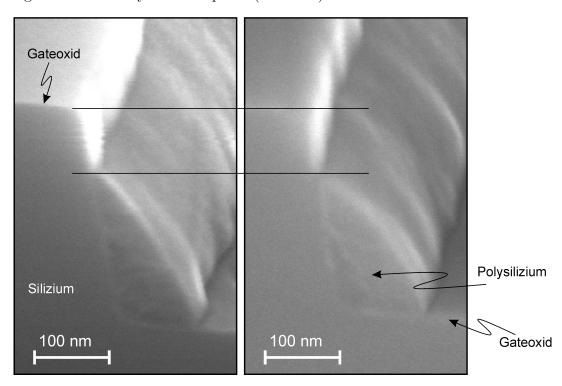

Abb. 2.2: (a) REM- und (b) XTEM-Aufnahmen der Strukturierung von CoSi<sub>2</sub>-Schichten auf SOI-Substrat. [8]

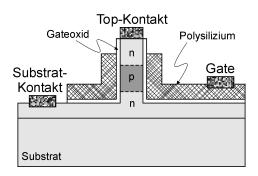

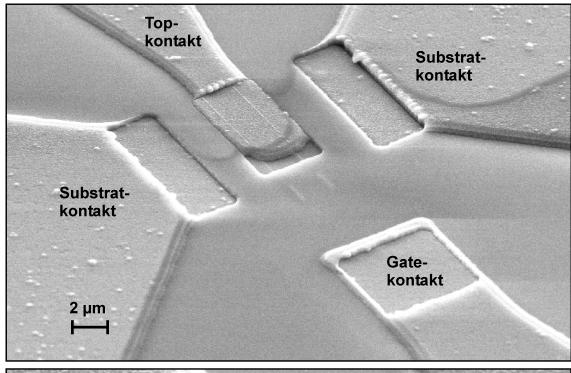

### 2.2 Der NovaFET

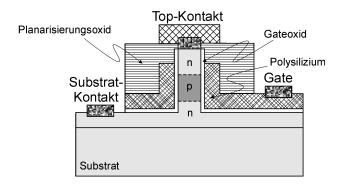

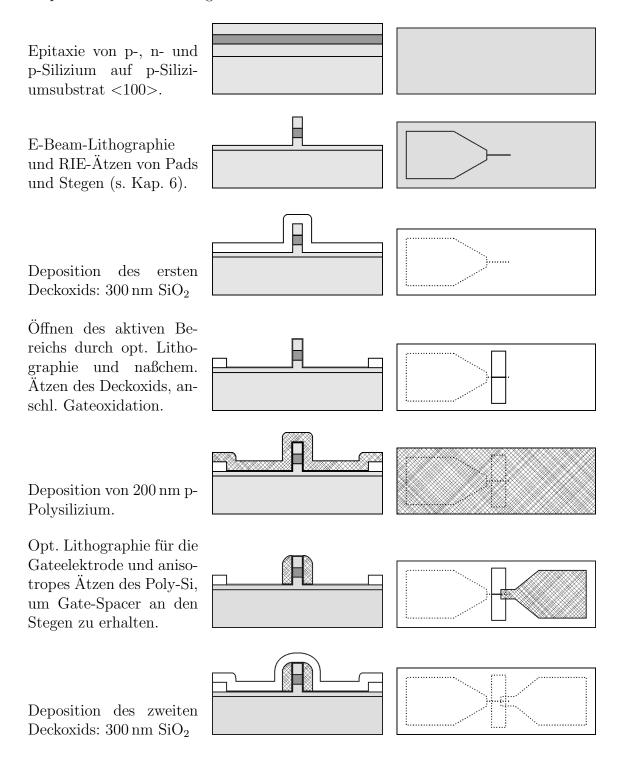

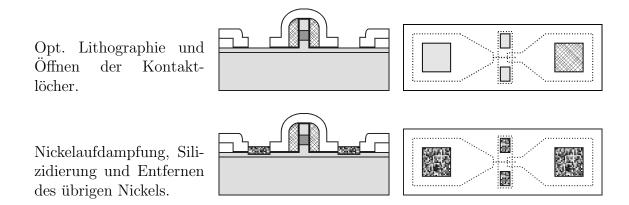

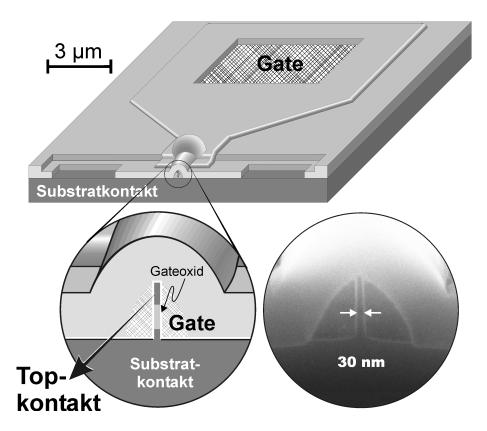

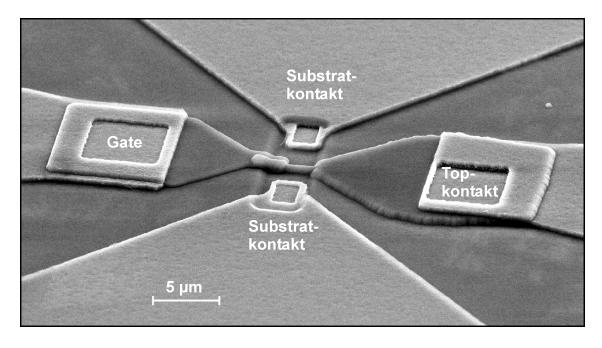

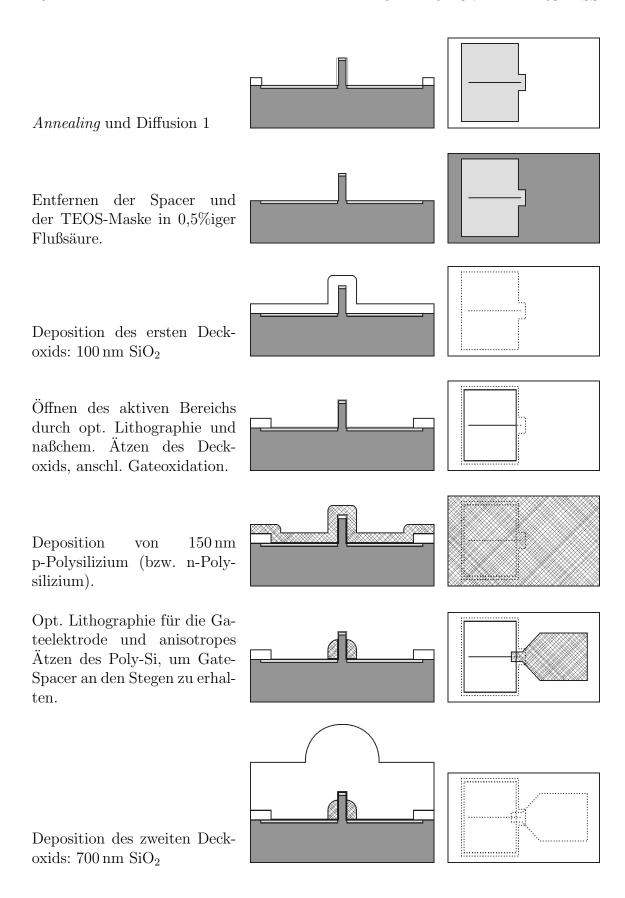

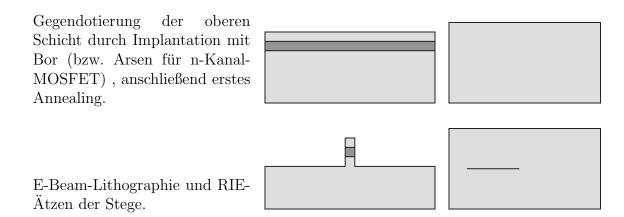

Der in diesem Projekt realisierte NovaFET ist ein vertikaler Double-Gate-MOSFET, wie er in 3.6.2 beschrieben wird. Da die Kanallänge über die Dicke der mittleren Schicht der Dotierfolge definiert wird, erfordert diese Variante des DG-MOSFETs noch eine laterale Strukturdefinition im kritischen sub-100 nm-Bereich. In Abbildung 2.3 ist das Prinzip des NovaFETs dargestellt. (Die genaue Prozeßfolge ist in Kapitel 5 sowie im Anhang A dargestellt.) Die Schlüsselprozesse sind:

#### 1. Nanolithographie

Es werden mehrere Mikrometer lange Stege benötigt, die ca. 300 nm hoch und 20–100 nm breit sind, um das Verhalten der Transistoren vergleichen zu können. Strukturen dieser Größenordnung herzustellen, wird auch in Zukunft aufwendig und teuer bleiben, jedoch werden für zukünftige Chipgenerationen neue parallele Lithographiemethoden entwickelt werden. So ist es gerechtfertigt, für Demonstratoren heute die aufwendige und langsame Elektronenstrahllithographie zu verwenden, zumal modernste Industrieeinrichtungen für die Forschung meist nicht verfügbar sind. Die Nanostrukturierung, bestehend aus Strukturdefinition und Strukturübertragung, ist in Kapitel 6 dargestellt.

#### 2. Herstellung der Dotierfolge

Ausgehend von einer in einer LPCVD epitaktisch gewachsenen Dotierfolge für die erste Version des NovaFETs, wurden die Transistoreigenschaften bei den weiteren Versionen durch Implantation verbessert. Die Motivationen und Maßnahmen dazu werden in 5 erläutert.

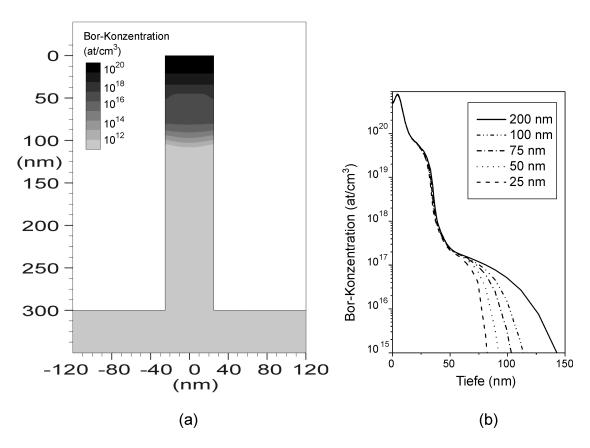

#### 3. Gateoxidation

Während zunächst die Gateoxidation durch RTP angewendet wurde, ist später eine Niedrigtemperatur-Feuchtoxidation etabliert worden. Diese Methode, die in 5.2.2 beschrieben ist, schont das thermische Budget.

#### 4. Topkontakt

Damit der Topkontakt direkt auf dem Steg angelegt werden kann, müssen verschiedene Voraussetzungen erfüllt sein:

- (a) Die Gatespacer müssen selektiv zurückgeätzt werden, damit sie nicht ebenfalls kontaktiert werden. Dies ist mit der ICP-RIE möglich geworden. Der Prozeß ist in 5.2.2 beschrieben; die Ätzprozesse sind die gleichen, wie sie für die Nanolithographie in 6 erläutert sind.

- (b) Eine Deckoxidschicht muß planarisiert werden. Dafür wurde eine konforme, dicke TEOS-Schicht durch Chemisch-Mechanisches Polieren planarisiert (siehe 5.2.2).

Abb. 2.3: Schema des vertikalen DG-MOSFETs.

Insgesamt sind durch die Auswertungen der Ergebnisse und das Potential der im Rahmen des Projektes neu installierten Technik drei verschiedene Variationen des NovaFETs entstanden:

#### 1. NovaFET (ursprüngliches Layout)

Im ersten Entwurf wird die Dotierfolge durch LPCVD-Epitaxie erstellt. Der obere Kontakt wird durch den dünnen Steg herausgeführt und außerhalb des aktiven Bereichs über ein Pad abgenommen. Diese Geometrie und die Top-Dotierung im Bereich  $4-5\cdot10^{18}$  at cm<sup>-3</sup> bewirken hohe Zuleitungswiderstände, wodurch die Transistoreigenschaften stark verschlechtert werden. Die Herstellung dieses Transistors ist in 5.1 dokumentiert.

#### 2. I-NovaFET

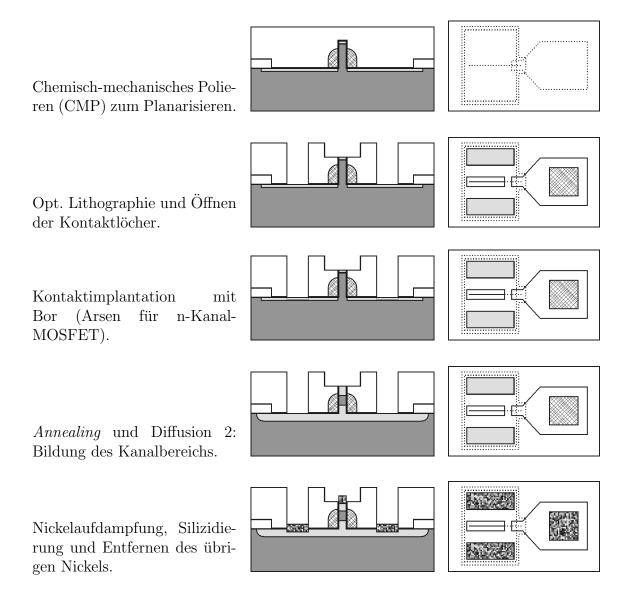

Flache Implantationen können Dotierungen im Bereich  $10^{20}$  at cm $^{-3}$  erzeugen. In der Implantationsvariante wird die Dotierfolge durch Implantation in die fertigen Nanostege und spätere Diffusion definiert. Der Einsatz von ICP-RIE und CMP ermöglicht die direkte Kontaktierung des Steges von oben. In 5.2 ist die Herstellung dieses Transistors beschrieben.

#### 3. EpiNovaFET

Der I-NovaFET hat flache Substratzuleitungen, die nun einen Engpaß bilden. Die Epitaxie in (niedriger) Kanaldotierung auf hochdotiertem Substrat und

7

Implantation nur der oberen Schicht (jetzt vor der Steg-Ätzung) verringern diese hohen Zuleitungswiderstände im Substrat. Diese ergänzenden Maßnahmen sind in 5.3 erläutert.

Kapitel 7 beinhaltet die Charakterisierung und den Vergleich der Transistoren, und im Anhang A sind detaillierte Protokolle zu den Prozessen dokumentiert.

# Kapitel 3

# Metall-Oxid-Halbleiter-Feldeffekttransistoren

Die auf Silizium basierende Transistortechnologie dominiert seit über 30 Jahren die Mikroelektronikindustrie. Metall-Oxid-Halbleiter-Feldeffekttransistoren (MOS-FETs) sind hierbei die zentralen Bauelemente. Kern eines MOSFETs ist eine Schichtfolge aus Metall (M), Oxid (O) und Halbleiter (S, semiconductor). Am Beispiel eines p-dotierten Halbleiters soll zunächst diese sogenannte MOS-Struktur diskutiert werden.

## 3.1 Die MOS-Struktur

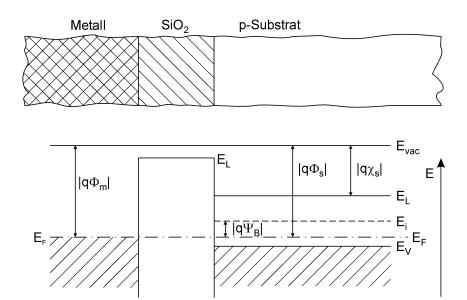

Im idealisierten Fall ist das Bänderschema einer MOS-Struktur ohne angelegte Spannung flach (Abb. 3.1, nach [9]).

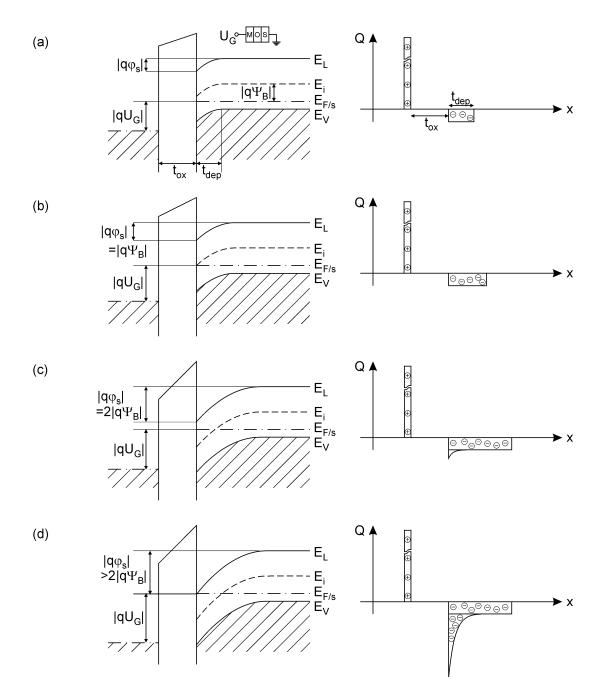

Wird am Metall eine Spannung  $U_G$  gegen das geerdete Substrat angelegt, so entsteht ein Potentialverlauf. Wählt man das Potential weit im Halbleiterinneren zum Nullpunkt, so können für das Oberflächenpotential  $\varphi_s$  am Isolator-Halbleiter-Übergang verschiedene Fälle auftreten [10]:

- 1.  $U_G < 0$ : Es ist dann das Potential  $\varphi_s < 0$ , so daß sich die Bänder des Halbleiters nach oben verbiegen. Es reichern sich in diesem Gebiet Löcher an, die hier Majoritätsladungsträger sind. Dieser Fall wird "Anreicherung" genannt. Es entsteht eine Raumladungszone positiver Ladung.

- 2.  $U_G = 0$ : Dieser Fall heißt bei einer idealisierten MOS-Struktur "Flachbandfall", da  $\varphi_s = 0$  ist und somit keine Bandverbiegung und keine Umverteilung von Ladung stattfindet. (Abb. 3.1)

- 3.  $U_G > 0$ : Es ist  $\varphi_s > 0$ ; Die Bänder werden nach unten verbogen. Je nach Größe des Potentials in Relation zum Volumenpotential  $\Psi_B$  treten verschiedene Effekte auf. (Bei einem p-dotierten Halbleiter ist  $\Psi_B < 0$ .)

- (a)  $0 < \varphi_s < -\Psi_B$ : Bewegliche Löcher werden verdrängt, so daß das Potential über die durch die negativ geladenen Akzeptoren des p-Halbleiters do-

Abb. 3.1: Aufbau und Bänderschema einer idealisierten MOS-Struktur.  $E_F$  bezeichnet die Fermienergie,  $E_L$  und  $E_V$  Leitungs- und Valenzbandkanten,  $E_i$  intrinsisches Ferminiveau im Halbleiter.  $|q\Phi_m|$  und  $|q\Phi_s|$  sind die Austrittsarbeiten von Metall und Halbleiter,  $|q\chi_s|$  ist die Elektronenaffinität des Halbleiters,  $\Psi_B = (E_F - E_i)/q$  dessen Volumenpotential.

minierte Raumladungszone, die Verarmungszone, abfällt. Die Dicke dieser Verarmungszone vergrößert sich mit zunehmender Spannung. (Abb.  $3.2\,(a)$ )

- (b)  $\varphi_s = -\Psi_B$ : Das Ferminiveau fällt an der Oberfläche mit dem intrinsischen Ferminiveau zusammen. Die Konzentrationen der positiven und negativen freien Ladungsträger sind gleich. Dieser Punkt wird "Einsatzpunkt der schwachen Inversion" genannt. (Abb. 3.2 (b))

- (c)  $-\Psi_B < \varphi_s < -2\Psi_B$ : Der Abstand zwischen Fermienergie und Leitungsband ist klein genug, daß neue Elektron-Loch-Paare erzeugt und Elektronen im Leitungsband bereitgestellt werden können. Die Löcher werden ins Volumen gezogen und haben keinen Einfluß mehr. Die Konzentration der Minoritätsladungsträger (hier Elektronen) ist größer als die der Majoritätsladungsträger (hier Löcher). Dieser Zustand heißt "Inversion", die sich dabei ausbildende Minoritätsladungsträgerschicht "Inversionsschicht".

- (d)  $\varphi_s > -2\Psi_B$ : Die Verarmungszone hat ihre maximale Dicke erreicht. Höhere Spannungen fallen nur noch über die Inversionsschicht ab, da dort eine sehr hohe Elektronendichte erzeugt werden kann. Die Raumladungszone ist somit gegen höhere Felder abgeschirmt und die Bandverbiegung ist nur noch schwach von der angelegten Spannung abhängig. Dieser Zustand heißt "starke Inversion" (Abb. 3.2 (c), (d)).

Für n-dotierte Halbleiter gelten ähnliche Überlegungen; die Inversionsschicht wird dann nicht aus Elektronen, sondern aus beweglichen Löchern gebildet.

Abb. 3.2: Bandverbiegung und Ladungsverteilung an einer MOS-Struktur bei angelegter positiver Spannung  $U_G$ . (a) Verarmung, (b) Einsatzpunkt der schwachen Inversion, (c) Beginn der starken Inversion, (d) starke Inversion.

Mit einer MOS-Struktur läßt sich also über eine angelegte Spannung die Ladungsträgerdichte an einem Isolator-Halbleiterübergang kontrollieren. Mit Hilfe dieses "Feldeffektes" kann der Widerstand in einem Halbleiter in einem Kanal nahe der Oberfläche gesteuert werden. Dieses Prinzip wird beim Feldeffekttransistor genutzt.

Für die Betrachtung der MOS-Struktur wurden einige Vereinfachungen gemacht: Beim der "idealisierten MOS-Struktur" wird davon ausgegangen [11],

- ... daß Metall und Halbleiter die gleichen Austrittsarbeiten haben. Sind diese verschieden, so verbiegen sich die Halbleiterbänder, bis die Ferminiveaus von Metall und Halbleiter angepaßt sind. Um den Flachbandfall zu erhalten, muß also eine Spannung  $U_G \neq 0$  angelegt werden. Diese Spannung heißt "Flachbandspannung"  $U_{FB}$  und geht als Offset in die bisherigen Überlegungen ein.

- ... daß am Isolator-Halbleiter-Übergang keine Grenzflächenladungen existieren. Werden beim Anlegen einer Spannung unbesetzte Grenzflächenzustände unter das Ferminiveau abgesenkt, so werden sie umgeladen und binden Ladungen. Die Inversionsladungsträgerdichte kann also nicht mehr so effektiv gesteuert werden. Eine geringe Grenzflächenzustandsdichte ist also angebracht, um ein Bauelement mit einer steuerbaren MOS-Struktur herstellen zu können ([9] S. 197 f).

- ... daß der Isolator ideal ist, also kein Strom durch ihn fließen kann.

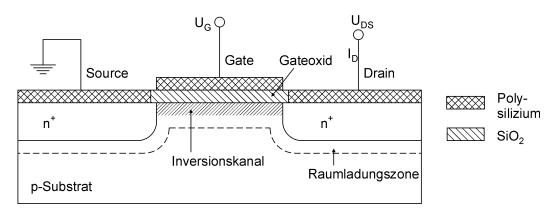

## 3.2 Aufbau und Wirkungsweise eines MOSFETs

Der Aufbau eines planaren n-Kanal-MOSFETs ist in Abbildung 3.3 gezeigt.<sup>1</sup> Die Oberfläche des p-dotierten Substrats ist mit einer dünnen SiO<sub>2</sub>-Schicht, dem Gateoxid, überzogen. Durch Öffnungen im SiO<sub>2</sub> werden hoch n-dotierte Wannen diffundiert oder implantiert, die Source und Drain bilden. Für die Anschlüsse werden Metallkontakte an Source und Drain angebracht. Eine Metall- oder eine kontaktierte Polysiliziumschicht auf dem Isolator bildet die Gateelektrode.

Abb. 3.3: Schematischer Aufbau eines planaren n-Kanal-MOSFETs.

Legt man die idealisierte MOS-Struktur zugrunde, so ist bei der Gatespannung  $U_G = 0$  kein n-leitender Kanal vorhanden und es kann, unabhängig von einer Source-Drain-Spannung  $U_{DS}$ , kein Drainstrom  $I_D$  fließen, weil einer der beiden p-n-Übergänge stets gesperrt ist. Da bei einer reellen MOS-Struktur jedoch bereits eine Bandverbiegung auftritt, unterscheidet man nun, ob bei  $U_G = 0$  ein Inversionskanal vorhanden ist oder nicht. Ist dies der Fall, so spricht man von einem "normally on"-,

<sup>&</sup>lt;sup>1</sup>Für einen p-Kanal-MOSFET gilt der analoge Aufbau mit einem n-dotierten Substrat.

andernfalls von einem "normally off"-Transistor ([9] S. 208 f). Im Folgenden wird der normally-off-Transistor betrachtet, der bei  $U_G = 0$  keinen Kanal ausbildet. Dieser Typ ist technologisch besonders relevant, da er im Ruhezustand nur Verlustleistung über Restsröme verbraucht.

Die Gatespannung, bei der die starke Inversion beginnt und somit ein Kanal beweglicher Ladungsträger entsteht, wird mit "Einsatzspannung" oder "Schwellenspannung"  $U_{th}$  des MOSFETs bezeichnet (engl.: threshold voltage). Ist  $U_G > U_{th}$ , existiert also ein Inversionskanal zwischen Source und Drain, so kann bei  $U_{DS} \neq 0$  Strom fließen.

## 3.3 Strom-Spannungs-Charakteristik

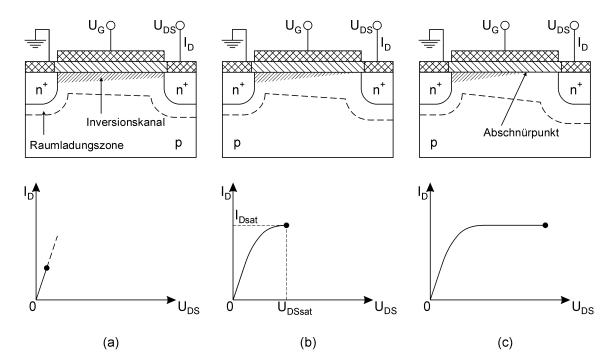

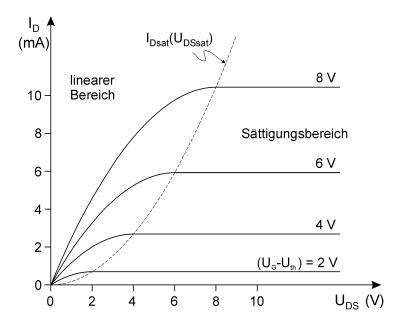

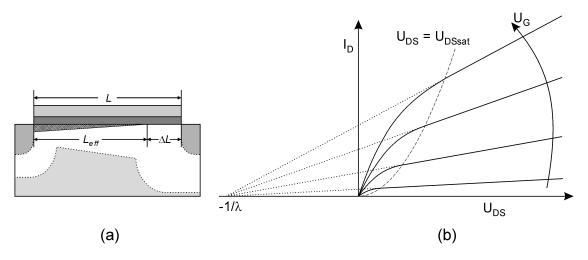

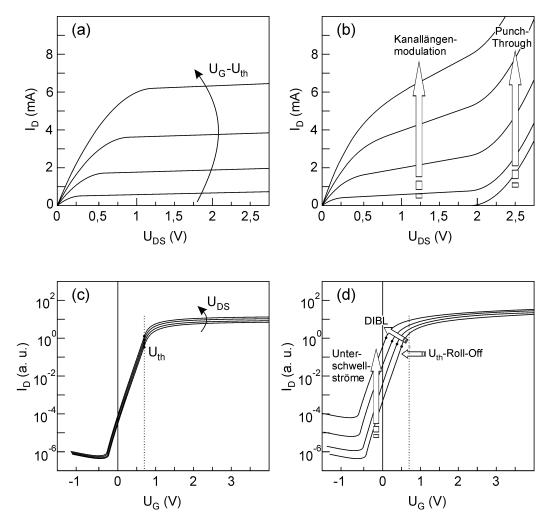

Die Ausgangskennlinie eines Transistors zeigt den Drainstrom als Funktion der Drainspannung. Bei angelegter Gatespannung  $U_G > U_{th}$  ergeben sich zwei Bereiche der  $I_D$ - $U_{DS}$ -Abhängigkeit ([9] S. 202 f) (vgl. Abb. 3.4):

1. Linearer Bereich. Für kleine Drainspannungen  $U_{DS}$  steigt die Stromstärke  $I_D$  nahezu linear mit der Spannung. Der MOSFET verhält sich wie ein Ohmscher Widerstand. Es gilt [11]:

$$I_D = 2k \left( U_G - U_{th} \right) U_{DS} , \quad \text{für} \quad U_{DS} \ll U_G - U_{th} ,$$

wobei k, der sogenannte "Entwurfsparameter", eine von den Material- und Geometrieeigenschaften des MOSFETs abhängige Konstante ist.

Der Inversionskanal wird vom Source zum Drain schmaler, da zwischen diesen beiden Elektroden eine Spannung – im idealen Fall linear – abfällt und sich das lokale Potential als Differenz der vom Gate erzeugten, konstanten und dieser ortsabhängigen Komponenten ergibt.

2. Sättigungsbereich. Wenn die Drainspannung  $U_{DSsat} = U_G - U_{th}$  anliegt, hat die Inversionsschicht am Drain die Dicke Null erreicht. Der Drainstrom beträgt  $I_{Dsat} = k \cdot U_{DSsat}^2$  und ändert sich auch für größere Spannungen  $U_{DS}$  nicht mehr. Gründe für dieses Sättigungsverhalten sind die Kanalabschnürung und -verkürzung. Diese haben zur Folge, daß ein Teil des Kanals nicht mehr im Zustand der Inversion, sondern nur noch in dem der Verarmung ist. Aufgrund des hohen Feldes erreichen Elektronen, die aus der Inversionsschicht in diesen Bereich injiziert werden, dennoch die Drainelektrode, so daß der Strom nicht absinkt. Da über den Inversionskanal bis zum Abschnürpunkt immer dieselbe Spannung abfällt, steigt der Strom jedoch auch nicht an.

Das Ausgangskennlinienfeld eines Transistors zeigt die beschriebene Strom-Spannung-Abhängigkeit mit der Gatespannung als Parameter. Abbildung 3.5 zeigt das Feld eines MOSFETs und veranschaulicht die quadratische Beziehung zwischen Sättigungsstrom und -spannung in Abhängigkeit von der Gatespannung.

<sup>&</sup>lt;sup>2</sup>Sättigung, engl. saturation (Abk. "sat")

Abb. 3.4: Verschiedene Bereiche der Kennlinie. Es ist  $U_G > U_{th}$ . (a) kleine Drainspannung. Die Abhängigkeit ist annähernd linear. (b) Die Drainspannung hat den Sättigungswert  $U_{Dsat}$ , es fließt der Sättigungsstrom  $I_{Dsat}$ . Der Inversionskanal wird auf der Drainseite abgeschnürt. (c) große Drainspannung. Der Drainstrom befindet sich im Sättigungsbereich, zwischen dem Abschnürpunkt und der Drainelektrode fließt der Drainstrom aufgrund von injizierten Elektronen in einer Sperrschicht ohne Inversionskanal.

Eine wichtige Größe zur Charakterisierung der Gleichstromeigenschaften eines Transistors ist die Steilheit g. Sie ist definiert als ([9] S. 206)

$$g = \frac{\partial I_D}{\partial U_G} \bigg|_{U_{DS} = const.} \sim \frac{W}{L \cdot t_{ox}}$$

mit Kanalweite W und Oxiddicke  $t_{ox}$ , und ist ein Maß für das Steuerverhalten des Transistors. Um die Werte von Transistoren unterschiedlicher Geometrie miteinander vergleichen zu können, wird die Steilheit auf die Kanalweite W normiert:

$$g_m = \frac{g}{W_G} \sim \frac{1}{L_G \cdot t_{ox}}$$

Hohe Steilheit bedeutet: Eine kleine Änderung der Gatespannung reicht aus, um eine große Änderung des Drainstroms zu bewirken. Da die Betriebsspannungen zukünftiger Schaltkreise immer kleiner werden, um die Leistungsaufnahme zu begrenzen, ist eine hohe Steilheit angestrebt. Diese kann durch Verkleinerung der Kanallänge L und der Oxiddicke  $t_{ox}$  erreicht werden.

Die Transferkennlinie eines Transistors beschreibt die Steuerwirkung. Der Drainstrom wird als Funktion der Gatespannung aufgetragen. Bei einem idealen MOSFET sind die Transferkennlinien unabhängig von der angelegten Source-Drain-Spannung.

Abb. 3.5: Ausgangskennlinienfeld eines MOSFETs in schematischer Darstellung. Der Drainstrom  $I_D$  ist gegen die Drainspannung  $U_{DS}$  aufgetragen; die Differenz zwischen Gatespannung und Schwellenspannung  $(U_G - U_{th})$  erzeugt bewegliche Ladungsträger und ist Parameter.

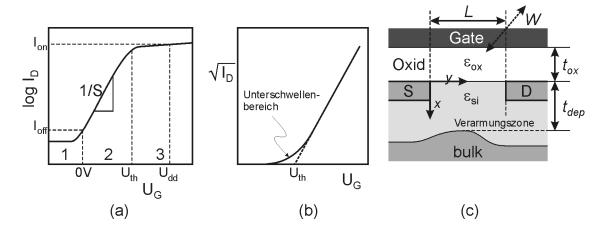

Wie in Abbildung 3.6 a ersichtlich, kann die Kennlinie in drei Bereiche unterteilt werden:

- 1. Ausgeschalteter Bereich. Der Transistor ist ausgeschaltet, wenn kein Kanal vorhanden ist. Dies ist bei Gatespannungen der Fall, bei denen das Silizium im Kanalgebiet in Verarmung ist. Die Leckströme, die zu  $I_{off}$  zusammengefaßt werden, sollten möglichst klein sein.

- 2. Unterschwellenspannungsbereich. Die MOS-Struktur ist in schwacher Inversion. Es fließt ein Drainstrom, der exponentiell mit der angelegten Gatespannung ansteigt. Für  $U_{DS} > 3kT/q$  ist  $I_D$  von  $U_{DS}$  unabhängig [12]. Die Steigung in diesem Bereich ist ein wichtiges Maß für die Schalteigenschaften des Transistors. Diese "Unterschwellenspannungssteigung" S ist die reziproke Steigung im logarithmischen Auftrag von  $I_D$  und hat die Einheit mV/dec.

- 3. Überschwellenspannungsbereich. Die MOS-Struktur ist in starker Inversion. Die Einsatzspannung der starken Inversion ist  $U_G = U_{th}$ . Wegen der quadratischen Abhängigkeit des Sättigungsdrainstroms von  $U_G U_{DS}$ , kann die Schwellenspannung grafisch bestimmt werden (Abb. 3.6 b).

Die wichtigsten technologischen Kenngrößen sind in Abbildung 3.6 (c) veranschaulicht: Die Gatelänge L ist der Abstand zwischen Source (S) und Drain (D), zwei dem Substrat gegendotierte Wannen, W die Gateweite (in der Abbildung die Ausdehnung in z-Richtung). Die Gateoxiddicke wird mit  $t_{ox}$  bezeichnet, die Dicke der Verarmungszone unter dem Gate mit  $t_{dep}$  (von depletion, engl. für Verarmung).  $\varepsilon_{ox}$  und  $\varepsilon_{si}$  sind die Dielektrizitätskonstanten für Oxid bzw. Silizium.

Abb. 3.6: (a) Schematische Darstellung der Transferkennlinie eines MOSFETs mit den drei Bereichen: Restströme, Unterschwellenspannungsbereich und Überschwellenspannungsbereich. Es sind die wichtigsten elektrischen Kenngrößen eingezeichnet.  $U_G = U_{DS} = U_{DD}$  ist der Arbeitspunkt im eingeschalten Zustand,  $U_G = 0$  und  $U_{DS} = U_{DD}$  der bei ausgeschaltetem Zustand. (b) Grafische Bestimmung der Schwellenspannung  $U_{th}$ . (c) Technologische Kenngrößen eines MOSFETs.

Motor der Weiterentwicklung von MOSFETs ist die Ökonomie. Kleinere Transistoren auf größeren Wafern bedeuten billigere Bauelemente mit besseren Eigenschaften. Derzeit an der 100 nm-Grenze (DRAM half pitch), nähert sich die Technologie zwar noch nicht fundamentalen physikalischen Grenzen [2], während die Skalierung bislang jedoch einfachen Regeln folgte (Skalierungsmethode nach Dennard et al. [13]), die mit der Zeit nur leicht angepaßt werden mußten, können in wenigen Jahren wohl nur neuartige Bauelementkonzepte die geometrischen und elektrischen Anforderungen erfüllen. Im Folgenden werden die Skalierungsregeln vorgestellt und die Grenzen diskutiert.

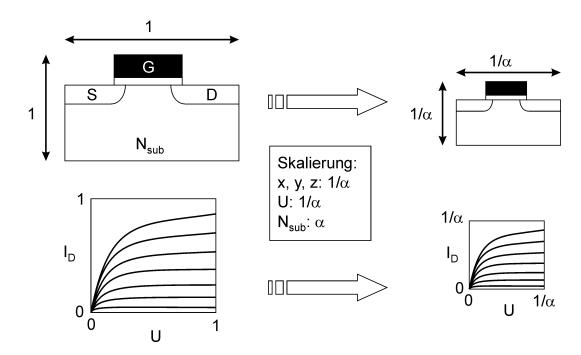

## 3.4 MOSFET-Skalierung

Um die guten Schalteigenschaften der Transistoren zu bewahren, schlugen Dennard et~al.~[13] 1974 eine einfache Skalierungsregel vor (s. Abb. 3.7): Wenn sämtliche geometrische Größen eines planaren MOSFETs mit dem Faktor  $\alpha$  verkleinert werden, ebenso die angelegten Spannungen, dabei gleichzeitig die Substratdotierung um den Faktor  $\alpha$  vergrößert wird, so ändert sich das elektrische Feld im Bauelement nicht. Die Drainströme werden dabei ebenfalls um den Faktor  $\alpha$  verkleinert, behalten aber ihre Charakteristik bei. Die Schaltzeiten verkleinern sich ebenfalls um den Faktor  $\alpha$  und ermöglichen so höhere Schaltfrequenzen.

Grenzen dieser Skalierung treten für Submikrometer-MOSFETs auf, zum einen, wenn nicht alle Parameter gleichmäßig skaliert werden (können), zum anderen, wenn zusätzliche Effekte auftreten, die bei größeren Dimensionen vernachlässigt werden konnten. Nicht im selben Maß skaliert wie die anderen Größen wurde in der Vergangenheit z. B. die Betriebsspannung  $U_{dd}$ . Ein Grund dafür ist die Kompatibilität der

Abb. 3.7: Skalierungsregeln nach Dennard et al.: Werden die Dimensionen eines MOS-FETs sowie die angelegte Spannung um den gleichen Faktor  $1/\alpha$  skaliert, dabei die Substratdotierung um den Faktor  $\alpha$  erhöht, so bleiben die Felder im Transistor gleich und die Charakteristik des Transistors ändert sich nicht.

verschiedenen Bauelementgenerationen, ein anderer, daß die Schwellenspannung  $U_{th}$  nicht skaliert werden kann. Diese wiederum ist hauptsächlich an die Unterschwellenspannungssteigung S gekoppelt: Bleibt sie unverändert, so sind geringere Werte von  $U_{th}$  mit höheren Unterschwellenströmen und größerem  $I_{off}$  verbunden. Die Verringerung von  $U_{th}$  um 0.1 V bedeutet dann einen Anstieg des Leckstroms bei  $I_{off}$  um den Faktor zehn [14]. Daß S nicht oder nur wenig verbessert werden kann, ist in ihrer starken Abhängigkeit von der thermischen Diffusion der Elektronen begründet [15]:

$$S = \left(\frac{kT}{q} \ln 10\right) \left(1 + \frac{\varepsilon_{si} t_{ox}}{\varepsilon_{ox} t_{dep}}\right)$$

$$= 60 \,\text{mV} \left(1 + \frac{\varepsilon_{si} t_{ox}}{\varepsilon_{ox} t_{dep}}\right) \qquad \text{(für RT)}$$

$$= 60 \,\text{mV} \cdot m$$

S ist also von der Betriebsspannung und der Kanallänge unabhängig und hat bei Raumtemperatur eine Untergrenze bei  $60\,\mathrm{mV}$ . Der Koeffizient m ist von Materialkonstanten und der Ausdehnung der Raumladungszone  $t_{dep}$  abhängig und liegt üblicherweise bei 1,2-1,5 [14]. Für  $t_{dep}$  wiederum gilt [9]:

$$t_{dep} \approx \sqrt{\frac{4 \,\varepsilon_{si} \, kT \ln(N_{sub}/n_i)}{q^2 N_{sub}}}$$

mit  $n_i$  der intrinsischen Ladungsträgerkonzentration von Silizium und q der Elementarladung. Die Unterschwellenspannungssteigung S kann somit nicht skaliert werden

und könnte nur über das Absenken der Betriebstemperatur unter den Grenzwert von  $60 \,\mathrm{mV/dec}$  gedrückt werden. Der Skalierungsparameter  $t_{dep}$  kann für einen "normalen" MOSFET nur über die Erhöhung der Kanaldotierung verkleinert werden, was jedoch zu einer Erhöhung von  $U_{th}$ , zu größeren Feldern am Oxid und zu einer Verringerung der Ladungsträgerbeweglichkeit führt [16, 17].

Eine physikalische Grenze wird bald bei der Verwendung von  $SiO_2$  als Gateoxid erreicht: In einer MOS-Struktur sind mindestens vier Atomlagen  $SiO_2$  (=0,7 nm) notwendig, damit sich eine Bandlücke ausbilden kann; auf Grund der Oberflächenrauhigkeit heutiger Herstellungstechniken sind 1,2 nm die Grenze [18]. Diese Gateoxiddicken werden bereits für 2006 oder 2010 (je nach Anwendung) benötigt [19]. Ein weiteres Problem dabei sind Tunnelströme, die bei Schichtdicken unterhalb von 3 nm signifikant zunehmen. Ein Ausweg sind alternative Gateoxide, sogenannte "high-k-Dielektrika"<sup>3</sup>. Ziel der dünneren Gateoxide ist eine Vergrößerung der Gatekapazität  $C_{ox}$ . Dies kann jedoch auch durch andere Dielektrika erzielt werden, sofern die Dielektrizitätskonstante k > 3, 9 ist – dies ist der Wert für SiO<sub>2</sub>. Es gilt dann:

$$C_{\text{high-}k} = \frac{k_{\text{high-}k} \, \varepsilon_0}{t_{\text{high-}k}}$$

Damit ergibt sich für die äquivalente Oxiddicke  $EOT^4$ :

$$EOT = \frac{k_{ox}}{k_{\text{high-}k}} t_{\text{high-}k}$$

Das heißt, bei der Verwendung von alternativen Gateoxiden kann das Oxid um den Faktor  $k_{\text{high-}k}/k_{ox}$  dicker sein als SiO<sub>2</sub>, so daß Tunneln unterdrückt wird. Damit hofft man die Skalierungsregeln der kommenden Generationen erfüllen zu können, auch wenn sich mit der Auswahl und den Eigenschaften der alternativen Gateoxide weitere Problemfelder eröffnen.

## 3.5 Kurzkanaleffekte

Die Herleitung der Transistoreigenschaften galt für bestimmte Bedingungen [12]. Diese sind eine ideale MOS-Struktur, eine konstante Ladungsträgerbeweglichkeit  $\mu$  im Inversionskanal, homogene Kanaldotierung, vernachlässigbare Leckströme und ein im Vergleich zur lateralen Feldstärke großes transversales Feld im Kanalgebiet. Diese Voraussetzungen sind bei relativ großen Abmessungen (Kanallängen im  $\mu$ m-Bereich und Oxiddicken > 10 nm) in der Regel erfüllt, so daß man von "Langkanalverhalten" spricht. Langkanalverhalten entspricht dem bisher beschriebenen Transistorverhalten.

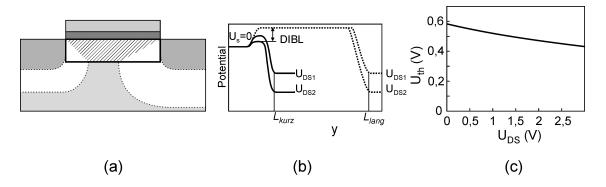

Abweichungen vom Langkanalverhalten bezeichnet man allgemein als "Kurzkanalverhalten", da sie insbesondere bei kleindimensionierten Bauelementen zu finden sind. Im Folgenden werden die wichtigsten Kurzkanaleffekte beschrieben. Abbildung 3.12 verdeutlicht abschließend ihre Auswirkungen auf die Kennlinienfelder.

<sup>&</sup>lt;sup>3</sup>Teilweise wird statt k auch  $\kappa$  verwendet, im Deutschen meist  $\varepsilon_r$ .

<sup>&</sup>lt;sup>4</sup>Equivalent oxide thickness, die entsprechende Dicke SiO<sub>2</sub>, die zu einer gleichen Gatekapazität führt.

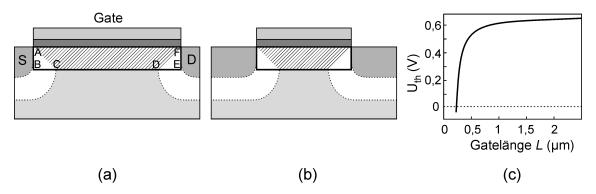

#### 3.5.1 $U_{th}$ -Roll-Off

Mit dem Begriff " $U_{th}$ -Roll-Off" wird die Abhängigkeit der Schwellenspannung  $U_{th}$  von der Kanallänge L bezeichnet. Wie in 3.1 beschrieben, ist bei  $U_G = U_{th}$  die Raumladungszone unter dem Gate maximal, und bei größeren Gatespannungen bildet sich ein Inversionskanal aus. Die Größe dieser Zone, die durch die Gatespannung verarmt werden muß, bestimmt also den Wert von  $U_{th}$ . In der Abbildung 3.8 a wäre die vollständige Raumladungszone das Rechteck ABEF. An den Rändern jedoch wird ein Teil dieses Kanalgebietes durch die p-n-Übergänge an Source und Drain, welche ebenfalls Raumladungszonen ausbilden, verarmt. Es wird also effektiv nur noch das Trapez ACDF durch das Gate kontrolliert. Aus diesem Grund setzt die Inversion bei kleineren Schwellenspannungen ein. Ist die Gatelänge in der Größenordnung der Verarmungszonen, so ist der relative Anteil der nicht vom Gate kontrollierten Gebiete signifikant größer als bei langen Kanälen (Abb. 3.8 b). Die Verminderung der Schwellenspannung mit abnehmender Gatelänge ist in Abbildung 3.8 c dargestellt.

Abb. 3.8:  $U_{th}$ -Roll-Off: An den Rändern des Kanalgebietes sind Bereiche der Raumladungszone nicht durch die Gatespannung kontrolliert (Dreiecke ABC und DEF in (a)). Dieser Anteil wächst relativ zum Gesamtgebiet, wenn die Gatelänge schrumpft (b). Kommt L in die Größenordnung der Raumladungszonen, so ist der Effekt dominierend. In (c) ist die Abhängigkeit beispielhaft dargestellt.

## 3.5.2 Drain-Induced Barrier Lowering

Dieser Effekt beschreibt die Abhängigkeit der Schwellenspannung  $U_{th}$  von der Source-Drain-Spannung  $U_{DS}$ . Für die Dicke der Verarmungsgebiete an Source und Drain gilt [9]:

$$t_S = \sqrt{\frac{2 \,\varepsilon_{si}}{q \,N_{sub}} (2 \,\Psi_B + U_{SB})}$$

$$t_D = \sqrt{\frac{2 \,\varepsilon_{si}}{q \,N_{sub}} (2 \,\Psi_B + U_{SB} + U_{DS})}$$

<sup>&</sup>lt;sup>5</sup>Dieses Modell, bei dem die Größe der Verarmungszone betrachtet wird, die tatsächlich vom Gate kontrolliert wird, heißt "Trapez-Ansatz" oder "charge-sharing".

mit  $U_{SB}$  einer möglichen Substratvorspannung. Die Raumladungszone dehnt sich also am Drain mit ansteigender Source-Drain-Spannung aus, da dieser p-n-Übergang in Sperrichtung geschaltet ist. Dies hat zur Folge, daß ein weiterer, von  $U_{DS}$  abhängiger Anteil der Raumladungszone unter dem Gate nicht von der Gatespannung kontrolliert wird (Abb. 3.9 a). Dieser Effekt kann auch mit Hilfe der Potentialbarriere für die Ladungsträger zwischen Source und Drain am Kanal beschrieben werden. Bei kurzen Kanälen sinkt diese Barriere durch die angelegte Source-Drain-Spannung und die Inversion setzt bei geringeren Spannungen  $U_{th}$  ein (Abb. 3.9 b). Dieser Ansatz ist der Grund für die Bezeichnung "Drain-Induced Barrier Lowering" (DIBL). Eine Folge des DIBL sind höhere Leckströme  $I_{off}$ .

Abb. 3.9: Drain-Induced Barrier Lowering: (a) Bei angelegter Source-Drain-Spannung dehnt sich die Raumladungszone am Draingebiet aus. (b) Eine alternative Beschreibung betrachtet die Potentialbarriere zwischen Source und Drain, die bei kurzen Kanälen durch  $U_{DS}$  abgesenkt wird. (c) Beispielhafter Verlauf der Abhängigkeit.

### 3.5.3 Punch-Through

Wird die Raumladungszone am Drain so groß, daß  $t_S + t_D = L$  ist, berühren sich also die Raumladungszonen von Source und Drain (Abb. 3.10), so fließt ein zusätzlicher, nicht vom Gate kontrollierter Strom auch unterhalb der Schwellenspannung [12]. Der Strom ist proportional zu  $U_{DS}^2$  und kann durch Erhöhung der Substratdotierung verhindert werden, da sich dann die Raumladungszonen verkleinern. Bei Kurzkanal-MOSFETs bestimmt der *Punch-Through* meist die maximale Source-Drain-Spannung.

Abb. 3.10: Punch-Through: Berühren sich die Raumladungszonen von Source und Drain, so fließt ein nicht vom Gate kontrollierter Strom.

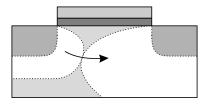

### 3.5.4 Kanallängenmodulation

Als Kanallängenmodulation wird die Kanallängenverkürzung im Sättigungsbereich bezeichnet. Wenn für  $U_{DS} > U_G - U_{th} = U_{DSsat}$  der Inversionskanal am Drain abschnürt (siehe Abb. 3.4), verkleinert sich die effektive Kanallänge  $L_{eff}$ , da die gesamte Spannung nur über dem verkürzten Inversionskanal abfällt (Abb. 3.11 a). Für die Verkürzung gilt [20]:

$$\Delta L = \sqrt{\frac{2\,\varepsilon_{si}}{q\,N_{sub}}(U_{DS} - U_{DSsat})}$$

Diese, von der Kanallänge unabhängige Änderung ist ebenfalls für kleine Kanallängen signifikanter als für große. Die Folge ist eine größere laterale Feldstärke, so daß mehr Ladungsträger aus dem Source gezogen werden. In den Kennlinien äußert sich die Kanallängenmodulation also durch fehlende Sättigung: Der Sättigungsstrom steigt linear mit der Drainspannung. Die Sättigungsstromgleichung  $I_{Dsat} = k U_{DSsat}^2$  von Langkanal-MOSFETs (siehe Abb. 3.3) verändert sich dann zu

$$I_{Dsat} = k U_{DSsat}^{2} \cdot (1 + \lambda U_{DS})$$

Der Kanallängenmodulationsfaktor  $\lambda$  der Parametrisierung kann grafisch aus dem Ausgangskennlinienfeld bestimmt werden (Abb. 3.11 b).

Abb. 3.11: Kanallängenmodulation: (a) Die effektive Kanallänge bei Sättigung ist nicht mehr der geometrische Abstand zwischen Source und Drain, da der Inversionskanal abschnürt. (b) Der lineare,  $U_{DS}$ -abhängige Anstieg im Sättigungsbereich läßt sich durch  $\lambda$  beschreiben und geometrisch aus den Ausgangskennlinien bestimmen.

#### 3.5.5 Unterschwellströme

Nach dem vereinfachten Modell fließt im Unterschwellbereich  $(U_G < U_{th})$  überhaupt kein Drainstrom. Tatsächlich aber klingt  $I_D$  exponentiell ab, wenn  $U_G$  unter  $U_{th}$  sinkt:

$$I_D \propto \frac{1}{L_{eff}} \, \mathrm{e}^{q \, U_G/kT}$$

Bei schwacher Inversion fließt also ein Reststrom. Während die Unterschwellströme bei Langkanaltransistoren für  $U_{DS} > 3kT/q$  von der Source-Drain-Spannung unabhängig sind [12], steigen sie für kleine Gatelängen stark mit  $U_{DS}$ . Grund ist die Proportionalität zu  $1/L_{eff}$ .  $L_{eff}$  ist hier die um die Raumladungszonen an Source und Drain reduzierte Gatelänge und ist – wie beim DIBL beschrieben – für kleine L stark von  $U_{DS}$  abhängig.

Restströme unterhalb der Einsatzspannung können die statische Stromaufnahme von integrierten Schaltungen wesentlich beeinflussen, denn diese Ströme fließen bei jedem inaktiv geschalteten Transistor. Auch werden Haltezeiten dynamischer Schaltungen, bei denen digitale Informationen auf Kapazitäten gespeichert werden, verkürzt.

Abb. 3.12: Auswirkungen der Kurzkanaleffekte auf die Kennlinien eines MOSFETs (schematisch). Ausgangskennlinienfelder beim Langkanal- und Kurzkanal-Transistor (a)+(b). Transferkennlinienfelder beim Langkanal- und Kurzkanal-Transistor (c)+(d).

## 3.6 Neue MOSFET-Konzepte

Für die Chipgenerationen der vergangenen Jahre mußten die Designs der MOS-FETs abweichend von der Skalierungsregel verändert werden, damit das beschriebene Kurzkanalverhalten unterdrückt werden konnte. Zunächst wurde das elektrische Feld mit einem anderen Skalierfaktor entworfen, dann Transistordimensionen und deren Zuleitungen entkoppelt [21]. Derzeitige MOSFETs unterdrücken Kurzkanaleffekte mit Dotierprofilen im Kanalbereich ("channel design", Abb. 3.13). Dadurch werden die Verarmungszonen an Source und Drain verkleinert, wodurch das vom Gate kontrollierte Gebiet maximiert wird. Für zukünftige MOSFET-Generationen jedoch ist das größte Problem die Tiefe der Verarmungszone  $t_{dep}$ , die nicht wie die anderen Parameter skaliert werden kann und dadurch Hauptursache für den  $U_{th}$ -Roll-Off ist. Neue MOSFET-Konzepte setzen deshalb auf die Begrenzung des Kanalgebietes durch die Verwendung dünner Siliziumschichten, die dann vollständig verarmen. Hier wiederum kann man unterscheiden zwischen planaren MOSFETs, die aus einer Siliziumschicht auf Oxid hergestellt werden – sogenannten SOI-MOSFETs<sup>6</sup> - und vertikalen MOSFETs, bei denen die Siliziumschicht als Steg senkrecht zur Waferoberfläche angeordnet ist.

Abb. 3.13: Der  $U_{th}$ -Roll-Off kann durch geeignetes Doping im Kanalbereich vermindert werden. Diese hier gezeigte Form wird "Halo-Doping" genannt (aus [16]).

#### 3.6.1 SOI-MOSFETs

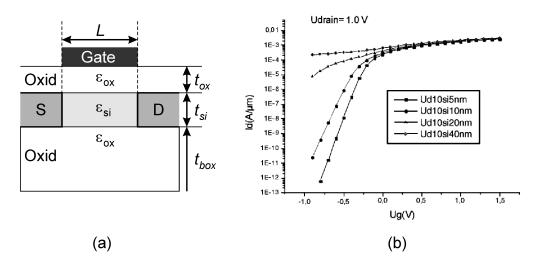

Bei einem SOI-MOSFET ist die Tiefe der Verarmungszone  $t_{dep}$  durch die Dicke der Siliziumschicht  $t_{si}$  begrenzt. (Abb. 3.14 a). Ist die Schicht so dünn, daß das gesamte Kanalgebiet verarmt, vermindern sich die Kurzkanaleffekte (Abb. 3.14 b). Kleine-

<sup>&</sup>lt;sup>6</sup>SOI, silicon on insulator, Silizium auf Isolator.

re Gatelängen können somit erreicht werden. Nachteilig sind die extrem dünnen Siliziumschichten (5–10 nm) sowie die relativ hohen Kosten für SOI-Wafer.

Abb. 3.14: (a) Bei einem SOI-MOSFET ist das Kanalgebiet vom Substrat durch eine Isolierschicht getrennt. (b) Die Folge sind verminderte Kurzkanaleffekte: Je dünner die Oxidschicht ist, desto größer sind Schwellenspannung und Off-Ströme und desto kleiner die Unterschwellenspannungssteigung (Simulationen für  $L=50\,\mathrm{nm},\ t_{si}=40\,\mathrm{nm}$  und  $t_{ox}=2\,\mathrm{nm},\ aus\ [2]$ ).

#### 3.6.2 Double-Gate-MOSFETs

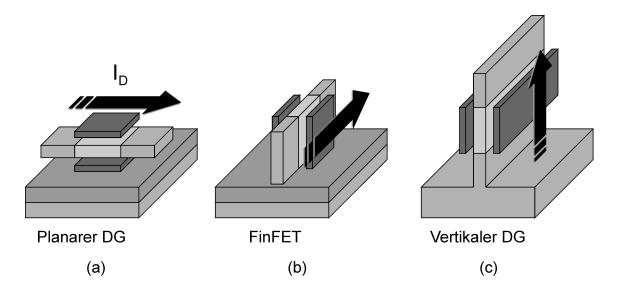

Weitere Vorteile können erzielt werden, wenn das Kanalgebiet von beiden Seiten jeweils durch ein Gate gesteuert wird; man spricht dann von "Double-Gate" (DG). Es gibt drei verschiedene Arten von DG-MOSFETs, die sich in der Orientierung ihrer Kanäle unterscheiden:

| Planarer DG   | Kanal und Strom parallel zur Waferoberfläche    | Abb. 3.15 a           |

|---------------|-------------------------------------------------|-----------------------|

| FinFET        | Kanal senkrecht und Strom parallel zur Wafer-OF | Abb. 3.15 b           |

| Vertikaler DG | Kanal und Strom senkrecht zur Waferoberfläche   | Abb. $3.15\mathrm{c}$ |

Der planare DG-MOSFET entspricht einem SOI-MOSFET, bei dem auf der Unterseite des Kanals ein zweites Gate angebracht ist. Beim FinFET wird der Steg aus einer SOI-Schicht herausgeätzt. Source, Kanal und Drain sind lateral angeordnet, so daß der Strom im Steg, aber parallel zur Waferoberfläche fließt. Beim vertikalen DG sind Source, Kanal und Drain übereinander angeordnet in einem Steg, der aus dem Substrat geätzt wurde. Das Kanalgebiet ist also über die Dicke der mittleren Schicht definiert, nicht durch Lithographie, wie bei den anderen Versionen. Der Strom fließt vertikal zur Waferoberfläche.

Auf Grund des symmetrischen Aufbaus können das elektrische Feld am Drain noch besser unterdrückt und bessere Transistoreigenschaften erreicht werden. Die Siliziumschicht muß nicht so dünn sein wie bei SOI-MOSFETs, da an jedem Gate nur die halbe Dicke der Siliziumschicht verarmt werden muß:  $t_{dep} = t_{si}/2$ . Dabei fließt

Abb. 3.15: Es gibt drei verschiedene Arten von Double-Gate-MOSFETs: (a) Planarer DG, (b) FinFET und (c) vertikaler DG. Die ersten beiden Variationen werden aus SOI-Wafern hergestellt, und der Stromfluß ist bei beiden parallel zur Waferoberfläche, beim planaren DG Flach in der Schicht, beim FinFET im Steg. Der vertikale DG ist aus Substrat geätzt, und der Strom fließt senkrecht im Steg.

durch die Parallelschaltung der beiden Kanäle der doppelte Strom [2]. Auch können Dotierprofile im Kanalgebiet vermieden werden, die einen zusätzlichen Beitrag zum elektrischen Feld an der Oberfläche leisten [21]. Undotierte Kanalgebiete verbessern sogar den Ladungstransport: Coulombstreuung wird reduziert bei weniger ionisierten Störstellen im undotierten/gering dotierten Kanal, und geringere elektrische Felder an der Oberfläche verringern Oberflächenstreuungen [21].

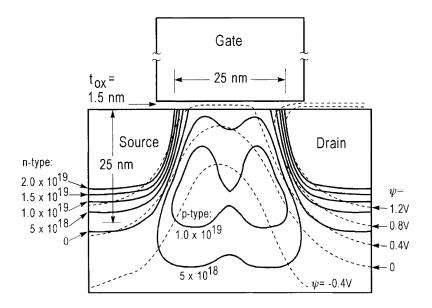

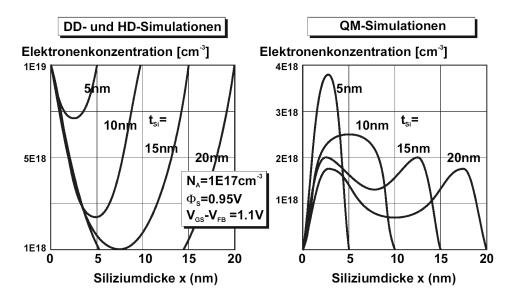

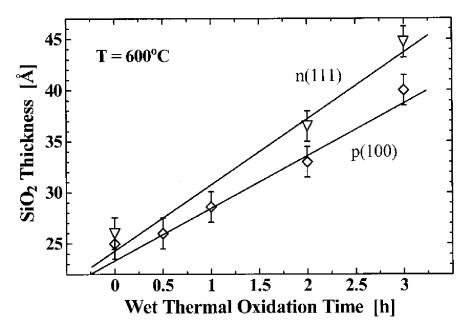

Eine Besonderheit von Double-Gate-MOSFETs ist die Möglichkeit, bei hinreichend dünnem Silizium eine Volumeninversion erreichen zu können. Simulationen von Schulz von vertikalen DG-MOSFETs [4] haben gezeigt, daß diese Volumeninversion mit den Standardmodellen "Drift-Diffusion" und "Hydrodynamik" nicht erfaßt werden können (Abb. 3.16, links). Quantendynamische Simulationen jedoch zeigen eine maximale Elektronenkonzentration in der Stegmitte für  $t_{si} \leq 10 \,\mathrm{nm}$ .

Vollständige Verarmung bei vertikalen DG-MOSFETs mit einer Kanallänge von 100 nm und einer Substratdotierung von  $N_{sub}=10^{18}\,\mathrm{cm}^{-3}$  wurde bei Simulationen für  $t_{si}<70$  nm erreicht, bei skalierten Transistoren mit  $L=50\,\mathrm{nm}$  und  $N_{sub}=5\cdot10^{18}\,\mathrm{cm}^{-3}$  für  $t_{si}<30$  nm. Mit diesen vollständig verarmten DG-MOSFETs können Kurzkanaleigenschaften jedoch bereits verbessert werden (siehe Abb. 3.17).

<sup>&</sup>lt;sup>7</sup>Beim Drift-Diffusions-Modell setzt sich die Ladungsstromdichte aus dem Driftstrom und dem Diffusionsstrom zusammen.

<sup>&</sup>lt;sup>8</sup>Beim Hydrodynamik- Modell werden zusätzlich sog. "heiße Elektronen" berücksichtigt durch Einführung einer teilchenabhängigen Ladungsträgertemperatur.

Abb. 3.16: Simulationen der Elektronenverteilung im DG-MOSFET mit dünnen Siliziumstegen. Volumeninversion ist nur bei quantenmechanischer Simulation bei Schichtdicken von höchstens 10 nm zu beobachten. (Abb. aus [4]).

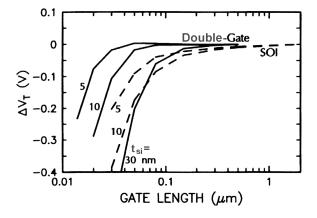

Abb. 3.17: Das Einbrechen der Schwellenspannung  $U_{th}$  bei Verringerung der Kanallänge tritt bei DG-MOSFETs deutlich später auf als bei SOI-MOSFETs. (Simulation, nach [14].)

# Kapitel 4

## Verwendete Technologie

In diesem Kapitel werden die wichtigsten Technologien beschrieben, die für die Herstellung der Transistoren verwendet wurden. Die genauen Prozeßparameter sind im Kapitel 5 angegeben, in dem die Prozeßfolge der drei Varianten des NovaFETs erläutert sind.

## 4.1 Technologien zur Strukturerzeugung

Die Strukturerzeugung gliedert sich in zwei Bereiche: den der Strukturdefinition, die hier mittels Elektronenstrahlschreiben oder optischer Lithographie erfolgt, und den der Strukturübertragung, die in der Regel durch Ätzung erreicht wird.

## 4.1.1 Elektronenstrahl-Lithographie

Neben dem üblichen Verfahren der optischen Lithographie (siehe 4.1.2), bei dem die Energie durch Photonen übertragen wird, können auch Elektronen verwendet werden. Während das parallele Schreiben (Projektionsverfahren) mit Elektronen noch in den Anfängen steckt, da die Masken hierbei ein Problem darstellen, ist das serielle oder "direkte" Schreiben etabliert. Möglich ist dies, da Elektronen geladene Teilchen sind, deren Strahlen fokussiert werden können; ein optisches System wird dadurch möglich. Das darauf basierende Lithographieverfahren heißt Elektronenstrahl-Lithographie oder "E-Beam-Schreiben" und ist üblich zur Maskenherstellung oder Einzelfertigung von Wafern. Dabei wird ein dünner Strahl über die Probe geführt und so der für diese Energie empfindliche Resist seriell belichtet. Der Resist wird - wie bei der optischen Lithographie - vorher auf die Probe aufgeschleudert und getrocknet. Näheres zu Auswahl und Eigenschaften des hier verwendeten Resists ist in Kapitel 6 beschrieben. Vorteil von E-Beam-Schreiben ist das hohe Auflösungspotential (die Wellenlänge ist nicht begrenzend), Nachteil der geringe Durchsatz. Die wichtigsten Variablen beim E-Beam-Schreiben sind die Strahlgröße (beam size), die Schrittweite (beam step size), die Dosis und die Beschleunigungsspannung.

Der hier verwendeten Elektronenstrahlschreiber EBPG 5HR der Firma Leica verwendet das Gauß-Rundstrahl-System im Vektor-Scan-Verfahren. Dabei wird ein runder, gaußförmig gebündelter Elektronenstrahl nur auf die zu belichtenden Flächen

gelenkt. Andere mögliche Systeme von E-Beam-Schreibern sind z. B. das Rechteckstrahl- oder das Variabler-Strahl-System, ein anderes Verfahren das Raster-Scan-Verfahren, bei dem das gesamte Feld mit dem Elektronenstrahl überstrichen wird; die Blende wird dann nur bei den zu belichtenden Flächen geöffnet.

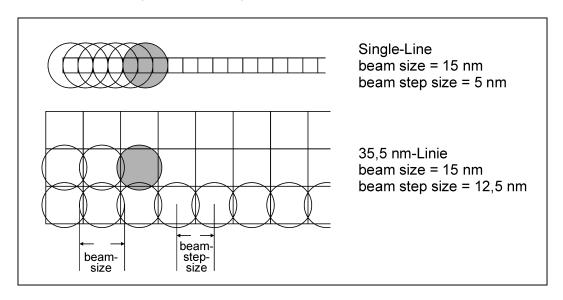

Während die Spannung beim Standardwert 50 kV unverändert gelassen wurde, waren die anderen Parameter Optimierungsgrößen. Bei der Strahlgröße wurde unterschieden zwischen Linienschreiben und Flächenschreiben: Die Flächen (Pads, Justiermarken etc.) wurden mit einem 300 nm-Strahl geschrieben, die Linien mit dem dünnsten Strahl, dessen Durchmesser nominell 15 nm beträgt. Die Schrittweite ist abhängig von der Strahlgröße: Für glatte Kanten und gleichmäßige Flächenbelichtung muß die Schrittweite kleiner als der Strahldurchmesser sein, für eine akzeptable Schreibzeit darf sie nicht zu klein sein. Die Flächen wurden deshalb mit einer Schrittweite von 250 nm, die Linien mit einer Schrittweite von 12,5 nm geschrieben. Eine Ausnahme bildeten hier die Single-Lines, die mit einer Schrittweite von 5 nm geschrieben wurden (siehe Abb. 4.1).

Abb. 4.1: Strahlführung beim Elektronenstrahlschreiben. Im gleichen Maßstab sind hier eine Single-Line und eine 37,5 nm-Linie schematisch dargestellt.

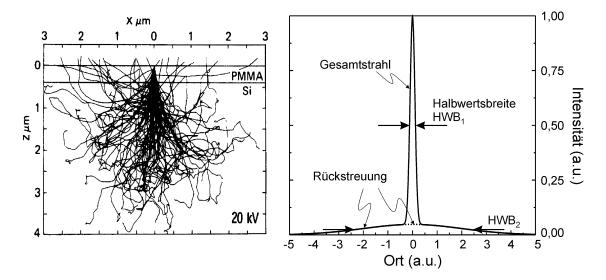

Die Abbildung 4.2 zeigt Auswirkung der Streuung in der Probe auf die Intensität im Resist: Mehrere Mikrometer abseits des Hauptstrahls wird der Resist durch tief im Substrat rückgestreute Elektronen belichtet. Dieser sog. Proximityeffekt ist insbesondere bei *lines and spaces*<sup>2</sup> sowie bei unbelichteten Flächen inmitten großer belichteter Flächen spürbar, da sich die geringe Intensität durch die Rückstreuung integriert, wenn viele Orte innerhalb der HWB<sub>2</sub> eines unbelichteten Ortes belichtet werden. Diese integrierte Proximitydosis kann in der Größe der Dosis durch den Hauptstrahl liegen.

$<sup>^1\</sup>mathrm{Auch}$  bei gaußförmigem Strahl wird weiterhin von Strahlgröße oder -durchmesser statt von Halbwertsbreite gesprochen.

<sup>&</sup>lt;sup>2</sup>Lines and spaces nennt man Linienfelder, bei denen der Abstand zwischen den Linen in der Größenordnung der Linienbreite ist.

Abb. 4.2: Strahlform beim E-Beam-Schreiben. Streuung der Elektronen tief im Substrat bewirkt, daß der Resist auch mehrere Mikrometer abseits des Hauptstrahls belichtet wird. Links eine Monte-Carlo-Simulation von 20 kV-Elektronen in PMMA mit Silizium als Substrat (aus [22]). Rechts schematisch die resultierende Intensität im Resist. Die Halbwertsbreiten von Vorwärts- und Rückwärtsstreuung sind nicht maßstabsgetreu; der Hauptstrahl ist deutlich schärfer.

### 4.1.2 Optische Lithographie

Außer den dünnen Linien, die den aktiven Bereich des Transistors beinhalten, werden die übrigen Strukturen mit optischer Lithographie übertragen. Dazu wird ein lichtempfindlicher Film (Lack oder Resist genannt) auf die Probe aufgeschleudert. Die Strukturen liegen auf einer Maske vor und werden von dort auf die Probe abgebildet. Die Maske besteht aus Quarzglas mit einer strukturierten Chromschicht; die Bereiche der Probe, die nicht belichtet werden sollen, werden durch das Chrom maskiert. Bei der Belichtung verändert sich die chemische Struktur des Photolackes derart, daß er sich bei der anschließenden Entwicklung in der Entwicklerlauge löst (Positivprozeß).<sup>3</sup> Man unterscheidet zwischen Projektions-, Proximity- und Kontaktbelichtung. Bei der Projektionsbelichtung wird die Maske so in den Lichtweg eingebaut, daß ein (meist verkleinertes) Bild der Strukturen auf die Probe projeziert wird. Bei der Proximitybelichtung wird ein direkter Schatten auf die Probe geworfen, während die Maske einige Mikrometer von der Probe entfernt ist. Dies schont die Maske und die Probe, verringert aber die Auflösung. Beim hier angewendeten Verfahren der Kontaktbelichtung wird die Maske auf den Wafer gepreßt bzw. im Vakuummodus der Raum zwischen Maske und Wafer leergepumpt und so der Wafer an die Maske gesaugt.

Das Prinzip der Kontaktbelichtung hat verschiedene begrenzende Auflösungskriterien: zum einen die theoretische "minimal feature size" (MFS, kleinste darstellbare Strukturgröße), die sich aus verwendeter Lackdicke d (Schirmabstand) und verwen-

<sup>&</sup>lt;sup>3</sup>Beim Negativprozeß löst sich der unbelichtete Resist im Entwickler, während der belichtete Teil stehen bleibt.

deter Wellenlänge  $\lambda$  ergibt. Für Nahbeugung gilt

$$MFS \approx \sqrt{\lambda \cdot d}$$

Hieraus ergibt sich für  $\lambda=250\,\mathrm{nm}$  und Lackdicke  $d\approx500$ –600 nm eine theoretische minimale Strukturgröße von 350–400 nm.

Dieser theoretische Wert kann allerdings nur erreicht werden, wenn die Strukturgrößen auf der Maske mit mindestens dieser Auflösung realisiert werden können, im Gegensatz zur Projektionsbelichtung, bei der die Maske auf den Wafer verkleinert projiziert wird und sich so die Auflösung gegenüber der Maske verbessern läßt. Aus diesem Kriterium folgt die hier mögliche minimale Strukturgröße von ca. 700 nm durch optische Lithographie. Dies entspricht ungefähr dem Industriestandard von 1989.

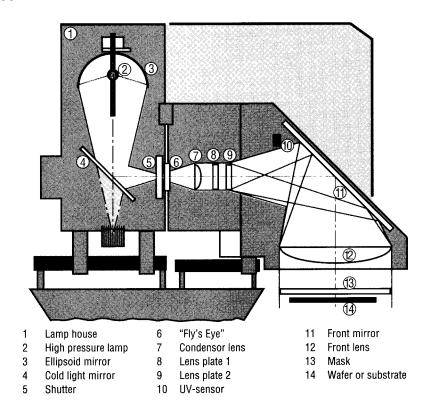

Die Belichtung erfolgte hier durch den Belichter MA 6 der Firma  $S\ddot{u}ss$  (Abb. 4.3). Als Lichtquelle dient eine Xenon-Quecksilberdampflampe mit einer hohen Intensität bei  $\lambda \approx 250\,\mathrm{nm}$ .

Abb. 4.3: Optisches System des Belichters MA6 der Firma Süss.

## 4.1.3 Strukturübertragung durch RIE-Ätzen

Man kann zwei verschiedene Ätzprinzipien unterscheiden: die naßchemische Ätzung und die Trockenätzung. Bei der naßchemischen Ätzung wird die Probe in eine Ätzlösung eingebracht, die chemisch mit dem zu entfernenden Material reagiert und

dieses dadurch auflöst. Nachteile sind die Isotropie der Ätzung und Benetzungsprobleme beim Ätzen kleinster Löcher. Die Trockenätzung stellt heute den wichtigsten Strukturübertragungsprozeß in der Halbleiterfertigung dar, weil durch ihre Anwendung eine sehr genaue Übertragung der immer kleiner werdenden Maskenstrukturen erzielt werden kann. Das "Reaktive Ionen Ätzen" ist ein Trockenätzverfahren, das sich als Standardverfahren in der Halbleitertechnik etabliert hat.

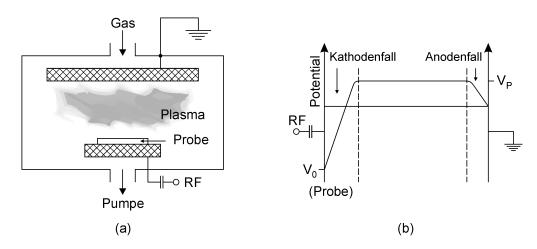

In einer RIE (Abb. 4.4 (a)) liegt die zu ätzende Probe auf einer Elektrode, an die gegenüber einer anderen, geerdeten Elektrode im Hochvakuum ( $\sim 10^{-5}$  bar) eine hochfrequente Wechselspannung angelegt wird. Durch diese Wechselspannung werden die in den Reaktor geleiteten Prozeßgase teilweise dissoziiert ( $\sim 0.1-10\%$ ) bzw. ionisiert ( $\sim 0.001-0.01\%$ ). Durch die einsetzende Plasmaentladung bildet sich zwischen den Elektroden ein Potentialverlauf aus (Abb. 4.4 (b)).

Abb. 4.4: Schematische Darstellung der RIE. (a) Reaktorgeometrie eines RIE-Parallel-plattenreaktors. (b) Potentialverlauf während des Ätzprozesses.

Das Plasmapotential  $V_P$  ist durch die Prozeßparameter Gasfluß, Leistung, Wechselspannung und Prozeßdruck bestimmt. Im elektrischen Feld werden die reaktiven Ionen zur Probe hin beschleunigt; ist die Potentialdifferenz  $V_P - V_0$  zwischen Plasmapotential und Probenort groß, können die Ionen fast senkrecht auf die Probe auftreffen und anisotropes Ätzen ist möglich.

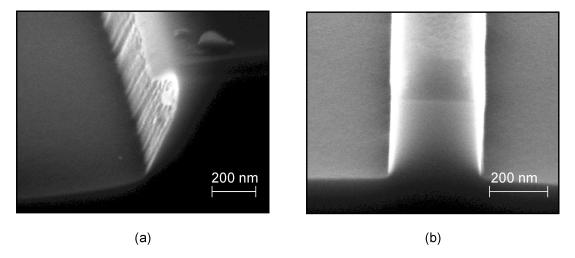

Der Ätzmechanismus ist eine Kombination aus physikalischem Ätzen (Sputtern), bei dem das Material durch den Impuls der auftreffenden Ionen abgetragen wird, und chemischem Ätzen, bei dem das Material mit den Ionen chemisch reagiert und flüchtige Reaktionsprodukte bildet. Die Ätzkomponenten beeinflussen sich gegenseitig, da die Bindungen im Material chemisch geschwächt werden und dadurch das Material leichter gesputtert werden kann. Andererseits werden durch den Ionenbeschuß Oberflächenschäden induziert und Energien bereitgestellt, die das chemische Ätzen erleichtert. Die physikalische Komponente des Ätzprozesses führt zur Anisotropie, während die chemische Komponente selektives Ätzen ermöglicht. Ergebnisse isotropen und anisotropen Ätzens werden in Abbildung 4.5 gezeigt.

<sup>&</sup>lt;sup>4</sup>Man spricht auch von "RIE-Ätzen" von engl. reactive ion etcher

Abb. 4.5: REM-Aufnahmen: Beispiele für isotropes und anisotropes RIE-Ätzen. (a) Isotropes Ätzen von Silizium mit TEOS-SiO<sub>2</sub> als Maske. 7,5 min mit Plasma: Ar 40 ml, SF<sub>6</sub> 1 ml, 150 W, 20 mbar, auf Quarzteller. (b) Anisotropes Ätzen von Silizium mit Resist UV 6 als Maske. 10 min mit Plasma: Ar 40 ml, SF<sub>6</sub> 1 ml, 150 W, 20 mbar, auf Graphitteller.

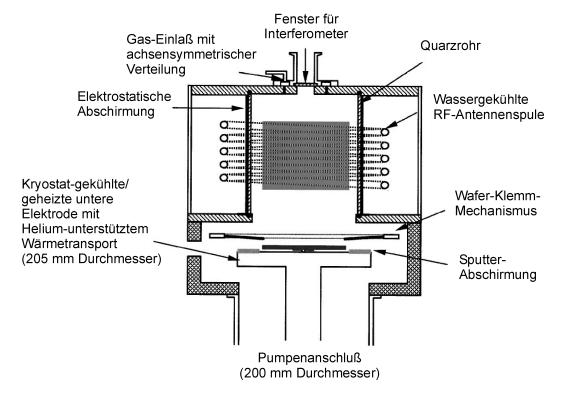

Abb. 4.6: Prinzip der ICP-RIE. Die Ionenstromdichte wird durch die induktiv gekoppelte RF-Leistung unabhängig von der Ionenenergie eingestellt, welche an der Substratelektrode eingestellt wird.

Bei dieser Standardtechnologie werden Ionenenergie und -stromdichte durch eine einzige angelegte Leistung erreicht. Es wurden Techniken entwickelt, um diese

Werte unabhängig voneinander zu kontrollieren: Mit einer "ICP-RIE" wird das Plasma über eine Spule durch eine induktiv gekoppelte RF-Leistung erzeugt. Eine zweite, kapazitiv gekoppelte RF-Leistung an der Substratelektrode kontrolliert die Ionenenergie über die eingestellte Bias-Leistung. Die Komponenten einer solchen ICP-Kammer sind in Abbildung 4.6 dargestellt. Dieser weitere Freiheitsgrad ermöglicht besonders selektive Ätzprozesse (siehe auch 6.4).

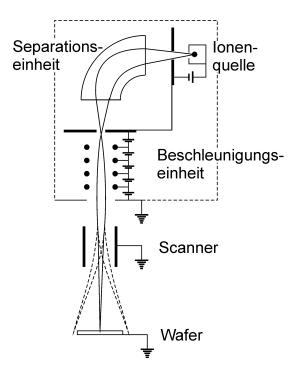

## 4.2 Ionenimplantation

Die Ionenimplantation ist ein Dotierverfahren, bei der geladene Teilchen auf hohe Geschwindigkeit gebracht und auf einen Körper geschossen werden. Die Ionen werden im Innern des Targets durch Stöße abgebremst und lagern sich in den oberen Schichten ein. Ein Ionenimplanter besteht im Wesentlichen aus einer Ionenquelle, welche Festkörper, Flüssigkeiten oder Gase ionisiert, einer Beschleunigungseinheit, einer Separationseinheit, die die Ionen nach ihrer Masse und Ionisierung trennt, und einer Strahlablenkung (Scanner), die die Ionen gleichförmig über das Ziel verteilt (Abb. 4.7).

Abb. 4.7: Prinzip eines Ionenimplanters (nach [23]).

Der vorbeschleunigte Ionenstrahl besteht aus einem Gemisch von Ionen, aus denen die gewünschte Sorte herausgefiltert werden muß. In der einfachsten Form geschieht das in einem homogenen Magnetfeld senkrecht zum Ionenstrahl. Die Ionen werden auf Kreisbahnen abgelenkt, deren Radien von der Masse und der Ladung der Ionen abhängen. Der Austrittswinkel hinter der Separationseinheit ist also typisch

<sup>&</sup>lt;sup>5</sup>Inductive Coupled Plasma, induktiv gekoppeltes Plasma

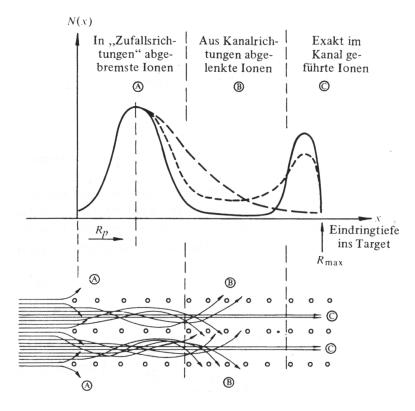

für die gewünschte Ionenart, so daß mit einer Blende die nicht benötigten Ionen herausgefiltert werden können. Am Ende seiner Bahn hat der Ionenstrahl nur einen geringen Durchmesser. Eine ionenoptische Aufweitung des Strahls wäre nicht homogen genug über einen Wafer, so daß durch waagerechten und senkrechten Feldplatten mit angelegter Wechselspannung der Strahl über eine größere Fläche geführt wird. Bei der Implantation in einen amorphen Festkörper mit zufälliger Stoßverteilung ergibt sich eine Gaußverteilung für das Tiefenprofil der implantierten Ionen, wie es auch in Abbildung 4.8 in Bereich A dargestellt ist. Ist das Target ein Einkristall, so ist jedoch sogenanntes *Channelling* möglich: Ionen, die in bestimmte kristallographische Richtungen einfallen, "sehen" die Gitteratome hintereinander und können zwischen den Gitterebenen tief in den Kristall eindringen, ohne durch zufällige Streuung abgebremst zu werden (Abb. 4.8, Bereich C). Ein <100>-Siliziumwafer z. B. darf deshalb nicht senkrecht zum Strahl eingebaut werden, sondern wird um 7° und 21° um die beiden anderen Raumachsen gekippt, um *Channelling* zu vermeiden.

Die implantierten Ionen bleiben allerdings meist auf Zwischengitterplätzen stehen – sie werden also nicht richtig in den Kristall eingebunden. Da die Ionen dann nicht zur elektrischen Leitung beitragen, müssen diese Störstellen durch eine thermische Nachbehandlung "aktiviert" werden. Auch wird der Kristall während der Implantation teilweise zerstört, weil Atome aus ihren Gitterplätzen herausgeschlagen werden. Auch für die Beseitigung dieser Gitterschäden ist die nachfolgende Temperaturbehandlung notwendig. Um unerwünschte Diffusion der eingebrachten Ionen zu vermeiden, wird diese Temperung mit RTP durchgeführt.

In der Mikroelektronik ist die Ionenimplantation ein Standardverfahren zur Erzeugung von lokalen Dotierungen. Eine Vielzahl von Elementen kann dafür verwendet werden; die Beschleunigungsenergien reichen dabei von einigen hundert eV bis zu einigen MeV, wodurch die Eindringtiefe gesteuert werden kann.

Beim I-NovaFET-Prozeß wurde das Kanalgebiet durch Implantation und Diffusion definiert (siehe 5.2.2), beim EpiNovaFET die Schicht am Topkontakt (siehe 5.3.2). Für diese Prozesse wurde ein *Axcelis 8250 Implanter* verwendet, der mit Energien von 1 keV bis  $250 \, \mathrm{keV}$  arbeitet.

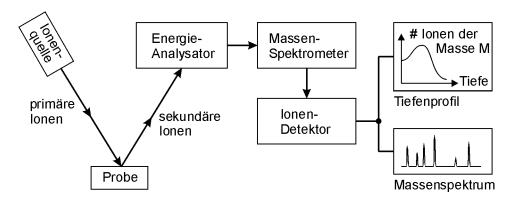

## 4.3 Secondary Ion Mass Spectrometry

Secondary ion mass spectrometry (SIMS) ist eine Analysetechnik zur Charakterisierung der Oberfläche und oberflächennahen Region von Festkörpern (und der Oberfläche einiger Flüssigkeiten). Der Beschuß mit primären Ionen bewirkt ein Sputtern an der Oberfläche, also den Abtrag der Oberflächenschichten in Form von ionisierten und neutralen Atomen oder Molekülen, die auch angeregt sein können. Die ionisierten Partikel, die Sekundär-Ionen, werden nach ihrer Masse analysiert und liefern somit bei zeitaufgelöster Messung ein Tiefenprofil der Zusammensetzung (Abb. 4.9) [25].

Abb. 4.8: Schematische Darstellung von möglichen Reichweitenprofilen für Ionen, die in einen Einkristall implantiert wurden.  $R_p$  ist die mittlere Reichweite für den amorphen Festkörper. Das Phänomen, daß Ionen tief eindringen können, wenn sie ungestreut tief in das Gitter eines Einkristalls geführt werden, nennt man "Channelling". (Bild aus [24].)

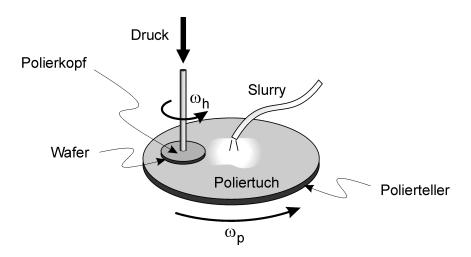

## 4.4 Chemisch-Mechanisches Polieren (CMP)

Aus verschiedenen Gründen können Planarisierungen in einem Prozeßablauf notwendig sein. Am wichtigsten ist wohl eine planarisierte Fläche für die Verdrahtung der Bauelemente integrierter Schaltungen. Ein topographisches Dielektrikum verhindert die Herstellung gleichmäßiger Leiterbahnen, da die Schärfentiefe der optischen Lithographie von nur wenigen hundert Nanometern zu Unschärfe und Linienverbreiterungen führt, wenn Niveauunterschiede zu groß sind. Mehrere Planarisierungsmethoden sind etabliert, z. B. SOG,  $Resist/Etchback^7$  oder CMP. Während die anderen Verfahren lediglich lokal planarisieren  $(1-100\,\mu\text{m})$ , ist mit CMP eine Nivellierung über den gesamten Wafer möglich.

Beim CMP wird der Wafer außermittig auf ein rotierendes Poliertuch (*Pad*) gedrückt, während eine Polierflüssigkeit, die *Slurry*, dazugegeben wird (siehe Abb. 4.10). Die *Slurry* für Oxid-CMP besteht aus einer basischen Lösung, in der kleine

<sup>&</sup>lt;sup>6</sup>Spin On Glass, eine Planarisierungsmethode, bei der ein gelöster Isolator aufgeschleudert und anschließend thermisch vernetzt wird. Durch das flüssige Auftragen wirkt es planarisierend. HSQ, der für die Nanolithographie verwendete Elektronenstrahlresist, ist ein solches SOG.

<sup>&</sup>lt;sup>7</sup>Beim Resist/Etchback-Verfahren wird zunächst SiO<sub>2</sub> konform deponiert, anschließend ein Resist aufgeschleudert. Beides wird dann mit gleicher Ätzrate zurückgeätzt.

Abb. 4.9: Prinzip der SIMS: Durch Sputtern ausgelöste Ionen werden analysiert und liefern ein Tiefenprofil der Atomkonzentration.

Schleifkörper (Abrasive) aus SiO<sub>2</sub> schweben.<sup>8</sup> Diese sind durch direkten Abrieb für die mechanische Komponente der Abtragung verantwortlich. Die chemische Komponente wird wesentlich durch das Wasser in der Slurry beeinflußt: H<sub>2</sub>O-Moleküle passivieren die Oxidoberflächen sowohl an den Abrasiven als auch auf der Wafer. Zwischen diesen Passivierungen kann es nun zu einer Reaktion kommen, bei der molekulare Bindungen entstehen, die dann Abrasive und Oxidschicht verbinden. Ohne mechanische Komponente fände hier also eine Passivierung oder sogar eine Deposition statt, so allerdings werden die Partikel und damit auch Teile aus der Oxidschicht vom Poliertuch mitgerissen. Der chemische Anteil bewirkt eine deutlich schnellere Abtragung sowie eine bessere Oberflächenstruktur der polierten Schicht. (Erläuterungen nach [26].)

Abb. 4.10: Schematische Darstellung des Chemisch-Mechanischen Polierens. Auf ein rotierendes Poliertuch (Pad), das mit der sog. "Slurry" bedeckt ist, wird der ebenfalls rotierende Wafer gepreßt. SiO<sub>2</sub>-Partikel in der Slurry bewirken mechanisches Schleifen, die chemische Komponente eine Ätzung sowie das Auflösen der Schleifprodukte.

$<sup>^8</sup>$ Die Base (meist NH<sub>4</sub>OH oder KOH) stabilisiert die Abrasive in der Flüssigkeit. Sie trägt nicht zur chemischen Komponente bei.

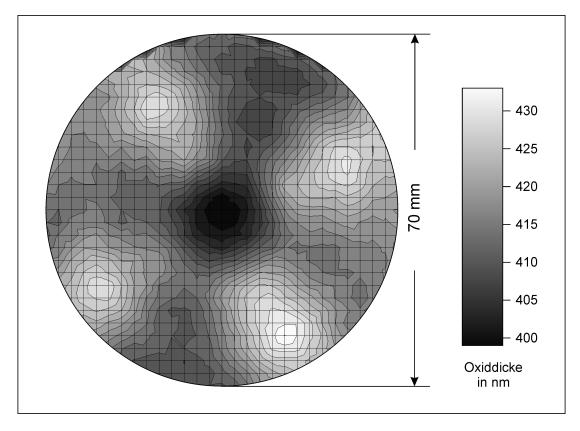

Viele Parameter gehen in das Ergebnis der Planarisierung ein: Die zu polierende Oberfläche und deren Material, die Eigenschaften des Polierpads, die Zusammensetzung der Slurry sowie diverse geometrische und kinetische Größen. Das Know-how für das äußerst genaue Polieren ist in weiten Teilen aus dem Schleifen von Linsen transferiert worden. Einige Variablen können vom Anwender optimiert werden, um ein für die Anforderungen des jeweiligen Prozesses optimales Ergebnis zu erzielen: der Druck des Polierkopfes auf das Poliertuch, die Drehzahlen von Polierkopf und -teller und natürlich die Dauer des Polierschrittes. Maße für das Polierergebnis sind die Abtragsrate und die Inhomogenität.

# Kapitel 5

## Der NovaFET-Prozeß

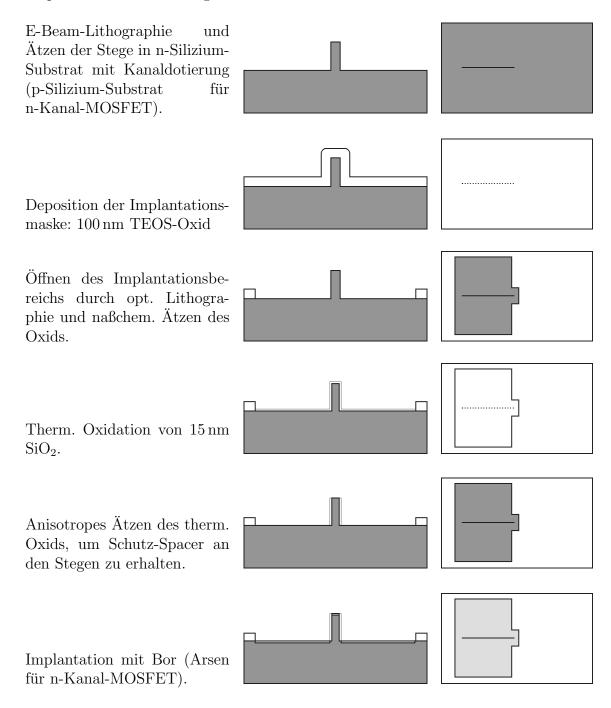

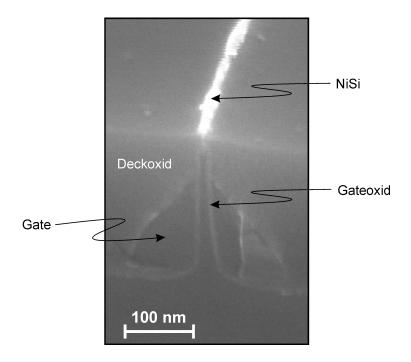

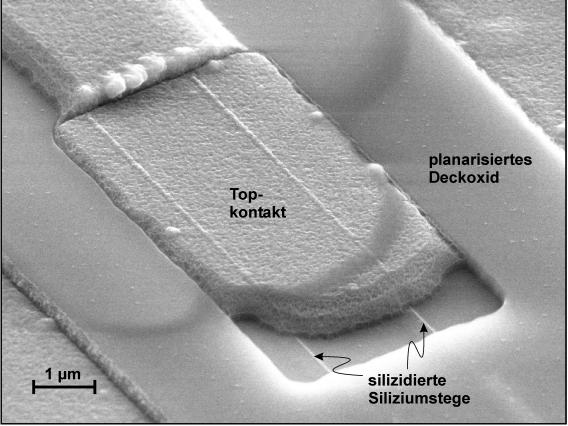

Der NovaFET ist ein vertikaler Double-Gate-MOSFET. Wie in Abbildung 5.1 ersichtlich ist, ist das Zentrum ein Siliziumsteg, der dünn genug sein muß, damit das Kanalgebiet vollständig verarmen oder – im besten Fall – sogar vollständig invertieren kann. Vertikal angeordnet in diesem Steg ist die p-n-p-Schichtabfolge für p-Kanal-Transistoren bzw. n-p-n-Folge für n-Kanal-Transistoren. Die Gatelänge ist somit die Dicke dieser mittleren Schicht, die im Gegensatz zur Stegbreite nicht lithographisch definiert werden muß, sondern durch Epitaxie oder Implantation und Diffusion eingestellt wird. Wichtige Prozesse der Herstellung sind die Definition der Stege, die Erzeugung der Schichtfolge und der Topkontakt.

Im Folgenden werden zunächst die Prozeßfolge des ursprünglichen Layouts vorgestellt und die Grenzen dieses Konzepts diskutiert. Zwei weiterentwickelte Layouts – die Implantationsvariante und der EpiNovaFET, die sich in der Herstellung der Schichtfolge unterscheiden – werden im Anschluß beschrieben und die für ihre Realisierung benötigten Schlüsselprozesse erläutert. Die Herstellung der Stege wird separat in Kapitel 6 behandelt.

Abb. 5.1: Schematischer Aufbau des NovaFETs.

## 5.1 NovaFET – ursprüngliches Layout

Bei dieser ursprünglichen Variante wird der aktive Bereich als p-n-p-Schichtfolge epitaktisch gewachsen. Der obere Kontakt wird entlang des Steges herausgeführt

und über ein Pad kontaktiert.

## 5.1.1 Prozeßfolge

Die Prozessierung des Transistors wird hier qualitativ beschrieben. Das genaue Prozeßprotokoll ist im Anhang A.1 dokumentiert.

Zuleitungen zu den silizidierten Kontakten durch opt. Lithographie, Aufdampfung von Aluminium und Lift-Off.

Abb. 5.2: Querschnitt durch den NovaFET im ursprünglichen Layout in realistischem Maßstab. Der Ausschnittsvergrößerung des aktiven Bereichs ist die REM-Aufnahme einer solchen Struktur gegenübergestellt.

#### 5.1.2 Schlüsselprozesse

#### Dotierfolge

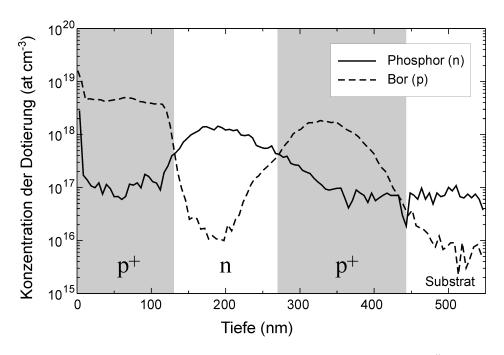

Die Schichtfolge wurde in einer LPCVD epitaktisch gewachsen. Abbildung 5.3 zeigt das SIMS-Spektrum<sup>1</sup> einer gleichzeitig gewachsenen Teststruktur, allerdings auf undotiertem Substrat. Die Dicke der mittleren, n-dotierten Schicht und somit die Kanallänge beträgt 140 nm. Die obere Schicht ist 130 nm dick. Dies bedeutet, daß die Stege mindestens 270 nm hoch sein müssen. Problematisch ist der flache untere pn-Übergang. Er ist bedingt durch den sogenannten Memory-Effekt: Beim Wachsen einer Phosphor-dotierten Schicht deponiert ein Film an den Kammerwänden und auf dem Suszeptor, aus dem beim Wachsen der folgenden Bor-dotierten Schicht Phosphor wieder in die Kammer diffundiert. Dadurch fiele die Phosphor-Konzentration in der p-Schicht kaum ab, wenn keine Gegenmaßnahmen getroffen würden. Ein Temperschritt von 1000°C für eine Stunde nach der Deposition der n-Schicht reinigt die Kammer, so daß die p-Schicht wieder mit großem Phosphor-Dotiergefälle gewachsen werden kann. Allerdings verursacht ein solcher Temperschritt beim bereits bestehenden p-n-Übergang starke Diffusion, die sich auf die elektrischen Eigenschaften des Ubergangs auswirkt: Obwohl der Transistor eigentlich symmetrisch funktionieren sollte, sind deutliche Unterschiede zwischen Source on Top und Source on Bottom sichtbar (siehe 7.1).

Eine weitere Einschränkung ist die Konzentration der Dotierung:  $3 \cdot 10^{17}$ – $2 \cdot 10^{18}$  at cm<sup>-3</sup> (untere Schicht) bzw. 4– $5 \cdot 10^{18}$  at cm<sup>-3</sup> (obere Schicht) erzeugen zu geringe Ladungsträgerkonzentrationen. Höhere Konzentrationen und schärfere Übergänge können durch Implantationen hergestellt werden. Dies wurde beim weiterentwickelten Layout realisiert.

#### Gateoxid

Ein gebräuchliches Verfahren zur Herstellung von Gateoxiden ist die Rapid thermal processing-Oxidation (RTP). Beim RTP werden einzelne Wafer kurzzeitig durch Lampen aufgeheizt; die Kammer besteht aus Quarzglas, das für die Strahlung weitgehend transparent ist und sich somit nicht im gleichen Maße erwärmt. Da die Kammer nicht auf die Wafertemperatur gebracht werden muß, sind schnellere Temperaturrampen möglich als in einem Konvektionsofen. Das Gateoxid für diesen Transistor wurde mit einem Temperschritt von 950°C für 3 min hergestellt und war 6 nm dick (Ellipsometermessung auf dem Substrat).

## Gatespacer-Ätzung

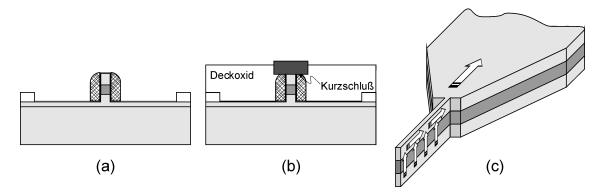

Die Ätzung des Polysiliziums, um die Gatespacer zu erhalten, sollte im optimalen Fall eine Überätzung beinhalten, damit das Gate nicht mit der oberen Schicht parasitäre Kapazitäten bildet. Dafür ist jedoch ein Ätzprozeß mit hoher Selektivität zwischen Silizium und SiO<sub>2</sub> notwendig, da ansonsten sowohl die obere Zuleitung als auch die Substratzuleitung zerstört werden (Abb. 5.4). Bei der Herstellung des No-

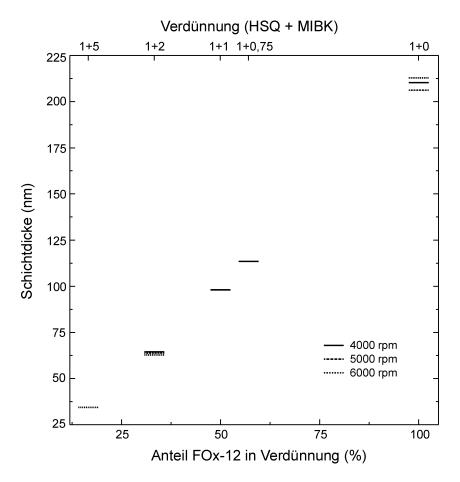

<sup>&</sup>lt;sup>1</sup>, Secondary ion mass spectrometry", siehe 4.3.