FACULTY OF INFORMATION TECHNOLOGY AND ELECTRICAL ENGINEERING

## **Tuomas Tuokkola**

# LATENCY AND ACCURACY OPTIMIZED MOBILE FACE DETECTION

Master's Thesis

Degree Programme in Computer Science and Engineering

December 2020

Tuokkola T. (2020) Latency and Accuracy Optimized Mobile Face Detection. University of Oulu, Degree Programme in Computer Science and Engineering, 69 p.

#### **ABSTRACT**

Face detection is a preprocessing step in many computer vision applications. Important factors are accuracy, inference duration, and energy efficiency of the detection framework. Computationally light detectors that execute in real-time are a requirement for many application areas, such as face tracking and recognition. Typical operating platforms in everyday use are smartphones and embedded devices, which have limited computation capacity.

The capability of face detectors is comparable to the ability of a human in easy detection tasks. When the conditions change, the challenges become different. Current challenges in face detection include atypically posed and tiny faces. Partially occluded faces and dim or bright environments pose challenges for detection systems. State-of-the-art performance in face detection research employs deep learning methods called neural networks, which loosely imitate the mammalian brain system. The most relevant technologies are convolutional neural networks, which are designed for local feature description.

In this thesis, the main computational optimization approach is neural network quantization. The network models were delegated to digital signal processors and graphics processing units. Quantization was shown to reduce the latency of computation substantially. The most energy-efficient inference was achieved through digital signal processor delegation. Multithreading was used for inference acceleration. It reduced the amount of energy consumption per algorithm run.

Keywords: energy-efficiency, face detection, smartphones, real-time, quantization, deep learning, convolutional neural networks, RetinaFace

Tuokkola T. (2020) Latenssi- ja tarkkuusoptimoitu kasvontunnistus mobiililaitteilla. Oulun yliopisto, Tietotekniikan tutkinto-ohjelma, 69 s.

### TIIVISTELMÄ

Kasvojen ilmaisu on esikäsittelyvaihe monelle konenäön sovellukselle. Tärkeitä kasvoilmaisimen ominaisuuksia ovat tarkkuus, energiatehokkuus ja suoritusnopeus. Monet sovellukset vaativat laskennallisesti kevyitä ilmaisimia, jotka toimivat reaaliajassa. Esimerkkejä sovelluksista ovat kasvojen seurantaja tunnistusjärjestelmät. Yleisiä käyttöalustoja ovat älypuhelimet ja sulautetut järjestelmät, joiden laskentakapasiteetti on rajallinen.

Kasvonilmaisimien tarkkuus vastaa ihmisen kykyä helpoissa ilmaisuissa. Nykyiset ongelmat kasvojen ilmaisussa liittyvät epätyypillisiin asentoihin ja erityisen pieniin kasvokokoihin. Myös kasvojen osittainen peittyminen, ja pimeät ja kirkkaat ympäristöt, vaikeuttavat ilmaisua. Neuroverkkoja käytetään tekoälyjärjestelmissä, joiden lähtökohtana on ollut mallintaa nisäkkäiden aivojen toimintaa. Konvoluutiopohjaiset neuroverkot ovat erikoistuneet paikallisten piirteiden analysointiin.

Tässä opinnäytetyössä käytetty laskennallisen optimoinnin menetelmä on neuroverkkojen kvantisointi. Neuroverkkojen ajo delegoitiin digitaalisille signaalinkäsittely- ja grafiikkasuorittimille. Kvantisoinnin osoitettiin vähentävän laskenta-aikaa huomattavasti ja suurin energiatehokkuus saavutettiin digitaalisen signaaliprosessorin avulla. Suoritusnopeutta lisättiin monisäikeistyksellä, jonka havaittiin vähentävän energiankulutusta.

Avainsanat: energiatehokkuus, kasvoilmaisu, älylaitteet, reaaliaikainen, kvantisointi, syväoppiminen, konvoluutioneuroverkot, RetinaFace

## TABLE OF CONTENTS

| ABSTRACT                          |                                          |                       |                                    |          |  |  |  |  |

|-----------------------------------|------------------------------------------|-----------------------|------------------------------------|----------|--|--|--|--|

| TIIVISTELMÄ                       |                                          |                       |                                    |          |  |  |  |  |

| TABLE OF CONTENTS                 |                                          |                       |                                    |          |  |  |  |  |

| FOREWORD                          |                                          |                       |                                    |          |  |  |  |  |

| LIST OF ABBREVIATIONS AND SYMBOLS |                                          |                       |                                    |          |  |  |  |  |

| 1.                                | INTRODUCTION                             |                       |                                    |          |  |  |  |  |

|                                   | 1.1. Scope of the Thesis                 |                       |                                    |          |  |  |  |  |

| 2.                                | 2. FACE DETECTION                        |                       |                                    |          |  |  |  |  |

|                                   | 2.1. Hand-Crafted Features Based Methods |                       |                                    |          |  |  |  |  |

|                                   |                                          | 2.1.1.                | Viola-Jones                        | 11       |  |  |  |  |

|                                   |                                          |                       | LBP Based Face Detection.          |          |  |  |  |  |

|                                   |                                          |                       | Feature Learning in Face Detection |          |  |  |  |  |

|                                   | 2.2.                                     | Feedforward Algorithm |                                    |          |  |  |  |  |

|                                   |                                          | 2.2.1.                |                                    |          |  |  |  |  |

|                                   |                                          |                       | Convolutions                       |          |  |  |  |  |

|                                   | 2.3.                                     |                       | Network Optimization               |          |  |  |  |  |

|                                   |                                          |                       | Quantization                       |          |  |  |  |  |

|                                   |                                          |                       | Folding                            |          |  |  |  |  |

|                                   |                                          | 2.3.3.                | <del>-</del>                       |          |  |  |  |  |

|                                   |                                          | 2.3.4.                | Clustering                         |          |  |  |  |  |

|                                   | 2.4.                                     |                       | ary                                |          |  |  |  |  |

| 3.                                | NEU                                      |                       | OMPUTING ON EMBEDDED PLATFORMS     |          |  |  |  |  |

|                                   |                                          |                       | er Representations                 |          |  |  |  |  |

|                                   |                                          |                       | Number Formats for Neural Networks |          |  |  |  |  |

|                                   | 3.2.                                     |                       | ıting Concurrency                  |          |  |  |  |  |

|                                   |                                          | 3.2.1.                |                                    |          |  |  |  |  |

|                                   |                                          | 3.2.2.                | Data Order                         |          |  |  |  |  |

|                                   |                                          | 3.2.3.                |                                    |          |  |  |  |  |

|                                   |                                          | 3.2.4.                |                                    |          |  |  |  |  |

|                                   |                                          |                       | ution                              |          |  |  |  |  |

|                                   |                                          |                       | Graphics Processing Units          |          |  |  |  |  |

|                                   |                                          |                       | Digital Signal Processors          |          |  |  |  |  |

|                                   |                                          | 3.3.3.                | Field Programmable Gate Arrays     |          |  |  |  |  |

|                                   |                                          | 3.3.4.                | Systolic Arrays                    |          |  |  |  |  |

|                                   |                                          | 3.3.5.                |                                    |          |  |  |  |  |

|                                   | 3.4.                                     | Summa                 | ary                                |          |  |  |  |  |

| 4.                                |                                          |                       | ECTION IMPLEMENTATION              |          |  |  |  |  |

|                                   | 4.1.                                     |                       | Fill                               | 32       |  |  |  |  |

|                                   | 4.2.                                     | •                     |                                    |          |  |  |  |  |

|                                   | 4.3.                                     |                       | Outputs                            | 32<br>33 |  |  |  |  |

|                                   |                                          | 4.3.1.                |                                    | 33       |  |  |  |  |

|                                   |                                          | 4.3.2.                |                                    | 33       |  |  |  |  |

|                                   |                                          |                       | Anchors                            | 3/       |  |  |  |  |

|     | 4.4.                       | Predictions                             |                                            |    |  |  |  |  |

|-----|----------------------------|-----------------------------------------|--------------------------------------------|----|--|--|--|--|

|     |                            | 4.4.1.                                  | Intersect over Union                       | 35 |  |  |  |  |

|     |                            | 4.4.2.                                  | Non-Maximum Suppression                    | 36 |  |  |  |  |

|     | 4.5.                       | Implementation Toolkit                  |                                            |    |  |  |  |  |

|     |                            | 4.5.1.                                  | TensorFlow                                 | 37 |  |  |  |  |

|     |                            | 4.5.2.                                  | TensorFlow Lite                            | 37 |  |  |  |  |

|     |                            | 4.5.3.                                  | C++                                        | 38 |  |  |  |  |

|     |                            |                                         | Calibration                                | 38 |  |  |  |  |

| 5.  | FAC                        | FACE DETECTION EXPERIMENTS              |                                            |    |  |  |  |  |

|     | 5.1.                       | .1. Optimal Threading                   |                                            |    |  |  |  |  |

|     | 5.2.                       | Accura                                  | ncy Benchmarking                           | 42 |  |  |  |  |

|     | 5.3.                       | Detecti                                 | ion Ranges                                 | 47 |  |  |  |  |

|     | 5.4.                       | nce Benchmarking                        | 49                                         |    |  |  |  |  |

| 6.  | POWER DISSIPATION ANALYSIS |                                         |                                            |    |  |  |  |  |

|     | 6.1.                       | Measurement Environment Setup           |                                            |    |  |  |  |  |

|     |                            | 6.1.1.                                  | CPU Measurement Visualization              | 50 |  |  |  |  |

|     |                            | 6.1.2.                                  | GPU and DSP Delegation Visualization       | 51 |  |  |  |  |

|     | 6.2.                       | Quantitative Power Dissipation Analysis |                                            |    |  |  |  |  |

|     |                            | 6.2.1.                                  | Initial Setup for Measurements             | 51 |  |  |  |  |

|     |                            | 6.2.2.                                  | Energy Consumption Tests                   | 51 |  |  |  |  |

|     |                            | 6.2.3.                                  | Estimated Power Consumption on Smartphones | 52 |  |  |  |  |

| 7.  | DISCUSSION                 |                                         |                                            |    |  |  |  |  |

|     | 7.1.                       | Initialization Pipelining               |                                            |    |  |  |  |  |

|     | 7.2.                       | About                                   | Evaluation                                 | 53 |  |  |  |  |

|     | 7.3.                       | New D                                   | etection Technologies                      | 53 |  |  |  |  |

| 8.  | CON                        | ONCLUSION                               |                                            |    |  |  |  |  |

| 9.  | REFERENCES                 |                                         |                                            |    |  |  |  |  |

| 10. | 0. APPENDICES 60           |                                         |                                            |    |  |  |  |  |

|     |                            |                                         |                                            |    |  |  |  |  |

## **FOREWORD**

I want to thank everyone at Visidon for their good team spirit and emphasis on relaxed but efficient working culture. I want to give my greatest gratitude to Henri Nykänen, Olli Silven, Jari Hannuksela, Jukka Holappa and Tuomas Holmberg.

Henri Nykänen was my technical supervisor at the company and without Henri's original work and help I would have been, to large extent, lost in time. Olli Silven was my thesis supervisor at University and helped me with the scoping of the thesis and in theoretical writing. Jari Hannuksela was the second examiner of the thesis and helped with the power dissipation test setup. Jukka Holappa and Tuomas Holmberg were my roommates in the old office (from January of 2020 to May of 2020) and helped me to grow professionally. Sometimes with some implementation tips and in-depth questions about work, but sometimes also of life. Special thanks to Tuomas Holmberg for helping me with the challenges with the LaTeX-template of this thesis.

I want to show my gratitude to everyone who has contributed to this thesis through writing clear and unambiguous blog posts and books on related subjects and to everyone who has been mentioned in these blog posts and books as contributors of any sort.

Oulu, December 8th, 2020

Tuomas Tuokkola

## LIST OF ABBREVIATIONS AND SYMBOLS

ReLU rectified linear unit

CNN convolutional neural network

PTQ post-training quantization

DSP digital signal processor

TPU tensor processing unit

MAC multiply accumulate operation

FP floating point

FP-16 16-bit floating point FP-32 32-bit floating point

FX fixed point

FX-8 8-bit fixed point

MM matrix multiplication

FFT fast fourier transform

SIMT single instruction, multiple threads

MIMT multiple instructions, multiple threads

CPU central processing unit GPU graphics processing unit IoU intersect over union

NMS non-maximum suppression QVGA quarter video graphics array

VGA video graphics array FHD full high definition

4K DCI 4K digital cinema initiatives

PR precision-recall

FPR false positive rate

FNR false negative rate

DC direct current

T1 single thread

TB balanced threading

TT maximum throughput threading

$\sigma^2$  batch variance  $\mu$  batch mean

$\gamma$  standard deviation parameter

$\beta$  mean parameter

$\begin{array}{ll} \epsilon & \text{epsilon} \\ z \text{ or } X_z & \text{zero point} \\ s \text{ or } X_s & \text{scaling factor} \\ q \text{ or } X_q & \text{quantized value} \end{array}$

$egin{array}{ll} T & ext{tensor} \ M & ext{matrix} \ oldsymbol{v} & ext{vector} \ s & ext{scalar} \ \end{array}$

#### 1. INTRODUCTION

Computer vision is a field of artificial intelligence in which systems are designed to interpret the visual world. Due to the importance of vision, the human body has developed a vast system for processing and interpreting visual signals that the research tries to imitate. [1]

With early face detection algorithms, slight differences in the orientation of a head could easily affect the prediction outcome. Another goal was low latency. For some real-world applications the processing should be done in real-time. [2]

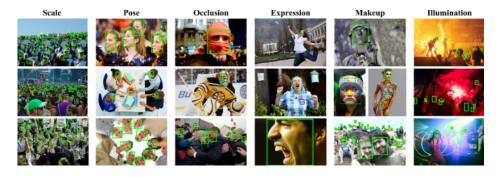

Face detection deals with a variety of challenges. Datasets are used for categorization of known problem cases. Figure 1 represents core challenges in WIDER Face dataset. [3]

Figure 1. Datasets contain various challenges for face detection algorithms.

Decades ago computers were lacking the computational resources needed for processing useful artificial neural networks. Although some systems were introduced, not many were effectively put in use. Development of hardware efficiency and power output in coming years changed the situation.

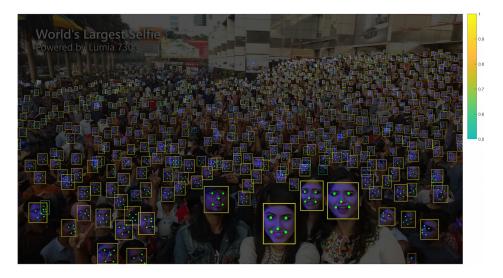

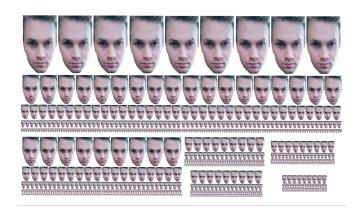

Multi-scale detection is one of many active object detection research areas. Finding small faces in large images has been a complex issue in face detection research. An example of a challenging multi-scale detection situation is presented in Figure 2. [4]

Figure 2. World's largest selfie by Lumia 730 is a challenging face detection scenario.

The use of smartphones introduced new challenges for face detection algorithm design. Energy efficiency became important, while neural computing-based solutions require traditionally vast amounts of computation. The majority of neural computation is multiply-accumulate operations. The needed operations are simple but the problem is in the quantity. Optimization techniques designed for dealing with this computation bottleneck have branched in many directions. [2]

Common optimization solutions for neural computing can be roughly categorized followingly:

#### • Speeding-up the detection pipeline

Speeding-up the detection pipeline is achieved by implementing multiply-accumulate computation on novel specialized hardware. The most common delegation hardware are graphics processing units (GPUs) and digital signal processors (DSPs). Specialized hardware is more efficient in terms of energy usage.

#### • Numerical precision reduction

Optimization methods introduce a level of error to classification accuracy. The precision reduction is called quantization. The predictive power of a neural network is based on the idea of receptive fields, which capture both large- and small-scale structures. Due to a huge amount of variables, most networks are tolerant of error.

#### Algorithm innovations

Lightweight deep learning methods are used for energy-efficient face detection. Mobile deep learning algorithms are the optimal choice for a trade-off in terms of prediction accuracy and detection latency.

#### 1.1. Scope of the Thesis

In Chapter 2 traditional face detection systems are considered. Main mechanisms and elements of neural computing are covered and the most relevant neural network optimization techniques are elaborated. In Chapter 3 the fundamentals of computer arithmetics and computing models are described. The architectures are considered in neural computing context. In Chapter 4 a face detection implementation is presented. In Chapter 5 a set of measurements are conducted and metrics are introduced for evaluation purposes. Chapter 6 discusses topics that are relevant for the future of this work.

#### 2. FACE DETECTION

Face detection is a relevant phase in various modern problems involving person verification, identification, and expression analysis. The first stage of a face detection system is feature extraction, where representations of features are acquired. Extracted feature representations are used for detection classification.

#### 2.1. Hand-Crafted Features Based Methods

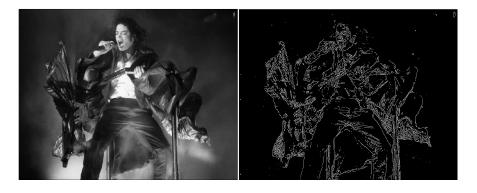

Face detection is traditionally based on using hand-crafted features. The most common feature forms are edges and corners. Features are used for finding proportionally distinct intensity changes within image presentation [2]. For instance, Harris corner detector is an algorithm where edge and corner feature representation was combined into a single detector [5]. Early detector pipelines usually consisted of noise reduction, feature calculation, thresholding, and normalization algorithms [6]. Figure 3 visualizes the features used by a Canny edge detector. Image taken from [3].

Figure 3. Example of an edge detection algorithm.

Feature variance is relevant challenge in object detection systems. Scale-invariant features (SIFT) is a traditional algorithm for scale and variance tolerant feature extraction. Scale, translation, and rotation invariant features are expensive to calculate due to image information richness. [7]

For latency minimization speeded-up robust features (SURF) algorithm was developed for efficient GPU execution. Both SURF and SIFT are based on local information, and on features calculated from gradients in an image [8]. Another traditionally popular algorithm is histogram of oriented gradients (HOG), the flow of which is displayed in Figure 4 [9].

Figure 4. HOG detector workflow.

The basic face detection methods can be categorized into template-matching and part-based model schemes. Template-matching methods introduced a face template, which can contain dimensions, contour, and facial elements. Elements can contain

knowledge about relationships present in a face or a set of facial features. This approach is simple to implement, but performs poorly compared to other face detection algorithms. [10]

The idea in part based models is that each object consists of one global base filter and several part models, for example, a head and eyes. Usually the first model, the body, is defined by a coarse template. The model defines the placement space for its child part models, which are usually inspected at a higher resolution. Both body and child filters are scored based on some evaluation rules. These rules have been extended to include multiple methods during the years and a large portion of algorithmic success was due to these advancements. [11]

Image channel features have played a huge part in face detection over the years. Image channel methods are used for non-linear and linear face detection, where the most common features are extracted from color channels [12]. There are also many non-linear channels, and the most popular use of non-linear channels were adapted with a Canny edge detector [6] by displaying edges and gradient magnitude (edge strength) [2].

#### 2.1.1. Viola-Jones

Among the first robust and real-time capable face detection algorithm is the Viola-Jones (VJ) face detector. One of the main contributions was the integral image representation method for accelerated feature evaluation. It is a method for narrowing the total number of needed haar-like features without losing quality from the prediction.

VJ detector used several weak learners for forming a strong classifier for a classification task. A weak learner is a learner that does not hold enough information for a detection alone.

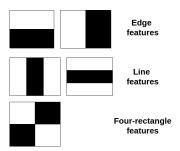

In Figure 5 haar features are visualized. The features are obtained by subtracting the sum of pixels under the white rectangle from pixels under the black rectangle. This way the detector gains information from relevant relationships for a face detection. [13]

Figure 5. Example of a haar-feature set.

Vast number of predictions in a detection are negative. Detection cascade was developed for dealing with this challenge. The cascading technique increases the performance of a detector significantly by focusing attention on promising image regions. In the VJ detector, a variant of adaptive boosting (Adaboost) is used for

selecting a core set of features and boosting the classification performance of a system. [14]

#### 2.1.2. LBP Based Face Detection

Local binary pattern (LBP) methods are originally general texture descriptor methods. The methods were extended to face detection domain as a rotation invariant and lightweight techniques. LBP considers compositions of micro-patterns as global descriptors and the method is commonly applied on a grey-scale image. LBP operator is calculated using a pixel and its neighbourhoods, originally an eight-pixel neighbourhood method was used. In this method a binary collection of pixels is obtained by starting binary from top-left corner and advancing in clockwise direction. [15]

LBP for face detection relies on extended usage of neighbourhoods, some variations are (8,1) and (16,2) neighbourhood sizes. Later the operator was extended to uniform patterns, which is an pattern, where transition between bits is at most two. [15]

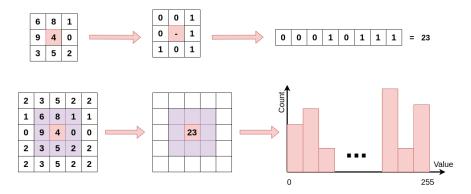

The first step in using LBP for face detection is calculating feature histograms. Figure 6 represents LBP histogram generation stages, in which extracted binary values form histograms of features.

Figure 6. LBP feature generation stages.

Some more recent advances in LBP usage have been adaptations from other traditional detection paradigms: usage of other classification techniques in pre- or post-processing, and efficient usage of a cascade of classifiers. Some applied classification techniques are support vector machine (SVM) and eigenface (PCA) methods. Facial representation is considered as small non-overlapping regions used to form feature histograms for the prediction. [16]

LBP is a lightweight and fast algorithm in terms of feature calculation. However, LBP based features cannot be learned by neural computing.

#### 2.1.3. Feature Learning in Face Detection

Feature learning methods capture efficient feature representations. Two main categories exist: supervised and unsupervised learning. In supervised learning we

have data and labels. The goal is to adjust the parameters so the system finds how the data and labels are correlated based on a loss function. Unsupervised learning works without the labels. [17]

In this thesis we apply supervised learning. Its phases are

#### Training

The learning goal is reached through an iterative training process. Model weights are either tuned or learned in this process.

#### Testing

In testing phase the testing data is used for model evaluation during training. Testing can be used as an evaluation tool for observing the loss function.

#### Validation

The validation data is used for the final validation of the model.

Datasets that consist of data, labels, and noise, are used for feature learning. In a supervised learning environment labels can be used for building a meaningful loss function for the trained network. The network is meant to learn weight parameters from the training data. Testing and validation data sets are often smaller, and are used for determining if the loss converges. The network has not used the testing and validation data for training, so the classification situations are new for the network. [18]

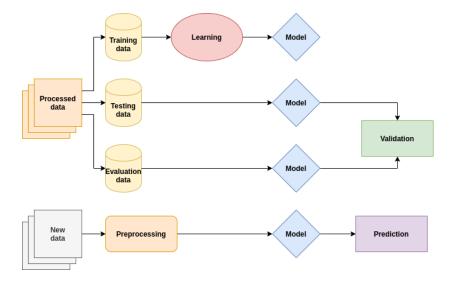

In Figure 7 the design flow of a supervised learning system is depicted.

Figure 7. Supervised learning stages.

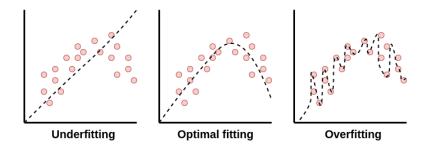

In training phase the prediction ability of a model is created. The challenges in feature learning are over- and underfitting. Overfitting means that the model follows the details of the data too closely thus being unable to adapt to new situations. Underfitting means that the model has not been able to capture patterns present in the data. [19]

In Figure 8 model fitting challenges are visualized. The system needs to be able to find essential patterns in the data for optimal detection capability. [18]

Figure 8. Challenges present in fitting of a Machine Learning model.

Neural networks are usually trained with backpropagation algorithm. Feedforward algorithm is used for predicting. [17]

#### 2.2. Feedforward Algorithm

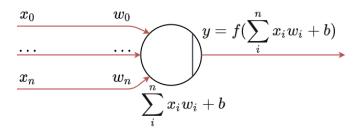

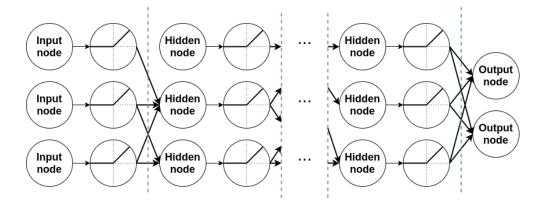

In feedforward, models the information flow is directed from input layers through the hidden layers to the output layers. Layers consist of neurons that get their inputs from the output signals of the preceding layer, forming a chain of processes. The output layer of the network constitutes the overall response to the activation pattern fed by the input layer [20]. A neuron is visualized in Figure 9, where a node consist of n connections, input values  $x = \{x_0, \ldots, x_n\}$ , synapse weights  $w = \{w_0, \ldots, w_n\}$ , a bias b, and an activation function f. Figure is adapted from [17].

Figure 9. Early prototype of a neuron.

Feedforward algorithm is the backbone of neural computing. In Figure 10 a feedforward system is presented, consisting of input, hidden, output, and activation nodes, which define what connections are active during neural computing.

Activation functions enable networks to learn complex data. Nonlinear activation function rectified linear unit (ReLU) and its variations are often used in the state-of-the-art (SOTA) classification networks. The algorithm of ReLU is given in Equation (1). ReLU introduces non-linearity by mapping negative values as zeros. In other cases input values remain intact. [21]

$$f(x) = max(x,0) \tag{1}$$

Due to its simplicity ReLU has small computation cost, and negative values do not form connections. [22]

Figure 10. Feedforward algorithm is the backbone of a neural network.

Convolutional neural networks (CNNs) are used for SOTA face detection feature calculation. CNNs employ multistage texture extraction. Feature learning can be accelerated by use of preprocessing techniques, such as batch normalizations. [23]

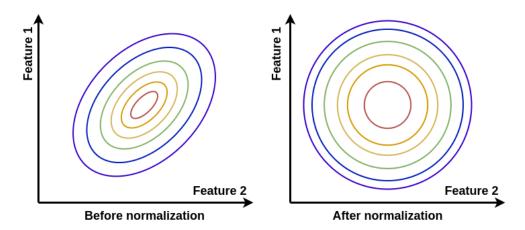

## 2.2.1. Preprocessing

Feature scaling enables faster and stabler learning. As we progress deeper in the network, the input parameters for each layer shift in the distribution of inputs, slowing down the optimization. This is known as internal covariate shift. [23]

Parameter whitening has been used for accelerating learning. In whitening the mean and variance of each feature is normalized to be the same. Figure 11 illustrates the principles: The range of features is transformed into the same scale. [23]

Figure 11. Features are normalized into the same scale.

Batch normalization uses four parameters in each batch normalization layer. Batch variance  $(\sigma^2)$  and batch mean  $(\mu)$  are used for shifting and scaling of variables. Other parameters are standard deviation  $(\gamma)$  and mean  $(\beta)$  parameters, which are learned during the normalization process. [23]

Parameter learning in a batch normalization is based on Equations (2) and (3), where  $b = \{x_1, \dots, x_m\}$  is the input batch.

$$\mu = \frac{1}{m} \sum_{i=1}^{m} x_i \tag{2}$$

$$\sigma^2 = \frac{1}{m} \sum_{i=1}^{m} (x_i - \mu)^2 \tag{3}$$

Each normalization layer applies Equation (4), where x is an input element of the layer, x' is the normalized element value, and  $\epsilon$  is a small constant for numerical stability. [23]

$$x' = \frac{x - \mu}{\sqrt{\sigma^2 + \epsilon}} \tag{4}$$

With these equations, the process enables more independent learning of parameters for each layer.  $\sigma$  and  $\mu$  are sometimes randomly initialized, as previous optimizations might no longer be optimal: an optimizer might unlearn these normalizations if it is a convenient way to minimize the loss function.

$\gamma$  and  $\beta$  parameters in a batch normalization transform change weights per activation in Equation (5), where x is the input to a layer and x' is the normalized value.  $\gamma$  and  $\beta$  are used for batch scaling and shifting. [23]

$$x' = \gamma x + \beta \tag{5}$$

Batch normalization reduces internal covariate shift and the dependence of gradients on the scale of parameters, regularizing the model and normalizing layer level responses [23]. This is an important aspect in quantization, which saves energy, improves computing speed, and enables higher learning rates. [24] For inference, the network needs to do the same normalizations as during training. These normalizations can be calculated offline by folding [25].

#### 2.2.2. Convolutions

Let's presume we have an input signal x(n), an impulse response h(n) and an output signal y(n). Equation (6) is a convolutional system, where  $\circledast$  is the convolution operator. [26]

$$y(n) = x(n) \circledast h(n) \tag{6}$$

In CNNs convolutional layer computations essentially extract features. In Equation (7) the output vector (y) is equated, where W is the weight matrix, x is the input vector, and b is the bias vector.

$$y = Wx + b \tag{7}$$

$\boldsymbol{W}$  is represented as a multi-dimensional array and  $\boldsymbol{b}$  is defined as an vector in Equation (8).

$$\mathbf{W} = \begin{bmatrix} w_{0,0} & w_{0,1} & \dots & w_{0,n} \\ w_{1,0} & w_{1,1} & \dots & w_{1,n} \\ \dots & \dots & \dots & \dots \\ w_{m,0} & w_{m,1} & \dots & w_{m,n} \end{bmatrix} \mathbf{b} = \begin{bmatrix} b_0 \\ b_1 \\ \dots \\ b_m \end{bmatrix}$$

(8)

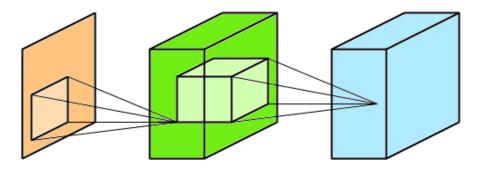

Convolutional layers are fundamentally built on local receptive fields, shared weights, and spatial sub-sampling. Local receptive fields refer to design architecture, where convolutions are connected to their input layer. Input image can contain millions of pixels, but we can detect meaningful features, that only inhabit a region of dozens of pixels, as the convolution kernels are small.

The execution time depends on the kernel size [26]. Figure 12 visualizes convolutional layers and the kernel computation flow from layer to layer.

Figure 12. Convolutional layers form a chain of operations in neural network.

#### 2.3. Neural Network Optimization

Neural computing acceleration needs to consider operator throughput, memory access compression, precision arithmetic, bitwidth, and quantization. The aim is to accelerate inference, to reduce model size, and to achieve better energy efficiency. The problem with most methods is the inability to exploit sparsity or value homogeneity. [25]

It is known that classification neural networks are robust under heavy quantization noise, and 8-bit, or even 4-bit precision may suffice [25]. Among the optimization techniques are weight clustering, quantization aware training (QAT), post-training quantization (PTQ) and pruning. The most effective optimization method is QAT, but it is the hardest to deploy. PTQ is relevant technique in many cases, as the accuracy difference between QAT and PTQ is usually marginal [27].

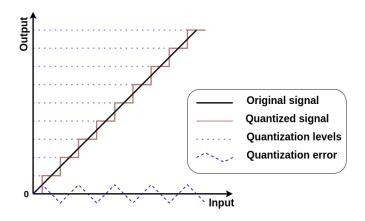

#### 2.3.1. Quantization

In this thesis quantization means mapping 32-bit floating point models into lower precision and numeric range. Important attributes in quantization are dynamic range and precision. Dynamic range refers to the range of variable space and precision is the number of levels in range [25]. Range and precision impact the amount of quantization error.

Quantization of a signal is visualized in Figure 13, where quantization error is the rounding error between the original and quantized signals, and the number of quantization levels is defined by the value range of original signal.

Figure 13. Visualization of signal quantization.

Most common quantization approaches in convolutional neural computing are range- and clipping-based approaches. Range-based quantization approaches use the full variable range. Clipping-based approaches use a static or a learned range that results in limiting the maximum and minimum values. Common quantization methods are symmetric and asymmetric methods. [28]

Typically three variables are used in quantization:

#### Common exponent

The exponent is often called zero-point. It is the offset of values, and is a neural computing specific constraint. For many operations we need the real value of 0 to be exactly representable in a quantized form, as it is an optimality constraint. [24]

#### Scaling factor

The scaling factor is used to adapt weights of tensors to a dynamic range. Scaling factor is usually defined per-channel or per-layer. [24]

#### Minimum and maximum activation ranges

The range functions are applied to the variable before and after to-be quantized layers and they map the activation range of each layer. [24]

Quantization of a scalar is defined in Equation (9), where  $X_{ij}$  is the input element,  $X_{q(ij)}$  is the quantized value of x, z is the zero-point, and s is the scaling factor. [24]

$$\boldsymbol{X}_{ij} = (\boldsymbol{X}_{q(ij)} - z) * s \tag{9}$$

Digital signal processors (DSPs) and tensor processing units (TPUs) used in neural computing rely on quantized inputs. For eliminating as much floating point arithmetic as possible, the matrix multiplications (MMs) must be quantized.

Computation using a low precision general matrix multiplication (GEMMLOWP) algorithm is in Equation (10), where notations  $\mathbf{R}_{q(ij)}$  are the quantized values,  $R_z$  the zero-point, and  $R_s$  the scale of the result, and  $\mathbf{LHS}_{q(ij)}$  and  $\mathbf{RHS}_{q(ij)}$  are quantized left-hand and right-hand side matrices. [29]

$$\mathbf{R}_{q(ij)} = R_z + \frac{lhs_s * rhs_s}{R_s} * ((\mathbf{LHS}_{q(ij)} - lhs_z) * (\mathbf{RHS}_{q(ij)} - rhs_z))$$

(10)

The innermost part of an accumulation is called the kernel loop. In neural networks it is the most computationally intensive part. Elimination of as many variables as possible from the kernel loop reduces the computation cost of MMs. Neural network inference is often measured in terms of multiply accumulate operations (MACs). Accumulator size is minimized as computational cost significantly increases along the size of the accumulator. [29]

Optimal accumulation  $A_q$  for a quantized general matrix multiplication is defined in Equation (11).

$$\boldsymbol{A}_{q(ij)} = \boldsymbol{L}\boldsymbol{H}\boldsymbol{S}_{q(ij)} * \boldsymbol{R}\boldsymbol{H}\boldsymbol{S}_{q(ij)}$$

(11)

Post-training quantization is a common technique used to optimize model inference. In parameter abundant networks there are outliers in learned weights, so losing information on these variables does not change the model behaviour fundamentally [24]. Smaller models are different as their lightweight architecture provides smaller representation capacity [30].

#### 2.3.2. *Folding*

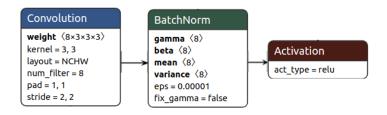

CNN computation is a repetitive pipeline, which consists of calculation, normalization and activation of features. Figure 14 visualizes the most repetitive neural computation scheme, a block, which consists of convolution, batch normalization and activation layers.

Figure 14. Convolutional, batch normalization and activation layers.

Folding is a technique where offline calculable weights are fused to weights of another layer. This decreases the number of operations per inference. Usual way for folding is fusing together convolution, normalization and activation layers. [24]

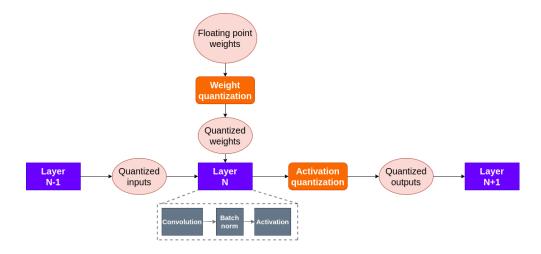

Folding process is visualized in Figure 15 where input, convolution, and activation weights are quantized. Quantization nodes are used for quantization, and they contain information about the minimum and maximum activation ranges of the layer. [24]

Figure 15. Folding of convolution, normalization and activation layers.

The convolution layers consist of weights (W) and biases (b) [24]. Folding of a weight w, which is one of the elements defined in Equation (8), is presented in Equation (12), where  $\gamma$  is batch standard deviation parameter,  $\sigma^2$  a variance parameter and  $\epsilon$  a small constant for numerical stability. [23]

$$w_{fold} = \frac{\gamma * w}{\sqrt{\sigma^2 + \epsilon}} \tag{12}$$

Folding of bias element b, which is defined in Equation (8), is presented in Equation (13), where  $\beta$  is the mean parameter of batch normalization. [23]

$$b_{fold} = \frac{\gamma * (b - \mu)}{\sqrt{\sigma^2 + \epsilon}} + \beta \tag{13}$$

Equations (12) and (13) are combined in Equation (14). With this folding technique both weights and biases of a convolutional layer can be folded. [23]

$$x_{fold} = \frac{\gamma * w(b - \mu)}{\sqrt{\sigma_w^2 + \epsilon}} + \beta \tag{14}$$

An example of the quantization and folding of a block is presented in Appendix 1.

#### 2.3.3. Pruning

Pruning is a network compression technique. Pruning is based on the fact that model has many weights that hold little to no information for the detection [31]. Network sparsity is the goal of pruning. Layer sparsity is defined in Equation (15).

$$|\mathbf{X}_{p}| = \begin{bmatrix} |x_{0,0}^{0}| & |x_{0,1}^{0}| & \dots & |x_{0,n}^{0}| \\ |x_{1,0}^{0}| & |x_{1,1}^{0}| & \dots & |x_{1,n}^{0}| \\ \vdots & \vdots & \ddots & \vdots \\ |x_{m,0}^{0}| & |x_{m,1}^{0}| & \dots & |x_{m,n}^{0}| \end{bmatrix}$$

(15)

Sparsity can be conducted on multiple levels: on fine-grained-, vector-, kernel-, and filter-level. Better results can be achieved by using smoother pruning algorithms [32], but there are no general guidelines what is the breaking point of a model [33]. In Equation (16) calculation of the zero-element count of a layer takes place.

$$x = \sum_{i=0}^{n} \sum_{j=0}^{m} |x_{ij}^{0}| \tag{16}$$

Neurons with no connections can be safely pruned in any pruning algorithm. The most straightforward pruning technique is one-shot pruning, where algorithm randomly deletes data based on threshold. The more advanced pruning includes training-aware pruning, where a training optimizer is used for fine-tuning. The idea is to learn which weights are the least important. [33]

Traditional neural architectures are error tolerant by design, but mobile neural architectures are not as error tolerant due to smaller parameter count [31]. However, for most classification networks, pruning of later layers should prove useful as long as the most critical layers are avoided [34].

#### 2.3.4. Clustering

Clustering is based on weight sharing. Weight sharing means dropping the number of unique weight values in a model. Weights are put into clusters and each weight belonging to the cluster is replaced with centroid value of the cluster. K-means implementation on neural computing is illustrated in Figure 16. [35]

Figure 16. Feature homogeneity is increased by use of clustering methods.

#### 2.4. Summary

Normal computations can be accelerated and the energy efficiency improved by quantization, and by exploitation of the specific opportunities provided by the ReLU activation function. By folding offline calculable weights the number of operations can be reduced. By applying sparsity to the model the model size can be reduced, but pruning has narrow applicability on mobile networks as the number of parameters is limited. In mobile implementations, high level performance is desired while the computational solution should be minimized.

#### 3. NEURAL COMPUTING ON EMBEDDED PLATFORMS

Understanding hardware and model design is fundamental in training and inference optimization. Most optimization methods concern one or multiple aspects of throughput, efficiency, latency, accuracy and memory usage. Usually optimization is a trade-off between these issues. [36]

The most vital components used in neural network training are memory, central processing units (CPUs), accelerators (e.g. GPUs), high-speed connectors (network connection and buses) and fast storage. Seamless design of the computing pipeline is a requirement for producing a low latency solution.

#### 3.1. Number Representations

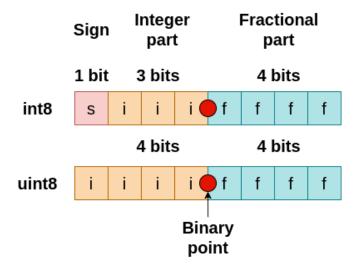

A computer representation is always restricted due to storage requirements. There are two main types of numbers modern microprocessors operate on: fixed- (FX) and floating point (FP) representations [37]. Fixed-point (FX) numbers represent fractional values and are heavily used in low-cost embedded microprocessors. Figure 17 illustrates FX 8-bit (FX-8) unsigned (uint8) and signed (int8) representation examples, where s is a sign,  $i = \{i_1, \ldots, i_m\}$  is the integer part, and  $f = \{f_1, \ldots, f_m\}$  is the fractional part of a representation [38].

Figure 17. Representations of important signed and unsigned FX formats.

Neural networks are often trained using FP arithmetic, but for efficient neural network inference we need to map FP to FX representation. For mapping a FX presentation from a FP presentation, we need to consider the dynamic range of the conversion, and precision. Dynamic range is defined by the largest and smallest numbers, and precision is the number of levels in the representation. FX arithmetic is often represented in Q-, or UQ-format, for signed and unsigned, respectively, where m is the integer bit count and n is the fractional bit count. [26]

FP to FX optimization can improve performance and accuracy. In used optimization methods the FX scaling factor is shared. [36]

FX approximation of a FP number can be calculated by Equation (17), which is the two's complement representation. [38]

$$FX = |(FP * 2^m)| \tag{17}$$

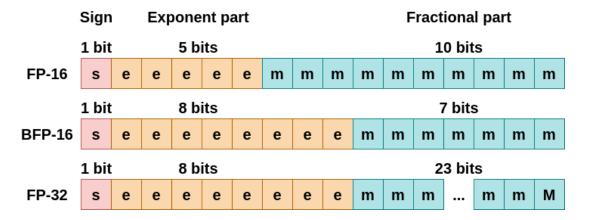

The required FX representation for optimal neural 8-bit precision is (U)Q1.7 format. FP arithmetic is the most common way of representing numbers in computing systems. FP consists of three parts: The sign s, the exponent  $e = \{e_1, \ldots, e_m\}$  and the mantissa  $m = \{m_1, \ldots, m_m\}$  [39]. FP arithmetics are visualized in Figure 18. In a FP system the compromise is made between the mantissa and the size of the exponent [40]. FP formats useful for neural computing are:

- IEEE 754 floating point 32-bit (Single-precision) representation (FP-32) Single-precision FP is typically used during training of neural network.

- IEEE 754 floating point 16-bit (Half-precision) representation (FP-16)

Mapping between IEEE 754 FP data types requires conversion of values due to differences in exponent and fractional part sizes.

- Brain floating point 16-bit representation (BFP-16)

Google brain team has presented brain floating point format (BFP-16) for usage instead of conventional FP-16. BFP-16 uses same amount of bits in exponent part making the conversion easier to implement. The range of BFP-16 is the same as with FP-32. The hypothesis is to have better classification accuracy on BFP-16 compared to FP-16. [41]

Figure 18. Representations of important FP formats.

In hardware, saturated or unsaturated arithmetics are used. Saturated arithmetics clip over- or underflow to maxima or minima, respectively. Unsaturated arithmetics allow overflows. [42]

#### 3.1.1. Number Formats for Neural Networks

CNNs employ FP-32s for storing gradient weights. This is currently the most commonly used procedure for keeping gradient values from vanishing during training [17]. In inference we need only to compute the forward pass. Typically FP-16 or FX-8 suffices for classification networks [25]. When utilizing a particular arithmetic, speed, accuracy, range, portability, ease of use, and speed are the core attributes [38].

#### 3.2. Computing Concurrency

Computing concurrency in neural computing has many levels, most relevant ones for inference being operator and network concurrency. At operator level there are two scales: the single operator and the decomposition of operators. Decomposition of operators deals with convolutions. [43]

Data parallelism deals with batch size and communication, which are important for training of a network, but model parallelism and pipelining are relevant for latency optimization. Model parallelism deals with layer level optimization methods and memory footprint reduction. Pipelining concerns the data flow of a model and layer process partitioning. Hybrid parallelism is a combination of multiple parallelism schemes, it is a common practice to combine multiple parallelism schemes. [43]

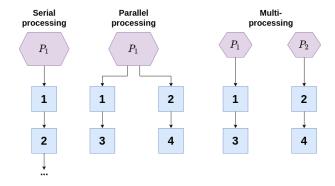

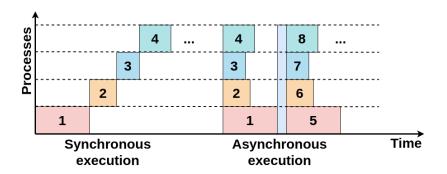

Multiprocessing and parallel processing, in theory, provide for linear speedup, while Amdahl's law shows it is limited by serial parts of the application [44]. In practise linear speedup is limited due to communication and memory bottlenecks. Load balancing, communication, and processor synchronization are important aspects for effective parallelization [45]. Different computing schemes are visualized in Figure 19, where  $P = \{1, 2\}$  are processors.

Figure 19. Different processing schemes.

#### 3.2.1. Convolution Algorithms

One of the most important hardware features for neural computing is the effectiveness of convolution computation. Convolutional layers in neural computing are the SOTA method for feature representation, but are heavy to compute due to high number of operations. Convolutional layers include majority of computations involved in

inference and training of CNNs [43]. Convolution optimization algorithms reduce the total number of operations and communication [46].

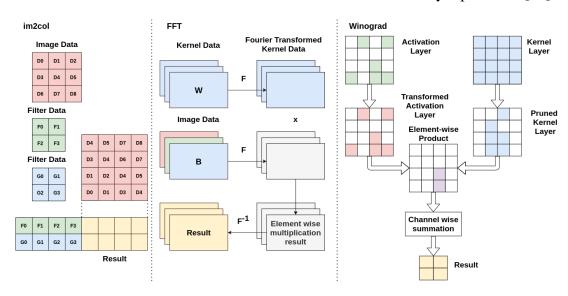

Three convolution algorithms are typically used in neural computing:

#### • im2col

In im2col a discrete convolution is transformed into a matrix multiplication (MM). The im2col method is good method for acceleration, but it consumes a high amount of memory which results in bad scalability. im2col is also known as general matrix multiplication (GEMM) method. [43]

#### • Fast Fourier Transform (FFT)

Compared to im2col, FFT algorithm is efficient for large convolutions due to weight reuse. FFT can be optimized further by usage of zero-padding due to many kernel values being zero. For optimality pruned FFT is especially efficient. In pruned FFT number of operations is reduced. [43]

#### • Winograd's fast convolution algorithm

Winograd's algorithm cuts the number of multiplications, but its cost grows quadratically with kernel size so it is only used for small kernels. Winograd's algorithm affects the numerical accuracy. [47]

Visualization of each algorithm is in Figure 20, which is adapted from [43] and [47]. In im2col 3D tensors are disassembled into 2D matrices. Kernels and image data are multiplied and the result is the convolved tensor. In FFT algorithm data and kernels are transformed by FFT and element-wise multiplied. Inverse FFT is then applied for getting the result. In Winograd's algorithm, convolutions are decomposed into sums of tiled small convolutions from transformed kernel and activation layer products. [43]

Figure 20. Convolutional Computation method visualizations.

There is no effective general use algorithm for neural convolution computation. The layout of the data has a huge effect on acceleration speedup of each convolution optimization algorithm. [43]

#### 3.2.2. Data Order

For a high-performance matrix computation system, minimization of operation count is not enough. Data order has a significant role for the performance. All inputs, outputs and transformations of the data are represented in tensors that are multidimensional arrays [43]. In Equation (18) an example of input data order for a tensor is visualized, where T is a tensor, B is the batch size, C is the number of channels, H is the height and W is the width of a tensor [36].

$$T = [B, C, H, W] \tag{18}$$

Convolution processing efficiency is related to the processing architecture. Most commonly the [C, H, W, B] format is used, which is the interleaved format. [48]

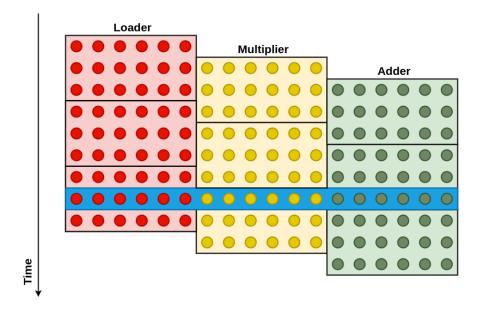

#### 3.2.3. Pipelining

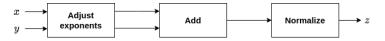

FP operations require multiple steps for finishing a calculation, as a clock cycle is used for each step. When we feed x and y to an adder we get an output sum z. Figure 21 represents example figure of a FP adder, that requires three clock cycles. [49]

Figure 21. A 3-cycle adder.

Pipelining means streaming each phase at one cycle. We can expect thrice better processing throughput by using pipelined addition [49].

For neural computing concurrency acceleration it is limited by the longest-latency element in the pipeline. Pipelining can be conducted on layer and model levels. Pipelining in neural computing needs to address data dependency and resource allocation related challenges. [43]

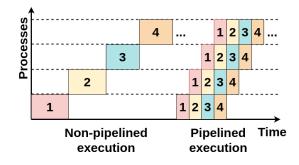

During inference the data is used when available, but data dependency is a bottleneck when using batch normalization techniques. Layer partitioning has been shown to reduce the required amount of parameters and communication between processors [43]. Figure 22 visualizes pipelined execution, where  $\{1, \ldots, 4\}$  are execution groups.

For efficient pipelining specialized hardware, such as systolic arrays, are used [50].

Figure 22. Pipelined computation visualization.

FX calculations are simpler, however both FX and FP representations are restricted in precision and dynamic range. Restrictions manifest rounding and saturation errors, which propagate through networks, and the effects on the networks are hard to analyze, requiring experimentation [51]. Design of a concurrent system requires consideration of instruction and data stream(s). A popular taxonomy for computation concurrency is Flynn's taxonomy [52].

#### 3.2.4. Instruction and Data Streams

An instruction stream is an sequence of instructions performed by the machine and a data stream is a sequence of data called by the instruction stream. A program is an ordered set of instructions. [53]

Usage of multiple threads is called multithreading (MT). MT is a prominent way of accelerating computing. In interleaved MT the tasks are coarse- or fine-grained, where thread executions are based on cycle counts, cache misses and fairness. [43]

Figure 23 displays the idea of fine-grained parallel execution, where threads are used for asynchronous tasks  $t = \{1, ..., 8\}$  processing.

Figure 23. Multiple threads are used for accelerating computational tasks in fine-grained parallelism.

The weaknesses of fine-grained parallelism appear when dealing with elements that need to be saved to cache for long time spans, while coarse-grained tasks are good for environments where large number of cache misses are an issue. [43]

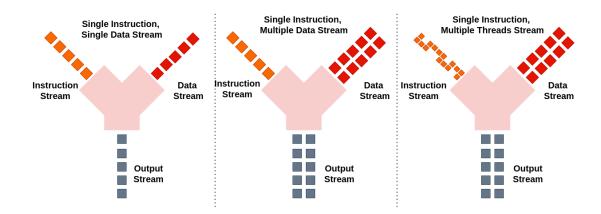

Single instruction, multiple threads (SIMT) and multiple instructions, multiple threads (MIMT) architectures are used for efficient neural computing. In neural computing

## • Single instruction, multiple threads (SIMT)

Single instruction, multiple threads (SIMT) is based on idea of thread warping, where warps are collections of threads. Multiple entities of data are accesses simultaneously and divided into smaller tasks [54]. Advantages of using the SIMT model are thread individuality and flexibility of warping, which translate to inference acceleration possibilities by fine-grained task scheduling.

Figure 24 illustrates differences between Single Instruction architecture pipelines.

Figure 24. Single instruction stream architectures.

#### • Multiple instructions, multiple threads (MIMT)

MIMT is an execution model used in parallel computing, where system utilizes multithreading with multiprocessing. In multithreaded computing a set of parallel threads are grouped into warps. Ideal warp execution happens without conflicts. Different conflict cases are instruction and data level read misses, and data write misses. If threads of a warp come to a data dependent branch, the warp serially executes each branch till the paths are completed. [54]

The inference acceleration idea behind MIMT is based on fine-grained thread warping. Instruction level warping for multiply-add is in Figure 25.

Figure 25. Optimal instruction level parallelism in multiply-add.

Multiple instruction architectures offer a possibility for simplifying matrix multiplication (MM) algorithms, but simplifying the algorithms is not straightforward process as systems have different bottlenecks and data dependencies. [46]

#### 3.3. Delegation

CPU, GPU and DSP are exhibits of instruction set architecture (ISA) implementations. An implementation is built on top of instructions. A system consisting of multiple processors with different architectures is called a heterogeneous computer. Heterogeneous computing is typical when reaching for an optimized computing system, where computing is delegated to the most efficient platform. [50]

Data handling, memory operations and control flow operations are cornerstones of ISA design, where parallelism is divided into three types:

#### • Task-level

Task-level parallelism is achieved when different threads are executed on different or same data.

#### • Data-level

Data-level parallelism is achieved when each processor performs same task on different pieces of distributed data. Location of memory access affects read and write times and cause of increasing memory latency. This is one reason why memories are grouped into private and shared memories. The smaller the memory is in size, the faster the processing speed. [45]

#### • Instruction-level

Instruction-level parallelism is achieved when instructions are grouped and executed in parallel without changing the end result. Instructions can only be grouped together if there is no data dependency between instructions. [45]

CPUs commonly use SIMT architecture, but are optimized for serial operations. CPUs have large cache sizes and complex control logic, but low processing unit capability. Many computation pipelines map data initially to CPU accessible memories, which account to low initialization durations.

The most common delegation platforms for smartphones are GPUs and digital signal processors (DSPs). Less common mobile delegation platforms are field programmable gate arrays (FPGAs). For delegation the system needs to decrease information richness, as the information processing pipeline is dependent on used delegation hardware and software.

#### 3.3.1. Graphics Processing Units

GPUs have high memory access costs. It is therefore important that the processing time is optimized against data transfers. Boosting performance of a GPU is done by keeping memory access patterns local. [45]

GPUs used for neural acceleration excel either at training or inferencing. Biggest problems with GPU delegation are enormous memory allocation times, which is the critical factor in mobile GPU delegation. GPU architectures specialize for maximal FP burst reading throughput, but are not good at handling interrupts and sparse data formats,. The way of boosting GPU performance is to keep memory access patterns

local and to minimize handling interrupts and sparsity of data. Generally data transfer is the most common bottleneck when delegating on a GPU. [55]

#### 3.3.2. Digital Signal Processors

Typical MIMT implementations are parallel DSPs used in digital image processing. Generally main benefits are lower power consumption and better inference speed compared to CPUs and GPUs. In our context DSPs employ FX inference pipeline.

Fundamentally DSPs are designed to perform some basic operation very quickly. System should be designed to be sustainable and meet minimum requirement for task processing speed as processing speed increases the power consumption. Power consumption of algorithm is affected by the complexity of the algorithm. [56]

#### 3.3.3. Field Programmable Gate Arrays

Field programmable gate arrays (FPGAs) provide high speedups and data parallelism compared to regular processors. FPGAs are reprogrammable special-purpose hardware. Relevant design techniques for accelerating MM algorithms on FPGAs are systolic arrays. [57]

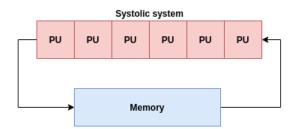

#### 3.3.4. Systolic Arrays

Systolic systems consist of cells, which are processing- (PUs) and memory units. Systolic design is bound on a particular computational task. The systolic array is a good design choice memory bandwidth-, computational output- and modularity-wise as the system is simple and regular by design. [54]

The idea of a systolic system is to reduce latency by reducing the communication time and by having a pipeline of operations, enabling processing of multitudes of operations compared to the original system. Figure 26 represents a systolic system, where the processing units form a chain of operations.

Figure 26. A systolic system is a set of processing units working together for solving a task.

Producing special systolic hardware comes with a price: for a large input size the cost and performance increase proportionally, but due to usage of simple elements the design will remain regular: it needs to be tailored to the problem. [54]

#### 3.3.5. Tensor Processing Units

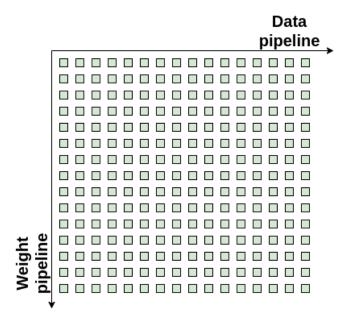

For efficient tensor processing unit (TPU) design, a matrix multiplier unit (MXU) is one of the most specialized designs. TPU is a specialized architecture for NN inference, where MXU consists of FX-8 multiply-and-add operations. MXU is a matrix processor, which is capable of processing hundreds of thousands of matrix operations in a single clock cycle. [58] The MXU provides vast number of multiplies per second and usage of variables without need for intermediate storage. The weight pipeline forms a partial sum pipeline. A MXU is visualized in Figure 27, where cells form a systolic array for multiplications.

Figure 27. MXU flow in a TPU.

A systolic array is used for allowing the data to flow into the matrix multiplication without storing variables to registers. While TPUs offer accelerated performance, they are single purpose application-specific integrated circuit (ASIC) designs. [59]

#### 3.4. Summary

Computation can be reduced by mapping the variables into smaller number formats. The representations are important factors for enabling a trade-off for precision and inference acceleration of a neural computation system. Pipelining and parallelism are key elements which have led to many coherent concurrent hardware implementation designs. The general convolution algorithm can be simplified by replacing it with faster convolution methods. Neural inference can be accelerated by dividing computational tasks into fine-grained threads, which are coordinated between processing cores. Computation throughput can be accelerated by using special hardware with narrow implementation pipelines, but bottlenecks for each hardware vary.

#### 4. FACE DETECTION IMPLEMENTATION

The Common face detection pipeline consists of three steps. The first step is filling the input, the second is inference and the third step is output decoding. The objective on the last step is turning output to format where it becomes useful information for the end user. In our implementation RetinaFace project was chosen for the baseline. The reasons being clear technical documentation and the results on public benchmarks. [4]

#### 4.1. Input Fill

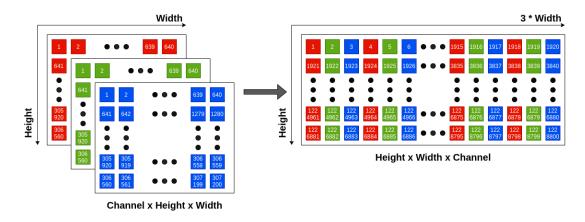

Initially the input image is transformed to the needed format and moved to memory for the inference engine. In TensorFlow Lite the input tensor expects the model format to be formatted in [B, H, W, C] format. In Figure 28 the input image is transformed from planar to interleaved image representation.

Figure 28. Converting image from continuous to interleaved format.

#### 4.2. RetinaFace Computing

Before the model inference, the input dimensions are allocated, and the model is initialized. The inference engine calculates weights for the input image. The forward pass is used for producing outputs. Outputs need to be decoded after extraction.

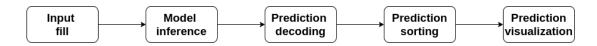

The most common decoding approach is using bounding boxes and classification scores. Classification scores are used as the first discarding value. For bounding box representation, in a single shot detector scheme, we need to connect anchor boxes to the matching bounding boxes. Bounding box voting is used to discard non-interesting predictions. Bounding box voting consists of intersect over union (IoU) [60], and non-maximum suppression (NMS) [61] techniques. Single shot detection phases are visualized in Figure 29.

Figure 29. The Single shot detector pipeline.

#### 4.3. Model Outputs

Outputs of the model are prediction scores, and bounding box deltas. Prediction scores are extracted from softmax layers, and bounding box deltas are extracted from convolutional layers. The outputs are designed to be extracted for each anchor per the densification parameter. Densification means the number of bounding box locations for each anchor position.

#### 4.3.1. Prediction Scores

Output level always contains an output layer for extracted bounding boxes and classification scores. Prediction scores need to be mapped according to the transformations applied to the bounding box outputs (bounding box deltas).

#### 4.3.2. Bounding Boxes

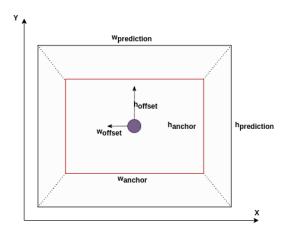

We want to extract minimum bounding boxes for detected faces. Bounding boxes adopt scale-invariant transformations for the centers, and log-scale transformation for the height and width. For determining a prediction position, the prediction center position, and the bounding box delta and anchor are used, which are visualized in Figure 30, where offsets are the extracted delta variables of a bounding box layer.

Figure 30. The bounding box decoding phase.

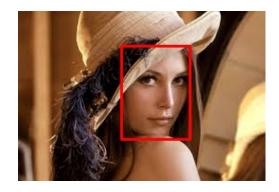

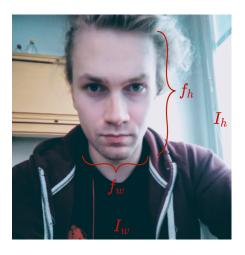

A minimum bounding box is visualized in Figure 31. The detection is defined to tightly contain the forehead, chin and cheek. If the face is occluded, parameters are used for placing the bounding box on the estimated location of the face. [3]

Figure 31. An example of minimized bounding box.

#### 4.3.3. Anchors

After we have decoded the bounding box deltas the generation of anchors commences. An anchor is an default position for a bounding box. The face detector implementation contains three levels. The anchors are calculated based on the levels and each level defines a stride length. Strides are fixed constants with lengths of 8, 16 and 32 pixels.

#### 4.4. Predictions

We have a number of predictions by linking the bounding box predictions with matching scores. By reshaping the tensor data into shape where we can easily align corresponding bounding boxes with prediction scores. An example of predictions with high detection scores are visualized in Figure 32, which consists of example images from [3]. A voting scheme is needed for removing predictions representing the same faces.

Figure 32. Examples of predictions with high confidence scores.

The previous processes generate a large number of detections. The detector needs to determine acceptable discarding criteria for predictions. Bounding box voting is a set of techniques, where the aim is to limit proposed detections per object to the most matching detection. Intersect over union (IoU) and non-maximum suppression (NMS) are used for voting of predictions.

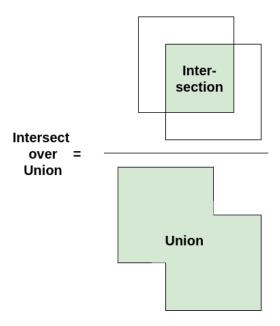

#### 4.4.1. Intersect over Union

In intersect over union (IoU) the area of each bounding box is measured and the intersection between each targeted bounding box is calculated. Figure 32 shows examples of detections without applying voting techniques. An example visualization of IoU is in Figure 33.

Figure 33. Intersect over Union visualization.

IoU is a popular evaluation metric used in face detection for removing unwanted candidate predictions. For calculating IoU a cost function is used, common ones being Manhattan and Euclidean distances. The formulae of IoU is in Equation (19), where a and b are the areas of predicted bounding boxes, i is the intersection area and u is the union area.

$$IoU = \frac{|a \cap b|}{|a \cup b|} = \frac{i}{u} \tag{19}$$

Suggested alternative for IoU is the generalized IoU (GIoU). If the voted predictions do not overlap, the value of IoU is zero. GIoU is defined in Equation (20), where c is the smallest convex area that encloses both predictions. The smaller c value, the better prediction score is. [60]

$$GIoU = IoU - \frac{|c/(a \cup b)|}{|c|}$$

(20)

#### 4.4.2. Non-Maximum Suppression

NMS is a post-processing technique where a set of bounding boxes are transformed into a single detection. The most important parameter of the voting scheme is the threshold which is used for discarding boxes with large IoU score.

In our implementation we use a greedy-NMS algoritm. Greediness means the system assumes the best scoring bounding box covers the object and drops other bounding boxes based on the suppression threshold.

When each bounding box below threshold value is removed, the second highest scoring window is selected and the procedure is repeated until all windows have been iterated through. Combining the IoU and NMS gives Algorithm 1.

#### Algorithm 1. Bounding Box voting scheme

1 In voting p stands for prediction, t stands for target and i stands for intersect. Before this algorithm we have sorted predictions from ascending by prediction.

```

2 for p preds do

3

threshold = 0.5

4

p_{a_{rea}} = (p_{x_{max}} - p_{x_{min}} + 1) * (p_{y_{max}} - p_{y_{min}} + 1)

5

for t to preds do

7

8

i_{x_{min}} = \max(p_{x_{min}} - t_{x_{min}} + 1)

i_{y_{min}} = max(p_{y_{min}} - t_{y_{min}} + 1)

10

i_{x_{max}} = \max(p_{x_{max}} - t_{x_{max}} + 1)

11

i_{y_{max}} = max(p_{y_{max}} - t_{y_{max}} + 1)

12

13

i_{a_{rea}} = max(i_{x_{max}} - i_{x_{min}} + 1) * max(i_{y_{max}} - i_{y_{min}} + 1)

14

t_{a_{rea}} = (t_{x_{max}} - t_{x_{min}} + 1) * (t_{y_{max}} - t_{y_{min}} + 1)

15

iou = i_{a_{rea}}/(p_{a_{rea}} + t_{a_{rea}} - i_{a_{rea}})

16

17

if iou > threshold then

18

erase t from preds

19

else

20

continue

21

end

22

end

23

24 end

```

After processing the detection proposals, the detector outputs the selected outcome. In optimal cases the detection contains one detection per object in an input image. In Figure 34 we have removed the detections representing the same object. Notice the difference to Figure 32. Images taken from [3].

Figure 34. Examples of voted predictions.

# 4.5. Implementation Toolkit

The detector is implemented using TensorFlow (TF) C++ API and TensorFlow Lite (TFLite). [59]

#### 4.5.1. TensorFlow

TF is a framework for neural network computing. It supports both model training and inference. The design of a neural network is done by using dataflow graphs. Important aspects, why TF was chosen for implementation, are the on-device acceleration capabilities. Typically custom code is required for delegation, however TF contains a delegate API. Usage of APIs minimizes the programming work required for delegating a model on specialized platforms. [62]

## 4.5.2. TensorFlow Lite

TFLite is an optimization toolkit for transforming the TF models into TFLite models, which is a compressed, smaller, faster, and efficient format. The toolkit has two main components: an interpreter and a converter. TFLite has optimized versions for most operators, but some optimizations are hardware-specific. [24]

For inference we extracted FP-32 and FX-8 models. For accuracy tests we used FP-32, FP-16 and FX-8 models. Our final model has estimated 423420 parameters.

Operations and MACs are related to input sizes. The estimated number of arithmetic operations required for inference are in Table 1.

| rable 1. Estimated number of artifilities operations |                                 |  |  |

|------------------------------------------------------|---------------------------------|--|--|

| Input size                                           | Number of arithmetic operations |  |  |

| QVGA [320 240]                                       | $4.0 * 10^8$                    |  |  |

| VGA [640 480]                                        | $1.5 * 10^9$                    |  |  |

| FHD [1920 1080]                                      | $1.0*10^{10}$                   |  |  |

| DCI 4K [4096 2160]                                   | $4.3*10^{10}$                   |  |  |

Table 1. Estimated number of arithmetic operations

#### 4.5.3. C++

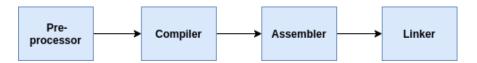

In the implementation the project was ported to a C++ environment, main reasons being ability for compilation and better portability. Compiled languages offer the ability for building executables from source files which, in terms of speed, are on a different level compared to interpreted languages. [63]

Portability in C++ means that we can build source files with one device, move the source files to another device, and the device has minimal asset requirement outside of the project. This becomes crucial when developing applications for hardware with limited computational capabilities, such as embedded and mobile devices. The compilation process is visualized in Figure 35. Preprocessor processes the macros and defined files are expanded based on declarations. The compilation process assembles the code into machine-readable formats. In the linking process, a library or an executable is produced. [63]

Figure 35. Compilation Process in C++.

# 4.5.4. Calibration

Before the evaluation phase, calibration was conducted. In this process, the model was prepared for folding by dividing operations into separate nodes. Calibration consists of two phases: calibration and model conversion.

In calibration we finalize the graph and insert fake quantization nodes. Fake quantization nodes are containers for the quantization parameters. For calibration, a small dataset was gathered. The model was finalized before quantization, meaning that the network weights are not modified. Fake quantization nodes are used for mapping quantization ranges of quantized layers. Activation ranges are saved to checkpoint files. For conversion, we used the TensorFlow Lite optimization toolkit.

# 5. FACE DETECTION EXPERIMENTS

In inference benchmarking there are two fundamental issues of interest. Average runtime and the initialization time. The tests concern model inference time, model size, accuracy and power consumption.

The model inference test includes two parts: optimal threading and resolution. Testing each threading option gives the optimal threading for each hardware: CPU, GPU and DSP. Tests have been carried out for each important resolution. They are

- Quarter Video Graphics Array (QVGA) [320 240],

- Video Graphics Array (VGA) [640 480],

- Full High-Definition (FHD) [1920 1080], and

- Digital Cinema Initiatives (DCI 4K) [4096 2160].

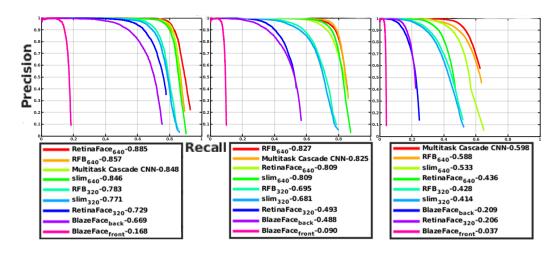

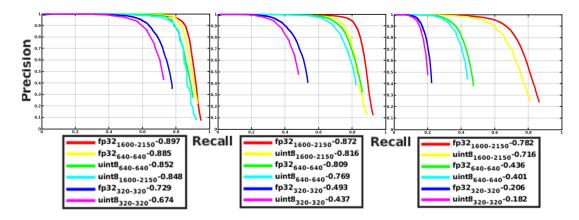

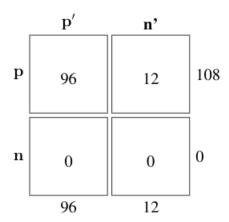

For model accuracy tests we need to select meaningful datasets. The most important attributes are consistency, scalability, and the level of difficulty. The dataset needs to contain images with multiple levels of detection challenges in various situations, so the detector required balanced data for proper benchmark scoring. Precision-recall data was used for accuracy evaluation.

Model weights and parameters of a network are saved for inference. We were interested in FP-32, FP-16 and FX-8 models, because the different hardware options support different arithmetics. During quantization information is lost and there are no distinct guidelines for model capacity and the breaking point of the model. Delegates are helper functions for accelerating models on certain platforms.

Hardware development kit 8250 (HDK8250) was used for measurements. Important characteristics for tests are computation arithmetic, delegation and hardware. Tests were conducted on:

• CPU (Qualcomm Kryo 585 CPU)

Supports both FP and FX arithmetics. CPU calculations are operated on an OpenCL optimized solution. Qualcomm Kryo 585 consists of single 2.84GHz (Cortex A77), three 2.4GHz (Cortex A77) and four 1.8GHz (Cortex A55) cores.

• GPU (Qualcomm Adreno 650 GPU)

Requires a FP model for inference. For GPU acceleration we use TFLite GPU delegate, which supports OpenGL.

• Mobile DSP (Qualcomm Hexagon 698 DSP)

Requires a FX model. NNAPI and Hexagon delegates are used for accelerating on DSP. NNAPI is a general-purpose accelerator and Hexagon delegate is specific for Qualcomm devices. The DSP has a theoretical output of 15 Tera operations per second (TOPS). However, the actual processing time for an image is more meaningful metric, representing the time the model needs for inference.

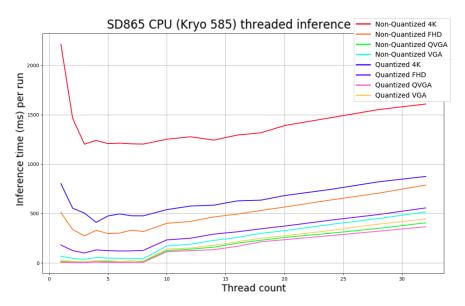

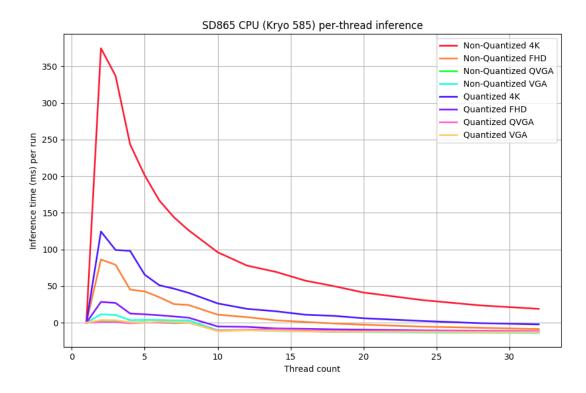

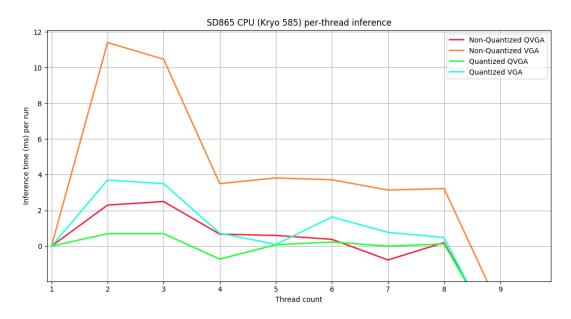

The threading benchmark provides minimum-, average- and maximum inference times of the run as standard deviation.

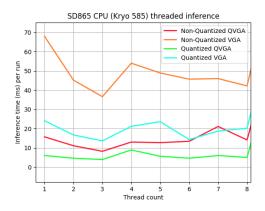

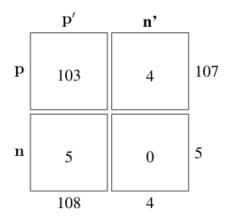

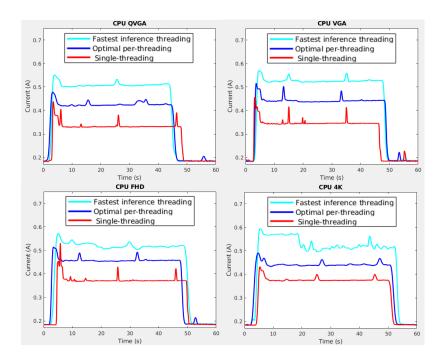

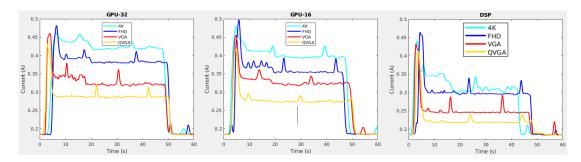

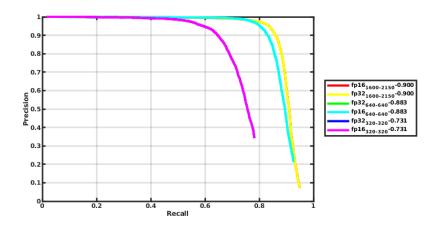

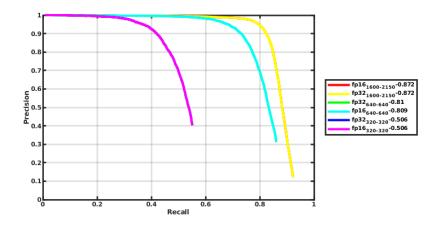

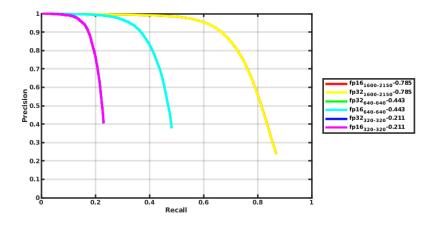

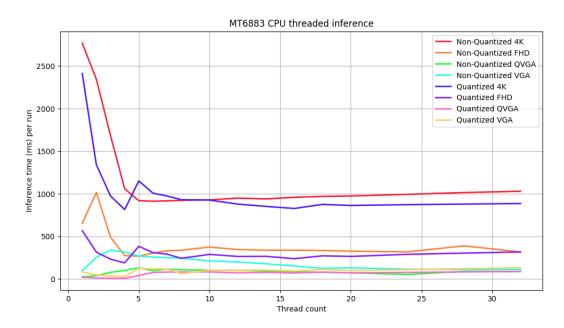

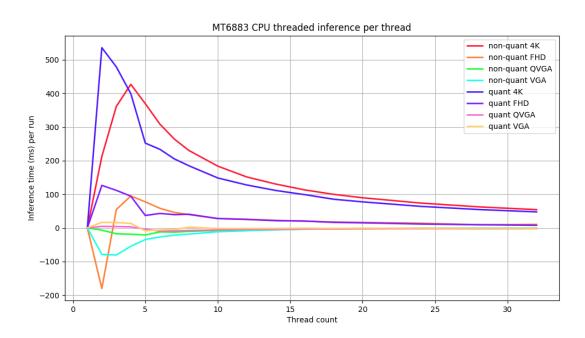

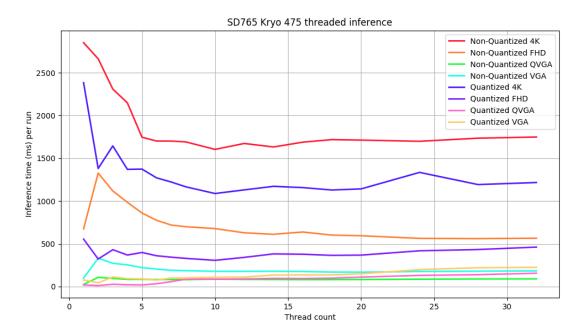

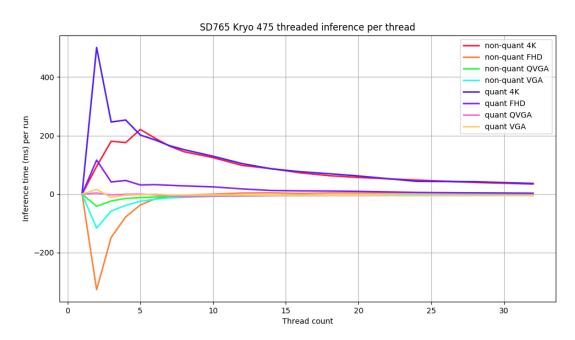

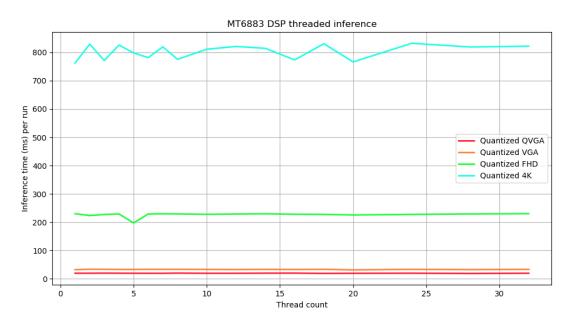

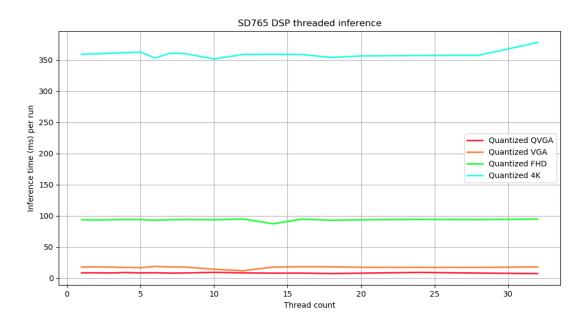

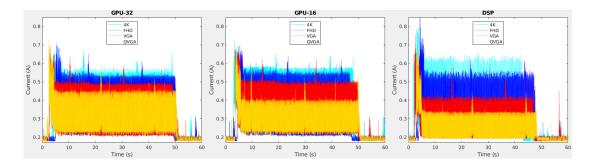

# 5.1. Optimal Threading