# HELSINKI UNIVERSITY OF TECHNOLOGY Department of Electrical and Communications Engineering

#### SAMI LALLUKKA

## Programmable logic design for an optical access network

Thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Technology

Espoo 27th May 2003

**Supervisor:** Professor (pro tem) Samuli Aalto, HUT **Instructor:** Lic.Sc. (Tech.) Kari Seppänen, VTT

## **Abstract**

HELSINKI UNIVERSITY OF TECHNOLOGY ABSTRACT OF THE MASTER'S THESIS

Author: Sami Lallukka

Name of the Thesis: Programmable logic design for an optical access network

Date: 27th May 2003

Number of pages: 99

Department: Department of Electrical and Communications Engineering

**Professorship:** S-38

**Supervisor:** Professor (pro tem) Samuli Aalto **Instructor:** Lic.Sc. (Tech.) Kari Seppänen

The structure of communication networks is going to change in the future. Datacom, telecom and broadcast traffic is conventionally transported over separated networks, which is a major cost factor in network management for operators. In addition, legacy communication networks cannot provide adequate quality of service for the emerging interactive multimedia services. For this reason, the development of communications networks is heading towards flexibility and convergence.

At the moment, the bottleneck factor in the development of communication networks transfer speed is the complexity of the metropolitan area feeder networks. This has a considerable effect on the service quality in this area as well. The TEKES-funded OAN-project concentrates on developing a new and simpler metropolitan optical feeder network, which could be used to improve the quality of service in the metropolitan area.

This thesis has been prepared as a part of the OAN-project. In this thesis, the structure of the present communication networks is presented and its problems are discussed. Based on this discussion, the future structure of communication networks is illustrated. Furthermore, the HDL-implementation process with its aggregates will be discussed. Finally, a programmable logic design for the optical metropolitan feeder network prototype, implemented in the OAN project, is presented.

Keywords: FPGA, VHDL, DoS, optical feeder network

## Tiivistelmä

TEKNILLINEN KORKEAKOULU

DIPLOMITYÖN TIIVISTELMÄ

Nimi: Sami Lallukka

**Työn nimi:** Optisen liityntäverkon ohjelmoitavien logiikkapiirien ohjelmoinnin

suunnittelu

Päivämäärä: 27. toukokuuta 2003 Sivumäärä: 99

Osasto: Sähkö- ja tietoliikennetekniikan osasto

Laboratorio: S-38

Valvoja: Professori (ma.) Samuli Aalto

Ohjaaja: TkL. Kari Seppänen

Tiedonsiirtoverkkojen rakenne elää muutoksen aikaa. Perinteisesti data-, puhelinja laajakaistaliikenne on siirretty erillisissä verkoissa, joiden samanaikainen ylläpitäminen tuottaa ylimääräisiä kustannuksia operaattoreille. Lisäksi uudet interaktiiviset palvelut vaativat toimiakseen sellaista palvelunlaatua, jota nykyiset tiedonsiirtoverkot eivät kykene tarjoamaan. Näiden epäkohtien johdosta tiedonsiirtoverkkojen kehityksessä tähdätään uusiin, entistä joustavampiin ja eri toiminnot yhdistäviin verkkoratkaisuihin, joissa tiedonsiirron palvelunlaadulla on entistä suurempi merkitys.

Tällä hetkellä tiedonsiirtoverkkojen kokonaistiedonsiirtonopeuden kasvun pullonkaulatekijäksi on muodostunut kaupunkialueiden syöttöverkkojen monimutkaisuus, millä on suuri vaikutus myös tiedonsiirron palvelunlaatuun. TEKESrahoitteisessa OAN-projektissa kehitetään uutta ja yksinkertaisempaa kaupunkialueen optista syöttöverkkoratkaisua, jolla alueen palvelunlaatua saataisiin parannettua.

Tämä diplomityö on tehty osana OAN-projektia. Työssä kuvataan tiedonsiirtoverkkojen tämänhetkinen rakenne, tarkastellaan sen ongelmia ja tulevaisuuden kehityssuuntia, sekä esitetään pohdintojen pohjalta rakennettu malli tulevaisuuden tiedonsiirtoverkkojen rakenteelle. Työssä esitetään myös HDL-implementointiprosessiin kuuluvat työvaiheet sekä käydään läpi suunnitelma OAN-projektissa toteutettavan prototyypin ohjelmoitavien logiikkapiirien ohjelmaa varten.

Avainsanat: FPGA, VHDL, DoS, optinen syöttöverkko

## **Foreword**

This thesis has been written in partial fulfillment of the requirements for the degree of Master of Science in Technology while participating in the OAN research project at VTT Information Technology, Broadband Communications.

On behalf of the employer, I would like to thank Markku Sipilä and Kristiina Hytönen for the possibility to write this thesis at VTT. Furthermore, I would like to thank all of my colleagues for their support and advice during the writing process; in particular, Kari Seppänen for his excellent ideas, guidance and proof reading; also, Risto Mutanen and Juha Zidbeck for their valuable advice and insights. Most of all, I would like to thank all of the VTT personnel located in the same premises for a splended atmosphere, especially, the gang in the coffee and lunch breaks. Finally, special thanks to my supervisor, Samuli Aalto at Helsinki University of Technology for excellent cooperation, careful proof reading and guidance.

I would also like to thank all of my family, relatives and friends, who have motivated me in my studies.

27th May 2003, Espoo, Finland

sen Seellebla

Sami Lallukka

## **Contents**

| Al | ostrac  | et       |                                        | i      |

|----|---------|----------|----------------------------------------|--------|

| Ti | iviste  | lmä      |                                        | ii     |

| Fo | rewo    | rd       |                                        | iii    |

| Ta | ble of  | conten   | its                                    | vi     |

| A  | crony   | ms       |                                        | vii    |

| Li | st of p | oictures |                                        | xiii   |

| Li | st of t | ables    |                                        | xiv    |

| 1  | Intr    | oductio  | n                                      | 1      |

|    | 1.1     | Motiva   | ation                                  | <br>2  |

|    | 1.2     | Goal .   |                                        | <br>2  |

|    | 1.3     |          | ure                                    | 2      |

| 2  | Con     | ımunica  | ation networks today                   | 3      |

|    | 2.1     | Access   | s network                              | <br>4  |

|    |         | 2.1.1    | Distribution networks                  | <br>6  |

|    |         | 2.1.2    | Feeder networks                        | <br>9  |

|    | 2.2     | Transp   | oort networks                          | <br>12 |

|    |         | 2.2.1    | Data centric services                  | <br>12 |

|    |         | 2.2.2    | Synchronisation                        | <br>13 |

|    | 2.3     | Netwo    | ork topologies                         | <br>14 |

|    | 2.4     |          | ll Networks                            | 15     |

|    |         | 2.4.1    | Synchronous Digital Hierarchy (SDH)    | <br>16 |

|    |         | 2.4.2    | Wavelength Division Multiplexing (WDM) | 18     |

|    |         | 2.4.3    | Optical Transport Network (OTN)        | 20     |

|    | 2.5     | Surviv   | ability                                | 21     |

| 3 | Con  |          | ation networks tomorrow         |     | 23 |

|---|------|----------|---------------------------------|-----|----|

|   | 3.1  | Future   | characteristics                 |     | 24 |

|   |      | 3.1.1    | Distribution networks           |     | 26 |

|   |      | 3.1.2    | Metropolitan area networks      |     | 27 |

|   |      | 3.1.3    | Transport networks              |     | 28 |

|   |      | 3.1.4    | Optical networks                |     | 29 |

|   | 3.2  |          | technologies                    |     | 29 |

|   |      | 3.2.1    | Passive optical networks (PONs) |     | 29 |

|   |      | 3.2.2    | Resilient Packet Ring (RPR)     |     | 32 |

|   |      | 3.2.3    | Data over SDH (DoS)             |     | 33 |

|   | 3.3  |          | t research projects             |     | 36 |

|   |      | 3.3.1    | HARMONICS                       |     | 36 |

|   |      | 3.3.2    | IP-HORNET                       |     | 38 |

|   |      | 3.3.3    | DAVID                           |     | 39 |

|   |      | 3.3.4    | Discussion                      |     | 40 |

|   |      | 0.0,,    | 2.500.5500                      | • • | 10 |

| 4 | Rese | -        | roject OAN                      |     | 41 |

|   | 4.1  | OAN to   | test network architecture       |     | 41 |

|   | 4.2  | OAN to   | test network prototype          |     | 43 |

|   |      | 4.2.1    | Functionality of the node       |     | 44 |

|   |      | 4.2.2    | Network structure               |     | 45 |

| 5 | FPG  | A prog   | ramming methodology             |     | 47 |

|   | 5.1  |          | basics                          |     | 47 |

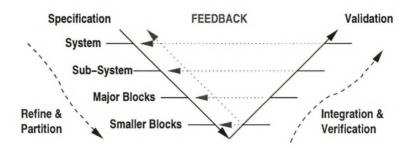

|   | 5.2  | HDL-i    | implementation process          |     | 49 |

|   |      | 5.2.1    | Design planning                 |     | 49 |

|   |      | 5.2.2    |                                 |     | 49 |

|   |      | 5.2.3    | Verification                    |     | 50 |

|   | 5.3  | Design   | n guidelines                    |     | 51 |

|   | 5.4  |          | quality                         |     | 52 |

| 6 | HDI  | design   | n options                       |     | 53 |

| U |      |          | architectures                   |     | 53 |

|   | 6.2  | Program  | amming tools                    |     | 55 |

|   | 6.3  |          | n options                       |     | 55 |

|   | 0.5  | 6.3.1    | Control functions               |     | 56 |

|   |      | 6.3.2    |                                 |     | 58 |

| _ | ***  |          |                                 |     |    |

| 7 |      | L Design |                                 |     | 62 |

|   | 7.1  |          | n functionality                 |     | 62 |

|   | 7.2  | Distrib  | oution of clocks                |     | 63 |

### **CONTENTS**

|    | 7.3   | Contro   | l part                                 | 67 |

|----|-------|----------|----------------------------------------|----|

|    |       | 7.3.1    | Registers                              | 67 |

|    |       | 7.3.2    | Accessing the interface card registers | 69 |

|    |       | 7.3.3    | Clock controller                       | 70 |

|    |       | 7.3.4    | PCI interface                          | 71 |

|    |       | 7.3.5    | Router control                         | 72 |

|    |       | 7.3.6    | I/O control                            | 73 |

|    |       | 7.3.7    | Control line                           | 73 |

|    |       | 7.3.8    | Microprocessor interface               | 74 |

|    |       | 7.3.9    | SRAM interface                         | 75 |

|    |       | 7.3.10   | Laser controller                       | 75 |

|    | 7.4   | Networ   | rk part                                | 77 |

|    |       | 7.4.1    | POS-PHY level 3                        | 77 |

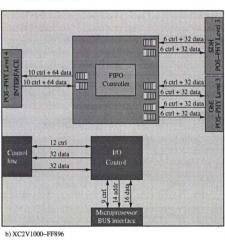

|    |       | 7.4.2    | FIFO controller                        | 79 |

|    |       | 7.4.3    | POS-PHY Level 4                        | 80 |

|    |       | 7.4.4    | Gb Ethernet (GbE) packet scheduler     | 81 |

|    |       | 7.4.5    | POS packet scheduler                   | 81 |

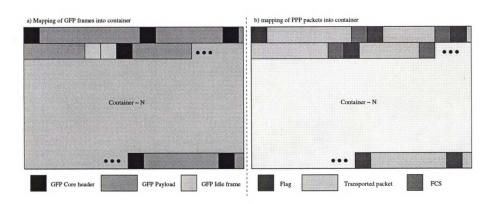

|    |       | 7.4.6    | GFP framing and deframing              | 82 |

|    |       | 7.4.7    | VC and LCAS                            | 83 |

|    |       | 7.4.8    | SDH framing                            | 85 |

|    |       | 7.4.9    | APS                                    | 85 |

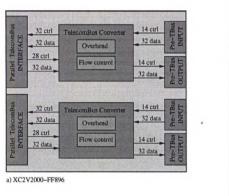

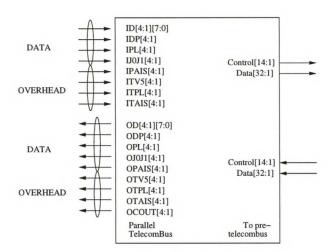

|    |       | 7.4.10   | Parallel TelecomBus interface          | 86 |

|    |       | 7.4.11   | Preliminary TelecomBus interface       | 87 |

|    |       |          |                                        |    |

| 8  | Con   | clusions | 3                                      | 89 |

|    | 8.1   | Results  | 8                                      | 89 |

|    | 8.2   | Future   | developments                           | 90 |

| Bi | bliog | raphy    |                                        | 92 |

| _  |       | J        |                                        | _  |

## **Acronyms**

ADM Add Drop Multiplexer

AN Access Node

APON ATM Passive Optical Network

APS Automatic Protection Switching

ASIC Application Specific Integrated Circuit

**ASON** Automatically Switched Optical Network

**ASTN** Automatically Switched Transport Network

ATM Asynchronous Transfer Mode

AWG Arrayed Waveguide Gratings

BER Bit Error Rate

**BPON** Broadband PON

**CATV** Cable Antenna Television

**CLB** Configurable Logic Block

CO Central Office

CPU Central Processing Unit

CRC Cyclic Redundancy Check

DCM Digital Clock Manager

**DIP** Diagonal Interleaved Parity

**DLL** Delay Locked Loop

**DWDM** Dense Wavelength Division Multiplexing

DoS Data over SDH

EFM Ethernet in the First Mile

**EPON** Ethernet PON

FDM Frequency Division Multiplexing

FEC Forward Error Correction

FIFO First In First Out memory

FPGA Field Programmable Gate Array

FSAN Full Service Access Networks

FTTx Fiber-to-the-x, where x stands for C (Curb), B (Building) or H (Home).

**GFP-F** Frame-mapped GFP

**GFP-T** Transparent GFP

**GFP** Generic Framing Procedure

**GMPLS** Generic MPLS

GPON Gb PON

**GSM** Global System for Mobile communication

HDLC High level Data Link Control

**HDL** Hardware Description Language

**HEC** Header Error Checksum

**HUT** Helsinki University of Technology

**IEEE** Institute of Electrical and Electronics Engineers

IOB Input/Output Block

**IPsec** IP Security

**IP** Internet Protocol

ISDN Integrated Services Digital Network

**IST** Information Society Technologies

ITU-T International Telecommunication Union, Telecommunication standardisation sector

**IWF** Interworking Functions

LAN Local Area Network

LCAS Link Capacity Adjustment Scheme

LED Light Emitting Diode

LVDS Low Voltage Differential Signalling

MAC Medium Access Control

MAN Metropolitan Area Network

MPLS Multi Protocol Label Switching

N-ISDN Narrow-band ISDN

OAN Optical Access Networking

**OLT** Optical Line Terminal

**OLT** Optical Line Termination

**ONT** Optical Network Terminal

ONU Optical Network Unit

**OPADM** Optical Packet Add/Drop Multiplexer

**OPR** Optical Packet Router

**OSI** Open Systems Interconnection

**OTN** Optical Transport Network

**OXC** Optical Cross Connect

**PCI** Peripheral Component Interconnect

PDH Plesiochronic Digital Hierarchy

PHY Physical Layer

PLL Phase Locked Loop

POH Path Overhead

PON Passive Optical Network

POS Packet Over SDH

POTS Plain Old Telephone Service

PPP Point-to-Point Protocol

PSTN Public Switched Telephone Network

QoS Quality of Service

RAM Random Access Memory

RPR Resilient Packet Ring

SAN Storage Area Network

**SDH** Synchronous Digital Hierarchy

SNMP Simple Network Management Protocol

**SONET** Synchronous Optical Network

**SRAM** Static Random Access Memory

STM-1 Synchronous Transport Module 1

**T1X1** Standards Committee T1 Telecommunications, Technical Subcommittee of Digital Hierarchy and Synchronization

TBS TelecomBus Serialiser

TDMA Time Division Multiple Access

TDM Time Division Multiplexing

**TEKES** National technology agency

**TOH** Transport Overhead

VCG Virtual Concatenation Group

VC Virtual Concatenation

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VPN Virtual Private Network

VTT Technical Research Centre of Finland

VoIP Voice over IP

WADM Wavelength Add Drop Multiplexer

WAN Wide Area Network

WDMA Wavelength Division Multiple Access

WDM Wavelength Division Multiplexing

xDSL x-Digital Subscriber Line

# **List of Figures**

| 2.1 | The overlaid structure of communication networks               | 5  |

|-----|----------------------------------------------------------------|----|

| 2.2 | The definition of access network                               | 6  |

| 2.3 | Access technologies in today's networks                        | 7  |

| 2.4 | MAN traffic characteristics today                              | 9  |

| 2.5 | The definition of transport network                            | 11 |

| 2.6 | Topologies used in networks today                              | 14 |

| 2.7 | Traffic grooming in WDM networks                               | 19 |

| 3.1 | The structure of the future communication network              | 25 |

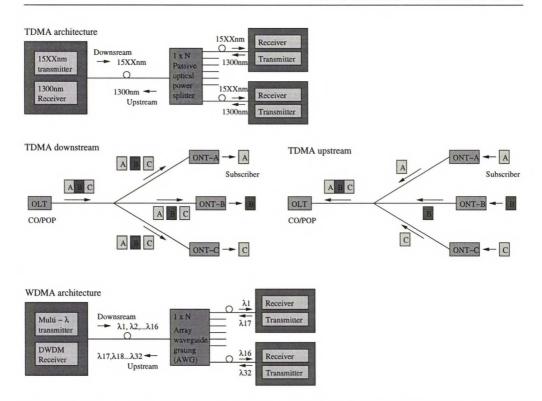

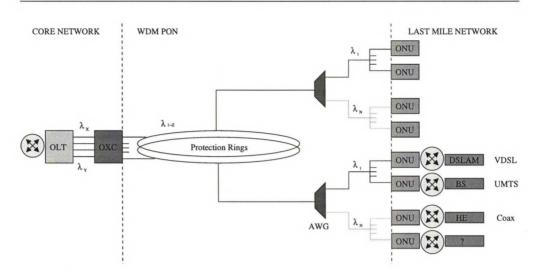

| 3.2 | The architecture and principle of TDMA and WDMA PONs           | 30 |

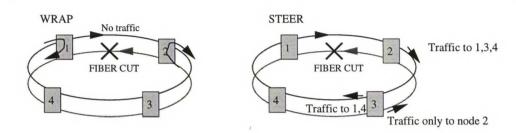

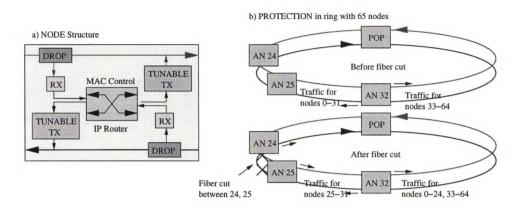

| 3.3 | Protection mechanisms in RPR                                   | 33 |

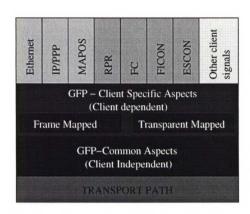

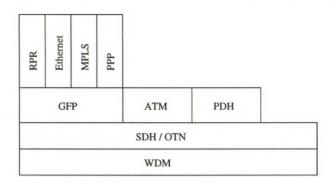

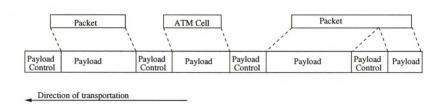

| 3.4 | Functional model of GFP                                        | 34 |

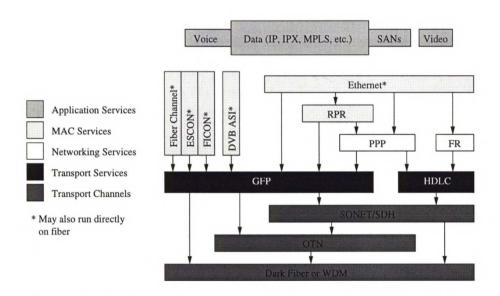

| 3.5 | The protocol stack of the GFP                                  | 34 |

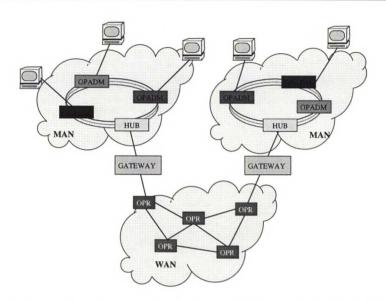

| 3.6 | The architecture of the HARMONICS project                      | 37 |

| 3.7 | The architecture of the IP-HORNET project                      | 38 |

| 3.8 | The outline of the DAVID project demonstrator                  | 40 |

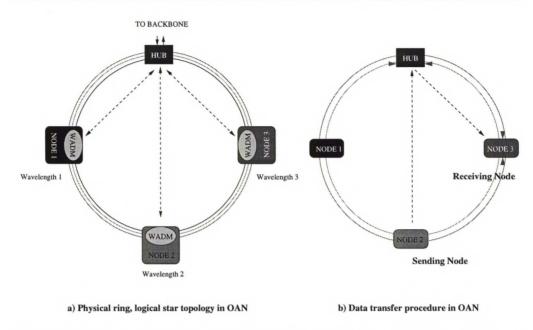

| 4.1 | The network layer protocol stack of the OAN test network       | 42 |

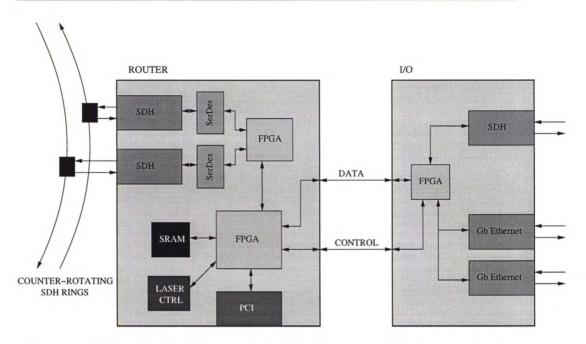

| 4.2 | Simplified architecture of the OAN test network prototype node | 44 |

| 4.3 | The network structure and data transmission process in the OAN |    |

|     | test network prototype                                         | 46 |

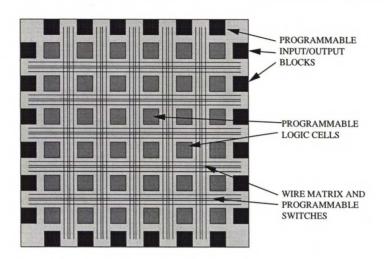

| 5.1 | The basic structure of the FPGA-chip                           | 48 |

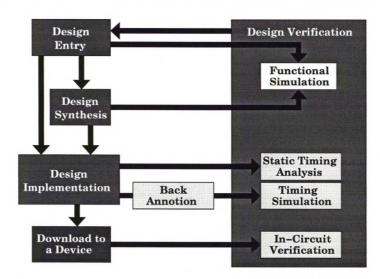

| 5.2 | The HDL design flow according to Xilinx                        | 50 |

| 5.3 | Verification as a part of design implementation process        | 51 |

| 6.1 | Virtex-II FPGA structure, adopted from [Inc00c]                | 54 |

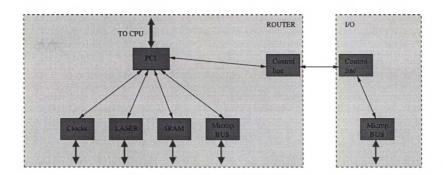

| 6.2 | The formation of the control functions in the OAN prototype    | 57 |

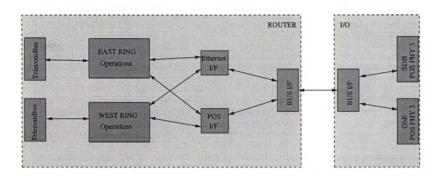

| 6.3 | The overall functionality of the OAN network                   | 58 |

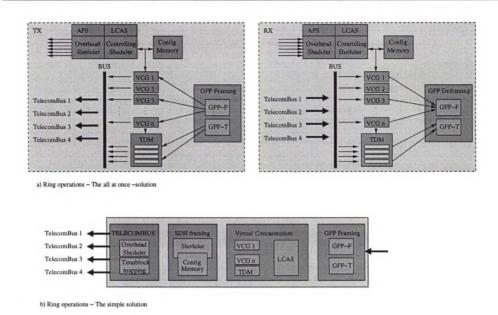

| 6.4 | The overall functionality of the OAN network ring operations   | 60 |

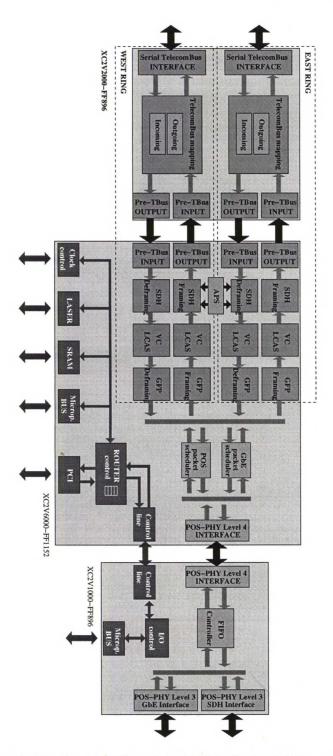

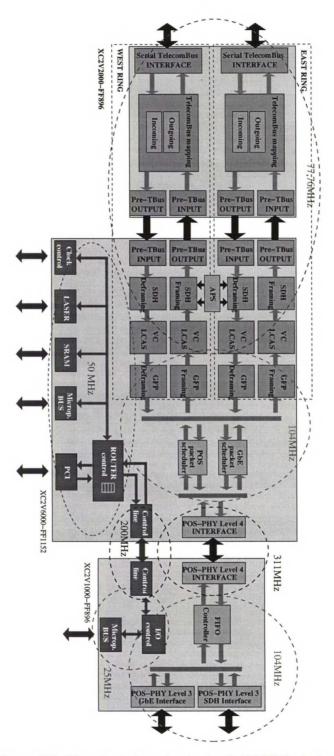

| 7.1 | The functionality of the FPGAs in the OAN prototype            | 64 |

### LIST OF FIGURES

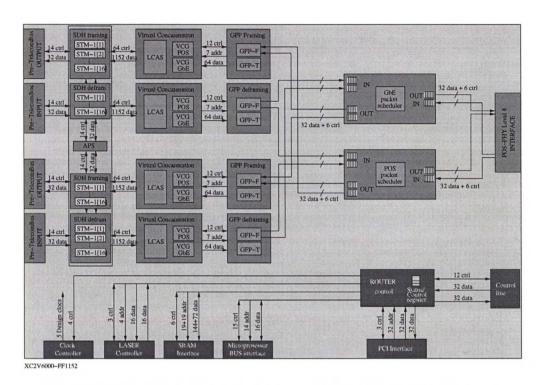

| 7.2  | The block design for the larger FPGA in the OAN prototype         | 65 |

|------|-------------------------------------------------------------------|----|

| 7.3  | The block designs for the smaller FPGA in the router card (a) and |    |

|      | for the FPGA in the interface-card (b)                            | 65 |

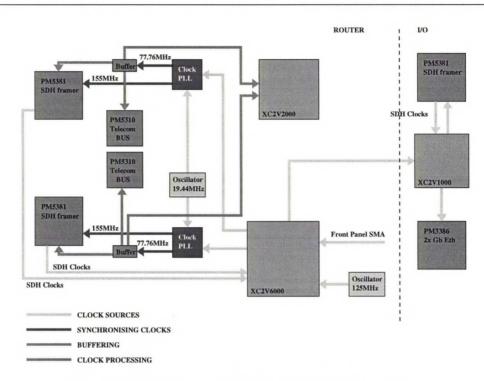

| 7.4  | The sources of clocks in the OAN prototype                        | 66 |

| 7.5  | The clock domains in the OAN HDL design                           | 68 |

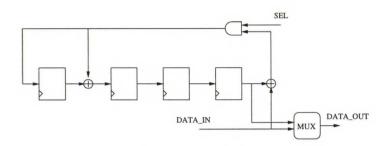

| 7.6  | The HW implementation of a bitwise CRC operation                  | 74 |

| 7.7  | The composition of the data transported over control line         | 74 |

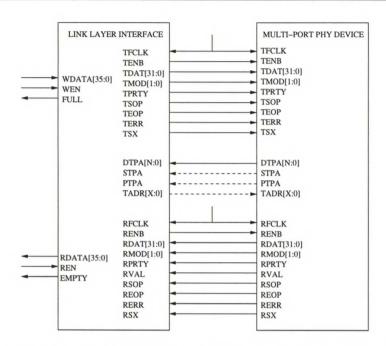

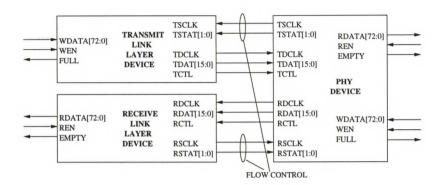

| 7.8  | The signals in POS-PHY level 3 interface                          | 78 |

| 7.9  | The signals in POS-PHY level 4 interface                          | 80 |

| 7.10 | The transmission protocol in POS-PHY level 4 interface            | 81 |

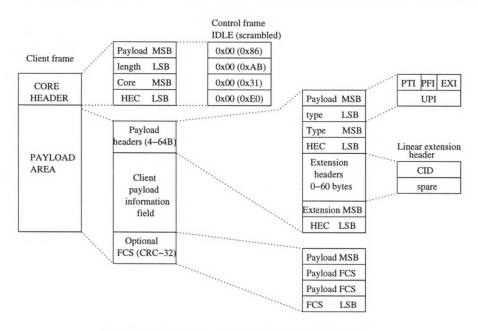

| 7.11 | The structure of the GFP frame                                    | 83 |

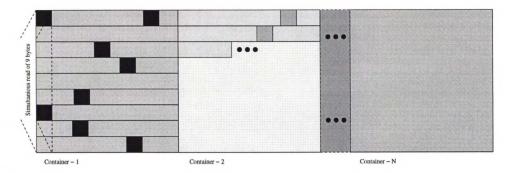

| 7.12 | The mapping of different frames into SDH containers               | 84 |

| 7.13 | The structure of the Virtual Concatenation Group (VCG) -memories. | 84 |

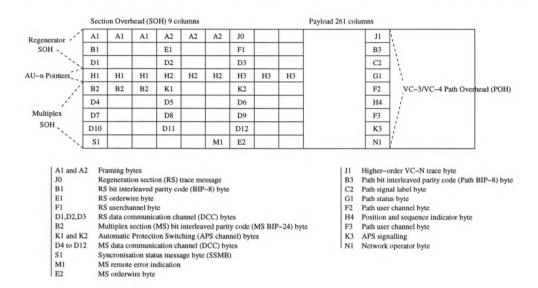

| 7.14 | The structure of the STM-1 frame                                  | 86 |

| 7.15 | The signals in the parallel TelecomBus interface                  | 87 |

## **List of Tables**

| 2.1        | Communication network characteristics in comparison                                                               | 4        |

|------------|-------------------------------------------------------------------------------------------------------------------|----------|

| 2.2        | The transmission speeds and frame period for the optical transport units in OTN                                   | 20       |

| 2.3        | Improvements in bit error rate (BER) when using forward error correction (FEC) in OTN                             | 21       |

| 3.1        | Virtual concatenation compared to contiguous concatenation                                                        | 35       |

| 4.1        | Devices attached to the OAN prototype node                                                                        | 45       |

| 6.1<br>6.2 | The resources available in the prototype FPGAs Programming tools used in different stages of the OAN design flow. | 55<br>56 |

| 7.1        | The device address spaces in the OAN prototype                                                                    | 69       |

| 7.2        | The address mappings in the Router control block                                                                  | 69       |

| 7.3        | The address spaces of the Status/Control register                                                                 | 70       |

| 7.4        | Clock inputs and outputs in the clock controller block                                                            | 71       |

| 7.5        | The control sequences for packet transportation inside the OAN                                                    |          |

|            | design                                                                                                            | 79       |

| 7.6        | Byte basis control code for Pre-TelecomBus interface                                                              | 88       |

## **Chapter 1**

## Introduction

The continuing development of computing and memory management capabilities of computers has brought out new challenges to networking technologies. The bandwidth is no longer a problem, but today it is the network management and more importantly the availability of new type of services, real-time and streaming media. The increase in bandwidth together with developments in end-user equipment, especially in wireless one, has encouraged researchers to find new ways to utilise this emerging possibility in communications. However, the quality of connection in two-way communication is sensitive for the end-to-end transmission delay. Today, most of the datacom networks suffer from long delays and especially from high packet delay variation, which makes the current situation even worse.

Enabled by the technologies already developed, the transfer speed in a point-to-point connection can be almost as high as we like. Point-to-point connections are used as building blocks of larger networks and the sufficient connection bandwidth is determined within the network. The available capacity of point-to-point connection can be most efficiently utilised in Wide Area Networks (WANs) and Local Area Networks (LANs), where the traffic is processed transparently leaving the technology specific processing for Metropolitan Area Networks (MANs) to handle. Most of the used telecommunication technologies come across in MAN, where a variety of conversions are needed between them. These conversions are slow and complex and have slowed down the development of metropolitan area networking, while other areas of networking have experienced major improvements. This is why the present MAN can be seen as a bottleneck for the transfer speed of the whole network [Inc02c].

#### 1.1 Motivation

The National technology agency (TEKES)-funded project called Optical Access Networking (OAN) <sup>1</sup> is a three-year project with several participants. The goal of the project is to implement a test network for development of new metropolitan area services and network structures. In this project, most of the test network functionality will be implemented with programmable logic. Programmable logic devices can be programmed over and over again, which gives much flexibility to the design, because different variations of the programs can be easily tested. In addition, they are large of their size and provide efficient processing abilities for the design. Of course, this is only when these Field Programmable Gate Arrays (FPGAs) are programmed properly, which is my task in this project and more deeply discussed later in this thesis.

#### 1.2 Goal

The goal of this thesis is to identify what kind of requirements the future optical access network gives for the underlying transport network, find ways to support these requirements, evaluate them and provide a Hardware Description Language (HDL) design for the FPGAs in the OAN network prototype.

### 1.3 Structure

After this brief introduction the rest of the thesis will be structured as follows. Chapter 2 introduces the reader to the characteristics of networks today, covering some of the networking history together with key technologies and methods. Chapter 3 carries on the issue and reveals the nature of the future communication networks. After that, in chapter 4 the research project called OAN is presented. Chapter 5 discusses the methodology of HDL-implementation. The options for the OAN HDL design are presented in chapter 6 and the final design in chapter 7. Finally, the conclusions of the thesis are presented in chapter 8.

<sup>&</sup>lt;sup>1</sup>Discussed more deeply in chapter 4

## **Chapter 2**

# **Communication networks today**

The first remarkable development in long distance communication was the invention of optical telegraph in 1791 [Bel03]. Since then, the desire for topical information among people has been fulfilled with the help of inventions like electrical telegraph, telephone, radio and television. In all of these communication methods, the information from sender to receiver is transported over a certain transmission media, usually air or cable and today even optical fibre. The need for transmission media has lead to a development of communication networks, which have now evolved to a situation where three separated networks can be identified: telephony, data communications and broadcast networks [Arm97].

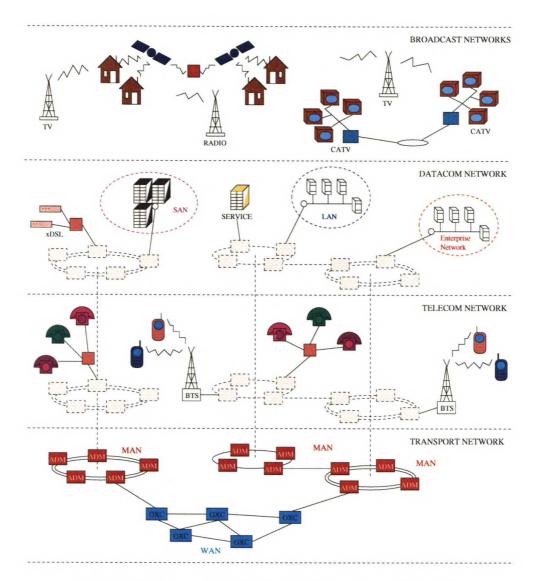

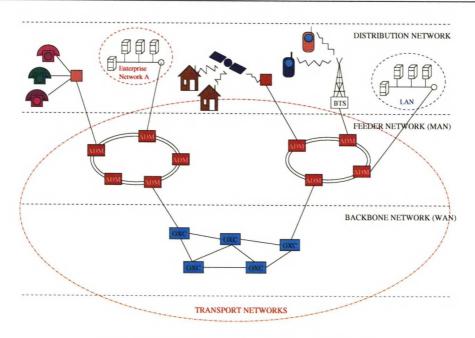

The overlaid structure of the communication networks today is depicted in figure 2.1. From the figure we can see that broadcast networks comprise of separated local and regional networks, which are designed for high downstream bandwidth and limited upstream bandwidth, providing communication from one to many. Because of the nature of the traffic, the bandwidth in datacom and telecom networks is usually the same in both directions. Differently from broadcast networks, telecom and datacom networks have some common parts in their structures. At least the core network is built in a way that both traffics could be transmitted over the same routes, not necessarily over the same physical network. From these networks, the telecom network was the first one to be built and eventually it reached almost every apartment worldwide<sup>1</sup>. Furthermore, the datacom networks exist mainly inside corporations as separated islands, which are then interconnected forming the Internet. The telecom network is mostly used for voice, but more often it is the end-users' only way to access datacom networks. For this reason, the common parts in telecom and datacom transport networks are the interconnections

<sup>&</sup>lt;sup>1</sup>At least this was the case in industrial countries.

Table 2.1: Communication network characteristics in comparison, adopted from [Arm97].

|                                       | Telephone world (com-<br>munication)                                 | Data world (information)                                                                | Radio/TV world (enter-<br>tainment)                                   |

|---------------------------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| Players                               | Telecom operators and suppliers                                      | Computer and software industries, science                                               | Consumer electronics,<br>broadcasters, cable TV,<br>content producers |

| Network<br>coverage                   | Global and ubiquitous (office, home)                                 | Islands, partly intercon-<br>nected (office), Internet<br>worldwide                     | Local and regional,<br>scarcely national and<br>continental (home)    |

| Access<br>media<br>(and<br>structure) | Twisted-pair copper, cel-<br>lular radio (star, circuit<br>switched) | Twisted-pair and coaxial<br>copper, wireless radio<br>(bus or star, packet<br>switched) | Broadcast radio/TV,<br>coaxial copper (tree,<br>non-switched)         |

| Standards                             | International (long-term oriented)                                   | International or de facto<br>(main players and alli-<br>ances)                          | Regional and de facto<br>(main players)                               |

between corporations and the end-user Internet connections. Table 2.1 identifies the most important characteristics of telecom, datacom and broadcast worlds.

The rest of the chapter concentrates on identifying the functionalities of the communication networks today. The main concentration in this contemplation is on datacom networks, because the future communication development is mainly concentrated on this area. The examination is done from a hardware designer's point of view, covering only the lower levels of Open Systems Interconnection (OSI) -networking model [fS94]. Furthermore, telecom and broadcast networks are briefly discussed in various parts of the document.

### 2.1 Access network

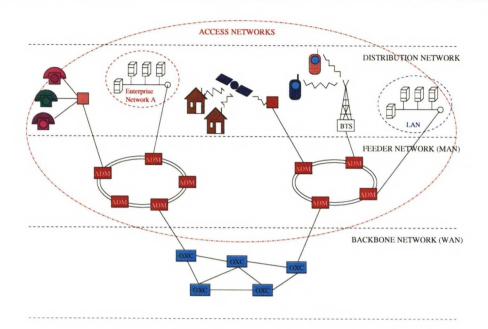

The commonly used definition of access network is described in figure 2.2 [Gro] and the recently proposed interface specification in [MF01]. Access networks collect the small data flows from end-users in the distribution network area, which are then binded into larger flows in the feeder network area. The larger flows are then easier to transport at high speed in the backbone network. This kind of traffic flow behaviour is a result from a centralised service supply. Furthermore, the servers in the Internet are located in certain locations and the end-users need to access the server directly from their home computers. Usually, the end-user who wants to use services from the server are located in another part of the world and

Figure 2.1: The overlaid structure of communication networks.

Figure 2.2: The definition of access network.

thus all of the traffic between the server and the user is transported over the core network. With this solution, almost all of the traffic in data networks will go through backbone networks.

#### 2.1.1 Distribution networks

End-users are connected to worldwide networks over their own distribution networks. They have the possibility to access the core network with variety of different technologies available today. The access network acts as an interface between the end-user equipment and the core network, enabling the conversation between technologies located on both sides. Usually this means that the access network needs to make transport conversions from one technology to another and vice versa. Furthermore, the distribution network has a collecting purpose. For example, all of the data traffic from one building is usually collected and transported further over a single channel.

The local operators, who provide most of the equipment and, more importantly, the physical networks for the end users, control the markets in the access network area. Operators have spent a lot of money laying out the telecommunication networks reaching out to every apartment. Because of that, there is a lot of effort put

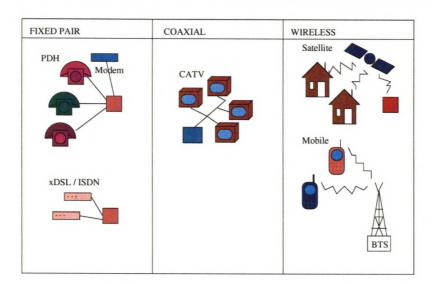

Figure 2.3: Access technologies in today's networks.

in the development of higher transfer speeds in twisted pair networks in order to provide better service to end-users within the existing networks. The efficient use of the old network infrastructure is vital, because in the present financial situation, operators cannot invest much money in building new networks, unless they get the profits from the old networks first.

#### **Technologies**

There is a variety of different technologies operating in the distribution network domain. This is mainly because electrical communication has evolved a lot during the time and most of the older solutions are still in use worldwide. It seems that these older solutions do not vanish at all, although new and more efficient solutions continually emerge to the market. Figure 2.3 presents the three main bases of the public access networks installed worldwide [LDA<sup>+</sup>98].

Twisted pair — This infrastructure was originally installed for Plain Old Telephone Service (POTS) with big financial investments and presents now a large legacy network owned mainly by incumbent operators. However, the digitalisation of this network has commenced in order to support Narrowband ISDN (N-ISDN) and x-Digital Subscriber Line (xDSL) services, which provide a convenient way for the end-users to access the Internet.

- Coaxial These networks were originally installed for Cable Antenna Television (CATV), which are analogue in nature and characterised by tree and branch structure, enabling large downstream bandwidth but limited upstream bandwidth.

- Wireless The wireless transmission is quite new and rapidly growing field in digital communications. The air interface has its own limits to data transfer but the benefits seem to be worth the risk as the Global System for Mobile communication (GSM) has already shown to us. On the other hand, new ways to use the satellite transmission systems have emerged and together with the other systems, the phrase: "Future is wireless" does not seem so impossible after all.

Conversions between technologies are usually needed when small data flows are integrated into larger ones or vice versa. For example, telecom networks use Plesiochronic Digital Hierarchy (PDH) for that purpose. However, problems arise when improvements to transmission efficiency are needed and data flows from different technologies are attempted to converge into the same transmission pipe. This is mainly due to the issue that different technologies need different supporting activities, which cannot be efficiently offered at the same time in the same media. For that reason several transmission paths between the same endpoints are needed to build and maintain, which is of course resource consumptive and expensive.

This is mainly the situation between telecom and Storage Area Network (SAN) traffic or Internet and SAN traffic. For example, if a company has a phone centre, a separate data storage and an Internet connection, all of them need to be transported over separate fibres or cables. As an exception, the Synchronous Digital Hierarchy (SDH) and Synchronous Optical Network (SONET)<sup>2</sup> technologies provide a convenient way to transport Internet and telecom traffic simultaneously over the same media. However, the data storage traffic cannot be transported with the help of SDH. And because of the implementation costs of the SDH technology, it is not suitable to be implemented outside MAN or WAN.

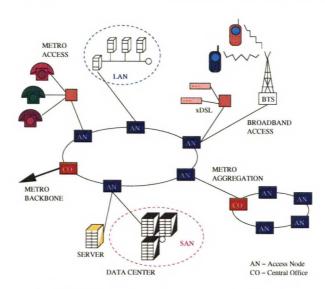

Figure 2.4: MAN traffic characteristics today.

#### 2.1.2 Feeder networks

A typical MAN in today communications networks acts like a feeder network. The MAN has both an abstract and a specific definition, which are both defined in [Net03] with the following phrase:

"Conceptually, the MAN is a set of networks that work together to provide access and services in a metro region. Specifically, a MAN is a single, separate, identifiable "metro area network" that is owned and run by a single network operator, usually a service provider or carrier."

MANs collect the traffic from access networks and then feed it to the backbone network. The traffic in a MAN is typically transparent from access to access, from core to access or from access to core network. Herein the Access Nodes (ANs) are only responsible for separating the incoming and merging the outgoing traffic flows from and to the metro transport pipe. Sometimes, certain Interworking Functions (IWF) may be needed to convert different technologies between each other. Furthermore, Central Offices (COs) act as connection points between other MANs or backbone networks. This behaviour can be seen in figure 2.4, which also presents the different types of access traffic in MANs today [Inc02c] [Mol88]. The different types of traffic in MAN are more deeply discussed later.

<sup>&</sup>lt;sup>2</sup>International Telecommunication Union, Telecommunication standardisation sector (ITU-T) has defined the SONET to be a subset of SDH, the acronym SDH is used in the rest of the thesis to refer both SDH and SONET.

#### Services

In order to function properly MAN has to offer certain services for access network technologies. First of all, the network configuration needs to be flexible, so that the changes in the network structure<sup>3</sup> can be managed quickly and without disturbing the traffic flow. At the same time the available bandwidth is allocated between different traffic flows in a way that data will not overflow in buffers and the utilisation of the bandwidth is as high as possible. In addition, several other services are provided depending on the MAN traffic type, presented in figure 2.4, and the following will list few of them [CSK88] [MHPG91].

- Metro access This category includes variety of technologies, ranging

from newly developed wireless technologies to older ones, which were used

already in the early days of communication networks. From MAN, these

technologies require the following services: LAN interconnection, support

for voice, connection-oriented or connectionless services, switched or nonswitched networking between hosts, broadcast and multicast traffic.

- Broadband access This category includes more recent technologies, specialised in one or two way broadband transmission. The broadband transmission technologies over cable (CATV) or fixed pair (xDSL) are older than these newly developed wireless technologies, now emerging to market. Technologies in this category need multimedia, security and mobility enabling services from MAN.

- Metro aggregation This category includes all the traffic between different MANs. This traffic is usually transported over a single pipe, where bandwidth allocation together with traffic monitoring services is required. This stands for both, incoming and outgoing traffic.

- Data centre Technologies in this category are specialised in data processing and data storage. Corporations use data centres and for that reason they require secure and fast connections from and to MAN. In today's networks, connections to data centres use separated fibres, providing low delays and high bandwidths. The server traffic is more one way, from servers to end-users and is not so sensitive for delays.

- Metro backbone This is the interface from MAN to backbone network. The traffic type here is similar to the connecting traffic between MANs, but it usually requires more bandwidth. For that reason the technologies used

<sup>&</sup>lt;sup>3</sup>Adding and removing of nodes, fibre cuts or other errors.

Figure 2.5: The definition of transport network.

here may differ from the technologies used connecting MANs. Depending on the technology (SDH, Asynchronous Transfer Mode (ATM), Packet Over SDH (POS), Dense Wavelength Division Multiplexing (DWDM)), bandwidth allocation and other higher layer management task are needed to support.

One important concept in data networks is the Quality of Service (QoS), which has attracted lots of discussion and is coming more important every day. It is a concept by which applications may indicate and even negotiate their specific service requirements to the network. Furthermore, the purpose is to define ways to guarantee certain delay and bandwidth limits for networking equipment [GJS03]. The need for QoS in networking emerges from the fact that the default service in many packet networks has been the best-effort service, where all applications get the same service. Now the amount of data traffic has increased and it is used in new ways. At the moment, the lack of strict delay and bandwidth guarantees prevents the connectionless transport to emerge into new areas.

## 2.2 Transport networks

The traffic characteristics in MAN and WAN differ from each other in transfer speed, connection distances and in service models. Still the transport network covers both of these areas, as depicted in figure 2.5. This is because the nature of transport networks is to provide fast data transfer activities, needed in both MAN and WAN. Furthermore, the transport network does not include services other than formed from the need to transfer data efficiently and error free from point-to-point. For this reason, the access network services provided by MAN are part of the feeder network functionalities, splitting the functionalities of MAN between transport and feeder networks.

Transport networks today are mainly optical and their bandwidths depend on the number of light paths included in the system. Adding more light paths into the network, the bandwidth can be increased enormously and the only limit seems to be the price of the equipment. However, these kinds of systems have just emerged to the markets and used mainly in the core network area. Furthermore, the most important transport networks, optical networks are more deeply discussed in section 2.4. In addition, high-bandwidth satellite connections can be used to transport data traffic as well.

#### 2.2.1 Data centric services

In order to transport traffic efficiently, certain transporting functionalities are needed from the underlying network. As transport networks are composed of point-to-point links, the transporting functionalities they provide are mainly concentrated on monitoring the link state and the traffic flow. Herein the transported data flow is transferred as it is, without deeper processing of its content. Transport networks have their own management functions for network configuration, routing and maintenance. These tasks are responsible for forwarding data packets and directing dataflow towards the receiver. The following list will identify the main functionalities provided by data transporting networks.

• Configuration, routing and maintenance — These activities are responsible for building and updating of routing tables when the network is configured at the first time or when the structure of the network changes. The change in network structure can happen because of a fibre cut or when old nodes are removed or new ones added in the network. After these functions are performed properly, the forwarding of packets will be automatic.

- Packet forwarding This operation is responsible for the forwarding of data packets. In other words, the incoming data packet is transmitted out from a specific port of the routing device. The routing table according to the address of the packet defines the output port.

- **Bandwidth allocation** This activity is responsible for sharing the available bandwidth between connections or data flows. Higher priority flows will have stable connections and lower priority traffic is transported if there is still bandwidth left in the transportation pipe.

- Link monitoring This functionality is responsible for the monitoring of the state of the transportation link between certain end-points. The management application is informed, whenever the link changes it state. The link can have different states or alarms, depending on the used technology.

- Traffic balance This is an important activity when the full bandwidth of the transportation pipe needs to be utilised. Packet oriented traffic is bursty and it is possible that the channel transportation pipe is not wholly utilised all of the time, or the traffic in the channel exceeds the limit reserved for the channel. To keep the pipe full all of the time, the traffic needs to be balanced in an appropriate way.

- Error monitoring usually the transport network tracks the Bit Error Rate (BER) of the transmission path or at least identifies the erred transmission blocks. In some cases, mainly in wireless transfer, the transmission errors can be corrected to a certain point in the receiver side.

#### 2.2.2 Synchronisation

In the past, nodes in the network were connected asynchronously in a way that every node had their own clocks and the traffic in the network was received and transmitted with this clock. This resulted problems, because electricity<sup>4</sup> propagates at a certain speed. Depending on the distance from node to node, the synchronisation of the received data stream according to the receiver clock could be exact, totally out of synchronisation or something in between. If the network is out of synchronisation, it is very probable that the data cannot be read correctly and for this reason, synchronised networks were developed. The synchronisation resulted in better functioning networks and the transfer speed was increased rapidly together with the decrease in network delay. In synchronised networks, the nodes

<sup>&</sup>lt;sup>4</sup>At that time, networks were all electrical.

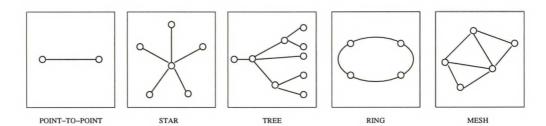

Figure 2.6: Topologies used in networks today.

synchronise their clocks according to incoming data. In the past, networks used general clock distribution as their synchronisation method, but today the Delay Locked Loop (DLL) and Phase Locked Loop (PLL) -methods are more widely used in transport networks world-wide. Together with clock synchronisation the networks need a common frame and network synchronisation methods as well, but these are specified separately within the technology limits [Bre02].

### 2.3 Network topologies

When building a network, you need to keep in mind, that the chosen network structure asserts certain limits for the functionalities that are possible to implement in the network. Although, some of the functionalities can be changed later by installing appropriate network equipment, it is worthwhile to examine different network structures in detail. Network structures are called topologies and today five types of network topologies can be identified: point-to-point, star, tree, ring and mesh. These topologies are all described in figure 2.6.

The basic building block of networks is the point-to-point link, from which all of the other topologies can be built. Network topology can be physical or logical, physical in how it is built and logical in how the network is configured. This phenomenon is used in datacom networks, where the use of a certain logical topology in a certain physical network can significantly decrease the routing effort. One example of separate logical and physical topologies is the Passive Optical Network (PON), where the physical topology of the network is a tree and the logical topology is a star. This way, a good reachability with easy management operations can be exploited. For further information, PONs are more deeply discussed in chapter 3. Furthermore, the characteristics of each of the presented topology are identified in the following list.

• Point-to-point — The point-to-point link is the basic building block of net-

works, where the lower level management and monitoring of network concentrates. The management of a point-to-point connection as such is easy and requires little management traffic. However, this is not the case when several point-to-point connections form a large network, because now the whole network is to be managed.

- Star In the star network, every node can reach all of the other nodes through the central node. This results in good accessibility between nodes, but the downsize of this feature is that the central node needs to be capable of handling all of the traffic in the network. This topology is popular in smaller networks, because it is easy to build and maintain.

- Tree The tree structure is widely used in terrestrial broadcast networks, like the CATV, because with this topology all of the end-users can be reached by simply forwarding the transmission down to the network. This results in a low cost and reliable network, because the forwarding equipment is simple and cheap. When this topology is used for two-way traffic, the upstream bandwidth is shared between all the users and often it is quite limited. On the other hand, the downstream bandwidth can be high, depending on the usage of the network.

- Ring The ring topology is the most popular one in the metropolitan area, because it provides good survivability features and spreads over a large area providing good base for the access networks.

- Mesh Nodes in the mesh topology have great amount of routes from one place to another and this results in a very complex network structure, especially when the amount of nodes is high in the network. In this structure, protection and accessibility levels can be high when appropriate routing methods are used. However, finding or developing these methods is a very demanding task and usually results in complex solutions.

## 2.4 Optical Networks

From the early 1980's, the telecommunication networks have evolved from asynchronous to synchronous and then optical, still trying to reach for all-optical techniques. SDH was the first functional optical network in the telecom driven industry. Now after two decades from its development this network is responsible for most of the transferred telecommunication traffic worldwide. However, it does

not support the transfer speeds typical to the core networks, and other technologies are needed for the purpose. Recently developed optical signal amplification and Wavelength Division Multiplexing (WDM) have revolutionised long-distance transport, resulting in capacity expansion, cost reduction and operations simplification in core networking [ASFG<sup>+</sup>98].

WDM is a technique where several light paths can be transported simultaneously in one fibre. This technique is already widely tested and implemented in the most important parts of the core networks. It seems that, in the future, this technique will be widely implemented in the other parts of the network as well. However, the complexity of the network management operations increases as the number of light paths in the network increases. This means that the cost of management is high, when there are a great number of light paths implemented in the WDM network. For this reason, the WDM is usually used to increase the capacity of the bottleneck links only. To ease the management operations in the WDM network, the concept called Optical Transport Network (OTN) has been developed. OTNs are WDM networks that have both, traffic and light path management systems implemented. There is a lot of flexibility how these OTNs can be deployed, depending on the transport services to be provided [Cav00]. Furthermore, the next three sections will give a more detailed presentation about the SDH, the WDM and the OTN technologies.

#### 2.4.1 Synchronous Digital Hierarchy (SDH)

SDH was originally designed to replace PDH based networks in transmission of connection-oriented telecom traffic in the beginning of 1980's. At that time the connectionless packet traffic was not common and nobody expected that this situation would change much in the future. During the following years, SDH networks were widely implemented all over the world and SDH is now the most popular network technology used today. However, the nature of the data traffic has changed since the early days, and the optimisation of SDH networks to better support the connectionless data transfer has been a major issue during past few years. The reason for this development is the goal to provide better QoS for the emerging multimedia and real-time services.

The functionality in SDH is based on synchronised and standard sized frames, where the data packet or data stream can be inserted in any part of the frame, pointing its start with a specific pointer [Tek01]. This structure allows efficient monitoring and management functionalities to be implemented and transported inside SDH-headers. Furthermore, these headers give only three percent of extra

overhead to the transport. The pointer-processed insertion of data packets or data streams allows the frames to be filled wholly and no empty space is left between packets in the frame. In addition, SDH has its own hierarchical system of how different transmission technologies are inserted, first into containers and then into the SDH-frame [Gor00]. SDH supports electrical and optical transport, but the management of the network is done electrically.

From the network owner, the operators, point of view the optimisation of the old networks to better support the new requirements has been a major goal for their development tasks. Their purpose is to save expenses by exploiting old network infrastructure as much as it is possible. At the moment, it seems that this stands for the survival of SDH networks in the future. There are some advantages in the SDH technology already. It provides very efficient transport services and is the only one available today to transmit connection-oriented telecom traffic in its delay limits, allowing simultaneous connectionless transport. The hierarchical frame structure of SDH enables bandwidth allocation and management between several users, although the legacy contiguous allocation is not so efficient in allocation granularity [OSG02].

#### Packet over SDH (POS)

Clearly the development of networking has shown that the Internet Protocol (IP) packets would be the most popular form in transporting data in the networks. Few years ago somebody suggested that the most efficient way would be to transmit IP packets directly over fibre, without the complex OSI layer structure. After this the whole industry was talking about "IP-over light" and other synonyms for that. The more optimistic ones actually believed that this hype could be the truth after a few years of research [MBK01]. However, the research efforts made for the goal showed that it was not possible to have efficient transport of traffic without the functionalities provided by these OSI layers [BRM01] and the matter was soon forgotten. However, the discussion brought more attention to the already available IP over fibre techniques, especially easy to use IP over SDH techniques. These are briefly presented in the following list.

• IP over SDH — This technique enables the direct transport of IP-packets (Point-to-Point Protocol (PPP) in High level Data Link Control (HDLC) frames) over SDH-link. The transported IP-packet is mapped into a container, which is then inserted into an SDH-frame. This operation does not interfere with the other ongoing transporting actions, allowing other SDH transport as well.

- IP over ATM over SDH This technique works similarly as the former one. The difference here is that first the IP-packet is mapped into ATM-frames, which are then mapped into SDH frame. With this method, a lot of bandwidth is lost into overhead, caused by ATM-headers. As a result, reliability and other functionalities of the ATM can be integrated into SDH. Still, because of the overhead, the efficiency of this method is low.

- **IP** over Ethernet over SDH In this technique ATM is replaced with Ethernet. The use of Ethernet over SDH requires less overhead than the use of ATM over SDH. On the other hand, the services provided by the Ethernet are not as efficient as the ones, provided by ATM. However, Ethernet fulfils the requirements for normal transporting operations quite well.

#### 2.4.2 Wavelength Division Multiplexing (WDM)

One of the research trends in today's networking is the development of all-optical network components and structures. This is an area, where a lot of development is needed before the final equipment can enter the markets. Before all-optical technologies, the WDM technology is the way to exploit the huge opto-electronic bandwidth mismatch in networking. WDM uses a technique called multiplexing, which is defined in [BP01] with a following phrase:

"Multiplexing is the simultaneous transmission of different messages over the communication network through a partitioning of the available bandwidth or other resource".

There are two types of multiplexing used in optical communication, Time Division Multiplexing (TDM) and Frequency Division Multiplexing (FDM), where the FDM is the method used in WDM. With the help of TDM, slower flows can be multiplexed consecutively into one light path, which is then easier to transport at higher speed. After TDM, WDM is used to multiplex the different light paths into the same fibre [Muk97].

By this way, multiple end-users may all have their own channels through a single fibre and the bandwidth of the network can be increased easily. Today the WDM technique is already widely used in core networks, and it is emerging into the MAN area as well. With the help of WDM the available bandwidth now exceeds the limit of 1 Tbps. The price of the WDM system is composed mainly of the number of optical channels needed, because every light path needs its own electrical and optical equipment and their management is complex [Muk97]. For this reason, the cost of the equipment exceeding the transfer speed of 1 Tbps is high.

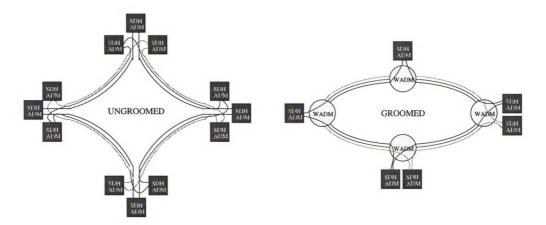

Figure 2.7: Traffic grooming in WDM networks.

#### **Traffic Grooming**

At the moment, it seems that WDM systems will be more widely utilised in networking in the future. This means that the number of light paths in the networks is going to increase, which increases the network complexity as well. The increased complexity brings new concerns into routing and network configuration tasks, and new solutions are needed in that area. In addition, every light path needs it own conversion equipment to convert the data from optical to electrical and vice versa. This equipment is relatively expensive, and it is good to try to decrease the number needed. Usually, there is no need to have a connection between each of the nodes in the network. The complexity of the network could be decreased for example by providing certain light paths between certain nodes, leaving some light paths unconnected. By this way the network could be divided into different logical topologies, independently from the physical topology. This manipulation of network light paths is called grooming and it is defined in [BP01] with the following phrase:

"Grooming is an industry term used to describe the optimisation of capacity utilisation in transport systems by means of cross-connections or conversions between different transport systems or layers within the same system".

With the help of grooming, the network could be optimised according to capacity utilisation or the number of Add Drop Multiplexers (ADMs) needed in the network. As an example, most of the traffic in ring network travels through consecutive nodes, which are only responsible for the retransmission of the traffic. The ungroomed situation of an example ring network is presented in the left side of figure 2.7. After grooming, few of the ADMs can be removed and the complex-

Table 2.2: The transmission speeds and frame period for the optical transport units in OTN.

| <b>Optical channel Transport Unit</b> | Line Rate/Mbps | Frame Period/ms |

|---------------------------------------|----------------|-----------------|

| OTU1                                  | 2666           | 48,971          |

| OTU2                                  | 10709          | 12,191          |

| OTU3                                  | 43018          | 3,035           |

ity of the network is decreased. This groomed situation is presented in the right side of figure 2.7. The extend of how much ADMs can be saved with grooming depends on the capacity needed between different nodes in the network. This needs to be considered separately in every case. However, the optimisation task becomes quite complex when the size of the network increases. For that reason, new algorithms for the optimisation task are continually been developed [LGP01]. In addition, grooming includes optimisation of multiple transport systems<sup>5</sup> and multiple layers of a single transportation system [BP01].

#### 2.4.3 Optical Transport Network (OTN)

As discussed before, SDH cannot fully exploit the possibilities of the WDM technology. To ease the management tasks in WDM networks, ITU-T study group 15 has defined a new set of recommendations for optical transport networking [IT00b]. These include architectural, interfacing and management issues and from now on, I will apply to all them with the term Optical Transport Network (OTN). OTN has many similarities with SDH, like the hierarchical structure and frame format. This makes sense, because the OTN is an improved version of SDH and regarded as a lifeline to increase the capacity in the future networking [Tec]. Currently, there are three optical line rates defined for OTN, presented in table 2.2. The management of optical channels is the most important improvement in OTN. Furthermore, it has another new feature implemented in it, the Forward Error Correction (FEC).

When the line rate of a certain optical channel is increased, the BER of that channel will most probably increase too. This is because of the dispersion effect in fibres, caused by their physical characteristics. If the BER of the connection increases, more efficient error correction mechanisms will be needed to provide the same reliability as before. FEC is just the method for the purpose, although it

<sup>&</sup>lt;sup>5</sup>Where the technology can be electrical, optical or microwave.

Table 2.3: The improvements in bit error rate (BER) when using forward error correction (FEC) with the Reed-Solomon RS(255,239) coding, adopted from [Tec].

| <b>BER</b> without FEC | BER with FEC          |

|------------------------|-----------------------|

| $10^{-4}$              | $5,0 \times 10^{-15}$ |

| $10^{-5}$              | $6,3 \times 10^{-24}$ |

| $10^{-6}$              | $6,4 \times 10^{-33}$ |

brings some amount of overhead into the transmitted frame. At the maximum, the code used in OTN can fix eight simultaneous errors and detect 16 simultaneous errors. This is when the Reed-Solomon RS(255,239) code is used [Tec]. The improvements in connection BER when this code is used are presented in table 2.3.

## 2.5 Survivability

The importance of survivability in networking has increased over the years and today the survivability issues are taken into account already in the network designing stage [DGA+99]. When designing survivable networks, the ideal goal is to achieve maximum survivability with minimum recovery time while maintaining the maximum resource utilisation. However, all of these goals are difficult to attain at the same time and usually some trade-offs between these goals are needed [ZD02]. Furthermore, the network structure, transmission media and the transmission technology together have their own effects for the survivability and all of these are needed to take into consideration when the network is designed. In addition, the cost of protection<sup>6</sup> could also be considered.

There are various protection mechanisms used in networks today. However, many of these can be used only with certain technology and in certain network structures. This decreases the number of available protection solutions and simplifies the survivability planning of networks. Furthermore, when designing the survivability scheme, we need to know which of the network layers are responsible for the recovery of each failure. Usually the recovery is designed to be quick enough so that the upper layers of the network do not even notice the failure. This means that the lower layers need to handle the protection, restoration and possible data losses in a very short period of time. This can happen only when the protection

<sup>&</sup>lt;sup>6</sup>Bandwidth efficiency and equipment costs.

scheme is fully planned in advance [DGA<sup>+</sup>99].

Protection is the primary mechanism used to deal the failure. After the protection function is completed, restoration is used to provide new routes or additional resilience against further failures before the first failure is fixed [GR00]. Protection mechanisms can be divided into electrical and optical protection, which both can be divided into link or path protection mechanisms. At the moment, the communication development is concentrated on optical communication and for that reason, the optical protection methods have experienced great improvements. Furthermore, the optical protection mechanisms can be faster than the electrical protection mechanisms, but more important is that some optical methods can be used passively, requiring cheaper and less complex devices. This is why the optical protection is coming more popular in networking.

# **Chapter 3**

# Communication networks tomorrow

In the future the networks are heading towards flexibility and scalability enabling new ways for interoperability. The reason for this development can be derived from the overlaid network model, presented in figure 2.1, and from the emerging new services, which require more speed and new supporting functions from the underlying networks. This means that the traffic in communication networks is once again changing its characteristics. Previously, the change was from connection-oriented to connectionless transportation, but now a third type of traffic is emerging, called the real-time traffic [And02]. The real-time traffic has some of the features from both of the connectionless and connection-oriented traffic, but still the current network structure prevents the efficient transport of this traffic. Furthermore, all of these three network types need to co-exist in the networks. This together with the issues discussed in chapter 2 is pushing the development of communication networks towards convergence. The main target of discussion in this chapter is the characteristics of converge networks.

The problem in today's networks lies in the metropolitan areas, where the complexity of access networks is a real problem. The great number of different accessing technologies has been the reason for slow development in metropolitan area networking for a long time. This is a real problem, because the legacy network structure cannot provide adequate support for the real-time traffic. It seems that the present MAN structure is not going to survive anymore. In the future, MANs need to be more adaptive and more intelligent and this means modifications and developments to the current networks. For this reason, it is quite clear that the metropolitan and access network areas are going to be a target for major developments and improvements in the near future [LDA<sup>+</sup>98].

The speed of electrical signal processing in today's transport networks is mov-

ing closer to the physical limit of silicon. At the moment, it seems ineluctable that the limit will be reached some day and more advanced systems are needed to develop. The hope for finding faster data transportation methods has increased efforts in the development of all-optical communication solutions, which are considered to be the most technically superior in the long term [LDA+98][YYMD01]. The problem in electrical networking is not the bandwidth, but rather the speed of how many packets can be forwarded in a certain time. However, in all-optical networking the forwarding of packets could be faster, because there is no need for opto-electrical and electro-optical conversions. With WDM we can already easily increase the network link bandwidth to meet our requirements, but the management of large WDM networks is a much harder task and the equipment is more expensive. The cost of the equipment is much lower with optical equipment, especially when passive optical network elements are used. Furthermore, the complexity of the management operations may be decreased with optical networking.

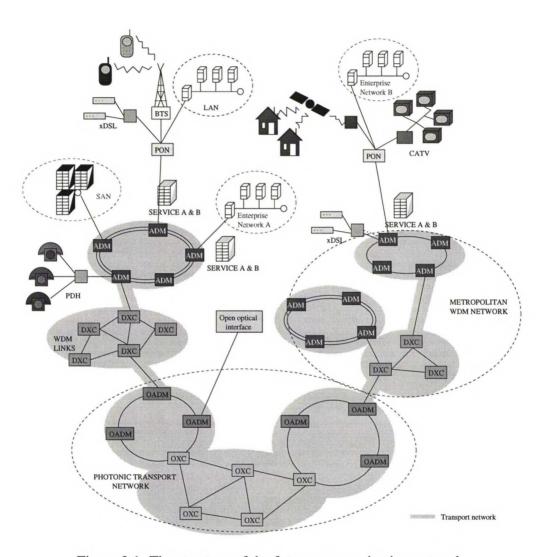

### 3.1 Future characteristics

This section will discuss future network requirements and the realisation strategies concerning future networking in access, metropolitan and core network areas. The areas of research in telecommunications are briefly described together with the requirements and possible solutions for the future networking. The main goal is to find the characteristics of the future data traffic and service functionalities. But first, the most probable structure of the future communication network is illustrated in figure 3.1 [LDA+98][SS99][YJH+00][STS02][Con89] and more deeply discussed later in this section.

Today, the end-user behaviour has greater effect on the network requirements than it has had before. The wireless communication techniques and end-user equipment are developing rapidly, attracting more and more people to buy the equipment and start using the available wireless services. In addition, the amount of data traffic in communications networks will increase continuously, bringing scalability and multiservice requirements to the existing networks. Furthermore, the operators are tired of maintaining overlapping network structures and are ready to invest on converged network solutions to save money from the management operations and concurrently provide better service for end-users. Even more money could be saved with automatic fault tolerant networks, which could use automatic protection and restoration mechanisms for fast recovery after network failure. In addition, automatic switching and network management issues are coming more important also [HM02]. Yet, the end-users and enterprises are more and more

Figure 3.1: The structure of the future communication network.

concerned about the network security and information copyrights. These have developed into a major issue, due to Internet banking and shopping. All this has lead to a desire to develop a new kind of network, where traffic flow between endpoints would happen transparently in a way that the underlying network does not see or process the transported data at all.

Transparent transfer is one of the most often mentioned solutions for the problems in today's networking. This is because the network needs to support different kinds of services with different requirements. So far, providing separate networks for different tasks or technologies has been enough. With the help of transparent transfer, different networks could be integrated into single network architecture. In legacy networks, the transmitted data needs to be processed with required way in every network node and to provide the support for all of the available technologies has been out of the question. The transparent transfer provides a way to transport the traffic through the network without technology dependent processing tasks. This is done by encapsulating the data into certain technology, capable of handling the transportation tasks. ATM is one of the technologies providing transparent transfer. The reason why ATM is not used here is the already laid SDH network structures, which are not capable for efficient ATM-transport. On the other hand, the protection and survivability issues in ATM are not in the same level as in the SDH and the amount of overhead in ATM exceeds the amount of overhead in other networks. At least this is the truth so far. Anyway, the opinions on using ATM or other system as a new transport network vary considerably [Sep02].

#### 3.1.1 Distribution networks

It seems that the number of access technologies is not going to decrease in the future but the opposite. This means that a greater number of conversions between technologies will be needed in the future. Supporting all of the needed interworking functions in the future in access region will result in complexity expansion and problems. This is not desirable, and one way to avoid this is to move the interworking functions towards distribution networks. This means that the transparent transfer will reach the access region as well. Together with this, the amount of bandwidth in access networks is going to increase in the near future when the multimedia services will come into the reach of people. The trend can already be seen as an increase of cable and xDSL connections on the end-user markets. At the moment, the most promising solution to solve the bandwidth increase and the interworking problems seems to be the PON, which allows transparent optical data transfer over MANs with low cost passive optical equipment [Com01]. The idea behind this solution is the passive optical feeder network, which collects the data

from the access domain and feeds it to the transport network for the transmission. The PON technology is more deeply discussed in section 3.2.1.

New wireless transmission techniques emerge to the market continuously. There are multiple developed and yet undiscovered ways to use these new technologies, which is why they are recognised as a part of the future access technologies. In the future, mobile equipment will come more intelligent and the need for bandwidth increases. However, it seems that high-speed transmissions cannot be supported over long distances and the user needs to accept the speed he or she gets. The wireless networking is said to move into a direction where mobile equipment can select the best technology for its purposes from all of the available wireless technologies [Tec02]. This switching between technologies does bring new considerations to wireless security. In addition, operators are searching new ways to exploit the existing CATV networks in data transfer as well.

### 3.1.2 Metropolitan area networks

As discussed before, the metropolitan area networking has been one of the main areas of research. This is because the legacy networks cannot fully support the new transportation requirements. The problem in MAN is the great number of access technologies, which creates complexity. Because of the complex structure, the transport network cannot provide an adequate QoS support. The most popular solution for these problems in the industry seems to be a flexible and scalable optical hybrid network [HV02]. The hybrid network is a network, where one or several transport technologies are supported directly over some other transport system. For example, this is the case in different Packet Over SDH (POS) technologies, where the other technology is supported over SDH. However, the POS solution as such is not flexible and scalable enough, and a scheme called Data over SDH (DoS) is developed for the purpose.

With DoS, the traffic flow between end-points will happen transparently, enabling more flexible transport with dynamic resource allocation and with the base for present and future services [GRF02]. It has a simple layered structure, which on the other side interfaces with access network technologies and on one side with transport network technologies. With this flexible interface, a variety of technologies could be transported simultaneously over a single transport network. This solution will decrease the amount of physical connections needed in networks, because now the telecom, SAN and datacom traffic can be transported simultaneously over a single fibre [MYMN02]. The DoS scheme is more deeply discussed later in the thesis.

Although the execution of interworking functions is moving towards distribution networks and end-user terminals, certain services still need to be supported in MAN level. One aggregate of these services is the network security, where the Virtual Private Network (VPN) seems to be the solution for enterprise networking and the IP Security (IPsec) a promising new technique to be used elsewhere. Furthermore, intelligent servers have been developed for some time, and when they are to be installed, services will move closer to end-users and there is no need to access them over the core network. This means that copies of the original service will be stored in the areas where the users of that service physically are. This will be responsible for the moving of the traffic from WANs to MANs [Inc02c]. Furthermore the operation of intelligent servers may require other services as well.

### 3.1.3 Transport networks