# HELSINKI UNIVERSITY OF TECHNOLOGY

Department of Electrical and Communications Engineering

30-06-1999 kkö-ja

Vesa Tuomainen

# ANALYSIS OF THREE SINGLE-STAGE CONVERTERS FOR POWER FACTOR CORRECTION

This thesis has been submitted for official examination for the degree of Master of Science in Engineering on June 14<sup>th</sup> 1999 in Espoo, Finland

Supervisor:

leye

Jorma Kyyrä

#### Helsinki University of Technology

# ABSTRACT OF THE MASTER'S THESIS

| Author:             | Vesa Tuomainen                                                        |  |

|---------------------|-----------------------------------------------------------------------|--|

| Name of the thesis: | Analysis of three single-stage converters for power factor correction |  |

| Date:               | 14.06.1999 Number of pages: 67                                        |  |

| Department:         | Electrical and Communications engineering                             |  |

| Professorship:      | S-81 Industrial Electronics and Electric Drives                       |  |

| Supervisor:         | Professor Jorma Kyyrä                                                 |  |

| Instructor:         |                                                                       |  |

In this thesis three single-stage solutions for Power Factor Correction are analyzed. Analyzed topologies are: Boost Integrated with Flyback Rectifier/Energy storage/Dc-dc converter (BIFRED), Boost Integrated with Buck Rectifier/Energy storage/Dc-dc converter (BIBRED) and a modified Dither converter. The steady state equations and operational limits for the converters are deduced. Practical power range and peak current ratings, based on the analysis, are discussed.

Thesis includes design guidelines for high frequency Discontinuous Conduction Mode inductors. A 200 W prototype of BIFRED was built with the help of the design guidelines. The aim of the protype is to verify the steady state analysis and assess the quality of Power Factor Correction of the converter.

**Keywords:** Single-stage, Power Factor Correction, Line harmonics, EN 61000-3-2, BIFRED, BIBRED, modified Dither.

## Teknillinen korkeakoulu

# DIPLOMITYÖN TIIVISTELMÄ

| Tekijä:       | Vesa Tuomainen                                                        |  |

|---------------|-----------------------------------------------------------------------|--|

| Työn nimi:    | Analysis of three single-stage converters for power factor correction |  |

| Päivämäärä:   | 14.06.1999 Sivumäärä: 67                                              |  |

| Osasto:       | Sähkö- ja tietoliikennetekniikan osasto                               |  |

| Professuuri:  | S-81 Teollisuuselektroniikka ja sähkökäytöt                           |  |

| Työn valvoja: | Professori Jorma Kyyrä                                                |  |

| Työn ohjaaja: |                                                                       |  |

Tässä diplomityössä on analysoitu kolmea yksiasteista ratkaisua tehokertoimen korjaukseen. Yksiasteisessa ratkaisussa tehokertoimen korjaus ja teholähteen lähtöjännitteen regulointi pyritään aikaansaamaan yhdellä aktiivisella kytkimellä. Analysoidut topologiat ovat: BIFRED, BIBRED ja modifioitu Dither.

Työssä johdetaan kyseisille topologioille pysyvän tilan yhtälöt ja toimintarajat. Yhtälöiden avulla pystytään määrittäämään mm. topologian ensiöpuolella sijaitsevan energivarastona toimivan ison kondensaattorin jännite kaikissa kuormitustilanteissa. Lisäksi tarkastellaan ratkaisuille sopivaa mielekästä tehoaluetta toimintarajojen puitteissa.

Työssä esitellään myös suunnitteluohjeita korkeataajuisten ja epäjatkuvalla toimintaalueella toimivien kuristimien ja muuntajien suunnitteluun. Työtä varten rakennettiin 200W BIFRED, jonka avulla laskettuja tuloksia, pysyvän tilan analyysin onnistumista ja ratkaisun soveltuvuutta tehokertoimen korjaukseen arvioidaan.

Avainsanat: Tehokertoimen korjaus, yksiasteinen, verkkoharmoniset, EN-61000-3-2, BIFRED, BIBRED, modifioitu Dither

# Preface

I am grateful to Professor Jorma Kyyrä for his valuable advice and support for this thesis. I also want to thank Vlad Grigore, Juha Wallius and the staff of the Laboratory of Power Electronics and Electric Drives for creating a pleasant working atmosphere.

This work was financially supported by TEKES (the Technology Development Centre of Finland), ABB Industry Oy and Efore Oyj.

I express my gratitude to Noora for her loving care, patience and support during my work and also for her enormous work in correcting my English.

Helsinki 14.6.1999

Vera Turminen

Vesa Tuomainen

# **Table of Contents**

| A  | bstract o | of the Master's Thesis                   |    |

|----|-----------|------------------------------------------|----|

| Ti | ivistelm  | a (Abstract in Finnish)                  |    |

| Pr | reface    |                                          |    |

| Ta | able of C | Contents                                 |    |

| Li | st of ab  | breviations and symbols                  |    |

| 1  | Intro     | duction                                  | 1  |

| 2  | Backg     | ground of Power Factor Correction        | 3  |

|    | 2.1 Gener | ral                                      | 3  |

|    |           | definitions                              | 4  |

|    |           | onic standard EN 61000-3-2               | 5  |

|    |           |                                          |    |

|    |           | ve solutions for power factor correction | 7  |

|    | 2.5 Activ | e solution                               | 9  |

| 3  | Some      | single-stage solutions                   | 10 |

|    | 3.1 BIFR  | ED                                       | 12 |

|    | 3.1.1     | General                                  | 12 |

|    | 3.1.2     | Operation                                | 12 |

|    | 3.1.3     | Input stage                              | 14 |

|    | 3.1.4     | Output stage                             | 15 |

|    | 3.1.5     | Calculated results                       | 19 |

|    | 3.2 BIBR  | ED                                       | 21 |

|    | 3.2.1     | General                                  | 21 |

|    | 3.2.2     | Operation                                | 22 |

|    | 3.2.3     | Input stage                              | 23 |

|    | 3.2.4     | Output stage                             | 24 |

|    | 3.3 Modi  | fied Dither                              | 27 |

|    | 3.3.1     | General                                  | 27 |

|    | 3.3.2     | Operation                                | 28 |

|    | 3.3.3     | Input stage                              | 30 |

|    | 3.3.4     | Output stage                             | 32 |

|    | 3.3.5     | Calculated and simulated results         | 33 |

|    | 3.4 Brief | summary of the topologies                | 34 |

| 4  | Practi     | cal design of BIFRED                                              | 35 |

|----|------------|-------------------------------------------------------------------|----|

| 4  | .1 DCM     | boost inductance                                                  | 35 |

|    | 4.1.1      | General                                                           | 35 |

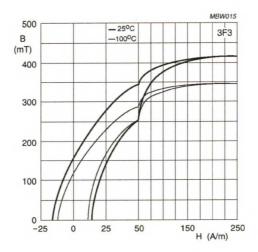

|    | 4.1.2      | Losses in the core                                                | 36 |

|    | 4.1.3      | Core saturation                                                   | 39 |

|    | 4.1.4      | Number of turns                                                   | 40 |

|    | 4.1.5      | Winding                                                           | 40 |

|    | 4.1.6      | Thermal conductivity                                              | 44 |

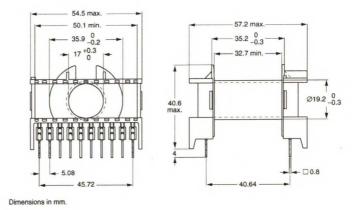

| 4  | .2 Flyba   | ck transformer for BIFRED application                             | 45 |

|    | 4.2.1      | General                                                           | 45 |

|    | 4.2.2      | Losses in the core                                                | 46 |

|    | 4.2.3      | Core saturation                                                   | 47 |

|    | 4.2.4      | Number of turns                                                   | 47 |

|    | 4.2.5      | Winding and winding losses                                        | 48 |

| 4  | .3 Leaka   | ge inductance of the transformer                                  | 49 |

|    | 4.3.1      | General                                                           | 49 |

|    | 4.3.2      | Effect of the leakage inductance                                  | 49 |

|    | 4.3.3      | Proposed solution                                                 | 51 |

| 5  | Proto      | type results                                                      | 53 |

| 4  | 5.1 Gener  | al                                                                | 53 |

| 4  | 5.2 Protot | ype                                                               | 53 |

| 4  | 5.3 Measu  | ured results                                                      | 54 |

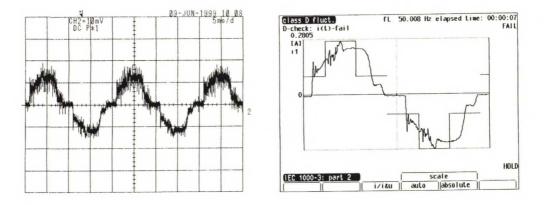

|    | 5.3.1      | Boost inductor current                                            | 54 |

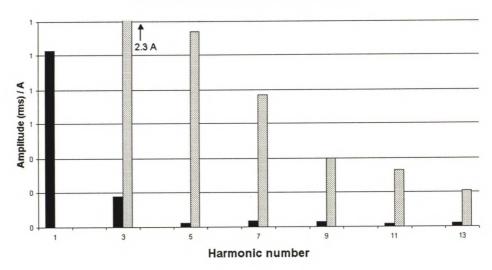

|    | 5.3.2      | Input current and compliance with the standard EN 61000-3-2       | 55 |

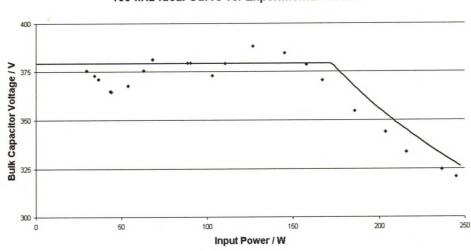

|    | 5.3.3      | Bulk capacitor voltage                                            | 57 |

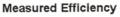

|    | 5.3.4      | Efficiency                                                        | 58 |

| 6  | Concl      | usions                                                            | 60 |

| Re | ference    | S                                                                 | 62 |

| Ap | opendix    | A Values used in the calculations, simulations and prototype      | 64 |

| Ap | opendix    | B Determination of the effective air gap area and number of turns | 65 |

| Ap | opendix    | C Peak flux densities in the magnetic components of the prototype | 66 |

| Ap | opendix    | D Calculated losses in the prototype                              | 67 |

# List of symbols and abbreviations

| $A_{\rm c}$        | Cross sectional area of a ferrite core                              |

|--------------------|---------------------------------------------------------------------|

| Ae                 | Effective cross sectional area of a ferrite core                    |

| $A_{\rm g}$        | Cross sectional area of an air gap                                  |

| $A_{\rm g,e}$      | Effective cross sectional area of an air gap                        |

| $A_{\min}$         | Minimum cross sectional area of the magnetic path in a ferrite core |

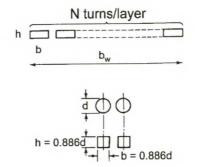

| b                  | Breadth of a bare conductor                                         |

| b <sub>a</sub>     | Length of the center limb of a ferrite core                         |

| $b_{w}$            | Winding breadth                                                     |

| $b_{ m w,min}$     | Minimum winding breadth                                             |

| В                  | Flux density                                                        |

| $B_{\text{peak}}$  | Peak flux density                                                   |

| С                  | Capacitance of a capacitor                                          |

| $C_{\rm oss}$      | Output capacitance of a MOSFET                                      |

| d                  | Diameter of a conductor                                             |

| DPF                | Displacement Power Factor                                           |

| $D_1$              | Duty ratio of an active switch                                      |

| $D_{2,n}$          | Relative portion of the switching cycle when the DCM boost inductor |

|                    | current is decaying from the peak value to zero                     |

| f                  | Frequency                                                           |

| $f_0$              | Resonance frequency                                                 |

| $f_{s}$            | Switching frequency                                                 |

| $F_1$              | Filling factor                                                      |

| Fr                 | Resistance factor                                                   |

| h                  | Effective height of a bare conductor                                |

| $I_{1,\text{rms}}$ | Root Mean Square value of the line frequency component of the line  |

|                    | current                                                             |

| ID                 | Maximum continuous drain current of a MOSFET                        |

| Irms               | Rms value of the line current                                       |

| In                 | <i>n</i> :th harmonic of the line current                           |

| I <sub>DC</sub>    | DC component of a current                                           |

|                    |                                                                     |

| I <sub>D,avg</sub>     | Average current through a diode                                             |

|------------------------|-----------------------------------------------------------------------------|

| IL2,peak               | Peak value of the current through the inductor $L_2$                        |

| $I_{\mathrm{L,avg},n}$ | Average value of <i>n</i> :th DCM boost inductor current pulse              |

| $I_{L,peak,n}$         | Peak value of the <i>n</i> :th current pulse through the DCM boost inductor |

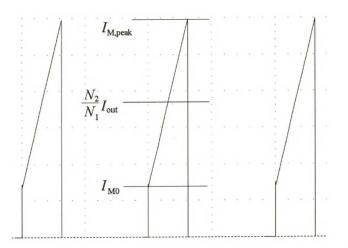

| $I_{\rm M,avg}$        | Average magnetizing current of a transformer                                |

| $I_{M0}$               | Value of the magnetizing current of a transformer at the end of a           |

|                        | switching cycle                                                             |

| I <sub>M,peak</sub>    | Peak value of the magnetizing current of a transformer                      |

| $I_{\mathrm{refl},n}$  | Average value of the n:th reflected DCM boost inductor current pulse        |

| $\Delta I$             | A change in current                                                         |

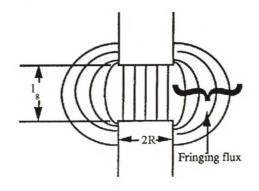

| $l_{\rm g}$            | Length of an air gap                                                        |

| le                     | Effective length of a ferrite core                                          |

| l <sub>m</sub>         | Length of the magnetic path                                                 |

| $L_{\rm x}$            | Inductance of the inductor x                                                |

| $L_{\rm M}$            | Magnetizing inductance of the transformer                                   |

| m                      | Mass                                                                        |

| Ν                      | Number of turns in the winding of an inductor                               |

| $N_1$                  | Number of turns in the primary winding of a transformer                     |

| $N_2$                  | Number of turns in the secondary winding of a transformer                   |

| $N_{1\mathrm{A}}$      | Number of turns in the upper part of the primary winding of a tapped        |

|                        | transformer                                                                 |

| $N_{1B}$               | Number of turns in the lower part of the primary winding of a tapped        |

|                        | transformer                                                                 |

| $N_1/N_2$              | Turns ratio of a transformer                                                |

| р                      | Number of winding layers                                                    |

| Р                      | Power                                                                       |

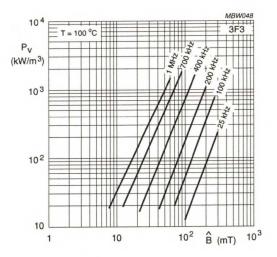

| $P_{\rm h}$            | Power loss in a ferrite core                                                |

| $P_{\rm h/V}$          | Relative power loss in a ferrite core (per volume of the core)              |

| $P_{\rm h,avg}$        | Average power loss in a ferrite core                                        |

| $P_{\rm h,max}$        | Maximum allowed loss of a magnetic component                                |

| $P_{\rm in,avg}$       | Average input power                                                         |

| $P_{M}$                | Average magnetizing power of a transformer                                  |

| $P_{\text{out,C}}$     | Average transferred power supplied by the bulk capacitor                    |

|                        |                                                                             |

| P <sub>out,L1</sub>  | Average transferred power supplied by the DCM boost inductor          |

|----------------------|-----------------------------------------------------------------------|

| $P_{\text{pulse},n}$ | Average power carried by the <i>n</i> :th DCM inductor current pulse  |

| PF                   | Power Factor                                                          |

| R                    | Radius of the center limb of a ferrite core                           |

| $\Delta R$           | An add to the air gap radius due to presence of fringing flux         |

| $R_{\rm DC}$         | DC resistance of a conductor                                          |

| Rs                   | Value of the load resistance in the border of CCM and DCM operation   |

| Rload                | Load resistance                                                       |

| R <sub>th</sub>      | Thermal resistance                                                    |

| 5                    | Apparent power                                                        |

| t                    | Time                                                                  |

| toff                 | Duration when the current through the switch decreases to zero        |

| THD                  | Total Harmonic Distortion                                             |

| Tambient             | Ambient temperature                                                   |

| $T_{\rm core}$       | Core temperature                                                      |

| $T_{\text{line}}$    | Duration of the line cycle                                            |

| T <sub>s</sub>       | Duration of the switching cycle                                       |

| V                    | Volume of a ferrite core                                              |

| $V_{\rm D}$          | Voltage across a forward biased diode                                 |

| Vin, n               | Discrete line voltage                                                 |

| $V_{1,\rm rms}$      | Rms value of the line frequency component of the line voltage         |

| $V_{\rm rms}$        | Rms value of the line voltage                                         |

| $V_{\rm in,peak}$    | Peak value of the line voltage                                        |

| $V_{\rm spike}$      | Peak value of the voltage spike caused by the leakage inductance of a |

|                      | transformer                                                           |

| V <sub>C</sub>       | Bulk capacitor voltage                                                |

| $V_{\rm C,min}$      | Minimum bulk capacitor voltage                                        |

| V <sub>C1b</sub>     | Voltage over the capacitor C <sub>1b</sub>                            |

| V <sub>DSS</sub>     | Maximum drain-source voltage of a MOSFET                              |

| Vout                 | Output voltage                                                        |

| $V_{\mathrm{L},n}$   | Voltage over the DCM boost inductor in de-energizing phase.           |

| $V_{L2}$             | Voltage over the output inductor L <sub>2</sub>                       |

| $ ho_{\rm c}$        | Conductivity of copper                                                |

| μ                  | Permeability                                                    |

|--------------------|-----------------------------------------------------------------|

| $\mu_{ m c}$       | Permeability of copper                                          |

| $\mu_0$            | Permeability of air                                             |

| Δ                  | Penetration depth                                               |

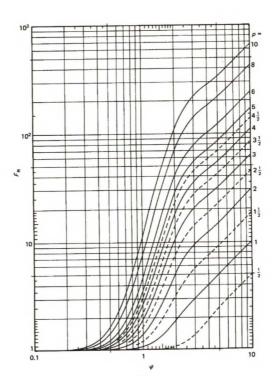

| $\varphi$          | Parameter needed for the Dowell analysis                        |

| $\phi_1$           | Phase difference between the fundamental components of the line |

|                    | voltage and current                                             |

| $\Phi$             | Flux                                                            |

| <br>$arPsi_{peak}$ | Peak flux                                                       |

|                    |                                                                 |

| AC                 | Alternating Current                                             |

| С                  | Capacitor                                                       |

| CCM                | Continuous Conduction Mode                                      |

| D                  | Diode                                                           |

| DC                 | Direct Current                                                  |

| DCM                | Discontinuous Conduction Mode                                   |

| L                  | Inductor                                                        |

| rms                | Root mean square                                                |

| SMPS               | Switched Mode Power Supply                                      |

|                    |                                                                 |

# **1** Introduction

The standard EN 61000-3-2 /1/ sets strict limits for the harmonic content of the input current of a power supply. It is well known fact that input current of a traditional kind of Switched Mode Power Supply (SMPS) has abundant harmonic content. Therefore, need for low cost power factor correction is obvious. Power factor correction can be achieved by passive or active solutions. Passive solutions are usually too clumsy and bulky for small power supplies. On the other hand, active solutions require additional control circuit and switching device, which means increase in costs of the power supply.

Although the name of the thesis includes the words power factor correction it must be emphasized that it is more question of reduction of line current of a rectifier. This should become evident within the thesis.

Single-stage solutions have only one switching stage and consequently only one control circuit. However, despite of only one switching stage they are able to produce an acceptable input current and a regulated output voltage. These features make the family of single-stage converters attractive as low cost solutions for power factor correction. However, single-stage solutions have a few disadvantages such as the rise of the bulk capacitor voltage at light loads. A comparative study was carried out between three single-stage solutions from a practical point of view. The study concentrates on determining the steady state operation of the converters under practical limits such as the upper limit for the bulk capacitor voltage of 450 V. Three topologies were chosen to be evaluated as low cost solutions: BIBRED, BIFRED and a modification of the Dither converter, what we call here as Modified Dither.

The input current of traditional kind of SMPS and standard EN 61000-3-2 are briefly discussed in Chapter two. Two passive solutions and one active solution for power factor correction is shown and discussed. The three single-stage solutions are analyzed in Chapter three. Steady state operation of the converters and particularly the behavior of the bulk capacitor voltage are deduced and discussed. Peak currents and practical power range are also considered. Design guidelines for the magnetic components of BIFRED are provided in Chapter four. Losses in the core and winding, winding arrangements and thermal aspects are discussed. Measured results are included in

Chapter five to support the analysis and to verify that compliance with the standard is achieved. Finally, conclusions are made and topics for further research proposed in Chapter six.

# 2 Background of power factor correction

## 2.1 General

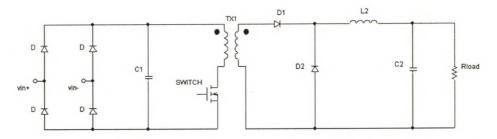

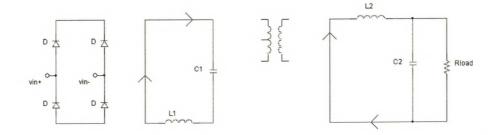

Traditional SMPS, for example the one in Fig. 2.1, has low power factor, which is due to the combination of the diode bridge and the large DC-capacitor  $C_1$ . An ultimate goal of the SMPS is to supply a smooth, regulated and, perhaps, isolated output voltage, which is usually processed from the sinusoidal line voltage. SMPS consist of three parts: an input rectifier, a high frequency inverter and an output rectifier. Purpose of the input rectifier is to convert the sinusoidal line voltage to a DC voltage. The input rectifier is composed of the rectifier bridge and the large DC capacitor. The bridge contains four diodes and the voltages before and after the bridge determine whether a diode in the bridge is able to conduct or not. The capacitor has three tasks to deal with: offer a DC input voltage for the inverter, balance the 100 Hz power swinging of the utility grid and provide an energy storage to cover sudden blackouts of the utility grid (lasting from couple of milliseconds to even tens of milliseconds). A large capacitor fulfills all of the requirements mentioned above because it is able to retain relatively steady DC voltage over itself and store a large amount of energy to cover the blackouts.

Figure 2.1 A forward type SMPS. The diode bridge and the capacitor  $C_1$  form the input rectifier. The SWITCH, transformer TX1 and  $C_1$  form the high frequency inverter. Diodes  $D_1$  and  $D_2$ , inductor  $L_2$  and capacitor  $C_2$  form the output rectifier.

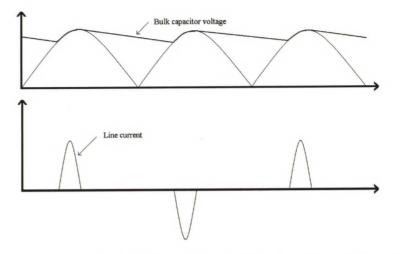

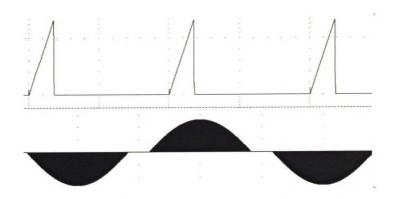

The bulk capacitor  $C_1$  is charged to a voltage level equal to the peak line voltage every half line cycle. Since the capacitor is large in value, the voltage across it droops only a little bit during next half line cycle. On the other hand, the diodes in the bridge are able to conduct only when the line voltage is larger than the voltage over the capacitor. This means that the DC energy being consumed in the load and the energy consumed to losses in the circuit itself, have to be brought into the circuit in a very narrow strip of time, when the diodes are able to conduct. The resulting line current is composed of narrow and high spikes. Rectified sinusoidal waveform, typical bulk capacitor voltage and the resulting distorted line current are presented in Fig. 2.2.

Figure 2.2 Rectified sinusoidal line voltage and a bulk capacitor voltage in the upper picture. The diodes in the bridge are able to conduct when the rectified line voltage reaches the bulk capacitor voltage. Resulting non-sinusoidal line current is shown in the lower picture.

#### 2.2 Basic definitions

SMPS can be considered as a resistive load. Phase-lag between the line frequency components of the line voltage and the current is often negligible. Power factor PF/2/ is defined as the actual power drawn from the utility grid divided by the corresponding apparent power. Power factor is as follows

$$PF = \frac{P}{S} = \frac{V_{1,\text{rms}}I_{1,\text{rms}}}{V_{\text{rms}}I_{\text{rms}}} \cos\phi_1 \approx \frac{I_{1,\text{rms}}}{I_{\text{rms}}} DPF \approx \frac{I_{1,\text{rms}}}{I_{\text{rms}}}$$

(2.1)

where *P* stands for power, *S* for apparent power,  $V_{1,rms}$  for the rms value of the line frequency component of the line voltage,  $V_{rms}$  for the rms value of the line voltage,  $I_{1,rms}$ for rms value of the line frequency component of a line current,  $I_{rms}$  for the rms value of line current,  $\phi_1$  symbolizes the phase-lag between the fundamental components of the voltage and the current and  $\cos\phi_1$  is the displacement factor *DPF*. SMPS is a tiny equipment compared to the utility grid. Line voltage distortion caused by a single power supply is negligible and thus  $V_{rms}$  and  $V_{1,rms}$  are approximately equal. As mentioned earlier, the phase-lag between the fundamental components of the voltage and the current is negligible in a diode rectifier. Therefore, the displacement factor  $\cos\phi_1$  can be omitted and power factor *PF* can be approximated to be the ratio of the rms value of the line frequency component of the current to the rms value of the line current. Another important factor is the total harmonic distortion *THD* /2/. *THD* describes the ratio of the root mean square value of the harmonic currents to the line frequency component of the line current. *THD* is as follows

$$THD = \frac{\sqrt{\sum_{n=2}^{\infty} I_n^2}}{I_1}$$

(2.2)

where the  $I_n$  denotes the rms value of the *n*:th harmonic of the line current and  $I_1$  is the rms value of the line frequency component of the line current.

When the line voltage is not distorted, the power factor and the total harmonic distortion have a relation /2/ as follows

$$PF = \frac{1}{\sqrt{(1 + THD^2)}} DPF$$

(2.3)

Crest Factor /2/ is defined as follows

$$\operatorname{Crest Factor} = \frac{I_{s, \text{peak}}}{I_s}$$

(2.4)

Where  $I_{s,peak}$  is the peak value of a current waveform and  $I_s$  the rms value of the current.

## 2.3 Harmonic standard EN 61000-3-2

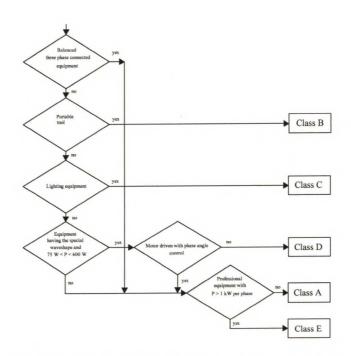

The imminent introduction of the standard EN 61000-3-2 will set strict limits for line current harmonics of SMPS for the power supply manufacturers /1/. Main points of the standard are briefly presented in this chapter. The standard divides electric equipment to five classes: A, B, C, D and E. Selection chart for a class of an electric equipment is presented in Fig. 2.3.

Figure 2.3 Selection chart for a class of an electronic equipment. The chart and thus the standard divides electric equipment into five different classes: A, B, C, D and E, /1/.

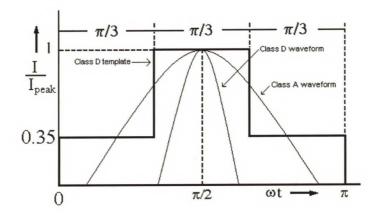

Classes A and D cover single-phase supplied electric equipment in the power range of 75 to 600 W. These two classes are of interest in the thesis. Whether an equipment belongs to class A or D is determined by a special template. The template is depicted in Fig. 2.4.

For the determination one has to set the waveform of a half line current to the template. The highest point of the waveform must coincide with the centerline of the template. If over 95 % of the current lies inside the template then the equipment belongs to the class D. If over 5 % of the current exceeds the template then the equipment is considered to belong to the class A. One must notice that the vertical axis of the template is relative.

Figure 2.4 Special template for the determination whether an electric equipment belongs to the class A or D. Note that the vertical axis of the template is relative, /1/.

Current limits for the class A and D equipment are presented in Table 2.1. The limits are absolute values for the class A and relative for the class D. For example, for a 100 W SMPS the limit for the third harmonic is in the class A is 2.3 A and in the class D only 0.34 A. The class D penalizes high crest factor equipment. One example of equipment, which has a high crest factor, is depicted in Fig. 2.1. Current with high crest factor is known to have a very abundant harmonic content. Since the limits for the harmonic currents are very strict for the high crest factor equipment, it may be difficult to meet the limits with the traditional kind of SMPS. The conclusion is that manufacturers have to add power factor correction into their SMPS's in order to meet the limits set by the standard EN 61000-3-2.

| Harmonic | Class A | Class D      |

|----------|---------|--------------|

| n        | A [rms] | mA [rms] / W |

| 3        | 2.30    | 3.40         |

| 5        | 1.14    | 1.90         |

| 7        | 0.77    | 1.00         |

| 9        | 0.40    | 0.50         |

| 11       | 0.33    | 0.35         |

| 13       | 0.21    | 0.296        |

| 15>      | 2.25/n  | 3.85/n       |

Table 2.1 Limits for the line current harmonics in the class A and the class D. The limits are relative for the class D and absolute for the class A, /1/.

### 2.4 Passive solutions for power factor correction

A passive solution does not have an active switch. The simplest passive solution has an inductor added between the bridge and the bulk capacitor. The schematic of the solution is presented in Fig. 2.5. The inductor tries to spread the current waveform and bring down the peak of the current. If the inductor is large enough, the current will have a desired shape and the equipment will belong to the class A. Drawback of the solution is that the inductor operates at the line frequency. This relatively low frequency means that the inductor is large in value and size. The purpose of SMPS is to be a small size power supply and therefore the large size of the inductor is not desirable and the solution is impractical for low power level equipment.

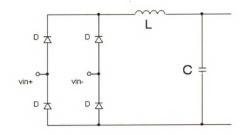

Figure 2.5 A simple passive solution for power factor correction. Inductor L is added between the bridge and the bulk capacitor C.

Another passive solution for power factor correction is presented in Fig. 2.6, /3/. Resonance frequency of the LC filter is tuned to the line frequency. Therefore, the filter represents zero impedance for the line frequency component of the line current and for the harmonics the filter represents a high impedance. Hence, the harmonics are attenuated to some extent. The resonance frequency of the filter is calculated as follows

$$f_0 = \frac{1}{2\pi\sqrt{LC}} \tag{2.5}$$

where the  $f_0$  symbolizes the desired resonance frequency of the filter, L inductance and C capacitance. A few drawbacks are unfortunately found from the solution. For example, if the frequency is chosen to be 50 Hz, the corresponding values for the inductor and the capacitor are (for example) L = 20 mH and C = 500 µF. Again, the inductor is large in value and due to the low operation frequency it is large in size, too. On the other hand, a 500 µF AC-rated capacitor is definitely not an economic solution. It seems that this is not a convenient solution for a low power level equipment either.

Figure 2.6 A passive solution for power factor correction. The LC-filter is tuned to attenuate the harmonic currents and pass the line frequency component of the current, /3/.

## 2.5 Active solution

The most popular way to attain a proper power factor is to add a boost converter between the bridge and the bulk capacitor, /4/. The two-stage solution, as we call it, includes two active converters: one to deal with the power factor correction and another to produce the desired output. The solution is depicted in Fig. 2.7. The boost converter operates at high frequency in order to keep the size of the boost inductor relatively small. There are many control methods for the boost converter found in the literature, /5/. The purpose of the converter, no matter how it is controlled, is to shape the input current of the SMPS to resemble the sinusoidal waveform. The solution is very effective and a unity power factor is almost attained. Drawbacks of the two-stage solution are: an additional switch and control circuit and more complicated circuit structure.

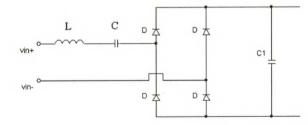

Figure 2.7 Two-stage solution for power factor correction.  $L_1$ ,  $D_1$  and SWITCH form the boost converter. The boost converter shapes the line current to resemble a sinusoidal waveform.

# **3** Some single stage solutions

Single-stage solution is a converter with only one active switching stage, which can be split to several switching devices in order to gain strength against voltage or current stresses, but only one control circuit is included in the converter. Consequently, a single-stage solution has only two operation modes: the switch is turned on or off. Single-stage solutions have two ultimate goals. They try to produce acceptable power factor correction and a regulated and isolated output voltage at the same time. These things are characteristic for them.

Three single stage solutions are presented in this chapter. The basic operation under steady state conditions is described and general equations ruling their behavior are deduced and presented. In the analysis all components of a converter are considered as ideal ones. This means that the conduction and switching losses are omitted and DC voltages throughout the converter do not have a ripple of any kind. The duty ratio  $D_1$  of a switch is assumed to be constant for a certain load. This means that  $D_1$  is adjusted to the constant value in order to get the output voltage  $V_{out}$  as desired.  $V_{out}$  is also considered to have an exact and constant value since one goal of a power supply is to produce the regulated output voltage. An EMI filter is an essential part of the converter. However, it does not have very much effect on the steady state analysis of a single stage converter and therefore it is omitted in the analysis.

In a line cycle there are  $n = T_{\text{line}}/T_{\text{s}}$  switching cycles.  $T_{\text{line}}$  symbolizes the length of the line cycle and  $T_{\text{s}}$  is inverse of the switching frequency. Supposing that the switching frequency is considerably higher than the line frequency, the sinusoidal line voltage can be approximated to be constant during one switching cycle. We can write

$$v_{\text{in},n} = V_{\text{in},\text{peak}} \sin(\omega_{\text{line}} * n * T_{\text{s}})$$

(3.1)

where  $v_{in,n}$  is the approximated constant value of the line voltage during the *n*:th switching period,  $V_{in,peak}$  the peak value of the line voltage,  $\omega_{line}$  the angular frequency of the line voltage. Here *n* ranges from 1 to  $T_{line} / T_s$  and it is assumed that n = 1 when  $0 \le t \le T_s$  and  $n = T_{line} / T_s$  when  $(T_{line} - T_s) \le t \le T_{line}$ , where *t* is time.

Single-stage solutions have only one switching stage and thus only one degree of freedom. However, they should be able to produce an acceptable power factor and a regulated output voltage. It is impossible to control two variables with only one degree of freedom. Consequently, one of the goals has to be achieved inherently or "free of charge". It is a well known fact that the current of a DCM boost converter tracks the feeding voltage waveform, if the switch operates at constant duty cycle, /6/. Good or moderate power factor can be expected if the current through the boost inductor tracks the sinusoidal waveform. Thus, the DCM operation of the boost converter is crucial for the single-stage solutions presented.

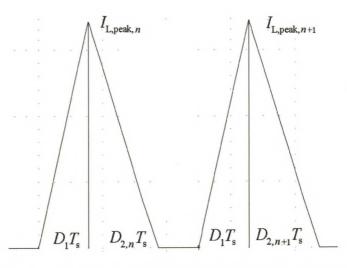

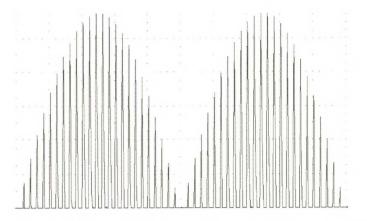

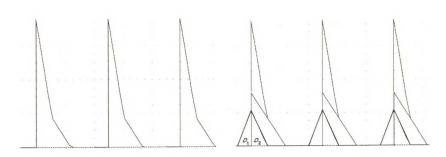

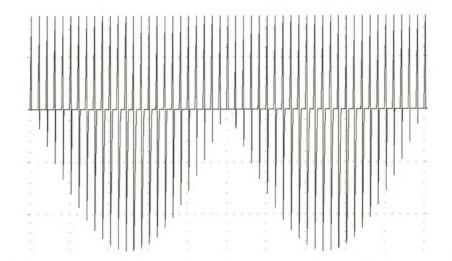

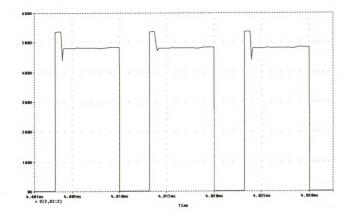

Current through the inductor consists of a sequence of triangular pulses, depicted in Fig. 3.1. Each switching cycle *n* causes a certain current pulse to flow through the inductor. The rise time of the pulse  $D_1T_s$  is constant all the time but the decaying time  $D_{2,n}T_s$  and the height of the pulse  $I_{L,peak,n}$  depend on the switching cycle *n*, which defines the voltage, Eq (3.1). This will be discussed for each topology separately.

Figure 3.1 DCM inductor current. Current pulse developes during  $D_1T_s$  and decays during  $D_{2,n}T_s$ . The width and the height of the current pulse depend on the switching cycle *n*.

The current through the DCM inductor should remain discontinuous, e.g.  $(D_1 + D_{2,n}) \le 1$ . Therefore, the condition  $(D_1 + D_{2,\max}) = 1$  defines the maximum available input power for the converter.  $D_{2,\max}$  denotes the value of  $D_{2,n}$  when  $v_{in,n} = V_{in,peak}$  and it is the critical instance of the line cycle.

In sections 3.1, 3.2 and 3.3 BIFRED, BIBRED and Modified Dither are analyzed respectively. In the following analysis DCM + CCM means that the input stage of the

converter operates in DCM and the output stage in Continuous Conduction Mode. Similarly, DCM + DCM means that both the stages operate in DCM.

#### 3.1 BIFRED

#### 3.1.1 General

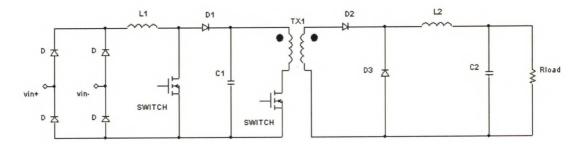

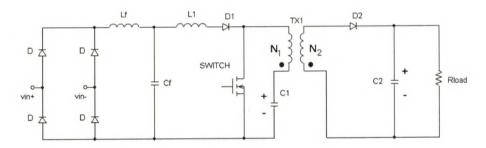

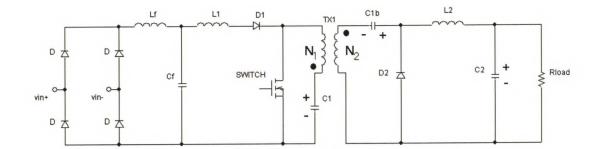

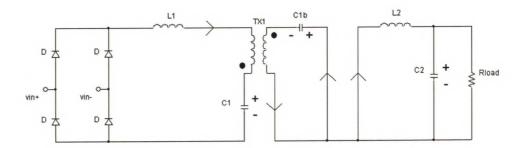

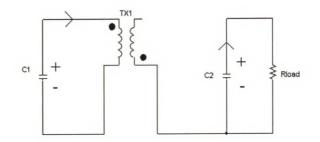

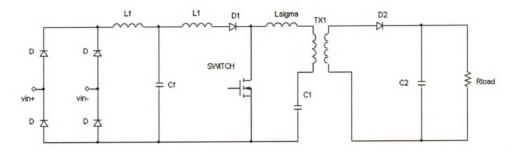

BIFRED stands for Boost Integrated with Flyback Rectifier/Energy storage/Dc-dc converter /7/. The topology is shown in Fig. 3.2. It has only one switching stage and thus it is clearly a single-stage converter. BIFRED consist of three parts: an EMI-filter  $(L_f + C_f)$ , a DCM boost converter and a flyback converter. The converters are little bit overlapped with each other. In the input side, inductor  $L_1$ , diode  $D_1$ , capacitor  $C_1$  and switch form the boost converter. The capacitor  $C_1$ , switch, flyback transformer TX1 and the whole secondary form the flyback converter.

Figure 3.2 BIFRED /7/.  $L_f$  and  $C_f$  form the EMI-filter,  $L_1$ ,  $D_1$  and switch form the DCM boost converter and switch,  $C_1$ , flyback transformer and the whole secondary form the flyback converter.

One essential part of BIFRED is the EMI filter right after the rectifier bridge. The purpose of the filter is to reduce the noise caused by the DCM operation of the boost inductor and to provide continuous line current trough the bridge during a half line cycle. Continuous current enables the use of slow diodes in the bridge.

#### 3.1.2 Operation

BIFRED has two operation modes: switch turned on or off. The operation of the converter in those two modes is briefly described in this section. Current paths for both of the modes are shown and applied voltages explained.

#### 3.1.2.1 Switch on

When the switch is turned on, the line voltage is applied across the DCM boost inductor. The sinusoidal line voltage energizes the inductor and the current through the inductor starts to rise from zero to  $I_{L,peak,n}$ , which is defined as follows

$$I_{\rm L,peak,n} = \frac{|v_{\rm in,n}| D_1 T_{\rm s}}{L_1}$$

(3.2)

where  $L_1$  denotes value of the inductance of the boost inductor and  $v_{in,n}$  is from Eq (3.1). At the same time, the bulk capacitor voltage is applied to the primary winding of the flyback transformer. The output diode  $D_2$  at the secondary side is reverse biased during this operation mode. Peak value of the magnetizing current of the transformer is as follows

$$I_{\rm M,peak} = I_{\rm M0} + \int_{nT_{\rm s}}^{nT_{\rm s} + D_{\rm I}T_{\rm s}} \frac{V_{\rm C}}{L_{\rm M}} dt = I_{\rm M0} + \frac{V_{\rm C} D_{\rm I} T_{\rm s}}{L_{\rm M}}$$

(3.3)

where  $I_{M0}$  is the minimum value of the current after a switching cycle,  $V_C$  is the bulk capacitor voltage which is a constant in steady state and  $L_M$  magnetizing inductance of the transformer. The load draws energy from the output capacitor C<sub>2</sub>.

Paths of the currents during the switch-on mode are illustrated in Fig. 3.3.

Figure 3.3 BIFRED during the switch-on mode. EMI filter is omitted. The rectified line voltage energizes the inductor  $L_1$  and the flyback transformer is energized by the capacitor  $C_1$ . Both of the currents circulate through the switch. The load draws power from the output capacitor  $C_2$ .

#### 3.1.2.2 Switch off

When the switch is turned off, the DCM boost inductor is de-energized. Voltage across the secondary winding of the flyback transformer is fixed to the output voltage  $V_{out}$  and

voltage across the primary winding is the output voltage multiplied by the turns ratio  $N_1/N_2$ . Therefore, the voltage over the boost inductor has the following value

$$V_{\mathrm{L},n} = v_{\mathrm{in},n} - \left( V_{\mathrm{C}} + \frac{N_1}{N_2} V_{\mathrm{out}} \right)$$

(3.4)

until the inductor is de-energize. At the same time, the magnetizing inductance of the flyback transformer reverses its polarity and the diode  $D_2$  becomes forward biased. Consequently, the flyback transformer is de-energized to the capacitor  $C_2$  and the load.

Paths of the currents during the switch-off mode are depicted in Fig. 3.4.

Figure 3.4 BIFRED during the switch-off mode. EMI filter is omitted. Boost inductor  $L_1$  is completely de-energized and the flyback transformer is partly (DCM operation) or completely (CCM operation) de-energized during the switch-off mode.

#### 3.1.3 Input stage

Eq. (3.2) reveals that the peak value of a current pulse is proportional to the discrete value of the line voltage. Peaks of the current follow the waveform of rectified line voltage if the duty ratio is kept constant. The current trough the boost inductor is depicted in Fig. 3.5.

Figure 3.5 The current trough the DCM-boost inductor. Duty cycle is kept constant during the line cycle. The envelope of the waveform greatly resembles the rectified sinusoidal waveform despite of the fact that in the picture the switching frequency is only 50 times higher than the line frequency.

From Fig. 3.5 it is easy to see that the current of the DCM boost inductor does track the rectified line voltage waveform, as was desired. Consequently, a proper power factor can be expected.

Power is transferred to the circuit in triangular current pulses. One pulse carries a power

$$P_{\text{pulse},n} = \left| v_{\text{in},n} \right| I_{\text{L},\text{avg},n} = \left| v_{\text{in},n} \right| \frac{I_{\text{L},\text{peak},n}}{2} \left( D_1 + D_{2,n} \right) = \frac{v_{\text{in},n}^2 D_1 T_s}{2L_1} \left( D_1 + D_{2,n} \right)$$

(3.5)

where  $P_{\text{pulse},n}$  is average power carried by a current pulse,  $I_{\text{L,avg},n}$  the average value of the pulse,  $D_{2,n}$  the relative portion of the switching cycle  $T_s$  when the triangular pulse is decaying.  $D_{2,n}$  is to be calculated as follows

$$D_{2,n} = \frac{\left| v_{\text{in},n} \right| D_1}{V_{\text{C}} + \frac{N_1}{N_2} V_{\text{out}} - \left| v_{\text{in},n} \right|}$$

(3.6)

Eq. (3.6) is based on the fact that the average volt-second balance across the boost inductor should be equal to zero in steady state.

By summing the value of power associated to every pulse during a line cycle and dividing it by the amount of switching cycles, average input power is obtained. Average input power of BIFRED is as follows

$$P_{\rm in,avg} = \frac{D_1 T_{\rm s}}{2L_1} \left[ \sum_{n=1}^{\frac{T_{\rm ine}}{T_{\rm s}}} v_{\rm in,n}^2 \left( D_1 + D_{2,n} \right) \right] \times \frac{T_{\rm s}}{T_{\rm line}}$$

(3.7)

#### 3.1.4 Output stage

The output stage of BIFRED is a regular flyback converter. When the switch is turned on, the bulk capacitor voltage is applied across the primary winding of the transformer as in a normal flyback converter. The flyback part can operate either in DCM or CCM. Because these two modes differ from each other radically, they are considered separately.

#### 3.1.4.1 CCM operation

In CCM the output voltage of the flyback-stage is strictly defined by  $V_{\rm C}$ , turns ratio and duty ratio. That is because the average volt-second balance across the magnetizing inductance of the flyback transformer has to be equal to zero. Hence, the output voltage is defined as follows

$$V_{\text{out}} D_1 T_s = \frac{N_2}{N_1} V_C (1 - D_1) T_s \Longrightarrow V_{\text{out}} = \frac{N_2}{N_1} V_C \frac{D_1}{1 - D_1}$$

(3.8)

If the output voltage is regulated to a constant value, as assumed, the voltage over the bulk capacitor has to be as follows

$$V_{\rm C} = \frac{N_1}{N_2} V_{\rm out} \, \frac{1 - D_1}{D_1} \tag{3.9}$$

Steady state value of  $V_{\rm C}$  is constant in DCM + CCM operation of the converter for a certain load because  $D_1$  and  $V_{\rm out}$  are assumed to be constants. However, if the load is reduced or increased then  $D_1$  has to be adjusted to a new value in order to retain the constant output voltage. Consequently,  $V_{\rm C}$  has also a new steady state value. The voltage over the bulk capacitor depends on the load: if the load is reduced the resulting new steady state voltage is higher than before the reduction and vice versa, if the load is increased the resulting steady state  $V_{\rm C}$  is lower than before the increase.

The minimum value for the bulk capacitor voltage is defined by the peak line voltage  $V_{in,peak}$ . There is a danger, if the  $V_C$  falls below the  $V_{in,peak}$ , that the input stage enters to CCM operation at vicinity of the peak line voltage and DCM operation of the boost inductor is lost while the capacitor is being charged to the peak line voltage. To ensure proper operation of the converter, the condition

$$V_{\rm C,min} \ge V_{\rm in,peak} \tag{3.10}$$

should be fulfilled, where  $V_{C,min}$  is the minimum allowed bulk capacitor voltage.

#### 3.1.4.2 DCM operation

Output stage enters to the DCM operation when the current through the secondary winding of the flyback transformer reaches zero before the end of a switching cycle.

This means that equations (3.8) and (3.9) are not valid anymore and voltage over the bulk capacitor has to be determined from a power balance.

Input power can be calculated as before because the input stage operates in the same way as it did earlier. Power is injected from the primary side of BIFRED to the secondary side in two different ways. First one is the power supplied by the bulk capacitor and the other the power supplied by the boost inductor directly to the secondary side. Both of the ways are discussed below.

In DCM operation of the flyback stage the power supplied by the bulk capacitor  $C_1$  from the primary side to the secondary side is as follows

$$P_{\text{out,C}} = V_{\text{C}} I_{\text{M,avg}} = V_{\text{C}} \frac{I_{\text{M,peak}}}{2} D_1 = \frac{V_{\text{C}}^2 D_1^2 T_s}{2L_{\text{M}}}$$

(3.11)

This is the energy stored in the magnetic circuit when the switch is conducting and it is released when the switch is turned off.

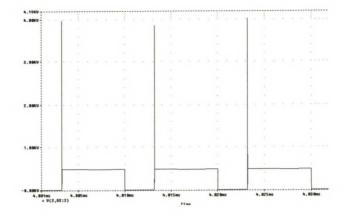

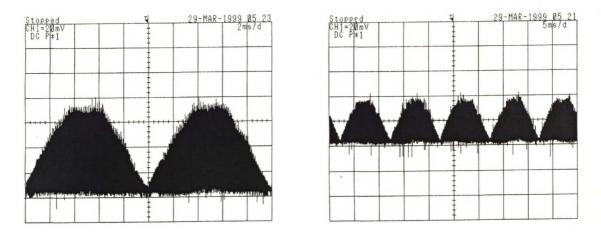

When the switch is turned off the energized boost inductor begins to de-energize to the bulk capacitor *through* the flyback transformer's primary winding as it was depicted in Fig. 3.4. This causes a current, proportional to the decreasing part of the boost inductor current pulse, to flow in the secondary side. Therefore, the current trough the output diode  $D_2$  is a sum of the reflected boost inductor and the 'normal' transformer current. This is depicted in Fig. 3.6.

Average value of the reflected current, for a current pulse, is as follows

$$I_{\text{refl},n} = \frac{N_1}{N_2} \frac{I_{\text{L,peak},n}}{2} D_{2,n} = \frac{N_1}{N_2} \frac{|v_{\text{in},n}| D_1 T_{\text{s}}}{2L_1} D_{2,n}$$

(3.12)

The reflected current carries power, which is delivered directly from the inductor to the output. Average power carried by the reflected boost inductor current pulses is as follows

$$P_{\text{out,L1}} = V_{\text{out}} \sum_{n=1}^{\frac{T_{\text{line}}}{T_{\text{s}}}} I_{\text{refl},n} = \frac{N_1}{N_2} \frac{V_{\text{out}} D_1 T_{\text{s}}}{2L_1} \left[ \sum_{n=1}^{\frac{T_{\text{line}}}{T_{\text{s}}}} \left( v_{\text{in},n} \middle| D_{2,n} \right) \right] \times \frac{T_{\text{s}}}{T_{\text{line}}}$$

(3.13)

It is delivered straight from the boost inductor to the secondary side during a line cycle.

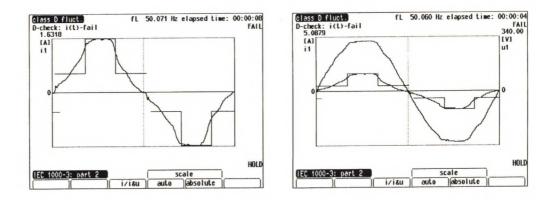

Figure 3.6 Output diode current of BIFRED converter, here in DCM operation. The left picture shows the current and the right picture depicts the same current and its two components: boost inductor current and the de-energizing transformer current. In the figure Boost inductor current is depicted as bolded (almost equilateral) triangle and the normal flyback transformer current is depicted as right-angled triangle. The diode current is sum of the right-angled triangle and right half of the bolded triangle multiplied by the turns ratio.  $P_{out,C}$  in Eq. (3.11) is carried by the right-angled triangles and  $P_{out,L1}$  of Eq. (3.13) is carried by the right halves of the bolded triangles.

Total amount of transferred power from the primary to the secondary is obtained by summing  $P_{\text{out,C}}$  and  $P_{\text{out,L1}}$ . Power balance between the input, Eq. (3.7), and the transferred power is as follows

$$P_{\text{in,avg}} = P_{\text{out,C}} + P_{\text{out,L1}}$$

(3.14)

Placing Eqs. (3.7), (3.11) and (3.13) into Eq (3.14) and reorganizing it, an equation for the bulk capacitor voltage during DCM operation of the flyback transformer is obtained. It is as follows

$$\frac{L_{1}}{L_{M}}V_{C}^{2} + \left[\frac{N_{1}}{N_{2}}V_{out}\sum_{n=1}^{\frac{T_{ine}}{T_{s}}}\left(\frac{v_{in,n}^{2}}{V_{C} + \frac{N_{1}}{N_{2}}V_{out} - |v_{in,n}|}\right) - \sum_{n=1}^{\frac{T_{ine}}{T_{s}}}v_{in,n}^{2}\left(1 + \frac{|v_{in,n}|}{V_{C} + \frac{N_{1}}{N_{2}}V_{out} - |v_{in,n}|}\right)\right] \times \frac{T_{s}}{T_{ine}} = 0$$

(3.15)

Eq. (3.15) indicates that the voltage over the bulk capacitor is only a function of parameters considered here as constants: the circuit parameters, the line voltage and the output voltage. Therefore, the steady state value of  $V_{\rm C}$  is constant in DCM + DCM operation of the converter and the value depends on the load.

Power balance between the power consumed in load and the power transferred to the secondary, for an ideal converter, is as follows

$$\frac{V_{\text{out}}^2}{R_{\text{load}}} = P_{\text{out,C}} + P_{\text{out,L1}}$$

(3.16)

Eq. (3.16) gives power balance between consumption and injection. One can set the desired output voltage by calculating  $R_{\text{load}}$  which gives the desired output voltage

$$R_{\text{load}} = \frac{V_{\text{out}}^2}{P_{\text{out},\text{C}} + P_{\text{out},\text{Ll}}}$$

(3.17)

#### 3.1.4.3 CCM & DCM border

The border between CCM and DCM operation can be defined by comparing the load resistance  $R_{load}$  to a resistance called here as resistance  $R_S$ . The output stage of BIFRED operates in DCM if the actual load resistance is greater than the  $R_S$ . Vice versa, if the load is smaller than  $R_S$  the stage operates in CCM.  $R_S$  is the value of the load resistance when the output stage of BIFRED operates in the border of CCM and DCM operation. It can be deduced as follows:

$$R_{\rm S} = \frac{V_{\rm out}}{I_{\rm out}} = \left(\frac{V_{\rm out}}{\frac{N_1}{N_2} \frac{I_{\rm M,peak}}{2} (1-D_1) + \sum_{n=1}^{\frac{T_{\rm line}}{T_{\rm S}}} I_{\rm refl,n}}{\sum_{n=1}^{N_1} I_{\rm refl,n}}\right) = \left(\frac{V_{\rm out}}{\frac{N_1}{N_2} \frac{V_{\rm C} D_1 T_{\rm s}}{2L_{\rm M}} (1-D_1) + \sum_{n=1}^{\frac{T_{\rm line}}{T_{\rm S}}} I_{\rm refl,n}}}{\left(\frac{N_1}{N_2} \frac{V_{\rm C} D_1 T_{\rm s}}{2L_{\rm M}} (1-D_1) + \sum_{n=1}^{\frac{T_{\rm line}}{T_{\rm S}}} I_{\rm refl,n}}\right)$$

(3.18)

$$= \left(\frac{\frac{V_{\rm out}}{\frac{N_1}{N_2} \left[\frac{N_1}{N_2} V_{\rm out} \frac{(1-D_1)}{D_1}\right] \frac{D_1 T_{\rm s}}{2L_{\rm M}} (1-D_1) + \sum_{n=1}^{\frac{T_{\rm line}}{T_{\rm S}}} I_{\rm refl,n}}\right) = \left(\frac{\frac{V_{\rm out}}{\left(\frac{N_1}{N_2}\right)^2 \frac{V_{\rm out} T_{\rm s}}{2L_{\rm M}} (1-D_1)^2 + \sum_{n=1}^{\frac{T_{\rm line}}{T_{\rm S}}} I_{\rm refl,n}}\right)$$

where  $I_{out}$  is the average current through the diode  $D_2$  in the border of CCM and DCM operation of the flyback stage and  $I_{refl,n}$  is calculated from Eq. (3.12). Eq. (3.18) is based on the fact that in the border of DCM and CCM operation the flyback transformer is completely demagnetized in time duration  $(1-D_1)T_s$ .

#### 3.1.5 Calculated results

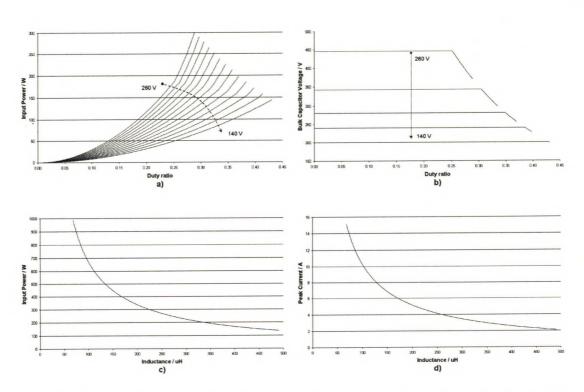

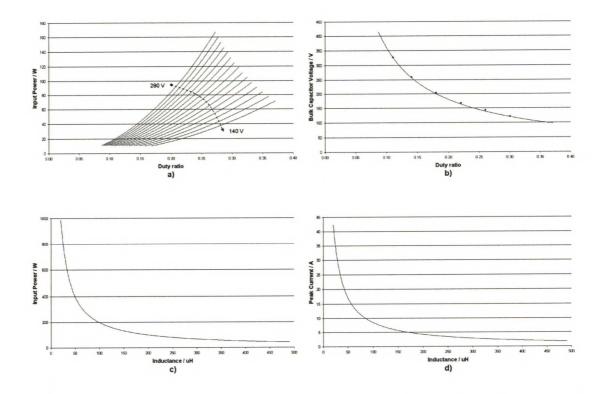

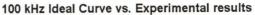

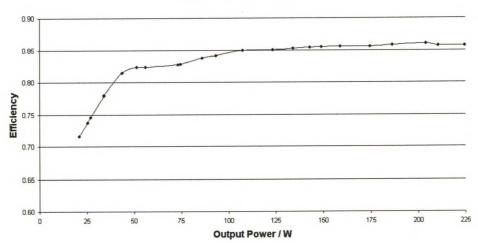

In Fig. 3.7 calculated results of an example of BIFRED are presented. Following values were used in the calculation of Fig. 3.7 a) and b) :  $T_{\text{line}} = 20 \text{ ms}$ ,  $T_{\text{s}} = 10 \text{ µs}$ ,  $L_1 = 250 \text{ µH}$ ,  $L_{\text{M}} = 450 \text{ µH}$ ,  $V_{\text{in,rms}} = 260\text{-}140 \text{ V}$ ,  $(N_1/N_2) \times V_{\text{out}} = 150 \text{ V}$  and  $(D_1 + D_{2,\text{max}}) \le 1$  (Appendix A).

Calculation of Fig. 3.7 c) and d) have been done with the following values:

$$D_1 + D_{2,\text{max}} = 1$$

,  $R_{\text{load}} < R_{\text{s}}$  and  $V_{\text{in,rms}} = 230 \text{ V}$ .

The change from DCM + CCM operation to DCM + DCM operation can be seen clearly from Fig 3.7 a) and b). In the latter one the rise of the bulk capacitor voltage, DCM + CCM operation, ceases to a constant value when the converter enters to DCM + DCMoperation. In the first one curves have a little knee when in the border of the two modes.

The input power curves of Fig. 3.7 clearly show that the available power from the utility grid decreases when the rms value of the line voltage decreases. It happens despite of the fact that the available range of duty ratio of the switch is enlarged at the same time. Consequently, BIFRED cannot be designed for universal input voltage, or it is not practical, if the correct operation mode of the converter is to be retained. Moreover, the bulk capacitor voltage curves show that the with  $V_{in,rms} = 260$  V the voltage is barely below the 450 V limit and with  $V_{in,rms} = 140$  V the bulk capacitor voltage,  $V_C = 199.8$  V, is barely above the  $V_{in,peak} = \sqrt{2} \times 140$  V  $\approx 197$  V. The 450 V limit is due the fact that it is hard to find suitable eletrolytic capacitors for higher voltage ratings. Hence, in order to achieve the correct operation mode, it is required that 140 V  $< V_{in,rms} < 260$  V in this example.

In Fig. 3.7 c) and d) it is shown that, as the value of the inductance decreases, the available maximum power and peak current through the inductor increases rapidly. This means that, perhaps, the practical power range of this kind of converter lies somewhere under 500 W input power. Otherwise, even a few percent inaccuracy in value of the inductance increases or decreases the available power remarkably. On the other hand the peak current becomes relatively high for a low power equipment and this could lead to unacceptable losses in the switch, winding (skin and proximity effects) and core.

Figure 3.7 a) Calculated input power curves of BIFRED as a function of the duty cycle and line voltage as a parameter, ranging from  $V_{\text{in,rms}} = 260 \text{ V}$  to 140 V with 10 V steps. b) Corresponding bulk capacitor voltage behavior for voltages  $V_{\text{in,rms}} = 260, 210, 180, 160 \text{ and } 140 \text{ V}. \text{ c})$ , d) Maximum input power,  $V_{\text{in,rms}} = 230 \text{ V}$ , and corresponding peak current as a function of inductance of the DCM-Boost inductor, respectively.

In the calculation of Fig 3.7 all the equations presented in this chapter were used. Bulk capacitor voltage in DCM + DCM operation was solved from Eq. (3.15) by iteration.

#### **3.2 BIBRED**

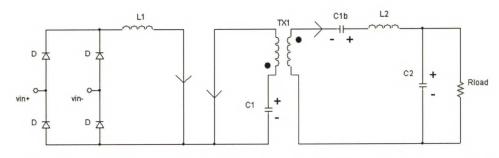

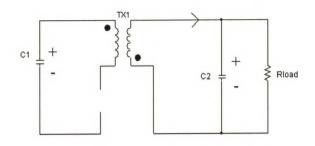

#### 3.2.1 General

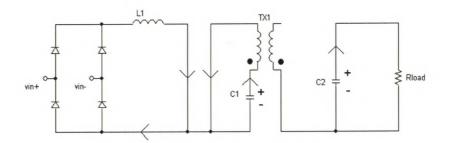

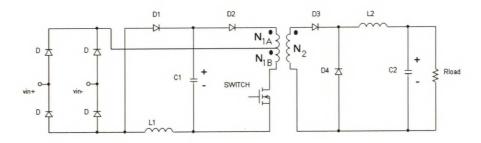

BIBRED stands for Boost Integrated with Buck Rectifier/Energy storage/Dc-dc converter /7/. The converter is shown in Fig. 3.8. BIBRED is quite similar to BIFRED. It is a combination of three parts: an EMI-filter, a DCM boost converter and a forward converter. BIBRED has only one switching stage and thus it is a single-stage solution, too. The input stage is almost identical with the one in BIFRED and consequently the analysis of it is very similar. The power factor correction is achieved by allowing the boost converter to operate in DCM. Duty ratio of the switch is used to adjust the output voltage to a desired level.

Figure 3.8 BIBRED /7/.  $L_f$  and  $C_f$  form the EMI-filter,  $L_1$ ,  $D_1$  and SWITCH form the DCM boost converter and SWITCH,  $C_1$ , transformer TX1 and the whole secondary form the forward converter.

The output stage is a little bit modified forward converter. One of the forward converter's output diodes is replaced by the capacitor  $C_{1b}$ .

#### 3.2.2 Operation

BIBRED has two operation modes: the switch turned on or off. When the switch is on, the line voltage is applied across the DCM boost inductor. At the same time the bulk capacitor voltage  $V_{\rm C}$  is applied across the primary winding of the transformer. Both the resulting currents, the line current and the transformer current, are circulating through the switch. The transformer current is reflected to the secondary, and the reflected current flows through the capacitor C<sub>1b</sub>. Capacitors C<sub>1</sub> and C<sub>1b</sub> are delivering power to the output inductor L<sub>2</sub>, capacitor C<sub>2</sub> and the load when the switch is turned on. Voltage across the inductor L<sub>2</sub> during that time is

$$V_{\rm L2} = \frac{N_2}{N_1} V_{\rm C} + V_{\rm C1b} - V_{\rm out}$$

(3.19)

where  $V_{C1b}$  is voltage over the capacitor  $C_{1b}$ . The two capacitors,  $C_1$  and  $C_{1b}$ , are actually in series during this time. This will be discussed later. The current paths when the switch is turned on are depicted in Fig. 3.9.

Figure 3.9 BIBRED, switch is turned on, EMI filter is omitted. The transformer current and the line current are both circulating through the switch. The current of the transformer is reflected to the secondary side and the output inductor  $L_2$  is being energized.

When the switch is off the boost inductor  $L_1$  is de-energized to the capacitor  $C_1$  through the primary winding of the transformer. The voltage over the inductor  $L_2$  reverses its polarity and it is fixed to the output voltage  $V_{out}$  because the diode  $D_2$  becomes forward biased. The inductor begins to de-energize to the output capacitor  $C_2$  and the load.

BIBRED has a hidden feature compared to a normal forward converter due to the presence of the capacitor  $C_{1b}$ . Usually a forward transformer is equipped with a third winding, de-magnetizing winding, which is needed to de-energize the magnetizing inductance of the transformer. In BIBRED application the magnetizing energy can be restored into the capacitor  $C_{1b}$  without additional components or a winding. After the switch was been turned off the magnetizing current is able to circulate a path closed by the forward biased diode  $D_2$ . Reflected boost inductor current can circulate through the same path as the magnetizing current. The two currents are charging the capacitor  $C_{1b}$ .

Figure 3.10 BIBRED, switch turned off, EMI filter is omitted. The boost inductor is de-energized completely to the capacitors  $C_1$  and  $C_{1b}$ . Transformers magnetizing energy is restored to the capacitor  $C_{1b}$  through the diode  $D_2$ . The reflected boost inductor current circulates also through the diode  $D_2$ .

#### 3.2.3 Input stage

BIBRED has the DCM boost converter as an input converter. DCM operation of the converter is crucial for BIBRED in order to achieve acceptable power factor correction. The operation of the input converter is almost identical with the one in BIFRED. The only difference of the operation of the input stages is in the reverse voltage in which the inductor is fixed right after the switch has been turned off. In BIFRED the voltage  $V_{L,n}$  is presented in Eq. (3.4). In BIBRED the voltage  $V_{L,n}$  is

$$V_{\rm L,n} = v_{\rm in,n} - \left( V_{\rm C} + \frac{N_1}{N_2} V_{\rm C1b} \right)$$

(3.20)

Careful look at the secondary side of BIBRED reveals that the capacitors  $C_{1b}$  and  $C_2$  are the only 'DC components' present at the secondary. In other words, the inductor  $L_2$  or the secondary winding of the transformer cannot store DC voltage in the steady state. Consequently, the capacitors  $C_2$  and  $C_{1b}$  must share the same average voltage. The voltage over the capacitor  $C_2$  is the output voltage, which addresses that the average voltage over the capacitor  $C_{1b}$  is the output voltage, too. Hence, Eq. (3.20) converts to a form identical with Eq. (3.4). The conclusion is that in the steady state the input stages of BIFRED and BIBRED operate identically. Equations (3.5), (3.6) and (3.7) are applicable for BIFRED as well as for BIBRED.

#### 3.2.4 Output stage

The output stage of BIBRED is a forward type converter. As mentioned earlier, one of the output diodes is replaced by the capacitor  $C_{1b}$ . The replacement is done in order to offer a circulation path for the reflected boost inductor current. The capacitor  $C_{1b}$  and the diode  $D_2$  form also an appropriate way to de-magnetize the forward transformer. The forward stage can operate either CCM or DCM. Because these two modes of operation differ from each other radically, they are considered separately.

#### 3.2.4.1 CCM operation

In CCM operation the output voltage of the forward stage is strictly defined by the bulk capacitor voltage, turns ratio and duty ratio because the average volt-second balance across the inductor  $L_2$  has to be equal to zero in steady state. The voltage over  $L_2$  during the switch on time is presented in Eq. (3.19). When the switch is off, it equals to the output voltage  $V_{out}$ . Equating these two yield ( $V_{C1b}$  equals  $V_{out}$ )

$$\left( \frac{N_2}{N_1} V_{\rm C} + V_{\rm C1b} - V_{\rm out} \right) D_1 T_{\rm s} = V_{\rm out} (1 - D_1) T_{\rm s}$$

$$\Rightarrow V_{\rm out} = V_{\rm C} \frac{N_2}{N_1} \frac{D_1}{1 - D_1}$$

(3.21)

If the output voltage is regulated to a constant value,  $V_{\rm C}$  has to be

$$V_{\rm C} = V_{\rm out} \, \frac{N_1}{N_2} \frac{1 - D_1}{D_1} \tag{3.22}$$

Equations (3.21) and (3.22) are identical with the corresponding ones, (3.8) and (3.9) of BIFRED. Since the input and output stages of the converters operate in an identical manner, the steady state analysis is the same for both the converters in DCM + CCM operation. The circuits look different but the equations ruling their behavior are exactly the same. The voltage over the bulk capacitor in BIBRED has the same pattern as BIFRED, depicted in Fig. 3.7 a).

#### 3.2.4.2 DCM operation

In DCM operation the current through the output inductor  $L_2$  reaches zero before the end of a switching cycle, which means that Equations (3.21) and (3.22) are not valid anymore. Therefore, the bulk capacitor voltage has to be determined from a power balance.

As mentioned earlier, BIFRED has two different ways to deliver power from the primary to the secondary: power supplied by the bulk capacitor  $C_1$  and the power supplied by the boost inductor. BIBRED has three ways to deliver power from the primary to the secondary. The first two ways are the same as in BIFRED. Demagnetizing of the forward transformer can be comprehended as power delivering as well as the two other ones. These three ways to deliver power are discussed below.

The power supplied by the bulk capacitor is as follows

$$P_{\text{out,C}} = V_{\text{C}} \left[ \left( \frac{N_2}{N_1} \right) \frac{I_{\text{L2,peak}}}{2} \right] D_1 = V_{\text{C}} \left[ \left( \frac{N_2}{N_1} \right) \frac{\left( \left( \frac{N_2}{N_1} \right) V_{\text{C}} + V_{\text{C1b}} - V_{\text{out}} \right) D_1 T_{\text{s}}}{2L_2} \right] D_1$$

$$= \left( \frac{N_2}{N_1} \right)^2 \frac{V_{\text{C}}^2 D_1^2 T_{\text{s}}}{2L_2}$$

(3.23)

where  $I_{L2,peak}$  is the peak current through the inductor  $L_2$ . The reflected transformer current  $I_{refl,n}$  calculated in section 3.1.5 can be calculated for BIBRED with same equation, Eq (3.12). The current has the same magnitude and power content in both cases but the circulating route is different. In BIFRED the current is flowing directly into the load and the output capacitor. In BIBRED the current charges the capacitor  $C_{1b}$ and the energy is not delivered to the actual output. However, the main point is that power is delivered from the primary side to the secondary side and Eq. (3.13) is applicable in BIBRED to calculation of  $P_{out,L1}$  as well.

Power delivered by the magnetizing inductance of the transformer is as follows

$$P_{\rm M} = \frac{V_{\rm C}^2 D_1^2 T_{\rm s}}{2L_{\rm M}}$$

(3.24)

Notice the similarity of Eq. (3.24) with Eq. (3.11)

Power balance between the input power and the power injected from the primary to the secondary is as follows

$$P_{\text{in,avg}} = P_{\text{out,C}} + P_{\text{out,L1}} + P_{\text{M}}$$

(3.25)

where  $P_{in,avg}$  is calculated from Eg. (3.7) and  $P_{out,L1}$  is calculated from Eq (3.13). By placing the variables in Eq. (3.25) and reorganizing it, an equation for the determination of the bulk capacitor voltage in DCM operation of BIBRED's output stage can be obtained. It is as follows:

$$\left[\frac{L_{1}}{L_{M}} + \left(\frac{N_{2}}{N_{1}}\right)^{2} \frac{L_{1}}{L_{2}}\right] V_{C}^{2} + \left[\frac{N_{1}}{N_{2}} V_{out} \sum_{n=1}^{T_{s}} \left(\frac{v_{in,n}^{2}}{V_{C} + \frac{N_{1}}{N_{2}} V_{out} - |v_{in,n}|}\right) - \sum_{n=1}^{T_{ine}} v_{in,n}^{2} \left(1 + \frac{|v_{in,n}|}{V_{C} + \frac{N_{1}}{N_{2}} V_{out} - |v_{in,n}|}\right)\right] \times \frac{T_{s}}{T_{line}} = 0$$

(3.26)

Eq. (3.26) shows clearly that the voltage over the bulk capacitor does not depend on the load or duty cycle but it is defined by the circuit parameters, the line voltage and output voltage. Therefore, the voltage is constant in DCM operation of the output stage of BIBRED.

Power balance between the power consumed in the load and the power injected to the secondary, for an ideal converter, is as follows

$$P_{\text{out,C}} + P_{\text{out,L1}} + P_{\text{M}} = \frac{V_{\text{out}}^2}{R_{\text{load}}}$$

(3.27)

Reorganizing Eq. (3.27) it is possible to obtain the value of the load resistance, which corresponds with the desired output voltage

$$R_{\text{load}} = \frac{V_{\text{out}}^2}{P_{C1,\text{out}} + P_{\text{out},\text{L1}} + P_{\text{M}}}$$

(3.28)

#### 3.2.4.3 CCM & DCM border

The border between CCM and DCM operation is determined by comparing the actual load resistance  $R_{\text{load}}$  to the resistance  $R_{\text{S}}$ .  $R_{\text{S}}$  is for BIBRED as follows

$$R_{\rm S} = \frac{V_{\rm out}}{I_{\rm out}} = \frac{V_{\rm out}}{\left(\frac{I_{M,peak}}{2}\right)} = \frac{V_{\rm out}}{\left(\frac{V_{\rm out}(1-D_1)T_{\rm s}}{2L_2}\right)} \frac{2L_2}{(1-D_1)T_{\rm s}}$$

(3.29)

where  $L_2$  is the inductance of the output inductor  $L_2$ . The output stage of BIBRED operates in DCM if the load resistance is greater than the  $R_s$ . Vice versa, if the load resistance is smaller than  $R_s$  the converter operates in CCM. Eq. (3.29) is based on the fact that the inductor  $L_2$  is completely demagnetized in time duration  $(1-D_1)T_s$ .

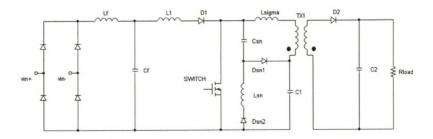

# 3.3 Modified Dither

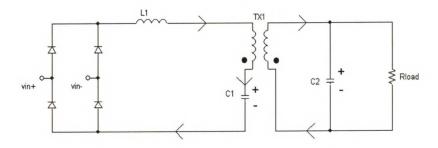

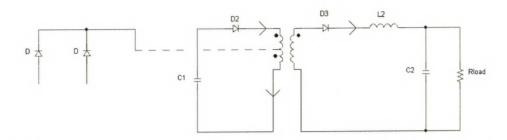

#### 3.3.1 General

Modified dither is an advanced Buck-Boost type single-stage converter, /8/. The schematic of the converter is shown in Fig. 3.11. The converter is clearly a single-stage solution because it has only one switching stage. Its ancestor, the regular dither converter has a problem with excessive voltage rise over the DC-energy storage element  $C_1$  during light loads. Modified dither has, at least, a partial solution for the problem. The converter has a tapped transformer, which is for prevention of the excessive voltage rise over the bulk capacitor. Diodes in the rectifier bridge are able to conduct when the line voltage is larger than a voltage imposed by the bulk capacitor to the lower part of the primary winding ( $N_{1B}$ ) of the transformer. When the bulk capacitor voltage rises due to a reduced load, the imposed voltage rises, too. Consequently, input power is reduced not only by the reduction of the duty cycle but also by the shortened conduction time of the bridge diodes.

By allowing DCM operation of the inductor  $L_1$  proper power factor correction is attained.

Figure 3.11 Modified dither converter /8/.

In single-stage converters like BIFRED or BIBRED the bulk capacitor voltage cannot fall below the peak line voltage. In Modified dither the diode  $D_2$  prevents the bulk capacitor from becoming automatically charged to the peak line voltage and the voltage can be considerably lower than in BIFRED or BIBRED. The converter suffers from the voltage rise during light loads but due to the low initial value it has 'space' to rise. Therefore, the converter can be designed to operate in DCM + CCM operation over a wide range of loads without exceeding the 450 V limit of the bulk capacitor voltage. Therefore, only the DCM + CCM operation of the converter is included in the analysis.

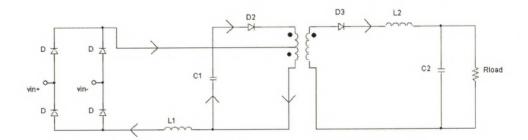

#### 3.3.2 Operation

The converter has two operation modes: the switch turned or off. When the switch is turned on, the bulk capacitor voltage is applied across the primary winding of the transformer. Since the transformer is tapped, the line voltage confronts an imposed voltage across the lower part of the primary winding  $N_{1B}$ . When instantaneous line voltage is below the imposed voltage, the diodes in the bridge are not able to conduct and no power is delivered from the utility grid to the circuit. Paths of the currents during the switch-on mode, when the instantaneous line voltage is less than the voltage across the  $N_{1B}$ , are shown in Fig. 3.12.

Figure 3.12 Modified dither, the switch is on and the instantaneous line voltage is less than the voltage across the  $N_{1B}$ . Diodes in the rectifier bridge are not able to conduct and power flow to the circuit is disabled. The bulk capacitor is supplying power to the secondary.

As the line voltage finally reaches the imposed voltage the diodes in the bridge are able to conduct and power flow from the utility grid to the converter is enabled. Paths of the currents during the mode are shown in Fig. 3.13. Line current energizes the inductor  $L_1$ and the bulk capacitor and a fragment of the line voltage are feeding the secondary. One interesting thing during the operation mode is the current through the forward biased diode  $D_2$ . The main portion of the current is the one supplied by the bulk capacitor. However, a look at the transformer and the winding arrangements reveal that the line current causes a reflected current, which flows through the diode to the 'wrong' direction. The current through the diode is the difference between the bulk capacitor current and the reflected current.

Figure 3.13. Modified dither switch turned on. Instantaneous line voltage is greater than the voltage over  $N_{\text{IB}}$  and the diodes in the bridge are able to conduct.

When the switch is turned off, the line current and the bulk capacitor current are cut off. Inductors  $L_1$  and  $L_2$  reverse their polarity and they are fixed to voltage level equal to the  $V_C$  and  $V_{out}$  respectively.  $L_1$  is de-energized to the bulk capacitor completely and  $L_2$  is de-energized partly or completely, depending on the output stage's operation mode (CCM or DCM), to the output capacitor  $C_2$  and the load. Paths of the currents during the switch-off mode are depicted in Fig. 3.14. Transformer of the converter is forward type. The magnetizing inductance of the transformer has to be de-energized during the switch off time. By adding a third winding to the transformer it is possible to demagnetize the inductance and restore the energy.

Figure 3.14. Modified dither during the switch-off time.  $L_1$  is completely de-energized to the bulk capacitor.  $L_2$  is partly or completely de-energized to the load and capacitor  $C_2$ .

### 3.3.3 Input stage

Modified Dither has a buck-boost type input stage. The converter has only one degree of freedom due to a single switching device. The degree of freedom has to be used either to adjust the output voltage or to build a proper power factor. Like in BIFRED and BIBRED, the duty ratio of the switch is used to adjust the output voltage and power factor correction is dealt with the DCM operation of the inductor  $L_1$ . As mentioned earlier, power flow to the converter is enabled only when the following is true

$$|v_{\text{in},n}| > V_{\text{C}} \frac{N_{1\text{B}}}{N_{1\text{A}} + N_{1\text{B}}}$$

(3.30)

where  $N_{1B}$  and  $N_{1A}$  are the numbers of turns in the lower and upper part of the primary winding respectively. Consequently,  $N_1 = N_{1A} + N_{1B}$  is the total amount of turns in the whole primary winding.

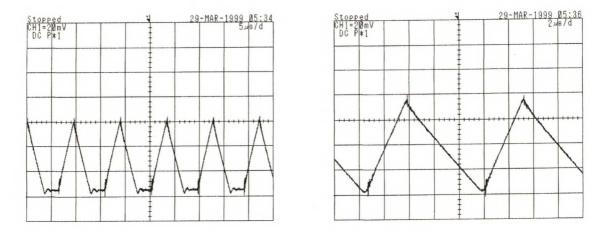

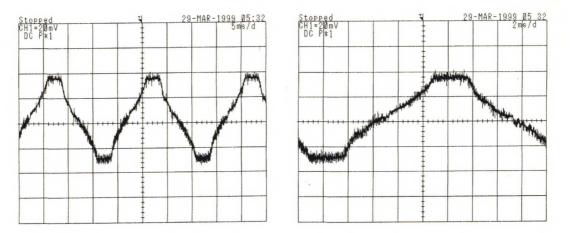

Line current of Modified Dither consist of a sequence of triangular pulses. The current is depicted in Fig. 3.15. Height of the current pulse can be calculated as follows

$$I_{\text{L,peak},n} = \frac{\left( \left| v_{\text{in},n} \right| - V_{\text{C}} \frac{N_{1\text{B}}}{N_{1\text{A}} + N_{1\text{B}}} \right) D_1 T_s}{L_1}$$

(3.31)

Figure 3.15 Line current of Modified Dither converter. Three single pulses above and the envelope of the current during one and a half line cycle below. Gaps in the envelope waveform is due to the low line voltage and consequent inability to deliver power to the circuit.

The inductor  $L_1$  is energized by a voltage difference between the line voltage and the voltage imposed across the winding  $N_{1B}$ . Average power transferred to the circuit by a pulse is as follows

$$P_{\text{pulse},n} = |v_{\text{in},n}| I_{\text{avg},n} = |v_{\text{in},n}| \frac{I_{\text{L,peak},n}}{2} D_1 = \frac{|v_{\text{in},n}| \left( |v_{\text{in},n}| - V \frac{N_{1\text{B}}}{N_{1\text{A}} + N_{1\text{B}}} \right) D_1^2 T_s}{2L_1}$$

(3.32)

Notice that  $P_{\text{pulse},n}$  is not the average power stored in the inductor L<sub>1</sub> during a switching cycle. It is the average power brought to the circuit during the *n*:th switching cycle.

More interesting than power carried by a pulse is the average power brought to the circuit during one line cycle. By summing power transferred by the pulses during the line cycle and dividing the sum by the amount of pulses, average input power is obtained. It is as follows

$$P_{\rm in,avg} = \frac{D_1^2 T_{\rm s}}{2L_1} \times \left( \sum_{n=1}^{\frac{T_{\rm line}}{T_{\rm s}}} v_{\rm in,n}^2 - V_{\rm C} \frac{N_{\rm 1B}}{N_{\rm 1A} + N_{\rm 1B}} \sum_{n=1}^{\frac{T_{\rm line}}{T_{\rm s}}} |v_{\rm in,n}| \right) \times \frac{T_{\rm s}}{T_{\rm line}}$$

(3.33)