# Power Switching Device Losses – Simulation and Non-Simulation Methods of Calculations

Sat Mohanram Brunel University London Electronic and Computer Engineering London, U.K. SatyanandVidyaSagar@Brunel.ac.uk M. Darwish Brunel University London Electronic and Computer Engineering London, U.K. mohamed.darwish@brunel.ac.uk CC Marouchos Cyprus University of Technology/Electrical Engineering Limassol, Cyprus christos.marouchos@cut.ac.cy

Abstract— In the design and manufacture of power supplies and converters, commercial factors demand high efficiency figures in the operation and performance of these products. Potential loss areas in the circuits are identified to achieve minimum losses [1] [2]. One of the main component contributing to losses in converters is the switching device.

The methods to calculate switching loss [3] are complex and involves several related parameters [4] [5]. Conduction loss, radiation interference [6] and temperature rise, impacts on design efficiency. Depending on the design limitations, a balance between the related parameters is necessary, which can be achieved by optimisation processes. Several methods are identified in this paper.

Keywords — Hard Switching, Input-Output Parameters, Losses, Switching Devices, Simulation and Non-Simulation Methods.

# I. INTRODUCTION

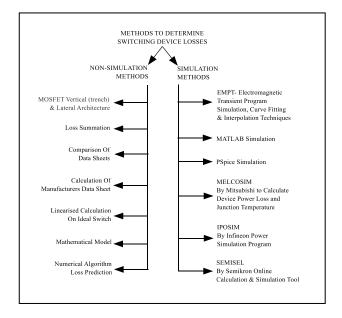

The switching loss methods, will give the engineer the flexibility of choosing a suitable component for the design application. Size of the switching device is important, since parasitic capacitance is proportional to the dimensions and structure of the device [7]. Comparison between the various methods will enable critical selection between expensive switching devices (IGBTs, MOSFETS), with high performance and low-cost devices with inferior performance. Articles reviewed have referred to the calculation of switching device losses [8] and other procedures involving an optimisation process. Some manufacturers' publications describe their own standalone device selection procedures to assist designers in choosing one of their own component or switching device for power applications [9] [10] [11]. Other papers refer to the use of popular, leading-edge application software that covers a range of design, simulation procedures which can include genetic algorithms, artificial intelligence or offer a simpler simulation process using models. Hence it was felt that there was a need to compile as many such methods as shown in Fig. 1.

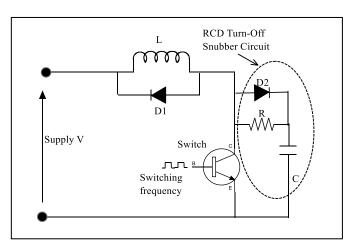

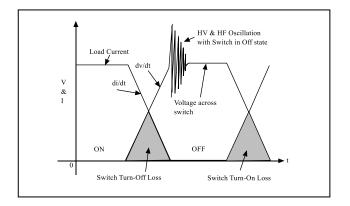

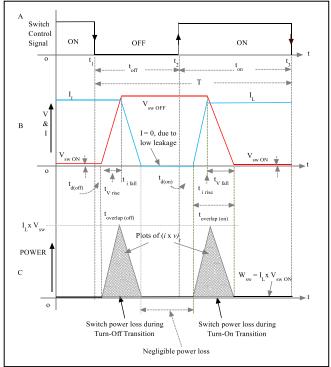

It is important to determine the total switching loss, in the event of hard switching [12] being used (see Fig.2). The losses due to the high peak voltage and dv/dt oscillations [13] [14] generated across the switch can be damped or removed by Turn-Off RC snubber circuits with an optimised value of time constant [15] [16].

Fig. 2, shows a linear representation of the loss in the switching device during the switch-off transition, represented by the shaded triangular area due to the intersection of the dv/dt and the di/dt gradients. This loss area as in the Linearised Calculation method listed shown in Fig. 1 is explained in the next section.

### II. METHODS TO DETERMINE SWITCHING DEVICE LOSSES

# A. Non-Simulation method - Linearised calculation on an ideal switch

Fig. 3 shows a solid-state switch in series with an inductive load with a free wheel diode connected in parallel, and an RCD snubber circuit connected across it. The circuit will be used to explain the current and voltage waveforms and the switch losses during the On/Off transitions and the On and Off cycle states of the switch.

Fig. 4, has three sections: -

Section (A), shows the control signal, with the ON and Off periods that closes and opens the switch. Section (B), shows the waveforms for the load current  $I_{L}$  and the switch voltage V<sub>SW</sub>. Section (C), shows the Power waveform for the losses in the switch during the switching On and Off transitions and the On and Off periods due to the control signal.

Figure 4 (A), shows the switch control signal, with period, T = (t off + t on) and frequency f = 1/T Hz.

Control Signal On – Fig. 4 (B), shows that the switch is initially ON, with a load current  $I_{L}$  and a low ' $V_{swON'}$  voltage drop across it.

At 't<sub>1</sub>' the control signal switches to the OFF state. The switch voltage remains at 'V<sub>swON</sub>' and starts to increase after a delay of 't<sub>d(off)</sub>' from 't<sub>1</sub>', and a further delay of 't<sub>Vrise</sub>' the switch voltage increases to 'V<sub>swOFF</sub>' (equal to the supply voltage) at a voltage gradient of dv/dt =  $(V_{swOFF})/(t_{Vrise})$ .

Control Signal Off - At 't<sub>2</sub>' the control signal switches to the OFF state, but the switch voltage remains at the 'V<sub>sw</sub> <sub>OFF</sub>' level. Since the load is inductive, due to the collapse of the magnetic field there is a delay for the growth of the -Ldi/dt voltage, whilst the diode D1 in Fig. 3 remains forward biased due to 'V<sub>swOFF</sub>' during the 't<sub>1</sub> to t<sub>2</sub>' Off period and maintains a connection between the top end of the switch and the supply voltage (equal to V<sub>swOFF</sub>). When the -Ldi/dt voltage is equal to the supply voltage, D1 is reversed biased and the switch voltage drops at a negative gradient of dv/dt = (V<sub>swOFF</sub>)/(t<sub>vfall</sub>) to a low value of 'V<sub>swON</sub>' volts. This cycle is repeated during the frequency of the control signal.

Current Wave Form Cycle - Fig. 4 (B), shows that the switch is initially ON, with a load current  $I_{L}$  flowing through it.

Control Signal Off - At 't1' the control signal switches to the OFF state, but the load current I<sub>L</sub> is maintained due to the load inductance and starts to decrease (when the switch voltage is at the open circuit level of 'V<sub>swOFF</sub>') at a negative gradient of di/dt = I<sub>L</sub>/(t<sub>i</sub> fall) and approaches zero level.

Control Signal On - At 't<sub>2</sub>', I<sub>L</sub> remains at the low level and begins to rise after a delay of 't<sub>d(on)</sub>' at a gradient of di/dt = I<sub>L</sub>/ (t<sub>i</sub> rise) and reaches full load current of I<sub>L</sub> and

remains at this level for the duration of the On period of the control signal.

and not as an independent document. Please do not revise any of the current designations.

Switch Losses, Transition and Closed States - Fig. 4 (C), is the power loss wave form due to the product of I<sub>L</sub> and V<sub>SW</sub> in Fig.4(B). The shaded areas represent this power loss, due to its linear shape it can be estimated by simply using the formula for the area of a triangle. See equations (4) and (5).

Equations derived from Fig.4 (A, B & C).

| Equations Key |         |    |       |    |        |  |  |  |  |

|---------------|---------|----|-------|----|--------|--|--|--|--|

| OL            | Overlap | PL | Power | SW | Switch |  |  |  |  |

|               |         |    | Loss  |    |        |  |  |  |  |

(A) Control signal period,  $T = (t_{on} + t_{off}) = 1/f Hz$  (1)

(B) Overlap (off) peri<sup>x</sup>od,  $t_{OLoff} = t_{Vrise} + t_{ifall}$  (2)

Overlap (on) period,  $t_{OLon} = t_{irise} + t_{Vfall}$  (3)

$$W_{PLoff} = \frac{1}{2} \times (t_{OLoff}) \times (I_L V_{SW}) \text{ Joules}$$

(4)

Switch energy during Turn-On Transition,

$W_{PLon} = \frac{1}{2} \times (t_{OLon}) \times (I_L V_{SW})$  Joules

Power loss in switch/cycle =  $\{(4) + (5)\} \times f$

$= \frac{1}{2} I_L V_{sw} (t_{OLoff} + t_{OLon}) f Watts$  (6)

(5)

$$= \frac{1}{2} I_{L} V_{sw} (t_{OLoff} + t_{OLon}) f Watts$$

(7)

And it is observed that,

Power loss

$$\propto$$

the duty cycle  $\frac{(t_{olon} + t_{oloff})}{(t_{on} + t_{off})}$  (8)

Power loss

$$\propto$$

f, (t<sub>OLon</sub>) and (t<sub>OLoff</sub>) (9)

Fower loss  $\infty$  f, (toLon) and (toLoff) (9) Turn-Off loss,

| Wsw = Vswoff × IL Joule | s (10) |

|-------------------------|--------|

|-------------------------|--------|

(Negligible, due to low leakage current)

Turn-On loss,

$$Wsw = V_{sw off} \times I_{L} Joules$$

(11)

and the average Power during the On state,

$$W_{SW} = I_{L} \times (V_{sw on}) \times (t_{on}/T) \text{ Joules}$$

(12)

Important deductions

Three important deductions are made from this simplified linear voltage and current wave form transitions:

1 From equation (6), approximate RC components values in the snubber circuit in Fig.3, can be estimated by equating the loss energy from equation (4) or (5) (whichever is greater) to the capacitor energy  $1/2C(V_{swoff})^2$  of the snubber circuit [17] [18]. These RC values may be

used as the initial weighted values for an optimisation process.

2 From equation (8), choosing switches with short switching times  $(t_{OLOn})$ , will dissipate less energy and therefore operate at higher frequencies.

3 From equation (11), adjusting the control switching signal On-period to a small value will minimise the switch loss energy during the On state [1].

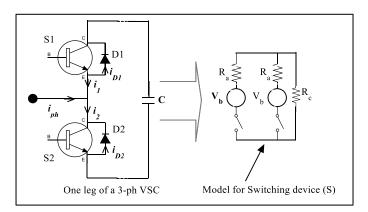

## B. Design of Switching Device Power model

A simple model is proposed to simulate switching devices (S) instead of using custom designed manufacturers' simulation programmes. These require very small-time steps (< 0.1µs) which would take a long to simulate if the simulation run-time is a few seconds and would also be very expensive. However, the (S) power loss in manufacturer's data sheet will be used to equate the total (S) and diode (D) losses. The power losses for switching devices in a two-level 3-ph voltage source converter (VSC) was considered [19]. Fig. 5 shows oneleg of the VSC and the corresponding model for a switching device. The model shows two resistors Ra to identify the separate losses in (S) and in (D). The (S) onoff switching transients generate high voltage and current spikes for short periods but contains high power. The conduction losses in the on state and the dv/dt, di/dt product loss in both the on and off states need to be considered.

The manufacturers' power loss data ( $P_{man}$ ) is equated to the losses related to I<sub>RMS</sub>/ph through (S).

i.e.

$$P_{man} = al^{2}_{ph} + bl_{ph} + c, \qquad (13)$$

where a, b and c are unknowns. These coefficients can be found during simulations, by varying the  $I_{ph}$  for the load range from the data sheet and measuring each simulation power loss as a function of  $I_{ph}$ . With at least three power equations (13), "a", "b" and "c" can be found.

In Fig.5, R<sub>a</sub> models the power losses due to the  $(I_{RMS})^2$ in the (S) and (D) and relates to "a" in (13). R<sub>c</sub> models the power losses due to  $(V_{DC})^2$  and relates to "c" in (13). Vb models the losses due to the  $I_{RMS}$  in the (S) and (D) relates to "b" in (13).

Computation of the Model parameters  $R_a$ ,  $R_c$  and  $V_b$ . Equating the phase current and the  $S_1$  and  $S_2$  currents.

In Fig. 5,  $i_{ph} + i_1 = i_2$  and  $iph = i_2 - i_1$  (14)

and  $i_1 = (i_{S1} - i_{D1})$  and  $i_2 = (i_{S2} - i_{D2})$  (15)

substituting (15) into (14),

$i_{ph} = i_{S2} - i_{D2} - i_{S1} + i_{D1} \tag{16}$

The power is related to the  $(I_{RMS})^2$  of  $i_{ph}$ ,

i.e.

$$I_{ph}^2 = (I_{S2}^2 + I_{D2}^2) + (I_{S1}^2 + I_{D1}^2)$$

(17)

Since the currents in  $S_1 = S_2$  and currents in  $D_1 = D_2$

(17) reduces to,

$$I_{ph}^2 = 2I_{S1}^2 + 2I_1^2$$

(18)

And from (15),

$$I_{ph}^2 = 2I_1^2$$

Total losses in Fig.5 model,

$$P_{S} = R_{a}I_{1}^{2} + V_{b}I_{1} + (V_{DC}^{2})/R_{c}$$

(19)

From (18),

$$lph^2 = 2l_{12}^2$$

and  $lph = \sqrt{2}l_1$  (20)

Therefore,

$$P_{s} = R_{a}(I_{ph}^{2})/2 + V_{b}(I_{ph}/\sqrt{2}) + (V_{Dc}^{2})/R_{c}$$

(21)

Comparing (13) and (21),

a

$$I_{ph}^2 = R_a(I_{ph}^2)/2$$

, and  $R_a = 2a$  (22)

$$b I_{ph} = V_b(I_{ph}/\sqrt{2}), \text{ and } V_b = \sqrt{2}b$$

(23)

$$c = (V_{DC}^2)/R_c \text{ and } R_c = (V_{DC}^2)/c$$

(24)

Having determined the values for "a", "b" and "c" in (13), the values for ( $R_a = 2a$ ), ( $R_c = (V_{DC}^2)/c$ ) and ( $V_b = \sqrt{2b}$ ), can be applied in the proposed model in Fig.5. This model has been designed for the VSC circuit for validation of power losses obtained from manufacturers' software. The designers of the model confirm that with some fine tuning of the parameters, simulation power loss results compare closely to actual VSC circuit losses. [19]. With further adjustments, this simple model may be used as the switching device in a converter. The simulation to determine the power losses can be crossed checked using equation (21) with modifications as necessary.

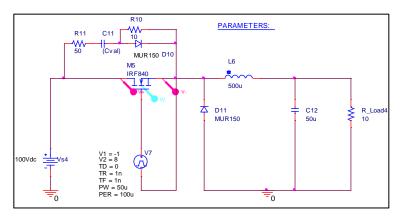

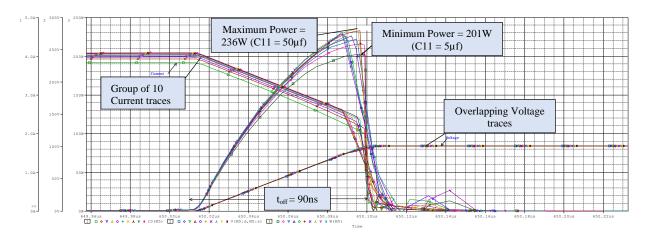

#### C. Power Switching Device losses by PSpice Simulation

This is an example in PSpice, to show that a component (in this case the capacitor in an RC snubber circuit) can be varied over a range of values to determine the value that reduces the switch loss to a minimum during its turnoff transition period. The power loss for the switching device in the Schematic shown in Fig.7, is simulated by the process shown in the flow diagram in Fig.6. PSpice converts all non-linear components to linear equivalent models. It creates Nodal matrix of any Conductance (G) and Currents (I) and solves the corresponding linear Nodal equations for G x V = I. In Fig. 7, a random selection of values for R11 =  $50\Omega$  and C11 varied from 5µf to 50µfin increments of 5µf. The ten simulation runs resulted in a "family" of waveforms of voltage, current and power shown in Fig.8. Table1 shows the ten simulation runs with corresponding symbols used to identify each trace. These symbols are also presented below the PSpice time axis for V, I and W. The peak value of the vellow trace was the lowest value of 201W and corresponded to the first simulation run giving the value for C11 = 5 $\mu$ f. The power traces show the effect of the variation of capacitor on the switch loss. The " $_{\Box}$ " symbol under Run 1, identifies the I, V and P traces for minimum power. The "grey" area has no entry.

In this example, the turn-off period,  $T = 50\mu s$

The measured switch transition period,  $t_{off} = 90$ ns

The RC time constant tau,  $\tau$  = 50 $\Omega$  × 5µf = 250µs

Comparing these periods,  $\tau = 5 \times T$  and 2777 × t<sub>off</sub>, which accounts for the 201W minimum power loss (in the family of traces) for the switch during t<sub>off</sub>. i. e. the RC time constant was too large to effectively reduce the switch loss to a negligible value. In UPEC Paper 4, it was shown that selecting the RC time constant  $\tau = t_{off}$ , or =  $\frac{1}{4} \times t_{off}$  would eliminate or reduce the switching loss to a negligible value. [20] [21] [22].

| TABLE 1.1, Par Traces Cymbols and Owner 1005 |   |                                          |    |    |    |    |    |    |    |    |

|----------------------------------------------|---|------------------------------------------|----|----|----|----|----|----|----|----|

| No. of<br>Runs                               | 1 | 2                                        | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 |

| C11-µf<br>range                              | 5 | 10                                       | 15 | 20 | 25 | 30 | 35 | 40 | 45 | 50 |

| Trace<br>ymbols<br>for V, I &<br>P           |   | \$                                       | V  | Δ  | 0  | +  | х  | λ  | Y  | *  |

| l (3.8A)                                     |   |                                          |    |    |    |    |    |    |    |    |

| V (100V)                                     |   | This grey area of the table is redundant |    |    |    |    |    |    |    |    |

| Pmin<br>(201W)                               |   |                                          |    |    |    |    |    |    |    |    |

| C11-5µf                                      |   |                                          |    |    |    |    |    |    |    |    |

TABLE 1.V, I & P Traces' Symbols and Switch loss

R11 fixed at 50Ω

## **III. CONCLUSIONS**

This paper presented seven non-simulation and six simulation methods which determine the switching device losses. One of the main cause of switching losses is in the use of hard switching. These losses have been critically described in the method of linear approximation assuming an ideal switch. To minimise these losses, the equations identified the relationship between these losses and the selection of switches with short switching times, and a short mark/space ratio of the switching frequency.

The design of a switching model was presented, based on the losses due to the high voltage spikes and oscillation, the conduction losses and the di/dt and dv/dt losses. These were represented in a basic three element differential equation and developed to determine the three related coefficients. The circuit model was derived by applying Thevenin's theorem and the values of the resistors and voltage generator were calculated from the analysis of the model differential equations. The final model can then be used in a schematic where the losses can be simulated.

Finally, a comprehensive PSpice PARAM simulation was carried out by sweeping through a range of capacitor values which resulted in a family of voltage, current and power traces. These traces show the effect of the capacitor value on the reduction of switching loss and also identified the particular capacitor value related to the minimum loss.

#### REFERENCES

- A. Smith, "Calculating Power Loss In Switching MOSFETS," Power Integrations, Inc, 8 January 2011. [Online]. Available: https://www.eetimes.com/document.asp?doc id=1278970.

- [2] N. Rao and D. Chamund, "Power Losses in an IGBT Module -AN6156-1, LN31943," DYNEX Semiconductor Ltd, September 2014. [Online]. Available: www.dynexsemi.com.

- [3] A. Brambilla and E. Dallago, "Snubber Circuits and losses of Voltage-Socurce GTO Inverters," IEEE Transactions on Power Electronics, Vol. 7, No. 1, pp. 231-239, January 1992.

- [4] A. Laprade and R. H. Randall, "Numerical Method for Evaluating IGBT Losses-Application Note AN-7520," Fairchild Semiconductor Corporation, January 2000. [Online]. Available: www.onsemi.com.

- [5] "Determination of switching losses in IGBTs by loss-summationmethod," in Industry Applications Conference, 1995. Thirtieth IAS Annual Meeting, IAS '95. Conference Record of the 1995 IEEE, Florida, USA, 1995.

- [6] K. Bose, "Benefits in both Hard and Soft Switching Topologies," infineon, June 2016. [Online]. Available: http://www.infineon.com/coolmos.

- [7] N. Mohan, T. M. Undeland and W. P. Robbins, Power Elctronics, Converters, Applications and Design, 2nd Edition, Minneaplois, USA: John Wiley, 1995.

- [8] H. Mao, J. A, A. Qahouq, W. QIU, Y. Wen and I. Batarseh, "Lossless Snubber Circuits for Current Doubler Rectifiers to Reduce Reverse-Recovery Losses," IEEE Transactions on Power Electronics Volume 26 No.1, pp. 2639-2644, 2003.

- [9] D. Graovac, M. Purschel and A. Kiep, "MOSFET Power Losses Calculation Using the Data Sheet Parameters -Application Note, V1.1, July 2006," Infineon Technologies AG, Neubiberg, Germany, 2006.

- [10] U. Nicolai and A. Wintrich, "Determining switching losses of SEMIKRON IGBT modules-Applcation Note AN 1403, 2014-08-19," SEMIKRON INTERNATIONAL GmbH, Nuremberg, 2014.

- [11] T. Platzer and P. Reiter, "Snubber Circuits for Inductive Loads-Application Note DE 0100, revision 0100," HIQUEL, Bad Gleichenberg, 2010.

- [12] S. Dong, Q. Zhang and S. Cheng, "Analysis and Design of Snubber Circuit for Z-Source Inverter Applications," IET Power Electronics, vol. 9, no. 5, pp. 1083-1091, 2015.

- [13] J. Alnasseir, "Theoretical and Experimental Investigations on Snubber Circuits for High Valves of FACTS-Equipment for Over-Voltage Protection," Fredrich-Alexander University of Erlangen-Nuremberg, 26 March 2007. [Online]. Available: http://www.tf.fau.eu/index.shtml.

- [14] F. Semiconductor, "Resistor-Capacitor (RC) Snubber Design for Power Switches," Digi-Key Electronics, 6 August 2014. [Online].

- [15] A. Caraveo, R. Gonzalez, P. Sanchez and A. Soto, "Brief Review on Snubber Circuits," in 2010 20th International Conference on Electronics Communications and Computers (CONIELECOMP), Choula Mexico, 2010.

- [16] "Snubber Circuit Design Calculators," Daycounter, Inc. Engineering Services, 2016. [Online]. Available: Http://www.daycounter.com/Contact.phtml.

- [17] J. Hagerman, "Calculating Optimum Snubbers," Hagerman Technology, 24 July 1995. [Online].

- [18] C. K. Huing, H. H. Nien, S. K. Changchien, C. H. Chan and C. K. Chen, "An Optimal Designed RCD Snubber For DC-DC Converters," in 10th International Conference on Control, Automation, Robotics and Vision, Hanoi, Vietnam, 2008.

- [19] J. M. Mauricio, J. M. Maza-Ortega and A. Gomez-Exposito, "Considering Power Losses of Switching Devices in Transient Simulations through a Simplified Circuit Model," in International Conference on Power System Transients, Kyoto, Japan, 2009.

- [20] M. Engelhardt, Spice Algorithm Overview ecircuitcenter.com/Spicetopics/overview.htm, eCircuit Center, 2003.

- [21] T. Murugajthi, A Survey of Fast Analog Circuit Analysis Algorithm using SPICE, Tamilnadu, India: PSNA College of Engineering & Technology, 2014.

- [22] C. R. Paul, A brief SPICE (Pspice) Tutorial, GA, USA: IEEE, 2010.

Fig. 1: Methods to Determine Switching Losses

Fig. 3. Switch with inductive load and turn-off snubber circuit

Fig.5. Model for a VSC switching Device

Fig. 2: Hard Voltage and Current Switching

Fig. 4. Losses in ideal switch based on linear approximation of V & I Switching waveform

Fig. 7. PSpice Schematic for simulation of Switching device Power Loss

Fig. 6. Flow diagram of PSpice Working Algorithms

Fig.8. Family of Ten Traces of Voltage, Current and Power for Switching Device during the switching period  $t_{\rm off}$