# ELECTROLUMINESCENT DEVICES VIA SOFT LITHOGRAPHY

A THESIS SUBMITTED TO BRUNEL UNIVERSITY IN FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY.

By

Richard James Hendley Young B.Sc.(Hons) School of Engineering & Design Brunel University October 2017

### Abstract

This thesis provides a compendium for the use of microcontact printing in fabricating electrical devices. Work has been undertaken to examine the use of soft lithographic techniques for employment in electronic manufacture. This thesis focusses on the use of high electric field generators as a means to producing electroluminescent devices. These devices provide a quantifiable output in the form of light. Analysis of the electrical performance of electrode structures can be determined by their success at producing light. A prospective reduction in driving voltage would deem these devices more efficient, longer lasting and an improvement on current specification.

The work focussed on the viability of using relatively crude print techniques to create high resolution structures. This was carried out successfully and demonstrated that lighting structures of 75  $\mu$ m and 25  $\mu$ m have been produced. Microcontact printing has been established as a method for patterning gold surfaces with a functionalising self-assembled monolayer using alkanethiol molecules. This layer is then utilised as an etch resist layer to expose gold tracks for use as electric field generator electrode arrays.

Through careful analysis of each step of the printing process, techniques were developed and reported to create a robust and repeatable print mechanism for reliability and accuracy. These techniques were employed to optimise the print process culminating in the development of each stage and final electrode structures mounted on a rigid backplate for use as electroluminescent devices for characterisation.

These devices were then modelled for their electrical characteristics and investigated for being used in low voltage application. In this case for the development of electroluminescent applications, a driving voltage of 65 V was achieved and represents a significant advance to the field of printed electronics and Electroluminescence.

## Acknowledgements

Special thanks must be made to my first supervisor Dr. Peter Evans, who wondered as did many whether I would make it. His advice and guidance gave direction and curiosity to undertake true scientific exploration. Peter's extensive encyclopaedic knowledge of all things pertaining to his field proved invaluable throughout the process. I would also like to thank my second and third supervisors, Prof. David Harrison and Dr. Gareth Hay respectively, both of whom have supported the entire endeavour their input provided insightful and challenging help.

Thanks must also be made to the EPSRC, who funded the project initially.

I would also like to thank my wife, Tenika Young, whose patience was demonstrated in bringing this work to completion. A silent and steady voice of reason and encouragement throughout what has been a turbulent journey. This coupled with my parents support, for the investment they made in providing opportunities that have allowed me to reach such a milestone. To the numerous friends and family who have encouraged and inspired me to keep going, thank you.

Finally, as a man of faith I do believe that any work or discovery made in this thesis is no accident but the revealing of great mysteries waiting for man to uncover. Belief in a creator has allowed me to approach the subject with humility, not expecting omniscience but expecting understanding.

# Contents

| Abstract                                               | 2  |

|--------------------------------------------------------|----|

| Acknowledgements                                       | 3  |

| List of figures                                        | 8  |

| List of tables                                         | 10 |

| List of equations                                      | 11 |

| Glossary of symbols and units                          | 12 |

| Glossary of terms                                      | 14 |

| Chapter 1 – Introduction                               | 16 |

| 1.1 – A brief history of electronic manufacture        | 16 |

| 1.1.1 – Valve-based 'chassis' systems                  | 17 |

| 1.1.2 – Tinker Toy                                     | 19 |

| 1.1.3 – Transistors and semiconductors                 | 19 |

| 1.1.4 – Current circuit boards                         | 21 |

| 1.1.5 Research question                                | 22 |

| 1.2 – Diversification of manufacturing methods         |    |

| 1.2.1 – Photolithography                               | 22 |

| 1.2.2 – Screen printing                                | 24 |

| 1.2.3 – Offset lithography                             | 25 |

| 1.2.4 – Inkjet                                         | 26 |

| 1.2.5 – Flexography                                    | 27 |

| 1.2.6 – Gravure printing                               | 27 |

| 1.2.7 The benefits of smaller geometry                 | 28 |

| 1.3 – Novel fabrication employing 'Soft Lithography'   | 29 |

| 1.4 – Specifying EL displays for quantifiable outcomes | 30 |

| 1.4.1 – Phosphor theory and ink formulation            | 33 |

| 1.4.2 – Interdigitated theory                          | 35 |

| 1.5 – Alternating Current Electroluminescent displays  | 37 |

| 1.6 – Plan of work                                     | 38 |

| 1.7 – Chapter summary                                  | 38 |

| Chapter 2 – Literature review                          | 40 |

| 2.1 – Established limitations                                       | 40 |  |

|---------------------------------------------------------------------|----|--|

| 2.2 – Soft lithographic techniques for moulding                     | 41 |  |

| 2.2.1 – Micromoulding in capillaries                                | 41 |  |

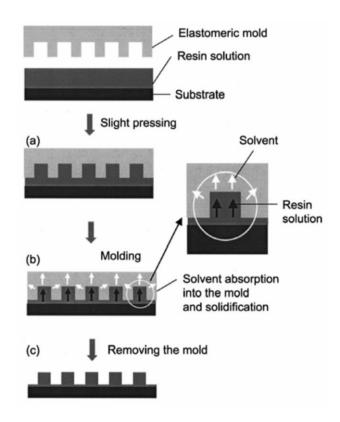

| 2.2.2 – Solvent assisted micromoulding                              | 42 |  |

| 2.2.3 – Limitations of moulding techniques                          | 43 |  |

| 2.3 – Soft lithographic techniques for embossing                    | 44 |  |

| 2.3.1 – Soft embossing                                              | 44 |  |

| 2.3.2 – Limitations of embossing techniques                         | 45 |  |

| 2.4 – Soft lithographic techniques for printing                     | 45 |  |

| 2.4.1 – Microtransfer printing                                      | 45 |  |

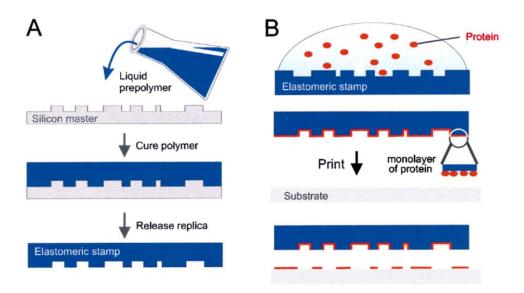

| 2.4.2 – Microcontact printing                                       | 46 |  |

| 2.5 – Suitability of soft lithographic methods for micro conductors | 46 |  |

| 2.6 – Current developments with Microcontact printing               | 48 |  |

| 2.6.1 – Whiteside's Research group                                  | 48 |  |

| 2.6.2 – IBM research                                                | 49 |  |

| 2.6.3 – Philips research                                            | 50 |  |

| 2.6.4 – Centre Suisse d'Electronique et de Microtechnique           | 51 |  |

| 2.6.5 – Massachusettes Institute of Technology                      | 52 |  |

| 2.6.6 – Microcontact printing for electronic applications to date   | 53 |  |

| 2.7 – Identification of the knowledge gap                           | 53 |  |

| 2.8 – Electroluminescent displays and phosphor particulates         |    |  |

| 2.8.1 – Refined objectives                                          | 55 |  |

| 2.8.2 – Identification of investigative procedure                   | 56 |  |

| Chapter 3 – Methods and materials                                   | 59 |  |

| 3.1 – Further investigation of the microcontact printing process    | 59 |  |

| 3.2 – Use of a commercially supplied microcontact printing kit      | 60 |  |

| 3.2.1 – Autonomous print development                                | 62 |  |

| 3.2.2 – Master manufacture                                          | 63 |  |

| 3.2.2.1 – Capacitance calculations                                  | 65 |  |

| 3.2.3 – Stamp fabrication                                           | 68 |  |

| 3.2.3.1 Linear Shrinkage of PDMS elastomer                          | 70 |  |

| 3.2.4 – Substrate production                                        | 72 |  |

| 3.2.5 – Thiol selection                                             | 75 |  |

| 3.2.6 – Thiol inking of the stamp                                 | 80  |

|-------------------------------------------------------------------|-----|

| 3.2.7 – Printing of thiol                                         | 81  |

| 3.2.8 – Etching process                                           | 81  |

| 3.3 – Progress and experimental procedure                         | 85  |

| Chapter 4 – Print development                                     | 86  |

| 4.1 – Investigation with kit                                      | 86  |

| 4.2 – Print runs with kit                                         | 86  |

| 4.2.1 – First print trial, track splitting                        | 86  |

| 4.2.2 – Improving the print techniques                            | 90  |

| 4.2.3 – Improvement of the etch solution                          | 91  |

| 4.2.4 – Confirming the substrates                                 | 93  |

| 4.2.5 – Substrate thickness                                       | 95  |

| 4.2.6 – Manufactured stamps                                       | 99  |

| 4.3 – Finalised print process as independent of the kit           | 101 |

| 4.4 – Outstanding objectives                                      | 102 |

| Chapter 5 – Print resolution                                      | 103 |

| 5.1 – Independent print experimentation                           | 103 |

| 5.2 – Further print investigation                                 | 104 |

| 5.2.1 – Optimising print conductivity at 75 $\mu$ m track and gap | 104 |

| 5.2.2 – Functional 75 $\mu$ m track and gap device emitting light | 107 |

| 5.2.3 – Reducing the track and gap spacing                        | 111 |

| 5.2.4 – Conductive 25 $\mu$ m device with low driving voltage     | 113 |

| 5.3 – Experimentation summary                                     | 116 |

| Chapter 6 – Summary of results                                    | 117 |

| 6.1 – Results for print components                                | 117 |

| 6.1.1 – Stamps                                                    | 117 |

| 6.1.2 – Gold substrates                                           | 118 |

| 6.1.3 – Thiol                                                     | 120 |

| 6.1.4 – Etch process                                              | 121 |

| 6.2 – Results for characterising printed functional devices       | 123 |

| 6.2.1 – Energy dissipated from structures                         | 125 |

| 6.2.2 - Determining instantaneous power (Pi) of the devices       | 127 |

| 6.2.3 – Comparison of how frequency affects Pi across the devices | 129 |

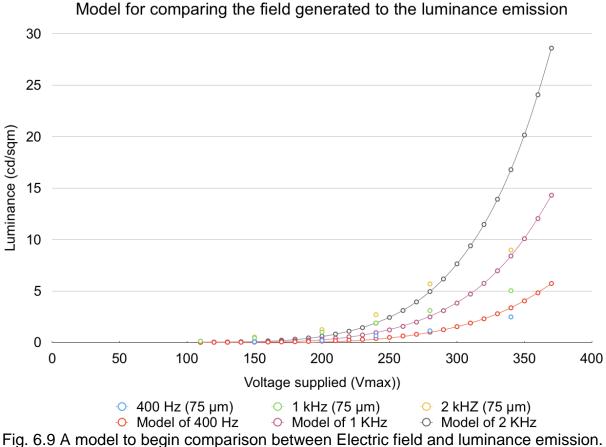

| 6.2.4 – Establishing a model for reducing the driving voltage        | 129   |

|----------------------------------------------------------------------|-------|

| 6.2.5 – Defining Luminance threshold                                 | 131   |

| 6.2.6 – Comparison with band gap energies                            | 132   |

| 6.2.7 – The effects of Phase shift                                   | 133   |

| 6.3 – Characterising a model for luminance                           | 133   |

| Chapter 7 – Conclusions and further work                             | 135   |

| 7.1 – Summary of conclusions                                         | 135   |

| 7.2 – Contribution to knowledge                                      | 136   |

| 7.3 – Further work                                                   | 136   |

| 7.3.1 – Energy calculations                                          | 136   |

| 7.3.2 – Exploration of the energy losses of imperfect capacitive dev | vices |

|                                                                      | 137   |

| 7.3.3 – Improvement to the printing process                          | 137   |

| 7.4 – Closing statements                                             | 137   |

| References                                                           | 138   |

| List of publications                                                 | 148   |

# List of figures

# Chapter 1

| Fig. 1.1 - Valve based amplifier                                         | 18        |

|--------------------------------------------------------------------------|-----------|

| Fig. 1.2 – Various arrays fabricated by photolithography                 | 23        |

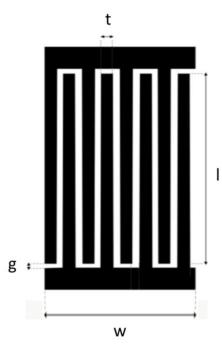

| Fig. 1.3 – Geometry of interdigitated electrodes                         | 31        |

| Fig. 1.4 - Offset lithographically printed electroluminescent display [2 | 21]       |

|                                                                          | 32        |

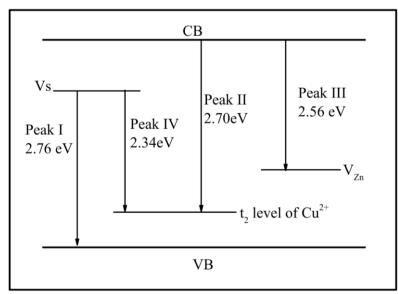

| Fig. 1.5 – Schematic energy level diagram showing the emission me        | echanism  |

| in ZnS:Cu nanoparticles, [22]                                            | 34        |

| Chapter 2                                                                |           |

| Fig. 2.1 - Demonstration of micromoulding in capillaries, [28]           | 42        |

| Fig. 2.2 An example of replica moulding and solvent assisted micr        | omoulding |

| combined, [30]                                                           | 43        |

| Fig. 2.3 – Microcontact printing of alkanethiol, [36]                    | 46        |

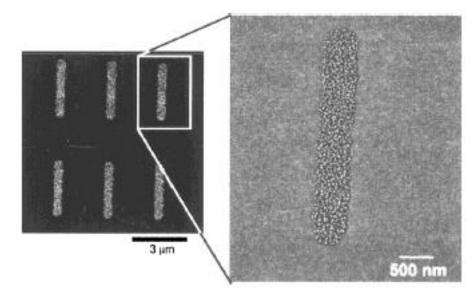

| Fig. 2.4 - Microcontact printing of immunoglobulins G on a Si wafer,     | [37]      |

|                                                                          | 48        |

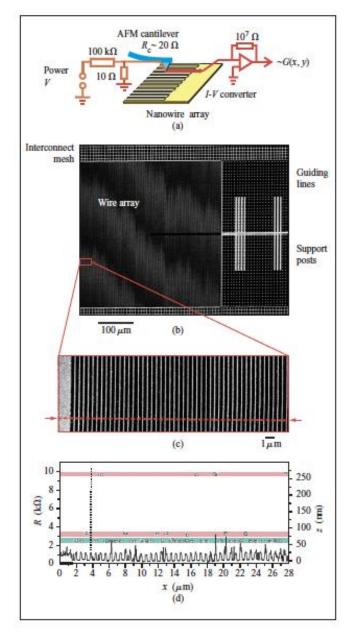

| Fig. 2.5 – Characterisation of microcontact printed wires, [43]          | 50        |

| Fig. 2.6 – Cross-section of the wave printing prototype, [44]            | 51        |

| Fig. 2.7 - Microcontact printed microbatteries, [48]                     | 52        |

| Fig. 2.8 - Structure of a traditional monochrome EL display, [51]        | 54        |

| Chapter 3                                                                |           |

| Fig. 3.1 - Common diffraction grating profiles, [61]                     | 63        |

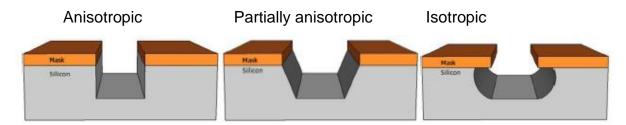

| Fig. 3.2 – Fully anisotropic through to isotropic etching, [63]          | 64        |

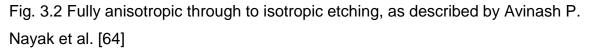

| Fig. 3.3 - Tearing of track profile during release from master           | 69        |

| Fig. 3.4 – Result for linear shrinkage superimposed on the model fo      | r linear  |

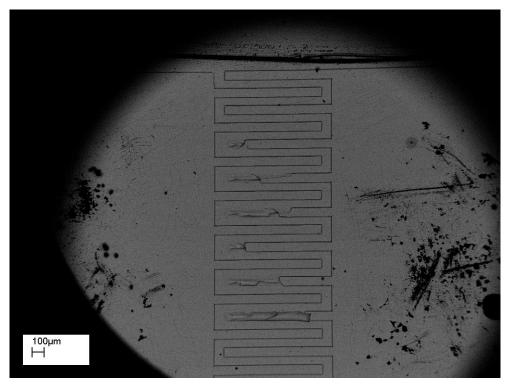

| shrinkage of PDMS, [68]                                                  | 72        |

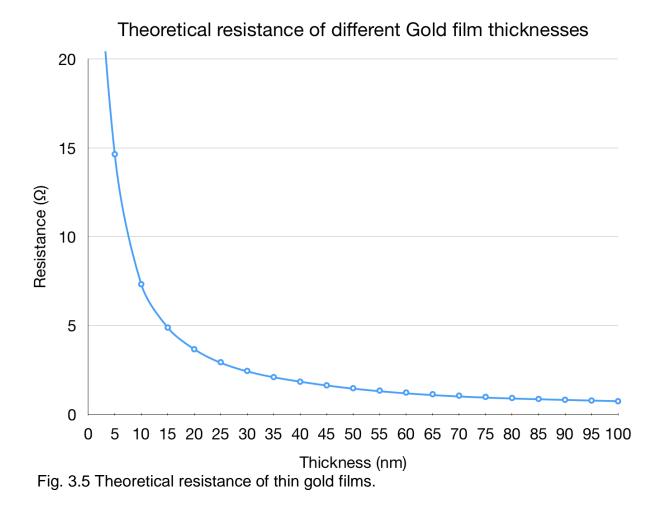

| Fig. 3.5 – Theoretical resistance of thin gold films                     | 75        |

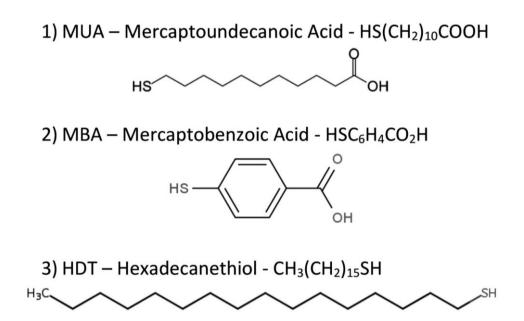

| Fig. 3.6 – Representation of thiol molecular structures                  | 76        |

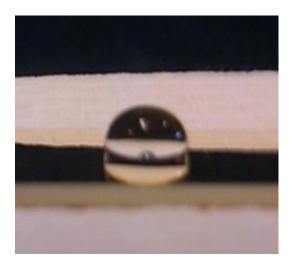

| Fig. 3.7 – Ball of water placed on a hydrophobic surface                 | 77        |

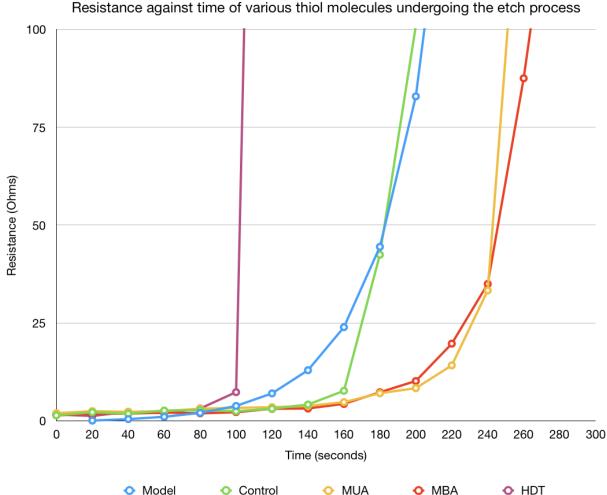

| Fig. 3.8 - Graph of thiol masking properties                             | 79        |

| Fig. 3.9 – Stamp immersion in alkanethiol                                | 80        |

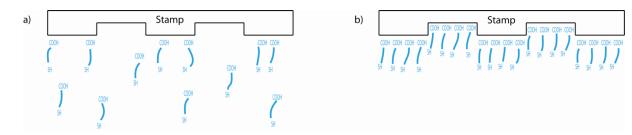

| Fig. 3.10 – Thiol transfer from the stamp to substrate                   | 81        |

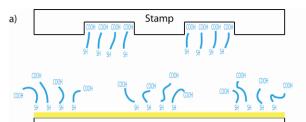

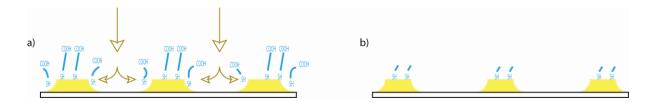

| Fig. 3.11 – Masking SAM layer undergoing wet chemical etching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 82        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

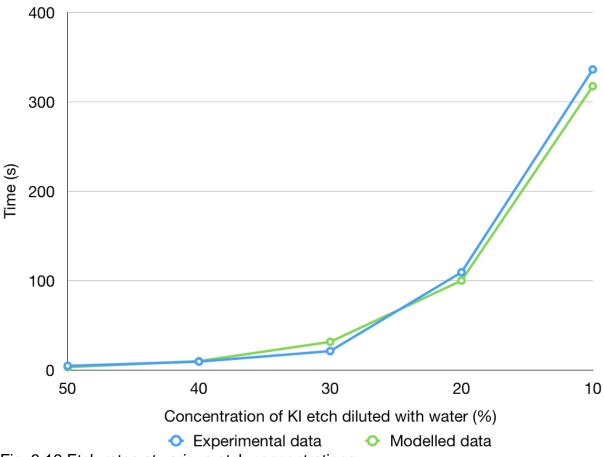

| Fig. 3.12 - Etch rates at various etch concentrations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 83        |

| Chapter 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

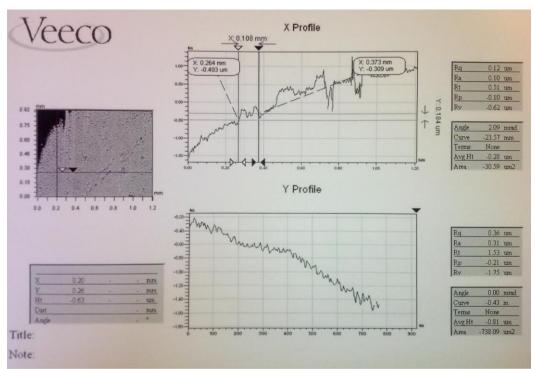

| Fig. 4.1 – Confocal microscopic cross-section of a printed track                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 88        |

| Fig. 4.2 – A 50 µm non-conductive track                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 93        |

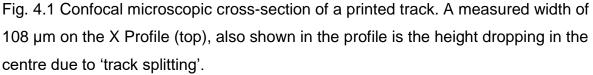

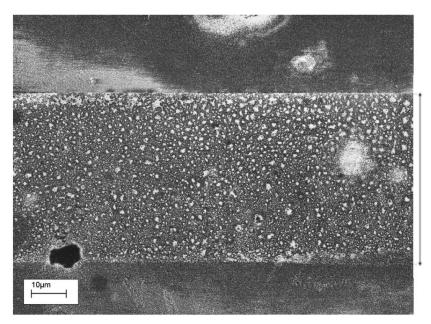

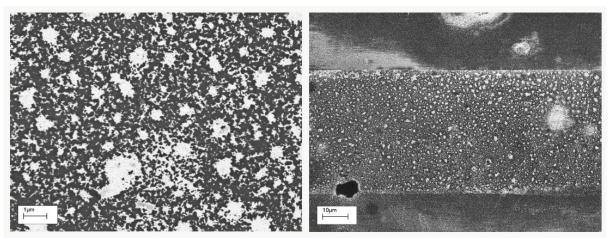

| Fig. 4.3 – Vapour deposited and sputtered gold layer comparison                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95        |

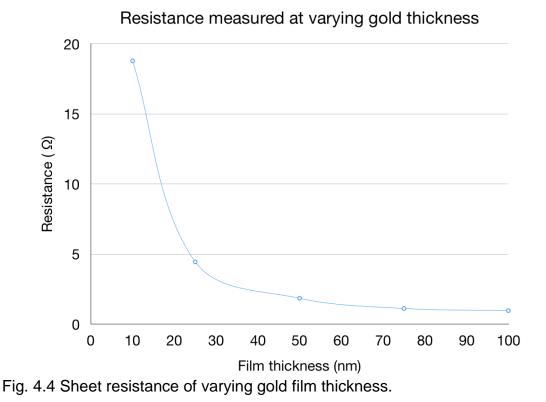

| Fig. 4.4 - Sheet resistance of varying gold film thickness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 97        |

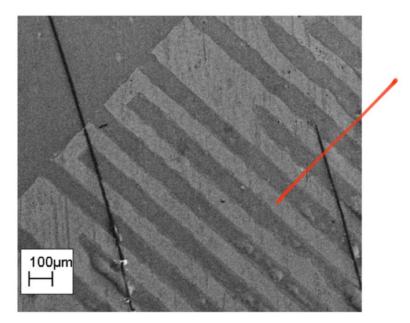

| Fig. 4.5 - Micrograph of inverse results with 50 $\mu$ m track and gap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 98        |

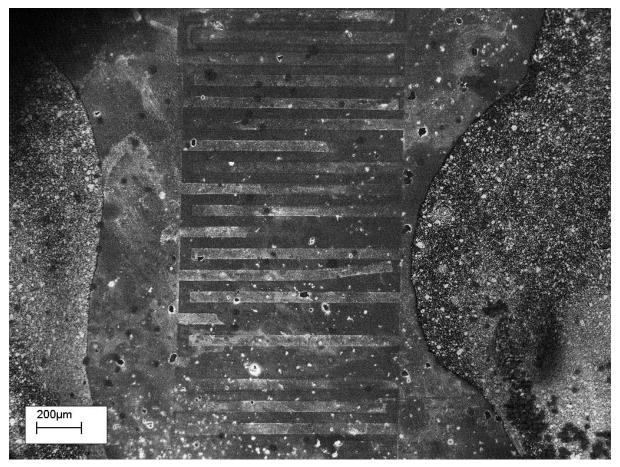

| Fig. 4.6 – Non-conductive 50 $\mu$ m track and gap patterning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 100       |

| Chapter 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

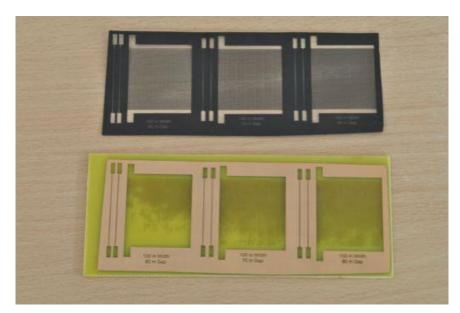

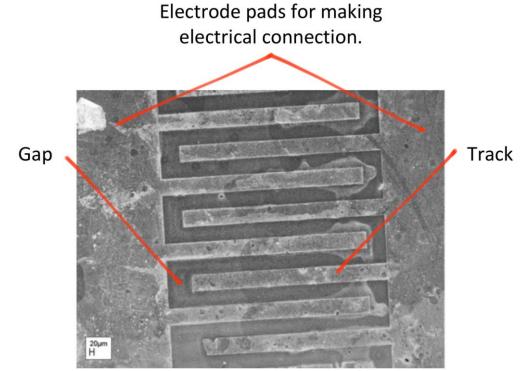

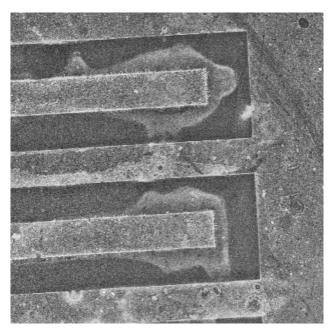

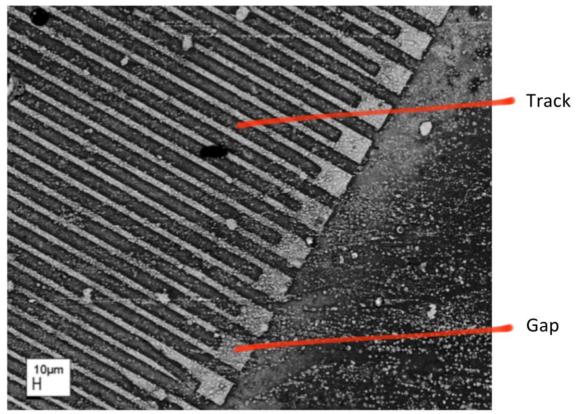

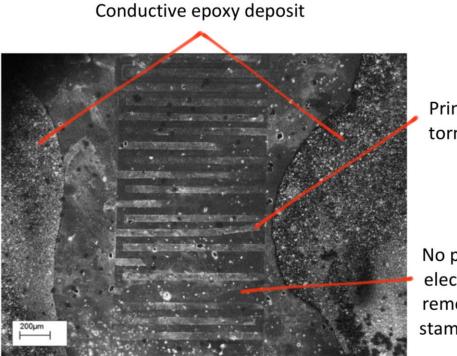

| Fig. 5.1 – Scanning Electron Micrograph of 75 $\mu$ m track and gap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 105       |

| Fig. 5.2 – Enlarged clouding region of 75 $\mu$ m track and gap device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | e 106     |

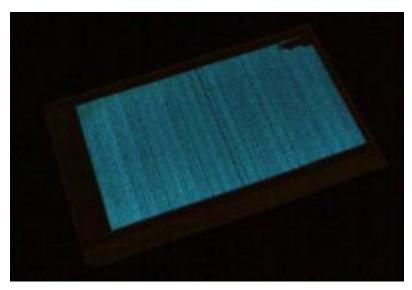

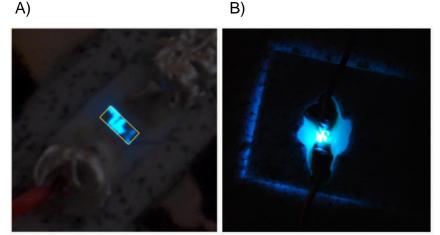

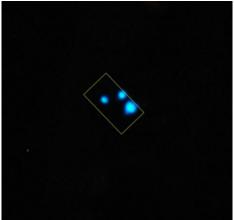

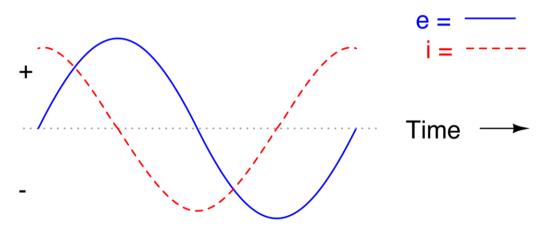

| Fig. 5.3 – Illuminated structure of 75 $\mu$ m track and gap at 400Hz a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | and 2 kHz |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 108       |

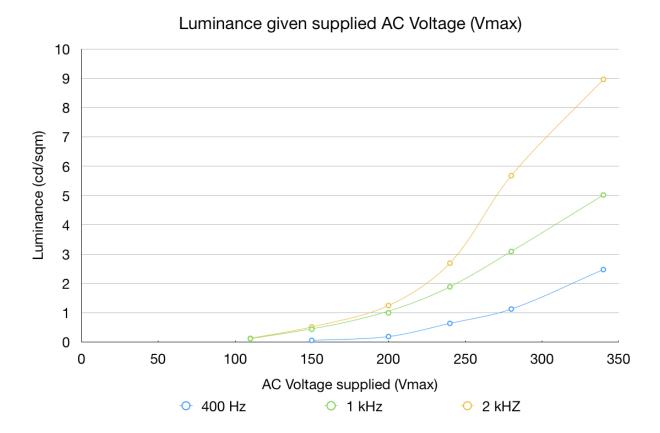

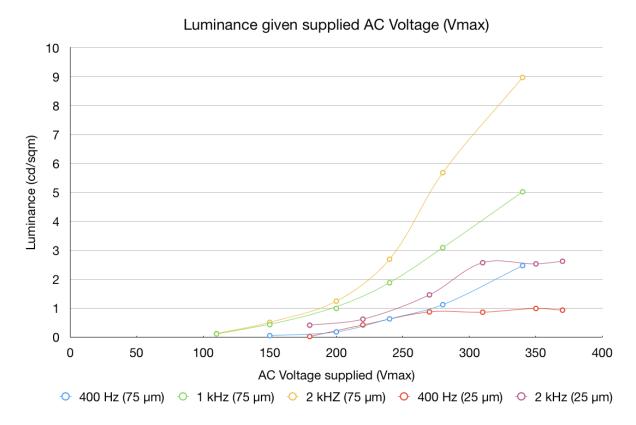

| Fig. 5.4 - Luminance results of the 75 $\mu$ m track and gap structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 109       |

| Fig. 5.5 – Potential for 15 $\mu$ m track and gap features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 112       |

| Fig. 5.6 - 50 $\mu$ m track and gap structure with poor conductivity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 113       |

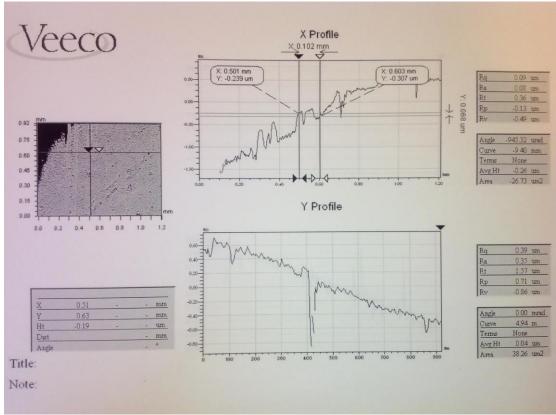

| Fig. 5.7 – 25 $\mu$ m track and gap structure illuminated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 114       |

| Fig. 5.8 – Luminance results of a) 25 $\mu$ m and b) 75 $\mu$ m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 115       |

| Chapter 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

| Fig. 6.1 – Effects of stress on the PDMS electrodes causing tearing te | ng 117    |

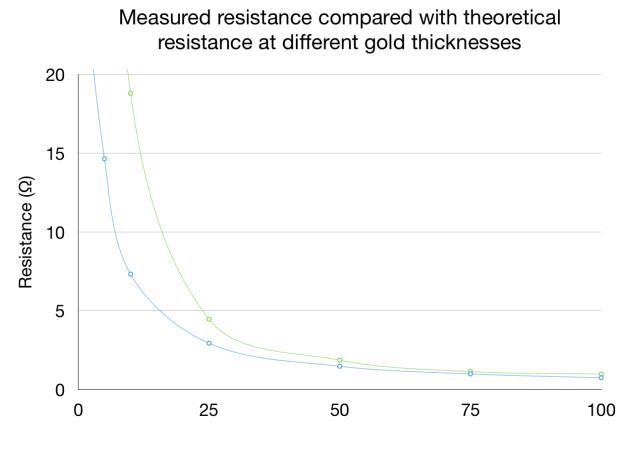

| Fig. 6.2 – Resistance for gold thin films compared with theory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 119       |

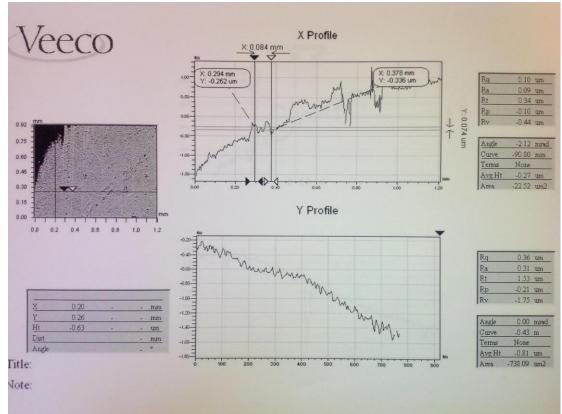

| Fig. 6.3 – Confocal microscopy illustration a line height of 74 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 123       |

| Fig. 6.4 – Confocal microscopy illustration a line height of 68 nm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 124       |

| Fig. 6.5 – A structure of 25 $\mu$ m stimulated with a driving voltage o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | f 65 V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 126       |

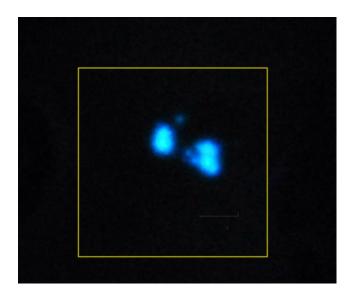

| Fig 6.6 – Phase diagram for a purely capacitive load                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 127       |

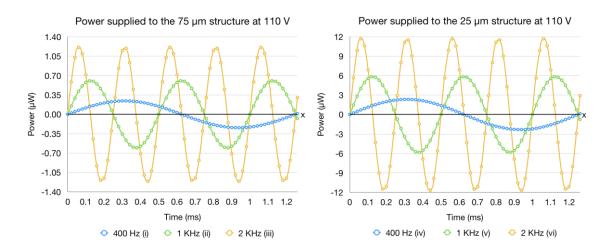

| Fig. 6.7 – Effects of frequency on instantaneous power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 129       |

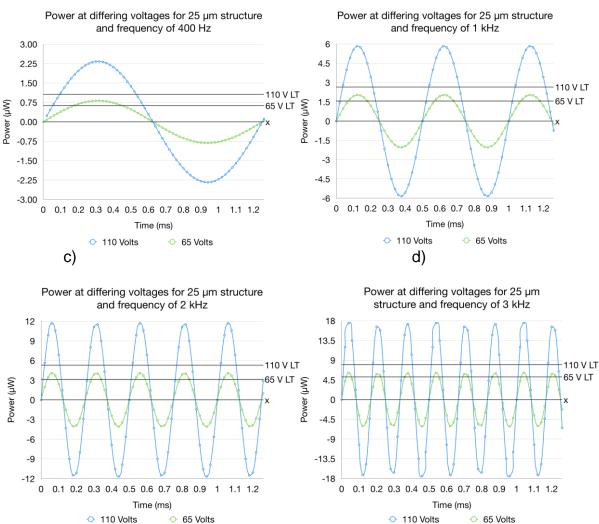

| Fig. 6.8 – Instantaneous power against time for 25µm structure, ir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ncluding  |

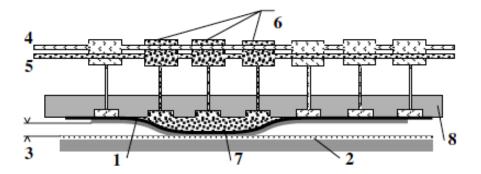

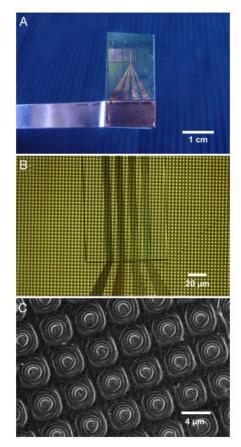

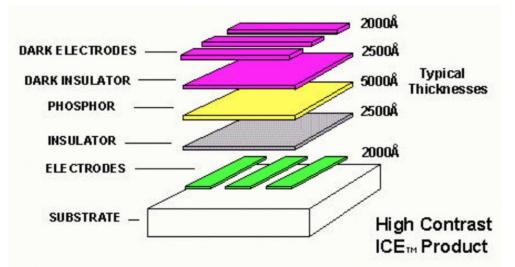

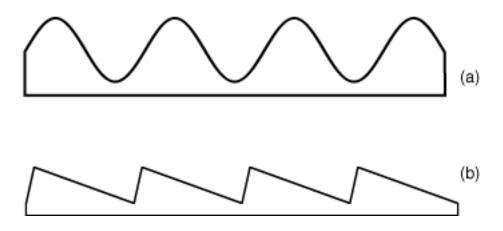

| Luminance threshold                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 130       |