# VNiVERSiDAD D SALAMANCA

CAMPUS OF INTERNATIONAL EXCELLENCE

HIGH-FREQUENCY RESPONSE

AND THERMAL EFFECTS

IN GAN DIODES AND TRANSISTORS:

MODELING AND EXPERIMENTAL

CHARACTERIZATION

DOCTORAL THESIS

HÉCTOR SÁNCHEZ MARTÍN

Salamanca, 2020

# HIGH-FREQUENCY RESPONSE AND THERMAL EFFECTS IN GAN DIODES AND TRANSISTORS: MODELING AND EXPERIMENTAL CHARACTERIZATION

DOCTORAL THESIS

### HÉCTOR SÁNCHEZ MARTÍN

Salamanca, 2020

**D. Tomás González Sánchez**, Catedrático de Electrónica del Departamento de Física Aplicada de la Universidad de Salamanca, y **D. Ignacio Íñiguez de La Torre Mulas**, Profesor Titular del Departamento de Física Aplicada de la Universidad de Salamanca,

### **CERTIFICAN:**

Que la memoria de trabajo de investigación titulado "High-frequency response and thermal effects in GaN diodes and transistors: modeling and experimental characterization" ha sido realizada por D. HÉCTOR SÁNCHEZ MARTÍN para optar al TÍTULO DE DOCTOR CON MENCIÓN DE DOCTOR INTERNACIONAL por la Universidad de Salamanca, bajo el marco del programa de doctorado FÍSICA APLICADA Y TECNOLOGÍA, y que ha sido desarrollada en su totalidad bajo la dirección de los directores de Tesis, en el Área de Electrónica del Departamento de Física Aplicada de la Universidad de Salamanca.

En Salamanca, a 6 de junio de 2020

Dedicado a mi familia

Gizonen lana jakintza dugu: ezagutuz aldatzea, naturarekin bat izan eta harremanentan sartzea. Eta indarrak ongi errotuz, gure sustraiak lurrari lotuz, bertatikan irautea: ezaren gudaz baietza sortuz, ukazioa legetzat hartuz beti aurrera joatea.

Mikel Laboa

# Agradecimientos

No quería dejar pasar esta oportunidad para recordar y agradecer a los directores Tomás González e Ignacio Íñiguez de la Torre que tanto me han ayudado en el proceso de confección de la tesis. Siempre han tenido el despacho abierto a cualquier problema o duda durante todo este tiempo y siempre han estado disponibles para cualquier discusión científica. Gracias de verdad.

También agradecer a Susana Pérez y Javier Mateos sus sugerencias y participación en las distintas reuniones que hemos mantenido todos estos años. Todo ello ha contribuido a que este trabajo sea lo más riguroso y completo posible.

Al resto de miembros del área de electrónica, María Jesús Martín, Raúl Rengel, Jesús Enrique Velázquez, Yahya Meziani, José Manuel Iglesias y José Antonio Novoa. Por supuesto, a los compañeros de despacho Elena Pascual, Beatriz García, Hamham El Mokhtar y Gaudencio Paz. Gracias por el buen clima diario y la ayuda que me habéis prestado este tiempo cuando lo he necesitado.

A los técnicos del laboratorio Daniel Vaquero y Adrián Martín, también parte de esto es labor vuestra. A mis compañeras de trabajo Elsa Pérez y Beatriz Orfao e Vale, cuyo sentido del humor también ha hecho más agradable todo este tiempo. No me quiero olvidar de dar un agradecimiento especial para Óscar García del que tanto aprendí sobre la parte experimental.

Quiero también acordarme de los compañeros de comidas del Fray Luis con los que tan buenos ratos y conversaciones he mantenido. Hicisteis muy amenos esos días en los que que después tenía mis cursos de idiomas.

A los responsables de mi estancia en Lille, Guillaume Ducournau y Cristophe Gaquière, al los que quiero reconocer la buena acogida que me dieron, y por la ayuda en el laboratorio a Nicolas Defrance y Walid Aouimeur, junto al resto de sus estudiantes que me acompañaron esos tres meses y me trataron como a uno más de los suyos, Caroline Maye, Haitham Ghanem e Issa Alaji.

Por último, pero sin duda lo más importante, agradezco a toda mi familia, mi hermana, mis padres y mi abuela, que ya no está, que hayan estado a mi lado todo este tiempo; con vosotros todo es siempre mucho más fácil.

### Abstract

GaN-based self-switching diodes (SSDs) and high-electron-mobility transistors (HEMTs) have been analyzed in DC and AC regimes both from the point of view of experiments and simulations. The non-linearities present in their current-voltage curves allow their operation as zero-bias microwave detectors. Despite of the good properties of GaN, technological problems often related to defects, traps and heating are still issues that need to be investigated to boost the performance of future power electronics.

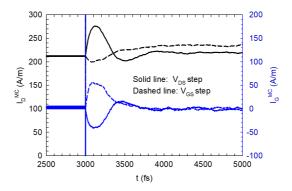

Pulsed and transient measurements performed in SSDs reveal the influence of surface and bulk traps on the DC characteristic and AC impedance. Surface trapping effects become relevant in narrow-channel SSDs as the surface-to-volume ratio of the device is increased, while in wider diodes bulk trapping effects prevail. Measurements show an anomalous enhancement of the microwave detection at low temperature, while the detected voltage exhibits a roll-off in frequency, which can be attributed to the presence of surface and bulk traps.

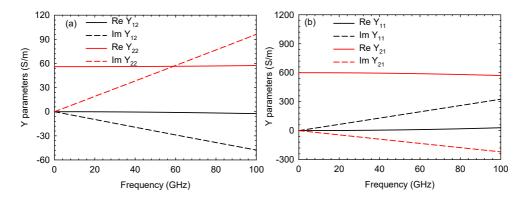

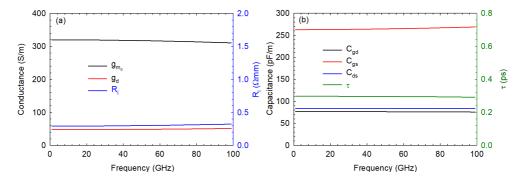

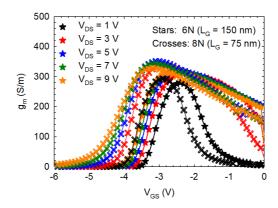

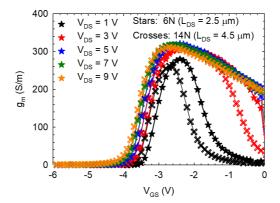

Virgin AlGaN/AlN/GaN HEMTs exhibit strong low-frequency dispersion in the microwave range both in the transconductance and output conductance, attributed to the presence of traps and defects both in the volume of the GaN channel and in the source and drain contacts. These effects have been modeled by means of a modified small-signal equivalent circuit (SSEC), achieving an excellent agreement with the measured S-parameters. The device geometry affects the values of the SSEC elements and hence the cutoff frequencies, the gate length being the most determinant geometrical parameter. For  $L_G=75$  nm,  $f_t$  and  $f_{max}$  are 72 and 89 GHz, respectively, in the HEMTs under analysis.

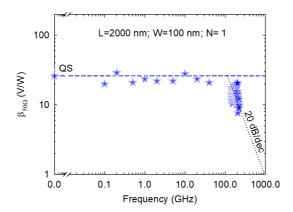

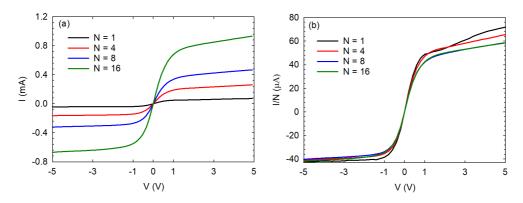

In the SSDs, a noise equivalent power (NEP) of 100-500 pW/Hz<sup>1/2</sup> and a responsivity of tens of V/W was observed with a 50  $\Omega$  source. A cutoff frequency of about 200 GHz, along with a square-law response up to 20 dBm of input power, have been demonstrated. At low frequency, RF measurements exhibit a responsivity that agrees well with the calculations performed by means of a quasi-static (QS) model based on

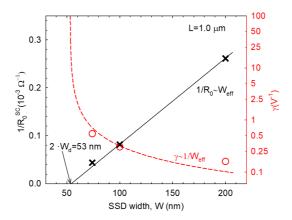

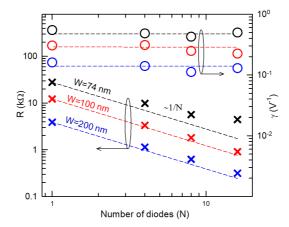

the slope and curvature of the current-voltage curve. Biasing the devices increases the detected voltage with the disadvantage of the power consumption and the excitation of 1/f noise. The QS model predicts that the reduction of the channel width improves the responsivity, what was confirmed by experiments. The increase of the number of diodes in parallel reduces the device impedance; when it coincides with 3 times that of the transmission line (or antenna) to which they are connected, the NEP reaches a minimum value. Diodes with a top-gate electrode, called gated SSDs (G-SSDs), exhibit, in free-space measurements at 300 GHz, a responsivity around 600 V/W and a NEP around 50 pW/Hz<sup>1/2</sup> when the gate bias approaches the threshold voltage. Again, a good agreement is found, but only above sub-threshold gate bias, between the results coming from the QS model and those obtained at low frequency (900 MHz) and in free space at 300 GHz. The NEP value can be improved by increasing the number of channels in parallel.

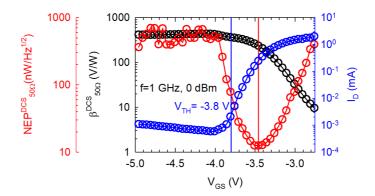

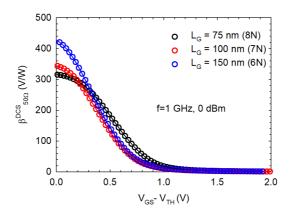

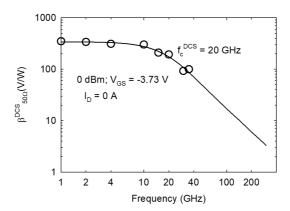

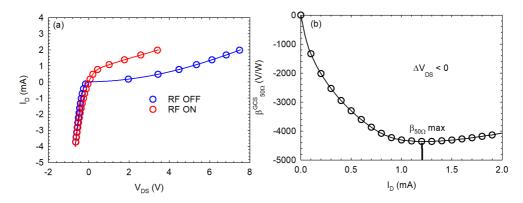

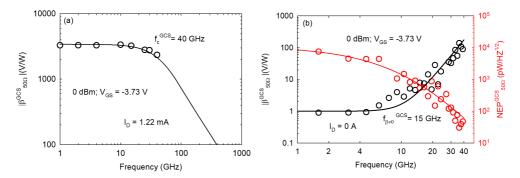

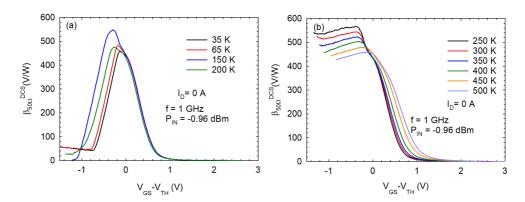

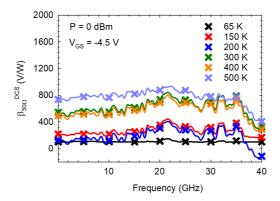

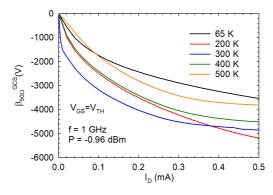

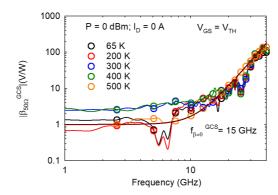

A comparison between the injection of the RF signal at the drain (DCS) or the gate (GCS) electrode in the HEMTs operating as detectors is performed up to 40 GHz. For DCS, a responsitivy around 400 V/W and a NEP around 30 pW/Hz<sup>1/2</sup> were obtained in a HEMT with  $L_G=150$  nm at room temperature under zero drain current and when the gate is biased near pinch-off conditions. On the other hand, the responsivity is strongly enhanced in GCS, up to 1.4 kV/W, but with the drawback that it is necessary to apply a supplementary drain bias of  $I_D=1.2$  mA. Both configurations show a similar cutoff frequency, with a -3 dB roll-off at about 40 GHz. Interestingly, in GCS, at a frequency high enough for the gate-to-drain branch to effectively short the RF signal to the non-linearity, a non-zero detected voltage has been recorded at zero drain current.

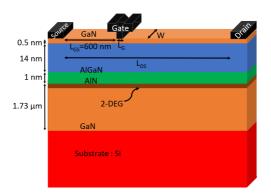

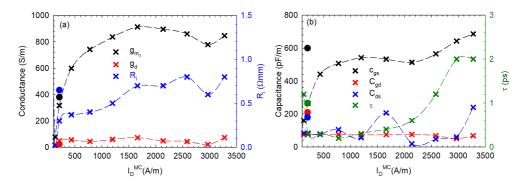

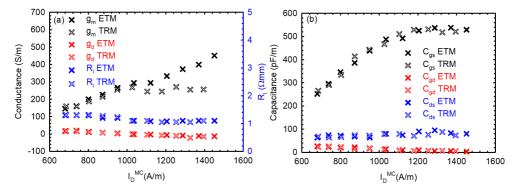

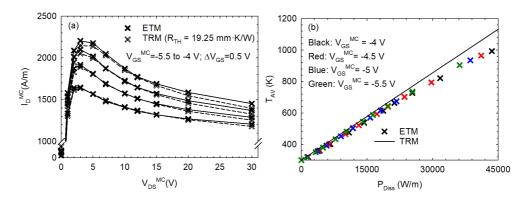

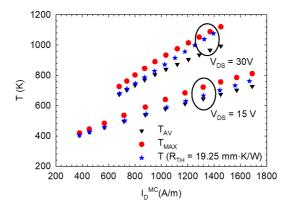

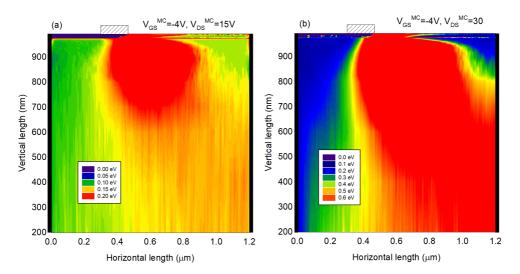

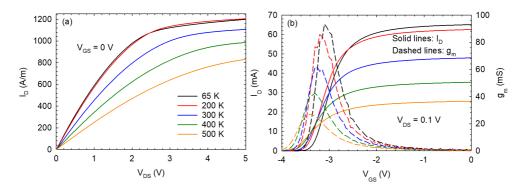

When devices work at high-power conditions, the study of self-heating becomes relevant. Simulations were done by means of an in-house Monte Carlo (MC) tool coupled with two thermal models: (i) a thermal resistance model (TRM) and (ii) an advanced electrothermal model (ETM) based on the self-consistent solution of the steady-state heat conduction equation. At room-temperature, the MC tool was first calibrated by comparison with experimental results in TLMs (transfer length measurement), so that sheet-carrier density and mobility values were replicated. Including the effects of the contact resistance, the Schottky barrier and the thermal boundary resistance, our results are validated with experimental measurements of a HEMT with  $L_{DS} = 1.5 \ \mu \text{m}$  and  $L_G = 150 \ \text{nm}$ , finding a reasonably good agreement. The TRM with well-calibrated values of thermal resistances ( $R_{TH}$ ) provides a similar behavior to ETM simulations. The advantage of the ETM is that it provides the temperature map inside the channel and allows to identify the hotspot location. In addition, the SSEC was obtained with MC simulations, finding a good correspondence with the

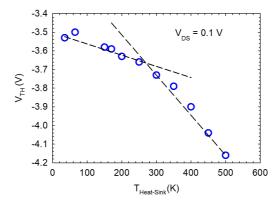

experimental values of the parameters. Impact of the biasing on the SSEC elements and discrepancies between TRM and ETM calculations are discussed. Pulsed measurements up to 500 K are used to estimate the channel temperature and the value of the  $R_{TH}$ . For T < 250 K, the responsivity in the DCS decreases abruptly in the sub-threshold region after reaching a maximum, while it remains practically constant for T > 250 K.

**Keywords:** gallium nitride (GaN), self-switching diode (SSD), high-electron-mobility transistor (HEMT), zero-bias microwave detectors, responsivity, noise-equivalent power, Monte Carlo, small-signal equivalent circuit, trapping effects, heating, thermal resistance.

## Resumen

Se han analizado diodos autoconmutantes (SSDs) y transitores de alta movilidad de electrones (HEMTs) de GaN, tanto en el régimen DC como en AC, tanto desde el punto de vista experimental como de simulaciones. Las no linealidades presentes en las curvas corriente-voltaje permiten su operación como detectores de microondas a polarización nula. A pesar de las buenas propiedades del GaN, existen problemas tecnológicos relacionados con defectos, trampas y calentamiento que deben ser investigados para perfeccionar la electrónica de potencia en el futuro.

Medidas pulsadas y de transitorios de corriente realizadas sobre el SSD han revelado la influencia de trampas volúmicas y superficiales, observándose anomalías en las características DC e impedancia AC. Los efectos superficiales son relevantes en canales estrechos puesto que la relación superficie-volumen del dispositivo aumenta, mientras que en los dispositivos más anchos prevalece la influencia de las trampas de tipo volúmico. Las medidas muestran un incremento anómalo de la detección a bajas temperaturas, mientras que a altas frecuencias el voltaje detectado muestra una caída que atribuimos a la presencia de trampas de tipo superficial y volúmico.

Se ha observado una fuerte dispersión a baja frecuencia tanto de la transconductancia como de la conductancia de salida en HEMTs de AlGaN/AlN/GaN en el rango de microondas, que atribuimos a la presencia de trampas y defectos tanto en el volumen de canal de GaN como en los contactos de fuente y drenador. Estos efectos han sido modelados mediante un circuito equivalente (SSEC) modificado, obteniéndose un acuerdo excelente con los parámetros S medidos. La geometría del dispositivo afecta a los valores de los elementos del circuito equivalente y con ello a las frecuencias de corte, siendo la longitud de puerta el parámetro más influyente. Para  $L_G=75$  nm,  $f_t$  y  $f_{max}$  son 72 y 89 GHz, respectivamente, en los HEMTs estudiados.

En los SSDs caracterizados, se ha observado una potencia equivalente del ruido (NEP) de 100 - 500 pW/Hz<sup>1/2</sup> y una responsividad de decenas de V/W con una fuente de 50  $\Omega$ . Se ha demostrado una frecuencia de corte de unos 200 GHz junto a una respuesta cuadrática hasta 20 dBm de potencia de entrada. A bajas frecuencias, las

medidas RF muestran una responsividad que reproduce bien los cálculos realizados mediante un modelo cuasiestático (QS) basado en la pendiente y la curvatura de las curvas corriente-voltaje. Polarizar los dispositivos aumenta el voltaje detectado a costa del consumo de potencia y la aparición de ruido 1/f. El modelo QS predice que la reducción de la anchura del canal mejora la responsividad, hecho que ha sido confirmado experimentalmente. El aumento del número de diodos en paralelo reduce la impedancia; cuando coincide con el triple de la impedancia de la linea de transmisión o la antena, la NEP alcanza su valor mínimo. Los diodos con puerta (G-SSDs) muestran, en espacio libre a 300 GHz, una responsividad en torno a 600 V/W y una NEP en torno a 50 pW/Hz $^{1/2}$  cerca del voltaje umbral. De nuevo, se obtiene un buen acuerdo entre los resultados del modelo QS, las medidas a 900 MHz y las medidas en espacio libre a 300 GHz, todo ello por encima de la zona subumbral. La NEP mejora al aumentar el número de canales en paralelo.

Se han comparado los resultados de la detección inyectando la señal por el drenador (DCS) y la puerta (GCS) de los HEMTs hasta 40 GHz. Para DCS, se han obtenido una responsividad en torno a 400 V/W y una NEP de 30 pW/Hz<sup>1/2</sup>, en un HEMT con  $L_G=150$  nm a temperatura ambiente bajo condiciones de polarización nula y puerta polarizada cerca del umbral. Por otro lado, la responsividad se incrementa en GCS hasta 1.4 kV/W, con la desventaja de polarizar con una corriente de drenador de  $I_D=1.2$  mA. Ambas configuraciones muestran una frecuencia de corte, con -3 dB de caída, en torno a 40 GHz. Resulta interesante que en GCS y a una frecuencia suficientemente alta para cortocircuitar la rama puerta-drenador con la de la no linealidad, se consigue detectar una responsividad no nula.

El estudio del autocalentamiento se vuelve relevante cuando los dispositivos trabajan en condiciones de alta potencia. Las simulaciones se han realizado con una herramienta Monte Carlo (MC) desarrollada por el grupo y acoplada con dos modelos térmicos: (i) modelo de resistencia térmica (TRM) y (ii) un modelo electrotérmico avanzado y que se basa en la resolución autoconsistente de la ecuación del calor independiente del tiempo. A temperatura ambiente la herramienta MC se calibró comparando con resultados experimentales de TLMs (transfer length measurement), lográndose reproducir la densidad superficial de portadores y la movilidad. Incluyendo la resistencia de contactos, la barrera Schottky y la barrera térmica, nuestros resultados se han validado con medidas experimentales de un HEMT de dimensiones  $L_{DS}=1.5~\mu{\rm m}$  y  $L_G=150~{\rm nm}$ , encontrándose un acuerdo razonable. El TRM da unos resultados similares al ETM con valores de la resistencia térmica ( $R_{TH}$ ) bien calibradas. La principal ventaja del ETM es la posibilidad de obtener mapas de temperatura dentro del canal e identificar la localización de los puntos calientes. También se discute el impacto de la polarización en el SSEC y las discrepancias entre los modelos ETM

y TRM. Se utilizan medidas pulsadas hasta 500 K para estimar la temperatura del canal y el valor de la  $R_{TH}$ . Para T<250 K, la responsividad en DCS decrece abruptamente en la región subumbral tras alcanzar un máximo, mientras que permanece constante a temperaturas T>250 K.

Palabras clave: nitruro de galio (GaN), diodo autoconmutante (SSD), transistor de alta movilidad de electrones (HEMT), detectores de microondas a polarización nula, responsividad, potencia equivalente del ruido, Monte Carlo, circuito equivalente de pequeña señal, efectos de trampas, calentamiento, resistencia térmica.

# Table of Contents

| A١ | bstra         | .ct     |            |                                                |  |   |     | IX   |

|----|---------------|---------|------------|------------------------------------------------|--|---|-----|------|

| Re | esum          | en      |            |                                                |  |   | 2   | XIII |

| Li | st of         | Tables  | 5          |                                                |  |   | -   | XXI  |

| Li | st of         | Figure  | es         |                                                |  |   | X   | XIII |

| Li | st of         | Abbre   | eviations  | and Symbols                                    |  |   | ХX  | XXV  |

| In | ${ m trod}_1$ | uction  |            |                                                |  | 3 | XX: | XIX  |

| 1. | Mod           | dels an | ıd Meası   | ırement Techniques                             |  |   |     | 1    |

|    | 1.1.          | Detect  | ion with   | $\operatorname{diodes}$                        |  |   |     | 2    |

|    |               | 1.1.1.  | Quasi-st   | atic model                                     |  |   |     | 2    |

|    |               | 1.1.2.  | Experim    | ental setups                                   |  |   |     | 4    |

|    | 1.2.          | Monte   | Carlo sir  | nulations                                      |  |   |     | 9    |

|    |               | 1.2.1.  | Monte C    | Carlo tool                                     |  |   |     | 10   |

|    |               |         | 1.2.1.1.   | Semiconductor physical model                   |  |   |     | 12   |

|    |               |         | 1.2.1.2.   | Scattering mechanisms                          |  |   |     | 13   |

|    |               |         | 1.2.1.3.   | Carrier dynamics                               |  |   |     | 15   |

|    |               |         | 1.2.1.4.   | Boundary conditions and electric field $\dots$ |  |   |     | 18   |

|    |               | 1.2.2.  | Thermal    | $\bmod els  \dots \dots \dots \dots \dots$     |  |   |     | 20   |

|    |               |         | 1.2.2.1.   | Thermal resistance model                       |  |   |     | 22   |

|    |               |         | 1.2.2.2.   | Electrothermal model                           |  |   |     | 22   |

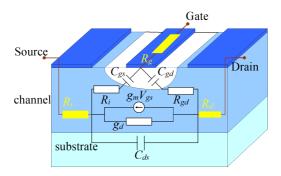

|    | 1.3.          | Small-  | signal cha | aracterization                                 |  |   |     | 23   |

|    |               | 1.3.1.  | Experim    | ental setup                                    |  |   |     | 24   |

|    |               | 1.3.2.  | Monte C    | Carlo simulations                              |  |   |     | 26   |

| 2. | Self | E-Switching Diodes                                | 29  |

|----|------|---------------------------------------------------|-----|

|    | 2.1. | The device                                        | 31  |

|    |      | 2.1.1. Fabrication                                | 31  |

|    |      | 2.1.2. Designs and geometries                     | 32  |

|    | 2.2. | Run 1: Trapping effects in SSDs                   | 35  |

|    |      | 2.2.1. Pulsed I-V measurements                    | 36  |

|    |      | 2.2.2. AC impedance measurements                  | 40  |

|    | 2.3. | Run 2: Detection in SSDs                          | 43  |

|    |      | 2.3.1. State of the art                           | 43  |

|    |      | 2.3.2. Topology of the SSDs under analisys        | 45  |

|    |      | 2.3.3. Number of diodes, width and length         | 46  |

|    |      | 2.3.4. Matching                                   | 50  |

|    |      | 2.3.5. Influence of bias conditions               | 52  |

|    |      | 2.3.6. Influence of temperature                   | 54  |

|    | 2.4. | Gated Self-Switching Diodes                       | 56  |

|    |      | 2.4.1. G-SSDs with antennas (Run 2)               | 56  |

|    |      | 2.4.2. Number of diodes, width and length (Run 3) | 62  |

| 3. | Hig  | h-Electron-Mobility Transistor: DC behavior       | 69  |

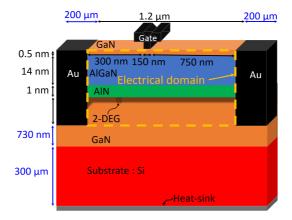

|    | 3.1. | GaN HEMTs                                         | 70  |

|    | 3.2. | Devices under test                                | 72  |

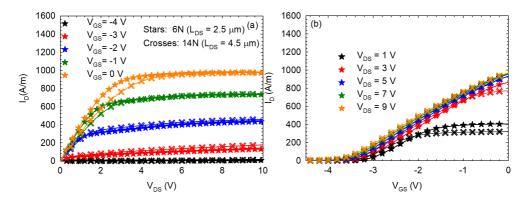

|    | 3.3. | DC characterization                               | 75  |

|    |      | 3.3.1. TLMs                                       | 76  |

|    |      | 3.3.1.1. Experimental results                     | 76  |

|    |      | 3.3.1.2. Monte Carlo simulations                  | 78  |

|    |      | 3.3.2. Transistors                                | 85  |

|    | 3.4. | Thermal effects                                   | 88  |

|    |      | 3.4.1. Room temperature operation                 | 89  |

|    |      | 3.4.2. High-temperature operation                 | 97  |

| 4. | Mic  | crowave Characterization of HEMTs                 | 103 |

|    | 4.1. | Small-signal equivalent circuit                   | 104 |

|    |      | 4.1.1. Extrinsic parameters                       | 104 |

|    |      |                                                   | 110 |

|    |      | 4.1.2. Intrinsic parameters                       | 110 |

|    |      |                                                   | 112 |

|         | 4.1.3.   | Geometrical dependence of the S-SSEC   | 129 |

|---------|----------|----------------------------------------|-----|

|         | 4.1.4.   | Cutoff frequencies $f_t$ and $f_{max}$ | 130 |

| 4.2.    | Detect   | ion with HEMTs                         | 134 |

|         | 4.2.1.   | Drain-coupling scheme                  | 136 |

|         | 4.2.2.   | Gate-coupling scheme                   | 140 |

|         | 4.2.3.   | Influence of temperature               | 142 |

| Conclu  | sions    |                                        | 147 |

| A. Infl | uence    | of the Geometry                        | 163 |

| A.1.    | Influer  | ace of gate length                     | 164 |

| A.2.    | Influe   | ace of the drain-to-source length      | 165 |

| B. Pub  | olicatio | ons and Conference Contributions       | 167 |

| Bibliog | graphy   |                                        | 171 |

# List of Tables

| 1.1. | GaN and AlGaN electron parameters                                                                                                                                                                                                              | 13  |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.1. | Summary of the devices of each run that have been characterized in this thesis attending to the geometries, dimensions and number $(N)$ of diodes in parallel.                                                                                 | 34  |

| 2.2. | Summary of figures of merit for detection with different technologies and materials                                                                                                                                                            | 44  |

| 2.3. | Summary of figures of merit for detection in SSDs fabricated with different materials                                                                                                                                                          | 44  |

| 2.4. | Geometry, channel width $W$ and length $L$ , and number of channels in parallel $N$ of SSDs fabricated on SiC substrate that were measured                                                                                                     | 45  |

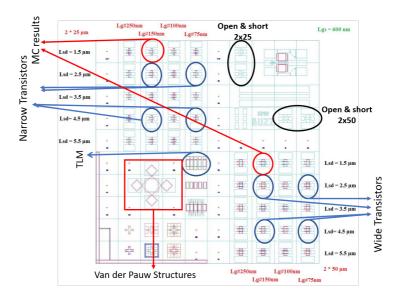

| 3.1. | Dimensions of the TLMs shown in Figure 3.4                                                                                                                                                                                                     | 73  |

| 3.2. | Numbers assigned to identify the transistors shown in Figure 3.4. Along the manuscript a letter N (narrow, W= 2 $\times$ 25 $\mu m)$ or W (wide, W= 2 $\times$ 50 $\mu m)$ referred to the width will be added to the number of the transistor | 74  |

| 3.3. | Thermal conductivities used in the resolution of the HCE $$                                                                                                                                                                                    | 91  |

| 3.4. | Average temperatures in each model at three bias point of interest $\dots \dots$                                                                                                                                                               | 94  |

| 3.5. | Experimental $R_{TH}$ at different $T_{amb}$ , and $T_{channel}$ estimated with $P_{Diss}$ at $V_{DS} = 10 \text{ V} \dots $             | 102 |

| 4.1. | Extrinsic elements obtained from the measurements, extracted with the software Ques according to the proposed equivalent circuits                                                                                                              | 109 |

| 4.2. | Parameters of the SSEC for the two models before and after HPC $\ \ldots \ \ldots$                                                                                                                                                             | 119 |

| 4.3. | Parameters of the S-SSEC extracted from measurements (at $V_{DS}=6$ V, $V_{GS}=-3$ V) and MC simulations (at $V_{DS}^{MC}=6$ V, $V_{GS}^{MC}=-8$ V)                                                                                            | 123 |

| 4.4. | Intrinsic elements of the S-SSEC model after the optimization with Qucs at the bias point $V_{GS}$ =-3 V, $V_{DS}$ = 6 V                                                                                                                       | 130 |

| 4.5. | Experimental intrinsic and extrinsic cutoff frequencies for eight transistors. |     |

|------|--------------------------------------------------------------------------------|-----|

|      | Bias point $V_{GS}$ =-3 V and $V_{DS}$ = 6 V                                   | 132 |

|      |                                                                                |     |

| Δ 1  | Dimensions of the transistors characterized in the wafer                       | 163 |

# List of Figures

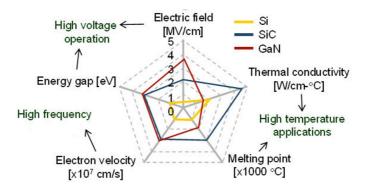

| 1.   | Comparison of material properties for high-power and high-frequency applications: Si, SiC and GaN                                                                | XXXIX |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

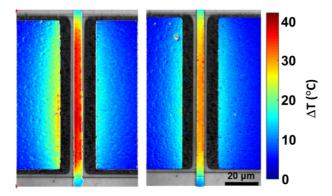

| 2.   | Thermoreflectance cartography of an AlGaN/GaN HEMT, where the temperature scale on top right indicates the temperature increase with respect to room temperature | XLII  |

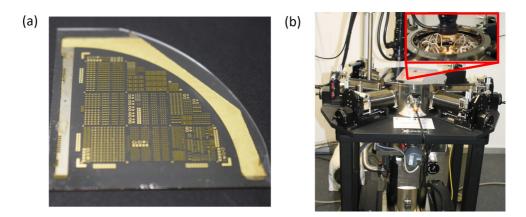

| 3.   | Picture of the RF Devices Laboratory of the USAL http://nanoelec.usal.es/facilities                                                                              | XLIV  |

| 4.   | (a) Picture of the wafer with the GaN-SSDs processed in the clean room of the R&D facilities of USAL. (b) Cryogenic probe station                                | XLV   |

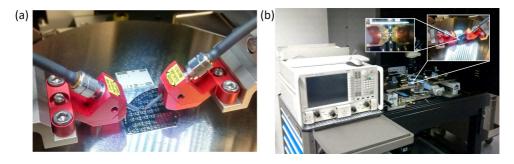

| 5.   | (a) Picture of the wafer with the HEMTs, calibration substrate and RF probes. (b) Probe station and equipment used in the microwave characterization             | XLV   |

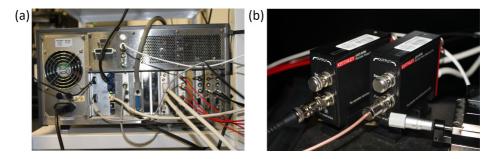

| 1.1. | (a) SMUs, PMUs and C-V connectors of the Keithley 4200-SCS semiconductor analyzer and (b) RPM-4225 remote amplifiers/switches                                    | 5     |

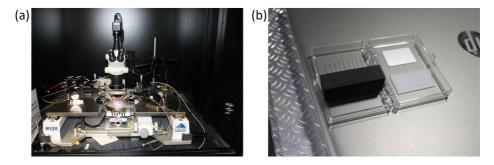

| 1.2. | (a) Room temperature Cascade M150 probe station and (b) needles used in the DC measurements                                                                      | 5     |

| 1.3. | Setup to measure detection for frequencies up to 1 GHz. The zoom shows the DC needles used in this setup                                                         | 6     |

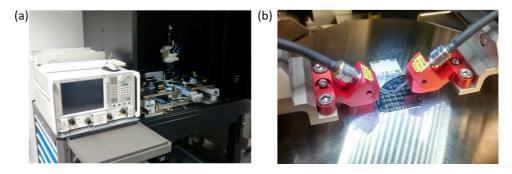

| 1.4. | Images of (a) the Vector Network Analyzer N5244A PNA-X and (b) the GSG RF probes (100 $\mu$ m pitch) used for on-wafer characterization                          | 7     |

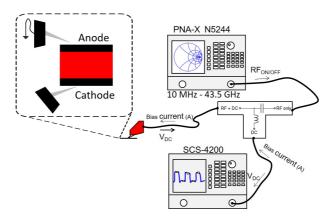

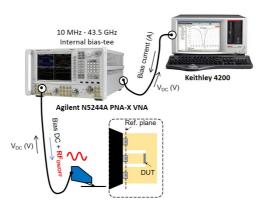

| 1.5. | Setup to measure detection for frequencies between 10 MHz and 43.5 GHz. The zoom shows the CPW access and GSG RF probe used in this setup                        | 8     |

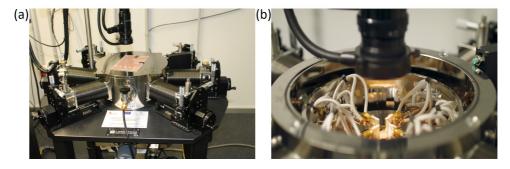

| 1.6. | Picture of (a) the LakeShore CRX-VF cryogenic probe station and (b) vacuum chamber with the probes and the sample holder                                         | 8     |

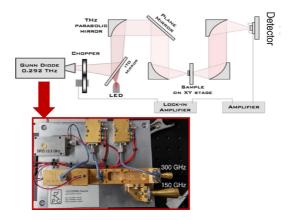

| 1.7. | Description of the free-space setup and the THz source                                                                                                           | 9     |

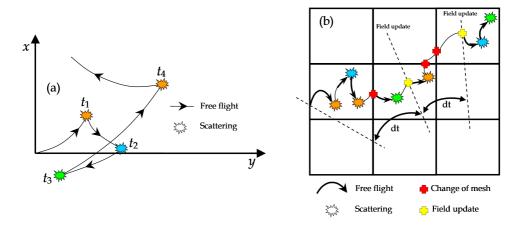

| 1.8.  | (a) Simple diagram of the single particle simulation in real space under a uniform electric field applied in the x-direction. (b) Scheme of the 2D device simulator with the main events indicated by symbols                                                                                                                                                                                             | 12 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.9.  | Election of the type of scattering mechanism after a free flight                                                                                                                                                                                                                                                                                                                                          | 17 |

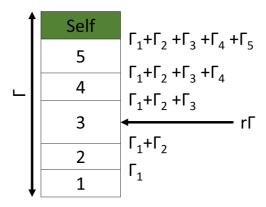

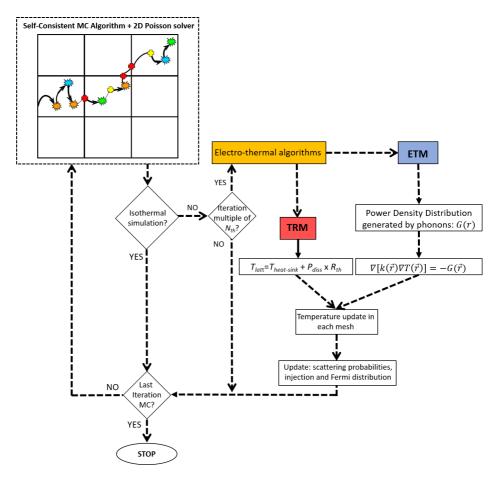

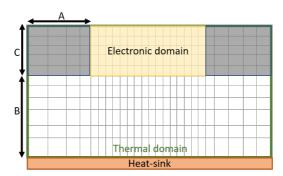

|       | Scheme of the coupling of thermal algorithms with the 2D-MC electrical device simulation                                                                                                                                                                                                                                                                                                                  | 21 |

| 1.11. | Scheme of the electronic and thermal domains and the division of the device into cells                                                                                                                                                                                                                                                                                                                    | 22 |

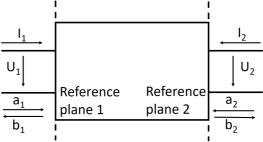

| 1.12. | Scheme of the four-pole (or two-port) device                                                                                                                                                                                                                                                                                                                                                              | 24 |

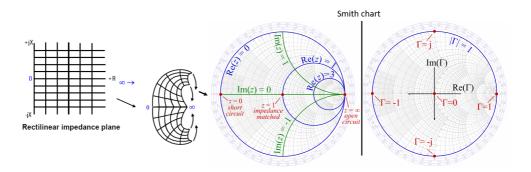

| 1.13. | . Conversion from the positive impedance plane to the Smith chart                                                                                                                                                                                                                                                                                                                                         | 25 |

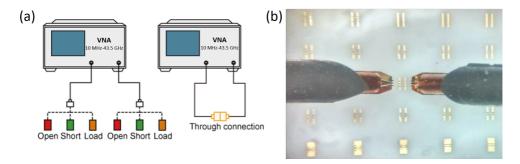

| 1.14. | (a) SOLT calibration process and (b) Allstron AC-2 calibration substrate                                                                                                                                                                                                                                                                                                                                  | 26 |

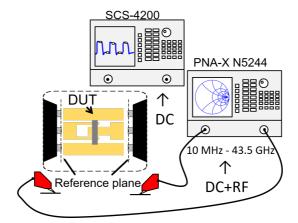

| 1.15. | Setup used to measure the S-parameters                                                                                                                                                                                                                                                                                                                                                                    | 26 |

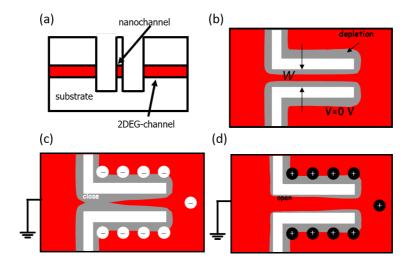

| 2.1.  | <ul> <li>(a) Front-view scheme showing the depth of the trenches in a 2DEG heterostructure, allowing the formation of the nanochannel, (b) depletion region originated by the charges located at the walls of the trenches at equilibrium,</li> <li>(c) and (d) redistribution of charges and electrostatic effects for negative and positive bias applied to the right terminal, respectively</li> </ul> | 30 |

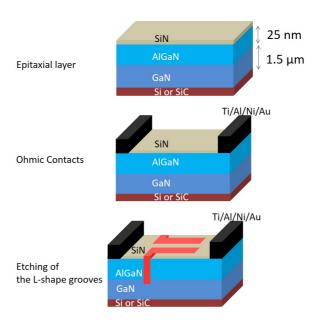

| 2.2.  | Fabrication process flow of an SSD                                                                                                                                                                                                                                                                                                                                                                        | 32 |

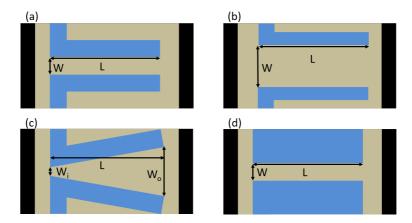

| 2.3.  | (a) T-shape or rectangular narrow SSD with a channel of width $W$ and length $L$ , (b) rectangular wide channel, (c) V-shape SSD with a channel of length $L$ and opening $W_i$ at the entrance and $W_o$ at the output and (d) symmetrical channel with both sides fully etched                                                                                                                          | 33 |

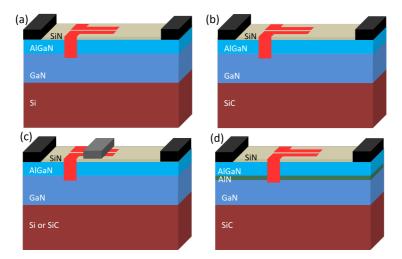

| 2.4.  | Topology and heterostructure of the SSDs with (a) Si substrate, (b) SiC substrate, (c) gate and (d) AlN spacer between the AlGaN and GaN layers                                                                                                                                                                                                                                                           | 34 |

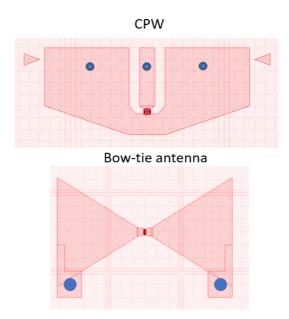

| 2.5.  | Schematic picture of the accesses used in the characterization of the devices. CPW and broadband bow-tie antennas are used in the RF characterization .                                                                                                                                                                                                                                                   | 35 |

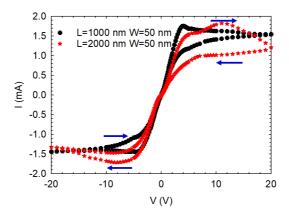

| 2.6.  | DC current-voltage characteristics of two narrow diodes ( $W=50$ nm) with different length ( $L=1000$ nm and 2000 nm). Measurements are performed in dual-sweep, arrows indicate the direction of the measurement                                                                                                                                                                                         | 36 |

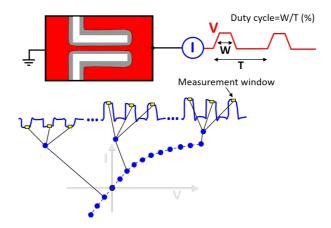

| 2.7.  | Schematic picture of the pulsed measurement setup for the SSD                                                                                                                                                                                                                                                                                                                                             | 37 |

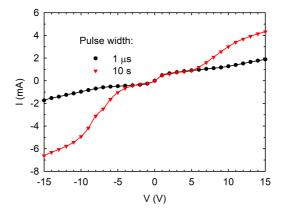

| 2.8.  | Pulsed current-voltage characteristic of an array of 16 SSDs in parallel, with $L=1000$ nm and $W=75$ nm, measured with two different pulse widths, 1 $\mu \rm s$                                                                                                                                                                                                                                         |    |

|       | (in black) and 10 s (in red). The duty cycle is $1\%$                                                                                                                                                                                                                                                                                                                                                     | 38 |

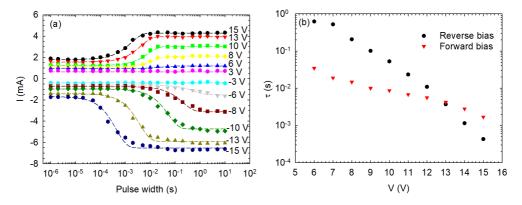

| 2.9. | (a) Symbols: measured current $vs$ . pulse width for different bias conditions. Dotted lines: fitting of the measurements to Equation 2.1. (b) Detrapping time constant extracted from the fittings in (a) $vs$ . applied voltage                                                                                                                                                                         | 38 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

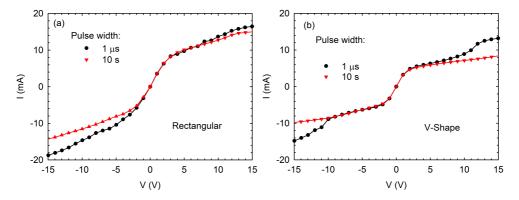

| 2.10 | . Pulsed current-voltage characteristics of an array of (a) 16 wide rectangular SSDs in parallel with $L=2000$ nm and $W=500$ nm, and (b) 16 V-shape SSDs in parallel with $L=1000$ nm, $W_i=250$ nm and $W_o=550$ nm. Two pulse widths are considered: 1 $\mu$ s (in black) and 10 s (in red)                                                                                                            | 39 |

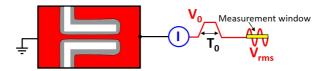

| 2.11 | . Schematic sketch of C-V impedance measurement setup for the SSD $$                                                                                                                                                                                                                                                                                                                                      | 40 |

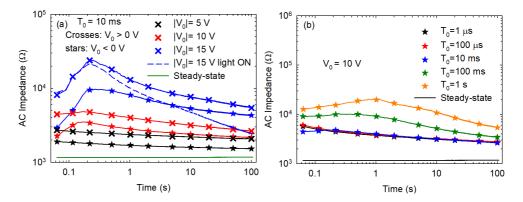

| 2.12 | Zero-bias AC impedance transients measured just after the application of prepulses of (a) width $T_0=10$ ms and different amplitudes $V_0$ in forward and reverse bias and (b) amplitude $V_0=10$ V and different widths $T_0$ to the narrow-channel SSDs of Figure 2.8. The steady-state value (at equilibrium) is also shown for comparison                                                             | 41 |

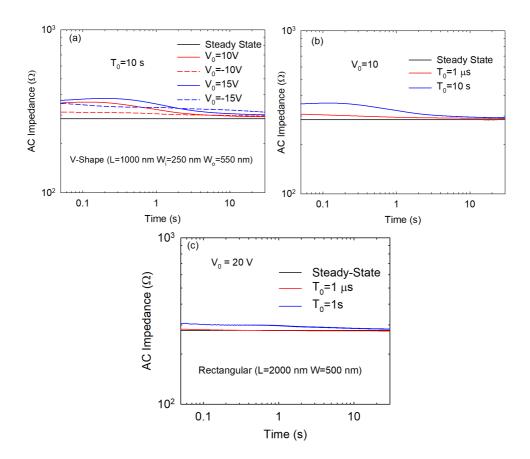

| 2.13 | Zero-bias AC impedance transients measured just after the application, to the wide-channel diodes of Figure 2.10, of pre-pulses with: (a) and (c) constant $T_0$ and different $V_0$ and (b) constant $V_0$ and different $T_0$ . (a) and (c) correspond to the V-shape diode and (b) to the wide rectangular one. The steady-state value measured without the pre-pulse is also shown for comparison     | 42 |

| 2.14 | Log-log plot of $\beta_{50\Omega}$ vs. frequency measured in a SSD with just one channel of length $L=2~\mu{\rm m}$ and width $W=100~{\rm nm}$ . The horizontal dash line and the star at the lowest frequency represents the QS value of $\beta_{50\Omega}$                                                                                                                                              | 46 |

| 2.15 | . (a) Current-voltage characteristics of SSDs with $L=1~\mu\mathrm{m},W=100~\mathrm{nm}$ and $N=1,4,8$ and 16 (b) Current normalized by the number of channels in parallel $N$                                                                                                                                                                                                                            | 47 |

| 2.16 | $1/R_0^{SC}$ (left axis) and $\gamma$ (right axis) extracted from the QS model as a function of the channel width. The black and red lines correspond to trends $W_{eff}$ and $1/W_{eff}$ , respectively. SC stands for single channel                                                                                                                                                                    | 48 |

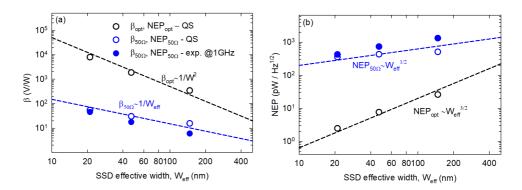

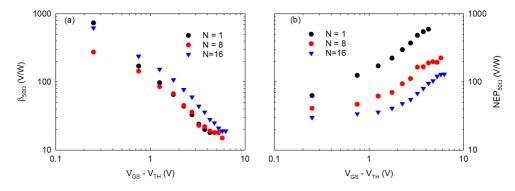

| 2.17 | $R_0$ (left axis) and $\gamma$ (right axis) $vs$ . the number of channels in parallel for three channel widths, $W=74,100$ and 200 nm. $L=1\mu{ m m}$                                                                                                                                                                                                                                                     | 48 |

| 2.18 | Log-log plots of (a) responsivity and (b) $NEP$ $vs$ . effective channel width extracted with the QS model from DC measurements (void symbols) and measured experimentally at 1 GHz (solid symbols) in SSDs with $N=1$ and $L=1~\mu m$ . $\beta_{opt}$ and $\beta_{50\Omega}$ were computed using Equations 1.8 and 1.9, respectively, and $NEP$ using Equations 1.12 and 1.13. Dashed lines indicate the | 46 |

|      | trends predicted by the model                                                                                                                                                                                                                                                                                                                                                                             | 49 |

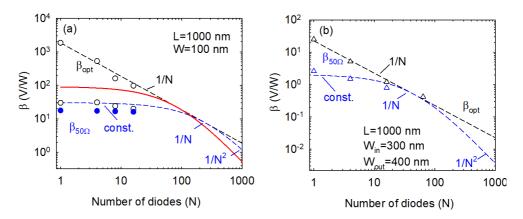

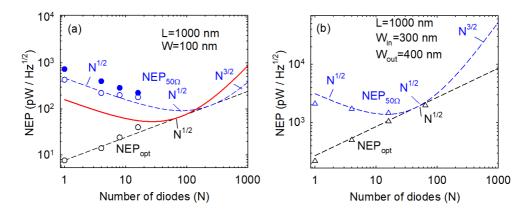

| 2.19. | Log-log plot of responsivity $vs.$ $N$ extracted with the QS model (void symbols) and measured experimentally at 1 GHz (solid symbols) in (a) T-shape $(L=1~\mu\mathrm{m}~\mathrm{and}~W=100~\mathrm{nm})$ and (b) V-shape $(L=1~\mu\mathrm{m},~W_{in}=300~\mathrm{nm})$ and $W_{out}=400~\mathrm{nm})$ SSDs. The dotted lines indicate the trends of $\beta_{opt}$ and $\beta_{50\Omega}$ following Equations 1.8 and 1.9 for $Z_s=50~\Omega$ . The solid red line shows reponsivity calculated using $Z_s=150~\Omega$ . | 51 |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.20. | Log-log plot of $NEP$ $vs.$ $N$ extracted with the QS model (void symbols) and measured at 1 GHz (solid symbols) in (a) T-shape ( $L=1~\mu{\rm m}$ and $W=100~{\rm nm}$ ) and (b) V-shape ( $L=1~\mu{\rm m}$ , $W_{in}=300~{\rm nm}$ and $W_{out}=400~{\rm nm}$ ) SSDs. The dotted lines indicate the trends of $NEP_{opt}$ and $NEP_{50\Omega}$ following Equations 1.12 and 1.13 for $Z_s=50~\Omega$ , while the red solid line shows the same analytical calculations using $Z_s=150~\Omega$                           | 52 |

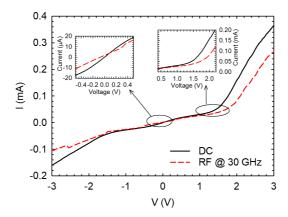

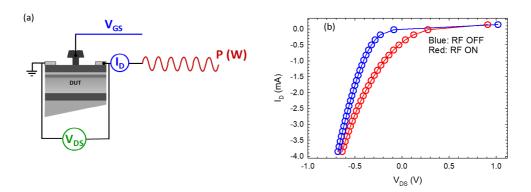

| 2.21. | Current-voltage curves in absence and presence of a 0 dBm power RF signal at 30 GHz applied to an SSD ( $L=1000$ nm, $W=74$ nm) of Run 1. Insets: zooms around 0 bias (left) and 1.3 V (right).                                                                                                                                                                                                                                                                                                                           | 53 |

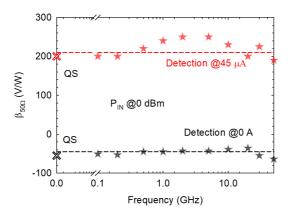

| 2.22. | Impact of biasing the SSD on the value of $\beta_{50\Omega}$ as a function of frequency. The horizontal dashed line and the cross at zero frequency represent the QS value. Incident power of 0 dBm and 0 and 45 $\mu A$ bias points                                                                                                                                                                                                                                                                                      | 54 |

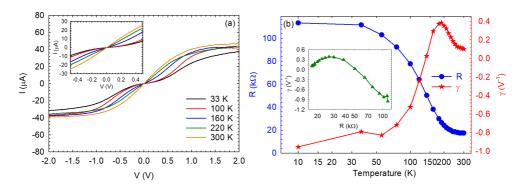

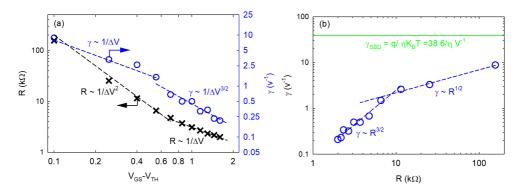

| 2.23. | (a) $I\text{-}V$ curves of a SSD with $L=1~\mu\mathrm{m}$ and $W=80~\mathrm{nm}$ measured at different temperatures. The inset shows a zoom around zero bias. (b) Resistance $R$ and bowing coefficient $\gamma$ obtained with the QS model as a function of temperature. The inset shows $\gamma~vs.~R$                                                                                                                                                                                                                  | 55 |

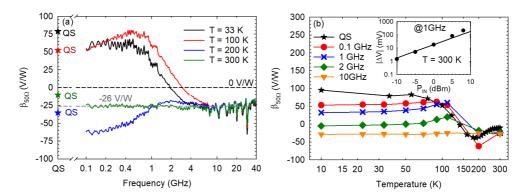

| 2.24. | (a) $\beta_{50\Omega}$ as a function of the RF frequency measured at different temperatures. The stars represent the $\beta_{50\Omega}$ extracted with the QS model. (b) QS value compared with $\beta_{50\Omega}$ measured at 0.1, 1 and 10 GHz as a function of temperature. Inset: detected voltage as a function of the input power, the line confirms the square-law detection                                                                                                                                       | 56 |

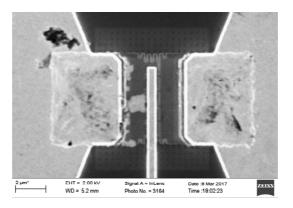

| 2.25. | SEM image of G-SSD with top gate fabricated in the center of the channel. The dimensions of the channels are $L=1~\mu{\rm m}$ and $W=100~{\rm nm}$ . $N=4~\dots$                                                                                                                                                                                                                                                                                                                                                          | 57 |

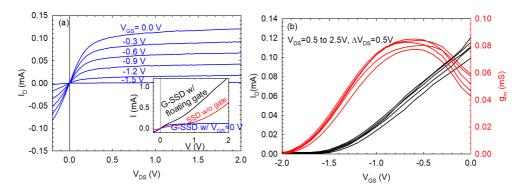

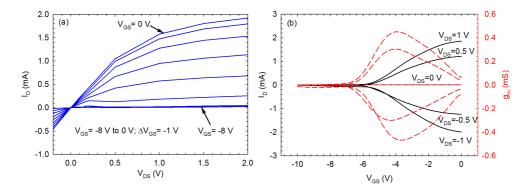

| 2.26. | (a) Output characteristics and (b) transfer characteristics (left axis) and transconductance $g_m$ (right axis) of the G-SSD under test. The inset shows the $I$ - $V$ curves of the G-SSD in open gate operation (floating gate) and a SSD without gate with a similar geometry (74 nm width and 1.0 $\mu$ m length)                                                                                                                                                                                                     | 58 |

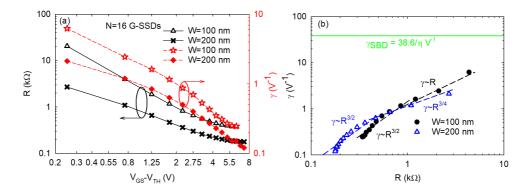

| 2.27. | (a) $R$ and $\gamma$ extracted from the DC measurements of the $I_D - V_{DS}$ curves as a function of $V_{GS}$ - $V_{TH}$ at $I_D = 0$ A. Dashed lines show different dependencies on $(V_{GS} - V_{TH})$ for eye guiding. (b) $\gamma vs$ . $R$ , with the eye guiding lines showing the $\gamma \sim R^{3/2}$ and $\gamma \sim R^{1/2}$ dependencies, appearing at high and low $V_{GS}$ ,                                                                                                                              |    |

|       | respectively. The green line corresponds to the value of $\gamma$ in SBD with $\eta=1$                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59 |

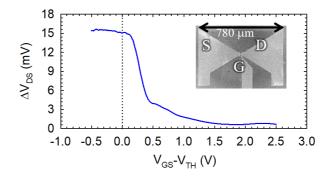

| 2.28. | Output voltage when illuminating the sample with a 300 GHz beam as a function of $V_{GS}$ - $V_{TH}$ at $I_D=0$ A. The inset shows the geometry of the bow-tie integrated antenna                                                                                                                                                                                                                                                                                                                                                      | 60 |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

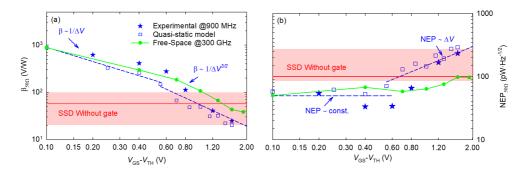

| 2.29. | Comparison of the values of (a) $\beta_{50\Omega}$ and (b) $NEP_{50\Omega}$ $vs.$ $V_{GS}-V_{TH}$ (at $I_D=0.0$ A) calculated from the DC measurements (QS model) with those obtained in the experimental free-space setup at 300 GHz and the RF measurements at 900 MHz. The values for the SSD without gate and the same geometry are shown by the horizontal solid line, while the results of GaN based SSDs with other geometries (fabricated in the same run and published in the literature) are indicated by the shaded regions | 62 |

| 2.30. | (a) Output characteristics, and (b) transfer characteristics (left-axis) and $g_m$ (right axis) of a G-SSD with $L=1000$ nm, $W=100$ nm and $N=16$                                                                                                                                                                                                                                                                                                                                                                                     | 63 |

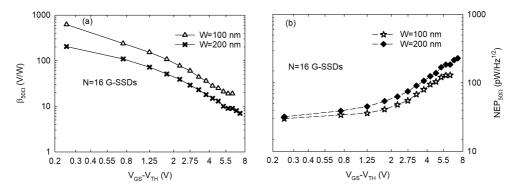

| 2.31. | (a) $\beta_{50\Omega}$ and (b) $NEP_{50\Omega}$ extracted from the QS model as a function of $V_{GS}$ - $V_{TH}$ at $I_D=0$ A in G-SSDs with RF accesses, with $L=1000$ nm, $W=100$ nm and different number of channels in parallel                                                                                                                                                                                                                                                                                                    | 63 |

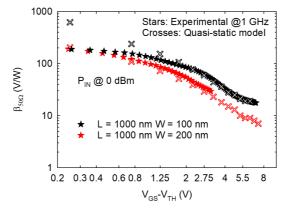

| 2.32. | (a) $R$ (left axis) and $\gamma$ (rigth axis) extracted from the QS model at $I_D=0$ A, and (b) $\gamma$ $vs.$ $R$ for G-SSDs with RF accesses, with $L=1000$ nm, $N=16$ and two different widths, $W=100$ nm and $W=200$ nm. The green line corresponds to the value of $\gamma$ in a SBD with $\eta=1$                                                                                                                                                                                                                               | 64 |

| 2.33. | (a) $\beta_{50\Omega}$ and (b) $NEP_{50\Omega}$ vs. $V_{GS}$ - $V_{TH}$ at $I_D=0$ A, extracted from the QS model for G-SSDs with RF accesses, with $L=1000$ nm, $N=16$ and two different widths, $W=100$ nm and $W=200$ nm                                                                                                                                                                                                                                                                                                            | 65 |

| 2.34. | $eta_{50\Omega}$ vs. $V_{GS}-V_{TH}$ at $I_D=0$ A extracted from the QS model (crosses) and RF measurements (stars) for G-SSDs with RF accesses, with $L=1~\mu{\rm m},$ $N=16$ and two widths, $W=100$ nm and $W=200$ nm. $P_{IN}=0$ dBm                                                                                                                                                                                                                                                                                               | 65 |

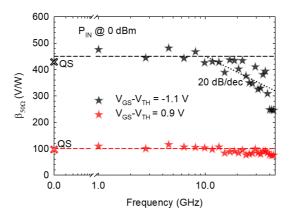

| 2.35. | $eta_{50\Omega}$ $vs.$ frequency measured at $I_D=0$ A in a G-SSD with $W=200$ nm, $L=1~\mu{\rm m}$ and $N=16$ , at $V_{GS}$ - $V_{TH}=0.9$ V and $V_{GS}$ - $V_{TH}=-1.1$ V. $P_{IN}=0$ dBm. The horizontal dashed line and the cross at zero frequency                                                                                                                                                                                                                                                                               |    |

|       | represent the QS value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 66 |

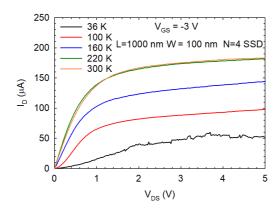

| 2.36. | Output characteristics measured in a G-SSD with $W=100$ nm, $L=1~\mu{\rm m}$ and $N=4$ at five temperatures, for $V_{GS}=$ -3 V                                                                                                                                                                                                                                                                                                                                                                                                        | 67 |

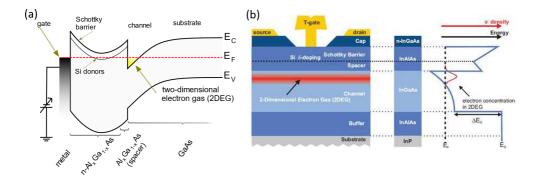

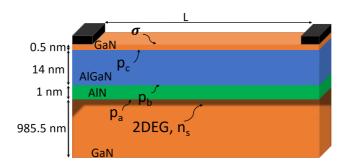

| 3.1.  | Heterostructure and band structure of (a) an AlGaAs/GaAs HEMT, which includes an n-doped AlGaAs barrier, and (b) an InAlAs/InGaAs HEMT, which                                                                                                                                                                                                                                                                                                                                                                                          | -  |

| 3.2.  | includes a very narrow $\delta$ -doping layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 71 |

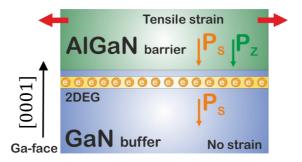

| J.∠.  | ture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71 |

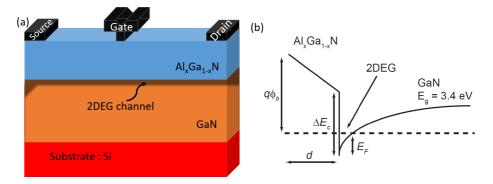

| 3.3.  | (a) Heterostructure and (b) band structure of a typical AlGaN/GaN HEMT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72 |

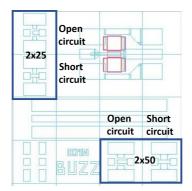

| 3.4.  | Layout of a section of the wafer. HEMTs are located in the up-left and down-right quadrants. The up-right quadrant contains $dummies$ and the down-left                                                                                                                                                                                             |    |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|       | one has TLMs, Shottky contacts and van der Pauw structures                                                                                                                                                                                                                                                                                          | 73 |

| 3.5.  | Geometry of a HEMT with its characteristic dimensions: gate length $(L_G)$ , drain-to-source length $(L_{DS})$ , gate-to-source length $(L_{GS})$ and width $(W)$ .                                                                                                                                                                                 | 74 |

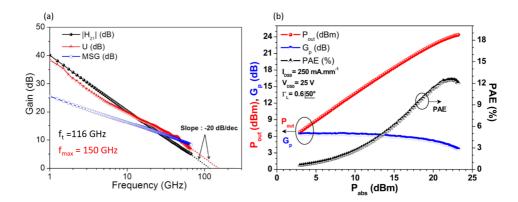

| 3.6.  | Figures of merit of HEMTs: (a) $H_{21}$ ( $f_t$ ), $U$ ( $f_{max}$ ) and $MSG$ (b) $P_{out}$ , output power of the device. The 1 dB compression point is the input power $P_{abs}$ at which $P_{out}$ does not follow the linear behavior (it is 1 dB less than expected). The PAE measures the efficiency by which a device converts DC into added |    |

|       | RF power                                                                                                                                                                                                                                                                                                                                            | 75 |

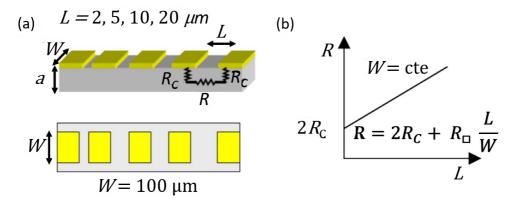

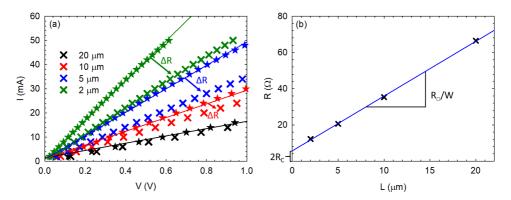

| 3.7.  | (a) Schematic picture of the TLM structure and dimensions ( $W=100~\mu\mathrm{m}$ ) and (b) diagram of the method used to calculate $R_C$ and $R_\square$                                                                                                                                                                                           | 76 |

| 3.8.  | (a) Current-voltage curves for TLMs of lengths 2 $\mu$ m (green), 5 $\mu$ m (blue), 10 $\mu$ m (red) and 20 $\mu$ m (black). Results obtained with 2-wire method (crosses) and 4-wire method (stars) are shown. (b) $R$ obtained from 4-wire measurements as a function of length of the TLMs                                                       | 77 |

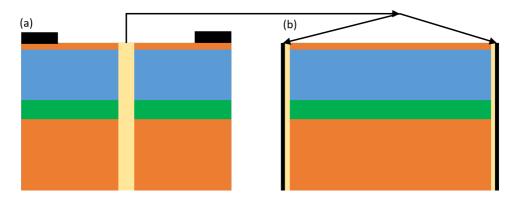

| 3.9.  | (a) Scheme to evaluate potential and concentration profiles in the center of a sample with top electrodes under equilibrium conditions. (b) Sample with vertical electrodes at the laterals, where the profiles previously calculated are used as boundary conditions for the potential and the injection of carriers                               | 79 |

| 3.10. | Electrical domain with surface and polarization charges included in the model and their position in the heterostructure                                                                                                                                                                                                                             | 80 |

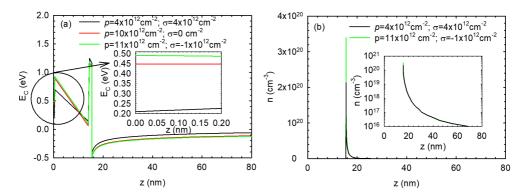

| 3.11. | (a) Vertical potential profiles (conduction band edge) along the first layers of the device for three configurations of $P$ and $\sigma$ . Inset: zoom of the profiles near the GaN/air surface. (b) Concentration profile for the first and third configurations. Inset: concentration profiles in logarithmic scale                               | 81 |

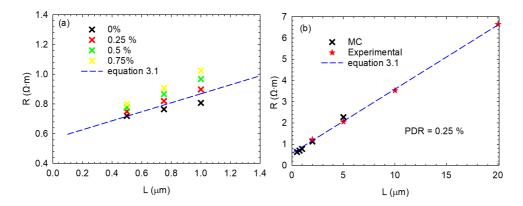

| 3.12. | (a) $R$ $vs$ . length obtained from the simulated $I$ - $V$ characteristics of TLMs for $PDR$ from 0 % to 0.75 %. The blue line corresponds to the linear fitting of experimental values. (b) $R$ $vs$ . length plot comparing experimental and MC results for $PDR = 0.25$ %                                                                       | 82 |

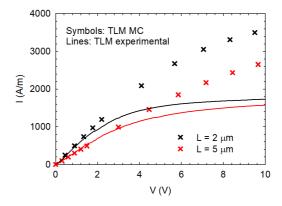

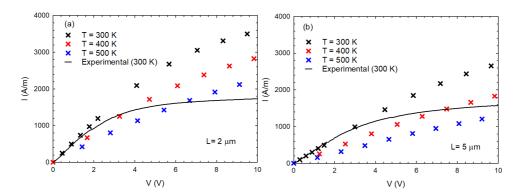

| 3.13. | Measured and simulated current-voltage characteristics of TLMs with lengths $L=2$ and 5 $\mu{ m m}$                                                                                                                                                                                                                                                 | 83 |

| 3.14. | Current-voltage characteristics simulated at different constant temperatures as compared with the experimental one measured at 300 K for TLMs of length                                                                                                                                                                                             |    |

|       | (a) $L=2~\mu\mathrm{m}$ and (b) $L=5~\mu\mathrm{m}$                                                                                                                                                                                                                                                                                                 | 84 |

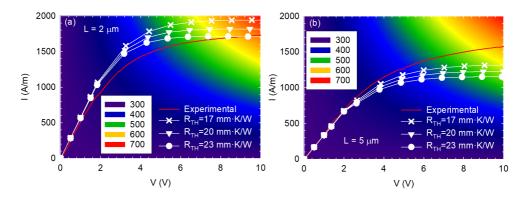

| 3.15. | Simulated current-voltage characteristics considering the TRM with different values of $R_{TH}$ for TLMs with (a) $L=2~\mu\mathrm{m}$ and (b) $L=5~\mu\mathrm{m}$ , as compared with the experimental $I\text{-}V$ curve measured at 300 K. The background color represents $T_{latt}$ obtained for $R_{TH}=20~\mathrm{mm\cdot K/W}$ | 85 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

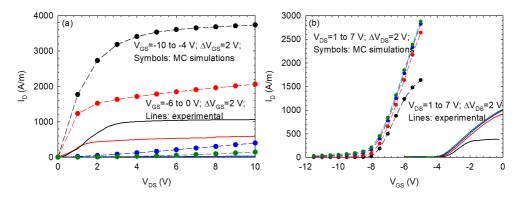

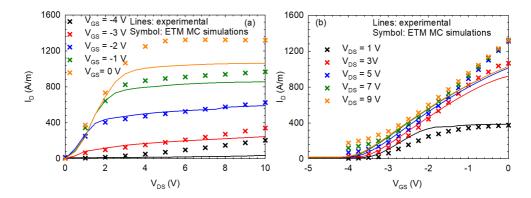

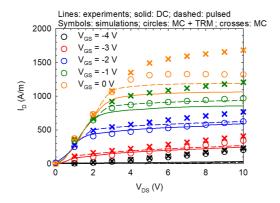

| 3.16. | Measurements and MC simulations without post-processing of the (a) output and (b) transfer characteristics of transistor $2N \dots \dots \dots \dots$                                                                                                                                                                                | 86 |

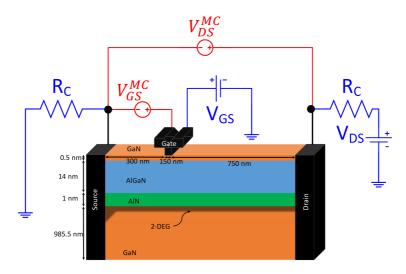

| 3.17. | Scheme for the inclusion of contact resistances in the HEMT. Blue lines stand for external or experimental elements and the red ones for MC (intrinsic) $$ .                                                                                                                                                                         | 87 |

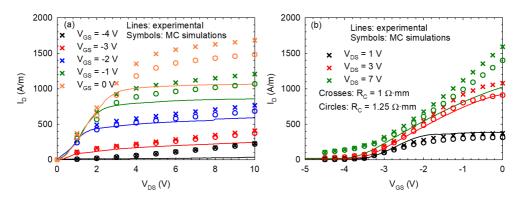

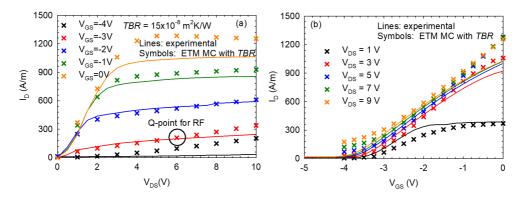

| 3.18. | (a) Output and (b) transfer characteristics with a post-processing including $R_C=1~\Omega\cdot {\rm mm}$ (crosses) and $R_C=1.25~\Omega\cdot {\rm mm}$ (circles), and $V_{SCH}=4.5~{\rm V}$ . (a) $V_{GS}$ from -4 V to 0 V with $\Delta V_{GS}=1~{\rm V}$ and (b) $V_{DS}=1~{\rm V}$ , 3 V, 7 V                                    | 87 |

| 3.19. | (a) Output and (b) transfer characteristics with a post-processing including $R_C=1~\Omega\cdot {\rm mm}$ , and $V_{SCH}=4.5~{\rm V}$ (crosses) and $V_{SCH}=5~{\rm V}$ (circles). (a) $V_{GS}$ from -4 V to 0 V with $\Delta V_{GS}=1~{\rm V}$ and (b) $V_{DS}=1~{\rm V}$ , 3 V and 7 V .                                           | 88 |

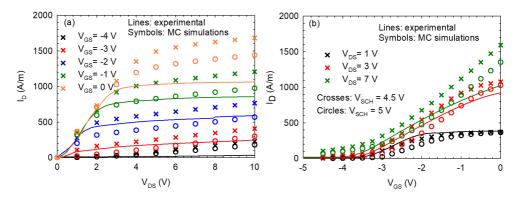

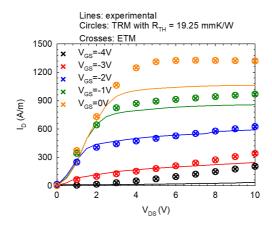

| 3.20. | Output characteristics of transistor 2N considering thermal effects using TRM with $R_{TH}=18.50~\mathrm{mm\cdot K/W}$ (circles) and $R_{TH}=19.25~\mathrm{mm\cdot K/W}$ (stars). Lines correspond to the experimental values                                                                                                        | 89 |

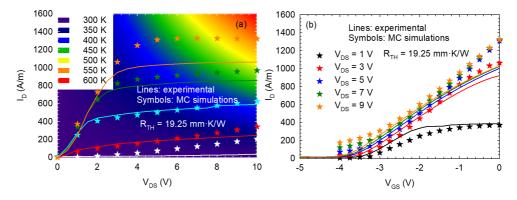

| 3.21. | (a) Output characteristics obtained with $R_{TH}=19.25~\mathrm{mm\cdot K/W}$ . The background color represents $T_{latt}$ at each operating point according Equation 3.13. $V_{GS}$ from -4 V to 0 V, with $\Delta V_{GS}=1$ V. (b) Transfer characteristics                                                                         | 90 |

| 3.22. | Thermal and electrical domains of the simulation for the electrothermal model (ETM). Blue lines and numbers stand for added elements in the resolution of the HCE                                                                                                                                                                    | 91 |

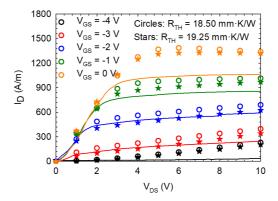

| 3.23. | (a) Output and (b) transfer characteristics of transistor 2N simulated using thermal effects with the ETM as compared with measurements                                                                                                                                                                                              | 92 |

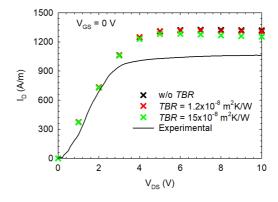

| 3.24. | Output characteristics obtained both with the TRM ( $R_{TH}=19.25~\mathrm{mm\cdot K/W}$ ) and ETM compared with measurements                                                                                                                                                                                                         | 93 |

| 3.25. | Output characteristics obtained with the ETM without $TBR$ and including it with values of 1.2 $\rm Km^2/W$ and 15 $\rm Km^2/W$ , as compared with experimental results                                                                                                                                                              | 93 |

| 3.26. | (a) Output and (b) transfer characteristics obtained with the ETM considering $TBR=15~{\rm Km^2/W}$ as compared with experimental results. The circle at $V_{DS}=6~{\rm V},~V_{GS}=-3~{\rm V},$ indicates the quiescent point (Q-point) for the subsequent RF MC characterization in subsection 4.1.2.2 of Chapter 4                 | 94 |

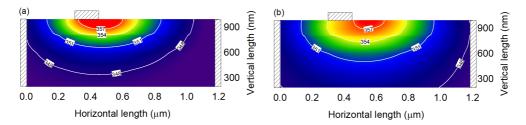

| 3.27. | Map of temperatures obtained in the electrical domain for the bias points: (a) $V_{DS}^{MC}=3~{\rm V},~V_{GS}^{MC}=$ -6.5 V ( $V_{DS}=3~{\rm V},~V_{GS}=$ -0.5 V) and (b) $V_{DS}^{MC}=$ 10 V, $V_{GS}^{MC}=$ -8.5 V ( $V_{DS}=9~{\rm V},~V_{GS}=$ -3 V). Shaded areas indicate the positions                                        |    |

|       | of the contacts                                                                                                                                                                                                                                                                                                                      | 95 |

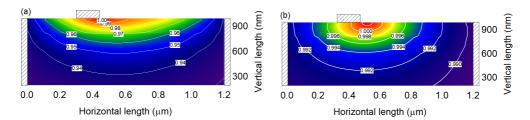

| 3.28. | Map of temperatures in the electrical domain normalized to the maximum value for bias points: (a) $V_{DS}^{MC} = 5 \text{ V}$ , $V_{GS}^{MC} = -4 \text{ V}$ ( $V_{DS} = 4.5 \text{ V}$ , $V_{GS} = 1 \text{ V}$ ) and (b) $V_{DS}^{MC} = 5 \text{ V}$ , $V_{GS}^{MC} = -8 \text{ V}$ ( $V_{DS} = 4.5 \text{ V}$ , $V_{GS} = -3 \text{ V}$ ). Shaded areas indicate the positions of the contacts | 96  |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.29. | Comparison between experimental DC and pulsed ( $\tau=1~\mu s$ , duty cycle 1%) output characteristics, and MC output characteristics calculated without considering thermal effects and including with TRM ( $R_{TH}=19.25~{\rm mm\cdot K/W}$ ) .                                                                                                                                                | 97  |

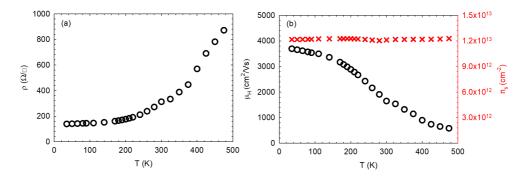

| 3.30. | Hall measurements $vs$ . temperature of (a) sheet resistivity, and (b) mobility (left axis) and sheet-carrier concentration (right axis)                                                                                                                                                                                                                                                          | 98  |

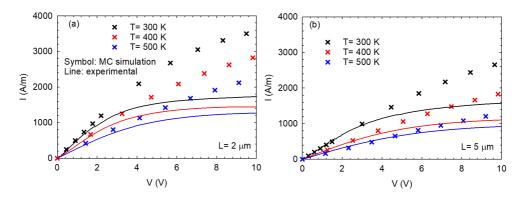

| 3.31. | Current-voltage characteristics measured using the cryogenic probe station (LakeShore CRX-VF) and calculated from MC simulations at different ambient temperatures for TLMs of length (a) $L=2~\mu{\rm m}$ and (b) $L=5~\mu{\rm m}$                                                                                                                                                               | 99  |

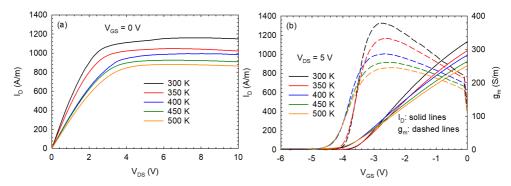

| 3.32. | (a) Output characteristic for $V_{GS}=0$ V, and (b) transfer characteristics (left axis) and transconductance (right axis) for $V_{DS}=5$ V measured in transistor 2N at different ambient temperatures                                                                                                                                                                                           | 99  |

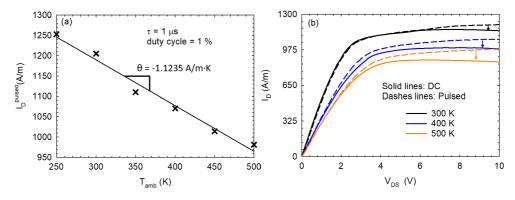

| 3.33. | (a) $I_D^{pulsed}$ ( $V_{GS}=0$ V, $V_{DS}=10$ V) $vs.$ $T_{amb}$ , pulse of $\tau=1$ $\mu s$ and duty cycle 1% (calibration step) and (b) $I_D^{DC}$ and $I_D^{pulsed}$ $vs.$ $V_{DS}$ at $V_{GS}=0$ V and different $T_{amb}$ (measurement step)                                                                                                                                                | 100 |

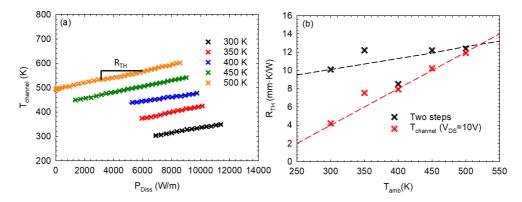

| 3.34. | (a) $T_{channel}$ $vs.$ $P_{Diss}$ for each heat-sink temperature $T_{amb}$ . (b) Comparison between $R_{TH}$ calculated with the described method (black symbols) and calculated with $T_{channel}$ and $P_{Diss}$ at $V_{DS}=10$ V. Dashed lines are an eye-guide to observe the trends.                                                                                                        | 101 |

| 4.1.  | Open and short circuit dummies: widths 2 $	imes$ 25 $\mu{\rm m}$ and 2 $	imes$ 50 $\mu{\rm m}$                                                                                                                                                                                                                                                                                                    | 105 |

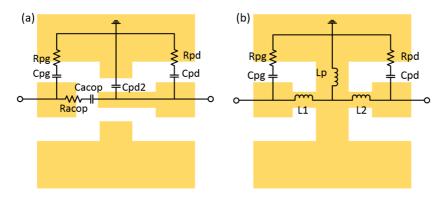

| 4.2.  | Equivalent circuit for the dummies: (a) open and (b) short circuit                                                                                                                                                                                                                                                                                                                                | 105 |

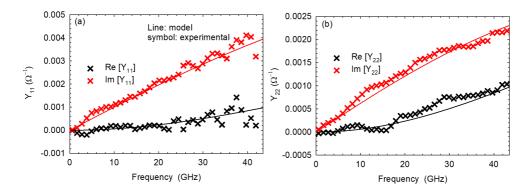

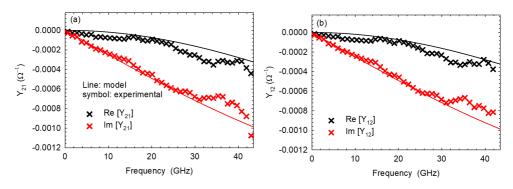

| 4.3.  | $\Re(Y)$ and $\Im(Y)$ for (a) $Y_{11}$ and (b) $Y_{22}$ in the open circuit. Symbols represent the experimental data and solid lines the model of the equivalent circuit                                                                                                                                                                                                                          | 106 |

| 4.4.  | $\Re(Y)$ and $\Im(Y)$ for (a) $Y_{21}$ and (b) $Y_{12}$ in the open circuit. Symbols represent the experimental data and solid lines the model of the equivalent circuit                                                                                                                                                                                                                          | 107 |

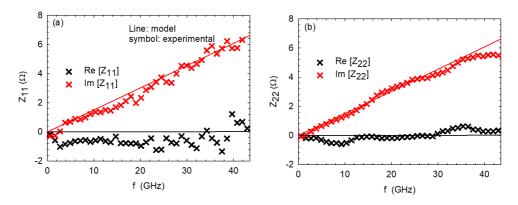

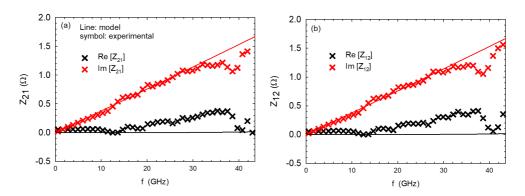

| 4.5.  | $\Re(Z)$ and $\Im(Z)$ for (a) $Z_{11}$ and (b) $Z_{22}$ in the short circuit. Symbols represent experimental data and solid lines model of equivalent circuit                                                                                                                                                                                                                                     | 108 |

| 4.6.  | $\Re(Z)$ and $\Im(Z)$ for (a) $Z_{21}$ and (b) $Z_{12}$ in the short circuit. Symbols represent experimental data the solid lines model of equivalent circuit                                                                                                                                                                                                                                     | 108 |

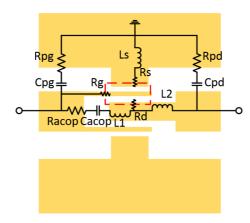

| 4.7.  | Actual pads of the HEMTs with the proposed equivalent circuit. The red square indicates the region corresponding to the device                                                                                                                                                                                                                                                                    | 110 |

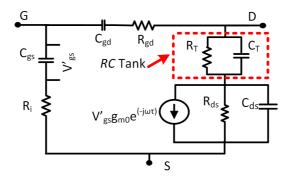

| 4.8.  | Scheme of the device with the proposed equivalent circuit                                                                                                                                                                                                                                                                                                                                         | 111 |

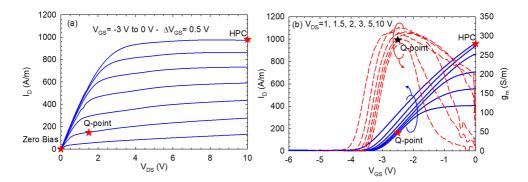

| 4.9. (a) Output and (b) transfer characteristics (left axis) and transconductance (right axis) of transistor 6N ( $L_G=150$ nm, $L_{DS}=2.5~\mu{\rm m}$ and $W=2\times25~\mu{\rm m}$ ). The relevant operation bias points are indicated with red stars                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

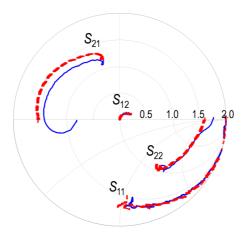

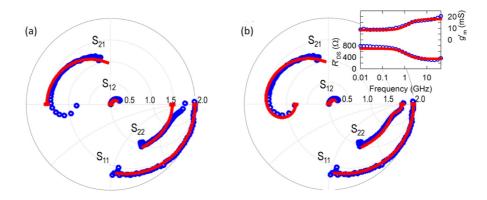

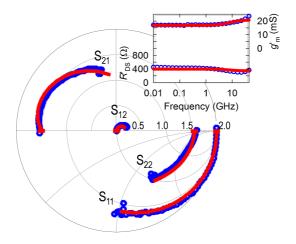

| 4.10. Intrinsic S-parameters extracted from measurements at Q-point ( $V_{GS}$ =-2.5 V and $V_{DS}$ = 1.5 V), before HPC in blue solid line and after HPC in dashed red line. $S_{11}$ and $S_{22}$ are plotted in a Smith Chart format, $S_{21}$ and $S_{12}$ are represented in polar format with a maximum scale of 2.0. Frequency from 10 MHz to 43.5 GHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 14  |

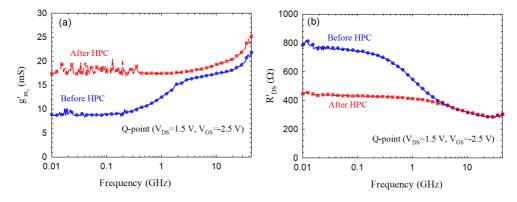

| 4.11. Apparent (a) transconductance and (b) drain-to-source resistance of S-SSEC calculated at the Q-point before and after HPC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 14  |

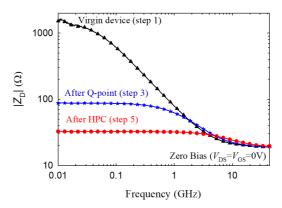

| 4.12. Magnitude of the drain-to-source impedance $(Z_D)$ of the virgin device (step 1), after biasing it at the Q-point (step 3) and HPC (step 5), measured at zero                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1.0 |

| bias $(V_{GS}=0 \text{ V} \text{ and } V_{DS}=0 \text{ V}) \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

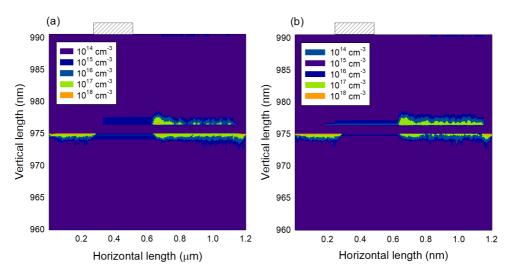

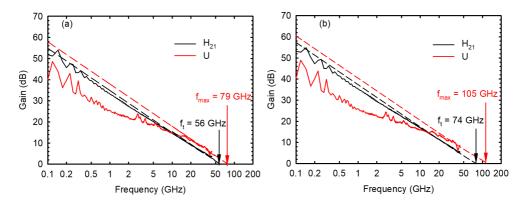

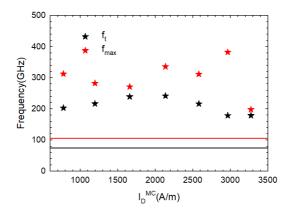

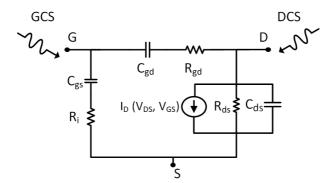

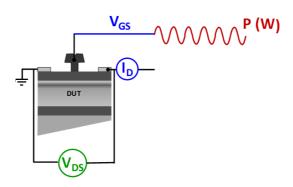

| <ul> <li>4.14. Intrinsic S-parameters extracted from measurements (blue symbols) at Q-point (V<sub>DS</sub> = 1.5 V, V<sub>GS</sub> =-2.5 V) before HPC, and model fitting (red lines) using: (a) the S-SSEC and (b) the proposed T-SSEC. The inset shows the apparent R'<sub>ds</sub> and g'<sub>m</sub> parameters extracted from the S-parameters obtained from the T-SSEC (red line) and the measurements (blue symbols). Parameters S<sub>11</sub> and S<sub>22</sub> are represented in Smith chart format, and S<sub>21</sub> and S<sub>12</sub> are represented in polar format with a maximum scale of 2.0</li> <li>4.15. Intrinsic S-parameters extracted from measurements (blue symbols) at Q-point (V<sub>DS</sub> = 1.5 V, V<sub>GS</sub> =-2.5 V) after HPC, and model fitting (red line) using the proposed T-SSEC. The inset shows the apparent R'<sub>ds</sub> and g'<sub>m</sub> parameters extracted from the S-parameters obtained from the T-SSEC (red line) and</li> </ul> |     |