# Technische Universität Dresden RELIABILITY ANALYSIS OF FOIL SUBSTRATE BASED INTEGRATION OF SILICON CHIPS

#### Nagarajan Palavesam

der Fakultät Elektrotechnik und Informationstechnik der Technischen

Universität Dresden

zur Erlangung des akademischen Grades

Doktoringenieur (Dr.-Ing.)

genehmigte Dissertation

Vorsitzender: Prof. Dr. rer. nat. Stefan Mannsfeld

1. Gutachter: Prof. Dr.-Ing. Dr. h.c. mult. Karlheinz Bock

2. Gutachter: Prof. emerit Dr. Ing. multi DHC. Paul Svasta

Prüfer: Prof. Dr. rer. nat. Johann W. Bartha

Tag der Einreichung: 04.05.2020 Tag der Verteidigung: 26.10.2020

#### **Declaration**

I hereby declare that except where specific reference is made to the work of submitted in whole or in part for consideration for any other degree or others, the contents of this dissertation are original and have not been qualification in this, or any other university. This dissertation is my own work and contains nothing which is the outcome of work done in collaboration with others, except as specified in the text.

Nagarajan Palavesam March 2020

#### Acknowledgements

First and foremost, I would like to thank my supervisor, Prof. Dr.-Ing. Dr. h.c. mult. Karlheinz Bock for his continuous support and guidance throughout this work. I very much appreciate the constructive discussions I had with him during this journey. My special thanks goes to his meticulous and detailed review of the thesis. Next, I would like to thank my second examiner, Prof. emerit Dr. Ing. multi DHC. Paul Svasta for generously offering his time to review this thesis.

I would like to extend my thanks to Prof. Dr. rer. nat. Christoph Kutter for allowing me to work on my doctoral thesis alongside my primary duties at Fraunhofer EMFT. Thanks to his understanding and support, I was able to work enthusiastically on my doctoral thesis. I would also like to express my gratitude to my manager, Mr. Christof Landesberger for his willingness and availability to participate in technical discussions during which he shared his profound knowledge about processing as well as integration of thin silicon chips. I have also learnt to handle the ups and downs in a research career with calmness from him.

I am sincerely grateful to the colleagues at Fraunhofer EMFT and TU Dresden for assisting me with fabrication and analysis of the samples, especially to Dr.-Ing. Detlef Bonfert for his constant support and interesting discussions. I am also thankful to Ms. Ute Wermuth and Mr. Martin Schubert for helping me to deal with the bureaucracy during various stages of this thesis. I owe a debt of gratitude to Ronnie and Anna for sharing their experiences with me and for their emotional support during my first months in Germany.

I would like to gratefully acknowledge the European Commission for co-funding this thesis via the Marie Curie Early Stage Research Fellowship. This thesis was also funded by the German Research Foundation (DFG, Deutsche Forschungsgemeinschaft) as part of Germany's Excellence Strategy – EXC 2050/1 – Project ID 390696704 – Cluster of Excellence "Centre for Tactile Internet with Human-in-the-Loop" (CeTI) of Technische Universität Dresden and I am grateful to the responsible funding bodies for their financial support. Besides, I am forever indebted to the Politecnico di Torino for financially assisting my Masters Studies with the Alta Scuola Politecnica and Compagnia di San Paolo - Politecnico project Merit Scholarships which kick-started my academic journey in Europe. My heartfelt thanks goes also to EDISU Piemonte for the merit and international mobility scholarships that allowed me

to focus on the academics without worrying about the financial burden during the exchange semesters of my Masters studies.

I am sincerely thankful to Dr. Luisa Bozano and Ms. Linda Sundberg at IBM Almaden Research Center for instilling the seeds for the research career within me. I would also like to thank Prof. Fabrizio Pirri for the longstanding collaboration between Politecnico di Torino and IBM Research that enabled my Masters Thesis at IBM Almaden Research Center.

I would never be able to thank my friends enough for making me feel at home in Europe with their love and care. You all have made me cherish my life abroad!

Finally, I would like to thank my family for having always been there for me. None of this would have been possible without the immense support and motivation I received from my brother and cousins. I would not have gotten this far in life without their encouragement. Thank you all! My special thanks goes to my wife, Amritha for her everlasting love, patience and understanding.

Last but not least, I would like to thank my parents from the bottom of my heart for their sacrifices as well as for going above and beyond for enabling me to access quality education despite the limited financial resources. I hope I have made you both proud and your sacrifices meaningful with this thesis. I dedicate this thesis to you both, Appa and Amma!

#### Abstract

Flexible electronics has attracted significant attention in the recent past due to the booming wearables market in addition to the ever-increasing interest for faster, thinner and foldable mobile phones. Ultra-thin bare silicon ICs fabricated by thinning down standard ICs to thickness below 50 µm are flexible and therefore they can be integrated on or in polymer foils to create flexible hybrid electronic (FHE) components that could be used to replace rigid standard surface mount device (SMD) components. The fabricated FHE components referred as chip foil packages (CFPs) in this work are ideal candidates for FHE system integration owing to their ability to deliver high performance at low power consumption while being mechanically flexible. However, very limited information is available in the literature regarding the reliability of CFPs under static and dynamic bending. The lack of such vital information is a major obstacle impeding their commercialization.

With the aim of addressing this issue, this thesis investigates the static and dynamic bending reliability of CFPs. In this scope, the static bending reliability of CFPs has been investigated in this thesis using flexural bending tests by measuring their fracture strength. Then, Finite Element Method (FEM) simulations have been implemented to calculate the fracture stress of ultra-thin flexible silicon chips where analytical formulas may not be applied. After calculating the fracture stress from FEM simulations, the enhancement in robustness of ultra-thin chips (UTCs) against external load has also been proved and quantified with further experimental investigations. Besides, FEM simulations have also been used to analyse the effect of Young's Modulus of embedding materials on the robustness of the embedded UTCs. Furthermore, embedding the UTCs in polymer layers has also been experimentally proven to be an effective solution to reduce the influence of thinning and dicing induced damages on the robustness of the embedded UTCs.

Traditional interconnection techniques such as wire bonding may not be implemented to interconnect ultra-thin silicon ICs owing to the high mechanical forces involved in the processes that would crack the chips. Therefore, two novel interconnection methods namely (i) flip-chip bonding with Anisotropic Conductive Adhesive (ACA) and (ii) face-up direct metal interconnection have been implemented in this thesis to interconnect ultra-thin silicon ICs to

the corresponding interposer patterns on foil substrates. The CFP samples thus fabricated were then used for the dynamic bending reliability investigations.

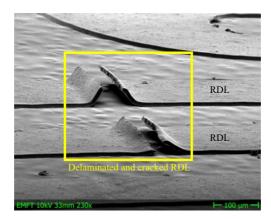

A custom-built test equipment was developed to facilitate the dynamic bending reliability investigations of CFPs. Experimental investigations revealed that the failure of CFPs under dynamic bending was caused mainly by the cracking of the redistribution layer (RDL) interconnecting the chip and the foil. Furthermore, it has also been shown that the CFPs are more vulnerable to repeated compressive bending than to repeated tensile bending. Then, the influence of dimensional factors such as the thickness of the chip as well as the RDL on the dynamic bending reliability of CFPs have also been studied. Upon identifying the plausible cause behind the cracking of the RDL leading to the failure of the CFPs, two methods to improve the dynamic bending reliability of the RDL have been suggested and demonstrated with experimental investigations.

The experimental investigations presented in this thesis adds some essential information to the state-of-the-art concerning the static and the dynamic bending reliability of UTCs integrated in polymer foils that are not yet available in the literature and aids to establish in-depth knowledge of mechanical reliability of the components required for manufacturing future FHE systems. The strategies devised to enhance the robustness of UTCs and CFPs could serve as guidelines for fabricating reliable FHE components and systems.

## **Table of contents**

| Li | st of f | igures                                                                     | xiii |

|----|---------|----------------------------------------------------------------------------|------|

| Li | st of t | ables                                                                      | xvii |

| Li | st of A | Acronyms                                                                   | xix  |

| Li | st of S | Symbols                                                                    | xxi  |

| 1  | Intr    | oduction                                                                   | 1    |

|    | 1.1     | Background and motivation for Flexible Electronics                         | 1    |

|    | 1.2     | Substrates for fabricating Flexible Electronics                            | 2    |

|    | 1.3     | Types of polymer foil based Flexible Electronics                           | 2    |

|    | 1.4     | Flexible Hybrid Electronics                                                | 3    |

|    |         | 1.4.1 Integration of SMD components on/in polymer foils                    | 3    |

|    |         | 1.4.2 Integration of bare ultra-thin chips on/in polymer foils - Chip Foil |      |

|    |         | Packages                                                                   | 4    |

|    | 1.5     | Bending reliability analysis of Chip Foil Packages                         | 4    |

|    | 1.6     | Outline of the Thesis                                                      | 5    |

| 2  | Stat    | ic bending reliability analysis of Chip Foil Packages                      | 7    |

|    | 2.1     | Description of test equipment and samples                                  | 7    |

|    | 2.2     | Fabrication of ultra-thin chips                                            | 8    |

|    | 2.3     | Principle of 3-point-bending tests                                         | 11   |

|    | 2.4     | Fracture force measurement of thin and ultra-thin chips                    | 12   |

|    | 2.5     | Fracture stress calculation                                                | 12   |

|    | 2.6     | Calculation of fracture stress of UTCs                                     | 14   |

|    | 2.7     | Enhancement of robustness of UTCs                                          | 16   |

|    | 2.8     | Effect of Young's Modulus of embedding material on the robustness of UTCs  | 19   |

|    | 2.9     | Minimising the impact of chip micro-defects on the robustness of UTCs      | 22   |

Table of contents

|   |      | 2.9.1    | Acoustic Emission assisted fracture force detection of chip foil pack- |    |

|---|------|----------|------------------------------------------------------------------------|----|

|   |      |          | ages                                                                   | 22 |

|   |      | 2.9.2    | Principle of Acoustic Emission sensors                                 | 24 |

|   |      | 2.9.3    | Effect of dicing induced micro-defects on the fracture force of UTCs   | 25 |

|   |      | 2.9.4    | Sidewall roughness analysis of UTCs                                    | 25 |

|   |      | 2.9.5    | Reducing the influence of surface damages of UTCs on their robustness  | 25 |

|   |      | 2.9.6    | Improvement in biaxial fracture force of UTCs due to embedding .       | 29 |

|   | 2.10 | Summ     | ary                                                                    | 31 |

| 3 | Fabi | rication | of Chip Foil Packages: Interconnection of bare ultra-thin chips        | 33 |

|   | 3.1  | Flip-C   | hip bonding of UTCs with ACA                                           | 33 |

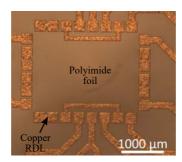

|   |      | 3.1.1    | Semi-additive patterning of RDL on polymer foils                       | 34 |

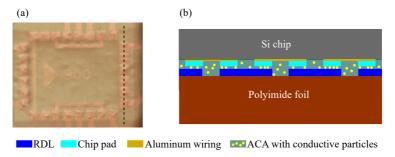

|   |      | 3.1.2    | Integration and interconnection of UTCs on RDL                         | 37 |

|   |      | 3.1.3    | Optimisation of flip-chip bonding process                              | 41 |

|   |      | 3.1.4    | Electrical characterisation                                            | 42 |

|   | 3.2  | Face-u   | p interconnection of ultra-thin chips                                  | 43 |

|   |      | 3.2.1    | Electrical characterisation                                            | 45 |

|   | 3.3  | Summ     | ary                                                                    | 47 |

| 4 | Dyn  | amic be  | ending reliability analysis of Chip-Foil Packages                      | 49 |

|   | 4.1  | Test ed  | quipment                                                               | 49 |

|   | 4.2  | Test pi  | rotocol                                                                | 51 |

|   | 4.3  | Choice   | e of bending stress                                                    | 53 |

|   |      | 4.3.1    | Test samples                                                           | 53 |

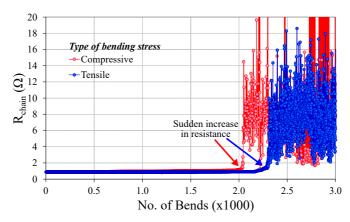

|   |      | 4.3.2    | Analysis of test results                                               | 54 |

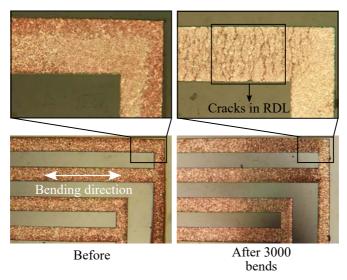

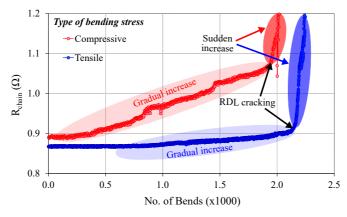

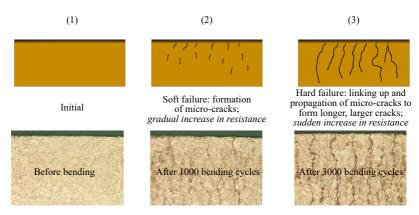

|   | 4.4  |          | racking mechanism                                                      | 57 |

|   | 4.5  |          | gations on the factors influencing the dynamic bending reliability of  |    |

|   |      | CFPs .   |                                                                        | 59 |

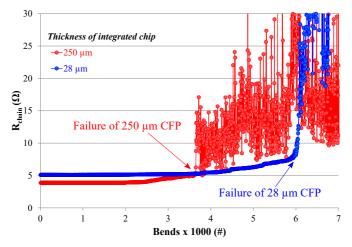

|   |      | 4.5.1    | Chip thickness                                                         | 61 |

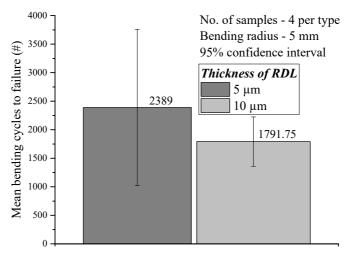

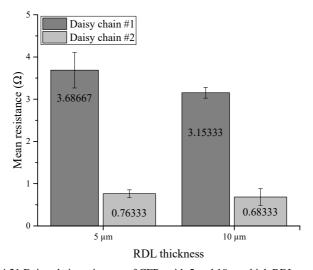

|   |      | 4.5.2    | Thickness of RDL patterns                                              | 63 |

|   | 4.6  | Strateg  | gies to enhance the dynamic bending reliability of the RDL             | 66 |

|   |      | 4.6.1    | By fabricating <i>very thin</i> RDL patterns                           | 66 |

|   |      | 4.6.2    | By fabricating RDL patterns with flexible metals                       | 70 |

|   | 4.7  | Dynan    | nic bending reliability of face-up direct metal interconnected CFPs    | 73 |

|   | 4.8  | Summ     | ary                                                                    | 75 |

| Ta | ble of | cont  | nts                                   |  |  |  | _ | <br> | _ | xi  |

|----|--------|-------|---------------------------------------|--|--|--|---|------|---|-----|

| 5  | Con    | clusi | n                                     |  |  |  |   |      |   | 77  |

|    | 5.1    | Key   | findings and contributions            |  |  |  |   |      |   | 77  |

|    | 5.2    | Out   | ook and perspectives for future works |  |  |  |   |      |   | 81  |

| Re | eferen | ices  |                                       |  |  |  |   |      |   | 83  |

| Aj | pend   | lix A | Daisy chain test patterns             |  |  |  |   |      |   | 99  |

| Aj | pend   | lix B | RDL cracks and hillocks               |  |  |  |   |      |   | 103 |

## List of figures

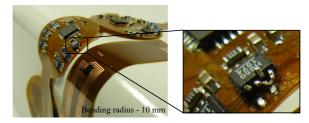

| 1.1  | FHE assemblies bent to a radius of 10 mm showing damaged SMD intercon-      |    |

|------|-----------------------------------------------------------------------------|----|

|      | nection                                                                     | 3  |

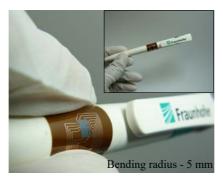

| 1.2  | Bent Chip Foil Package                                                      | 4  |

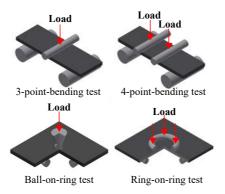

| 2.1  | Commonly used flexural bending tests                                        | 8  |

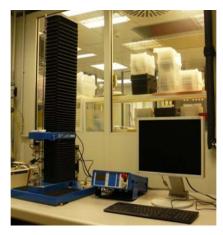

| 2.2  | Universal testing machine                                                   | 9  |

| 2.3  | A standalone UTC during a 3PB test                                          | 9  |

| 2.4  | Dicing-by-Thinning process for fabricating UTCs                             | 10 |

| 2.5  | Load-time curve plotted during a 3PB test                                   | 11 |

| 2.6  | Weibull probability plot comparing the fracture force of standalone chips   |    |

|      | having different thicknesses (30, 65 and 130 µm) during 3PB tests           | 13 |

| 2.7  | Principle of 3-point-bending test                                           | 14 |

| 2.8  | FEM model used for calculating fracture stress of UTCs                      | 15 |

| 2.9  | Weibull probability plot comparing the fracture stress values of standalone |    |

|      | chips having different thicknesses (30, 65 and 130 µm) calculated using FEM |    |

|      | simulations and analytical formula for 3PB tests                            | 16 |

| 2.10 | Position of neutral plane in an isotropic standalone chip                   | 17 |

| 2.11 | Schematic of the cross-section of a bent symmetrical CFP showing the        |    |

|      | position of the neutral plane                                               | 18 |

| 2.12 | Weibull probability plot comparing the fracture force of standalone and     |    |

|      | embedded chips having different thicknesses (30, 65 and 130 µm) during      |    |

|      | 3PB tests                                                                   | 19 |

| 2.13 | Bent UTCs: Standalone and embedded in PI substrates at the same bending     |    |

|      | radius                                                                      | 20 |

xiv List of figures

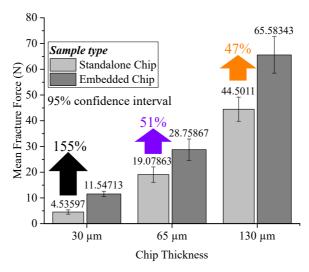

| 2.14 | Mean fracture force of standalone and embedded chips during 3PB tests. The     |    |

|------|--------------------------------------------------------------------------------|----|

|      | arrows and the numbers above the arrows represent the increase in fracture     |    |

|      | force of the chips due to embedding. The numbers elucidate that a higher       |    |

|      | load distribution was achieved for thinner chips for the same embedding foil   |    |

|      | thickness.                                                                     | 20 |

| 2.15 | Accurate determination of fracture force of embedded UTCs during LLT           | 23 |

| 2.16 | Schematic and photo of the AE assisted LLT test setup                          | 23 |

| 2.17 | Scanning Electron Microscope image of sidewalls of wafer sawn and plasma       |    |

|      | diced UTCs                                                                     | 24 |

| 2.18 | Surface profile of the sidewall of wafer sawn and plasma diced UTCs            | 26 |

| 2.19 | Weibull probability plot comparing the fracture force of standalone and        |    |

|      | embedded UTCs measured with LLT for chips singulated using wafer sawing        |    |

|      | and plasma dicing                                                              | 27 |

| 2.20 | Mean fracture force of standalone and embedded UTCs measured with LLT:         |    |

|      | Wafer sawing vs. Plasma dicing. The arrows and the numbers above the           |    |

|      | arrows represent the increase in fracture force of the chips due to embedding. | 28 |

| 2.21 | Schematic and photo of the Ball-on-ring test                                   | 29 |

| 2.22 | Weibull probability plot comparing the fracture force of standalone and        |    |

|      | embedded chips with three different thicknesses (30, 65 and 130 µm) during     |    |

|      | BOR tests                                                                      | 30 |

| 2.23 | Mean fracture force of standalone and embedded chips during BOR tests.         |    |

|      | The arrows and the numbers above the arrows represent the increase in          |    |

|      | fracture force of the chips due to embedding. $\hdots$                         | 31 |

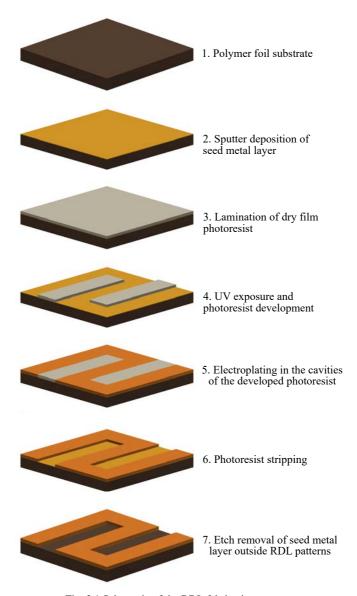

| 3.1  | Schematic of the RDL fabrication process                                       | 35 |

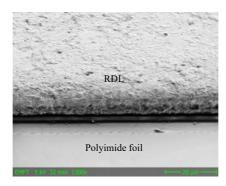

| 3.2  | SEM image of 10 µm thick electroplated RDL                                     | 37 |

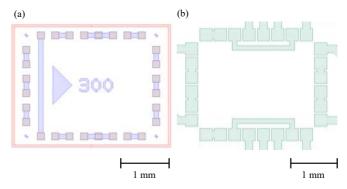

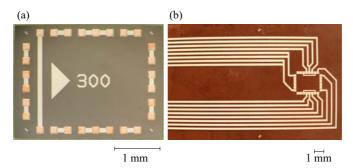

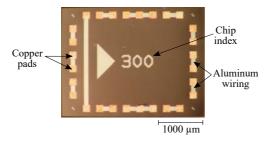

| 3.3  | Designed layout of the chip and its corresponding interposer RDL pattern .     | 37 |

| 3.4  | Fabricated chip and its corresponding interposer RDL pattern on foil showing   |    |

|      | the layout                                                                     | 38 |

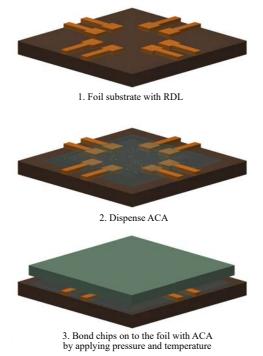

| 3.5  | Schematic of flip-chip bonding process of UTCs                                 | 38 |

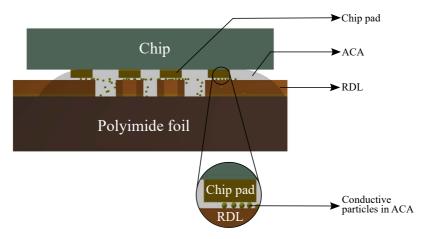

| 3.6  | Sketch of the cross-section of flip-chip bonded CFP                            | 39 |

| 3.7  | Rear view of a flip-chip bonded CFP revealing the ACA interconnection          |    |

|      | between the chip and the foil RDL                                              | 40 |

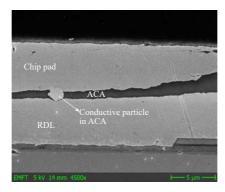

| 3.8  | SEM image of the cross-section of a single contact of a flip-chip bonded CFP   | 41 |

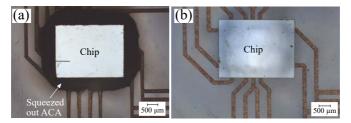

| 3.9  | Squeezed out ACA for unoptimised and optimised flip-chip bonding processes     | 42 |

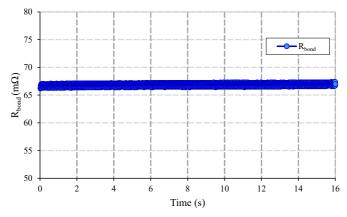

| 3.10 | Resistance of a single bond of the flip-chip bonded CFP                        | 42 |

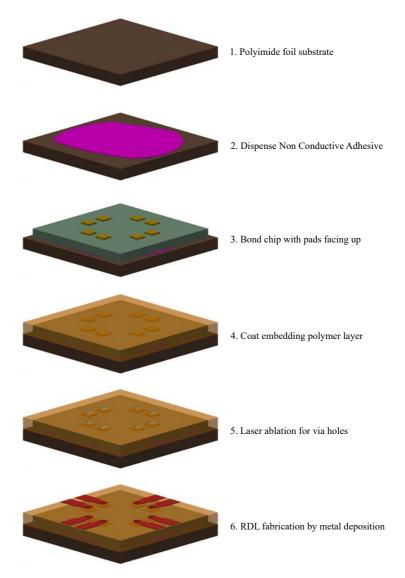

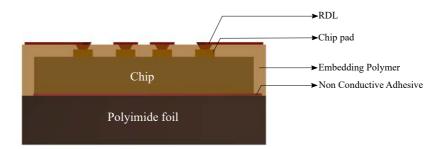

| 3.11 | Schematic of the face-up interconnection process for fabricating CFPs          | 44 |

List of figures xv

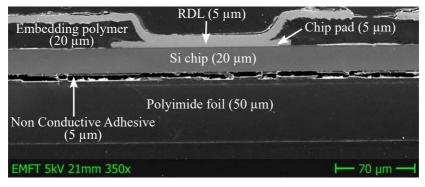

| 3.12 | Illustration of cross-section of the face-up interconnected CFP                 | 45 |

|------|---------------------------------------------------------------------------------|----|

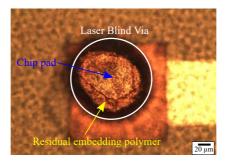

| 3.13 | Top view of a laser blind via                                                   | 45 |

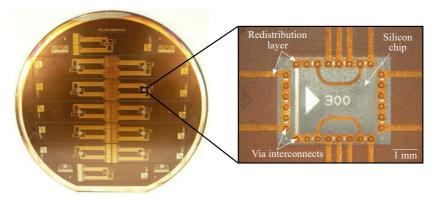

| 3.14 | Face-up interconnected CFPs prior to detachment from 6" handling wafer          |    |

|      | and a closer view of a CFP                                                      | 46 |

| 3.15 | SEM image of the cross-section of a single contact of face-up interconnected    |    |

|      | CFP                                                                             | 46 |

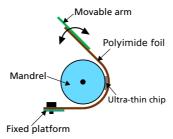

| 4.1  | Schematic of the test equipment used for the fixed radius dynamic bending tests | 50 |

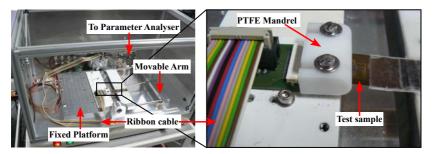

| 4.2  | Custom built test equipment used for the dynamic bending tests                  | 50 |

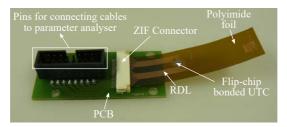

| 4.3  | A CFP sample attached to the PCB through the ZIF connector                      | 51 |

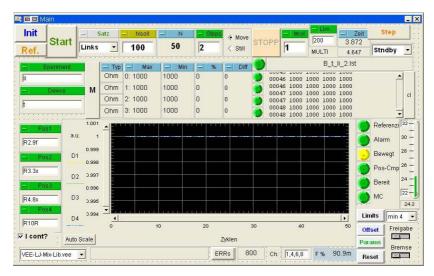

| 4.4  | Parameter analyser used for the dynamic bending tests                           | 52 |

| 4.5  | Software interface used for controlling the dynamic bending tests               | 52 |

| 4.6  | Dynamic bending test protocol                                                   | 53 |

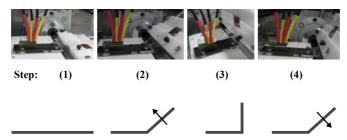

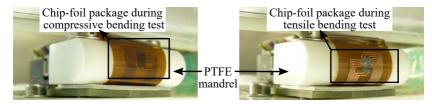

| 4.7  | Chip-foil package samples during 180° compressive and tensile bending tests     |    |

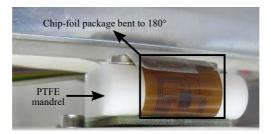

|      | at a bending radius of 5 mm                                                     | 53 |

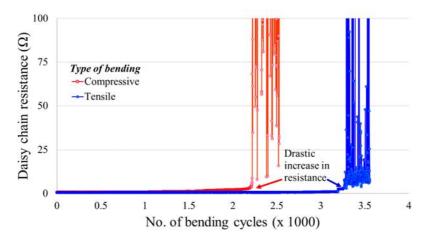

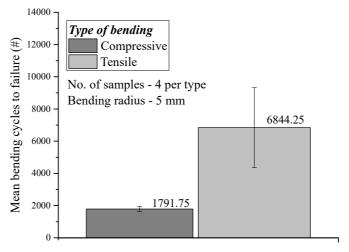

| 4.8  | Comparison of daisy chain resistance behaviour of CFPs during 180° com-         |    |

|      | pressive and tensile bending tests at a bending radius of 5 mm                  | 54 |

| 4.9  | Comparison of dynamic bending reliability of CFPs during compressive and        |    |

|      | tensile fixed radius bending tests at a bending radius of 5 mm                  | 55 |

| 4.10 | Comparison of daisy chain resistance behaviour of CFPs during 90° free-         |    |

|      | form compressive and tensile bending tests                                      | 56 |

| 4.11 | Microscopic view of RDL patterns revealing the cracks after 3000 compres-       |    |

|      | sive bending cycles                                                             | 56 |

| 4.12 | A closer view to the change in daisy chain resistance shown in figure 4.10      |    |

|      | elucidating the correlation between the cracking of the RDL and the increase    |    |

|      | in daisy chain resistance                                                       | 57 |

| 4.13 | Mechanism of formation of cracks in electroplated RDL patterns during           |    |

|      | dynamic bending tests                                                           | 58 |

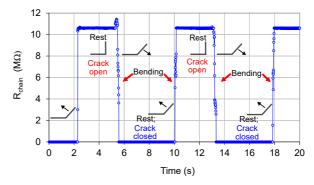

| 4.14 | Alternating increase and decrease in daisy chain resistance after abrupt        |    |

|      | increase due to opening and closing of RDL cracks                               | 59 |

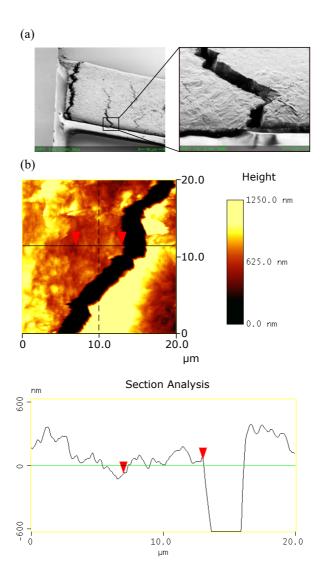

| 4.15 | AFM Section analysis of a crack in the electroplated RDL pattern                | 60 |

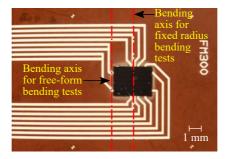

|      | Location of bending axis on the CFP for free-form and fixed radius dynamic      |    |

|      | bending tests                                                                   | 61 |

| 4.17 | Dynamic bending reliability of CFPs with two different chip thickness           | 62 |

|      | A CFP sample bent to a radius of 5 mm around the PTFE mandrel during            |    |

|      | 180° dynamic bending tests                                                      | 63 |

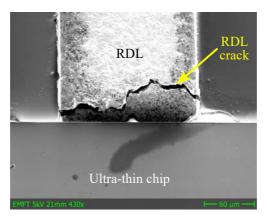

| 4.19 | SEM image of a CFP (top view) revealing an RDL crack                            | 64 |

|      |                                                                                 |    |

xvi List of figures

| 4.20 | Summary of dynamic bending reliability of CFPs with two different RDL                  |

|------|----------------------------------------------------------------------------------------|

|      | thickness                                                                              |

| 4.21 | Daisy chain resistance of CFPs with 5 and 10 $\mu m$ thick RDL patterns $$ 65          |

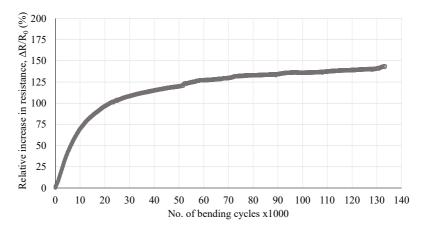

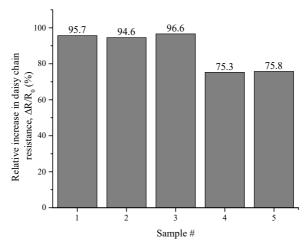

| 4.22 | Daisy chain resistance behaviour during fixed radius bending tests of a CFP            |

|      | with sputter deposited copper RDL                                                      |

| 4.23 | Relative increase in daisy chain resistance of CFPs with very thin copper              |

|      | RDL patterns during $180^{\circ}$ fixed radius bending tests                           |

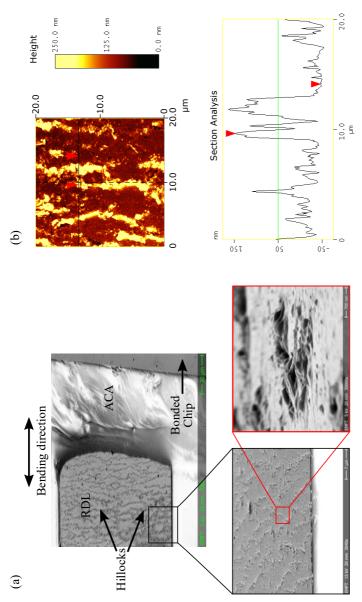

| 4.24 | SEM images and AFM section analysis of hillocks formed on sputter de-                  |

|      | posited copper RDL patterns after 20000 bending cycles 69                              |

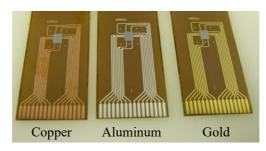

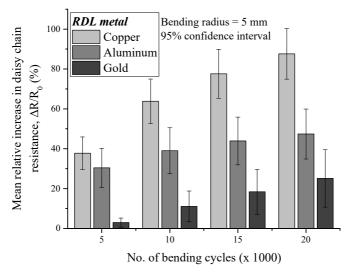

| 4.25 | CFPs with copper, aluminum and gold RDL patterns                                       |

| 4.26 | SEM images of the hillocks formed on sputter deposited aluminum and gold               |

|      | RDL patterns after 20000 bending cycles                                                |

| 4.27 | AFM section analysis of a hillocks formed on sputter deposited aluminum                |

|      | and gold RDL patterns after 20000 bending cycles                                       |

| 4.28 | Mean relative increase in daisy chain resistance of CFPs with copper, alu-             |

|      | minum and gold RDL patterns during dynamic bending tests                               |

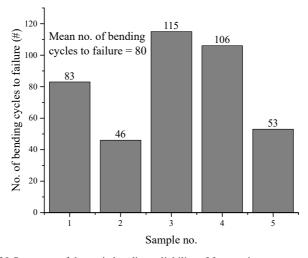

| 4.29 | Summary of dynamic bending reliability of face-up interconnected CFPs $74$             |

| 4.30 | SEM image with the delaminated and cracked RDL patterns                                |

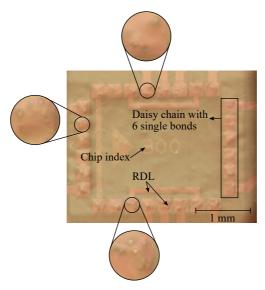

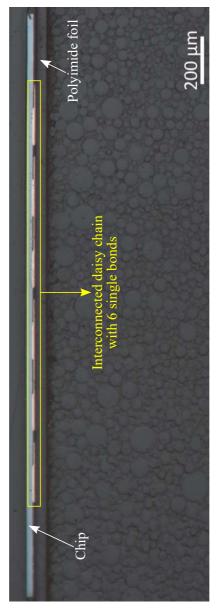

| A.1  | Flip-bonded CFP viewed from the rear side through the Polyimide foil and               |

|      | an illustration of the daisy chain with 6 single bonds investigated in this thesis 100 |

| A.2  | Layout of the test chip with daisy chain pattern                                       |

| A.3  | Layout of the Polyimide foil with daisy chain pattern                                  |

| A.4  | Cross-section of the interconnected daisy chain with 6 single bonds 101                |

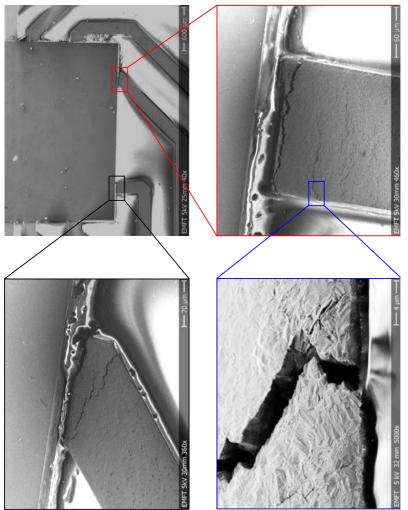

| B.1  | Cracks developed on electroplated copper RDL                                           |

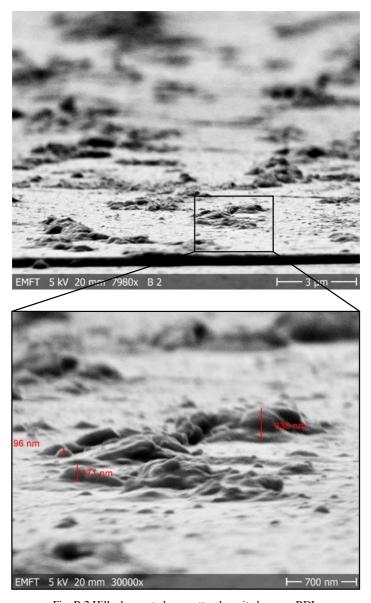

| B.2  | Hillocks created on sputter deposited copper RDL                                       |

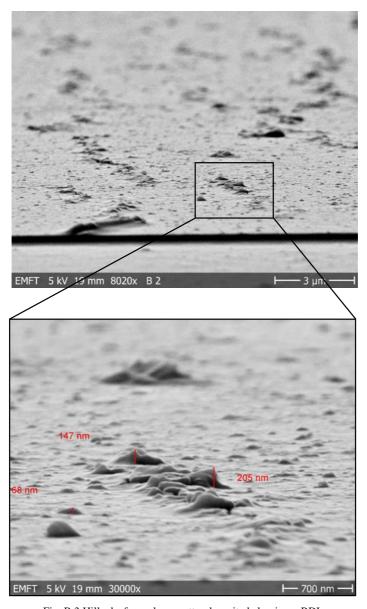

| B.3  | Hillocks formed on sputter deposited aluminum RDL                                      |

| B.4  | Hillocks inflicted on sputter deposited gold RDL                                       |

## List of tables

| 1.1 | Key properties of common polymer foil substrates                             | 2  |

|-----|------------------------------------------------------------------------------|----|

| 2.1 | Technologies for fabricating UTCs                                            | 10 |

| 2.2 | Mean fracture force of chips measured using 3PB tests                        | 12 |

| 2.3 | Mean fracture stress of standalone chips calculated using analytical formula |    |

|     | and FEM simulations                                                          | 15 |

| 2.4 | Fracture force of standalone and embedded chips measured using 3PB tests     | 2  |

| 2.5 | Material properties used for FEM simulations                                 | 2  |

| 2.6 | FEM calculated Fracture force and displacement for embedded UTCs with        |    |

|     | different embedding materials                                                | 22 |

| 2.7 | Fracture force of plasma diced vs. wafer sawn UTCs                           | 28 |

| 2.8 | Fracture force of standalone and embedded chips measured using BOR tests     | 30 |

| 4.1 | Number of bending cycles until failure for CFPs with two different chip      |    |

|     | thicknesses                                                                  | 62 |

| 4.2 | Material properties of metals used for fabricating RDL patterns              | 71 |

## **List of Acronyms**

ACA Anisotropic Conductive Adhesive

AE Acoustic Emission

**AFM** Atomic Force Microscopy

BOR Ball-on-Ring test

CFP Chip Foil Package

CMP Chemical Mechanical Polishing

**DUT** Device Under Test

eWLB embedded Wafer Level Ball Grid Array

FEM Finite Element Method

FHE Flexible Hybrid Electronics

FFOWLP Foldable Fan-Out Wafer Level Packaging

IC Integrated Circuit

IoT Internet of Things

LLT Line-Load Test

NCA Non Conductive Adhesive

PCB Printed Circuit Boards

PEN Polyethylene naphthalate

PET Polyethylene terephthalate

xx List of Acronyms

PI Polyimide

**PSA** Pressure Sensitive Adhesive

PTFE Polytetrafluoroethylene

RDL Redistribution Layer

R2R Roll-to-roll

**SEM** Scanning Electron Microscope

SMD Surface Mount Device

TTV Total Thickness Variation

UTC Ultra-Thin Chip

UTCP Ultra-Thin Chip Package

**ZIF** Zero Insertion Force

**3PB** 3-point-bending test

## **List of Symbols**

- Pf Failure Distribution

- F Applied Load or Force

- $F_C$  Characteristic Fracture Load or Force

- m Weibull Modulus

- $\sigma_{3PB}$  Fracture Strength

- L Load span

- b Breadth of the chip

- t Thickness of the chip

- p Position of the neutral plane

- E Young's Modulus

- rb Bending radius

- $t_s$  Thickness of chip foil package

- $\Delta R$  Increase in resistance

- R<sub>0</sub> Initial resistance

## Chapter 1

#### Introduction

#### 1.1 Background and motivation for Flexible Electronics

The emerging Internet-of-Things (IoT) framework aims to connect almost every physical object via devices placed on them, thereby enabling seamless communication between the objects without requiring human interaction [1–3]. Market research studies forecast that there will be at least 20 billion IoT devices in 2020 [4-6] and high computing performance at low power consumption will be the vital requirement for several of these devices that are expected to sense, acquire and transmit the data from the objects to the internet. Therefore, sensors and actuators providing high performance at low power requirements and manufactured at low cost will be the key for successful implementation of IoT. Furthermore, a substantial fraction of these IoT devices will be placed on curved surfaces of buildings, industrial equipment and automobiles as well as at locations that will be subjected to repeated bending and folding during device usage such as human skin, prosthetics and textiles. Conventional rigid electronics based on Printed Circuit Board (PCB) might not fulfill the flexibility and conformability demands of such IoT applications. Therefore, flexible electronics has often been touted as the key enabler of IoT [7-11]. Besides, flexible electronics has also captivated considerable attention generated by the booming wearables market [12, 13] as well as the arrival of flexible [14] and foldable mobile phones [15].

The market for flexible electronics has been estimated to reach up to \$24.78 billion in 2024 from \$5.53 billion in 2017 [16]. Driven by such a huge market potential, research and development of flexible electronics has garnered remarkable attention in the recent years with the evolution of a variety of devices and systems for a myriad of applications such as flexible displays [17–21], health monitoring [22–25], electronic skin for robotics [26, 27] and prosthetics [28–30], implantable devices [31–33], smart textiles [34–36], smart packaging [37, 38], point-of-care diagnostics [39, 40] and IoT sensors [41–44] to name a few.

2 Introduction

#### 1.2 Substrates for fabricating Flexible Electronics

Flexible electronics is a generic term that can be applied to define any electronic device or system that is mechanically flexible. Though development of flexible electronics has been around for more than 50 years when the first flexible solar cell arrays were assembled on plastic substrates [45, 46], significant progress in the field has been demonstrated during the last decade due to the rapid advances in materials and processes that has resulted in the emergence of novel materials, processes and devices for flexible electronics [47–54].

Flexible electronics is still at its nascent stage of development and a variety of substrates such as paper [55–58], polymer foils [59–63], flexible glass [64–66] and thin metal foils [67–69] have been explored and demonstrated to fabricate flexible electronic devices and systems. However, polymer foils are the most commonly used substrates owing to several advantages exhibited by them over other substrates such as very good flexibility and foldability, high surface quality, excellent dielectric properties, lightweight, thin form factor and large area manufacturing feasibility [63, 70, 71]. Furthermore, when roll-to-roll (R2R) manufacturing processes are implemented, high throughput with fast and continuous production can be achieved at low costs [72, 73]. Some of the commonly used polymer foil substrates and their important properties are summarized in table 1.1. The given numbers are typical values and the actual material properties could differ between different manufacturers as well as individual products.

| Property                                  | Polyimide<br>(PI) | Polyethylene<br>naphthalate (PEN) | Polyethylene<br>terephthalate (PET) |

|-------------------------------------------|-------------------|-----------------------------------|-------------------------------------|

| Glass transition temperature (°C)         | 270               | 120                               | 70                                  |

| Water Absorption (%)                      | 2-3               | 0.4                               | 0.6                                 |

| Coefficient of Thermal Expansion (ppm/°C) | 8-20              | 20                                | 33                                  |

| Surface Roughness                         | Good              | Poor                              | Poor                                |

Table 1.1 Key properties of common polymer foil substrates [74]

#### 1.3 Types of polymer foil based Flexible Electronics

Based on the principal materials used for the fabrication process, polymer foil based flexible electronics can be generally classified into three types namely,

- 1. organic semiconductor devices using thiophenes, pentacenes etc. [75–80]

- 2. inorganic thin film semiconductor devices with amorphous and polycrystalline silicon, indium gallium zinc oxide etc. [81–88] and

- 3. Flexible Hybrid Electronics (FHE) by integrating

- (a) standard rigid Surface Mount Device (SMD) components [89-96] and

- (b) bare flexible ultra-thin chips (UTCs) [97–109]

#### 1.4 Flexible Hybrid Electronics

#### 1.4.1 Integration of SMD components on/in polymer foils

Among the four types of polymer foil based flexible electronics listed above, FHE integrated with SMD components can be fabricated at cheaper costs and is capable of delivering higher performance at lower power consumption compared to the first two types [110]. However, FHEs integrated with SMD components fall short of delivering the desired (and often required) full flexibility for several emerging applications owing to the rigid and bulky SMD components. Figure 1.1 presents FHE assemblies integrated with SMDs and UTC bent to a radius of 10 mm where the interconnection of some SMD components were damaged, thus leading to failure of the system whereas the FHE assembly with the integrated UTC remained intact and functional even when bent to a radius of 5 mm (Figure 1.2). Such lack of complete flexibility and conformability is a massive bottleneck towards realising truly flexible electronics for futuristic applications such as electronic skin for robotics and prosthetics, implantable electronics, IoT applications, flexible displays and smart packaging to name a few. Thus, the quest for realising totally flexible and conformable electronic systems capable of delivering high performance at low power consumption has opened the doors for FHE systems fabricated by integrating UTCs.

Fig. 1.1 FHE assemblies bent to a radius of 10 mm showing damaged SMD interconnection

4 Introduction

Fig. 1.2 Conformability of Chip Foil Package. Originally published in [99]. ©2016 IEEE. Slightly modified and reused here with permission from IEEE.

# 1.4.2 Integration of bare ultra-thin chips on/in polymer foils - Chip Foil Packages

Since silicon becomes flexible at thicknesses below 50 µm, UTCs fabricated by thinning bare, rigid monocrystalline silicon Integrated Circuit (IC) chips can be used to replace SMD components in FHEs to improve the conformability and bending reliability. The resulting devices with improved flexibility and conformability obtained by integrating UTCs in polymer foils are referred to as *Chip Foil Packages (CFPs)* in this work. These CFPs thus fabricated are capable of providing industry standard high performance at low power consumption exhibited by the state-of-the-art devices since the UTCs are essentially the same ICs that are present inside the SMD components. Thus, by replacing standard SMD components with UTCs, the lack of conformability and complete flexibility encountered in FHE with rigid SMD components can be effectively addressed.

#### 1.5 Bending reliability analysis of Chip Foil Packages

Several applications targeting flexible electronics demand the systems to remain functional when bent, often times requiring them to undergo multiple bending cycles while remaining functional. FHE is a relatively younger field and therefore only very limited information is available regarding the bending reliability of FHEs and CFPs [100, 111–114]. However, extensive information about the bending reliability of CFPs is absolutely indispensable for transferring the processes for manufacturing CFPs from research labs to industrial platforms and thereon for enabling the products to reach consumer markets. In order to be considered

1.6 Outline of the Thesis 5

as a potential component in future flexible electronic systems, the bending reliability of the CFPs need to be investigated in detail to establish guidelines for their fabrication and product usage. This work aims to address this objective by primarily investigating the reliability of the CFPs under static and dynamic bending.

#### 1.6 Outline of the Thesis

This thesis is organised in three chapters.

In the following chapter 2, state-of-the-art static bending test methods for analysing the fracture stress of standalone thin chips is introduced. Then, the fracture strength or stress of silicon chips of varying thickness ranging from thin to ultra-thin regime have been calculated using analytical formula and Finite Element Method (FEM) simulations. Next, the enhancement in fracture force or robustness of UTCs against external load achieved by embedding of UTCs in polymer foils is elucidated with experimental investigations. Lastly, the influence of embedding on the damages on the chip surface and edges resulting from wafer thinning and dicing processes is discussed with experimental results. The investigations on the impact of embedding of UTCs on their robustness increase and the discussions on the influence of embedding on the damages induced on the UTCs arising from the wafer thinning as well as dicing processes have been performed for the first time to the extent of the author's knowledge.

Chapter 3 describes the two divergent interconnection approaches namely (i) *flip-chip bonding with Anisotropic Conductive Adhesive (ACA)* and (ii) *face-up direct metal interconnection* applied for fabricating CFPs in this work. The implementation of both processes to interconnect UTCs having daisy chain patterns have also been described in detail.

Chapter 4 begins with the description of the custom-built test equipment and the test protocol followed to study the dynamic bending reliability of the CFPs. Various investigations performed on the CFPs and the obtained test results are discussed in this chapter. Firstly, the effect of tensile as well as compressive bending stresses on the dynamic bending reliability of CFPs are compared and it has been experimentally found that the CFPs are more vulnerable to compressive stress than to tensile stress. Such an experimental analysis has been performed for the first time to the best of the author's knowledge. Then, the cause of failure of the CFPs during dynamic bending tests is identified and a hypothesis for the initiation as well as development of the failure under dynamic bending has been proposed which is in coherence with several other studies. Furthermore, the influence of dimensional factors such as the thickness of integrated chip and the interconnecting redistribution layer (RDL) on the dynamic bending reliability of the CFPs were also experimentally analysed for the first time

6 Introduction

to the best of the author's knowledge. Finally, two methods to improve the dynamic bending reliability of CFPs have also been suggested and the resulting enhancement in the dynamic bending reliability of CFPs have been experimentally verified for the first time to the extent of the author's knowledge.

The final chapter 5 includes the concluding remarks and outlook for follow-up works. The key contributions and findings of this thesis are also listed in this chapter.

## Chapter 2

## Static bending reliability analysis of Chip Foil Packages

The key advantage of UTCs over commercially available SMD components is their mechanical flexibility and bendability. The extent to which UTCs can be bent without fracture can be determined from the fracture strength of the UTCs. Fracture strength is the maximum stress at which the UTC breaks or fractures due to the externally applied load and it is commonly expressed in Pascal (Pa). Fracture strength of samples is generally calculated from experimentally measured force values using analytical formulas that depend on the geometry and dimensions of the UTC. The maximum load or force at which the UTC fractures (called the fracture load or force) is measured by conducting flexural bending tests where the device under test (DUT), UTC in this case, is placed on a holder of a defined geometry and a known external load is applied to the DUT until it fractures.

Based on the type of stress applied on to the DUT, commonly used flexural bending tests can be classified into two groups: (1) uniaxial bending tests and (2) biaxial bending tests. Some of the widely used flexural bending tests for assessing the fracture strength of silicon chips are illustrated in figure 2.1. Flexural bending tests are generally conducted with a universal testing machine. The test results are sensitive to the loading and specimen geometries. Therefore, it is important to maintain the same dimensions for the samples and the test setup throughout the experiment series.

#### 2.1 Description of test equipment and samples

As mentioned earlier, fracture strength of a DUT is determined from the experimentally measured fracture load or force obtained from flexural bending tests. The measured fracture

Fig. 2.1 Commonly used flexural bending tests

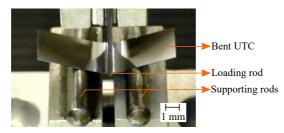

load or force is then used to calculate the fracture stress or strength by converting the measured force values to stress values using analytical formulas specific to the test and sample geometry. In this thesis, 3-point-bending (3PB) tests were conducted to measure the fracture force of UTCs having a thickness of 30 µm. The 3PB tests were performed with a universal testing machine, Inspektmini (Figure 2.2) from Hegewald & Peschke GmbH equipped with variable load cells. A 50 N load cell was used for measuring the force in this work. During the 3PB test, the UTC was placed on two supporting rods and a mechanical load was applied with a loading rod at a speed of 1 mm/min. Besides UTCs, the fracture strength of relatively thicker chips having thicknesses of 65 and 130 µm were also calculated in this work to understand the relationship between chip thickness and fracture strength. Figure 2.3 shows a bent UTC during a 3PB test. The loading rod used for applying the load had a radius of 1 mm and the loading span was 8 mm for chips with 30 and 65 µm thicknesses while a loading span of 10 mm was used for chips having a thickness of 130 µm. Rectangular samples having dimensions of 12 mm x 4 mm were used for the 3PB tests so that the stress along the breadth of the sample remains constant during load application, thus resulting in an equally loaded stress on the surface as well as along the edges of the sample. The same sample length and breadth was maintained for all chip thicknesses.

#### 2.2 Fabrication of ultra-thin chips

UTCs can be manufactured using both additive and subtractive approaches. Additive methods involve processes to grow and release thin silicon layers after fabrication of the device whereas subtractive methods consist of thinning and dicing of the device silicon wafer down to the

Fig. 2.2 Universal Testing Machine used for experiments

Fig. 2.3 A standalone UTC during a 3PB test [115]. Reused with permission from IMAPS.

desired thickness. Some of the renowned additive and subtractive techniques of fabricating UTCs are listed in table 2.1. In this work, UTCs were prepared using well-established *Dicing-by-Thinning* process that follows a subtractive approach consisting of two main steps: (a) wafer dicing and (b) wafer grinding. A schematic of the *Dicing-by-Thinning* process followed to prepare the thin and ultra-thin chips is portrayed in figure 2.4.

The process started with the selection of silicon prime wafers having thickness of  $\approx$ 700 µm. Since no electrical functionality is required to measure the fracture strength of the chips, test samples were fabricated from blank silicon wafers without any metal patterns. However, it should be noted that the fracture strength of processed chips with structures is expected to be lower than that of blank chips without any structures [113, 125]. After selection of wafers, grooves were scribed on the front side of the sample wafers using

further processing

| · ·                                              | C                                                              |

|--------------------------------------------------|----------------------------------------------------------------|

| Additive methods                                 | Subtractive methods                                            |

| Trench-protect-etch-release [116]                | Dicing Before Grinding [117]                                   |

| Controlled spalling technique [118]              | Soft-etch-back [119]                                           |

| Epitaxial layer transfer [120]                   | Dicing by Thinning [121]                                       |

| Chip Film [122]                                  | TAIKO Process [123]                                            |

| Sample wafer  1. Sample wafer with diced grooves | Sample wafer  Carrier wafer  3. Wafer stack ready for grinding |

| Sample wafer Thermal release tape                | Grinding wheel  Carrier wafer  4. Wafer grinding               |

| Carrier wafer                                    | Carrier wafer                                                  |

| 2. Bond sample wafer to carrier wafer            | 5. Thinned sample wafer ready for                              |

Table 2.1 Technologies for fabricating UTCs

Fig. 2.4 *Dicing-by-Thinning* process for fabricating UTCs, Figure originally published in [124]. Slightly modified and reused here with permission from Springer Science and Bus Media B V.

Wafer Sawing for the predefined  $l \times b$  dimensions in a sawing equipment having diamond equipped rotating cutting wheels. Precise dicing of the wafers is crucial since the depth of the grooves defines the final thickness of the chips. Then, the sample wafers were bonded to carrier wafers using a thermal release tape,  $Revalpha^{\oplus}$  from  $Nitto\ Denko\ Corporation$ , that is releasable at 90 °C. The carrier wafers provide rigid support for the sample wafers after thinning below 50  $\mu$ m where silicon becomes flexible, thus ensuring secure handling and further processing of the sample wafers. Next, the sample wafers were thinned from the rear side with  $Wafer\ grinding$  where rotating diamond wheels grind and remove material physically. The wafer grinding process usually consists of a coarse and a fine grinding step. Coarse grinding step is performed with bigger diamonds for fast material removal while fine grinding is effected with smaller diamonds. Wafer grinding usually results in a rough

rear side having total thickness variation (TTV) in the range of  $\approx 1-2 \, \mu m$ . Following the wafer grinding step, a *Wet chemical spin etching* process was performed as the stress-relief step where the damaged layers on the rear side of the sample wafer arising from the wafer grinding step were removed chemically. Wet-chemical spin etching normally results in a mirror-like finish on the rear side of the sample wafer and improves the fracture strength of the chips [126]. However, such complete removal of micro-defects from the surface as well as edges of the chips to achieve a mirror-like finish would require complex, long-lasting and expensive polishing processes. Therefore, some micro-cracks as well as notches would persist on the chips in most of the wafer thinning processes. Finally, the chips from the sample wafers were released from the carrier wafers on a hotplate at  $100 \, ^{\circ}$ C. Further detailed information regarding the *Dicing-by-Thinning* process of fabricating UTCs can be found here [121].

#### 2.3 Principle of 3-point-bending tests

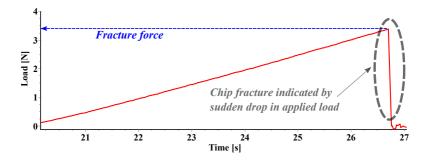

As mentioned earlier, 3PB tests were conducted on thin and ultra-thin silicon chips to measure their fracture force in this work. During the 3PB tests, the applied load was measured continuously and a load-time curve was plotted (Figure 2.5). When the chip fractured due to the applied load at its fracture force, the applied load drops suddenly as indicated by the vertical drop of the load curve (Figure 2.5) and the fracture force of the chip was determined from the load value corresponding to the peak of the load-time curve.

Fig. 2.5 Load-time curve plotted during a 3PB test. The load value corresponding to the peak of the red load-time curve denoted by the blue arrow line is the fracture force [115]. Reused with permission from IMAPS.

| Chip thickness | Mean Fracture Force | Characteristic Fracture Force<br>@63.2% Fracture Probability |

|----------------|---------------------|--------------------------------------------------------------|

| (µm)           | (N)                 | (N)                                                          |

| 30             | 0.0766              | 0.08                                                         |

| 65             | 0.6149              | 0.626                                                        |

| 130            | 2.2735              | 2.44                                                         |

Table 2.2 Mean fracture force of chips measured using 3PB tests

#### 2.4 Fracture force measurement of thin and ultra-thin chips

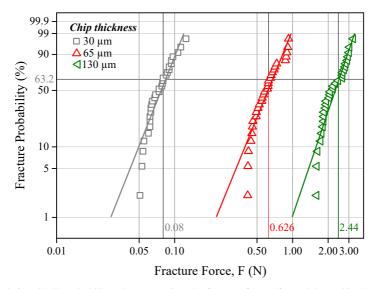

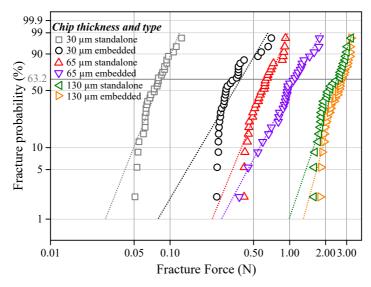

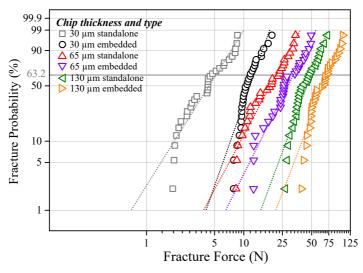

3PB tests were performed on 30 test samples for each chip thickness and the results obtained from the tests are summarized in table 2.2. Generally, data obtained from the tests are plotted in various types of graphs such as histograms, box charts, scatter plots and Weibull plots for statistical analysis. Among these different types of graphs, Weibull plots provide information concerning failure analysis, failure probability and failure forecasts even for a small number of samples. The slope of a Weibull plot corresponds to the variation in results and hence a steeper Weibull plot indicates lower distribution of the results. The fit of any chosen data to a Weibull distribution can be evaluated with a Weibull plot. In case of a Weibull probability plot for fracture strength analysis, the x axis of the Weibull plot is the fracture force (F in N) or fracture stress ( $\sigma$  in Pa) and the y axis is the fracture probability. Figure 2.6 presents the Weibull probability plot of the measured fracture force of the chips with three different thicknesses. In figure 2.6, the straight line corresponding to a fracture probability of 63.2% denotes the force at which 63.2% of the samples would fail indicating the most likely load for chip fracture called *Characteristic Fracture Force or Load*. The Failure Distribution ( $P_f$ ) is defined by the following formula:

$$P_{\rm f} = 1 - \exp(-\frac{F}{F_C})^m \tag{2.1}$$

where F is the applied load or the force,  $F_C$  is the characteristic fracture force or load and m is the value of variability or Weibull modulus.

#### 2.5 Fracture stress calculation

When a comparative analysis is performed with different chip types and if the chip thickness remains the same across the different types, either fracture force or strength can be used to compare the strength of the different chips. But, when the chip thickness changes, thicker chips would sustain a higher applied load before fracture than thinner chips, thus exhibiting

Fig. 2.6 Weibull probability plot comparing the fracture force of standalone chips having different thicknesses  $(30, 65 \text{ and } 130 \, \mu m)$  during 3PB tests

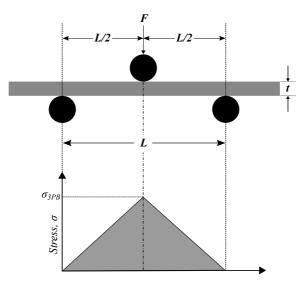

higher fracture forces. In such a case, fracture force can no longer be used to compare the strength of the chips and fracture stress is required to evaluate the strength of the chips since fracture stress is a material property that does not change with variations in the sample dimensions. However, it should be noted that material properties such as Young's Modulus of experimental samples differ from ideal material properties due to various process induced changes in the samples. Therefore, a comparative analysis based on fracture stress would provide the real information regarding the strength of the chips when chips with different thicknesses are examined. Hence, the measured fracture force must be converted to fracture stress by eliminating the influence of the geometrical factors such as cross-sectional area since stress is defined as the force applied per unit area. The fracture stress of chips examined using 3PB tests can be calculated using equation 2.2 given below.

$$\sigma_{\rm 3PB} = \frac{3FL}{2bt^2} \tag{2.2}$$

where  $\sigma_{3PB}$  is the fracture stress in Pa, F is the fracture force in N, L is the load span or the distance between the supporting rods, b is the breadth of the chip and t is the thickness of the chip (Figure 2.7).

Fig. 2.7 Principle of 3-point-bending test [115]. Reused with permission from IMAPS.

#### 2.6 Calculation of fracture stress of UTCs

The equation 2.2 can be used to calculate fracture stress from measured fracture force only when a linear force-displacement relationship exists for the samples. In case of flexible UTCs, the force-displacement relationship becomes non-linear at higher displacements due to slipping of the chips from the supporting rods of the sample holder causing the chips to undergo higher displacements before fracture [127]. Therefore, equation 2.2 may not be used to calculate the fracture strength of the UTCs. In such cases, Finite Element Method (FEM) simulations can be used to calculate the fracture stress of the UTCs. Such FEM simulations were performed in this work to calculate the fracture stress from the measured fracture force values. As mentioned earlier, the material properties of experimental samples are different from ideal material properties due to various process induced changes in the samples. For the sake of simplicity, ideal material properties of Silicon <110> (Young's Modulus = 168.9 GPa and Poisson's ratio = 0.361 [128]) were used for the simulations performed in this work. Due to sample and test setup symmetry, only a quarter symmetrical model was used for the simulations and the simulations were performed with displacement control. Figure 2.8 presents the quarter symmetrical model used for the FEM simulations.

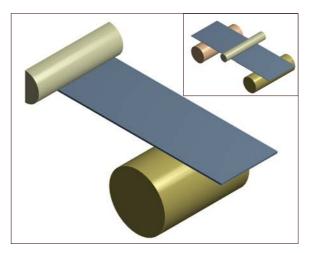

Fig. 2.8 Quarter symmetrical FEM model used for calculating fracture stress of UTCs. Inset: Full symmetrical model [115]. Reused with permission from IMAPS.

Table 2.3 Mean fracture stress of standalone chips calculated using analytical formula and FEM simulations

| Chip<br>Thickness | Mean<br>Fracture Force | Mean<br>Fracture Stress |              | Characteristic<br>Fracture Stress  |                                  |

|-------------------|------------------------|-------------------------|--------------|------------------------------------|----------------------------------|

| (µm)              |                        | Analytical (MPa)        | FEM<br>(MPa) | @63.2% Frac<br>Analytical<br>(MPa) | ture Probability<br>FEM<br>(MPa) |

| 30                | 0.077                  | -                       | 249          | -                                  | 260                              |

| 65                | 0.615                  | 437                     | 420          | 425                                | 445                              |

| 130               | 2.274                  | 505                     | 517          | 542                                | 554                              |

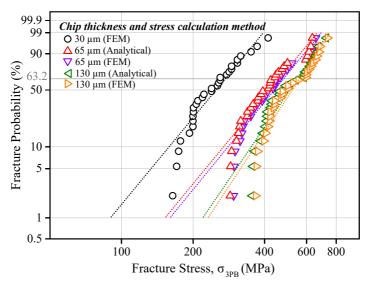

The stress values obtained from the FEM simulations are plotted alongside analytically calculated values (using equation 2.2) in a Weibull plot in figure 2.9. The mean stress values calculated from FEM simulations and analytical calculations that are summarized in table 2.3 indicate very good correlation with each other, thus validating the FEM simulations. Table 2.3 also reveals that the fracture stress of the chips decrease with a corresponding decrease in the chip thickness which complies with an earlier published work [129]. However, other studies have shown that the fracture stress of thinner chips can be increased by implementing advanced dicing and thinning processes [130, 131], thus indicating that wafer thinning as well as dicing processes followed in this work could be improved to achieve higher fracture stress

Fig. 2.9 Weibull probability plot comparing the fracture stress values of standalone chips having different thicknesses (30, 65 and  $130\,\mu m$ ) calculated using FEM simulations and analytical formula for 3PB tests. Figure originally published in [115]. Slightly modified and reused here with permission from IMAPS.

for thinner chips. Therefore, it becomes evident that the fracture stress of thinner chips could be enhanced by following advanced dicing and thinning processes such as plasma etching or longer stress relief processes to singulate the chips where almost all of the micro-cracks as well as notches could be eliminated resulting in defect-free edges and chip surface [132, 133]. However, plasma etching is rather expensive compared to wafer sawing due to the additional requirement of a mask to define the etching streets and it becomes cheaper only when huge number of wafers are processed [134]. Similarly, a longer stress relief process would also increase the cost due to the decrease in throughput. Therefore, a cheaper solution to enhance the fracture strength of the UTCs is required.

#### 2.7 Enhancement of robustness of UTCs

As mentioned earlier, fracture stress is a material property that depends on the thinning as well as the dicing processes and UTCs would fracture when they reach their fracture stress. Therefore, fracture stress of chips can not be enhanced without improvising the thinning and

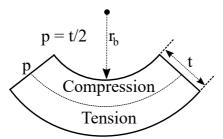

Fig. 2.10 Position of neutral plane (p) in an isotropic standalone chip

dicing processes. However, by embedding the chips in a stack of polymer layers, the applied load can plausibly be distributed across the sample surface, thus reducing and preventing the sample from stress peaks. Such a load distribution across the sample would result in enhancement of the robustness of the UTCs against externally applied loads without altering the thinning and dicing processes. The position of the embedded chip with respect to the neutral plane of the CFP stack determines the stress experienced by the UTC. Neutral plane is the plane of zero stress where compressive and tensile stresses cancel each other during bending (Figure 2.10). Since silicon is piezoresistive, the electrical performance of silicon ICs change when they are stressed due to both in-built stresses resulting from IC processing [135] and externally applied stress [136, 137]. Sometimes better electrical performance can be derived from the ICs when they are stressed [138, 139]. Yet, it is complicated to include the bending effects of ICs in most state-of-the-art simulation tools to predict the electrical performance. Therefore, it is simpler and advantageous to have the same electrical performance for the ICs in both flat and bent state.

When a standalone chip is bent to a radius  $(r_b)$ , the neutral plane lies at its mid-plane. Likewise, the neutral plane of a symmetrical stack lies at its mid-plane during bending. However, when the stack is unsymmetrical, the position of neutral plane is controlled by the thickness and the Young's Modulus of the embedding layers.

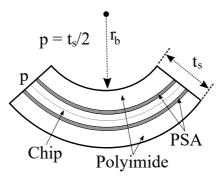

A schematic of the bent symmetrical CFP stacks analysed in this work is depicted in figure 2.11. The stacks were prepared by mounting ICs on commercially available Polyimide (*PI*) foil substrates, *UPILEX 50S*<sup>TM</sup> from *UBE Industries* having a thickness of 50  $\mu$ m. The chips were attached to the PI foil substrates with a  $\approx$ 5  $\mu$ m thin layer of a Pressure Sensitive Adhesive (*PSA*) coated on top of the PI foil substrates. A manually operated flip-chip bonder, *FINEPLACER*<sup>®</sup> from *Finetech Gmbh & Co. KG* was used to bond the chips. Then, similar PI foil substrates coated with  $\approx$ 5  $\mu$ m thin PSA were laminated on top of the chips to fabricate *Chip Foil Packages* (*CFPs*) with symmetrical layers so that the neutral plane

Fig. 2.11 Schematic of the cross-section of a bent symmetrical CFP showing the position of the neutral plane (p)

of the CFPs remained at their mid-plane during bending. 3PB tests were then performed on the fabricated CFPs using the same test geometries and conditions followed for the 3PB tests for standalone chips. The mean fracture force obtained from the tests were then used to analyse the enhancement of robustness of the UTCs by comparing the mean fracture force of embedded and standalone UTCs. Since fracture stress of the chip remains the same whether or not it is embedded, the chips would fracture when subjected to the same stress irrespective of embedding.

Figure 2.12 summarizes the fracture force ( $F_{max}$ ) measured for standalone chips and chips embedded in polymer layers (CFPs) for the three different chip thicknesses. It can be noticed in figure 2.12 that the fracture force is higher for the CFPs than for the standalone chips of corresponding thickness. This increase in fracture force indicates that a higher force is required to impose the same stress on the chips when they are embedded in polymer layers. The increase in fracture force of CFPs results from the increase in stiffness effected by the overall thickness increase arising from the additional polymer layers. Therefore, fracture of both standalone and embedded chips with the same chip thickness would occur at the same fracture stress irrespective of embedding. However, a higher force ( $F_2$ ) is required to induce the fracture stress in an embedded chip compared to a standalone chip ( $F_1$ ) having the same chip thickness as evident from the experimental results (Figure 2.13).

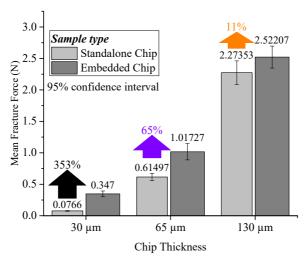

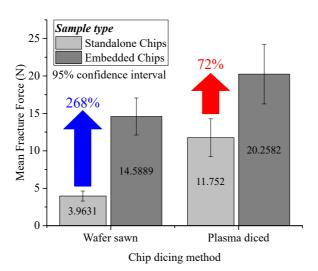

A summary of the mean fracture force values measured from 30 samples is presented in figure 2.14. It can be noticed from the graphs that the normalised difference between the mean fracture force of embedded and standalone chips increases as the chips become thinner. The normalised difference between the mean fracture force of embedded and standalone chips was 353.%, 65% and 11% for chip thickness of 30, 65 and  $130\,\mu m$  respectively. Thus,

Fig. 2.12 Weibull probability plot comparing the fracture force of standalone and embedded chips having different thicknesses (30, 65 and  $130\,\mu m$ ) during 3PB tests. Figure originally published in [115]. Slightly modified and reused here with permission from IMAPS.

it can be understood that the influence of embedding of chips on their fracture force/strength increases with a decrease in chip thickness. Since stiffness increases with an increase in thickness and Young's Modulus, a higher force is required to bend the chips embedded in PI substrates compared to standalone UTCs. Therefore, the robustness of chips against external load (i.e. fracture force or load) can be drastically enhanced either by increasing the thickness of the embedding polymer substrates or by replacing the polymer substrates by materials with higher Young's Modulus like metal foils.

# 2.8 Effect of Young's Modulus of embedding material on the robustness of embedded UTCs

The influence of Young's Modulus of the embedding material on the stress experienced by the chip during bending was analysed in this work with FEM simulations where the stress experienced by the embedded chip was compared for a CFP with top and bottom layer of the CFP made of Stainless Steel 316 and PI foil having the same thickness of  $50 \, \mu m$ . The

Fig. 2.13 Bent UTCs: Standalone and embedded in PI substrates at the same bending radius

Fig. 2.14 Mean fracture force of standalone and embedded chips during 3PB tests. The arrows and the numbers above the arrows represent the increase in fracture force of the chips due to embedding. The numbers elucidate that a higher load distribution was achieved for CFPs with thinner chips with the same embedding foil thickness. Figure originally published in [115]. Slightly modified and reused here with permission from IMAPS.

| Chip      | Type       | Mean           | Characteristic              |

|-----------|------------|----------------|-----------------------------|

| Thickness |            | Fracture Force | Fracture Force              |

|           |            |                | @63.2% Fracture Probability |

| (µm)      |            | (N)            | (N)                         |

| 30        | Standalone | 0.077          | 0.08                        |

|           | Embedded   | 0.347          | 0.332                       |

| 65        | Standalone | 0.615          | 0.626                       |

|           | Embedded   | 1.017          | 1.075                       |

| 130       | Standalone | 2.274          | 2.44                        |

|           | Embedded   | 2.522          | 2.74                        |

Table 2.4 Fracture force of standalone and embedded chips measured using 3PB tests

Table 2.5 Material properties used for FEM simulations [128, 140, 141]

| Material            | Young's Modulus (GPa) | Poisson's ratio |

|---------------------|-----------------------|-----------------|

| Silicon <110>       | 168.9                 | 0.361           |

| UPILEX 50S          | 9.3                   | 0.35            |

| Stainless Steel 316 | 194.6                 | 0.294           |

PSA layers bonding the chip with the foils were not included in the simulation model for simplifying the simulations. The material properties used for the FEM simulations are listed in table 2.5. Table 2.6 compares the fracture force as well as fracture displacement calculated using FEM simulations for a fracture stress of 249 MPa (determined from 3PB tests and corresponding FEM simulations) when PI and Stainless Steel 316 are used as the embedding layers. It can be noticed that the embedded chip in a CFP with Stainless Steel 316 foils would fracture at a lower displacement than the embedded chip in a CFP with PI foils. However, a much higher load (≈16x more) would be required by the UTC to reach its fracture stress of 249 MPa i.e.) the fracture force of an UTC embedded in Stainless Steel 316 foils would increase by ( $\approx$ 16x more) with a corresponding decrease in fracture displacement ( $\approx$ 4.4%) than an UTC embedded in PI foils. In other words, UTCs can be bent up to ≈4.4% more if a compliant substrate such as PI foil is used as the embedding layer instead of a stiffer substrate like Stainless Steel. Therefore, stiffer materials such as Stainless Steel 316 can be used as the embedding material where a higher durability against externally applied load at smaller bending radii is required and softer materials like PI foils can be used for applications targeting higher bendability. Thus, embedding of chips with appropriate material could prove as a faster and cost effective alternative to increase the robustness of chips against externally applied load rather than performing expensive polishing and stress relief processes.

Table 2.6 Fracture force and displacement for embedded UTCs with different embedding materials (calculated with FEM simulations for a fracture stress of 249 MPa)

| Embedding<br>Material | Fracture<br>Force | Fracture<br>Displacement |  |

|-----------------------|-------------------|--------------------------|--|

|                       | (N)               | (µm)                     |  |

| Polyimide             | 0.36              | 309                      |  |

| Stainless Steel 316   | 5.74              | 296                      |  |

# 2.9 Minimising the impact of chip micro-defects on the robustness of UTCs

## 2.9.1 Acoustic Emission assisted fracture force detection of chip foil packages

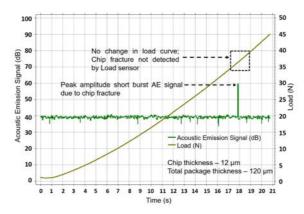

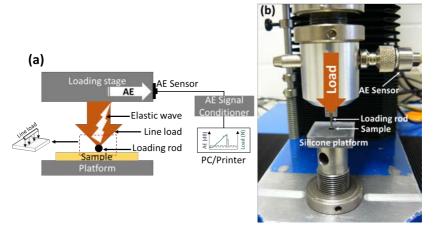

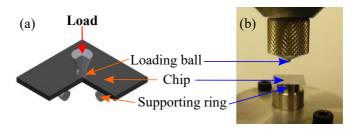

As mentioned earlier, the fracture force of UTCs can be improved if plasma etching is implemented instead of wafer sawing to singulate the chips. However, the higher costs effected for less number of samples hamper the usage of plasma etching for several applications. Nevertheless, the fracture force of chips singulated using plasma etching were investigated in this work to have a comparative analysis with the fracture force of chips diced using wafer sawing. Furthermore, both chip types were also embedded in polymer layers to evaluate the influence of embedding polymers on their fracture force and thereof on the micro-defects arising from chip dicing was analysed. The UTCs measured 3.2 mm x 2.4 mm with a thickness of 20 µm and the only difference between the UTCs was the dicing method. Owing to the smaller dimensions of the chips, Line-Load Test (LLT) [142] was implemented instead of 3PB tests to measure the fracture force of UTCs where the samples were placed on an elastomeric polymer platform and mechanical load was applied with a loading rod. A 7 mm thick Silicone supporting platform was picked off the shelf and the test samples were laid on top of the platform during the tests as the load was applied to the samples with the same loading rod used for 3PB tests. The measurement of fracture force of standalone UTCs was simpler and straight forward as the fracture of the samples was detectable by the force sensor of the universal testing machine. However, in case of CFPs, the fracture of the embedded UTCs was undetectable by the force sensor. Therefore, an Acoustic Emission (AE) sensor was added to the setup to accurately detect the fracture event and to precisely determine the fracture force by correlating the peak amplitude short burst AE signal of the AE sensor with the corresponding load value on the load-time curve (Figure 2.15). A schematic and the photo of the AE assisted LLT test setup used in this work are presented in figure 2.16.

Fig. 2.15 Accurate determination of fracture force of embedded UTCs during LLT by correlating load and AE curves. Figure originally published in [143]. Reused here with permission from Mesago Messe Frankfurt GmbH.

Fig. 2.16 (a) Schematic and (b) photo of the AE assisted LLT test setup implemented in this work. Figure originally published in [143]. Reused here with permission from Mesago Messe Frankfurt GmbH.

#### 2.9.2 Principle of Acoustic Emission sensors

AE sensors have long been used as quality assurance and failure identification tool in Civil Engineering, Geology, Material Science, industrial process monitoring and machine condition analysis to name a few [144-147]. Acoustic Emission is the phenomenon in which acoustic waves are generated due to the redistribution of the materials resulting from the irreversible changes in their internal structure. Internal changes such as plastic deformation, crack formation and propagation, erosion and corrosion, and impact produce transient elastic waves due to sudden release of elastic energy. The transient elastic wave arising from the internal structural change propagates in the material until it reaches the material surface where it creates a surface motion by interacting with the material surface. When AE sensors are attached to the surface of the material, the surface motion can be captured by the sensors which then convert the captured surface motion into an electric signal. The converted electrical signal can be then processed and used to identify the exact moment of failure occurrence. If the surface area of the material to be tested is too small, sensors can be mounted to an adjacent body that is in physical contact with the sample. Two types of failures, namely failures occurring once (burst AE) or repeatedly (continuous AE) can be identified and monitored using AE sensors. In short, AE sensors are much more sensitive to material damages than force sensors and hence they enable accurate detection of a fracture event. In this work, the exact fracture force of the samples were obtained by correlating the peak amplitude short burst AE signal with the corresponding load value on the load-time curve as elucidated in figure 2.15.

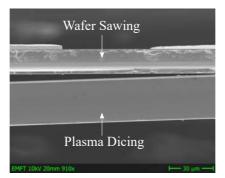

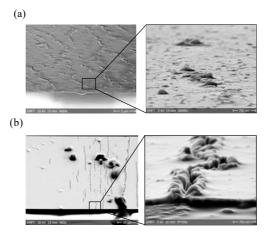

Fig. 2.17 Scanning Electron Microscope (SEM) image of sidewall of wafer sawn and plasma diced UTCs [99]. ©2016 IEEE. Reused here with permission from IEEE.

## 2.9.3 Effect of dicing induced micro-defects on the fracture force of UTCs

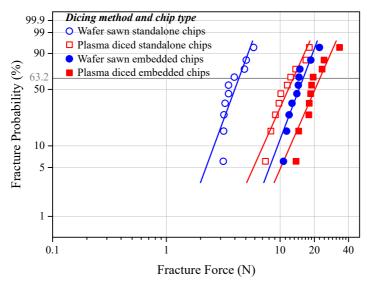

10 samples for each chip dicing type were tested and the measured fracture force values are plotted in a Weibull Plot (Figure 2.19). Since all the examined UTCs have the same thickness of 20  $\mu$ m, strength of the UTCs can be analysed by comparing their fracture force. The mean fracture force of the UTCs measured from the experiments are included in table 2.7. A closer look at (Figure 2.19) and the table 2.7 exemplifies the influence of the dicing induced damages on the fracture strength of standalone UTCs. It can be noticed that the mean fracture force of standalone plasma diced chips are higher (7.79 N or  $\approx$ 197% more) than that of standalone wafer sawn chips. The difference in fracture force between the two standalone UTC types is attributed to the presence of defects such as micro-cracks and notches on the edges as well as sidewalls of the UTCs. Since the chip edges of plasma diced chips are almost devoid of micro-defects, plasma diced UTCs tend to have a higher fracture strength compared to wafer sawn UTCs. The following subsection 2.9.4 elucidates the difference in the chip sidewall roughness of wafer sawn and plasma diced chips via Atomic Force Microscopy (AFM) analysis performed on the sidewall of the chips.

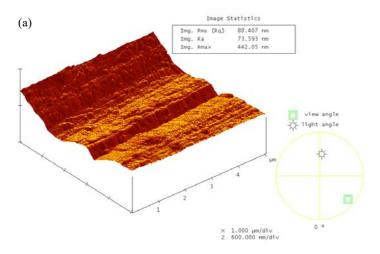

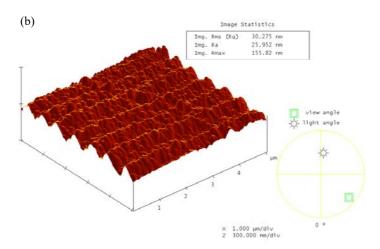

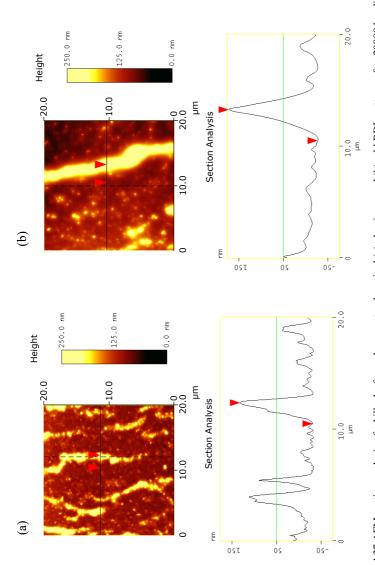

#### 2.9.4 Sidewall roughness analysis of UTCs