# A MODIFIED DOMINO LOGIC CIRCUIT FOR IMPROVED NOISE IMMUNITY AND DELAY VARIABILITY

RAVIKANT THAKUR<sup>1</sup>, AJAY KUMAR DADORIA<sup>2</sup>, TARUN KUMAR GUPTA<sup>3</sup>

<sup>1, 2, 3</sup> Electronics and Communication Department, MANIT, Bhopal, INDIA <sup>1</sup>ravielex55@gmail.com, <sup>2</sup>ajaymanit0@gmail.com, <sup>3</sup>taruniet@rediffmail.com

# ABSTRACT

This paper gives an approach for improvement in the reduction in delay variation in a domino logic circuits and it also gives improved noise immunity to the circuit. The improvement in delay observed here is better in the proposed circuit and the noise immunity is also enhanced by a good margin. The simulation process here is done by using Cadence Virtuoso 65nm process technology at  $27^{\circ}$ C operating temperature and 0.8 V operating supply voltage (V<sub>DD</sub>) for the circuit.

*Keywords:* High speed integrated circuit, dynamic logic circuit, Unity noise gain (UNG), Domino logic circuit, Noise immunity.

# [1] INTRODUCTION

Most of the dynamic logic circuits are used to achieve reliability, high speed, and compact circuits by using least complicated clocking scheme [9], [7]. Domino CMOS logic gates allow a significant reduction in number of transistors required to realize any complex Boolean function. A wide range of circuits where high speed and high performance is taken into consideration, Domino logic circuits are used. Keeper transistor approach is used in various domino logic circuits [6]. Some keeper transistor approach makes the circuit leakage tolerable but costs some performance regarding noise immunity [3], [5]. In Domino logic circuits the high performance is achieved because of the reduced input capacitance, observed by the driver gate [8]. Domino circuits are widely used in high performance microprocessors and DSP circuits, such as high fan-in multiplexer or comparator circuits [10].Section (1) explains some basics of Domino logic circuit for the betterment of the noise margin. Simulation result and conclusion is discussed in Section (4) and Section (5) respectively.

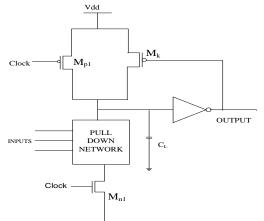

# [2.1] CONVENTIONAL APPROACH

The approach used here is to reduce the delay variation associated in the circuit. The Domino logic circuits are highly used for high speed and high performance applications. The problem of delay variation causes mostly in high performance application circuits, so, for Domino logic circuit the delay variation plays an important role. Therefore one should reduce the variation in delay as much as possible.

The previous analysis [1], [2] shows that delay variability in domino logic circuits is almost double compared to static logic circuits. Also it gives two important phenomenon that:-

a) The variability of delay at dynamic node is almost equal to the overall delay variability.

b) Variation in keeper transistor and pre-charge transistor do not significantly contribute to the delay variability at dynamic node.

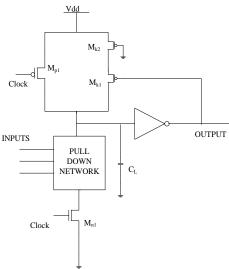

## Fig. 1: Simple Domino logic circuit

Therefore the conclusion to maintain the variability is that, the attention must be given to the positive feedback loop implemented by using the keeper transistor and the inverter. The delay variability here has calculated by using Monte Carlo simulation. The ratio of mean value of certain amount of delay sample and the variance of the same amount of sample is known as delay variability.

# [2.2] APPROACH USED

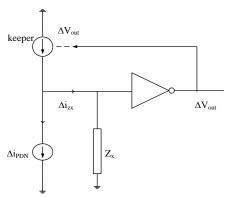

The positive feedback loop analysis:-

Fig. 2: Feedback loop analysis of Circuit

To calculate the small signal loop gain the pull down network can be considered as a dependent current source and the keeper transistor as an independent current source controlled by  $\Delta V_{out}$ .

$$\Delta i_{KEEPER} = -G_{m,KEEPER} * \Delta V_{out}$$

$$\Delta V_{x} = Z_{x} \Delta i_{zx}$$

$$\Delta i_{zx} = \Delta i_{PDN} - \Delta i_{KEEPER}$$

Therefore the feedback associated keeper transistor having non-inverting loop gain (T) can be given by-

$$T = A_{INV} G_{m,KEEPER} * Z_x$$

(1)

Where  $A_{INV} = Voltage gain of Inverter$

As equation (1) indicates, to reduce the loop gain the reducible parameters can be either  $A_{INV}$  or  $Z_x$  or  $G_{m,keeper}$ . In the conventional approach the main focus given is to reduce  $G_{m,keeper}$ , so that the loop gain can be minimized. The desired condition can be achieved by –

A) By splitting the keeper transistor into two keeper transistor :-

In the figure the keeper transistor  $M_{k1}$  is driven by the transistor and the second keeper  $M_{k2}$  here works as a resistor of which the resistance is

$$R \approx \left[\mu_{p} C_{ox} \left(\frac{W}{L}\right)_{kp\,2} \left(V_{DD} - |V_{tp}|\right)\right]^{-1}$$

and

By observing equation (2) it clearly shows the desired reduction in the trans-conductance,  $G_{m,keeper}$  associated in the circuit.

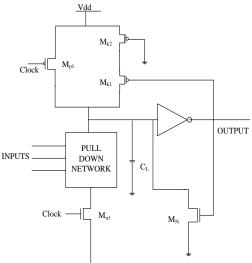

Fig. 3: Domino Logic Circuit with two keeper

Indexing in Process - EMBASE, EmCARE, Electronics & Communication Abstracts, SCIRUS, SPARC, GOOGLE Database, EBSCO, NewJour, Worldcat, DOAJ, and other major databases etc.,

#### B) By sizing the transistor :-

&

To provide the same DC current as the basic domino circuit, it is necessary to size  $M_{kp1}$  and  $M_{kp2}$ . Here the transistors are in series therefore

$$\begin{split} \mathbf{W}_{kp1} &= \mathbf{W}_{kp2} = \mathbf{W}_{min.} \\ \mathbf{L}_{kp1} + \mathbf{L}_{kp2} = \mathbf{L}_{kp} \end{split}$$

$$(L/W)_{kp1} + (L/W)_{kp2} = (L/W)_{kp2}$$

and hence

That equation shows that the overall length for the keeper transistor is the same, therefore the increment in silicon area is negligible.

# [3.1] PROPOSED TECHNIQUE FOR A LEAKAGE TOLERANT AND BETTER NOISE MARGIN CIRCUIT

The proposed circuit here is implemented in 65 nm Cadence Virtuoso CMOS technology with the power supply of 0.8 V. The proposed circuit is based on footed domino logic circuit and based on this the proposed circuit is given which is having better leakage tolerance and improved noise immunity. The circuit is shown in Fig. 4 and has been simulated for 2, 4, 8 and 16 inputs OR gate.

To operate the circuit basically there are two modes of operation, namely pre-charge mode and evaluation mode. During pre-charge phase, the dynamic node of all the gates are charged to  $V_{DD}$ , which also causes the inverter output to go to 0 V. Now during the evaluation phase the logic signal associated with the pull down network is evaluated and the inverter output perhaps changes from 0 to  $V_{DD}$  or some inverter output may remain at ground depending upon the logic signal provided to the pull down network.

In the proposed circuit an NMOS is added as shown in Fig. 4. The main function of this transistor is to draw the contention current of the PMOS keeper and also it helps to speed up the discharging process of the capacitor at the dynamic node. At the beginning of the pre-charge mode the pre-charge device is in active mode. Therefore the voltage at the dynamic node will be at 0 V and hence that will pass through an inverter so the output at the inverter will be  $V_{DD}$ . In consequence the extra added transistor will turn on and at the beginning of the pre-charge phase there will be contention of current between the two current derived from the extra added transistor and the keeper transistor because the pre-charge device tries to charge the capacitor  $C_L$  and the current due to the added NMOS tries to discharge the capacitor  $C_L$

Fig. 4: Proposed modified Domino Logic Circuit

During the evaluation phase the pre-charge device gets OFF because at this time the clock switches from logic '0' to logic '1'. Now the cases where inputs are such that the capacitor  $C_L$  must retain the charge, then the output will be zero. Also if the inputs are such that the Pull down network must discharge the capacitor  $C_L$ , then the dynamic node voltage will start decreasing. At the beginning of discharging process the inverter output will be at zero, which will cause the extra added NMOS to stay inactive. The extra added NMOS compensates the keeper current and speed up discharging of capacitor  $C_L$ .

### [3.2] UNITY NOISE GAIN

To check whether the circuit is tolerable to the noise or not, it may be checked by applying a small noise pulse to all the inputs provided to the circuit. That input noise pulse should be given primarily during the evaluation

Indexing in Process - EMBASE, EmCARE, Electronics & Communication Abstracts, SCIRUS, SPARC, GOOGLE Database, EBSCO, NewJour, Worldcat, DOAJ, and other major databases etc.,

phase. To check the noise immunity the metric used here is Unity noise gain. The amplitude of the input (noise input) for which the amplitude of the output is same as the input is known as Unity Noise Gain (UNG). Mathematically it can be presented as

$$UNG = (V_{noise}; V_{noise} = V_{out})$$

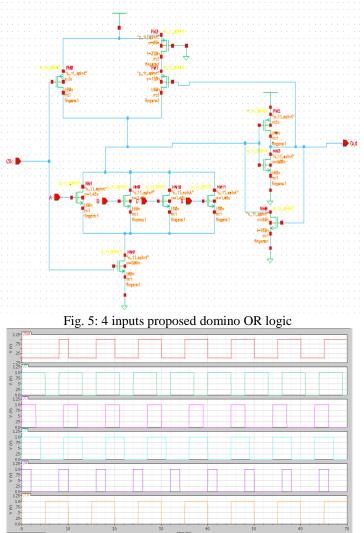

### [4] SIMULATION RESULT

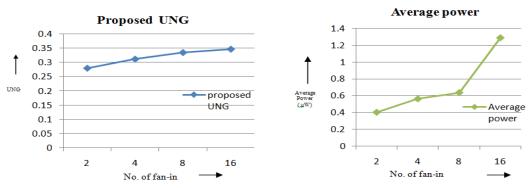

The simulation process here is done by using Cadence Virtuoso Tool 65 nm technology using analog design environment (ADE). The previous analysis shown in the conventional approach is majorly concentrated on the variation in delay in a Domino logic circuit and simulated in both 65 nm and 90 nm technology. In this proposed circuit the comparison of delay with the conventional circuit is done, using 65nm technology only and it is observed that the delay in both the circuits are almost same. In the proposed approach various parameters such as delay, Unity noise gain (UNG) and average power dissipation has been calculated for different-different inputs such as 2, 4, 8 and 16 inputs. The parameters calculated here is obtained by applying supply voltage  $V_{DD}$ as 0.8 V and operating temperature as  $27^{0}$  C. The result which compares the UNG of proposed circuits with the traditional circuit is shown in Table 1.

Fig. 6: Transient response of 4 inputs proposed domino OR logic

| ſ | Fan in | UNG of standard | UNG of conditional keeper | UNG of proposed Domino |

|---|--------|-----------------|---------------------------|------------------------|

|   |        | Domino          | Domino                    |                        |

|   | 2      | 0.218           | 0.287                     | 0.279                  |

|   | 4      | 0.196           | 0.263                     | 0.311                  |

|   | 8      | 0.171           | 0.242                     | 0.334                  |

|   | 16     | 0.132           | 0.159                     | 0.346                  |

### Table 1: Comparison of UNG

Indexing in Process - EMBASE, EmCARE, Electronics & Communication Abstracts, SCIRUS, SPARC, GOOGLE Database, EBSCO, NewJour, Worldcat, DOAJ, and other major databases etc.,

1203

Fig. 7: UNG of the proposed circuit Fig. 8: Average power dissipation of the proposed circuit

# [5] CONCLUSION AND FUTURE SCOPE

Domino logic dissipates very low standby power compare to static CMOS logic. In this paper the main objective was to improve the noise immunity and to reduce the average power consumed and delay associated with the circuit. The analysis shows that by proposed circuit it is possible to achieve an appreciable improvement in the noise margin and power consumption and marginal improvement in delay. The whole comparison is based upon 65 nm CMOS technology using Cadence Virtuoso tool at circuit level.

## REFERENCES

- [1] Gaetano Palumbo, Melita Pennisi and Massimo Alioto "A simple approach to reduce delay variation in Domino logic gates," IEEE transaction on Circuits and Systems, Vol. 59. No.10, October 2012.

- Massimo Alioto, Gaetano Palumbo and Melita Pennisi "Understanding the effect of Process variation on [2] the delay of static and Domino logic," IEEE transaction on Very Large Scale Integration (VLSI) systems, Vol.18. No. 5, May 2010.

- Volkan Kursun and Eby G. Friedman "Domino logic with variable threshold keeper" IEEE transaction on [3] Very Large Scale Integration System. Vol. 11. No. 6, December 2003.

- [4] A. Kabbani and A.J.Al-Khalili "A technique for Dynamic CMOS Noise immunity Evaluation" IEEE transaction on Circuits and Systems- 1; Fundamental theory of application; Vol. 50; No.1; January 2003.

- Atila Alvandpour, Ram K Krishnamurthy, K. Soumyanath and Shekhar Y. Borkar; "A sub 130-nm [5] Conditional Keeper Technology" *IEEE transaction on Solid State Circuits*; Vol. 37; No. 5; May 2002. V. Kursun and E.G. Friedman, "Variable threshold voltage keeper for contention reduction in dynamic

- [6] circuits" Proc. IEEE Int. ASIC/SOC conf. Pp 314-318, Sept. 2002.

- K. Oh, L.S.Kim "A clock delayed sleep mode Domino logic for wide dynamic OR gate", in proceedings of [7] ISLPED'03 on Low power electronics and Design, 2003.

- M.W. Allah, M.H. Anis and M.I. Elmasry, "High speed dynamic logic circuits for scaled-down CMOS and [8] MTCMOS technologies" in Proc. IEEE Inter. Symp. Low Power Electronics Design, July 2000.

- R. Sung and D.Elliott "Clock logic Domino circuits for high speed and energy efficient microprocessor [9] pipelines" IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 54, no.5, pp. 460-464, May 2007.

- [10] H. Suzuki, C. H. Kim, and K. Roy, "Fast tag comparator using diode partitioned domino for 64-bit microprocessors," IEEE Trans. Circuits Syst., vol. 54, no. 2, pp. 322-328, Feb. 2007.