## **Inductance Modeling for On-Chip Interconnects**

# SHANG-WEI TU,<sup>1\*</sup> WEN-ZEN SHEN,<sup>1</sup> YAO-WEN CHANG,<sup>2</sup> TAI-CHEN CHEN<sup>2</sup> AND JING-YANG JOU<sup>1</sup>

<sup>1</sup>Department of Electronics Engineering, National Chiao Tung University, Hsinchu 300, Taiwan ROC

<sup>2</sup>Department of Electrical Engineering, Graduate Institute of Electronics Engineering, National Taiwan University, Taipei 106, Taiwan ROC

E-mail: kuma@athena.ee.nctu.edu.tw; wzshen@cc.nctu.edu.tw; ywchang@cc.ee.ntu.edu.tw; tcchen@eda.ee.ntu.edu.tw; jyjou@bestmap.ee.nctu.edu.tw

Received October 6, 2002; Revised October 27, 2002; Accepted November 15, 2002

Abstract. As the operation frequency reaches gigahertz in deep-submicron designs, the effects of inductance on noise and delay can no longer be neglected. Most of the previous works on inductance extraction are field-solvers, which are intrinsically more accurate but computationally expensive. Others focus on modeling the inductances of special routing topologies such as the bus structure. Therefore, it is not suitable to incorporate them on-line into a layout (placement and routing) tool for inductance (delay and noise) optimization. In this paper, we consider the overlapping of unequal wire lengths and dimensions to efficiently extract the loop inductance from the coplanar interconnect structure. The difference between our simulation results and the estimation values obtained by FastHenry [12] is within 10% for practical cases. In particular, our modeling is extremely efficient, and thus can be incorporated into a layout tool for inductance optimization.

Key Words: inductance, mutual inductance, self inductance, modeling, simulation, layout, interconnect

## 1. Introduction

As technology advances into the very deep-submicron era, interconnection delay dominates overall circuit performance and noise becomes more serious than before. Therefore, accurately predicting the interconnection delay and noise becomes a major challenge in high performance designs. For deep-submicron, high-performance circuits, ignoring inductance effects may incur a large amount of error, since an RC model as compared to an RLC model may create errors of up to 30% in the total propagation delay of a repeater system [1], and in some worst cases the noise coupling due to C and L may reach around 55% of the supply voltage [2]. As technology improves and die size increases, short rise/fall times of signals and long wires make inductance effects much more significant than before [3]. Therefore, it is very important to consider the self and coupling inductance.

\*Address correspondence to: Shang-Wei Tu, ED413, Department of Electronics Engineering, National Chiao-Tung University, 1001 Ta-Hsueh Road, Hsinchu 300, Taiwan, Republic of China. Tel.: +886-3-5712121 #54226, Fax: +886-3-5710580. E-mail: kuma@athena. ee.nctu.edu.tw

Inductance extraction has been studied extensively in the literature. Grover [4] collected many formulas for extracting inductance. However, as mentioned in [5], there are limitations of applying the equations. For example, they do not consider internal inductance, and wire widths are not considered for mutual inductance. Also, Qi et al. [6] proposed some formulas for extracting bus structure's inductance with considering different effects such as skin effect and substrate effect. Greengard developed a multipole method to extract inductances [7]. Phillips, Kamon, and White [8] proposed an FFT-based approach for 3-D inductance extraction. Beattie and Pileggi proposed a hierarchical refinement method [9] that improves the running time for capturing the near field effects. Also, Beattie et al. [10] proposed equipotential shells methodology to efficiently extract the inductance of the bus structure. He et al. [5] presented a table-based approach to identify the structure of a circuit for inductance extraction.

Most of the previous works are field-solvers that are intrinsically more accurate but are computationally expensive. Others focus on modeling the inductances of special routing topologies such as the bus structure. Therefore, it is not suitable to incorporate them on-line into a layout tool for inductance optimization.

As [11] pointed out, no good approximation formula exists for coupling inductances of two parallel lines of unequal lengths and dimensions. We consider the overlapping of unequal wire lengths and dimensions (widths and heights) to extract the self and coupling inductance. We derive formulae and models to approximate both self and coupling inductance efficiently yet accurately for the coplanar routing structure. Simulation results show that the difference of the inductance values extracted from our models for practical cases is within 10% for the wires of unequal lengths and dimensions, compared with FastHenry [12]. In particular, our method is extremely fast. For example, the running time for extracting the coupling inductance of two wires of 2000  $\mu$ m by using our analytical formulas is typically within 0.11 seconds using Mathematica on a 566 MHz Cerelon PC with 128 MB RAM while FastHenry requires 141 seconds on SUN Sparc Ultra 60 with dual CPUs and 2GB memory. Therefore, it is feasible to incorporate our model into a layout tool on-line.

The rest of this paper is organized as follows. Section 2 describes the coplanar interconnect structure and some basic electromagnetic concepts. Section 3 derives formulae for self and coupling inductance. Section 4 gives the simulation results on the comparisons between our methods and FastHenry. Finally, Section 5 concludes our work.

## 2. Preliminaries

In this section, we describe some basic concepts of electromagnetism [13]. We first describe inductance in Subsection 2.1, and then introduce the coplanar structure used in this paper in Subsection 2.2.

## 2.1. Inductance

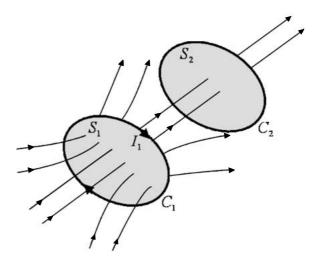

Considering two neighboring closed loops,  $C_1$  and  $C_2$  bounding surface  $S_1$  and  $S_2$ , respectively, as shown in Fig. 1. If a current  $I_1$  flows in  $C_1$ , a magnetic field  $\vec{B}_1$  will be created. Some of the magnetic flux due to  $\vec{B}_1$  will link with  $C_2$ —that is, it will pass through the surface  $S_2$  bounded by  $C_2$ . We refer to this mutual flux as  $\Phi_{12}$ . We have

$$\Phi_{12} = \int_{S_2} \vec{B}_1 \cdot d\vec{s}_2 \tag{1}$$

From Faraday's law of electromagnetic induction, we know that a time-varying  $I_1$  (and therefore a time-varying  $\Phi_{12}$ ) will produce an induced electromotive force or voltage in  $C_2$ . However,  $\Phi_{12}$  exists even if  $I_1$  is a steady d-c current. From Ampère's circuital law [13] (equation 2)

$$\oint_C \vec{B} \cdot d\vec{l} = \mu_0 I \tag{2}$$

we know that  $B_1$  is directly proportional to  $I_1$ ; hence  $\Phi_{12}$  is also proportional to  $I_1$ . We have

$$\Phi_{12} = L_{12}I_1 \tag{3}$$

where the proportionality constant  $L_{12}$  is called the mutual inductance or coupling inductance between loops  $C_1$  and  $C_2$ , with SI unit henry (H). In case  $C_2$  has  $N_2$  turns, the flux linkage  $\Lambda_{12}$  due to  $\Phi_{12}$  is

$$\Lambda_{12} = N_2 \Phi_{12} \tag{4}$$

Combining equations (3) and (4), we have

$$L_{12} = \frac{\Lambda_{12}}{I_1} \tag{5}$$

The coupling inductance between two circuits is then the magnetic flux linkage with the victim circuit ( $C_2$  in Fig. 1) per unit current in the aggressor circuit ( $C_1$  in Fig. 1).

Some of the magnetic flux produced by  $I_1$  links only with  $C_1$  itself, but not with  $C_2$ . The total flux linkage with  $C_1$  caused by  $I_1$  is

$$\Lambda_{11} = N_1 \Phi_{11} \tag{6}$$

Fig. 1. Two magnetically coupled loops.

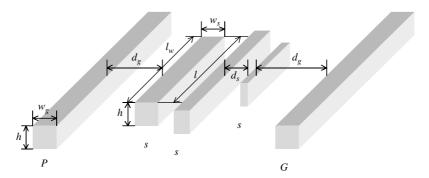

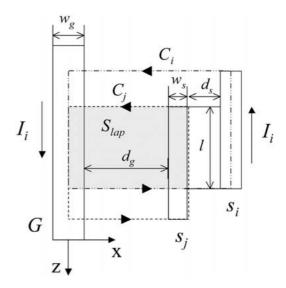

Fig. 2. Coplanar interconnect structure.

The self-inductance of loop  $C_1$  is defined as the magnetic flux linkage per unit current in the loop itself; that is

$$L_{11} = \frac{\Lambda_{11}}{I_1} \tag{7}$$

## 2.2. Coplanar Structure

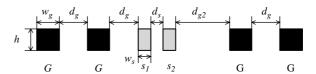

In this subsection, we introduce the coplanar interconnect structure and the notation which is intensively used in this paper. Figure 2 depicts the coplanar interconnect structure. Here, s stands for a signal wire while P and G stands for a power and a ground grid of identical width,  $w_{g}$ . Throughout this paper, both P and G are considered as ground wires. Assume that all wires are of the same height h, the width and length of each signal wire are  $w_s$  and  $l_w$  respectively, and the overlapping length of two signal wires is l. We use  $L_i$  to represent the selfinductance of  $s_i$  and  $L_{ij}$  for the coupling inductance between  $s_i$  and  $s_j$ . Throughout our paper, we assume quasi-static conditions, which imply that the currents vary very slowly in time and the dimensions of circuits are very small in comparison to the wavelength, and set the clock frequency to 3 GHz in our simulations.

Also, we assume that all signals use the nearest P/G wires as their return paths, same as [14]. Although quiet or opposite-switching neighboring nets may also serve as return paths, they are not ideal because currents returning from signal wires have to go through devices, which have significant resistances [14]. Therefore, the other wires that are not involved in the computation for the inductance between wires i and j are assumed floating. From Faraday's law, we know that a floating wire will not affect the inductance computation since it cannot form any current loop.

## 3. Inductance Modeling

In Subsection 3.1, we derive our formula *AMAS* (<u>Analytical Model Approximation of Self-inductance</u>) for extracting self-inductance in the coplanar structure. Subsection 3.2 <u>AMAC</u> (<u>Analytical Model Approximation of Coupling Inductance</u>) is derived for extracting coupling inductance in the coplanar structure. Finally, we re-derive two formulas, <u>IAMAC</u> (<u>Improved Analytical Model Approximation of Coupling Inductance</u>) and <u>IAMAS</u> (<u>Improved Analytical Model Approximation of Self-inductance</u>), to apply on some corner cases for extracting inductances.

## 3.1. Self-Inductance

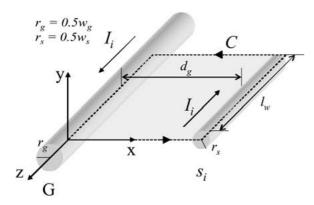

Because the rectangular shape of wires, as illustrated in Fig. 2, is complex for the computation of the magnetic flux density vector induced from it when carrying current, we apply cylindrical approximation for rectangular conductors. Figure 3 illustrates the approximation. If the current  $I_i$  flows in wire  $s_i$  and ground wire and its direction is shown as in Fig. 3, the current loop C can be determined by the dashed line. The area of  $S_i$ , the gray region shown in Fig. 3, is determined by the enclosed region of the loop C. To derive self-inductance from equation (7), we need to compute  $N_i$ ,  $S_i$ , and  $B_i$ , since  $\Lambda_i = N_i \Phi_i = N_i \int_{S_i} \vec{B}_i \cdot d\vec{s}_i$ . Although  $N_i = 1$  and  $S_i$ are already known,  $\vec{B}_i$  now is still unknown. Hence, we shall first derive the formula of the magnetic flux density vector  $B_i$ . Note that the unit of L' is henry per meter (H/m) and the unit of L is henry (H).

In the following discussion, we derive the magnetic flux density vector induced by a circular conductor which carrying current  $I_i$ . The cross-section view of

Fig. 3. Degeneration of metal wire from Fig. 2.

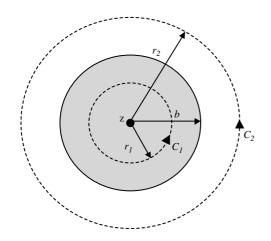

Fig. 4. Cross-section view of a circular conductor with radius b.

the circular conductor is shown in Fig. 4 where the radius of the conductor is b.

If we align the conductor along the z-axis in the cylindrical coordinate, current  $I_i$  flows in z-direction, which is outward direction of this paper. Assumed that current  $I_i$  is uniformly distributed in the conductor and the conductor is infinitely long  $(l_w \gg r, r)$  is the distance from the conductor's center to a certain point), we can derive equations (8) and (9) using equation (2).

$$\vec{B}_{in} = \hat{a}_{\phi} \frac{\mu_0 r_1 I_i}{2\pi b^2}, \quad r_1 \le b$$

(8)

$$\vec{B}_{out} = \hat{a}_{\phi} \frac{\mu_0 I_i}{2\pi r_2}, \quad r_2 \ge b$$

(9)

where  $\vec{B}_{in}$  is the magnetic flux density vector inside the conductor and  $\vec{B}_{out}$  is the vector outside the conductor.

As  $N_i$ ,  $S_i$ , and  $B_i$  are already known, we can then derive the formula of the internal inductance per unit

length, which is a part of the self-inductance, for a circular wire. Consider an annular ring in the inner conductor between radius r and r+dr ( $r \le b$ ). The current in a unit length of this annular ring is linked by the flux that can be obtained by integrating equation (8). We have

$$d\Phi'_{in} = \int_{r}^{b} B_{in} dr = \frac{\mu_0 I_i}{4\pi b^2} (b^2 - r^2)$$

(10)

The current in the annular ring, however, is only a fraction  $(2\pi r dr/\pi b^2 = 2r dr/b^2)$  of the total current  $I_i$ . As a result, the flux linkage for this annular ring is

$$d\Lambda'_{in} = \frac{2r\,dr}{b^2}d\Phi' \tag{11}$$

Hence, we can obtain the total flux linkage per unit length by integrating equation (11):

$$\Lambda'_{in} = \int_0^b d\Lambda'_{in} = \frac{\mu_0 I_i}{8\pi} \tag{12}$$

The unit length internal inductance of the circular wire is

$$L'_{in} = \frac{\Lambda'_{in}}{I_i} = \frac{\mu_0}{8\pi} \tag{13}$$

Then, the total internal self-inductance per unit length of the two wires system of Fig. 3 is

$$L'_{in} = 2 \times \frac{\mu_0}{8\pi} = \frac{\mu_0}{4\pi} \tag{14}$$

After computing the internal self-inductance, we derive the external self-inductance. Now, We change the coordinate to the Cartesian coordinate. In the xz-plane where the two wires lie, as in Fig. 3, the contributing  $\vec{B}$  vectors due to the equal and opposite currents in the two wires have only a y-component. Hence, from equation (9), we obtain

$$B_G = \frac{\mu_0 I_i}{2\pi x} \tag{15}$$

and

$$B_{s_i} = \frac{\mu_0 I_i}{2\pi (d_g + r_g + r_s - x)} \tag{16}$$

The flux linkage per unit length is

$$\Phi'_{ex} = \int_{r_g}^{r_g + d_g} (B_G + B_{s_i}) dx

= \frac{\mu_0 I_i}{2\pi} \ln \left( \frac{(r_g + d_g)(r_s + d_g)}{r_s r_g} \right)$$

(17)

Therefore, the unit length external inductance in Fig. 3 is

$$L'_{ex} = \frac{\Phi'_{ex}}{I_i} = \frac{\mu_0}{2\pi} \ln \left( \frac{(r_g + d_g)(r_s + d_g)}{r_s r_g} \right)$$

(18)

Finally, we can obtain the total self-inductance  $(L_i)$  in Fig. 3 by summing equations (14) and (18) and then multiplying with the signal wire length  $l_w$ .

$$L_{i} = l_{w} (L'_{in} + L'_{ex})$$

$$= l_{w} \left( \frac{\mu_{0}}{4\pi} + \frac{\mu_{0}}{2\pi} \ln \left( \frac{(r_{g} + d_{g})(r_{s} + d_{g})}{r_{s} r_{g}} \right) \right)$$

(19)

If another ground wire exists on the other side of the signal wire separated by the distance  $d_{g2}(d_{g2} \ge d_g)$ , the current flowing in the nearest G wire will decrease. We modify equations (14) and (15) to equations (20) and (21) with the branch current of  $0.5I_i$ , which is given from the *Kirchhoff's Current law* as follows:

$$L'_{in} = (1+0.5) \times \frac{\mu_0}{8\pi} \tag{20}$$

$$B_G = 0.5 \times \frac{\mu_0 I_i}{2\pi x} \tag{21}$$

Then, re-deriving equations (17) to (19), the new self-inductance formula for the case when there are two ground wires can be obtained as follows:

$$L_{i} = l_{w}(L'_{in} + L'_{ex})$$

$$= \frac{l_{w}\mu_{0}}{2\pi} \left( 0.375 + \ln\left(\frac{(r_{g} + d_{g})^{0.5}(r_{s} + d_{g})}{r_{s}r_{g}^{0.5}}\right) \right)$$

(22)

If there are n ground wires, we also simplify these cases to the two ground wires system. We named the above formula AMAS ( $\underline{A}$ nalytical  $\underline{M}$ odel  $\underline{A}$ pproximation of  $\underline{S}$ elf-inductance).

### 3.2. Coupling Inductance

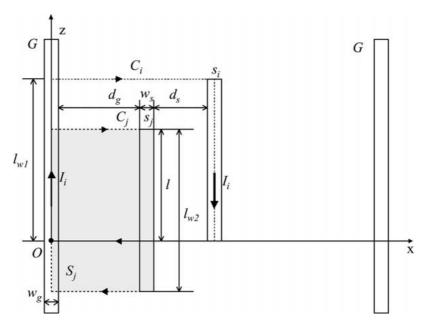

As in the previous subsection, we first consider single ground wire system. The top view of the coplanar structure is shown in Fig. 5. Now, we consider the xz-plane where the three wires lie, as shown in Fig. 5. The contributing  $\vec{B}$  vectors due to the current flowing in G and  $s_i$  wire have only a y-component. From equation (9), we have

$$B_G = \frac{\mu_0 I_i}{2\pi r} \tag{23}$$

Fig. 5. Top view of the coplanar structure.

and

$$B_{s_i} = \frac{\mu_0 I_i}{2\pi (0.5w_g + d_g + d_s + 1.5w_s - x)}$$

(24)

The coupling inductance  $L_{ij}$  is proportional to the overlapping area of  $S_i$  and  $S_j$ . The overlapping area  $S_{lap}$  is shown as the gray region in Fig. 5. We can derive the flux linkage per unit length from equation (4). We have

$$\Lambda'_{ex} = \Phi'_{ex} = \frac{1}{l} \int_{S_{lap}} B \, ds_{lap}

= \int_{0.5w_g}^{0.5w_g + d_g + w_s} (B_G + B_{s_i}) \, dx = \frac{\mu_0 I_i}{2\pi}

\times \ln\left(\frac{(0.5w_g + d_g + w_s)(d_g + d_s + 1.5w_s)}{0.5w_g(d_s + 0.5w_s)}\right)$$

(25)

Therefore, the external inductance is

$$L'_{ex} = \frac{\Lambda'_{ex}}{I_i} \tag{26}$$

and the internal inductance due to G wire is

$$L'_{in} = \frac{\mu_0}{8\pi} \tag{27}$$

Hence, the total coupling inductance of Fig. 5 is

$$L_{ij} = L_{ji} = l(L'_{in} + L'_{ex}) = \frac{l\mu_0}{2\pi} \times \left(\frac{1}{4} + \ln\left(\frac{(0.5w_g + d_g + w_s)(d_g + d_s + 1.5w_s)}{0.5w_g(d_s + 0.5w_s)}\right)\right)$$

(28)

If another ground wire exists on the other side of the signal wire with distance  $d_{g2}(d_{g2} \ge d_g + d_s + w_s)$ , the current flowing in the nearest G wire will decrease. As in the previous subsection, we modify equations (23) and (27) to equations (29) and (30) with the branch current of  $0.5I_i$ :

$$B_G = 0.5 \times \frac{\mu_0 I_i}{2\pi x} \tag{29}$$

$$L'_{in} = 0.5 \times \frac{\mu_0}{8\pi} \tag{30}$$

Re-deriving equations (25), (26), and (28), the new coupling inductance formula for the case when there are two ground wires can be obtained as follows:

$$L_{ij} = L_{ji} = l(L'_{in} + L'_{ex}) = \frac{l\mu_0}{2\pi}$$

$$\times \left(\frac{1}{8} + \ln\left(\frac{(0.5w_g + d_g + w_s)^{0.5}(d_g + d_s + 1.5w_s)}{(0.5w_g)^{0.5}(d_s + 0.5w_s)}\right)\right)$$

(31)

If there are n ground wires, we also simplify these cases to the two ground wires system as in Subsection 3.1. We named the above formula AMAC ( $\underline{A}$ nalytical  $\underline{M}$ odel  $\underline{A}$ pproximation of  $\underline{C}$ oupling Inductance).

## 3.3. Modeling Short Wires and Small Coupling

Previous subsections are all based on the assumption that wires are sufficiently long, namely,  $l_w \gg d_g$ . When wire lengths are comparable to wire spaces, however, equation (9) cannot be used to model the magnetic flux density, since we cannot find a closed path around the current-carrying wire such that the magnitude of B is constant over the path. Besides, if two signal wires have no overlapping length between them, does the coupling inductance exist? The answer is affirmative, although the coupling inductance is very small. Therefore, if we use the equations derived in Subsections 3.1 and 3.2 for all cases of the coplanar structure, our approximations will cause a large amount of errors in some corner cases. Based on the above fact, we should use more sophisticated formulas to approximate the inductances for the situations, when

- 1. The wire length is comparable to its distance to the nearest ground wire.

- The overlapping length is much smaller than the signal wire length.

Fig. 6. Top view of a carrying current wire.

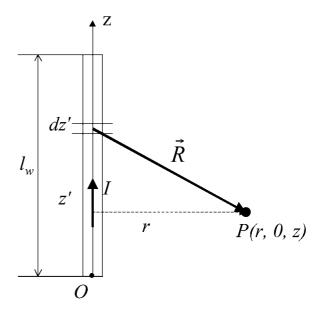

If above two situations are encountered, we should rederive the magnetic flux density vector induced from the wire before computing the inductance. In this subsection, we introduce the *Bioat-Savsrt law*, equation (32), to derive the formula of magnetic flux density vector.

$$\vec{B} = \oint_{C'} d\vec{B} = \frac{\mu_0 I}{4\pi} \oint_{C'} \frac{d\vec{l}' \times \vec{R}}{R^3}$$

(32)

where C' is the closed path of current I, and  $\vec{R}$  is the vector directed from the source to the field point. If we have a line segment carrying current I along the z-axis in the cylindrical coordinate shown in Fig. 6.

Therefore,

$$\vec{R} = \hat{a}_r r + \hat{a}_z (z - z') \tag{33}$$

and

$$d\vec{l}' \times \vec{R} = \hat{a}_z \, dz' \times (\hat{a}_r r + \hat{a}_z (z - z')) = \hat{a}_{\phi} r \, dz' \quad (34)$$

Using equations (32) and (34), we can obtain

$$\vec{B} = \hat{a}_{\phi} \frac{\mu_0 I}{4\pi} \int_0^{l_w} \frac{r \, dz'}{(r^2 + (z - z')^2)^{3/2}} \tag{35}$$

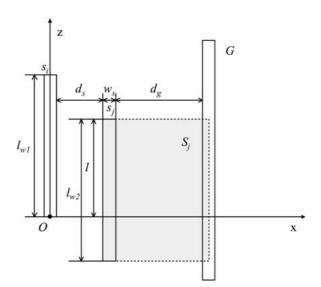

When the magnetic flux density vector is already known, we can then derive the formula of coupling inductance. Next, we consider the two ground wires system shown in Fig. 7.

Fig. 7. Top view of the coplanar structure.

The internal inductance is

$$L_{in} = 0.5 \times l \times \frac{\mu_0}{8\pi} \tag{36}$$

From equation (35), we know that the contributing  $\vec{B}$  vectors due to the equal and opposite currents in  $s_i$  and G wires have only a y-component in the Cartesian coordinate. Hence, the magnitude of the magnetic flux induced by the G wire of Fig. 7 is

$$B_G = 0.5 \frac{\mu_0 I}{4\pi} \int_0^{l_w} \frac{x \, dz'}{(x^2 + (z - z')^2)^{3/2}} \tag{37}$$

and the flux linkage due to the G wire is

$$\Lambda_G = \Phi_G = \int_{S_j} B_G \, ds_j$$

$$= \int_{0.5w_g}^{0.5w_g + d_g + w_s} \int_{l - l_w}^{l} B_G \, dz \, dx \qquad (38)$$

For the simplification of our formulation, we reverse the structure and align  $s_i$  with the *z*-axis as shown in Fig. 8.

Then the magnitude of the magnetic flux induced by the  $s_i$  wire in Fig. 8 is

$$B_{s_i} = \frac{\mu_0 I}{4\pi} \int_0^{l_w} \frac{x \, dz'}{(x^2 + (z - z')^2)^{3/2}} \tag{39}$$

The flux linkage due to  $s_i$  wire is

$$\Lambda_{s_i} = \Phi_{s_i} = \int_{S_j} B_{s_i} \, ds_j$$

$$= \int_{0.5w_g}^{0.5w_g + d_g + w_s} \int_{l - l_w}^{l} B_{s_i} \, dz \, dx \qquad (40)$$

Fig. 8. Reversed placement of Fig. 7.

Therefore, the total external inductance is

$$L_{ex} = \frac{\Lambda_{ex}}{I_i} = \frac{(\Lambda_G + \Lambda_{s_i})}{I_i}$$

(41)

Hence, summing up equations (36) and (41), we can compute the coupling inductance by

$$L_{ij} = L_{in} + L_{ex} = 0.5l \frac{\mu_0}{8\pi} + L_{ex}$$

(42)

For the simplification of our equation, we do not expand the term  $L_{ex}$ . We named the above formula IAMAC (Improved Analytical Model Approximation of Coupling Inductance).

Next, we derive the formula of the self-inductance for the situation when a signal wire length is comparable to its distance to the nearest ground wire. We consider the coplanar structure shown in Fig. 3 to derive the formula. The self-inductance also includes the internal and the external inductance. Therefore, in a two-ground wires system, the internal inductance is

$$L_{in} = (1 + 0.5) \times l_w \times \frac{\mu_0}{8\pi}$$

(43)

Assume the loop area is  $S_j$ . Since  $\Phi = \int_S \vec{B} \cdot d\vec{s}$ , we have

$$\Lambda_G = \Phi_G = \int_{S_j} B_G ds_j = \int_{0.5w_g}^{0.5w_g + d_g} \int_{l - l_w}^{l} B_G dz dx$$

(44)

and

$$\Lambda_{s_i} = \Phi_{s_i} = \int_{S_j} B_{s_i} ds_j = \int_{0.5w_s}^{0.5w_s + d_g} \int_{l - l_w}^{l} B_{s_i} dz dx$$

(45)

The formulae of  $B_G$  and  $B_{si}$  are the same as equations (37) and (39). Then we obtain the total self-inductance (by equations (41), (43), (44), and (45)) as follows

$$L_i = L_{in} + L_{ex} = 1.5l_w \frac{\mu_0}{8\pi} + L_{ex}$$

(46)

Again, we do not expand the term  $L_{ex}$  for simplicity. We named the above formula *IAMAS* (*Improved* <u>Analytical</u> <u>Model</u> <u>Approximation of</u> <u>Self-inductance</u>).

## 4. Experimental Results

We verify the accuracy of our formulae, *AMAS* (<u>Analytical Model Approximation of Self-inductance</u>), *AMAC* (<u>Analytical Model Approximation of Coupling</u>

Fig. 9. Cross-section view of the coplanar structure with multiple ground wires.

Inductance), *IAMAC* (*I*mproved <u>A</u>nalytical <u>M</u>odel <u>A</u>pproximation of <u>C</u>oupling Inductance), and *IAMAS* (*I*mproved <u>A</u>nalytical <u>M</u>odel <u>A</u>pproximation of <u>S</u>elf-inductance), by comparing with FastHenry. In Subsection 4.1, simulations of various ground wire structures are conducted to find the applicable structures for our formulae. Subsection 4.2 verifies the accuracy of our formulae by using different parameters. We show that our formulae are also suitable for the bus structure in Subsection 4.3.

#### 4.1. Ground Wire Structure

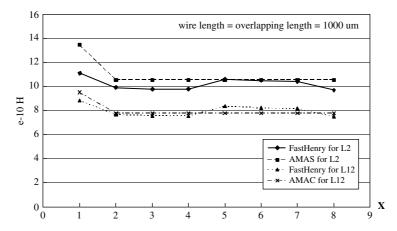

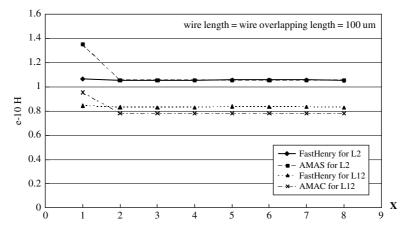

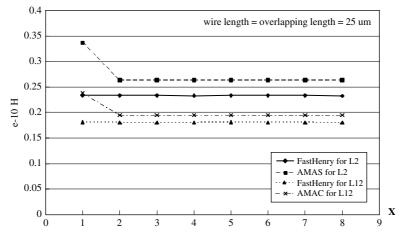

We discuss the effect of the number of ground wires on inductance in this subsection. Consider the crosssection view of the coplanar structure shown in Fig. 9 for the first simulation. We represent the structure by  $GGs_1s_2GG$ . In our simulation, we set  $h = 2 \mu m$ ,  $w_s = 0.8 \ \mu\text{m}, d_s = 0.8 \ \mu\text{m}, w_g = 2 \ \mu\text{m}, d_g = 12 \ \mu\text{m}.$ Also, we set  $d_{g2} = d_g + d_s + w_s = 18.4 \mu \text{m}$  to make  $s_2$ farther than  $s_1$  to a nearest ground wire. The length of the G wire was 4500  $\mu$ m, the lengths of both  $s_1$  and  $s_2$  were  $l_w = 1000 \mu \text{m}$ , and the overlapping lengths of  $s_1$  and  $s_2$  were  $l = 1000 \mu m$ . We simulated with the  $Gs_1s_2$ ,  $Gs_1s_2G$ ,  $Gs_1s_2GG$ ,  $Gs_1s_2GGG$ ,  $GGs_1s_2$ , GGGs<sub>1</sub>s<sub>2</sub>, GGGGs<sub>1</sub>s<sub>2</sub>, and GGs<sub>1</sub>s<sub>2</sub>GG structures and obtained the results shown in Figs. 10-12. From Figs. 10–12 we observe that our formulae are more suitable for the structures with two or more G wires since the results are closer to those obtained by FastHenry. This is a typical situation in a real design where there must be at least one ground and one power grids in a circuit.

# 4.2. Accuracy of AMAS, AMAC, IAMAS, and IAMAC

In this subsection, we conducted the following two simulations: (1) the accuracy of AMAS and IAMAS for

Fig. 10. Simulation results for different coplanar structures, where x = 1 stands for  $Gs_1s_2$ , x = 2 stands for  $Gs_1s_2G$ , x = 3 stands for  $Gs_1s_2GG$ , x = 4 stands for  $Gs_1s_2GG$ , x = 6 stands for  $GGs_1s_2$ , x = 7 stands for  $GGGs_1s_2$ , and x = 8 stands for  $GGs_1s_2GG$ .

Fig. 11. Simulation results for different coplanar structures, where x = 1 stands for  $Gs_1s_2$ , x = 2 stands for  $Gs_1s_2G$ , x = 3 stands for  $Gs_1s_2GG$ , x = 4 stands for  $Gs_1s_2GG$ , x = 5 stands for  $Gs_1s_2$ , x = 6 stands for  $GGGs_1s_2$ , x = 7 stands for  $GGGs_1s_2$ , and x = 8 stands for  $GGs_1s_2GG$ .

Fig. 12. Simulation results for different coplanar structures, where x = 1 stands for  $Gs_1s_2$ , x = 2 stands for  $Gs_1s_2G$ , x = 3 stands for  $Gs_1s_2GG$ , x = 4 stands for  $Gs_1s_2GG$ , x = 5 stands for  $GGs_1s_2$ , x = 6 stands for  $GGGs_1s_2$ , x = 7 stands for  $GGGs_1s_2$ , and x = 8 stands for  $GGs_1s_2GG$ .

### 74 Tu et al.

Table 1. Simulation results of our modelings, AMAS and IAMAS, and FastHenry for self-inductances. The lengths of ground wires are  $4,500~\mu m$ . We ran FastHenry on a SUN Ultra 60 model 1450 with dual CPUs and 2GB RAM and ran AMAS and IAMAS by using Mathematica Version 3.0 on a 566 MHz Cerelon PC with 128 MB RAM.

| Self-Inductance (Unit: 10 <sup>-10</sup> H) |           |            |         |            |           |         |            |           |

|---------------------------------------------|-----------|------------|---------|------------|-----------|---------|------------|-----------|

| $(l_w, d_g, w_s, w_g) (\mu m)$              | FastHenry | Time (sec) | AMAS    | Time (sec) | Error (%) | IAMAS   | Time (sec) | Error (%) |

| (2000, 12, 0.8, 2)                          | 18.70280  | 117.09     | 20.3658 | 0.11       | 8.892     | 20.3299 | 8.02       | 8.700     |

| (1500, 12, 0.8, 2)                          | 14.51540  | 120.80     | 15.2744 | 0.11       | 5.229     | 15.2385 | 6.97       | 4.982     |

| (1000, 12, 0.8, 2)                          | 9.99291   | 103.41     | 10.1829 | 0.11       | 1.901     | 10.1470 | 5.82       | 1.542     |

| (500, 12, 0.8, 2)                           | 5.14302   | 106.79     | 5.0915  | 0.11       | -1.003    | 5.0557  | 5.72       | -1.698    |

| (25, 12, 0.8, 2)                            | 0.22642   | 99.75      | 0.2546  | 0.05       | 12.436    | 0.2232  | 6.15       | -1.427    |

| (10, 12, 0.8, 2)                            | 0.07443   | 98.60      | 0.1018  | 0.06       | 36.806    | 0.0761  | 6.15       | 2.222     |

| (1000, 12, 0.8, 4)                          | 9.26282   | 111.57     | 9.3216  | 0.11       | 0.635     | 9.5280  | 5.66       | 2.863     |

| (1000, 12, 0.8, 1)                          | 10.59190  | 117.06     | 10.9551 | 0.11       | 3.429     | 10.8010 | 5.55       | 1.974     |

| (1000, 12, 1.6, 2)                          | 9.60097   | 110.11     | 8.8601  | 0.11       | -7.716    | 8.8243  | 5.71       | -8.090    |

| (1000, 12, 0.4, 2)                          | 10.24480  | 108.13     | 11.5367 | 0.11       | 12.610    | 11.5008 | 5.71       | 12.260    |

| (1000, 24, 0.8, 2)                          | 12.38490  | 99.46      | 12.1906 | 0.05       | -1.569    | 12.1191 | 5.71       | -2.146    |

| (1000, 6, 0.8, 2)                           | 7.73106   | 100.60     | 8.2411  | 0.05       | 6.597     | 8.2231  | 5.66       | 6.365     |

| Average (absolute value)                    |           | 107.78     |         | 0.09       | 8.235     |         | 6.07       | 4.522     |

Table 2. Simulation results of our modelings, AMAC and IAMAC, and FastHenry for coupling inductances. Here,  $w_s = d_s = 0.8~\mu m$  for both signal wires, both ground wire length = 4,500  $\mu m$ ,  $w_g = 2~\mu m$ ,  $d_g = 12~\mu m$ . We ran FastHenry on a SUN Ultra 60 model 1450 with dual CPUs and 2GB RAM and ran AMAC and IAMAC by using Mathematica Version 3.0 on a 566 MHz Cerelon PC with 128 MB RAM.

| Unit: $\mu$ m         |                       | Coupling Inductance (Unit: 10 <sup>-10</sup> H) |            |         |            |           |         |            |           |

|-----------------------|-----------------------|-------------------------------------------------|------------|---------|------------|-----------|---------|------------|-----------|

| Signal<br>Wire Length | Overlapping<br>Length | FastHenry                                       | Time (sec) | AMAC    | Time (sec) | Error (%) | IAMAC   | Time (sec) | Error (%) |

| 2000                  | 2000                  | 17.1868                                         | 141.67     | 17.3525 | 0.11       | 0.964     | 17.2998 | 6.10       | 0.657     |

|                       | 1500                  | 12.2176                                         | 141.98     | 13.0143 | 0.11       | 6.521     | 13.0140 | 15.82      | 6.518     |

| 1500                  | 1500                  | 13.4125                                         | 124.95     | 13.0143 | 0.11       | -2.969    | 12.9617 | 7.19       | -3.361    |

|                       | 1100                  | 9.4542                                          | 120.45     | 9.5439  | 0.10       | 0.949     | 9.5434  | 16.98      | 0.944     |

|                       | 750                   | 5.9326                                          | 125.98     | 6.5072  | 0.05       | 9.685     | 6.5071  | 4.94       | 9.683     |

| 1000                  | 1000                  | 9.2767                                          | 114.34     | 8.6762  | 0.06       | -6.473    | 8.6237  | 5.66       | -7.039    |

|                       | 750                   | 6.8253                                          | 116.70     | 6.5072  | 0.05       | -4.661    | 6.5064  | 15.70      | -4.672    |

|                       | 500                   | 4.3076                                          | 116.70     | 4.3381  | 0.05       | 0.709     | 4.3379  | 5.22       | 0.705     |

| 500                   | 500                   | 4.6593                                          | 110.60     | 4.3381  | 0.05       | -6.894    | 4.2858  | 5.55       | -8.016    |

|                       | 400                   | 3.7163                                          | 110.28     | 3.4705  | 0.05       | -6.614    | 3.4684  | 17.09      | -6.669    |

|                       | 200                   | 1.7031                                          | 110.00     | 1.7353  | 0.11       | 1.887     | 1.7352  | 9.12       | 1.884     |

| 100                   | 50                    | 0.4887                                          | 105.41     | 0.4338  | 0.11       | -11.237   | 0.4321  | 4.94       | -11.586   |

|                       | 25                    | 0.2422                                          | 106.55     | 0.2169  | 0.06       | -10.435   | 0.2191  | 11.70      | -9.523    |

|                       | 5                     | 0.0547                                          | 109.70     | 0.0434  | 0.05       | -20.706   | 0.0561  | 12.03      | 2.553     |

| Average (abso         | lute value)           |                                                 | 118.24     |         | 0.08       | 6.479     |         | 9.86       | 5.272     |

self-inductance extraction, and (2) accuracy of AMAC and IAMAC for coupling-inductance extraction. In the first simulation, we tested the accuracy of AMAS and IAMAS for self-inductance extraction in the  $Gs_1G$  structure with various  $l_w$ ,  $d_g$ ,  $w_s$ ,  $w_g$ . The parameters,  $d_{g2}$ ,  $d_g$ , h and the wire length of G wire, were identical

to the previous simulations of previous subsection. The simulation results are given in Table 1. Identical values of parameters and conditions are applied to the second simulation on the coupling inductance whose results are shown in Table 2. In Figs. 13 and 14, the inductance values obtained by our modeling and FastHenry are

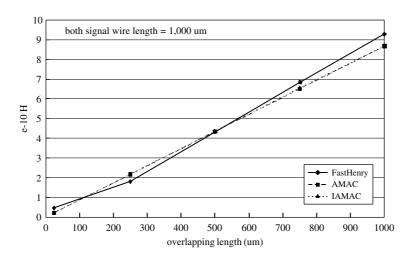

Fig. 13. Coupling inductance vs. signal wire overlapping length when both signal wire length =  $1,000 \, \mu \text{m}$ , and the other parameters are identical to simulations in the previous subsection.

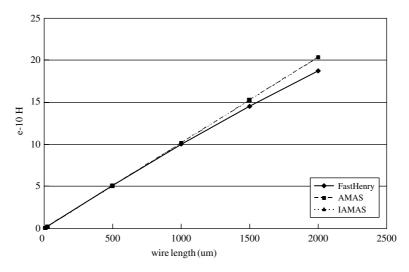

Fig. 14. Self-inductance vs. signal wire length when the other parameters are identical to simulations in the previous subsection.

plotted as functions of overlapping and wire lengths, respectively. The results show the accuracy of our work.

## 4.3. Experiments of Bus Structures

In this subsection, we simulate with the bus structure to show that our model is also suitable for the bus structure. In our simulation, the bus structure is 9-bit, all signal wire lengths are 2,000  $\mu$ m, and the other parameters are the same as in the previous subsection. Table 3 lists the results.

From Table 3, we can observe that the average difference between our simulation results and those obtained

*Table 3.* Self and mutual inductance estimated from FastHenry and our formulae for the bus structure ( $L_i$  stands the self-inductance of wire  $s_i$ ;  $L_{ij}$  stands the mutual inductance between wire  $s_i$  and  $s_j$ ).

| Inductance (10 <sup>-10</sup> H) |           |           |           |  |  |  |

|----------------------------------|-----------|-----------|-----------|--|--|--|

| Routing                          | FastHenry | AMAS&AMAC | Error (%) |  |  |  |

| $L_1$                            | 19.4186   | 20.3658   | 4.878     |  |  |  |

| $L_3$                            | 20.6165   | 21.7243   | 5.373     |  |  |  |

| $L_5$                            | 21.4648   | 22.8311   | 6.365     |  |  |  |

| $L_{13}$                         | 13.4016   | 12.6199   | -5.833    |  |  |  |

| $L_{15}$                         | 11.1896   | 10.3177   | -7.792    |  |  |  |

| $L_{35}$                         | 14.4393   | 13.7834   | -4.542    |  |  |  |

| Average erro                     | 5.797     |           |           |  |  |  |

76

by FastHenry for the self and coupling inductance is about 5.8%. Therefore, our formulae are also suitable for the bus structure.

#### 5. Conclusions

In this paper, we first introduced some basic electromagnetic concepts. Using these basic concepts, we derived analytical formulae to efficiently approximate the self and coupling inductance for wires of unequal lengths and dimensions. We first presented efficient formulae, *AMAS* and *AMAC*, for general cases. Then we derived more sophisticated formulae, *IAMAS* and *IAMAC*, for some corner cases to improve accuracy. By comparing with FastHenry, simulation results have shown the accuracy of our formulae. In particular, our modeling is extremely efficient, and thus can be incorporated into a layout tool for inductance optimization.

### Acknowledgment

This work was supported in part by the R.O.C. National Science Council under Grant NSC 90-2215-E-009-045.

## References

- Ismail, Y. I. and Friedman, E. G., "Effects of inductance on the propagation delay and repeater insertion in VLSI circuits." *IEEE Trans. Very Large Scale Integration (VLSI) Systems*, 8(2), April 2000.

- He, L. and Lepak, K. M., "Simultaneous shield insertion and net ordering for capacitive and inductive coupling minimization." *International Symposium on Physical Design*, pp. 55–60, 2000.

- Semiconductor Industry Association, International Technology Roadmap for Semiconductors, 1999.

- Grover, F. W., Inductance Calculations: Working Formulas and Tables. Dover Publications, New York, 1946.

- He, L., Chang, N., Lin, S. and Nakagawa, O. S., "An efficient inductance modeling for on-chip interconnects." *IEEE Custom Integrated Circuits Conference*, pp. 22.6.1–22.6.4, 1999.

- Qi, X., Kleveland, B., Yu, Z., Wong, S., Dutton, R. and Young, T., "On-chip inductance modeling of VLSI interconnects." *IEEE International Solid-State Circuits Conference*, pp. 172–173, 2000.

- Greengard, L., The Rapid Evaluation of Potential Fields in Particle Systems. The MIT Press, Cambridge, MA, 1987.

- Phillips, J. R., Kamon, M. and White, J., "An FFT-based approach to including non-deal ground planes in a fast 3-D inductance extraction program," in *Proceedings of the IEEE Custom Integrated Circuits Conference*, pp. 8.3.1–8.3.4, 1993.

- Beattie, M. W. and Pileggi, L. T., "Electromagnetic parasitic extraction via a multipole method with hierarchical refinement." *International Conference on Computer Added Design*, pp. 437– 444, 1999.

- Beattie, M. W., Krauter, B., Alatan, L. and Pileggi, L., "Equipotential shells for efficient inductance extraction." *IEEE Trans. Computer-Aided Design* 20(1), pp. 70–79, January 2001.

- 11. Cheng, C. K., Lillis, J., Lin, S. and Chang, N., *Interconnect Analysis and Synthesis*. John Wiley and Sons Inc, 2000.

- Kamon, M., Tsuk, M. J. and White, J. K., "FastHenry: a multipole-accelerated 3D inductance extraction program." *IEEE Trans. Computer-Aided Design*, pp. 1750–1758, September 1994.

- Cheng, D. K., Filed and Wave Electromagnetics, 2nd ed., Addison-Wesley, 1989.

- Zhong, G., Koh, C. K. and Roy, K., "A twisted-bundle layout structure for minimizing inductive coupling noise." *IEEE Inter*national Conference on Computer Aided Design, pp. 406–411, 2000

- Beattie, M. W. and Pileggi, L. T., "Inductance 101: modeling and extraction." *Design Automation Conference*, pp. 323–328, 2001

**Shang-Wei Tu** received the B.S. and M.S. degrees in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 1999 and 2001, respectively.

He is currently working toward the Ph.D. degree in the Department of Electronics Engineering, National Chiao Tung University, Hsinchu, Taiwan. His current research interests include circuit modeling and computer-aided design.

Wen Zen Shen received the Ph.D. degree in electronics engineering from National Chiao Tung University, Hsinchu, Taiwan, in 1982.

He was a professor in the Department of Electronics Engineering, National Chiao Tung University before he passed away in 2001. His research interests included VLSI design, low-power circuit design, computer-aided design, and VLSI for signal processing.

Yao-Wen Chang received the B.S. degree from National Taiwan University in 1988, and the M.S. and the Ph.D. degrees from the University of Texas at Austin in 1993 and 1996, respectively, all in computer science.

Currently, he is an associate professor in the Department of Electrical Engineering and the Graduate Institute of Electronics Engineering, National Taiwan University, Taiwan. He was with the VLSI design group of IBM T.J. Watson Research Center, Yorktown Heights, New York, in the summer of 1994. From 1996 to 2001, he was an associate professor in the Department of Computer and Information Science, National Chiao Tung University, Taiwan, where he received an inaugural all-university Excellent Teaching Award (ranked #1 in the Department) in 2000. His research interests lie in physical design automation,

architectures, and systems for VLSI and combinatorial optimization.

Dr. Chang received Best Paper Award at the 1995 IEEE International Conference on Computer Design (ICCD-95) for his work on FPGA routing. He is a member of IEEE, IEEE Circuits and Systems Society, ACM, and ACM/SIGDA.

**Tai-Chen Chen** received the B.S. and M.S. degrees in Computer and Information Science from National Chiao Tung University, Hsinchu, Taiwan, in 1999 and 2001, respectively.

He is currently working toward the Ph.D. degree in the Graduate Institute of Electronics Engineering, National Taiwan University. His current research interests include computer-aided design and interconnect optimization for deep submicron technology.

Mr. Chen received the Best M.S. Thesis Award from the National Science Council of Taiwan, ROC in 2002.

**Jing-Yang Jou** received the B.S. degree from the Department of Electrical Engineering at National Taiwan University, Taiwan, ROC, and the M.S. and Ph.D. degrees from the Department of Computer Science, University of Illinois at Urbana-Campaign, in 1979, 1983, and 1985, respectively.

He is currently a full professor and chairman of Electronics Engineering Department at National Chiao Tung University, Hsinchu, Taiwan, ROC. Before joining National Chiao Tung University, he was with GTE Laboratories and AT&T Bell Laboratories. His research interests include behavioral, logic and physical

synthesis, design verification, and CAD for low power. He has published more than 100 journal and conference papers.

Dr. Jou is a member of Tau Beta Pi and is the recipient of the distinguished paper award of the IEEE International Conference on Computer-Aided Design, 1990. He served as the Technical Program Chair of the Asia-Pacific Conference on Hardware Description Languages (APCHDL'97).