Hindawi Publishing Corporation Mathematical Problems in Engineering Volume 2013, Article ID 613025, 7 pages http://dx.doi.org/10.1155/2013/613025

### Research Article

# A Self-Adaptive Frequency Response Compensation Method for a TIADC System

#### Peng Ye, Huiqing Pan, Hao Zeng, Min Li, and Wuhuang Huang

School of Automation Engineering, University of Electronic Science and Technology of China, China

Correspondence should be addressed to Huiqing Pan; huiqing.pan@gmail.com

Received 4 January 2013; Accepted 25 March 2013

Academic Editor: Xing-Gang Yan

Copyright © 2013 Peng Ye et al. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Time interleaving is one of the most efficient techniques employed in high-speed sampling systems. However, the frequency response mismatch among different channels will create distortion tones that degrade the system performance. In this paper, a self-adaptive frequency response mismatch compensation method is presented, where the design of compensation filter is optimized with a self-adapting strategy. This digital postprocessing technique realizes the compensation of frequency response effectively and also the increase of the digital bandwidth of the acquisition system. MATLAB-based simulation and an actual two-channel acquisition system test verify the effectiveness of the algorithm.

#### 1. Introduction

High-speed digitizing of signals plays an important part in broadband communication and electronic measurement instruments, in particular, digital storage oscilloscopes (DSO). Increasing requirements are put forward for these systems. Because of the limits of existing electronic components and manufacturing technologies, the time-interleaved analog-to-digital converter (TIADC) parallel sampling technique is the most effective solution to high sampling rate and high sampling resolution needs.

Unfortunately, the performance of this TIADC system is degraded by following factors: (1) the mismatching of amplitude among various channels and (2) the different phase delay of sampling circuits. Generally, these mismatches are related to frequency and are also called frequency response mismatch. The frequency response mismatch will lead to additional spurious components in the spectrum and degrade the system's signal-to-noise ratio (SNR) [1, 2].

For data acquisition systems, as channel bandwidth becomes wider, both the acquisition bandwidth of the analog signals and the signal fidelity of the system increase. However, increasing the channel bandwidth is always difficult. The low integration due to manufacturing restrictions and the different input bandwidth of multiple electronic components easily lead to the deterioration of the system's bandwidth

[3]. On the other hand, the inconsistency of frequency response of each sampling channel in TIADC structure also exacerbates the unflatness of the system's frequency response, which results in the decrease in measurement bandwidth of the whole system.

To address this problem, many approaches are proposed. Among these approaches, digital postprocessing is the most popular technique, as analog matching techniques are either too imprecise or too expensive [4]. In [5], the channel of the TIADC system is fitted as a first-order RC circuit and it formulates the impact of bandwidth mismatching on SNR. Tsai, Satarzadeh et al. [6, 7] present corresponding calibration algorithms to such first-order modeled circuit. However, due to the diversity of the ADCs and other electronic components, the actual frequency response of acquisition channel is too complicated to be simply modeled as a first-order system. Based on WLS algorithm, Seo et al. [8] developed a bandwidth compensation filter. By employing LS algorithm Johansson and Löwenborg [9] suggested a technique for the filter design. However, whether in the WLS or LS, with the increase of test frequency points, the design of filter would be computationally burdensome, and the algorithm will become more complicated.

In this paper, we develop a digital postprocessing algorithm to compensate the frequency response in the TIADC system. Based on frequency domain sampling, an optimized

design technique is proposed by constructing the error function based on a self-adapting strategy. With the proposed algorithm, it is feasible to compensate frequency response and increase the bandwidth of the sampling system, and the fidelity of data acquisition system could also be ensured.

In the remainder of this paper, the frequency response mismatch is analyzed, and the compensation filter is presented in Section 2. The implementation details of the algorithm are given in Section 3. Several experiments using the proposed algorithm are reported in Section 4. Further discussions are summarized in Section 5.

## 2. Compensation of Frequency Response Mismatch

2.1. Frequency Response of Sampling System. Due to the limitation of front-end electronic elements, the sampling channel trends to be a low-pass filter. The passing capacity for different frequency components of the input signal is inconsistent; that is, the amplitude attenuation rate of high-frequency components is larger than that of low-frequency components. Meanwhile, the manufacturing processes also cause the inconsistent response of various parts of the acquisition channel, resulting in the unflatness of channel frequency response and the decrease of measurement bandwidth of the overall system. These bring the new challenge to the signal reconstruction of the TIADC system.

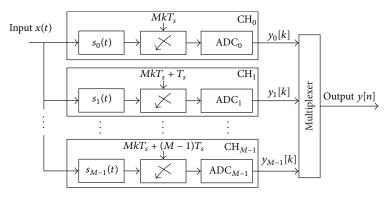

Figure 1 depicts a TIADC sampling system with M channels. It consists of M parallel ADCs, which is called "channel" and works at the same sampling rate of  $f_s/M$  driven by a master sampling clock. After reorganization, the M ADCs work equivalently as a single ADC operating at an M times higher sampling rate. The impulse response of signal conditioning components of each acquisition channel is defined as  $s_i(t)$ . Unfortunately, due to the mismatching of  $s_i(t)$ , the actual output of TIADC y[n] can be expressed as:

$$y[n] = \sum_{m=0}^{M-1} x(t) * s_m(t) \sum_{n=0}^{N-1} \delta(t - (nM + m)T_s)$$

$$= y_d[n] + e[n], \qquad (1)$$

where  $\delta(t)$  is the dirac delta function,  $T_s$  is the sampling period, and \* denotes the convolution operation.  $y_d[n]$  represents the desired output, and e[n] is an error term introduced by frequency response mismatch among channels.

e[n] is a frequency-associated error introduced by different responses to different frequency components of input signals through the acquisition channels. As the phase-frequency response may not change till very high sampling frequency, we only consider the amplitude-frequency response mismatch in this paper. If it is possible to estimate the error  $\widehat{e}[n]$  by certain construction function, the compensation of the frequency response mismatch can be realized.

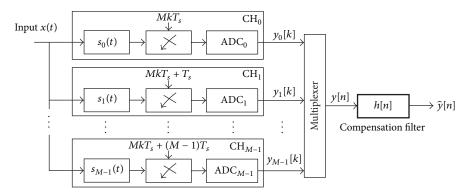

2.2. Frequency Response Compensation. In order to compensate the error e[n] introduced by the frequency response mismatch of each channel, a compensation filter h[n] may

be built for postprocessing the digital signals collected by the TIADC. The fundamental principle is described as below.

Equation (1) may be expressed as

$$y[n] = \sum_{n=0}^{N-1} \sum_{m=0}^{M-1} x (nMT_s + mT_s) * s (nMT_s + mT_s)$$

$$\cdot \delta (t - nMT_s - mT_s)$$

(2)

The Fourier transform of (1) can be written as

$$Y(\omega) = \frac{1}{MT_s} \sum_{k=-\infty}^{\infty} \sum_{m=0}^{M-1} S_m \left(\omega - k \frac{2\pi}{MT_s}\right) X\left(\omega - k \frac{2\pi}{MT_s}\right) \times e^{-jk(2\pi/M)m}.$$

(3)

If the frequency response of various channels is consistent, the ideal TIADC output frequency response will be

$$Y_d(\omega) = \frac{1}{MT_s} \sum_{k=-\infty}^{\infty} \sum_{m=0}^{M-1} X\left(\omega - k \frac{2\pi}{MT_s}\right) e^{-jk(2\pi/M)m}$$

(4)

Then it is possible to obtain the estimation of output's frequency response  $\widehat{Y}(\omega)$  from the TIADC system after the frequency response mismatch is calibrated by compensation filter h[n]:

$$\widehat{Y}(\omega) = H(\omega) Y(\omega) \approx Y_d(\omega),$$

(5)

where  $H(\omega)$  refers to the frequency response of compensation filter. Hence, it can be obtained according to (3), (4), and (5); it can be rewritten as

$$H(\omega) = \sum_{k=-\infty}^{\infty} \frac{1}{\sum_{m=0}^{M-1} S_m \left(\omega - k \left(2\pi/MT_s\right)\right)}.$$

(6)

The frequency response error e[n] may be compensated by constructing the calibration filter  $H(\omega)$ .

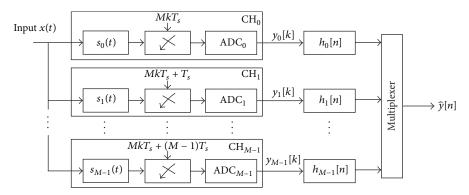

In the TIADC system, we could make full use of parallel features, and then signal processing could be decomposed to single channel, and Figure 2 can be converted into Figure 3.

Obviously, in order to design the compensation filter, in (6) the frequency response function  $S_m(\omega)$  of corresponding channel should be determined. We noted that the response of each channel is related to not only the parameters of the actual devices but also the attenuation of channel. Meanwhile, the design of the digital compensation filter is related to real-time sampling rate of the channel. For the acquisition systems which has different sampling rate  $f_s$ , the frequency response compensation filter needs to be redesigned. On the other hand, a different response mode will provide the system with different features. Therefore, a suitable reference response should be selected according to the testing requirements, such as the flat response, bessel response or gaussian response.

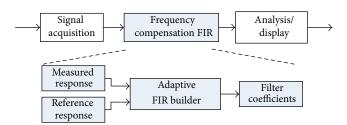

The fundamental principle that was used to construct the compensation system is shown in Figure 4. Based on frequency domain compensation techniques, the correction can be made to the amplitude frequency mismatch in the parallel acquisition system.

FIGURE 1: Block diagram of a typical parallel TIADC system.

FIGURE 2: Fundamental principle of frequency response mismatch compensation.

2.3. Design of Frequency Response Compensation Filter. We adopt the adaptive method to design the compensation filter. Considering the advantage of parallel structure in the TIADC acquisition system, we design the compensation algorithm by parallel computation.

We use the frequency response  $H_{md}(\omega)$  that meets the design objectives as the reference for the mth channel. The objective of the design is to minimize the mean square error (MSE) of the performance function

$$J = E\left\{e_m\left(\omega\right)e_m\left(\omega\right)^T\right\} = \frac{1}{N}\sum_{\omega}\left(H_m\left(\omega\right) - H_{md}\left(\omega\right)\right)^2, \quad (7)$$

where  $H_m(\omega)$  refers to the frequency response of the filter to be designed.

The  $H_{md}(\omega)$  can be calculated as

$$H_{md}(\omega) = \frac{H_{mr}(\omega)}{S_m(\omega)},$$

(8)

where  $H_{mr}(\omega)$  refers to the reference frequency response mode.

The minimax algorithm could be used for filter design that is, the design objective is achieved by the constrained conditions that the maximum mean squares error (MMSE) is minimal. Base on an iterative method, the filter that satisfies the minimize requirements of (7) could be obtained.

For reducing of multiplying operations in the filtering process, the symmetric or antisymmetric characteristic is

used as constraint for subfilters, that is, the implementation complex can be reduced approximately by a factor of two.

In summary, the design criteria of the frequency response compensation filter could be expressed as;

$$\Delta_{a} = \max_{\omega \in \omega_{p}} \left| \left| H_{m}(\omega) \right| - \left| H_{md}(\omega) \right| \right| \le \delta_{a}, \tag{9}$$

$$h_m(n) = \pm h_m(N - 1 - n),$$

(10)

where  $\delta_a$  refers to the amplitude error limits N refers to the length of each compensation filter. If both (9) and (10) are satisfied, the frequency response compensation filter may fulfill the compensation within the bandwidth  $\omega_p$ .

#### 3. Implementation

Considering the computational capacity of the existing computers, we adopt an optimization technique to design a compensation filter for each channel. The purpose is to minimize the design deviation under the condition to ensure the accuracy of channel frequency response correction with less resource consumption.

- (i) Step 1: obtain the frequency response of channels  $S_m(\omega)$ ,  $m=0,1,\ldots,M-1$  and select the reference frequency response mode  $H_{mr}(\omega)$ .

- (ii) Step 2: The optimal design of compensation filter, which meets the constraints of (9) and (10), could

FIGURE 3: Fundamental principle of frequency response error compensation.

FIGURE 4: Fundamental principle of frequency response compensation filter design.

be designed by combination with the frequency sampling filter design method and Parks-McClellan optimization algorithm [10, 11].

- (iii) Step 2(a): a proper filter should be firstly searched for as initial filter used for the iterative algorithm. As the amplitude-frequency response and the phase-frequency response have been known, the initial filter  $c_0(n)$  could be simply designed. The amplitude-frequency response of the filter within the given pass band  $|\omega| < \omega_p$  will be  $|H_{md}(\omega)|$  and within the stop band will be zero. And the phase response is linear a corroding to constraint (10). With  $N_0$  frequency response sampling data, it is very quick to obtain the initial filter coefficient  $c_0(n)$ ,  $n=0,\ldots,N_0-1$  by the frequency sampling design method and the IFFT transformation.

- (iv) Step 2(b): compute actual frequency response of initial filter  $c_0(n)$ . According to the Parks-McClellan optimization algorithm, if the actual frequency response of filter  $c_0(n)$  with order  $N_0$  does not satisfy the constraint condition (9) and (10), then the filter order  $N_1 = N_0 + 1$  will be updated. The minimax algorithm is used to design the new filter  $c_1(n)$  with order  $N_1$ , until the constrained conditions are satisfied. And then, the N-order filter is the frequency response compensation filter  $h_m(n)$  for the mth channel.

- (v) Step 3: repeat Steps 2(a) and 2(b), until the frequency response compensation filters  $h_m(n)$  for all channels

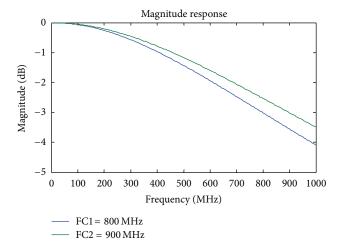

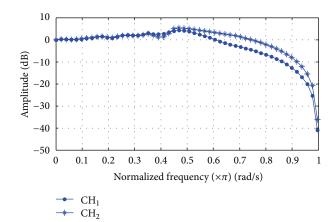

FIGURE 5: Frequency response of two channels.

(m = 0, 1, ..., M-1) are designed. Then, the design of frequency response compensation filter is completed.

In the design process, in order to utilize the filter design criteria simply, the pass band  $|\omega| < \omega_p$  is divided into I equivalent portions at equal spaces,  $\omega_i \in [0, \omega_p], i = 0, 1, \ldots, I - 1$ . Therefore, the constraint of (9) may be expressed as

$$\Delta_{a} = \max_{0 \le i \le l-1} \left| \left| H_{m} \left( \omega_{i} \right) \right| - \left| H_{md} \left( \omega_{i} \right) \right| \right| \le \delta_{a}. \tag{11}$$

#### 4. Experimental Results

In this section, we performed several simulations results to demonstrate the feasibility and effectiveness of the proposed algorithm.

Experiment (1). The feasibility of proposed calibration algorithm has been evaluated in a two-channel TIADC system with equivalent sampling rate at 1GSPS supported by two 8 Bit-500MSPS ADCs (Ideal\_8\_Bit.adc) [12]. Assume that a certain bandwidth mismatch exists among channels. Based

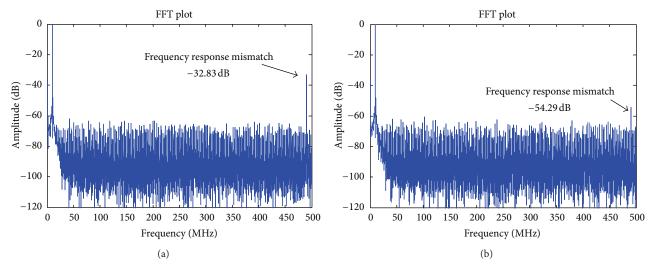

FIGURE 6: Frequency spectrum of 10 MHz sine wave captured by two-channel TIADC before and after compensation.

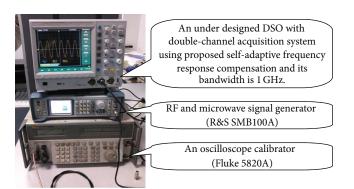

FIGURE 7: Under designed DSO (double-channel acquisition system) test platform.

on assumption, the frequency response of the *m*th channel can be defined as [4]

$$H_m(\omega) = \frac{1}{1 + j\omega\tau_m} \tag{12}$$

Equation (12) contains both magnitude and phase contributions, where  $\tau_m$  is the sampling time constant of mth channel, and  $\tau_1 = 0.8 f_s$ ,  $\tau_2 = 0.9 f_s$ . Figure 5 shows the frequency response of each channel in the TIADC system.

A sine wave with frequency  $f_0 = 10 \, \mathrm{MHz}$  is used as a test signal. The frequency spectra of the original output sequence before and after compensation are depicted in Figures 6(a) and 6(b), respectively.

The experimental results indicate that the error spectra caused by frequency response mismatches are with very weak power after compensation. Now the calculated value of SNR is approximately 41.95 dB leading to an improvement of 9.6 dB, the ENOB (effective number of bits) is increased by 6.67 Bit–5.09 Bit, and the SFDR (spurious free dynamic range) is enhanced from 32.83 dB to 54.29 dB. The additional spurious components in the spectrum have been reduced efficiently. The rest of the additional spurious components

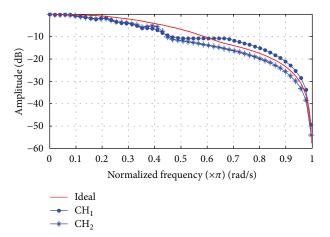

FIGURE 8: Amplitude-frequency response of actual double-channel DSO before compensation.

may be caused by phase-frequency response mismatch that is not calibrated in this paper. This performance of this TIADC system verifies the effectiveness of the proposed algorithm.

*Experiment* (2). The frequency response calibration is already used in an actual underdesigned digital storage oscilloscope (DSO) (shown in Figure 7). This system is a double-channel acquisition system with a whole sampling frequency of  $f_s = 6$  GSPS and designed bandwidth of  $f_c = 1$  GHz.

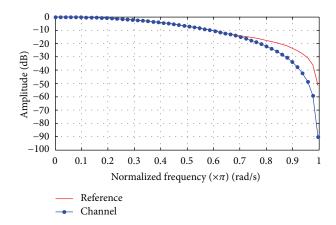

The amplitude-frequency response of each channel is characterized by a sinusoid sweeping test. Figure 8 shows the experimental result.

In Figure 8, the "Ideal" curve gives the reference amplitude-frequency response of the Gaussian response mode, curve with "." and curve with "\*" represent the amplitude-frequency response of two actual sampling channels respectively. Clearly, the gains of each channel with respect to different frequency components of input signals are changing, and it results in the unflatness of the actual frequency response.

FIGURE 9: Amplitude-frequency response of compensation filters.

FIGURE 10: Amplitude-frequency response of system after compensation.

Meanwhile, the insufficiency of designed bandwidth also degrades the actual system's performance.

According to the proposed design procedure, the amplitude-frequency response of compensation filters  $h_0(n)$  and  $h_1(n)$  are shown in Figure 9.

After applying the compensation, the amplitude-frequency response of the whole system is also evaluated using a sinusoid sweeping test, and the result is shown in Figure 10.

Obviously, it can be seen from Figure 10 that the bandwidth of the system after compensation is  $f_c = 1 \,\text{GHz}$  ( $\omega_c = 0.33\pi$ ), and, in the pass band, the flatness of the amplitude-frequency response also meets the requirements.

#### 5. Discussions and Conclusions

In the wideband TIADC acquisition system, the frequency response mismatch at the high-frequency part is not avoidable. The high fidelity of signals sampling could be ensured by employing the digital postprocessing technique. With the proposed algorithm, it is possible to improve the measurement bandwidth and compensate the frequency response mismatch. The algorithm is realized by an adaptive optimal filter that could meet the design requirements. By the digital

signal postprocessing technique, frequency response can be compensated online. And it breaks the limitation of the analog calibration and improves the system's measurement bandwidth so as to satisfy the testing requirements of wideband signals.

In this paper, we only consider the amplitude-frequency response mismatch of the TIADC system. As the phase-frequency response will change at a higher sampling frequency, our future work may focus on both amplitude-frequency response and phase-frequency response mismatches for high sampling system.

#### Acknowledgments

This work was supported by the Fundamental Research Funds for the Central University of China (A03007023801217) and (A03008023801080) and the Specialized Research Fund for the Doctoral Program of Higher Education of China (Grant no. 20120185130002).

#### References

- [1] A. Petraglia and S. K. Mitra, "Analysis of mismatch effects among A/D converters in a time-interleaved waveform digitizer," *IEEE Transactions on Instrumentation and Measurement*, vol. 40, no. 5, pp. 831–835, 1991.

- [2] H. Q. Pan and S. L. Tian, "An adaptive synthesis calibration method for time interleaved sampling systems," *Metrology and Measurement Systems*, vol. 17, no. 3, pp. 1–10, 2010.

- [3] N. Kurosawa, H. Kobayashi, K. Maruyama, H. Sugawara, and K. Kobayashi, "Explicit analysis of channel mismatch effects in time-interleaved ADC systems," *IEEE Transactions on Circuits and Systems I*, vol. 48, no. 3, pp. 261–271, 2001.

- [4] H. Li, The Effect of Oscilloscope's Response to Signal Acquisition Fidelity, LeCroy Corporation, 2009.

- [5] S. W. Sin, U. F. Chio, U. Seng-Pan, and R. P. Martins, "Statistical spectra and distortion analysis of time-interleaved sampling bandwidth mismatch," *IEEE Transactions on Circuits and Sys*tems II, vol. 55, no. 7, pp. 648–652, 2008.

- [6] T. H. Tsai, P. J. Hurst, and S. H. Lewis, "Bandwidth mismatch and its correction in time-interleaved analog-to-digital converters," *IEEE Transactions on Circuits and Systems II*, vol. 53, no. 10, pp. 1133–1137, 2006.

- [7] P. Satarzadeh, B. C. Levy, and P. J. Hurst, "Bandwidth mismatch correction for a two-channel time-interleaved A/D converter," in *Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS' 07)*, pp. 1705–1708, May 2007.

- [8] M. Seo, M. J. W. Rodwell, and U. Madhow, "Comprehensive digital correction of mismatch errors for a 400-Msamples/s 80dB SFDR time-interleaved analog-to-digital converter," *IEEE Transactions on Microwave Theory and Techniques*, vol. 53, no. 3, pp. 1072–1082, 2005.

- [9] H. Johansson and P. Löwenborg, "A least-squares filter design technique for the compensation of frequency response mismatch errors in time-interleaved A/D converters," *IEEE Trans*actions on Circuits and Systems II, vol. 55, no. 11, pp. 1154–1158, 2008

- [10] T. W. Parks and C. S. Burrus, *Digital Filter Design*, John Wiley & Sons, New York, NY, USA, 1987.

- [11] L. R. Rabiner, J. H. McClellan, and T. W. Parks, "FIR digital filter design techniques using weighted Chebyshev approximation," *Proceedings of the IEEE*, vol. 63, no. 4, pp. 595–610, 1975.

- [12] 2008, http://www.analog.com/en/converters-tools/adc-tools/topic.html#high-speed-ADC/.

Submit your manuscripts at http://www.hindawi.com

Journal of **Discrete Mathematics**