# A Model for Hot-Carrier Degradation in nLDMOS Transistors Based on the Exact Solution of the Boltzmann Transport Equation Versus the Drift-Diffusion Scheme

Prateek Sharma\*, Stanislav Tyaginov\*,†, Yannick Wimmer\*, Florian Rudolf\*,

Hubert Enichlmair\*, Jong-Mun Park\*, Hajdin Ceric\*, and Tibor Grasser\*

\*Christian Doppler Laboratory at the \*Institute for Microelectronics, Technische Universität Wien, 1040 Vienna, Austria

†Ioffe Physical-Technical Institute, 194021 St. Petersburg, Russia

\*ams AG, Unterpremstätten, Austria

Email:sharma@iue.tuwien.ac.at

Abstract—We present two schemes for carrier transport treatment to be used with our hot-carrier degradation (HCD) model. The first version relies on an exact solution of the Boltzmann transport equation (BTE) by means of the spherical harmonics expansion (SHE) method, whereas the second one uses a simplified drift-diffusion (DD) scheme to avoid the computationally expensive SHE approach. We use both versions of the model to simulate the change of the characteristics of an nLDMOS transistor subjected to hot-carrier stress and compare these theoretical degradation traces with the experimental ones. The similarity in the results of the SHE- and DD-based models together with the flexibility of the latter approach makes it attractive for fast and predictive HCD simulations for LDMOS devices.

Index Terms—hot-carrier degradation, nLDMOS, spherical harmonics expansion, drift-diffusion scheme

#### I. INTRODUCTION

Physics-based modeling of hot-carrier degradation (HCD) requires proper treatment of carrier transport [1]-[4]. This is because only the information about the carrier energy distribution function (DF) allows a proper description of the competing mechanism of Si-H bond dissociation. In fact, the single-carrier process is related to hot carriers and colder carriers contribute to the multiple-carrier mechanism. A criterion to distinguish between these hot and cold carriers can be based on the carrier DF. The correct way to obtain the DF is via the solution of the Boltzmann transport equation, which is computationally very expensive. As a result, some HCD models try to avoid this solution and substitute the information about the DF by some empirical factors which are connected to device characteristics such as the drain current [2], [5], [6]. In this context, an attractive technique would be to use simplified approaches to the Boltzmann transport equation solution such as the drift-diffusion (DD) or the energy transport schemes [7]. As we have shown, these schemes are not applicable to model HCD in planar CMOS nMOSFETs with short gate lengths [7]. However, they can be useful for the case of LDMOS transistors which typically have quite long channel and drift regions and are operated at high voltages. At the same time,

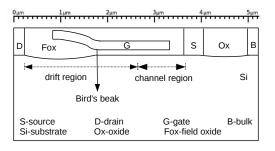

Fig. 1: The schematic representation of the nLDMOS transistor with all the characteristic sections labeled.

a proper treatment of carrier transport in LDMOS devices is challenging due to the large device dimensions, high operating voltages and such architectural peculiarities as the bird's beak and the non-planar interface, see Fig. 1. Furthermore, we have shown recently [8] that both the single- and multiplecarrier mechanisms of bond dissociation provide substantial contributions to HCD. Contrary to the commonly accepted idea, the multiple-carrier bond-breakage process appears to be a crucial component for HCD in nMOSFETs with gate lengths as long as  $2 \mu m$  and stressed at high voltages [2], [9], [10]. Thus, both components need to be considered for a comprehensive model. We apply our physics-based HCD model which uses the spherical harmonics expansion (SHE) approach to the solution of the Boltzmann transport equation for the case of nLDMOS transistors and then derive and verify a DD-based version of the model.

### II. EXPERIMENT

nLDMOS transistors (schematically represented in Fig. 1) fabricated by a  $0.35\,\mu\mathrm{m}$  process were subjected to hot-carrier stress at different combinations of gate and drain voltages  $V_{\mathrm{gs}}$  and  $V_{\mathrm{ds}}$ . The  $\mathrm{Si/SiO_2}$  interface length is  $\sim 3.4\,\mu\mathrm{m}$ , while the gate length is  $\sim 2.5\,\mu\mathrm{m}$ . To assess HCD, the normalized changes in the linear drain current  $\Delta I_{\mathrm{d,lin}}$  (measured at  $V_{\mathrm{ds}}$

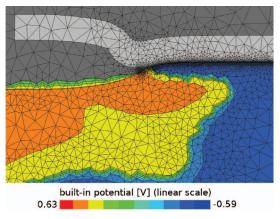

Fig. 2: The adaptive mesh used for the simulation of the nLDMOS. The density of the mesh is modulated depending on variations of the builtin potential.

=  $0.1 \,\mathrm{V}$  and  $V_{\mathrm{gs}} = 3.6 \,\mathrm{V}$ ) and in the saturation drain current  $\Delta I_{\rm d,sat}$  (at  $V_{\rm ds}$  = 1.0 V and  $V_{\rm gs}$  = 3.6 V) were recorded as a function of stress time. These relative drifts in the currents at any time t are defined as:

$$\Delta I_{\rm d,sat/lin}(t) = \frac{I_{\rm d,sat/lin}(t) - I_{\rm d,sat/lin}(0)}{I_{\rm d,sat/lin}(0)}$$

(1)

The threshold voltage shifts ( $\Delta V_{\rm th}$ ) were also recorded for all stress conditions.

#### III. MODEL DETAILS

Our HCD model incorporates three main sub-tasks: a carrier transport description, simulations of the defect generation rates, and simulation of the degraded devices [4], [11], [12]. We generated the device structure using the Sentaurus Process simulator [13], while MINIMOS-NT [14] was used for device simulations. The device and process simulators were calibrated in a coupled manner so that the characteristics of the fresh device are reproduced. We used the ViennaMesh framework [15] to generate an adaptive mesh based on the built-in potential, see Fig. 2. Such a mesh is very fine in important

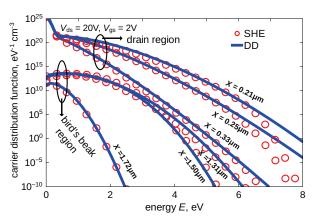

Fig. 3: Comparison of DFs from the DD-based model with those obtained from ViennaSHE for stress voltages  $V_{\rm ds}$  = 20 V and  $V_{\rm gs}$  = 2 V, calculated for different positions near the drain and bird's beak region.

regions of the device like the Si/SiO<sub>2</sub> interface and the bird's beak, while coarser in other regions as for instance in the Si bulk. This kind of meshing scheme allows efficient simulations as the number of variables are reduced while the important characteristics of the device are still captured.

## A. Carrier Transport

The SHE-based version of our model uses the full solution of the Boltzmann transport equation. It uses the simulator ViennaSHE [16] which considers such important scattering mechanisms as impact ionization, scattering at ionized impurities and surfaces as well as electron-electron and electronphonon interactions. The second and more compact version of our HCD model is based on the DD-scheme. In the latter version the electric field profile F(x), carrier mobility  $\mu(x)$ , and carrier concentration n(x) are obtained from the DD simulations. Then the carrier temperature is estimated as

$$T_n = T_{\rm L} + \frac{2}{3} \frac{q}{k_{\rm B}} \tau \mu F^2 \tag{2}$$

where q is the carrier charge,  $T_{\rm L}$  the lattice temperature, au the energy relaxation time, and  $k_{\rm B}$  the Boltzmann constant [17]. The DF is then approximated as [18]

$$f(\varepsilon) = A \exp\left[-\left(\frac{\varepsilon}{\varepsilon_{\text{ref}}}\right)^b\right] + C \exp\left[-\frac{\varepsilon}{k_{\text{B}}T_{\text{L}}}\right]$$

(3)

This expression for the DF considers the contribution of both the hot and the cold carriers. The parameters A, C, and  $\varepsilon_{ref}$ are found using the carrier concentration, carrier temperature obtained from (2) and DF normalization, see (4)-(6), while the parameter b is assigned a constant value of 1 near the drain and source regions and 2 otherwise.

$$\int_{0}^{\infty} f(\varepsilon)g(\varepsilon)d\varepsilon = n$$

$$\int_{0}^{\infty} \varepsilon f(\varepsilon)g(\varepsilon)d\varepsilon = \frac{3}{2}nk_{\rm B}T_{n}$$

(5)

$$\int_{0}^{\infty} \varepsilon f(\varepsilon)g(\varepsilon)d\varepsilon = \frac{3}{2}nk_{\rm B}T_n \tag{5}$$

$$\int_{0}^{\infty} f(\varepsilon)d\varepsilon = 1 \tag{6}$$

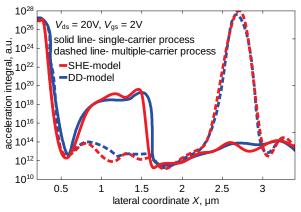

Fig. 4: The acceleration integral calculated using the DFs obtained from the DD-based model and ViennaSHE for  $V_{\rm ds}$  = 20 V and  $V_{\rm gs}$  = 2 V for the single-and multiple-carrier processes.

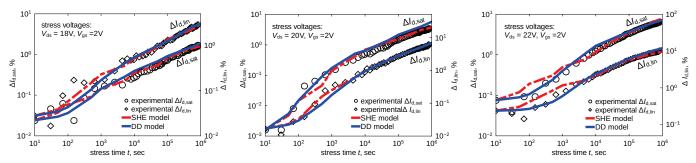

Fig. 5: Comparison of the change in the saturation and linear drain currents obtained from experiments and simulations, using the SHE- and DD-based models, for stress voltages  $V_{\rm gs}$  = 2 V and  $V_{\rm ds}$  = 18, 20, and 22 V using stress times up to 1Ms.

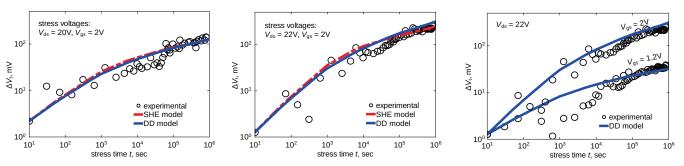

Fig. 6: Comparison of the change in the threshold voltage obtained from experiments and simulations, Fig. 7: The threshold voltage shift vs. stress time: using the SHE- and DD-based models, for stress voltages  $V_{\rm gs} = 2 \, {\rm V}$  and  $V_{\rm ds} = 20$  and 22 V for stress

a comparison between experiment and simulations with the DD-based model for a fixed drain voltage  $V_{\rm ds}$  = 22 V and two different gate voltages  $V_{\rm gs}$  = 1.2 and 2 V.

ViennaMesh proves to be beneficial even for the simplified DD approach which can become computationally challenging for nLDMOS devices.

# B. Modeling of Defect Generation

Our HCD model considers such important aspects of HCD as the consistent consideration of single- and multiple-carrier mechanisms of Si-H bond-breakage, the reduction of the bond rupture activation energy due to the interaction of the dipole moment of the bond with the electric field, and statistical fluctuations of this energy. The carrier DF is used to calculate the carrier acceleration integral which determines the rates of both single- and multiple-carrier processes of Si-H bondbreakage:

$$I = \int_{0}^{\infty} f(\varepsilon)g(\varepsilon)v(\varepsilon)\sigma(\varepsilon)d\varepsilon \tag{7}$$

with  $g(\varepsilon)$  being the density of states,  $v(\varepsilon)$  the carrier group velocity, and  $\sigma(\varepsilon)$  the reaction cross section [4], [11], [12]. Note that we consider all the superpositions of the singleand multiple-carrier bond-breakage processes. This means that first the bond can be excited to an intermediate state by the multiple-carrier process and then be dissociated by a solitary hot electron which induces a single-carrier process.

# C. Simulation of the Degraded Device

The bond-breakage rates allow evaluation of the density of interface states  $N_{it}(x)$  for arbitrary stress times as

$$N_{\rm it} = \frac{\sqrt{\Re_{\rm a}^2/4 + N_0 \Re_{\rm a} \Re_{\rm p}}}{\Re_{\rm p}} \frac{1 - f(t)}{1 + f(t)} - \frac{\Re_{\rm a}}{2\Re_{\rm p}},$$

$$f(t) = \frac{\sqrt{\Re_{\rm a}^2/4 + N_0 \Re_{\rm a} \Re_{\rm p}} - \Re_{\rm a}/2}{\sqrt{\Re_{\rm a}^2/4 + N_0 \Re_{\rm a} \Re_{\rm p}} + \Re_{\rm a}/2} \times \exp\left(-2t\sqrt{\Re_{\rm a}^2/4 + N_0 \Re_{\rm a} \Re_{\rm p}}\right),$$

(8)

where  $N_0$  is the density of Si-H bonds present in the fresh device, while  $\Re_p$  and  $\Re_a$  are cumulative passivation/depassivation rates [11]. The  $N_{\rm it}(x)$  profiles are then used as input data for the device simulator which evaluates the device characteristics vs. stress time.

### IV. RESULTS AND DISCUSSION

Fig. 3 shows a family of DFs simulated with ViennaSHE and with the DD-based model for different positions (X) at the interface, i.e. close to the bird's beak and to the drain. One can see in Fig. 3, that the agreement between the nonequilibrium DFs obtained with the SHE and DD methods is also quite good, especially near the bird's beak. This agreement deteriorates for the drain DFs at energies higher than ~6 eV, but the DF values at these high energies have already dropped by more than 20 orders of magnitude. To check whether this discrepancy affects the HCD model, we plot also the carrier acceleration integral for both single-

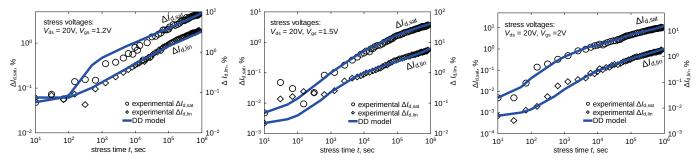

Fig. 8: The change in the saturation and linear drain currents: experiment vs. the DD-based model. Results are obtained for a fixed drain voltage  $V_{\rm ds} = 20\,{\rm V}$  and three different gate voltages  $V_{\rm gs} = 1.2, 1.5,$  and  $2\,{\rm V}.$

and multiple-carrier processes. From Fig. 4 one can see that the acceleration integral profiles obtained with the full and simplified versions of the model are almost identical. Fig. 4 also proves our assertion that the multiple-carrier process plays an important role in large devices and should be considered for thorough modeling. This idea is in good agreement with our previous findings [9], [10] as well as with the results published recently by the Bravaix group [2].

Fig. 5 summarizes the experimental change of the linear and saturation drain currents plotted as a function of stress time for a fixed  $V_{\rm gs} = 2.0 \,\rm V$  and varying  $V_{\rm ds} = 18$ , 20 and 22 V. In addition, the simulated data obtained with the SHE- and DDbased versions of our model are shown for comparison. One can see that agreement between experimental and theoretical  $\Delta I_{\rm d,lin}(t)$  and  $\Delta I_{\rm d,sat}(t)$  degradation traces is very good for both versions of the model. The  $\Delta I_{\rm d.lin}(t)$  and  $\Delta I_{\rm d.sat}(t)$ curves from both our approaches are almost the same within the whole experimental window. The threshold voltage shift  $\Delta V_{\rm t}$  is plotted as a function of stress time for  $V_{\rm gs} = 2\,{\rm V}$  and two different  $V_{\rm ds}$  = 20 and 22 V in Fig. 6. Regarding  $\Delta V_{\rm t}$ , the DD-based version of the model leads to similar results as those obtained with the exact solution of the Boltzmann transport equation. This makes the drift-diffusion scheme very attractive for predictive HCD modeling in LDMOS transistors.

To finally prove the predictive capabilities of our model, we have also plotted the simulated and experimental change of the threshold voltage for  $V_{\rm ds}=22\,\rm V$  and two different  $V_{\rm gs}=1.2$  and  $2\,\rm V$  (Fig. 7) as well as the degradation of the linear and saturation drain currents (also experiment vs. theory) for a fixed  $V_{\rm ds}=20$  and three different  $V_{\rm gs}=1.2$ , 1.5, and 2.0 V, Fig. 8. In all cases the agreement between experiment and theory is very good. We finally remark that all simulations were of course performed with the same parameter set.

# V. CONCLUSIONS

We have presented and verified a physics-based model for hot-carrier degradation in nLDMOS transistors which is based on the evaluation of the carrier energy distribution function. The more computationally expensive variant of the model uses the exact solution of the Boltzmann transport equation, while the simplified version employs the driftdiffusion scheme. Although the first approach is more accurate, the DD-based model can represent the carrier DFs and the acceleration integral with very good accuracy. Both versions were shown to capture the change in the linear and saturation drain currents and the threshold voltage shift in nLDMOS transistors subjected to hot-carrier stress for a wide range of gate and drain voltages. We also represented  $\Delta I_{\rm d,lin}(t),$   $\Delta I_{\rm d,sat}(t),$  and  $\Delta V_{\rm t}(t)$  for different stress conditions with the DD-based version exclusively. The good agreement between experiments and our hot-carrier degradation model which uses the drift-diffusion scheme allows us to conclude that this scheme is suitable for predictive HCD simulations in nLDMOS transistors.

#### ACKNOWLEDGMENTS

The authors acknowledge support by the Austrian Science Fund (FWF), grant P23598, by the European Union FP7 project ATHENIS\_3D (grant No 619246) and by the European Research Council (ERC) project MOSILSPIN (grant No 247056).

# REFERENCES

- [1] K. Hess et al., Physica E 3, 1 (1998).

- [2] Y. Randriamihaja et al., Microel. Reliab. 52, 2513 (2012).

- [3] S. Reggiani et al., Solid-State Electronics 102, 25 (2014).

- [4] M. Bina et al., IEEE Trans. Electron Dev. 61, 3103 (2014).

- [5] S. Rauch et al., Proc. International Reliability Physics Symposium (IRPS) (2005).

- [6] C. Guerin et al., IEEE Trans. Dev. Material. Reliab. 7, 225 (2007).

- [7] S. Tyaginov et al., Proc. European Solid-State Device Research Conference (ESSDERC) (2011), pp. 151–154.

- [8] Y. Wimmer et al., Proc. International Integrated Reliability Workshop (IIRW), in press, 2014.

- [9] S. Tyaginov et al., Microelectronics Reliability 50, 1267 (2010).

- [10] S. Tyaginov et al., Proc. International Conference on Simulation of Semiconductor Processes and Devices (SISPAD) (2011), pp. 123–126.

- [11] S. Tyaginov et al., Proc. International Reliability Physics Symposium (IRPS), 2014.

- [12] S. Tyaginov et al., Proc. Simulation of Semiconductor Processes and Devices (SISPAD) (2014), pp. 89–92.

- [13] Synopsis, Sentaurus Process, Advanced Simulator for Process Technolo-

- [14] MiniMOS-NT Device and Circuit Simulator, Institute for Microelectronic, TU Wien.

- [15] http://viennamesh.sourceforge.net/, 2014.

- [16] http://viennashe.sourceforge.net/, 2014.

- [17] T. Grasser et al., Proceedings of the IEEE (2003), pp. 251-274.

- [18] T. Grasser et al., Journ. Appl. Phys. 91, 3869 (2002).