## Assembly and Cleaning of CSPs for High, Low, and UltraLow Volume Applications

R. Ghaffarian , A. Mehta, J.K. Bonner

Jet Propulsion Laboratory, California Institute of

Technology , Pasadena, CA

Reza.Ghaffrian@JPL.NASA.Gov, (818) 354-2059

C. Achong, O. Vogler, D. Phillips, A. Chen

Celestica, Toronto, Canada

M. Mehrotra, M.Siméus, S. Stegura

Raytheon Systems Company, Tucson, AZ

## **ABSTRACT**

A JPL-led CSP Consortium of enterprises, composed of representing government agencies and private companies, recently joined together to pool in-kind resources for developing the quality and reliability of chip scale packages (CSPs) for a variety of projects. Since last year, more than 150 test vehicles, single- and double-sided multilayer PWBs, have been assembled and are presently being subjected to various environmental tests. Recent reliability data, specifically the impact of assembly underfill on reliability, is being presented in another paper in this conference. This paper presents lessons learned on assemblies at three facilities with high, low, and ultralow volume production.

Keywords: electronic assembly, SMT (surface mount technology), CSP (chip scale package), solder volume, fine pitch, solder print, solder joint.

## **INTRODUCTION**

In recent years, chip scale packages (CSPs) have emerged as the packaging technology of choice, fulfilling industry's continual need for smaller, faster and lighter performance electronics products. This technology has found many applications in the memory, telecommunications and aerospace industries.

To investigate the many issues of implementing CSP technology and verifying its reliability, a consortium led by the Jet Propulsion Laboratory (JPL) was formed to design and build a test vehicle with different types and styles of CSP <sup>1,2</sup>. Another objective was to utilize CSPs on test vehicle (TV) assemblies produced on several different surface mount technology (SMT) assembly lines. Three assembly lines were chosen. A high throughput, low throughput, and ultralow throughput.

Celestica's Customer Oriented Rapid Engineering Lab (CORE Lab, Facility A) was used for the assembly and inspection of the CSP test vehicles for CSP implementation in high volume assembly production. Key printing process variables including quality and solder paste volumes for

various CSPs were established. In addition, Raytheon (Facility B), using its internal resources, successfully assembled several of these test vehicles to demonstrated assembly capability in low volume application and potential cleaning issues using water soluble paste and cleaning. JPL (facility C) also assembled several test vehicles in an ultralow volume environment using RMA paste. Four cleaning agents were considered and their effectiveness was established. This paper will present lessons learned on assemblies at these three facilities.

#### **TEST VEHICLES**

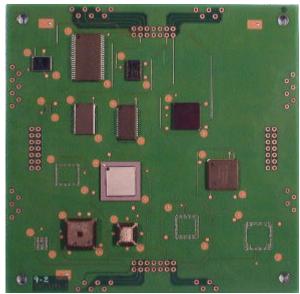

The CSP test vehicle one (hereafter TV1) is 4.5"x 4.5" double-sided board consisting of five layers. Each side is populated with ten different CSPs and one TSOP as a control. The TV1 CSPs range in pitch from 0.5 mm to 0.8 mm and in I/O count from 12 to 275 (see Figure 1 and Reference 3 in this proceedings). All packages used are daisy-chained to check the integrity and reliability of the solder joints. Test vehicle 2 (hereafter TV2) with 15 packages from 48 to 784 I/O with pitches from 0.5 to 1.27 mm was used for solder paste screen print optimization prior to full assembly of this test vehicle.

Figure 1 Test Vehicle 1 (TV1)

## HIGH VOLUME ASSEMBLY (FACILITY A)

As an in-kind contribution, facility A was involved in the process development and test vehicle assembly of more than 150 TV1 assemblies. The manufacturing processes were more precisely defined by assembling a number of trial test vehicles, and they were further fine tuned during a sixmonth test vehicle build. Post-assembly inspection played a very important part as a quality control tool as different optimization techniques were performed. A set of test vehicles was built to investigate CSP's manufacturing robustness by increasing the placement offsets from that of normal assemblies. In order for the process to be effective on a large scale, it became important to ascertain the

allowable margin of errors that could still produce a reliable product.

Further studies were performed using the TV2 to determine the effects of key process variables on solder paste deposition quality and volume. These included solder paste application uniformity and effects by process parameters such as stencil thickness and squeegee angle and materials.

#### **Packages**

- From a manufacturing point of view, the eleven CSPs used on the test vehicle were classified based on their basic structure. There were three basic types of CSP structures:

- leadless packages similar to leadless chip carriers (LCCs);

- leaded packages similar to a gull wing package;

- grid packages similar to BGAs<sup>4,5</sup>.

Table 1 lists the CSPs with their characteristics.

Table 1. CSPs Assembled

| Table 1. CSPs Assembled |                           |                  |             |  |  |  |  |  |

|-------------------------|---------------------------|------------------|-------------|--|--|--|--|--|

| Package<br>ID           | Package<br>Type           | Package<br>Style | Pitch<br>mm |  |  |  |  |  |

| В                       | Leadless-1                | Bottom Lead      | 0.8         |  |  |  |  |  |

| C                       | TAB CSP-2                 | Full Array       | 0.75        |  |  |  |  |  |

| D                       | TSOP44                    | Lead             | 0.8         |  |  |  |  |  |

| E                       | Leadless -2               | Bottom Lead      | 0.5         |  |  |  |  |  |

| F                       | TAB CSP-1                 | Full Array       | 0.75        |  |  |  |  |  |

| G                       | Chip-on-Flex-1<br>(COF-1) | Full Array       | .020 in.    |  |  |  |  |  |

| J                       | Wire bond on Flex-1       | Peripheral       | 0.8         |  |  |  |  |  |

| K                       | Wire bond on Flex-2       | Peripheral       | 0.5         |  |  |  |  |  |

| M                       | Chip-on-Flex-2<br>(COF-2) | Peripheral       | .020 in.    |  |  |  |  |  |

| N                       | Ceramic CSP               | Full Array       | 0.8         |  |  |  |  |  |

| 0                       | Wafer Level               | Peripheral       | .020 in.    |  |  |  |  |  |

<sup>\*</sup> All measurements are in mm unless otherwise specified

The printed wire boards (PWBs) were designed with microvias on one side, and a conventional design on the other. All soldering pads on the test boards were non-solder mask defined (NSMD). The use of such a board allowed the team to investigate the effects of microvia build up technology on assembly void levels in comparison to conventional technology under the same assembly conditions. Each assembly step will be discussed briefly as follows.

## **Receiving Inspection: CSPs and PWBs**

All CSPs were inspected visually and screened for:

- a) Physical package damage

- b) Missing or deformed solder balls

- c) Organic residues

- d) Polarity marks

All PWBs were inspected for:

- a) Warpage

- b) Missing solder mask dam or misregistration

- c) Microvia misregistration

#### **Panel Preparation**

The PWBs received did not need any preparation, but packages B, D, and E, as level 3 (moisture sensitive, allowed one week out of bag at 30°C/60% RH), were processed with a 125°C moisture bake-out for 24 hours prior to assembly. All CSPs were stored in a dry nitrogen chamber prior to assembly to avoid any time dependent moisture effects.

## **Solder Paste Printing**

Stencil design proved to be the most challenging part of screen printing. As it is rare to find a board that contains CSPs exclusively, it was critical to take into account other SMT packages into the paste volume calculations. In general, a 6-mil to 8-mil stencil is required to deposit adequate amounts of solder paste for surface mount devices (SMDs). When CSPs become incorporated into standard assembly processes, soldering problems may arise. The finer pitch and pad size involved could cause solder bridging should the same stencil be used for both conventional SMDs and CSPs. In addition, the low print area aspect ratio causes a reduced solder paste release rate.

Figure 2 Solder paste on pads

Good stencil design can improve solder printing quality for CSPs and SMDs and meet their solder paste volume requirements. A step-down stencil was evaluated in early experiments. Although it allowed for the solder volume variations needed in mixed technology assembly, (conventional SMDs and CSPs), inconsistency in the solder volume deposited and higher solder volume variation were observed. Another solution was attempted, which consisted of optimizing the combination of stencil thickness and aperture size.

Based on previous experiments, a 6 mil stencil was chosen for 141 of the 150 test vehicle built. The print area aspect ratios ranged from 0.47 to 1.09. The aperture size to pad

size ratio was optimized to maximize the solder volume without sacrificing process robustness. To ensure that adequate amounts of paste were deposited, the aperture shape became an important parameter. From prior builds, it was determined that a square aperture with rounded corners provided superior paste release characteristics in comparison to round apertures.

A more recent model printer was used to improve consistency and quality of the screening process. This printer was equipped with a pressurized solder paste dispensing head; it has an alignment repeatability of  $6\sigma$  at  $25~\mu m,$  and a print accuracy of  $3\sigma$  at  $25~\mu m.$  Figure 2 shows the paste screened onto a component pattern on a PWB.

## Cleaning

The clearance between the bottom of the CSPs and the surface of the board was found to vary from component to component. The minimum height was found to be as small as 1.2 mil<sup>1</sup>. Conventional in-line deionized (DI) water cleaners cannot adequately clean underneath such a component; therefore a no-clean paste was chosen. The noclean paste had a 63/37 Sn/Pb particle size of -325+500 (Type 3) and a room temperature viscosity of 900 to 1000 kcps. Also, another, no-clean solder paste was tried which improved print quality.

#### **Solder Volume**

Although paste volume was an important parameter, it was impossible to accurately measure it using the automated inline machine since there were no reference surface. The conventional dog bone design used in BGA design as reference was no longer existed. The microvias eliminated the need for the usual via features that are used for reference in paste volume measurements. Therefore, for TV1 solder paste heights rather solder paste volumes were measured manually using an LSM machine. For TV2, copper trace lines were designed as control references to facilitate the automatic measurement of solder volume.

#### **Solder Paste Reflow**

For the TV1 assembly, a 10-zone convection reflow oven was used, having a nitrogen atmosphere controlled to less than 500 PPM oxygen level. No fixture or additional support was used as the test vehicle rode along the handling fingers of the oven. Any warpage incurred during reflow was then observed and measured.

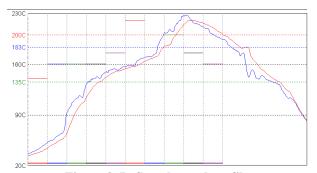

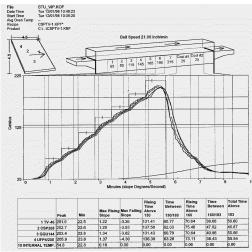

Different thermal profiles were attempted during this project. It has been shown that a low thermal profile will reduce the percentage of solder voids<sup>6</sup>. The reflow profiles used were all within the boundaries of paste specifications provided by the supplier. Figure 3 shows the thermal profile in both sides of the control part on the assembly.

Different thermal reflow profiles, produced a different number of voids in the solder joints. Solder joint integrity could be undermined by the location and size of those voids. Excessive voiding reduces the amount of solder at the joint and can possibly affect reliability. However, entirely eliminating voiding is not necessary. If they are in the benign location, they could increase the package standoff, thus improving solder joint reliability.

Figure 3 Reflow thermal profile

### Solder paste deposition study for TV2

Solder paste deposit quality, i.e., solder paste consistency and volume, is critical to solder joint reliability. It has been shown that forty percent of the soldering defects in SMT assembly are associated with the solder paste printing process.

A series of experiments were performed to establish solder past deposition with printing process variables for package patterns with various pitch and size. In the TV2 design, a 3D laser measuring system in conjunction with reference traces was used to measure solder paste volume. Quality of print was established by visual inspection. Aspects of this experiment are discussed below.

#### Solder paste printing for TV2

The TV2 PWB had an OSP surface finish and a pad size variation from 0.25 mm to 0.66 mm and a pitch variation from 0.5 mm to 1.27 mm. Six package patterns out of fifteen were included in the experimental analysis. These were chosen as representative samples of fine (0.5 mm), medium (0.80 mm) and coarse (1.27 mm) pitch modules. The study included a no-clean paste, type III (-325+500) mesh, with a metal content of 90.25% and a viscosity of 900-1000 Kcps at room temperature (22 °C). Table 2 lists the variables considered in this study. Study details is a subject of another paper.

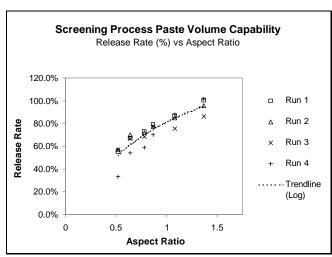

## Paste volume with aspect ratio

The paste volume release by the screening process changes as the pad size decreases from BGA to CSP. Two parameters were considered to establish such changes: (1) release rate (measured paste volume as a percentage of theoretical volume) and (2) aspect ratio (ratio of wall area to aperture area). Relationship between the two for many screening process variables were characterized as shown in Figure 4. Generally, solder volume release decreased as aspect ratio decrease. This was also reported by another investigator (see Clouthier<sup>7</sup>). For printer B, a sharp decrease in release ratio was observed at 0.5 aspect ratio

Table 2: Variables for screening printing of TV2

| <b>Experimental Run</b> | 1         | 2         | 3                | 4         |

|-------------------------|-----------|-----------|------------------|-----------|

| Equipment               | Printer A | Printer A | Printer A        | Printer B |

| Squeegee Angle          | 45        | 60        | N/A              | 60        |

|                         |           |           | Pressurized Head |           |

| Squeegee Blade          | 5 mm      | 15 mm     | N/A              | 22        |

| Overhang                |           |           | Pressurized Head |           |

| Print speed             | Standard  | Standard  | Standard         | Standard  |

| Pressure                | Standard  | Standard  | Standard         | Standard  |

Figure 4 Effect of aspect ration on paste volume

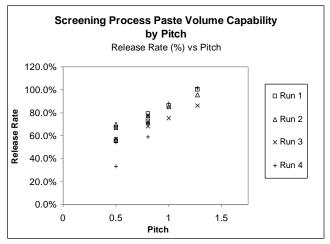

#### Paste volume with pitch

The effect of pitch on paste releases are shown in Figure 5. As the pitch decreases the paste release decreases. Paste volume release for printer A under various conditions was better than printer B, even though printer B showed comparable release at 1 mm and 1.27 mm pitches.

Figure 5 Past volume variation with package pitch

## LOW VOLUME ASSEMBLY (FACILITY B)

To address low volume assembly issues additional features must be incorporated up-front in the design as packaging density continues to increase and the pitch decreases<sup>8</sup>. Stencil design, solder volume measurement, pick and place, and reflow issues have to be resolved before embarking on low volume assembly to insure high yields and low defect levels. These are addressed below for a low volume throughput assembly performed in Facility B.

## **Stencil Printing**

CSP stencil printing was a challenge as compared to that of BGAs. The stencil was designed to have laser etched, trapezoidal, nickel polished aperture openings. Square aperture opening with rounded corners, instead of round aperture openings, was used for CSPs. A 6-mil thick stencil was used to provide optimum solder volumes to ensure a good solder joints for the CSP. In addition, solder paste suitable for printing pad sizes smaller than 0.080 mm was used. Solder print thickness was also monitored during printing to ensure optimum solder volume.

During the low volume assembly of CSP TV-1, the boards were manually loaded and unloaded on the machine and manually transferred between processes, providing the opportunity to check the boards after each process. The boards and components were baked prior to assembly at 125 °C for six and twenty four hours respectively.

Figure 6 Solder Print on an 0.5 Pitch CSP Pads

The global fiducials on the PWB and the stencil were used to facilitate accurate alignment of solder paste to the pad on the board (see Figure 6). A semiautomatic vision system was used requiring fiducials to align stencil to the board

pattern with an accuracy of +/-0.001. Using a microscope with 10-40X magnification, all boards were verified for the following:

- misalignment of solder deposition to the pads;

- solder bridges;

- void.

## **Pick-and-Place**

Because of the CSP's fine pitch (0.5 mm), small pad sizes (0.254 mm), and high I/O count, precise placement is necessary to achieve maximum mechanical contact (package to board) and minimize assembly defects. At first, a mechanical centering system was tried to place the CSPs. However, due to the inconsistent location of solder balls on the package, the placement onto the board was not repeatable. Later, a dual vision system was used to assemble the test vehicles. The system is equipped with a high-resolution camera with side and front lighting to handle fine pitch devices (= 0.8-mm). It is also capable of handling asymmetrical area array configurations. In addition, the system can identify missing solder balls on package dimensions up to 38 mm x 38 mm.

An X-ray imaging system was used to verify placement of the CSPs to the board. The local fiducials on the PWBs were used to facilitate accurate alignment of the CSPs to the attachment pads.

#### Solder Reflow

A convection system equipped with seven heating and two cooling zones was used to reflow the assemblies. Top and bottom heaters of each zone are independently controlled. The entire system is software driven which allows for better belt speed and temperature controls and endless menu options. The seven-zone design allows for a slower temperature rise as required by the water soluble solder paste used in the assembly process. Compressed dry air was used in the oven during reflow process.

To achieve optimum reflow profiles, a thermocouple was attached to the test board underneath the ceramic CSP (package N, see Table 1). The ceramic CSP was chosen to monitor the temperature due to the difference in its thermal mass compared to other packages and the board. A radio transmitter portable unit was also used during profiling and was found to be a convenient option for achieving a real time profile. See Figure 4 for peak reflow temperature and dwell time. To avoid "popcorning", the peak temperature of the packages was monitored to make sure it does not exceed 220°C, as required for all plastic encapsulated microcircuits (PEMs).

Optimum reflow profile is critical to achieve a good solder joint fillet and optimum standoff height (see Figure 7). Standoff heights for assembled packages varied from 0.033 mm to 0.380 mm, depending on the package pitch and ball size.

Figure 7 Reflow Profile of CSP TV1

Figure 8 Cross-section of an assembled CSP

## **Aqueous Cleaning**

The aqueous cleaning of the assembled boards was performed after initial solder reflow and rework. Due to the small standoff height, flux cleaning under the packages was a challenge. High-pressure deionized water at an elevated temperature was used to clean the assemblies. This was followed by a hot air dry cycle. Ionic contamination testing was also performed on the boards using an Omegameter tester to verify cleanliness. In all cases, test results indicated that contaminant levels were  $<\!14\mu g/in^2$ , well below the MIL-STD-2000A specifications. Results were not verified by destructive testing.

## X-ray Inspection

A state of the art X-ray system was used to verify the quality of the solder joints after reflow. Because of final inspection requirements for non-commercial circuit card assemblies, it is very important to utilize the X-Ray

capability to inspect the CSP solder joints as a process control. The inspection is a verification of probable assembly defects such as solder bridges, solder voids, and misalignment of solder ball to pad (see Figure 9).

Figure 9 X-ray Photo of a 0.5 mm Pitch after Reflow

#### Rework

Rework is an integral part of the development process, especially for non-commercial applications. Because of the high costs associated with non-commercial circuit card assemblies, rework is a "must" option.

A new rework system has been used to validate the removal and replacement of components due to misalignment, shorts, opens, and missing solder balls. This rework system is also equipped with a split beam vision system, which greatly facilitates alignment of component to board. An appropriate nozzle size is required for each CSP type. Water-soluble flux and water-soluble solder paste were used during rework of the CSPs.

# ULTRALOW VOLUME ASSEMBLY (FACILITY C)

The study carried out at Facility C was focused on improving the SMT assembly process in a low-volume, high reliability environment with emphasis on development of cleaning materials and processes. Except for use of RMA solder paste, vapor phase for reflow, and cleaning, the other steps used were similar to the low volume processes.

## **RMA Solder Paste**

Residues from RMA fluxes and pastes have the potential for being corrosive, and residues from WS pastes and fluxes are extremely corrosive. Commercial SMT facilities generally operate using a no-clean flux or no-clean paste. RMA flux, however, still continues to be used for space and most military electronic applications. For high reliability applications, residues and contaminants under CSPs must be removed during cleaning. The commercial SMT assembly facility was not well equipped for investigating and cleaning RMA and WS paste residues.

Additional work done to find a better technique for cleaning CSP assemblies since residues could be problematic. CSPs typically have a low standoff of less than 0.1mm, cleaning under such components is difficult and further complicated by the hundreds of solder ball leads that such components have. Currently, a low flash point semi-aqueous material, in conjunction with a batch cleaning unit, is being used to clean printed wiring assemblies (PWAs). The approach taken at facility C was to investigate the use of (1) semi-aqueous materials having a high flash point and (2) aqueous cleaning involving a saponifier.

## **Experiment**

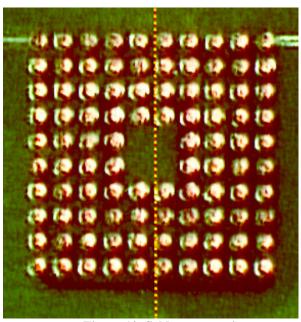

Figure 10 Solder paste print

Ten test vehicles were built at facility C using a vapor phase reflow equipment. Each test vehicle had only a few representative packages and were not fully populated. Processing the assemblies involved the following steps:

- Preclean the PWBs in an ECD 7600 aqueous cleaner and bake at 100°C for 8 hours

- Screen print boards on DEK 248 screen printer. The parameters were:

- Stencil laser cut, 6 mil stainless steel.

- Paste Qualitek, Sn 63 with RMA flux.

- Metal squeegee was used.

- Average solder paste height was measured to be 5.8 mil.

- Example of screen print quality is shown in Figure 10

- All the components were placed on the PWB by using split vision AirVac rework system.

- A profile similar to the JPL BGA Consortium board assembly with the following heating steps were used:

- An average preheat temperature of 140°C was reached under the package.

- An average maximum Temperature of 213°C was reached under the package.

- Boards were reflowed in the vapor phase reflow system with the following parameters:

- Preheat temperature equal to 250°C and dwell equal to 130 seconds

- Reflow temperature equal to 216°C and dwell equal to 50 seconds

Cleaning effectiveness of cleaning were determined using an Ionograph 500M. A few were pried off and visually inspected for signs of contamination residue. In Table 3 below, each number represents an arithmetic average of two independent determinations. The quality characteristic measured was the ionic residue expressed in micrograms of NaCl or equivalent per square inch ( $\mu g$  NaCl or eq./in<sup>2</sup>).

It is apparent that most of cleaning agents successfully remove flux residue. The next step is to perform chemical analysis on boards with parts removed to determine the nature of the residue.

#### CONCLUSIONS

#### **High Volume**

- CSPs are robust for assembly, and it was demonstrated that they can be integrated in an SMT line for high volume production by optimizing the stencil thickness, aperture size, use of high quality paste, and the printer.

- Solder paste deposit quality (volume and consistency) depends on the aspect ratio of the stencil and printing parameters. Better CSP integration in an SMT assembly is possible when the aspect ratio become close to that of a BGA with 1.27 mm pitch

#### Low Volume

- A visual system with a high resolution camera was required for placement of fine pitch CSPs.

- CSPs with water soluble flux residues were successfully cleaned using high pressure deionized water at elevated temperature (Omegameter test results).

#### **Ultralow Volume**

CSPs were successfully assembled using RMA paste in a vapor phase reflow system after optimization of paste and reflow processes.  CSPs with RMA paste residues were successfully cleaned using four different cleaning agents (Omegameter test results).

#### **ACKNOWLEDGEMENTS**

The authors would like to acknowledge the effort and support of the JPL Microtype BGA Consortium members, especially R. Smedley, Raytheon; D. Baken and S.Tisdale, AlliedSignal. Authors from Raytheon appreciate support of P. Temple, C. Altamirano, M. Brown, S. Walsh, M.Lyson, and J. Robson.

The portion of research described in this publication is being conducted by the Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration.

#### REFERENCES

- Siméus, E. J.; S.R. Stegura; R. W Smedley; R. W III, Sterian; A. Chen; C. Quan; R. Mohabir; J. Bragg; K. Chang; M.Chan; T. Buschor; D. Norton; R. Ghaffarian, J.K. Bonner; "CSP Consortia Activities: Program Objectives and Status" SMI Proceedings, August 98.

- Ghaffarian, R., N.P. Kim; K. Selk; K., B. Bjorndahl;

J.K. Bonner; S. Barr; "CSP Assembly Reliability: Commercial and Harsh Environments", SMTA International Proceedings, Sept. 12-16, 1999

- 3. Ghaffarian, R.,"Impact of CSP Assembly Underfill on Reliability,", APEEX 2000 Proceedings, March 2000

- 4. Chen, A., "Assembly Process Development for CSP Application and Issues", IPC/SMTA Electronics Assembly Expo, pp.S12-1-1 S12-1-4, October 24-29, 1998.

- 5. Sterian, I., Chen, A., et. al., "Compatibility of CSPs in SMT Assembly", Surface Mount International, San Jose, August 23-27, 1998.

- 6. Horsley, R. and N. Ekere, "Causes of Voiding in Plastic Ball Grid Array Eutectic Solder Joints", Soldering & Surface Mount Technology, pp.18-22, September 3, 1997.

- 7. Clouthier, R., "SMT Printing Process for Fine and Ultra Fine Pitch", Surface Mount International, pp.674-686, San Jose, September 7-11, 1997.

- 8. Siméus, E. J., Stegura, S.R. "Chip Scale Packaging Design for Aerospace and Military Applications" Chip Scale International Symposium, May '98

Table 3 Cleaning agents and test results (Facility C)

| PWB<br>SN  | Cleaning Processes                                                                                                                                                                                                          | Prior to remova<br>Visual | l of components<br>lonograph                                                                       | After Component<br>Removal<br>Visual                                                          |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 001        | Asahi AK 225T Solvent was used in a batch type degreaser. Cycle - 4 min. in vapor zone at 140 F, 60 seconds ambient spry.  Board placed at an angle in the basket.                                                          | No visual residue         | Passed the test.<br>0.0 microgram/sq.in                                                            |                                                                                               |

| 002        | Asahi AK 225T Solvent was used in a batch type degreaser. Cycle - 3 min. in vapor zone at 140 F, 60 seconds ambient spry.  Board placed flat in the basket.                                                                 |                           | Failed lonograph test -<br>21.5 micrograms/sq.in.<br>pass limit = 15 ug/sq.in.                     |                                                                                               |

| 003        | Asahi AK 225T Solvent was used in a batch type degreaser. Cycle - 4 min. in vapor zone at 140 F, 30 seconds ambient spry.  Board placed at an angle in the basket.                                                          | No visual residue         | Passed the test.  1.73 microgram/sq.in                                                             | Parts were removed.<br>Residue was visible<br>under two small<br>TSOPs.                       |

| 004        | Zestron A200, 20% solution in DI water used in an aqueous batch cleaner made by Unit Design model ABC 2400. Cycle - 7 min. wash at 140 F, 5 ea. 2min rinses at 140 F, followed by 10 min drying at 170 F.                   | No visual residue         | Passed the test. 0.88 microgram/sq.in                                                              |                                                                                               |

| 005        | Zestron A200, 20% solution in DI water used in an aqueous batch cleaner made by Unit Design model ABC 2400. Cycle -10 min. wash at 140 F, 7 ea. 1 min rinses at 140 F,followed by 10 min drying at 170 F.                   | No visual residue         | Not tested in Ionograph                                                                            | Parts were removed. Residue was visible under two small TSOPs.                                |

| 006        | Zestron A200, 20% solution in DI water used in an aqueous batch cleaner made by Unit Design model ABC 2400. Cycle - 7 min. wash at 140 F, 4 ea. 1 min rinses at 140 F,followed by 10 min drying at 170 F.                   | No visual residue         | Not tested in lonograph                                                                            |                                                                                               |

| 007<br>008 | Armakleen 2000P, 20% solution in DI water used in Unit Design Batch cleaner ABC 2400.  Cycle - 7 min. wash at 140 F, 5 ea., 1 min. rinses at 140 F,followed by 10 min. drying at 170 F.  Both boards were cleaned together. |                           | Passed Ionograph test -<br>0.03 microgram/sq.in                                                    | Parts were removed<br>from S/N 008. White<br>residue was visible<br>under two small<br>TSOPs. |

| 009<br>010 | EC7-R, DI water/Soponifier wash and alcohol rinse in ECD 6307 and 6300 batch aqueous cleaner.                                                                                                                               |                           | Passed lonograph test -<br>4.23 microgram/sq.in<br>Passed lonograph test -<br>0.00 microgram/sq.in | Parts were removed from S/N 009. Some residue was visible under two small TSOPs.              |