# Design and technology of DEPFET pixel sensors for linear collider applications

R.H. Richter<sup>a\*</sup>, L. Andricek<sup>a</sup>, P. Fischer<sup>b</sup>, K. Heinzinger<sup>c</sup>, P. Lechner<sup>c</sup>, G. Lutz<sup>a</sup>, I.Peric<sup>d</sup>, M. Reiche<sup>e</sup>, G. Schaller<sup>a</sup>, M. Schnecke<sup>a</sup>, F. Schopper<sup>a</sup>, H. Soltau<sup>c</sup>, L. Strüder<sup>a</sup>, J. Treis<sup>a</sup>, M. Trimpl<sup>d</sup>, J. Ulrici<sup>d</sup>, N. Wermes<sup>d</sup>

> <sup>a</sup>MPI Halbleiterlabor Munich, Germany <sup>b</sup>University of Mannheim, Germany <sup>c</sup>PNSensor gGmbH Munich, Germany <sup>d</sup>University of Bonn, Germany <sup>e</sup>MPI für Mikrostrukturphysik Halle, Germany

### Abstract

The performance requirements of vertex detectors for future linear collider experiments is very challenging, especially for the detector's innermost sensor layers. The DEPleted Field Effect Transistor (DEPFET), combining detector and amplifier operation, is capable to meet these requirements. A silicon technology is presented which allows production of large sensor arrays consisting of linear DEPFET detector structures. The envisaged pixel array offers low noise and low power operation. To ensure a high radiation length a thinning technology based on direct wafer bonding is proposed.

Keywords: Active pixel detector; DEPFET; Low noise operation; Vertex detector; Linear collider

## **1. Introduction**

Active pixel detectors play a growing role in high energy and astrophysics experiments. Future experiments, e.g. TESLA (Tera Electron Volt Energy Superconducting Linear Accelerator) [1] and XEUS (X-Ray Evolving Universe Spectroscopy Mission) [2], will need large area pixel detectors with very challenging requirements. In astrophysics, the spatial resolution of the detector is less crucial than the energy resolution, because the degree of spatial precision is limited more by the Wolter X-ray telescopes than by the silicon sensors. The requirements in high energy physics are often opposite.

<sup>\*</sup> Corresponding author. Tel.: +49-89-83940043; fax: +49-89-83940011; e-mail: rar@hll.mpg.de.

Especially for the inner layer of the TESLA vertex detector, a lot of partially contradictionary demands have to be addressed. In order to meet the required resolution of primary and secondary vertices, the innermost detector layer has to be placed at a radius of 15mm from the interaction point. The pixel detector at this place has to provide a spatial resolution of less than 5µm. The high occupancy, caused by the beamstrahlung, has to be suppressed by a very fast readout cycle of about 50MHz. To reduce multiple scattering, the material introduced in the detector must be minimized. This means that no extra material for cooling pipes etc. is allowed and, additionally, the sensor substrates must be thinned to ~50µm thickness. This results in a reduced signal charge compared to that generated in standard silicon detectors, where the depletion layer extensions are of the order of 500µm. In summary, the ideal vertex detector for TESLA should fulfill the competing boundary conditions simultaneously: High position resolution should be achieved with small signal amplitudes, i.e. with thin detectors. Simultaneously, the operation must be fast, e.g. 20ns processing time with low power dissipation in an environment of a significant radiation level.

The DEPleted Field Effect Transistor structure, abbreviated DEPFET, is a monolithic device which is integrated onto a high ohmic fully depletable detector substrate [3]. The device is one proposal for a detector design that is consistent to a large extent with all of the above requirements [4]. While the system aspects and the readout concept are discussed in [5], this paper proposes a technology for the production of large area DEPFET arrays. The different operation modes of the device are evaluated by process and device simulations. A thinning procedure compatible to the DEPFET process and the module concept is discussed.

# 2. DEPFET operation principles

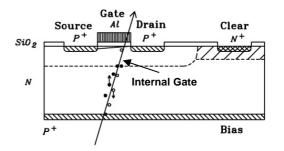

The DEPFET combines detection and amplification within one device [3]. It is based on the sideward depletion as used in semiconductor drift chambers, [6]. The principle of operation is shown in Fig.1. A p-channel MOSFET or JFET (junction field effect transistor) is integrated onto a silicon detector substrate, which becomes fully depleted by the application of a sufficiently high negative voltage to a backside p+ contact. By means of the sideward depletion, a potential minimum is formed which is shifted directly underneath the transistor channel at a depth of about 1 $\mu$ m by an additional phosphorous implantation underneath the external gate. Incident particles generate electron-hole pairs within the fully depleted bulk. While the holes drift into the back contact, electrons are accumulated in the potential minimum, called the internal gate resulting, in a modulation of the channel current. The readout is non-destructive and can be repeated several times.

The removal of the signal charge and thermally generated electrons from the internal gate is called *Clear*. A neighboring n+ contact is pulsed at a positive voltage providing a punch-through into the internal gate. This pulsed clear mechanism is discussed below in detail.

Fig.1: Cross section of a DEPFET indicating the operation principle.

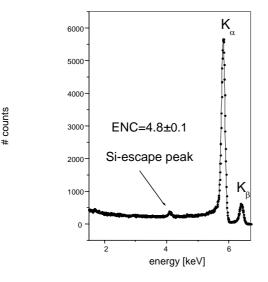

Intrinsic advantages of the DEPFET device are the amplification of the signal charge at the position of its generation, thus avoiding any charge transfer where losses could occur. The entire bulk is depleted and sensitive to incident radiation. Therefore, the non-structured backside can be used as an entrance window thereby improving the spectroscopic performance, especially for low energy photons. The main advantage of the device is its very small input capacitance that provide a very low noise operation even at room temperature. Fig.2 illustrates the excellent noise performance with a measured Fe<sup>55</sup> spectrum.

DEPFET structures can be operated individually, as an integrated on-chip amplifier, for instance in the readout node of a silicon drift chamber, or collectively as a pixel array.

Fig.2: Fe<sup>55</sup> spectrum measured on a single DEPFET pixel at room temperature [8]. The equivalent noise charge was fitted to be ENC =  $4.8 \pm 0.1$ .

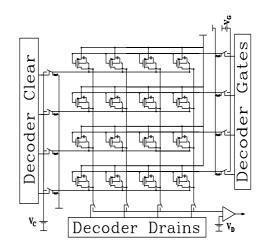

Fig.3 shows a DEPFET pixel matrix which is operating with a line-by-line access via the external gates. Note that the external gates just switch the pixel on and off while the signal amplification is achieved via the internal gate. There is no current flow in a non-selected DEPFET row, resulting in a very low power consumption of the array [4].

A first 2 x 2 pixel array was produced and operated in 1997 [7]; results from a 64 x 64 pixel imaging system were presented in 1999 and 2000 [9-12]. The readout amplifiers at the end of the columns can be connected either to the sources (source follower) or to the drains (drain read out) of the DEPFETs. For linear collider applications we need the faster drain (current) readout, (see also [5]). A measurement cycle consists of a collection stage (Collect), the read out (Read) and the reset of the internal gate (Clear). A pedestal subtraction is obtained by a consecutive Read-Clear-Read sequence. Therefore, the clear process affects the noise performance of the device significantly. Any reset noise is avoided if the entire charge is completely removed from the internal gate. If this is not guaranteed an additional noise contribution occurs due to an undefined amount of remaining charge in the internal gate.

Fig.3: Basic pixel array readout scheme. Only the row addressed by the decoder gates is active while the other rows are switched off and do not contribute to power consumption of the detector.

# 3. DEPFET technology development and design

Until now, the DEPFET device concept was evaluated mainly on circularly shaped JFETs<sup>1</sup>. However, a position resolution in the range of 5µm, needed for vertexing, requires pixel cell sizes of about 25 x  $25\mu$ m<sup>2</sup>. This is impossible to achieve with JFETs at the presently given minimum technological feature sizes of 2µm to 3µm. Linear structures are innately smaller than circular ones but the fabrication of linear JFETs is very complicated due to the problem of lateral channel isolation. Another intrinsic difficulty of JFET technologies is the pinch-off voltage variation over the wafer, within fabrication batches and from batch to batch. Therefore, we are going to use MOS devices. In principle MOSFETs can be produced in any shape, linear as well as circular. In terms of reliability and homogeneity they are suitable for large area devices and have a much higher geometrical scaling potential than JFETs.

<sup>&</sup>lt;sup>1</sup> 'Circularly shaped' means a closed transistor where the drain surrounds the source region or vice versa, in contrast to linearly shaped transistors having a lateral confinement of the channel by an isolation structure.

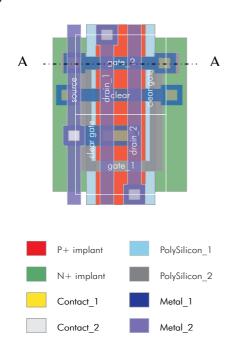

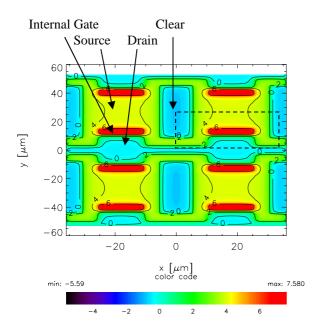

Fig.4: Layout example for a linear double pixel cell. Each white rectangle surrounds a DEPMOS.

For larger area sensor arrays, the availability of more than one metal layer is mandatory due to the necessity of the row- and column-wise connections of the pixels. At the Semiconductor Laboratory of the Max-Planck-Institutes, a 150mm silicon technology for MOS type DEPFETs on high ohmic substrates with two polysilicon and two metal layers has been developed. Using the two polysilicon layers, linear DEPMOS transistors can be fabricated whereby the first polysilicon forms a lateral isolation frame and the second one is used for the external gate of the DEPFET. This approach is different from that used in common MOS technologies, where the lateral transistor isolation is provided by locally oxidized field regions or shallow trenches filled with oxide. The channel isolation structure of the DEPFETs must not collect signal electrons and has to accomplish the integration of the clear contacts.

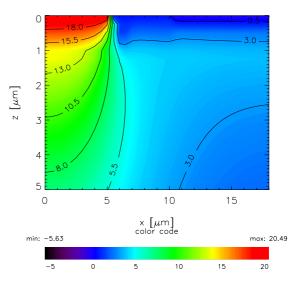

Fig.5: Potential distribution across the section A-A in Fig.4 during the clear operation simulated with the 3D-Poisson solver Poseidon [18] (VClear = 20V, VBack = -30V, VSource = 0V, VDrain = -5V, VGate = -3V, VClear-Gate = 1V).

The n+ doped clear region is close-by the internal gate, separated only by the first polysilicon layer. In the Collect and Read modes, the region underneath the polysilicon acts as a potential barrier between the clear region and the internal gate. The barrier has to be overcome during the Clear cycle when the clear contact gets positive. The first polysilicon acts not only as an isolation frame but also as a reset (clear) gate. It is held at a constant potential or can be switched in order to alleviate the clear process. As shown in Fig.4, the linear cell geometry allows for a very compact pixel layout free from potential pockets where the signal charge could disappear (see also Fig.6). In any case, the implanted drain, source and clear regions are shared by neighboring cells. In this way a small pixel size is achievable even with rather relaxed lithographic requirements. This feature, which defines also the tolerable defect size in the process, is important concerning the yield of large area detectors.

We have started a production run on 6-inch wafers containing prototype arrays of up to 128x64 pixels for high energy and astrophysical applications [13-15]. The smallest pixel cell size is presently  $30x20\mu m^2$ .

# 4. Device simulations

Two and three dimensional simulation tools [16-19] are used to optimize the layout and the technology parameters. Fig.6 shows the simulated potential distribution (section A-A in Fig.4) during the clear operation.

Fig.6: Potential distribution of a 2x4 array section parallel to the surface at a depth of  $z=1\mu m$  during charge collection simulated with Poseidon (VClear = 3V, VBack = -25V, VSource = 0V, VDrain = -5V, VGate = 2V, VClear-Gate = 1V). A single cell is marked by the dashed line.

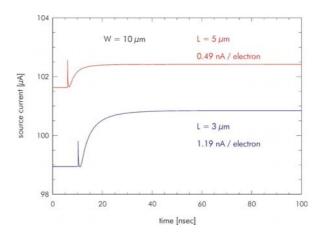

The simulation illustrates that the electrons can flow unopposed from the internal gate into the clear contact. The applied clear voltage of 20V can be reduced by lowering the potential barrier in the clear gate region. During charge collection, the transistor is switched off and the potential of the internal gate can be adjusted by the voltage of the external gate via capacitive coupling. Fig.6 shows the potential at a depth of 1 $\mu$ m, as seen by drifting electrons generated in the bulk. Note that there is not any attraction of the n+ clear contact to the electrons at this depth. This is the result of the negative space charge of a deep boron doping implanted beneath the clear region. By switching on the external gate the device current is read out. The drain current response to a given signal charge defines the amplification of the internal gate  $g_q = k I_D/k q$ . To analyze the signal response of the DEPFET, 1600 electron-hole pairs were introduced by a locally and temporally limited increase of the Shockley-Read-Hall generation rate using the two dimensional device simulator TeSCA [16]. The simulated signal response, shown in Fig.7, demonstrates an amplification potential of more than 1nA per electron for optimized DEPFET structures.

Fig.7: Simulated signal response to a signal charge generation of 1600 electron-hole pairs.

## 5. Thinning technology

The DEPFET, as a fully depleted device, needs, in addition to the front side structures, a p+n diode at the backside. Therefore a standard thinning process is not applicable because it would destroy the backside pn - junctions. The key technology of the process sequence illustrated in Fig.8 is the direct wafer bonding [20]. It starts with a sensor wafer on top and a handle wafer on bottom, which are bonded together on their oxidized surfaces (Fig.8 a). The top wafer, already contains the backside which p+implantations, is thinned to a thickness of ~50µm by standard wafer grinding and polishing (Fig.8 b). This side is where the actual device is fabricated. During the front side fabrication process, the obtained sandwich package can be handled like a standard

wafer without special precautions for backside protection (Fig.8 c). After topside metallization and passivation, the handle wafer is partially etched back (Fig.8 d) leaving a small frame large enough to provide mechanical stability and space for the affixed steering and readout chips [5].

Fig.8 a-d: Joint process sequence of wafer thinning and DEPFET production.

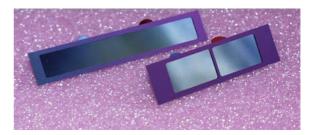

An inherent advantage of this technology is that the inner silicon oxide acts as a stop layer for the etchant, leaving the backside diode of the sensor wafer unaffected by the etching. With the proposed concept, the material budget per layer can be reduced to the range of 0.1-0.15% of a radiation length, including the already thinned read out and line driver chips. Pictures of the first mechanical samples produced with this technology are shown in Fig.9.

Fig.9: First results of the thinning technology development - mechanical samples. The size of the upper part is 800x104mm<sup>2</sup>.

# 6. Summary

The DEPFET is a promising candidate to fulfill the challenging detector requirements of future high energy physics experiments, e.g. the TESLA vertex detector. It offers excellent low noise performance at room temperature. Thus the DEPFET has the potential to achieve a good spatial resolution and a fast readout speed even on a thinned detector substrate. The overall requirement of a minimum material budget is addressed by an intrinsically low power consumption, thereby saving material for cooling structures. At the MPI Semiconductor Laboratory, a new MOS based technology on 150mm wafer has been developed to produce large detector arrays.

Linearly shaped DEPFETs of a size of about  $25x25\mu$ m<sup>2</sup> can be made by using two polysilicon layers. As a detector pixel cell consists of only one single DEPFET transistor, it can be produced by rather large lithographic structures with minimum size of  $2\mu$ m. Therefore the yield problem occurring especially in large area detectors is expected to be relaxed. Technology development and detector design based on two and three dimensional processes and device simulations demonstrating the operation and the technological feasibility of DEPFET arrays. The first production run has been started. A thinning technology based on direct wafer bonding is proposed. Mechanical samples with 50 $\mu$ m thinned regions were fabricated successfully.

# Acknowledgments

We would like to thank K. E. Ehwald and B. Heinemann from IHP, Frankfurt/Oder for helpful discussions and suggestions. The simulation software POSEIDON was developed by A. Castoldi, E. Gatti and P. Rehak within the INFN-RIMAX project.

### References

- T. Behnke, S. Bertolucci, R.D. Heuer and R. Settles, TESLA: The superconducting electron positron linear collider with an integrated X-ray laser laboratory. Technical design report. Pt 4: A detector for TESLA', DESY-01-011.

- [2] XEUS astrophysics working group, X-ray evolving universe spectroscopy – the XEUS science case, ESA, SP-1238 (2000).

- [3] A DEPFET based pixel vertex detector for the detector at TESLA, LC-DET-2002-004, April 5<sup>th</sup>, 2002.

- [4] J. Kemmer and G. Lutz, New semiconductor detector concepts, Nucl. Instr. & Meth. A253, 356 (1987).

- [5] M. Trimpl et al., A fast read out using switched current techniques for a DEPFET pixel based vertex detector at TESLA, these proceedings.

- [6] E. Gatti and P. Rehak, Semiconductor drift chamber An application of a novel charge transport scheme, Nucl. Instr. & Meth. A225, 608 (1984).

- [7] G. Cesura et al, New pixel detector concepts based on junction field effecxt transistors on high resisitivity silicon, Nucl. Instr. & Meth. A377, 521 (1996).

- [8] J. Ulrici et al., Spectroscopic and imaging performance of DEPFET pixel sensors, Nucl. Instr. & Meth. A465, 247 (2001).

- [9] P. Klein et al., Study of a DEPJFET pixel matrix with continuos clear mechanism, Nucl. Instr. & Meth. A392, 254 (1997).

- [10] P. Fischer et al., First operation of pixel imaging matrix based on DEPFET pixels, Nucl. Instr. & Meth. A451, 651 (2000)

- [11] W. Neeser et al., The DEPFET Pixel BIOSCOPE, IEEE Trans. Nucl. Sci. 47 No.3 (2000).

- [12] W. Neeser et al., DEPFET a pixel device with integrated amplification, Nucl. Instr. & Meth. A477, 129 (2002).

- [13] G. Lutz, R.H. Richter and L.Strüder, Novel Pixel detectors for X-ray astronomy and other applications, Nucl. Instr. & Meth. A461, 393 (2001).

- [14] L. Strüder et al., Active pixel sensors for imaging x-ray spectrometers, submitted to SPIE

- [15] L. Strüder et al., Fully depleted backside illuminated spectroscopic active pixel sensors from the infrared to X-rays, Proc. SPIE Conference, Munich 2000, Vol. 4012 (2000).

[16] H. Gajewski et al., TeSCA – Two Dimensional

- Semiconductor Analysis Package, Handbuch, WIAS, Berlin, 1997.

- [17] ISE TCAD Release 7.0, V0l. 2b, DIOS, 2001.

- [18] A. Castoldi, E. Gatti and P. Rehak, Three-Dimensional Analytical Solution of the Laplace Equation Suitable for Semiconductor Detector Design, IEEE Trans. on Nucl. Sci., 43, 256-265, (1996).

- [19] A. Castoldi and E. Gatti, Fast tools for 3-D design problems in semiconductor detectors, Nucl. Instr. & Meth. A377, 381 (1996).

- [20] Q.-Y. Tong and U. Gösele, Semiconductor Wafer Bonding, John Wiley & Sons, Inc., NY, 1999.