# Electronically-Controllable Floating Inductor using OMA with Enhanced Input Dynamic Range

R.K.Sharma<sup>1</sup>, R. Senani<sup>2</sup>, D. R. Bhaskar<sup>3</sup>, A. K. Singh<sup>4</sup> and S. S. Gupta<sup>5</sup>

<sup>1</sup> Electronics and Communication Engineering Department, Ambedkar Institute of Technology, Geeta Colony, Delhi-INDIA, 21.ravindra@gmail.com

<sup>2</sup>Division of Electronics and Communication Engineering, Netaji Subhas Institute of Technology, Sector-3, Dwarka, New Delhi- INDIA, senani@nsit.ac.in, \*Corresponding Author

<sup>3</sup> Department of Electronics and Communication Engineering, Faculty of Engineering and Technology, Jamia Millia Islamia, New Delhi- INDIA, bhaskar.ec@jmi.ac.in

<sup>4</sup> Department of Electronics and Communication Engineering, R.D. Engineering College, Ghaziabad, UP- INDIA, abdheshks@yahoo.com

<sup>5</sup> Ministry of Commerce and Industry, Government of India, Udyog Bhawan, New Delhi- INDIA, ss.gupta@nic.in

#### Abstract

Recently a new formulation for realizing a floating inductance (FI) using an OMA, which takes into account the dominant pole of the op-amp employed in the OMA, without requiring any external capacitor was proposed. The proposition, however, suffered from a limited inputdynamic-range of operation owing to limited open-loop signal handling capability of the op-amp used. In this paper we propose an improved FI formulation with increased input signal handling capability. The electronically controllable floating inductance feature of the resulting circuit has been shown by replacing all the building blocks of the FI formulation by their CMOS counterparts. The workability of the proposed FI has been demonstrated by PSPICE simulations.

#### 1. Introduction

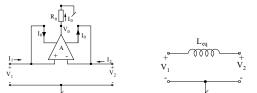

Importance and useful applications of operational mirrored amplifier (OMA) as a four terminal building block have been successfully demonstrated by several previous researchers; see for instance [1]-[11]. For a detailed account of these varieties of OMA applications reader is referred to [1]-[11] and references cited therein. In a previous communication [12] we proposed an FI formulation, the CMOS version of which was completely resistor-less and capacitor-less. The basic schematic of FI formulation [12] is reproduced here in Fig.1. The proposition, however, suffered from an inferior dynamic range of input signal handling capability.

Fig. 1. The basic schematic of FI formulation [12]

In this paper, we present a new improved FI formulation which offers an extended dynamic range over the previous FI formulation.

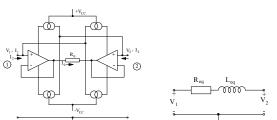

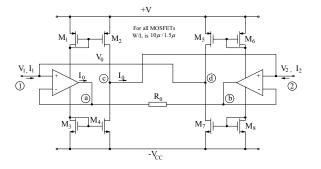

## 2. The Proposed Floating Inductance Configuration

The proposed configuration has been detailed out in Fig. 2 where Fig. 2(a) shows the basic schematic using a composite-OMA and its equivalent and Fig. 2(b) shows its complete transistor level realization. In the circuit of Fig. 2(b), the op-amp employed in the circuit senses the voltages  $V_1$  and  $V_2$  and creates a current  $I_0$  flowing into  $R_0$  proportional to  $(V_1-V_2)$ . The current mirrors  $M_1-M_8$  create a replica of this output currents between the junction 'a' and 'b'.

(a). Basic schematic and its equivalent

<sup>(</sup>b). Transistor level realization employing op-amp [9]

### Fig. 2. The proposed FI

By assuming the open loop voltage gain of the op-amp

$$A(s) = \frac{A_0 \omega_p}{s + \omega_p} \cong \frac{\omega_t}{s}; \text{ for } \omega >> \omega_p \tag{1}$$

and taking  $A_0 \omega_p = \omega_l$ , where  $\omega_l$  represents the gainbandwidth product of the op-amp, we can write the voltage at node 'a' and at node 'b' respectively

$$V_{01}(s) = \frac{V_1 A(s)}{A(s) + 1}$$

and

$$V_{01}(s) = \frac{V_2 A(s)}{V_2 A(s)}$$

(2)

(3)

$V_{02}(s) = \frac{V_2 A(s)}{A(s) + 1}$

which in turn, gives current through R<sub>0</sub> as

$$I_0(s) = \frac{V_1 - V_2}{R_0 \left(1 + \frac{s}{\omega_t}\right)}$$

<sup>(4)</sup>

which realizes a lossy-inductance<sup>1</sup> (series R-L) element of which inductance and lossy resistance part can be extracted from (4) as

(1)

(7)

$$R_L + sL_{eq} = R_0 + s\left(\frac{R_0}{\omega_t}\right) \tag{5}$$

Thus, the circuit simulates floating impedance which represents a lossy-FI with inductance  $(L_{eq})$  value

$$L_{eq} = \frac{R_0}{\omega_i}$$

(6)

and the associated series  $R_{\rm L}$  value as

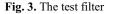

$R_L = R_0$ For an entirely CMOS version, the resistor R<sub>0</sub> may be replaced by a voltage-controlled-resistance (VCR) such as the one shown here in Fig.4 and is a modified version of proposition of [13], simulating an equivalent resistance of value

$$R_{eq} = \frac{1}{k_0 \left( V_n - V_p - V_{Tn} + V_{Tp} \right)}$$

(8)

where  $k_0 = \mu(W/L)C_{OX}$  is the transconductance,  $V_{Tn}$ ,  $V_{Tp}$  are threshold voltages of nMOS and pMOS respectively and V<sub>n</sub>, V<sub>p</sub> are the control voltages given to the gates of nMOS and pMOS transistors for controlling the equivalent resistance, thus, realized. With this modification, the Leq is, thus, given by

$$L_{eq} = \frac{1}{k_0 (V_n - V_p - V_{Tn} + V_{Tp})\omega_l}$$

(9)

from which it is seen that the inductance value can be electronically controlled by varying the external control voltage V<sub>n</sub> and/or V<sub>p</sub>.

$$R_{0} = \frac{1}{\left(\frac{W}{L}\right) \mu_{n} C_{OX} \left[ (V_{n} - V_{T_{n}}) - 0.4 (V_{p} - V_{T_{p}}) \right]}$$

(10)

#### **3. SPICE Simulation results**

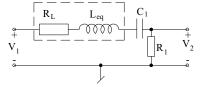

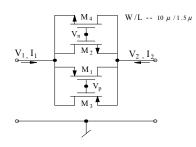

To check the workability of the proposed structure of Fig. 2, a simple BPF shown in Fig. 3 was set up, where the series R-L section was simulated by the proposed circuit. A selfcompensated CMOS op-amp from [9] was employed, as was also done in [12], for testing the validity of the proposed idea. The CMOS VCR of Fig.4 was used in place of R<sub>0</sub> for testing the complete CMOS formulation functionality of the proposition. The DC power supplies were ±5Volts. Level-7 process parameters for MOSFETs were used in PSpice simulations.

Fig. 4. A modified version of VCR of [13]

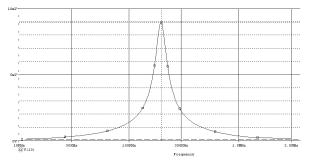

The VCR of Fig. 4 was designed to have equivalent resistance of value  $625 \Omega$  for which the control voltages at V<sub>p</sub> and  $V_n$  in the CMOS VCR were -0.9V and 2.5V respectively. The amplitude response of the filter circuit is shown in Fig. 5. In frequency response of Fig. 5(a) a fixed  $R_0$  equal to 625  $\Omega$  has been employed whereas in the frequency response of Fig. 5(b) the R<sub>0</sub> has been replaced by the equivalent value of VCR of Fig.4. These identical frequency responses confirm complete CMOS formulation functionality of the proposition. These results, thus, confirm the workability of the proposed circuit.

(a). With  $R_0$  employed as a fixed resistor equal to  $625 \Omega$ .

(b). With R<sub>0</sub> replaced by the equivalent value of VCR of Fig.4.

Fig. 5. The amplitude response of the filter of Fig. 3.

<sup>&</sup>lt;sup>1</sup> It is interesting to note that the FI formulation [12], as mentioned therein, also turns out to be a series R-L when opamp is replaced by its one-pole model rather than the integratormodel approximation.

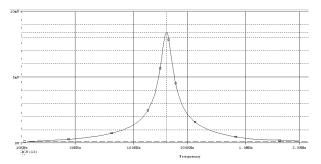

#### 4. Comparisons of input dynamic range

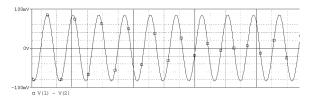

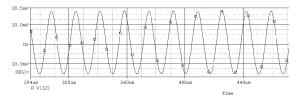

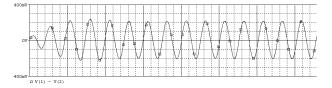

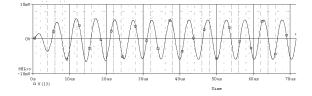

The inductance realization in our earlier proposition of [12] employed operational amplifier in open-loop and hence, had limited input signal voltage handling capability. This was equal to maximum of linear differential input range of the op-amp typically of the order of fraction of milivolts. With this present modified version of the FI, due to existence of the negative feedback arrangement, the dynamic-range of the input signal increases significantly. In order for measuring this and comparing the same with the input signal handling capability of the new proposition of this paper a fixed R<sub>0</sub> (not the CMOS VCR) was used in both propositions (the [12] and the proposition of this paper). The maximum signal voltages across the floating inductors in the band-pass filters and the corresponding undistorted output signal at the output for the two propositions ([12] and the present one) have been shown in Fig. 6. This clearly proves the superiority of the present FI formulation over the previous one [12].

(a). Maximum signal voltage between FI of the band-pass filter in [12]

(b). Maximum undistorted signal output of the band-pass filter in [12]

(c). Maximum signal voltage between FI of the band-pass filter in the present proposition

(d). Maximum undistorted signal output of the band-pass filter in the present proposition

Fig. 6. The comparison of the signal handling capability of the proposed OMA-FI configuration with that of [12]

The VCR of Fig. 4 also has a very small dynamic range and, thus, when used in the present OMA-FI formulation limits the signal handling capability of the formulation severely. An improved CMOS  $R_0$ , with greater signal handling capability, when substituted in the FI realization of Fig. 2 will make the present proposition a fully CMOS type having significantly improved dynamic response.

#### 5. Discussions and Concluding remarks

In an earlier paper the authors have presented a single OMAbased FI formulation, however, the circuit suffered from the drawback of a very limited input signal handling capability. In this paper, we have presented a new improved formulation which has advantage of enhanced input signal handling capability. With the resistance employed in the circuit replaced by a floating CMOS VCR it becomes possible to control the inductance value electronically. Like its predecessor of [12] the new circuit can also be implemented in CMOS. SPICE simulation-results have been presented that confirm the workability of the proposed circuit.

#### 6. Acknowledgements

This work was partly supported from RPS grants of AICTE, MHRD, Government of India for ASPR lab at Ambedkar Institute of Technology, Delhi and performed in collaboration with ASPR lab, NSIT, New Delhi, India.

#### 7. References

- G. Normand, "Floating impedance realization using a dual operational mirrored amplifier", *Elect. Lett.*, vol. 22, no. 10, pp. 521-522, 1986.

- [2] C. Toumazou, and F. J. Lidgey, "Analog IC Design: The current mode approach", Peter Peregrinus Lt., 1990.

- [3] J. Malhotra, and R. Senani, "Class of floating generalized positive/negative immittance converters/inverters realized with operational mirrored amplifier", *Elect. Lett.*, vol. 30, no. 1, pp. 3-5, 1994.

- [4] J. Malhotra, and R. Senani, "Minimal realizations of a class of operational-mirrored-amplifier-based floating impedance", *Elect. Lett.*, vol. 30, no. 14, pp. 1113-1114, 1994.

- [5] S. Ozoguz, and C. Acar, "Single-input and three-output current-mode universal filter using a reduced number of active elements. *Elect. Lett.*, vol. 34, no. 7, pp. 605-606, 1998.

- [6] R. Senani, "Floating GNIC/GNII configuration realized with only a single OMA", *Elect. Lett.*, vol. 31, no. 6, pp. 423-425, 1995.

- [7] G. Wilson, and P. K. Chan, "Novel voltage-controlled grounded resistor", *Elect. Lett.*, vol. 25, no. 25, pp. 1725-1726, 1989.

- [8] S. Minaei, O. Cicekoglu, H. Kuntman, and S. Turkoz, "Electronically tunable active-only floating inductance simulation", *Int. Journal of Electronics*, vol. 89, no. 12, pp. 905-912, 2002.

- [9] P. E. Allen, and D. R. Holberg, "CMOS Analog Circuit Design", Holt Rinehart and Winston Inc., 1987.

- [10] O. Saaid, and A. Fabre, "Class AB current-controlled resistor for high performance current mode applications", *Elect. Lett.*, vol. 32, no. 1, pp. 4-5, 1996.

- [11] M. T. Abuelma'atti, "Active-only immittance simulators", *Frequenz*, vol. 57, no. 1-2, pp. 8-11, 2003.

[12] R. K. Sharma, R. Senani, D. R. Bhaskar, A. K. Singh and S.

- [12] R. K. Sharma, R. Senani, D. R. Bhaskar, A. K. Singh and S. S. Gupta, "Electronically-controllable Floating Inductor Using Operataional mirrored Amplifier", *JCSC*, vol.18, no.1, pp. 59-66, 2009.

- [13] S. M. Al-Shahrani, "CMOS wideband auto-tuning phase shifter circuit", *Elect. Lett.*, vol. 43, no. 15, pp. --, 2007.