# A new CMOS voltage reference scheme based on Vthdifference principle

Luis Toledo, Walter Lancioni, Pablo Petrashin, Carlos Dualibe, Carlos Vázquez

Laboratorio de Microelectrónica, Facultad de Ingeniería

Universidad Católica de Córdoba

Córdoba, Argentina

Email: toledo@uccor.edu.ar

Abstract— a new CMOS voltage reference, which takes advantage of the temperature dependence of NMOS and PMOS threshold voltages, is presented. Due to the circuit architecture the mobility factor is completely cancelled. It does not use resistors and all transistors works in strong inversion. The circuit is simple, opamp-less and can be implemented in a standard CMOS process. When the input power supply changes from 1.8V to 2.1V and the temperature changes from -20 to  $80^{\circ}\text{C}$ , simulations for the reference circuit using the proposed architecture shows an output voltage of 1.184V and a  $T_{\rm FC}$  of  $100~\rm ppm/^{\circ}C$ .

#### I. Introduction

References are intrinsically required by circuits such as biasing circuits, digital-to-analog converters, analog-todigital converters and operational amplifiers. These building blocks are the basic elements that make up phones, computers and many other popular electronics products. For this reason, much research has been conducted and is still continuing in order to improving reference circuits. Generally speaking, reference circuits based on BJT technology have put emphasis in improving accuracy by implementing second or higher order temperature compensation schemes [1][2], while the development of CMOS circuits has focused more on low voltage applications [3][4]. The design objective of this work is to propose a novel structure that can be implemented in low cost CMOS technology and with performance comparable to the performance of the bandgap voltage reference. The proposed CMOS reference circuit has the potential to establish a reference voltage for analog-to-digital and digital-to-analog converters and to provide a biasing voltage for other circuits that is insensitive to the power supply and temperature. Section II provides a detailed analysis of the temperature characteristics of MOS transistors, which are the basic elements of the reference circuit used in this work. Section III has a more practical engineering orientation. First, the proposed voltage reference is presented. The concept of the reference circuit is described and analyzed to derive the

equations governing its functioning. An example of the proposed design and simulation results are presented in Section IV and the conclusions are given in Section V.

#### II. THEORY REVIEW

# A. Temperature dependence of MOS transistors

To successfully design a CMOS current/voltage reference, one must have a thorough understanding of the temperature behavior of MOS transistors. The threshold voltage and the mobility are the main temperature-dependent parameters. As the temperature increases, both the threshold voltage and the mobility decrease. But the decrease of  $V_{TH}$  and the decrease of  $\mu$  have opposite effects on the drain current; a lower threshold voltage tends to increase the drain current, but a lower mobility tends to decrease it. It has been shown in [5] that the threshold voltage decreases approximately linearly with an increase in temperature. The temperature dependency of the threshold voltage usually used is:

$$V_{TH}(T) = V_{TH}(T_0) - \alpha_{VT}(T - T_0)$$

(1)

where  $\alpha_{VT}$  is the temperature coefficient of the threshold voltage. The value of  $\alpha_{VT}$  varies from 1mV/°C to 4mV/°C, it is technology dependent and differs from a NMOS to a PMOS transistor. On the other hand, a general expression which is used to describe the temperature dependency of the mobility is given by:

$$\mu(T) = \mu(T_0) \left(\frac{T}{T_0}\right)^{-m} \tag{2}$$

where  $\mu(T_0)$  is the mobility at the reference temperature,  $T_0$ , and  $1 \le m \le 2.5$ .

# B. Mobility cancellation

Since mobility is a nonlinear function of temperature, it is difficult to build voltage references that rely on MOS

3840

This work was supported by the Research Secretary, Universidad Católica de Córdoba and in part by the SeCyT under Grant BID 1728/OC-AR PAV 2003-076-0

characteristics [3]; it is not easy to obtain a low TC reference voltage by canceling mobility with a linear voltage (Vth). This is the same problem as in the traditional bandgap voltage reference where a PTAT voltage is used to cancel a nonlinear voltage of V<sub>BE</sub>. It is obvious that the curvature comes from the nonlinear temperature dependence of mobility. Reference [6] uses a voltage that is inversely proportional to mobility to cancel it. Nevertheless, the mobility factor can be totally cancelled if transistors NMOS are not combined with the PMOS in a same branch. This mobility cancellation idea is intuitive. While the intuition has the advantage of understanding the operation of a circuit without have to describe it in equations, mathematical analysis can find the exact relationship among variables from equations. This intuitive idea is developed into a voltage reference design. In the mathematical analysis of the circuit, it is revealed how the mobility is eliminated to avoid the temperature dependency contribution on Vref caused by it.

#### III. CIRCUIT IMPLEMENTATION

For voltage references in a CMOS process, one obvious design method is to emulate that of the well known bipolar reference designs. However, independent bipolar transistors are not available in a standard CMOS process. Most previous CMOS voltage references use the bandgap architecture and their performances are limited due to the poor performance of the well transistors in CMOS process. The CMOS bandgap voltage reference designs also suffer from the weaknesses of a large amplifier offset. There are many methods to minimize the effects of the offset voltage. In this design, the op amp is eliminated to avoid the offset, drift, chip area and power consumption associated with it. In this section, a different architecture for voltage references is proposed. The proposed architecture is based on the threshold voltage difference principle [6] [7] and no parasitic transistors are used.

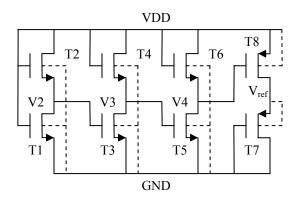

The principle of the circuit relies on two independent groups of NMOS and PMOS as shown in Fig. 1. Observe that resistors are not used and its temperature dependence is avoided [8] [9]. If the mobility is cancelled, the only dependency with the temperature comes from the threshold voltage.

For example, for the two threshold voltages  $V_{THN}$  and  $V_{THP}$  that vary in the same direction with temperature (but different in magnitude), we choose  $k_1$  and  $k_2$  so as to accomplish:

$$k_1 \frac{\partial V_{THN}}{\partial T} - k_2 \frac{\partial V_{THP}}{\partial T} = 0$$

(3)

In this way, a reference voltage is given by:

$$V_{REF} = k_1 V_{THN} - k_2 V_{THP} \tag{4}$$

Both  $V_{THN}$  and  $V_{THP}$  have negative TCs, but they are different in value. Hence, they can be subtracted with different weighting factors to form a near zero-TC output voltage. The voltage reference is fully compatible with

Fig.1. Voltage reference circuit

standard digital CMOS processes and gives moderate temperature performance.

### A. Operation

To provide a qualitative understanding of the circuit behavior, the circuit can be analyzed using a simple squarelaw MOS model. The circuit of Fig. 1 operates as follows; transistors T<sub>2</sub>, T<sub>3</sub> and T<sub>4</sub> are saturated and T<sub>1</sub> works in the triode region. The effect of supply-voltage variations is twofold. Suppose  $V_{\text{DD}}$  increases. First, since the currents of T<sub>1</sub> and T<sub>2</sub> are the same, the gate-source voltage of T<sub>1</sub> will increase proportional to the increase in V<sub>DD</sub>. Therefore the voltage V2 will also increase proportionally. Secondly, the gate-source voltage of T<sub>3</sub> increases with V<sub>DD</sub> due to its gate is connected to V<sub>2</sub>. Therefore, despite the body effect, its drain current will increase proportionally with the increase in V<sub>DD</sub>. The circuit is designed so that the required increase in current through  $T_3$  is provided by the increase in  $T_4$ 's current. As a result  $V_3$  will remain constant with changing  $V_{DD}$ . Transistors  $T_5$  and  $T_6$  (both are saturated) have to convert from a supply-independent threshold-referenced NMOS voltage (V<sub>3</sub>) relative to ground to a voltage relative to V<sub>DD</sub>. The final result is that V<sub>DD</sub>-V<sub>4</sub> will remain constant with changing V<sub>DD</sub> for a given range of values.

Transistor  $T_7$  and  $T_8$  will act as a subtractor of both  $V_{THN}$  and  $V_{THP}$  which have different weighting factors to form a reference voltage.

Due to Body effect affects the group of NMOS transistors, it is necessary to change slightly the relationship between sizes of transistors in order to reach a true independence of  $V_{\rm DD}$ . The PMOS transistors are on different wells so they are insensitive to Body effect.

#### B. Equations

It can be demonstrated that, considering body effect, the voltages  $V_2$ ,  $V_3$  and  $V_4$  are:

$$V_2 = \frac{\left(V_{DD} - V_{THN}\right)}{\delta} \left(1 - \sqrt{\frac{\beta_1}{1 + \beta_1}}\right) \tag{5}$$

$$V_{3} = \frac{\left(V_{DD} - V_{THN}\right)}{\delta} \left[1 - \frac{\sqrt{\beta_{2}}}{\delta} \left(1 - \sqrt{\frac{\beta_{1}}{1 + \beta_{1}}}\right)\right]$$

$$+ \frac{\sqrt{\beta_{2}}V_{THN}}{\delta}$$

$$V_{4} = \frac{\left(V_{DD} - V_{THN}\right)}{\delta} - \frac{\sqrt{\beta_{3}}}{\delta} \frac{\left(V_{DD} - V_{THN}\right)}{\delta}$$

$$+ \frac{\sqrt{\beta_{3}}}{\delta} \frac{\left(V_{DD} - V_{THN}\right)}{\delta} \frac{\sqrt{\beta_{2}}}{\delta} \left(1 - \sqrt{\frac{\beta_{1}}{1 + \beta_{1}}}\right)$$

$$- \frac{\sqrt{\beta_{3}}}{\delta} \frac{\sqrt{\beta_{2}}}{\delta} V_{THN} + \frac{\sqrt{\beta_{3}}}{\delta} V_{THN}$$

where  $\beta_{1} = \frac{\left(W/L\right)_{1}}{\left(W/L\right)_{2}}$ ,  $\beta_{2} = \frac{\left(W/L\right)_{3}}{\left(W/L\right)_{3}}$ , and  $\beta_{3} = \frac{\left(W/L\right)_{5}}{\left(W/L\right)_{5}}$ .

The constant  $\delta$  which accounts for the body effect is approximately 1.36 for the 1.5  $\mu m$  AMI Technology. If the

conditions

$$\frac{\sqrt{\beta_3}}{\delta} = 1$$

and  $\frac{\sqrt{\beta_2}}{\delta} = \frac{\delta}{1 - \sqrt{\frac{\beta_1}{1 + \beta_1}}}$  are fulfilled,

then

$$V_4 = V_{DD} - \frac{\sqrt{\beta_2}}{\delta} V_{THN} \tag{8}$$

As expected, the voltage  $V_4$  is relative to the supply voltage but still a linear function of temperature. Finally, the voltage of Vref is calculated as:

$$V_{ref} = \frac{\frac{\sqrt{\beta_2}}{\delta} V_{THN} - \left(1 - \sqrt{\beta_4}\right) V_{THP}}{\sqrt{\beta_4}}$$

where  $\beta_4 = \frac{\left(W/L\right)_7}{\left(W/L\right)_9}$ . (9)

The temperature coefficient of Vref can be derived by differentiating (9) with respect to temperature and is given by:

$$\frac{\partial V_{ref}}{\partial T} = \frac{-\frac{\sqrt{\beta_2}}{\delta} \alpha_{vthn} + \left(1 - \sqrt{\beta_4}\right) \alpha_{vthp}}{\sqrt{\beta_4}}$$

(10)

where  $\alpha_{vthn}$  and  $\alpha_{vthp}$  are the temperature coefficients for the threshold voltages of a NMOS and PMOS transistors

respectively. To obtain  $\frac{\partial V_{ref}}{\partial T}=0$ , the ratio of temperature coefficients must be equal to:

$$\frac{\alpha_{vthp}}{\alpha_{vthn}} = \frac{\frac{\sqrt{\beta_2}}{\delta}}{1 - \sqrt{\beta_4}}$$

(11)

All equations show that the voltage reference and its temperature coefficient can be determined by circuit parameters.

## IV. DESIGN EXAMPLE AND SIMULATIONS RESULTS

The circuit shown in Fig. 1 was designed for realization in 1.5  $\mu m$  AMI Technology using the BSIM3v.3 MOS model. The dimensions of transistors used for simulation are indicated in table 1. Long-channel devices are chosen in order to minimize channel-length modulation effect.

| Transistors | Size [μM/μM] |

|-------------|--------------|

| T1          | 12/54.8      |

| T2          | 54.8/12      |

| Т3          | 24.5/12      |

| T4          | 12/24.5      |

| T5          | 16.3/12      |

| Т6          | 12/16.3      |

| T7          | 12/40        |

| Т8          | 40/12        |

TABLE I. DEVICE SIZES

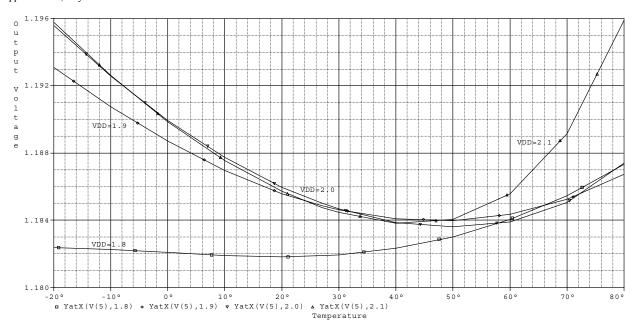

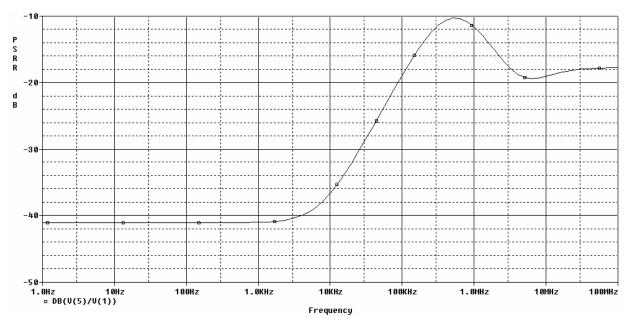

The temperature behavior is shown in Fig. 2. When the input power supply changes from 1.8V to 2.1V and the temperature changes from -20 to 80°C, simulations for the reference circuit using the proposed architecture shows an output voltage of 1.184V and a *TFC* of 100 ppm/°C. The PSRR for a 1.9V supply voltage, without using a filtering capacitor to improve the high-frequency behavior, is shown in Fig. 3.

### V. CONCLUSIONS

A novel CMOS reference voltage scheme was presented. A startup circuit commonly present in other configurations is not necessary. In standard digital CMOS technologies, models for the resistors may not be available or reliable. For this reason it is advantageous to avoid them. The proposed circuit does not use resistors. This reference is suitable for standard low-cost CMOS technologies since additional fabrication steps are not needed. The devices operate in strong inversion, for which accurate device models are usually available, simplifying the design procedure, especially in digital CMOS technologies. Mobility compensation is not necessary. Since the NMOS transistors are not combined in the same branch with PMOS transistors the mobility factor is completely cancelled.

#### REFERENCES

- Inyeol Lee, Gyundong Kim, Wonchan Kim, "Exponential curvaturecompensated BiCMOS bandgap references," IEEE Journal of Solidstate, vol 29, no.11, pp. 1396-1403, November 1994.

- [2] G.A. Rincon-Mora and P.E. Allen, "A 1.1 V Current Mode and Piecewise Linear Curvature Corrected Bandgap Reference", IEEE Journal of Solid-state, vol.33, no.10, pp.1551-1554, October 1998.

- [3] Ka Nang Leung, and Philip K. T. Mok, "A CMOS voltage reference based on weighted  $\Delta V_{GS}$  for CMOS low-dropout linear regulators", IEEE Journal of solid-state circuits, vol. 38, no. 1, pp. 146-150, January 2003.

- [4] Laleh Najafizadeh, and Igor M. Filanovsky, "Towards a sub-1V CMOS voltage reference", IEEE ISCAS 2004, Canada, pp. I-53 – I-56, May 2004.

- [5] I.M. Filanovsky, and A. Allam, "Mutual compensation of mobility and threshold voltage temperature effects with application in CMOS circuits", IEEE Transactions on Circuits and Systems-I, vol. 48, no. 7, pp. 876-883, July 2001.

- [6] Y. Dai, D.T. Comer, D.J. Comer, and C.S. Petrie, "Threshold voltage based CMOS voltage reference", IEE Proc.-Circuits Devices Syst., vol. 151, no. 1, pp. 58-62, February 2004.

- [7] I.M. Filanovsky, F. Fang, A. Allam, and K. Iniewsky, "0.6-V Supply Voltage References for CMOS technology based on thresholdvoltage-difference architecture", IEEE international symposium on circuits and systems, 2005. ISCAS 2005. Vol. 5, page(s) 4249-4252, 23-26 May 2005.

- [8] H. J. Oguey, D. Aebisher, "CMOS current reference without resistance", IEEE Journal of Solid-state, vol 32, no.7, pp. 1132-1135, July 1997.

- [9] Arne E. Buck, Charles L. Mcdonald, Stephen H. Lewis, T.R. Viswanathan, "A CMOS bandgap reference without resistors," IEEE Journal of Solid-state, vol 37, no.61, pp. 81-83, January 2002.

Fig.2. Output voltage vs. Temperature for different VDD

Fig.3. PSRR of the proposed voltage reference for a 1.9V power supply