# Accounting for Quantum Effects and Polysilicon Depletion in an Analytical Design-Oriented MOSFET Model

Matthias Bucher mbucher@elab.ntua.gr

National Technical University of Athens (NTUA), Athens, Greece

Jean-Michel Sallese jean-michel.sallese@epfl.ch

Swiss Federal Institute of Technology (EPFL), Lausanne, Switzerland

Christophe Lallement lallem@erm1.u-strasbg.fr

# ERM-PHASE / ENSPS, Strasbourg, Illkirch, France Abstract

An analytical MOSFET model is presented that accounts for energy quantization in inversion charge and depletion in the poly gate. The model consistently describes effects on charges, transcapacitances, drain current and transconductances in all regions of operation, depending on five physical device parameters and bias conditions. Comparison to experimental data is provided and parameter extraction briefly discussed. The model offers manageable equations providing insight into the physical phenomena, thereby supporting analog circuit design practice as well as efficient circuit simulation.

## 1 Introduction

Depletion in the polysilicon gate and energy quantization of the mobile carriers drastically reduce the performance of deep submicron CMOS technology. Quantum mechanical (QM) effects and polydepletion (PD) delay the formation of the inversion layer with applied gate bias. The most commonly observed changes in device characteristics are increased threshold voltage [1], decreased slope of inversion charge versus gate voltage resulting in decreased gate capacitance, as well as reduced drain current (e.g. [2]-[4]).

The surface-potential based charge-sheet models offer a suitable basis for MOSFET modelling. Depletion in the polysilicon gate can be included using the depletion approximation [3]. A suitable description of quantum mechanical effects according to Van Dort e.a. [1] has been used in the context of surface-potential based models [2][5]. Even if approximations to relieve the computational burden are made [5], the surface-potential based models do usually not offer an easy insight into the physical phenomena and their interactions.

Manageable expressions for device characteristics in terms of process parameters and bias conditions are very desirable for analog IC design. An alternative to purely surface potential based models is offered by the "charge linearization" models [6]-[9], following the "EKV" [6] model approach. The charge linearization models are charge-sheet models that offer an analytical approximation to the surface-potential based model, retaining the essence of the physical phenomena required for precise analog IC design while offering increased analytical versatility and computational efficiency.

We present the essentials of simultaneously accounting for PD and QM effects in the context of the charge linearization following [9] and using the Van Dort model to account for QM effects. Once the local charges, now including QM and PD effects, are known, a full model for charges, transcapacitances, drain current and transconductances can be formulated for all regions of operation of the MOSFET, from weak to moderate and strong inversion as well as from conduction to saturation [8]. The new analytical model is compared to experimental data. Parameter determination is briefly discussed.

# 2 Analytical model formulation

The relationship between voltages and charges across the MOS structure is established supposing uniform doping concentration and complete depletion in gate and substrate [9],

$$V_G = V_{FB} + \Psi_s - \frac{Q_C'}{C_{ox'}} + \frac{1}{\gamma_p^2} \left(\frac{Q_C'}{C_{ox'}}\right)^2$$

(1)

where  $V_G$ ,  $V_{FB}$  and  $\Psi_s$  are the gate voltage, flat-band voltage and surface potential,  $Q_C'$  is the total charge in the semiconductor,  $C_{ox}' = \varepsilon_{ox}/T_{ox}$  is the oxide capacitance. The gate and substrate factors are defined as  $\gamma_{p(s)} = \sqrt{2q_e\varepsilon_{si}N_{p(s)}}/C'_{ox}$  related to the poly and substrate doping levels  $N_{p(s)}$ , and other symbols have their usual meanings. Solving (1), the inversion charge  $Q_i' = Q_C' - Q_B'$  (where  $Q_B' = -\gamma_s C_{ox}' \sqrt{\Psi_s}$  is the depletion charge) is obtained in terms of  $V_G$  and  $\Psi_s$ . Linearizing  $Q_i'$  in terms of  $\Psi_s$  leads to a versatile analytical model accounting for PD effects. Even if this linearization is performed under strong inversion conditions – where PD effects are most notable – the model remains applicable at all levels of inversion over a wide range of device parameters with excellent accuracy.

However, QM effects lead to a considerably increased surface potential compared to the classical solution [2], particularly in strong inversion. The strong inversion condition  $\Psi_s \cong 2\phi_F + V_{ch}$ , where  $\phi_F$  is the bulk Fermi potential and  $V_{ch}$  the channel potential, is no longer directly applicable. Therefore, a modification of (1) is necessary to account for QM effects, considering the increase of the surface potential  $\Psi_s^{qm} = \Psi_s + \Delta \Psi_s$ . According to Van Dort [1], energy quantization increases the energy gap,

$$\Delta E_g \cong \kappa \cdot \left| \frac{Q_C'}{C_{ox'}} \right|^{2/3} \qquad \kappa = \frac{13}{9} \cdot \kappa_Q \cdot \left[ \frac{C_{ox'}^2}{4kT\varepsilon_{si}} \right]^{1/3}$$

(2)

where  $\Delta E_g$  is expressed in Volt and  $\kappa_Q$  is a constant [1]. The corresponding increase of the surface potential in strong inversion may be estimated as  $\Delta \Psi_s \cong \Delta E_q$  [5][8]. Expanding  $\Delta \Psi_s$  to second order in terms of  $Q_C$  around  $Q_{B0} \cong -\gamma_s C_{ox} / 2\phi_F + V_{ch}$ , we have

$$\Delta \Psi_{s} \cong p + q \cdot \left| \frac{Q_{C'}}{C_{ox'}} \right| - r \cdot \left( \frac{Q_{C'}}{C_{ox'}} \right)^{2} \qquad where \begin{cases} p = (2\kappa/9)[Q_{B0}'/C_{ox'}]^{2/3} \\ q = (8\kappa/9)[Q_{B0}'/C_{ox'}]^{-1/3} \\ r = (\kappa/9)[Q_{B0}'/C_{ox'}]^{-4/3} \end{cases}$$

(3)

where p, q and r are the expansion factors depending on  $\kappa$ . Eqn. (1) is now solved for  $Q_C'$  using  $\Psi_s^{qm}$  containing the additional charge terms from the expansion (3), as

$$\frac{Q_{C}'}{C_{ox}'} = \frac{1 + q - \sqrt{(1+q)^2 + 4(\gamma_p^{-2} - r)(V_G - V_{FB} - \Psi_s - p)}}{2(\gamma_p^{-2} - r)}.$$

(4)

The inversion charge density  $Q_i'$  is then obtained as a function of  $V_G$ ,  $\Psi_s$  and the other auxiliary variables and process parameters. In the above, p simply is a shift in flatband voltage  $\Delta V_{FB} = p$  due to QM effects. Linearizing the inversion charge versus surface potential, the charge linearization factor  $n_Q \equiv -[dQ_i'/d\Psi_s]/C_{ox}'$  is obtained. The factor  $n_Q$  does directly affect inversion charge and drain current [8][9]. Modified expressions for the pinch-off voltage  $V_P$ , and the slope factor  $n_v \equiv [dV_P/dV_G]^{-1}$ , both related to the

substrate and gate effects, are obtained. While  $n_v$  is not directly used in the analytical model, it is employed for parameter extraction and has further practical importance; a useful approximation is  $V_P \cong (V_G - V_{TO})/n_v$ , where  $V_{TO}$  is the threshold voltage. These expressions are not detailed here due to limited space. Note that all model expressions correctly revert to their counterparts in [9] if QM effects are negligible.

As a consequence, the new model for charges and drain current is obtained through integration of inversion charge density along the channel. Transcapacitances and transconductances are obtained as their partial derivatives [8][9], where QM and PD effects are now accounted for consistently in all model expressions. In particular, the charges model is then further exploited to model mobility dependence on charges [4][8].

# 3 Experiment and discussion

The model parameters to be determined are the following:  $V_{FB}$ ,  $2\phi_F$ ,  $C_{ox}'$ ,  $\gamma_s$  and  $\gamma_p$ , or equivalently  $T_{ox}$ ,  $N_s$ ,  $N_p$  for the latter three. Parameter determination uses an original scheme involving DC measurements at constant current as well as CV characteristics. Devices are from a standard  $0.25\mu m$  CMOS technology with a physical  $T_{ox}$  of 5nm.

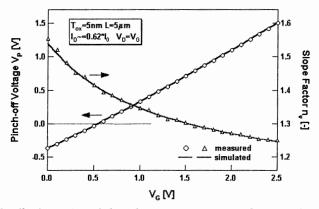

In Fig. 1, the analytical expressions for the pinch-off voltage  $V_P$  and the slope factor  $n_v$  are compared to the measurements obtained from the constant current technique [8][10][11], where devices are biased in moderate inversion at a constant level of inversion. Model parameters are adjusted so that  $V_P$ ,  $n_v$  and the transcapacitances characteristics in Fig. 2 are simultaneously and correctly fitted. The slope factor  $n_v$  as well as the transcapacitances, all involving derivatives, are particularly sensitive to bias conditions and parameter values, thus helping to obtain the best set of physical device parameters. Note that the slope factor  $n_v$  increases due to both QM and PD effects; the weak inversion slope  $S = 2.3 \cdot n_v \cdot U_T$  [8] is degraded. The transconductance-to-current ratio, an important quantity in analog IC design, is degraded in weak inversion due to both QM and PD effects.

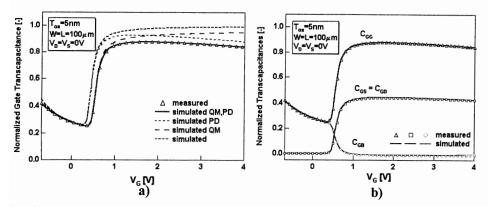

The gate capacitance of an n-channel device from depletion to strong inversion is shown in Fig. 2 a). The simulated curves correspond to the analytical model, including QM and PD effects individually, and the final result including both contributions. The value of the gate capacitance corresponds to the physical oxide thickness.

**Fig. 1:** Pinch-off voltage  $V_P$  and slope factor  $n_v$  versus gate voltage, analytical model (lines) including PD and QM effects, compared to measurements (markers) of an n-channel device. The measurement is performed at constant current in moderate inversion.

**Fig. 2:** Transcapacitances versus gate voltage compared to measurements (markers); a) gate capacitance, model with QM/PD effects (line); QM and PD effects separately; model without QM/PD effects (dashed), b) transcapacitances using the full QM/PD model.

In Fig. 2 b), other transcapacitances for the same device show excellent agreement between measurement and simulation. The linearization factor  $n_Q$  is responsible for the reduction of gate capacitance (and transconductance) observed mainly in strong inversion.

### 4 Conclusions

In summary, the extension of an analytical circuit simulation model to account for the combined effects of polydepletion and energy quantization has been presented. The charge linearization scheme leads to manageable analytical expressions offering insight into the physical phenomena. All device characteristics are affected in a consistent manner, depending simply on five device parameters, and bias conditions. Model parameter extraction is thus considerably simplified, while the accuracy of the model fits is excellent for all bias conditions. The new charges model now accounting for polydepletion and quantum effects is then used as the basis for a complete compact MOSFET model for IC design and simulation using deep submicron CMOS technologies.

#### Acknowledgment

The first author wishes to acknowledge W. Grabinski for performing the CV measurements, F. Krummenacher and C. Enz for helpful discussions and Y. Papananos for his support.

#### References

- [1] M. Van Dort, P. Woerlee, A. Walker, Solid State Electronics, Vol. 37, N° 3, pp. 411-414, 1994.

- [2] R. Rios, N. Arora, C.-L. Huang, N. Khalil, J. Faricelli, L. Gruber, IEDM Tech. Dig., 1995, pp. 937-940.

- [3] C.-L. Huang, N. D. Arora, *IEEE Trans. ED*, Vol. 40, N° 12, pp. 2330-2337, Dec. 1993.

- [4] T. Janik, B. Majkusiak, *IEEE Trans. ED*, Vol. 45, N° 6, pp. 1263-1271, June, 1998.

- [5] G. Gildenblat, T. L. Chen, P. Bendix, *Electron. Lett.*, Vol. 36, N° 12, pp. 1072-1073, June 2000.

- [6] C. C. Enz, F. Krummenacher, E. A. Vittoz, Analog Int. Circ. Signal Proc. J., Vol. 8, pp. 83-114, 1995.

- [7] A. I. A. Cunha, M. C. Schneider, C. Galup-Montoro, *IEEE J. Solid-State Circuits*, Vol. 33, N° 10, pp. 1510-1519, 1998.

- [8] M. Bucher, Ph. D. Thesis No. 2114 (1999), Swiss Federal Institute of Technology (EPFL).

- [9] J.-M. Sallese, M. Bucher, C. Lallement, Solid State Electronics, Vol. 44, N° 6, pp. 905-912, 2000.

- [10] M. Bucher, C. Lallement, C. Enz, Proc. IEEE Int. Conf. on Test Structures (ICMTS' 96), Vol. 9, pp. 145-150, March 1996.

- [11] C. Lallement, M. Bucher, C. Enz, Solid State Electronics, Vol. 41, N° 12, pp. 1857-1861, 1997.