# Adaptive Equalization Architecture Using Distributed Arithmetic for Partial Response Channels

Sorawat Chivapreecha, *Student Memeber*, IEEE, Aungkana Jaruvarakul, Nivat Jaruvarakul, and Kobchai Dejhan, *Senior Memeber*, IEEE

Abstract — This paper proposes a design and implementation of transversal adaptive digital filter using LMS (Least Mean Squares) adaptive algorithm. The filter structure is based on Distributed Arithmetic (DA), which is able to calculate the inner product by shifting, and accumulating of partial products and storing in look-up table, also the desired adaptive digital filter will be multiplierless filter. In addition, the hardware implementation uses VHDL (Very high-speed integrated circuit Hardware Description Language) and synthesis using FLEX10K Altera FPGA (Field Programmable Gate Array) as target technology and uses Leonardo Spectrum and MAX+plusII program for overall development. The results of this design are shown that the speed performance and used area of FPGA. The experimental results are presented to demonstrate the feasibility of the desired adaptive digital filter..

Index Terms — LMS Algorithm, Adaptive Digital Filter, Distributed Arithmetic, FPGA.

# I. INTRODUCTION

Adaptive digital filters are widely used in the area of signal processing such as echo cancellation, noise cancellation, channel equalization and beamforming. The necessity of hardware implementation requires various of performances such as high speed, low power dissipation and good convergence characteristics. However, generally for design of adaptive digital filters need for fast multiplication and many multipliers. These multipliers will decrease the speed of processing time since the multiplying stage is consumption process and uses large silicon area in VLSI design. Also, this paper proposes a design of distributed arithmetic structure for adaptive digital filter.

Distributed arithmetic (DA) digital filter architecture was first proposed by Peled and Liu in 1974 [1].

S. Chivapreecha and K. Dejhan are with the Faculty of Engineering and Research Center for Communication and Information Technology, King Mongkut's Institute of Technology Ladkrabang, Bangkok, 10520, Thailand (e-mail: {sorawat, kobchai}@telecom.kmitl.ac.th).

A. Jaruvarakul is with the Department of Industrial Electrical Technology, Faculty of Engineering, King Mongkut's Institute of Technology North Bangkok, Bangkok 10800, Thailand

N. Jaruvarakul is with the Department of Computer Engineering, Faculty of Engineering, Rajamangala University of Technology Phra Nakhon, Bangkok 10800, Thailand

The DA is a direct method for sum of products operations, partial products can pre-compute by difference equation and storing in look-up table contained in memory, input signals is used for addressing. The product can be computed by scaling accumulate of partial products from memory, therefore, multipliers do not necessary for this method, the desired digital filter is multiplierless. Generally, adaptive digital filter has its basis on the widely used LMS adaptive algorithm, originally proposed by Widrow and others [2], it is the popular algorithm for adaptive digital filter. Cowan and others [3] proposed the application of DA for adaptive digital filter with offset binary coding, which is not suitable for the DA adaptive algorithm because the convergence speed of this method degrades extremely. However, this paper proposes the distributed arithmetic adaptive digital filter generalizing with two's complement representation which corresponds to original ideas of Peled and Liu and much more suitable for its implementation.

## II. LMS ADAPTIVE ALGORITHM BASED DA

The digital FIR filter is important component of state-ofthe-art partial response signaling maximum likelihood (PRML) detection for magnetic hard disk drive (HDD) read channels.

Consider the Nth order of FIR (Finite Impulse Responses) digital filter with input signal vector  $\mathbf{S}(k)$  and N-taps coefficients vector  $\mathbf{W}(k)$  can be expressed as;

$$\begin{aligned} \mathbf{S}(k) &= \left[ s(k), \, s(k\text{-}1), \, ..., \, s(k\text{-}N\text{+}1) \right]^T \\ \text{and} \\ \mathbf{W}(k) &= \left[ w_0(k), \, w_1(k), \, ..., \, w_{N\text{-}1}(k) \right]^T \end{aligned} \tag{1}$$

An output signal of FIR digital filter can be expressed as

$$y(k) = \mathbf{S}^{T}(k)\mathbf{W}(k) = \mathbf{F}^{T}\mathbf{A}^{T}(k)\mathbf{W}(k)$$

(3)

Defining an address matrix A(k) and scaling vector F as;

$$\mathbf{A}(\mathbf{k}) = \begin{bmatrix} b_0(\mathbf{k}) & \cdots & b_0(\mathbf{k} - \mathbf{N} + 1) \\ b_1(\mathbf{k}) & \cdots & b_1(\mathbf{k} - \mathbf{N} + 1) \\ \vdots & \ddots & \vdots \\ b_{B-1}(\mathbf{k}) & \cdots & b_{B-1}(\mathbf{k} - \mathbf{N} + 1) \end{bmatrix}^{T}$$

(4)

$$\mathbf{F} = [-2^0, 2^1, \dots, 2^{-(B-1)}]^T$$

(5)

where B is input signal wordlength, the relationship between input signal and address matrix can be shown as follows:

$$s(k) = [b_0(k), b_1(k), ..., b_{B-1}(k)] \mathbf{F}$$

(6)

From Eq. (4), the address vector will be defined as;

$$\mathbf{A}_{vi}(k) = [b_i(k), b_i(k-1), ..., b_i(k-N+1)]^T$$

$$i = 0, 1, ..., B-1$$

(7)

Digital equalization for PRML channels uses least mean square (LMS) algorithm in order to update filter coefficients. The equation for coefficients updating of LMS algorithm [2-9] can be expressed as;

$$\mathbf{W}(k+1) = \mathbf{W}(k) + 2\mu e(k)\mathbf{S}(k)$$

(8)

Hence, multiply the both sides of Eq. (8) by  $\mathbf{A}^{\mathrm{T}}(\mathbf{k})$  will give

$$\mathbf{A}^{T}(k) \ \mathbf{W}(k+1) = \mathbf{A}^{T}(k)[\mathbf{W}(k)+2\mu e(k) \ \mathbf{S}(k)] \label{eq:approx}$$

(9)

Replace S(k) = A(k)F into Eq. (9) will be

$$\mathbf{A}^{\mathrm{T}}(\mathbf{k}) \mathbf{W}(\mathbf{k}+1) = \mathbf{A}^{\mathrm{T}}(\mathbf{k})[\mathbf{W}(\mathbf{k})+2\mu\mathbf{e}(\mathbf{k})\mathbf{A}(\mathbf{k})\mathbf{F}]$$

(10)

The error signal e(k) can be obtained by;

$$e(k) = d(k) - y(k)$$

(11)

where d(k) is a desired signal The adaptive function space (AFS) [3-5] is defined as

$$\mathbf{P}(\mathbf{k}) = \mathbf{A}^{T}(\mathbf{k})\mathbf{W}(\mathbf{k}) = [p_{0}(\mathbf{k}), ..., p_{B-1}(\mathbf{k})]^{T}$$

(12)

and

$$\mathbf{P}(k+1) = \mathbf{A}^{T}(k)\mathbf{W}(k+1)$$

=  $[p_0(k+1), ..., p_{B-1}(k+1)]^{T}$  (13)

The ith elements of  $\mathbf{P}(k)$  and  $\mathbf{P}(k+1)$  are partial products that related to address vector  $\mathbf{A}_{vi}(k)$  which is ith row vector of  $\mathbf{A}^T(k)$ . Also, time index of  $\mathbf{P}(k)$  and  $\mathbf{P}(k+1)$  correspond to  $\mathbf{W}(k)$  and  $\mathbf{W}(k+1)$  respectively. There are  $2^N$  partial products for the Nth order input signal vector.  $\mathbf{P}(k)$  and  $\mathbf{P}(k+1)$  include B elements selected by B address vectors. Substituting Eq. (12) and Eq. (13) to Eq. (10), will be obtained

$$\mathbf{P}(k+1) = \mathbf{P}(k) + 2\mu \mathbf{e}(k)\mathbf{A}^{\mathrm{T}}(k)\mathbf{A}(k)\mathbf{F}$$

(14)

The output signal can be represented as;

$$y(k) = \mathbf{F}^{T} \mathbf{P}(k) \tag{15}$$

Assume the input signal is white noise with zero mean unit variance. An expectation value of  $\mathbf{A}^{T}(k)\mathbf{A}(k)\mathbf{F}$  [5] becomes

$$E[\mathbf{A}^{\mathrm{T}}(\mathbf{k})\mathbf{A}(\mathbf{k})\mathbf{F}] = 0.25N\mathbf{F}$$

(16)

Replace  $\mathbf{A}^{\mathrm{T}}(\mathbf{k})\mathbf{A}(\mathbf{k})\mathbf{F}$  in Eq. (14) with Eq. (16), also Eq. (14) is simplified to

$$\mathbf{P}(k+1) = \mathbf{P}(k) + 0.5 \mu Ne(k)\mathbf{F}$$

(17)

The term  $0.5\mu N$  in Eq. (17) can be treated as a constant, integer power of two. Therefore, it is possible to implement hardware without multipliers. Also, it can be obtained multiplierless adaptive digital filter with LMS adaptive algorithm.

## III. HARDWARE ARCHITECTURE

An architecture for hardware implementation of adaptive filter uses distributed arithmetic (DA), which is one method often preferred since it eliminates the need for hardware multipliers and is capable of implementing high order filters with very high throughput.

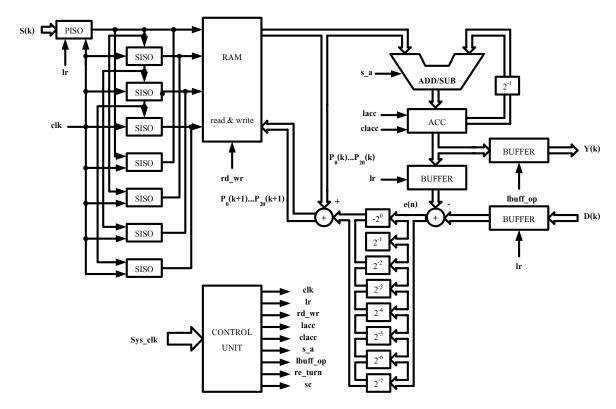

Distributed Arithmetic realization of LMS adaptive digital filter can be derived from Eq. (17). The major design hardware components consist of PISO (parallel in serial out shift register), SISO (serial in serial out shift register), buffer, scaling accumulator, adder, subtractor, update new partial products circuit, RAM and control unit. Therefore, the hardware architecture can be shown in Fig. 1. The operation can be described by 6 steps as follow;

- A/D is controlled by signal sc, will convert analog signal s(t) to 8 bit digital signal s(k), hence, signal lr will be loaded to PISO and signal clk will be shifted each bit of data. Data that shift out from PISO will enter to SISO and will be shifted each bit of SISO by same signal clk.

- Output of PISO and each SISO can be divided to two groups, one group used for RAM addressing. In the same time another used for prepare data to repeat RAM addressing after input signal shifted already (for RAM coefficient updating).

- 3. For the first time of RAM addressing, output of RAM will be added to scaled value from ACC using scaling accumulator that controlled by signal *s\_a*. Result will be loaded to ACC by signal *lacc*. In this time signal *rd\_wr* that used for RAM reading will be active.

- 4. Repeat in step 3 until eight bit, output of RAM will be subtracted from scaled value from ACC. Result will be loaded to first buffer by signal *lr*, then signal *clacc* will clear ACC and signal *lbuff\_op* will be loaded to second buffer for converting digital signal y(k) to analog signal y(t) by D/A.

- 5. Error signal e(n) can be found by difference between desired signal d(k) and output signal y(k), the error

- signal will be passed to update new partial products circuit that contained with bank of shift register to calculate value  $0.5\mu Ne(k)F$  that follows by Eq.(17).

- For the second time of RAM addressing, the new partial products will be replaced old partial products at the

same address by new partial products P(k+1) are old partial products P(k) added with results in step 5. In this time signal rd\_wr that used for RAM reading will be active, and repeat in step 1-6, respectively.

Fig. 1 Proposed hardware architecture for adaptive digital filter based DA

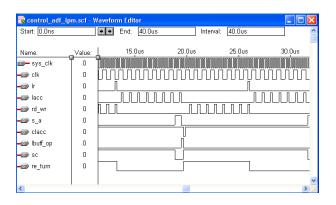

In an implementation will be used VHDL to design and using Leonardo Spectrum and MAX+plusII program for overall development. Timing diagram of control unit is used for controlling all components can be shown in Fig. 2.

Fig. 2 Timing diagram of control unit

# IV. SYSTEM IMPLEMENTATION AND **EXPERIMENTAL RESULTS**

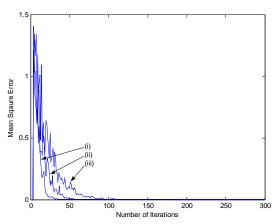

The simulation result as shown in Fig. 3 shows traces of mean-square error (MSE) plotted versus the number of iterations for 4-taps transversal filter. A number of convergence curves are plotted by showing the performance for 3 cases of the convergence factor.

(i)

$$y = 2^{-3}$$

(i)

$$\mu = 2^{-3}$$

(ii)  $\mu = 2^{-4}$

(iii)

$$\mu = 2^{-5}$$

It can be seen that the convergence time increases in the expected manner.

Fig. 3 Plot of MSE versus number of iterations for three convergence factors

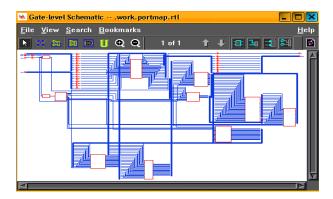

An EPF10K10LC84-4 device in FLEX10K family used for circuits synthesis. Device summary of proposed distributed arithmetic adaptive digital filter is shown in Fig. 4 and synthesis result that shown the synthesized circuits in gate-level can be shown in Fig. 5.

|             | ** DEV   | ** DEVICE SUMMARY ** |       |        |       |        |           |     |            |  |

|-------------|----------|----------------------|-------|--------|-------|--------|-----------|-----|------------|--|

|             | Chip/    |                      | Input | Output | Bidir | Memory | Memory    |     | LCs        |  |

|             | POF      | Device               | Pins  | Pins   | Pins  | Bits   | %Utilized | LCs | % Utilized |  |

| ad_filter20 |          |                      |       |        |       |        |           |     |            |  |

|             | EPF10E   | C10LC84-4            | 18    | 9      | 0     | 320    | 5 %       | 506 | 87 %       |  |

|             | User Pir | 15:                  | 18    | 9      | 0     |        |           |     |            |  |

Fig. 4 Device summary of proposed adaptive digital filter

Fig. 5 Synthesized circuits in gate-level

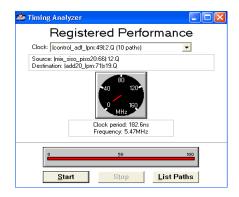

From device summary, 18 input pins used for 8 bits input signal, 8 bits desired signal, system clock and reset, 9 output pins for 8 bits output signal and signal sc for A/D, 320 memory bits used for implementing 16 address RAM with 20 bits wordlength. Others component will use 506 LCs (logic cells) for implementing. Timing summary shows the maximum frequency of synthesized circuits is shown in Fig. 6.

Fig. 6 Timing summary of proposed adaptive digital filter

It should be noted that the major component in this system is RAM, which is independent of number of bits in the input signal wordlength. The size of RAM is determined by number of filter taps used. The number of filter taps chosen for the prototype adaptive digital filter was four since using any more than this involves the use of very large RAMs to store the partial products for filter results. The convergence factor in experiment was fixed at 2<sup>-4</sup> and the prototype board is shown in Fig. 7.

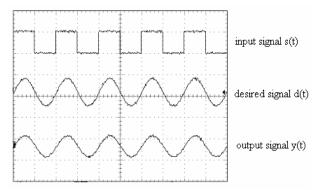

The experimental result in Fig. 8 is used to show results achieved with this prototype. Input signal s(t) was a square wave, desired signal d(t) was a sinusoidal signal of the same frequency that correspond to fundamental frequency of square wave. The output signal y(t) is the filter output after convergence, which is obviously very close to the desired output.

Fig. 7 Prototype of adaptive digital filter using FPGA

Fig. 8 Experimental result for input signal is square wave

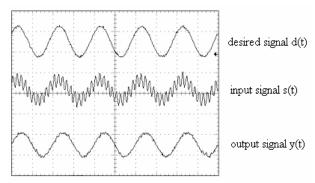

Fig. 9 Experimental result for input signal is composite signal

In Fig. 9 shows the second experimental result from a prototype hardware. The input signal s(t) is a composite signal made up of two frequency sinusoidal inputs at 100 Hz and 1 kHz by amplitude of second frequency is half amplitude of first frequency. Desired signal d(t) is sinusoidal input signal at 100 Hz. After adaptation the filter will be give 100Hz sinusoidal signal that correspond to desired signal with the correct phase.

# V.CONCLUSIONS

The experimental results are ensured to the feasibility of the prototype distributed arithmetic adaptive digital filter. The convergence factor analysis of DA adaptive algorithm theoretically using Matlab program, the results are shown in mean square error (MSE) plotting for each convergence factor that must have the values in power of two coefficients.

In Cowan and others papers [3], [5], [7], adaptive digital filter was developed without multipliers using standard integrated circuits and memory devices which have large area and power consumption. This paper uses FPGA in the design and uses VHDL for describing the behavior of proposed hardware architecture. Consequently, it can be obtained the single chip adaptive digital filter and reduces the power consumption. An architecture for hardware implementation of the adaptive equalizer in partial response class 4 (PR4) channel is proposed using this concept.

### REFERENCES

- [1] A. Peled and B. Liu, "A new hardware realization of digital filters," *IEEE Trans.ASSP.*, vol.ASSP-22, no.6, pp. 456-462, Dec. 1974.

- [2] B. Widrow, J. R. Glover, J. M. McCool, J. Kaunitz, C. S. Williams, R. H. Hearn, J. R. Zeidler, E. Dong and R. C. Goodlin, "Adaptive noise cancelling: Principles and applications," *Proc. IEEE*, vol. 63, pp. 1692-1716, Dec. 1975.

- [3] C. F. N. Cowan and J. Mavor, "New Digital Adaptive Filter Implementation using Distributed Arithmetic Techniques," *IEE Proc.*, vol. 128, Pt. F, No. 4, pp. 225-230, Aug. 1981.

- [4] C. F. N. Cowan and P. M. Grant, Adaptive Filters, Prentice-Hall, 1985.

- [5] K. Takahashi, "Analysis of the Convergence Condition of LMS Adaptive Digital Filter Using Distributed Arithmetic," *IEICE Trans. Fundamental*, vol.E85-A, No.6, pp.1249-1256, June 2002.

- [6] S. Haykin, Adaptive Filter, Prentice-Hall, 2002.

- [7] C. H. Wei and J. J. Lou, "Multimemory Block Structure for Implementing a Digital Adaptive Filter using Distributed Arithmetic," *IEE Proc.*, vol. 133, Pt. G, No.1, pp. 19-26, Feb. 1986.

- [8] A. V. Oppenheim, R. W. Schafer, J. R. Buck, *Discrete-Time Signal Processing*, Prentice-Hall, 1999.

- [9] E. C. Ifeachor and B. W. Jervic, *Digital Signal Processing A Practical Approach*, Adison-wesley, 1998.

Sorawat Chivapreecha (S'04) Received his B. Eng. in Telecommunication Engineering from the Suranaree University of Technology (SUT), Nakhon Ratchasima in 1998 and M. Eng. in Electrical Engineering from the King Mongkut's Institute of Technology Ladkrabang (KMITL), Bangkok in 2001, Thailand. Since then, he has been working as lecturer at Telecommunication

Engineering Department with studying Doctoral degree in Electrical Engineering at KMITL. His research interests about Digital Filter Design and Implementation, VLSI for Signal Processing and Modern Digital Systems Design using HDL with FPGA Applications. He is a student member of IEEE, IEICE and member of ECTI Association.

North Bangkok.

Aungkana Jaravarakul Received her B. Eng. in Electronics Engineering and M. Eng. in Electrical Engineering from King Mongkut's Institute of Technology Ladkrabang (KMITL), Bangkok in 1996 and 2002, Thailand. Since then, she has been working as lecturer at Department of Industrial Electrical Technology, King Mongkut's Institute of Technology

**Nivat Jaruvarakul** Received his B. Sc. And M. Sc. in Technical Education from King Mongkut's Institute of Technology North Bangkok (KMITNB) in 1985 and 1999, respectively, Thailand.

**Kobchai Dejhan** (S'87-M'89-SM'02) Received the B.Eng. and M.Eng. degree in electrical engineering from The King Mongkut's Institute of Technology Ladkrabang (KMITL), Bangkok, THAILAND, in 1978 and 1980, respectively and Docteur degree in telecommunication from Ecole Nationale Superieure des Telecommunications Paris (ENST/Telecom Paris),

France in 1989. Since 1980, he has been a member of the Department of Telecommunication at Faculty of Engineering, KMITL, where he is currently an associate professor of telecommunication. He is senior member of IEEE, member of IEICE and ACM. His research interests analog circuit design, digital circuit design and telecommunication circuit design and system.