### UNIVERSIDADE ESTADUAL DE CAMPINAS Faculdade de Engenharia Elétrica e de Computação

Rafael Oliveira Nunes

# Study of Electromigration in Integrated Circuits at Design Level

Estudo da Eletromigração em Circuitos Integrados na Fase de Projeto

Campinas

#### Rafael Oliveira Nunes

# Study of Electromigration in Integrated Circuits at Design Level

## Estudo da Eletromigração em Circuitos Integrados na Fase de Projeto

Thesis presented to the School of Electrical and Computer Engineering of the University of Campinas in partial fulfilment of the requirements for the degree of Doctor in Electrical Engineer, in the area of Electronics, Microelectronics and Optoelectronics.

Tese apresentada à Faculdade de Engenharia Elétrica e de Computação da Universidade Estadual de Campinas como parte dos requisitos exigidos para a obtenção do título de Doutor em Engenharia Elétrica, na Área de Eletrônica, Microeletrônica e Optoeletrônica

Supervisor/Orientador: Dr. Roberto Lacerda de Orio

Co-supervisor/Coorientador: Dr. Leandro Tiago Manera

Este trabalho corresponde à versão final da tese defendida pelo aluno Rafael Oliveira Nunes, orientado pelo Prof. Dr. Roberto Lacerda de Orio e coorientado pelo Prof. Dr. Leandro Tiago Manera.

Campinas

# Ficha catalográfica Universidade Estadual de Campinas Biblioteca da Área de Engenharia e Arquitetura Rose Meire da Silva - CRB 8/5974

Nunes, Rafael Oliveira, 1983-

N922s

Study of electromigration in integrated circuits at design level / Rafael Oliveira Nunes. – Campinas, SP: [s.n.], 2020.

Orientador: Roberto Lacerda de Orio. Coorientador: Leandro Tiago Manera.

Tese (doutorado) – Universidade Estadual de Campinas, Faculdade de Engenharia Elétrica e de Computação.

1. Eletromigração. 2. Circuitos integrados. 3. Microeletônica. 4. Confiabilidade (Engenharia). 5. Circuitos eletrônicos. I. Orio, Roberto Lacerda de, 1984-. II. Manera, Leandro Tiago, 1977-. III. Universidade Estadual de Campinas. Faculdade de Engenharia Elétrica e de Computação. IV. Título.

#### Informações para Biblioteca Digital

**Título em outro idioma:** Estudo da eletromigração em circuitos integrados na fase de

projeto

#### Palavras-chave em inglês:

Electromigration

Integrated circuits

Microelectronics

Reliability (Engineering)

Elecronic circuits

Área de concentração: Eletrônica, Microeletrônica e Optoeletrônica

Titulação: Doutor em Engenharia Elétrica

Banca examinadora:

Leandro Tiago Manera [Coorientador]

José Alexandre Diniz

Leonardo Breseghello Zoccal

Pietro Maris Ferreira Michelly de Souza

Data de defesa: 05-06-2020

Programa de Pós-Graduação: Engenharia Elétrica

Identificação e informações acadêmicas do(a) aluno(a)

- ORCID do autor: 0000-0001-6105-9100

- Currículo Lattes do autor: http://lattes.cnpq.br/1309786111812453

### Comissão Julgadora – Tese de Doutorado

Candidato: Rafael Oliveira Nunes RA: 143170

Data da defesa: 05 de junho de 2020

**Título da Tese**: "Study of Electromigration in Integrated Circuits at Design Level (Estudo da Eletromigração em Circuitos Integrados na Fase de Projeto)"

Prof. Dr. Leandro Tiago Manera (Presidente)

Prof. Dr. José Alexandre Diniz

Prof. Dr. Leonardo Breseghello Zoccal

Prof. Dr. Pietro Maris Ferreira

Profa. Dra. Michelly de Souza

A Ata de Defesa, com as respectivas assinaturas dos membros da Comissão Julgadora, encontra-se no SIGA (Sistema de Fluxo de Dissertação/Tese) e na Secretaria de Pós-Graduação da Faculdade de Engenharia Elétrica e de Computação.

### Acknowledgements

First and foremost, I would like to thank God Almighty for giving me the strength, knowledge, ability and opportunity to undertake this research study and to persevere and complete it satisfactorily. Without his blessings, this achievement would not have been possible.

I would like to express my gratitude to Prof. Roberto Orio for the opportunity to study for a doctorate under his supervision, for his guidance, and all support throughout my work. Sincerely, the dedication and hours invested in this work give me the conviction that I had an exceptional advisor.

I would like to thanks to my uncle José Edimar Barbosa Oliveira for giving me inspiration and motivation in 2011 to go from Maranhão to Campinas to study at CTI – Centro de Tecnologia da Informação Renato Archer and then at University of Campinas UNICAMP. If he had not given me thought of wisdom, I wouldn't have studied to this level and with this dedication

I thank the staff of the FEEC - Faculdade de Engenharia Elétrica e Computação for keeping a perfect environment of work.

I would like to thank all my colleagues from DSIF, for the moments of technical discussion and of friendship, in special José Ramirez, Orlando Trindade, Júlio Cesar, Elvis Alegria, Jean Pierre, Guilherme Martins, Angie Forero, Jorge Andrés, Marlene Charagua, Clarissa Loureiro, Felipe Fonseca, Leonardo Queiroz, and Estevão Magro.

I would like to thank the dozens of friends that I knew in Barão Geraldo, in special the friends fom ADBarão. The days with these friends made this period easier.

I wish to acknowledge the support and great love of my family, my wife, Tamare; my mother, Ana; my father, Dino; my sister, Adriana; and my brother Tiago. They kept me going on and this work would not have been possible without their input.

This study was financed in part by the Coordenação de Aperfeiçoamento de Pessoal de Nível Superior - Brasil (CAPES) - Finance Code 001.

### **Abstract**

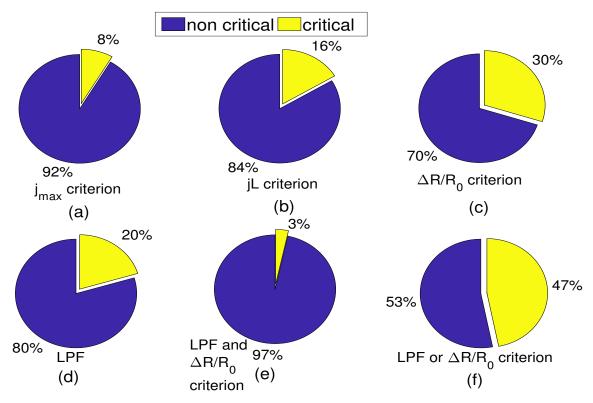

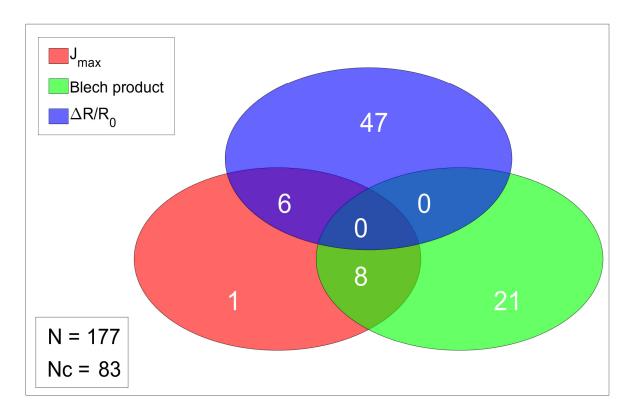

Electromigration damage in interconnects is a well-known bottleneck of integrated circuits, because it causes reliability problems. Operation at high temperatures and current densities accelerates the damage, increasing the interconnect resistance and, therefore, reducing the circuit lifetime. This issue has been accentuated with the technology down-scaling. To guarantee the interconnect reliability and, as a consequence, the integrated circuit reliability, traditional methods based on the so-called Blech Effect and on the maximum allowed current density are implemented during interconnect design. These methods, however, do not take into account the impact of the electromigration on the circuit performance.

In this work the traditional approach is extended and a method to evaluate the effect of the electromigration in an integrated circuit performance is developed. The method is implemented in a tool which identifies the critical interconnect lines of an integrated circuit and suggests the proper interconnect width based on different criteria to mitigate the electromigration damage and to increase the reliability. In addition, the variation of performance parameters of the circuit as an interconnect resistance changes is determined. The tool is incorporated into the design flow of the integrated circuit and uses the data from design kits and reports directly available from the design environment.

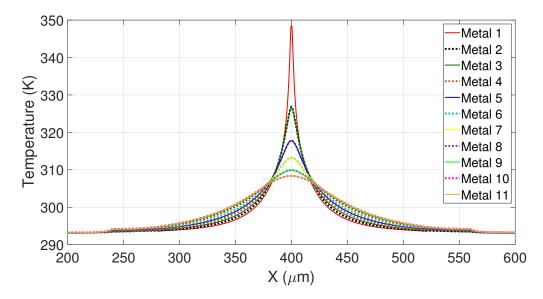

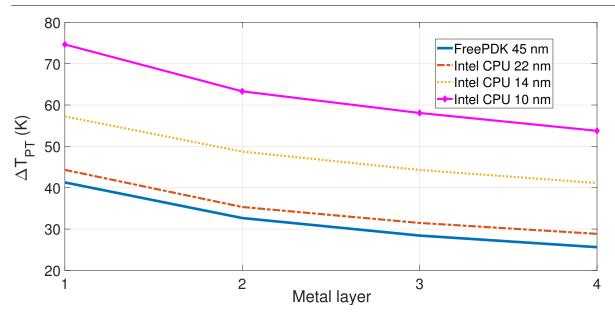

An accurate analysis of the temperature distribution on the interconnect structure is essential to a better assessment of the interconnect reliability. Therefore, a model to compute the temperature on each metallization level of the interconnect structure is implemented. The temperature distribution on the metallization layers of different technologies is investigated. It is shown that the temperature in the Metal 1 of the Intel 10 nm can increase by 75 K, 12 K higher than in the Metal 2. As expected, the layers that are closer to the transistors undergo a more significant temperature increase.

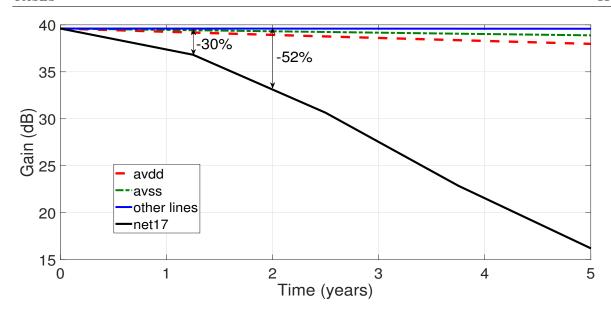

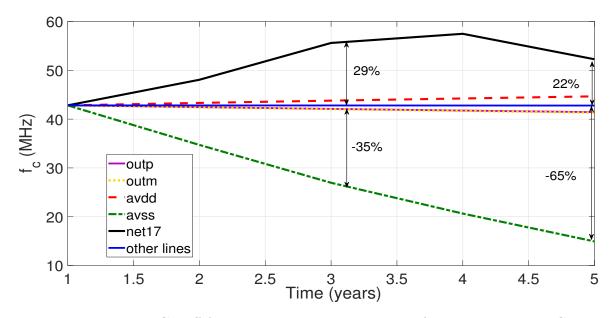

The tool is applied to evaluate the interconnects and the robustness of different circuits, namely a ring oscillator, a bandgap voltage reference circuit, and an operational amplifier, against electromigration. The operational amplifier, in particular, is thoroughly studied. The proposed methodology identifies critical interconnects which under electromigration cause large variations in the performance of the circuit. In a worst-case scenario, the cutoff frequency of the circuit varies by 65% in 5 years of operation. An interesting finding is that the proposed methodology identifies critical interconnects which would not be identified by the traditional criteria. These interconnects have current densities below the limit recommended by the design rules. Nevertheless, one of such an interconnect leads to a variation of 30% in the gain of the operational amplifier. In summary, the proposed

tool verified that from the 20% paths with a critical current density, only 3% degrades significantly the circuit performance.

This work brings the study of the reliability of the interconnects and of integrated circuits to the design phase, which provides the assessment of a circuit performance degradation at an early stage of development. The developed tool allows the designer to identify critical interconnects which would not be detected using the maximum current density criterion, leading to more accurate analysis of the robustness of integrated circuits.

Keywords: electromigration; interconnect; reliability; integrated circuit design.

### Resumo

O dano por eletromigração nas interconexões é um gargalo bem conhecido dos circuitos integrados, pois causam problemas de confiabilidade. A operação em temperaturas e densidades de corrente elevadas acelera os danos, aumentando a resistência da interconexão e, portanto, reduzindo a vida útil do circuito. Este problema tem se acentuado com o escalonamento da tecnologia. Para garantir a confiabilidade da interconexão e, como consequência, a confiabilidade do circuito integrado, métodos tradicionais baseados no chamado Efeito Blech e numa densidade de corrente máxima permitida são implementados durante o projeto da interconexão. Esses métodos, no entanto, não levam em consideração o impacto da eletromigração no desempenho do circuito.

Neste trabalho, a abordagem tradicional é estendida e um método para avaliar o efeito da eletromigração no desempenho de circuito integrado é desenvolvido. O método é implementado em uma ferramenta que identifica as interconexões críticas em um circuito integrado e sugere larguras adequadas com base em diferentes critérios para mitigar os danos à eletromigração e aumentar a confiabilidade. Além disso, é determinada a variação dos parâmetros de desempenho do circuito conforme a resistência das interconexões aumenta. A ferramenta é incorporada ao fluxo de projeto do circuito integrado e usa os dados dos *kits* de projeto e relatórios diretamente disponíveis no ambiente de projeto.

Uma análise precisa da distribuição de temperatura na estrutura de interconexão é essencial para uma melhor avaliação da confiabilidade da interconexão. Portanto, é implementado um modelo para calcular a temperatura em cada nível de metalização da estrutura de interconexão. A distribuição de temperatura nas camadas de metalização de diferentes tecnologias é investigada. É mostrado que a temperatura no Metal 1 da tecnologia Intel 10 nm aumenta 75 K, 12 K mais alta que no Metal 2. Como esperado, as camadas mais próximas dos transistores sofrem um aumento de temperatura mais significativo.

A ferramenta é aplicada para avaliar eletromigração nas interconexões e na robustez de diferentes circuitos, como um oscilador em anel, um circuito gerador de tensão de referência tipo bandgap e um amplificador operacional. O amplificador operacional, em particular, é cuidadosamente estudado. A metodologia proposta identifica interconexões críticas que quando danificadas por eletromigração causam grandes variações no desempenho do circuito. No pior cenário, a frequência de corte do circuito varia 65% em 5 anos de operação. Uma descoberta interessante é que a metodologia proposta identifica interconexões críticas que não seriam identificadas pelos critérios tradicionais. Essas interconexões operam com densidades de corrente abaixo do limite recomendado pelas regras de projeto. No entanto, uma dessas interconexões leva a uma variação de 30% no ganho do amplificador operacional. Em resumo, a ferramenta proposta verificou que dos 20% de

caminhos com uma densidade crítica de corrente, apenas 3% degradam significativamente o desempenho do circuito.

Este trabalho traz o estudo da confiabilidade das interconexões e de circuitos integrados para a fase de projeto, o que permite avaliar a degradação do desempenho do circuito antecipadamente durante o seu desenvolvimento. A ferramenta desenvolvida permite ao projetista identificar interconexões críticas que não seriam detectadas usando o critério de densidade máxima de corrente, levando a uma análise mais ampla e precisa da robustez de circuitos integrados.

Palavras-chaves: eletromigração; interconexão; confiabilidade; projeto de circuito integrado.

## List of Figures

| Figure  | 1.1 – | Electronic circuit before (a) and after (b) be evaluated under harsh                                                                   |            |

|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------|------------|

|         |       | conditions similar to Venus                                                                                                            | 28         |

| Figure  | 1.2 – | Reliability bathtub curves of a chip for different applications                                                                        | 29         |

| Figure  | 1.3 – | Bathtub curve change with introduction of a new technology node                                                                        | 29         |

| Figure  | 1.4 – | Costs of transistors and EDA tools for different technology nodes                                                                      | 30         |

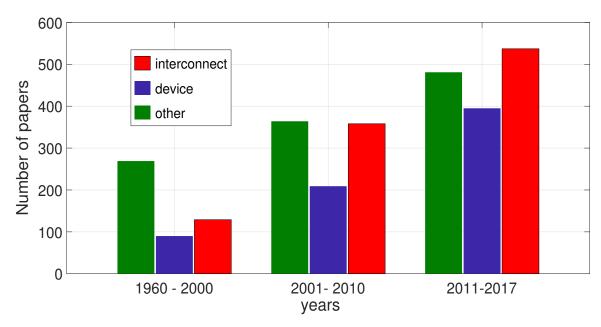

| Figure  | 1.5 – | Number of papers published in leading journal and conferences related                                                                  |            |

|         |       | to IC reliability                                                                                                                      | 31         |

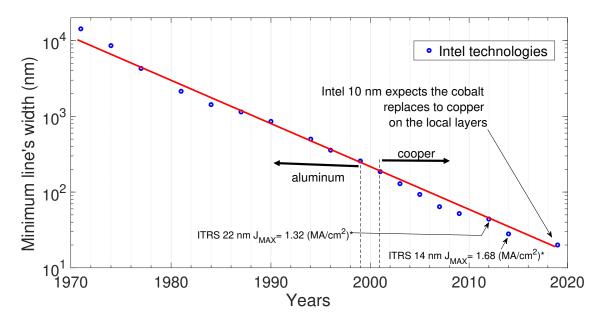

| Figure  | 1.6 – | Evolution of the minimum interconnect width in five decades based on                                                                   |            |

|         |       | Intel processors, from the 10 $\mu\mathrm{m}$ until the 10 nm technology node                                                          | 32         |

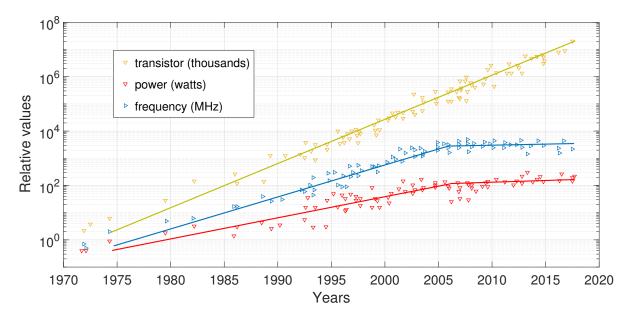

| Figure  | 1.7 – | Evolution of power, frequency and number of transistors in micropro-                                                                   |            |

|         |       | cessors with the technology evolution                                                                                                  | 33         |

| Figure  | 1.8 – | FEOL and BEOL of a CMOS chip structure                                                                                                 | 34         |

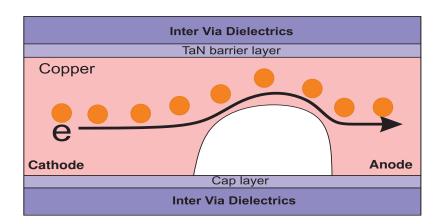

| Figure  | 1.9 – | Illustration of a void formed in an interconnect line under EM                                                                         | 35         |

| Figure  | 1.10- | -Typical Cu interconnect made of a TaN diffusion barrier and a Ta                                                                      |            |

|         |       | adhesion liner                                                                                                                         | 36         |

| Figure  | 2.1 – | Different diffusion paths in a line: through lattice, grain boundaries,                                                                |            |

|         |       | along interfaces and surfaces                                                                                                          | 41         |

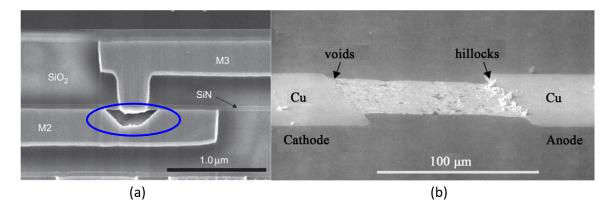

| Figure  | 2.2 – | Wire under EM. (a) Void below a via. (b) Voids and hillocks formed at                                                                  |            |

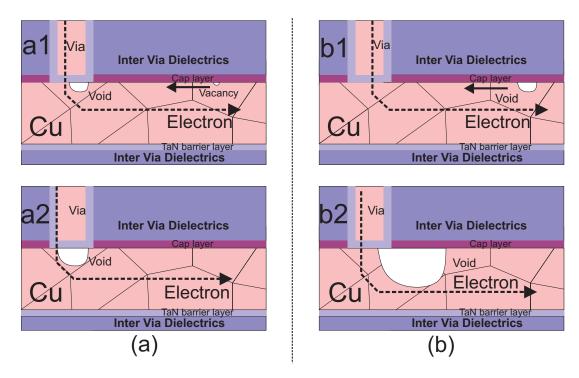

|         |       | the cathode and anode end of the line                                                                                                  | 42         |

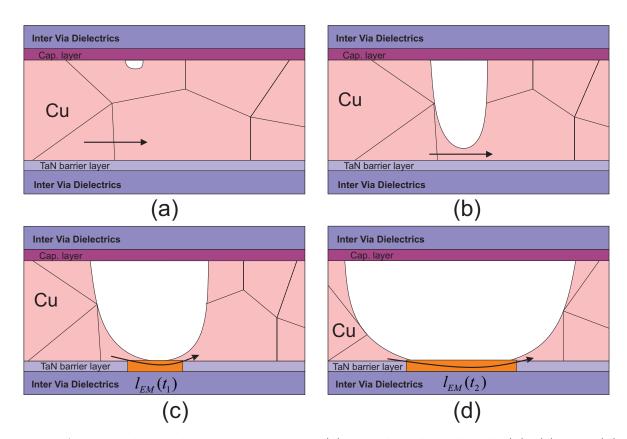

| Figure  | 2.3 – | Schematic of void formation in Cu during an EM stress for kinetics                                                                     |            |

|         |       | limited by (a) void nucleation and (b) void growth and migration                                                                       | 43         |

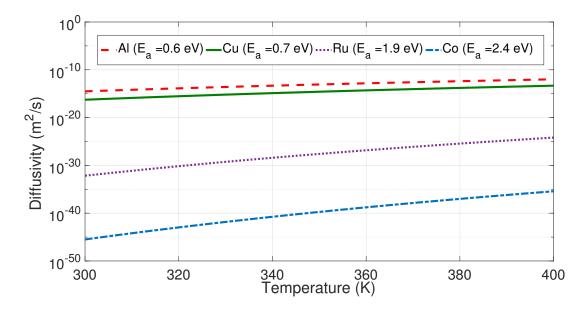

| Ü       |       | Diffusivity variation with the temperature for 4 different metals                                                                      | 47         |

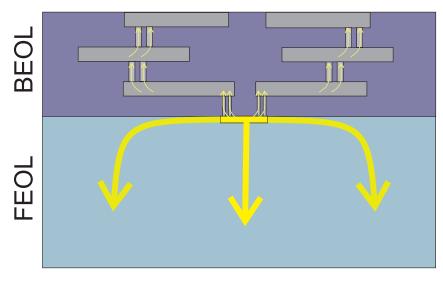

| Figure  | 2.5 – | Heat flow through the BEOL and the FEOL due to power dissipation                                                                       |            |

|         |       | of the transistors' operation                                                                                                          | 47         |

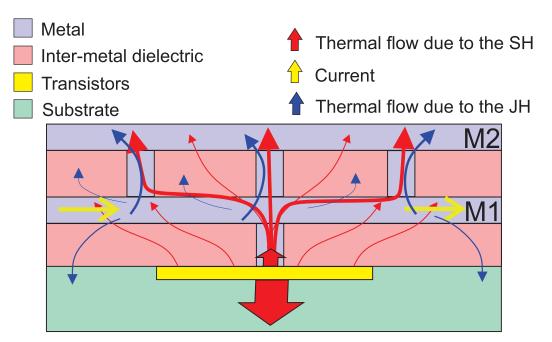

| Figure  | 2.6 – | A schematic diagram of the combined effect of transistor self-heating                                                                  |            |

|         |       | (SH) and Joule heating (JH) heats up metal line, with the heat flowing                                                                 |            |

|         |       | mainly through the metal and the substrate                                                                                             | 49         |

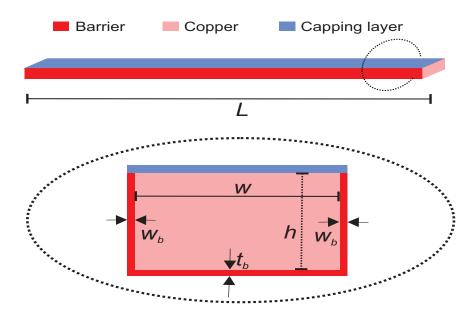

| _       |       | Typical Cu interconnect structure                                                                                                      | 51         |

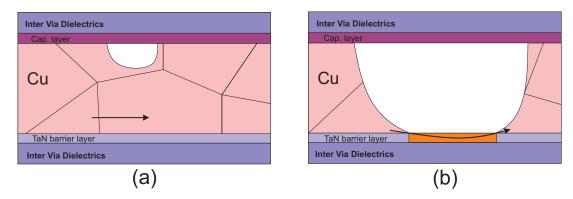

| Figure  | 2.8 – | Cross section of an interconnect. In (a), the growing void has not reached the wire barrier and the current passes throught the Cu. In |            |

|         |       | (b), the void reaches the barrier and the current begins to flow through                                                               |            |

|         |       | part of the barrier                                                                                                                    | 52         |

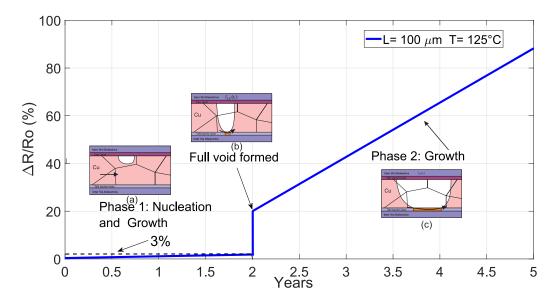

| Figure  | 20_   | Resistance change of an interconnect during the phases of nucleation                                                                   | IJΔ        |

| 1 18011 | ۵.⊍   | and growth                                                                                                                             | 53         |

|         |       | WII STON VII                                                                                                                           | $^{\circ}$ |

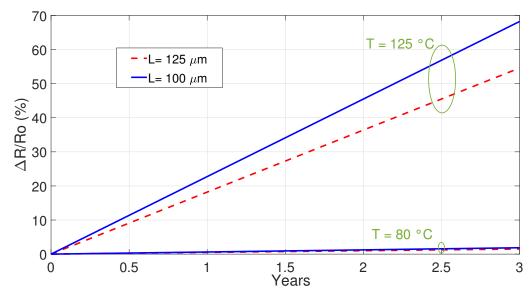

| Figure 2.10  | Resistance ratio variation as a function of time according to (2.14) for XFAB 180 nm technology.                                                                                                                                         | 53                              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Figure 2.11  | Different crystal lattice structures in metallic interconnects (a) polycrystalline, (b) near-bamboo and (c) bamboo                                                                                                                       | 54                              |

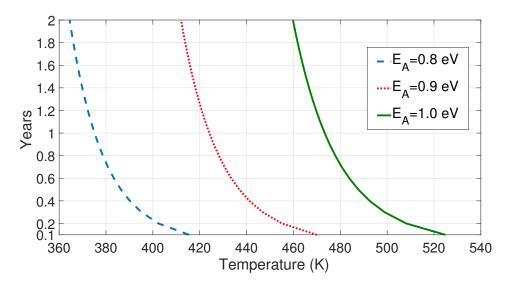

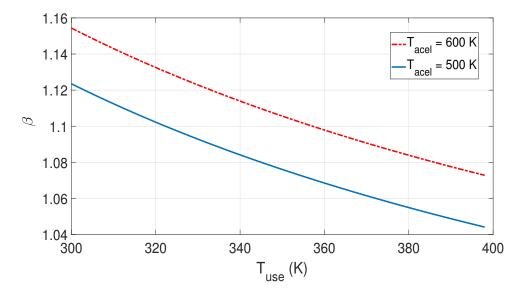

| Figure 2.12  | Time for a wire resistance variation of 10% as a function of the temperature for three activation energies operating with a current of 1.1 mA, and a width of 60 nm, thickness of 170 nm and length of 125 $\mu$ m.                      |                                 |

| Figure 2.13  | $-\beta$ change with $T_{use}$ variation from 300 K to 398 K, for $T_{acel}$ of 500 K and 600 K, and $T_0 = 293$ K                                                                                                                       | <ul><li>56</li><li>57</li></ul> |

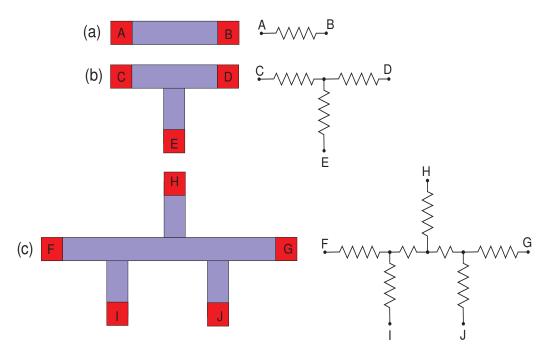

| Figure 2.14  | Different interconnect structures and possible equivalent representation with resistances.                                                                                                                                               | 59                              |

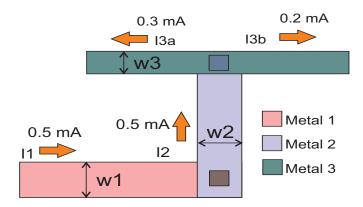

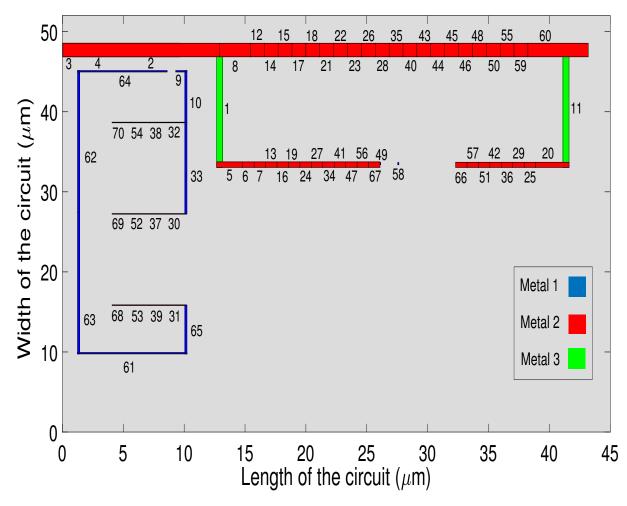

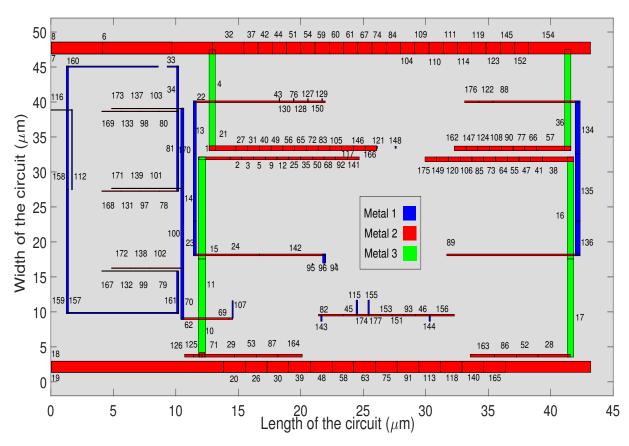

| Figure 3.1 - | Layout top view of an interconnect line with paths made of Metal 1, Metal 2, and Metal 3 and the corresponding currents flowing through them.                                                                                            | 61                              |

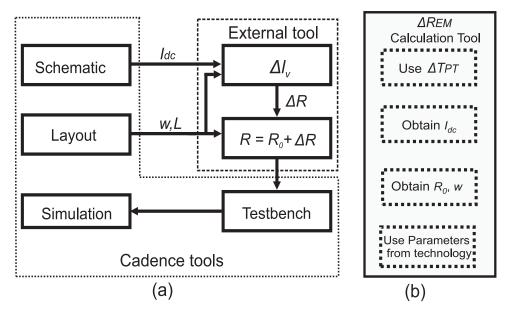

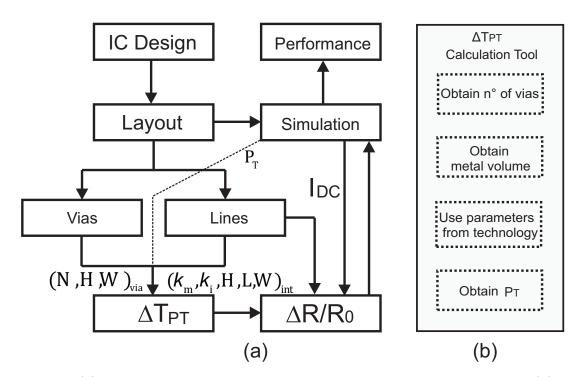

| Figure 3.2 - | - (a) Proposed methodology flow to calculate the resistance change of interconnects due to EM. (b) Main procedures to calculate the EM                                                                                                   | 01                              |

| Figure 3.3 - | resistance change                                                                                                                                                                                                                        | <ul><li>63</li><li>66</li></ul> |

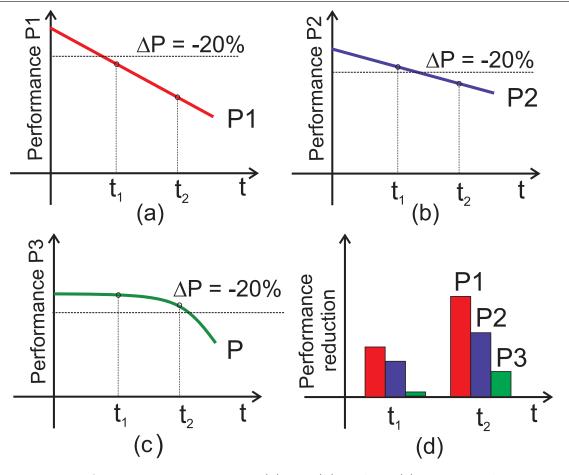

| Figure 3.4 - | Performance parameters P1 (a), P2 (b) and P3 (c) variation due to EM on one wire. In (d) P1, P2 and P3 reduction after $t_1$ and $t_2$                                                                                                   | 67                              |

|              |                                                                                                                                                                                                                                          | 68                              |

| Figure 3.7 - | Resistance degradation. (d) Venn Diagram                                                                                                                                                                                                 | 69                              |

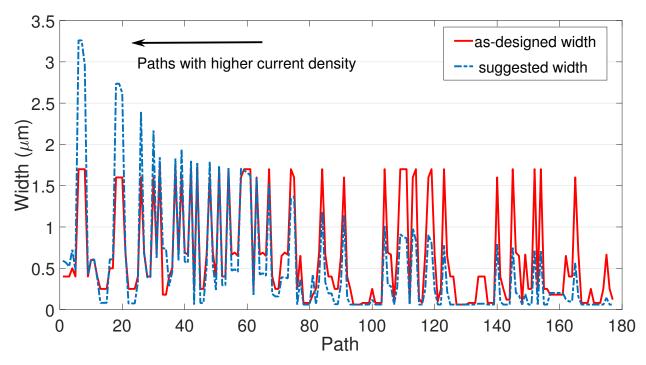

| Figure 3.8 - | criteria                                                                                                                                                                                                                                 | 71<br>72                        |

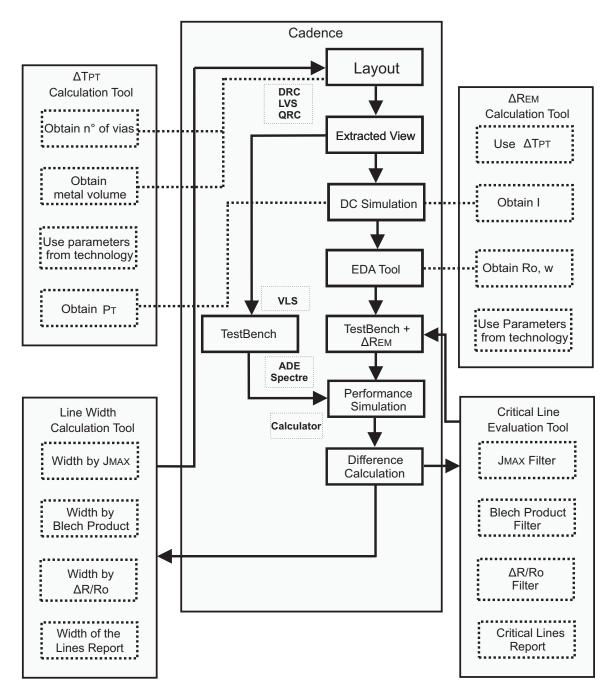

| Figure 3.9 - | Full methodology to evaluate the EM on chips. Cadence tools are used complemented by tools to calculate the $\Delta R_{EM}$ , $\Delta T_{PT}$ , the width of the lines, and to determine the critical lines, which were developed during |                                 |

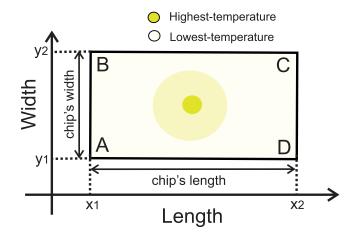

| Figure 4.1 - | this work                                                                                                                                                                                                                                | 74                              |

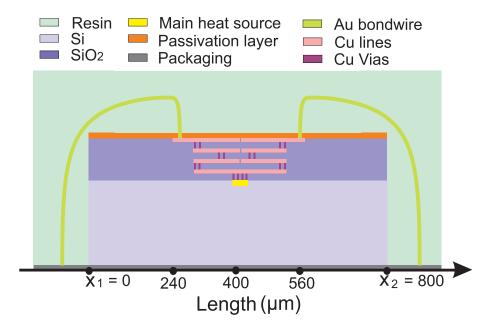

| Figure 4.2 - | source in the center                                                                                                                                                                                                                     | 75<br>76                        |

|              | the temperature in metal layers                                                                                                                                                                                                          | 76                              |

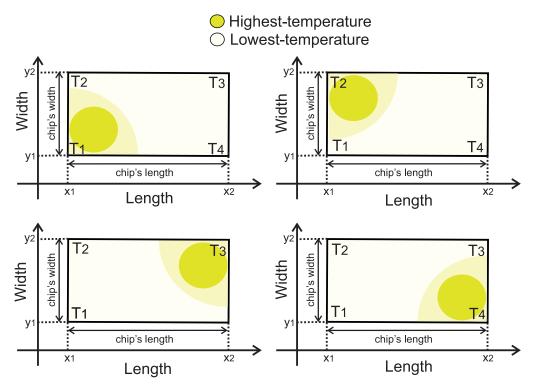

| Figure 4.3 – | Temperature on the BEOL with the heat source in the center of the                            |

|--------------|----------------------------------------------------------------------------------------------|

|              | chip at x = 400 $\mu$ m and the power dissipation of 400 W/m                                 |

| Figure 4.4 – | Temperature distribution with the primary heat source near the corners                       |

|              | of the chip                                                                                  |

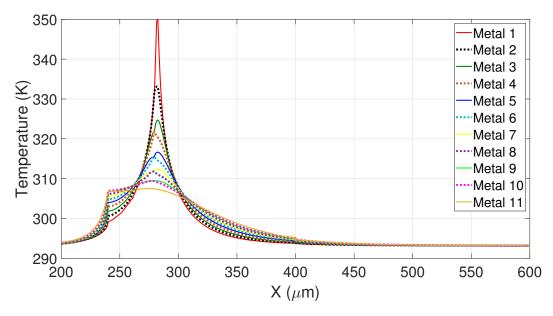

| Figure 4.5 – | Temperature on the BEOL with the primary heat source near the corner                         |

|              | A of the chip at x = 280 $\mu m$ and the power dissipation of 400 W/m 78                     |

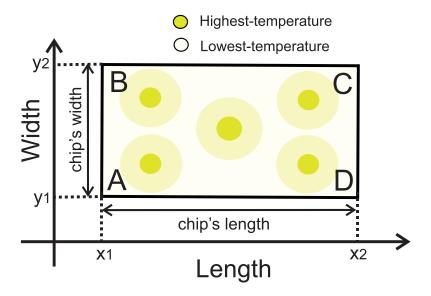

| Figure 4.6 – | Temperature distribution with heat sources at the center and near the                        |

|              | corners of the chip                                                                          |

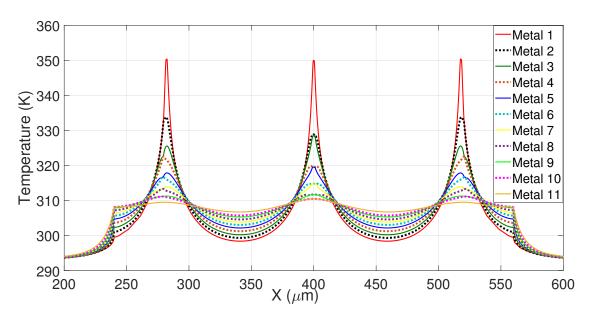

| Figure 4.7 – | Temperature on the BEOL with the primary heat source near the cor-                           |

|              | ners A and D at $x=280~\mu m$ and $x=520~\mu m$ , respectively and in the                    |

|              | center of the chip at x = 520 $\mu$ m, with $P_T = 400 \text{ W/m.} \dots 79$                |

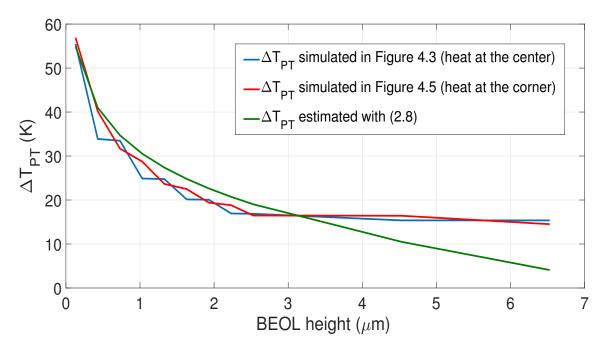

| Figure 4.8 – | Comparision between the maximum $\Delta T_{PT}$ estimated with (2.8) and                     |

|              | simulated in Figure 4.3 and 4.5                                                              |

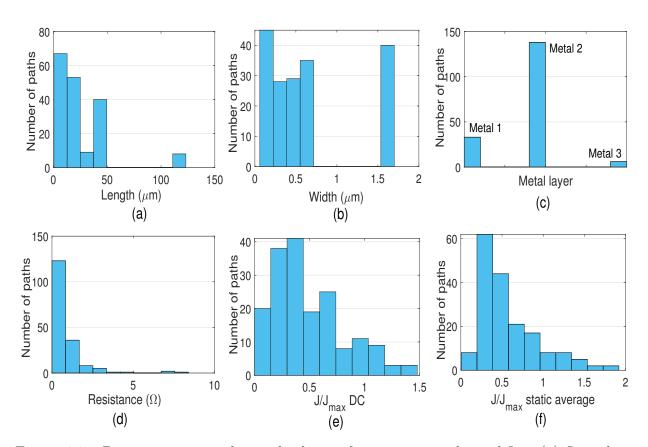

| Figure 4.9 – | Parameters to evaluate the lines of an operational amplifier: (a) Length.                    |

|              | (b) Width. (c) Metal layer. (d) Resistance. (e) Current density ratio in                     |

|              | DC operation. (f) Current density ratio in static operation 81                               |

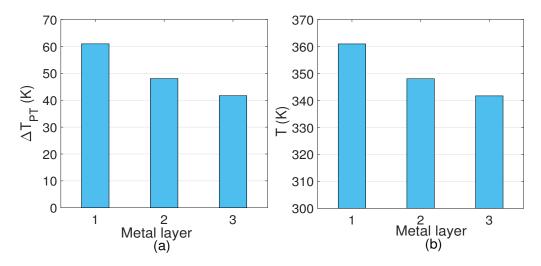

| Figure 4.10- | -(a) $\Delta T_{PT}$ in metal layers. (b) Temperature estimated in the metal layers. 82      |

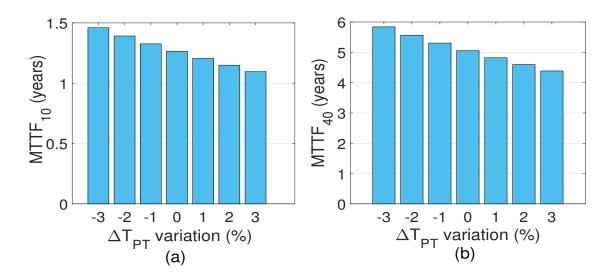

| Figure 4.11- | -(a) Time to the resistance of the lines increase 10% with a $\Delta T_{PT}$ vari-           |

|              | ation from -3% to 3%. (b) Similar analysis with the critical resistance                      |

|              | of the lines of 40%                                                                          |

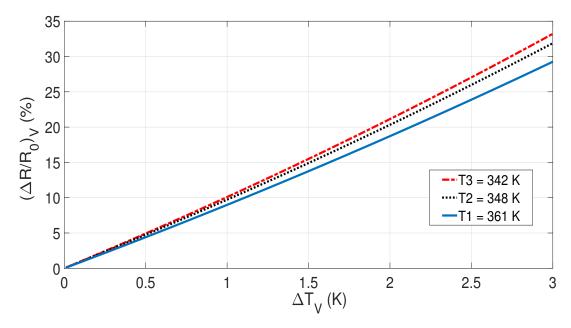

| Figure 4.12- | $-(\Delta R/R_0)_V$ of the lines with the $\Delta T_V$ from 0 to 3 K 83                      |

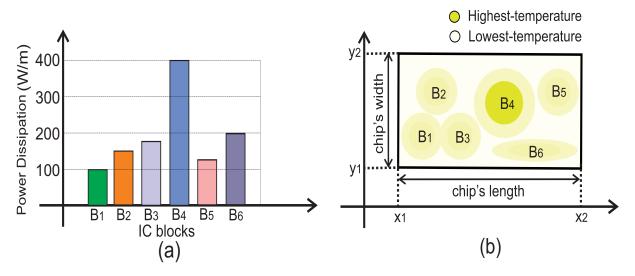

|              | -(a) Power dissipation of the six blocks. (b) Temperature map of the chip. 84                |

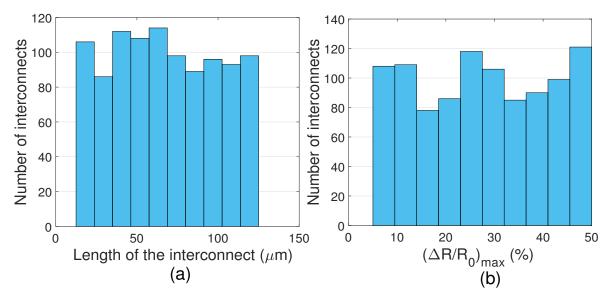

| Figure 4.14- | -Histograms from parameters of the 1000 lines. (a) Length. (b)                               |

|              | $(\Delta R/R_0)_{MAX}$                                                                       |

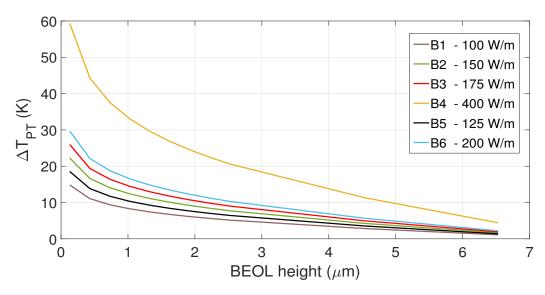

| Figure 4.15- | $-\Delta T_{PT}$ in the layers from the blocks B1 to B6                                      |

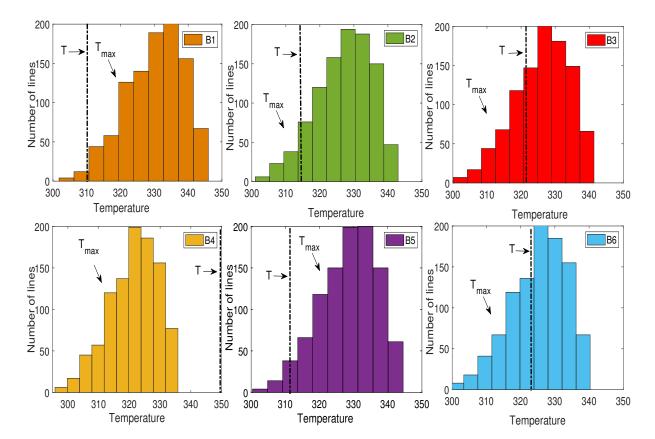

| Figure 4.16- | $-T$ and $T_{max}$ of the Metal 1 lines from B1 to B6                                        |

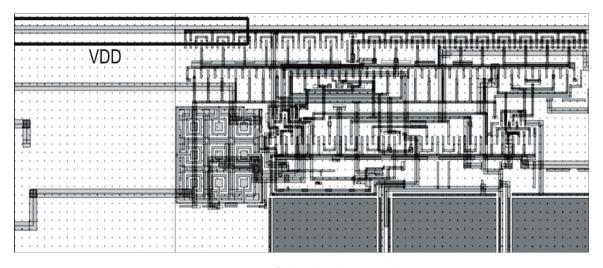

| Figure 5.1 – | Vdd line of an operational amplifier designed with three metal layers.                       |

|              | The interconnect paths are enumerated from 1 to 70 90                                        |

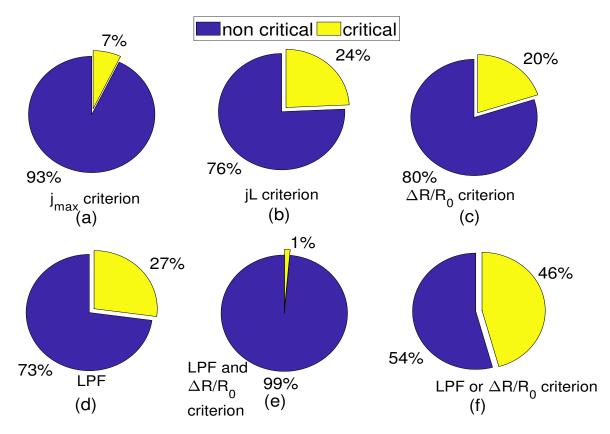

| Figure 5.2 – | Critical paths from the Vdd line according to: (a) $j_{max}$ . (b) jL. (c)                   |

|              | $\Delta R/R_0$ . (d) LPF. (e) LPF and $\Delta R/R_0$ . (f) LPF or $\Delta R/R_0$ 98          |

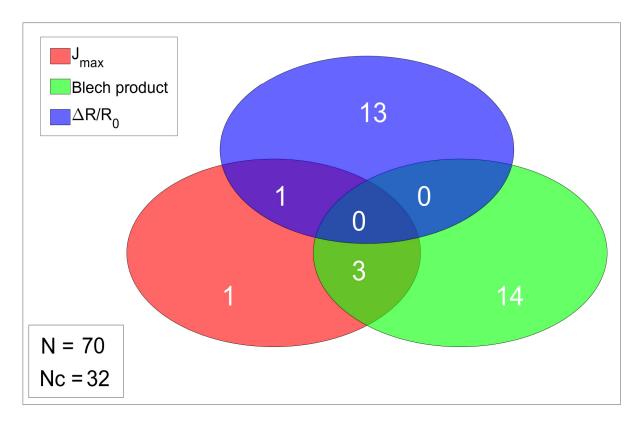

| Figure 5.3 – | Venn diagram with the critical paths of the Vdd line 99                                      |

| Figure 5.4 – | Interconnects with 177 paths of the operational amplifier 100                                |

| Figure 5.5 – | Critical lines from the operational amplifier according to: (a) $j_{max}$ . (b)              |

|              | jL. (c) $\Delta R/R_0$ . (d) LPF. (e) LPF and $\Delta R/R_0$ . (f) LPF or $\Delta R/R_0$ 100 |

| Figure 5.6 – | Veen diagram with the critical paths of the operational amplifier 101                        |

| Figure 5.7 – | Comparison of the width of the lines and the suggested width $101$                           |

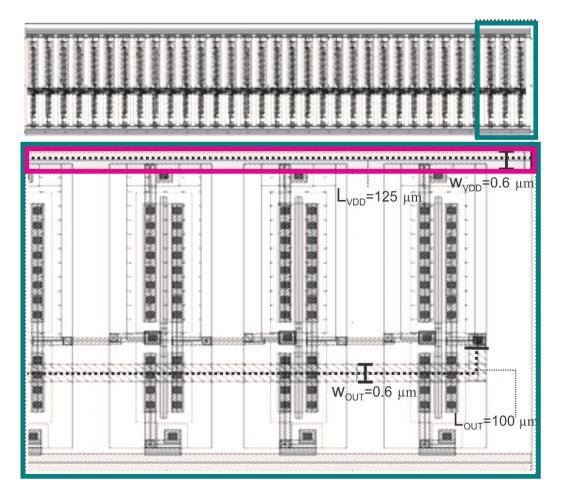

| Figure 6.1 – | Ring oscillator layout and detailed view showing the evaluated lines 102                     |

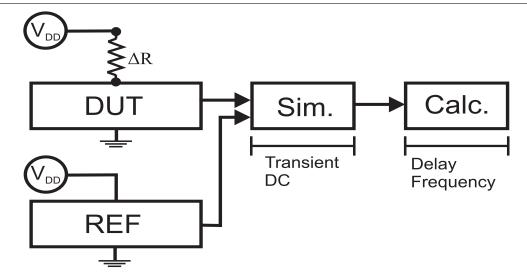

| Figure 6.2 – | Testbench for lines of a ring oscillator under EM                                            |

|              |                                                                                              |

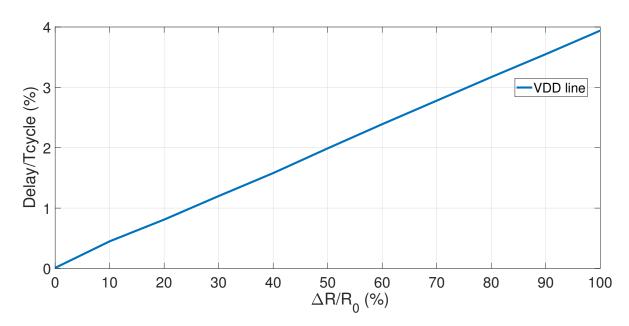

| Figure 6.3 – | Delay change of the oscillator as a function of the resistance increase 103              |

|--------------|------------------------------------------------------------------------------------------|

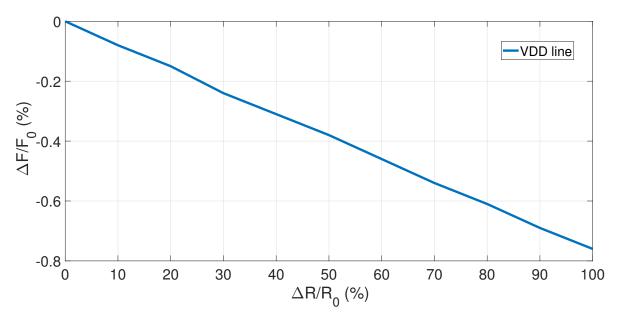

| Figure 6.4 – | Frequency change in oscillator as a function of the resistance increase 104              |

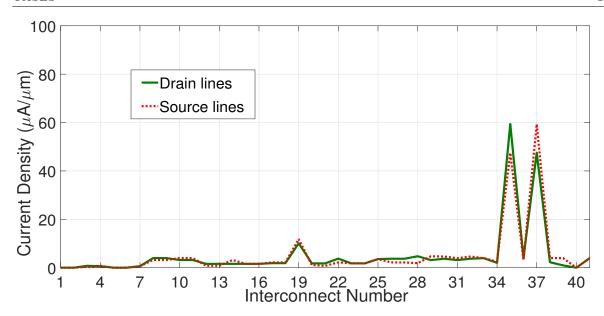

| Figure 6.5 – | Layout of the bandgap voltage circuit                                                    |

| Figure 6.6 – | Current density through lines connected to the drain and source of the                   |

|              | transistors                                                                              |

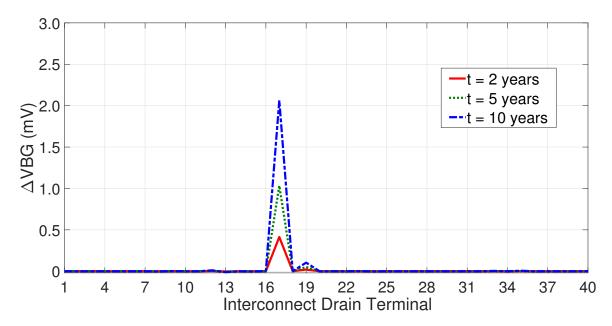

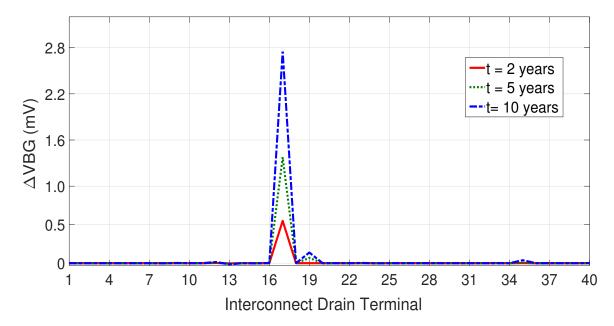

| Figure 6.7 – | VBG change due to EM in the drain interconnects for different opera-                     |

|              | tion times                                                                               |

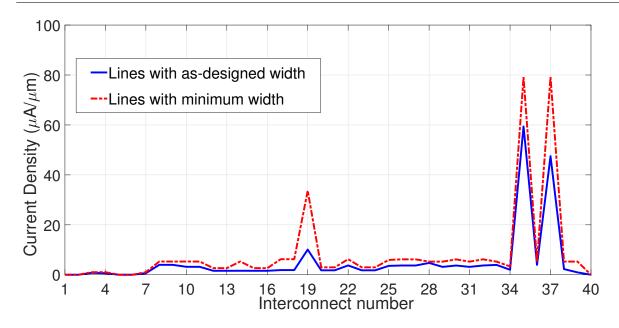

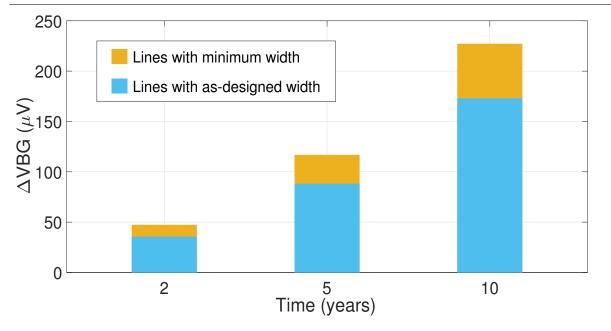

| Figure 6.8 – | Current density thought the lines with the designed width and the                        |

|              | minimum width                                                                            |

| Figure 6.9 – | VBG change for the lines with the minimum width                                          |

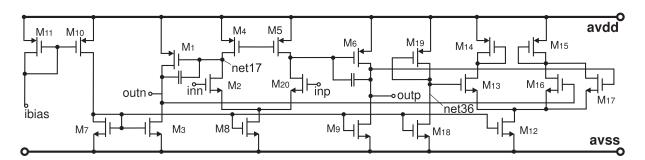

| Figure 6.10- | -VBG variation when all lines are assumed to be under EM 109                             |

| Figure 6.11- | -Operational amplifier used to evaluate the EM effect of the lines resis-                |

|              | tance variation on the circuit performance degradation                                   |

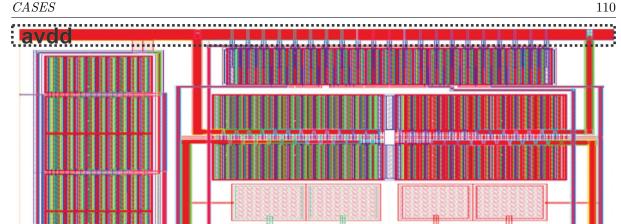

| Figure 6.12- | -Layout extract from the evaluated differential amplifier with the avdd                  |

|              | line highlighted                                                                         |

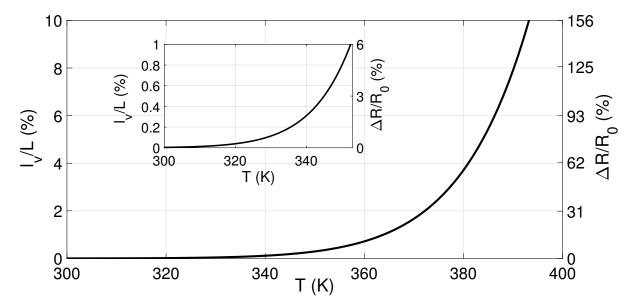

| Figure 6.13- | -Void length relative to the line length and the line resistance increase                |

|              | as a function of time for 353 K (80°C) and 398 K (125°C) 111                             |

| Figure 6.14- | -Void length relative to the line length variation with temperature and                  |

|              | line resistance change after 1 year                                                      |

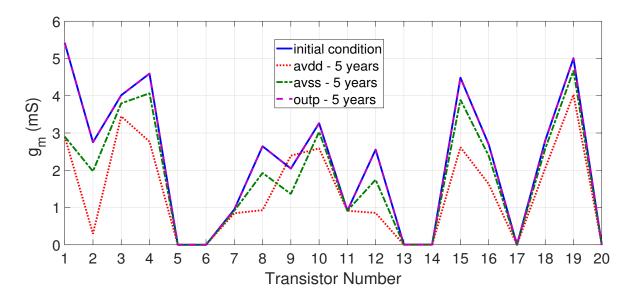

| Figure 6.15- | -Transconductance variation for the 20 Opamp transistors due to the                      |

|              | EM in several lines for 125 °C                                                           |

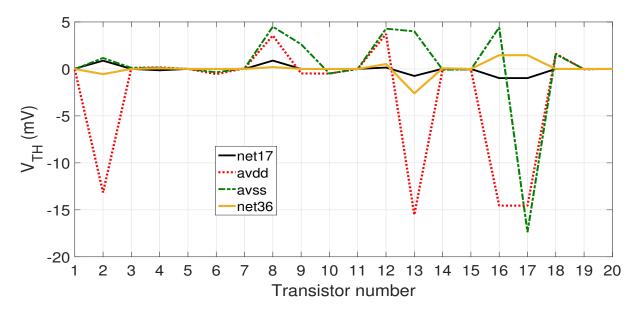

| Figure 6.16- | $-V_{TH}$ variation for the 20 Opamp transistors due to the EM in several                |

|              | lines for 5 year operating at 125 °C                                                     |

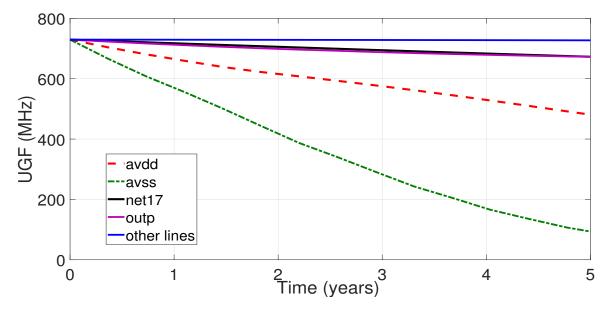

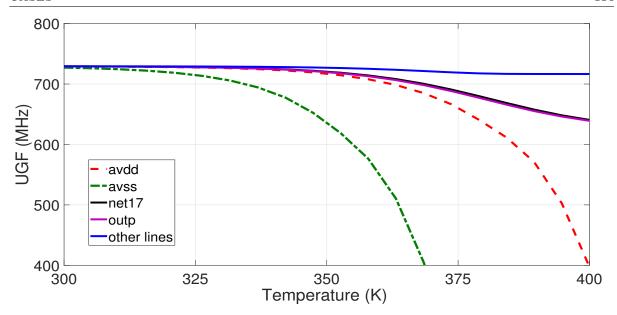

| Figure 6.17- | -Unit gain frequency variation with time for different interconnects un-                 |

|              | der EM at 125 °C                                                                         |

| Figure 6.18- | -UGF variation with temperature after 7 years                                            |

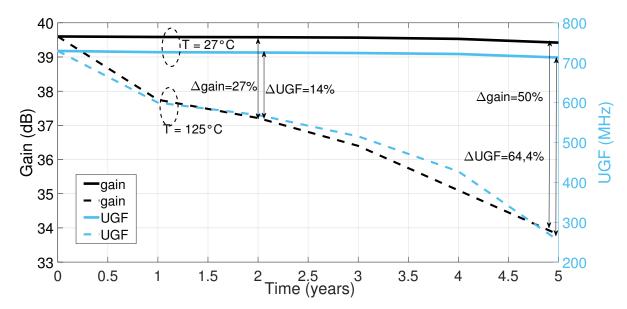

| Figure 6.19- | -Gain variation in 5 years of operation at 125 °C                                        |

| Figure 6.20- | -Cutoff frequency variation<br>in 5 years of operation at 125 °C 115                     |

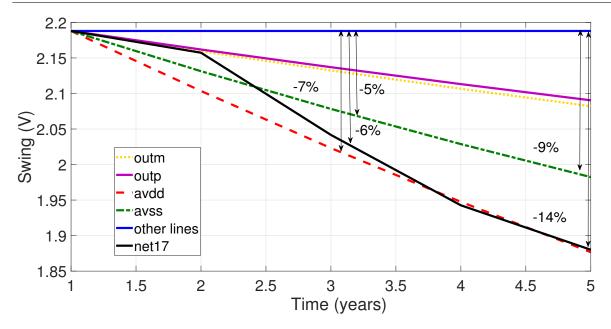

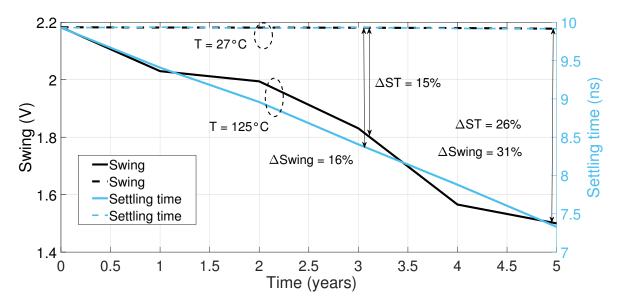

| Figure 6.21- | -Swing voltage variation in 5 years of operation at 125 °C 116                           |

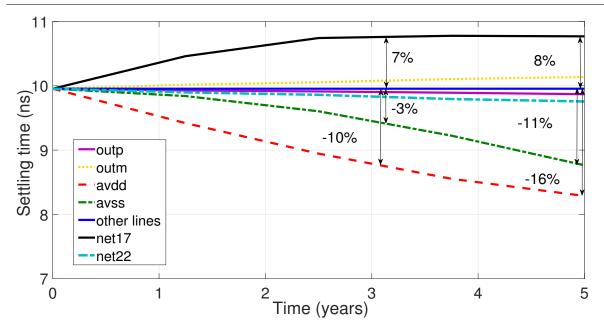

| Figure 6.22- | -Settling time variation in 5 years of operation at 125 °C 117                           |

| Figure 6.23- | -Gain and UGF variation considering all interconnects under EM simul-                    |

|              | taneously                                                                                |

| Figure 6.24  | -Settling time and swing voltage variation for all lines affected simulta-               |

|              | neously by EM                                                                            |

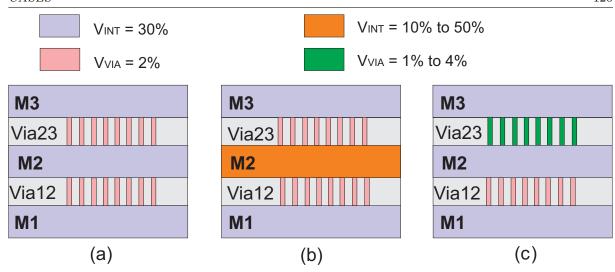

| Figure 6.25- | -(a) Structure used to evaluate the temperature change in local layers                   |

|              | with the changes in: (b) metal volume fraction in $V_{\rm INT}M2$ from 10% to            |

|              | $50\%$ and (c) via volume fraction in $V_{VIA}23$ from $1\%$ to $4\%.$ 120               |

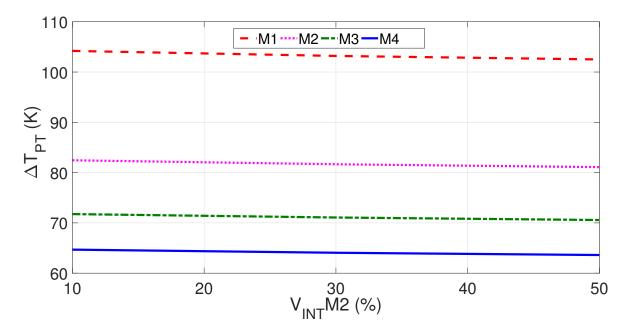

| Figure 6.26- | $-\Delta T_{PT}$ in local layers for different V <sub>INT</sub> M2 for $P_T=500$ W/m 120 |

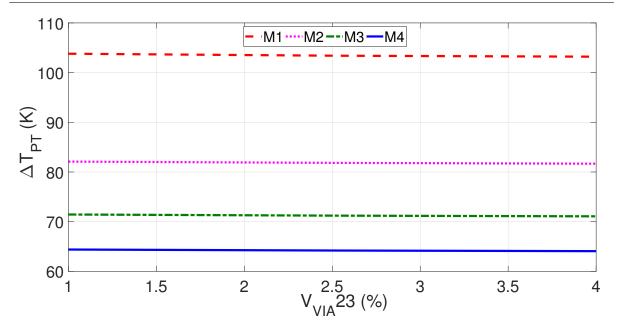

| Figure 6.27– $\Delta T_{PT}$ in local layers for different fractions of V <sub>VIA</sub> 23 for $P_T=500$ W/m.121 |

|-------------------------------------------------------------------------------------------------------------------|

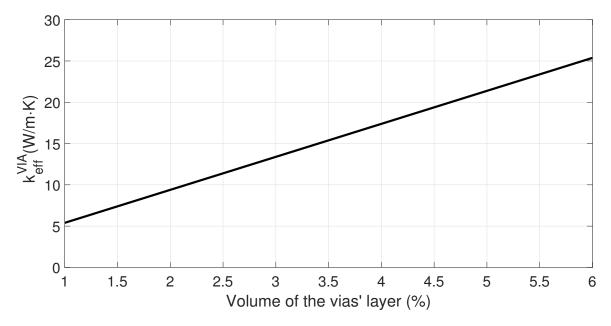

| Figure 6.28–Effective thermal conductivity variation of the via layers as a function                              |

| of the via volume fraction                                                                                        |

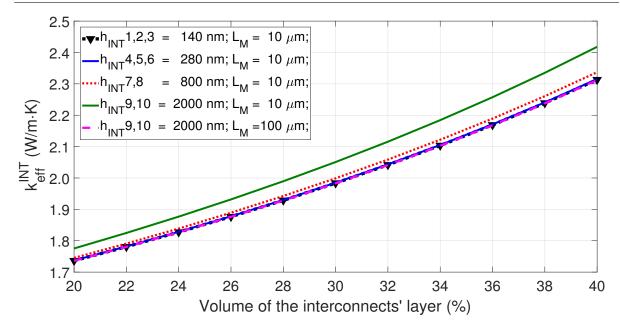

| Figure 6.29–Effective thermal conductivity variation of the interconnect layers as a                              |

| function of volume fraction                                                                                       |

| Figure 6.30–Effective thermal conductivity variation of the BEOL as a function of                                 |

| interconnect layer volume fraction for various via layer volume fraction. 123                                     |

| Figure 6.31–Temperature variation in the BEOL layers for a 45 nm technology due                                   |

| transistors self-heating for a dissipated power of 500 W/m 124                                                    |

| Figure 6.32–Temperature variation difference in the BEOL layers for two cases of                                  |

| volume via and interconnect variation for $P_T = 500 \text{ W/m.}$ 125                                            |

| Figure 6.33–Minimum interconnect pitch of modern technologies                                                     |

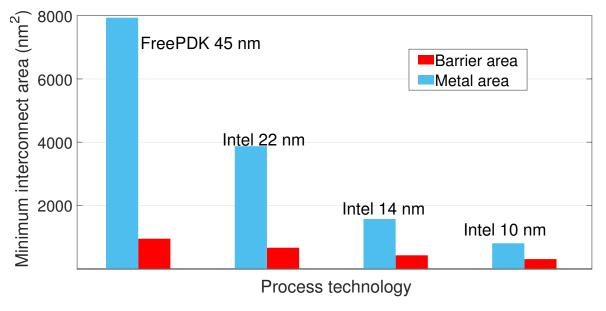

| Figure 6.34–Minimum interconnect cross-sectional area of modern technologies. $$ . $$ . $$ . $$ .                 |

| Figure 6.35–Temperature change of the metallic layers for different technologies. A                               |

| power dissipation of 200 W/m is considered                                                                        |

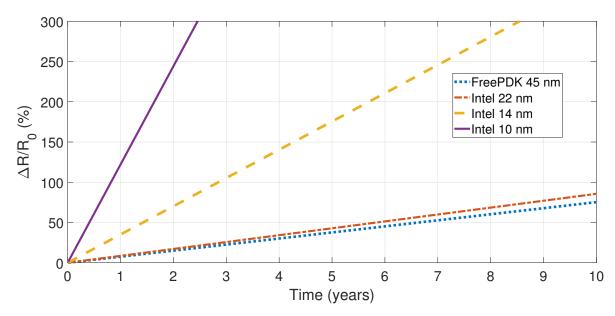

| Figure $6.36$ – $\Delta R/R_{\theta}$ variation of the Metal 1 lines of modern technologies consider-             |

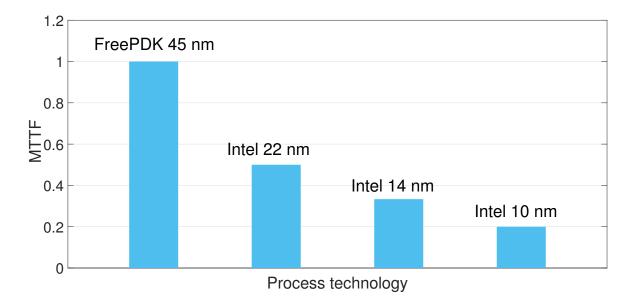

| ing the temperature increase from Figure 6.35                                                                     |

| Figure 6.37–Mean-time-to-failure of interconnects of modern technologies under a                                  |

| current density of 2 $MA/cm^2$                                                                                    |

| Figure A.1–Void growth in a interconnect. (a) Initial nucleated void. (b), (c), and                               |

| (d) Void growth through the metal until it reached the barrier layer $156$                                        |

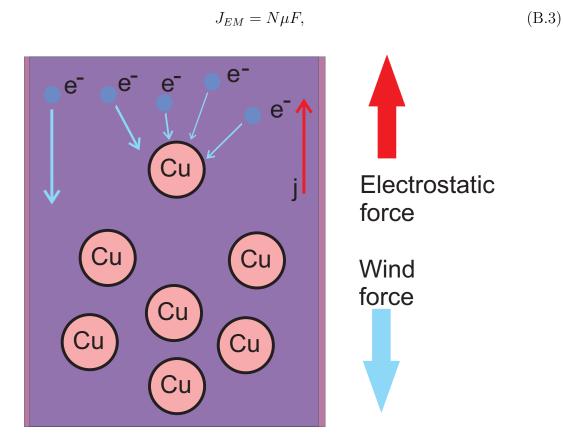

| Figure B.1–Illustration of electrostatic and "electron wind" forces on a metal $159$                              |

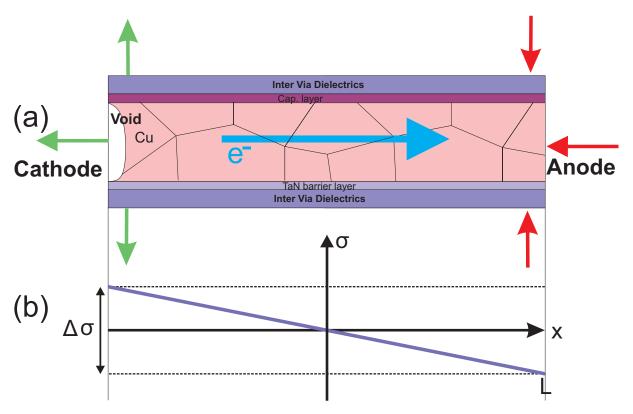

| Figure B.2–The stress difference $\Delta\sigma_c$ in a segment of length L. The arrows in the                     |

| line indicates the tensile stress in the cathode and the compressive stress                                       |

| in the anode. Electron flow direction is from cathode to anode $161$                                              |

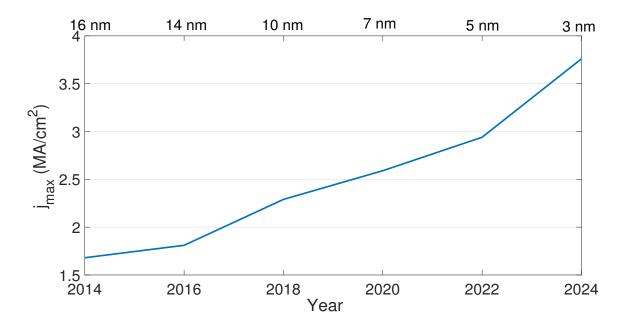

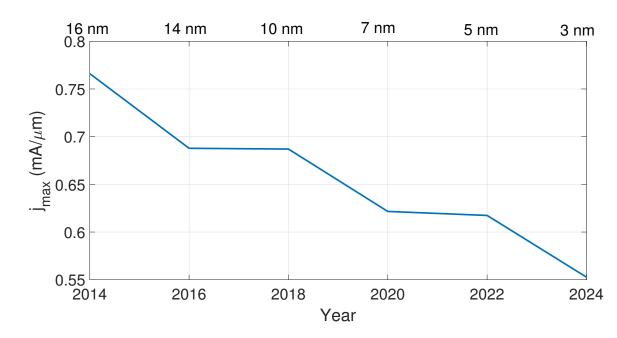

| Figure C.1 – Maximum allowed current density prediction of different technologies $162$                           |

| Figure C.2-Maximum allowed current density prediction converted to design                                         |

| nomenclature                                                                                                      |

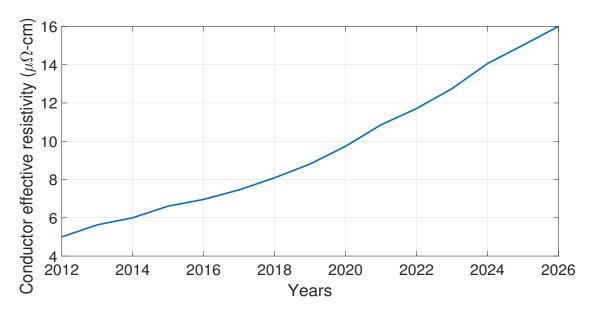

| Figure C.3 – Effective resistivity of the metal lines estimated from 2012 to 2026. $$ 164                         |

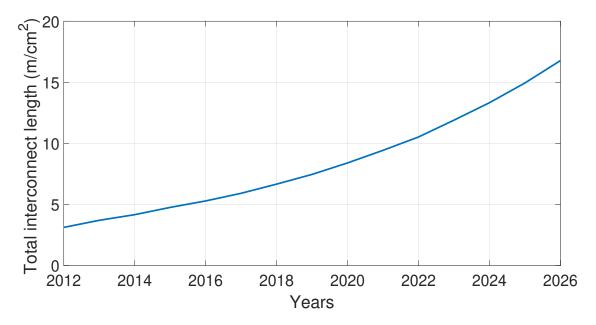

| Figure C.4–Total interconnect length evolution estimated for MPU                                                  |

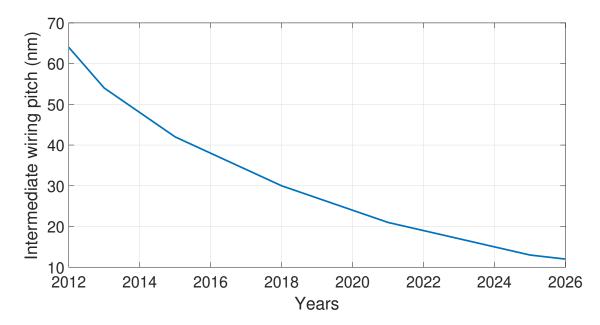

| Figure C.5 – Pitch evolution of the intermediate lines estimated from 2012 to 2026 $165$                          |

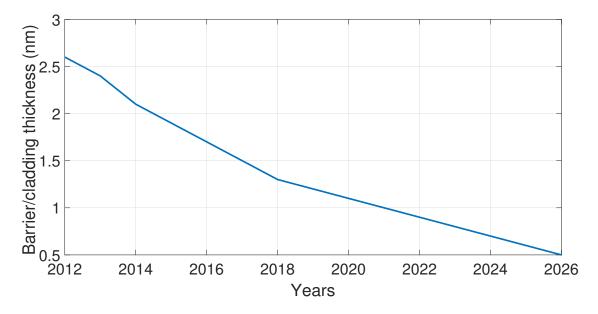

| Figure C.6 – Barrier and cladding thickness evolution estimated from 2012 to 2026 165 $$                          |

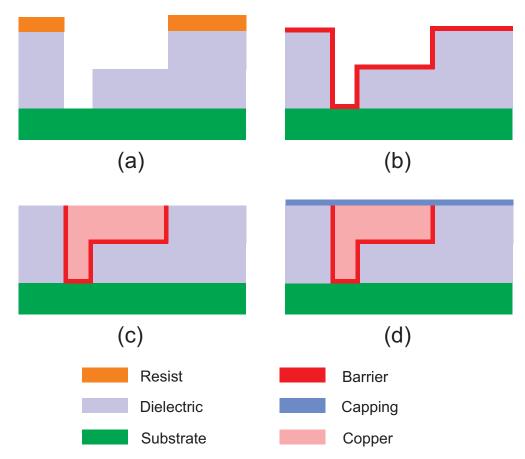

| Figure E.1 – Cooper dual-damascene process: nucleation in (a) via and trench pat-                                 |

| terning, (b) barrier layer deposition, (c) Cu electroplating and excess                                           |

| removal by CMP, and (d) capping layer deposition                                                                  |

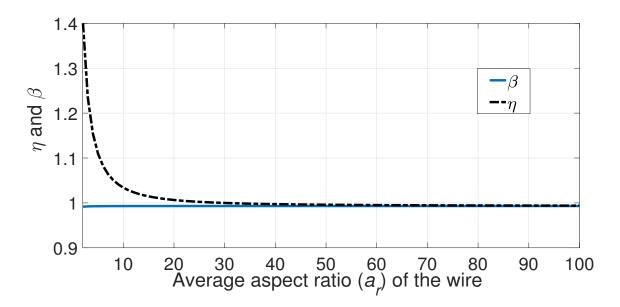

| Figure F.1 – Parameters $\beta$ and $\eta$ as a function of the average aspect ratio $a_r$ 191                    |

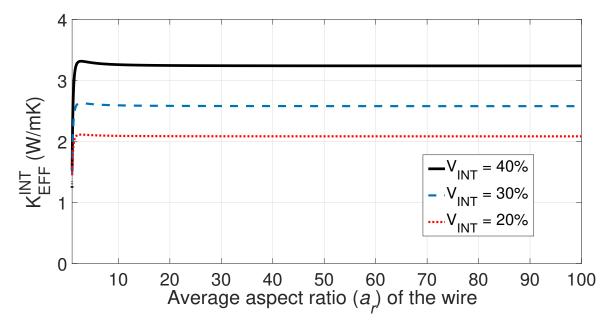

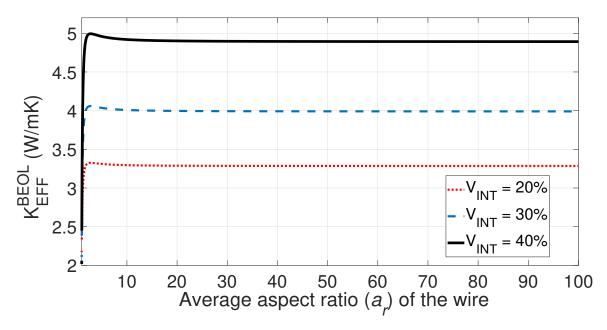

| Figure F.2 – Effective thermal conductivity of the Metal 1 layer as a function of the                             |

| average aspect ratio $(a_r)$ for $h_0=11720$ nm and $L_I^{int}=130$ nm 191                                        |

| Figure F.3 – Effective thermal conductivity of the BEOL as a function of the average          |

|-----------------------------------------------------------------------------------------------|

| aspect ratio $(a_r)$ with $L_n^{int}$ and $L_n^{via}$ dimensions from a 45 nm technology. 192 |

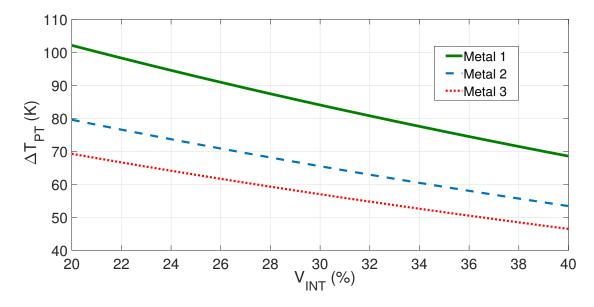

| Figure F.4 – Temperature variation in the Metal1, Metal2 and Metal 3 layers, as a             |

| function of the fraction volume of lines $(k_{eff}^{int})$                                    |

## List of Tables

| 1able 2.1 –   | Typical activation energies $(\mathbb{E}_a)$ for different EM diffusion paths in Al |   |

|---------------|-------------------------------------------------------------------------------------|---|

|               | and Cu lines                                                                        | 1 |

| Table 2.2 –   | Parameters for Cu, Al, Co and Ru                                                    | 3 |

| Table 2.3 –   | Parameters of the interconnects based on the ITRS reports                           | 1 |

| Table 2.4 –   | Parameters based on the XFAB 180 nm technology used to calculate                    |   |

|               | the $\Delta R/R_0$ ratio from (2.14) [1]                                            | 1 |

| Table 3.1 –   | Parameters from the interconnect of Figure 3.1                                      | 2 |

| Table 4.1 –   | Parameters used in the BEOL model simulated in the COMSOL $[2]$ 77                  | 7 |

| Table 4.2 –   | Normalized values for current and width of the six blocks                           | 5 |

| Table 4.3 –   | Thickness of the lines and via layers from GPDK 45 nm                               | 5 |

| Table 4.4 –   | EM evaluation of the blocks B1 to B6                                                | ĵ |

| Table 5.1 –   | EDA data of the Vdd paths enumerated from 1 to 40                                   | 1 |

| Table 5.2 –   | EDA data of the Vdd paths enumerated from 41 to 70 92                               | 2 |

| Table 5.3 –   | Parameters to estimate the resistance and the temperature change 92                 | 2 |

| Table 5.4 –   | Parameters of the metal layers to calculate $k_{eff}^{int}$                         | 3 |

| Table 5.5 –   | Parameters of the via layers to calculate $k_{eff}^{via}$                           | 3 |

| Table 5.6 –   | Temperature of the metal layers                                                     | 3 |

| Table 5.7 –   | Evaluation of the critical paths 1 to 40 with the EM criteria 94                    | 1 |

| Table 5.8 –   | Evaluation of the critical paths 41 to 70 with the EM criteria 95                   | 5 |

| Table 5.9 –   | Dimensions of the paths 1 to 40 of the Vdd interconnect 96                          | 3 |

| Table 5.10-   | Dimensions of the paths 41 to 70 of the Vdd interconnect 97                         | 7 |

| Table 6.1 –   | Parameters based on the XFAB 180 nm technology used to calculate                    |   |

|               | the $\Delta R/R_0$ ratio from (2.14)                                                | 1 |

| Table 6.2 –   | Oscillator performance for $\Delta R/R_0$ of 100% and 200% at 353 K 104             | 1 |

| Table $6.3 -$ | Parameters used to evalute the Al lines of the bandgap circuit $106$                | 3 |

| Table $6.4 -$ | VDD line evaluation for the bandgap circuit                                         | 3 |

| Table $6.5 -$ | Summary of performance parameters indicating the most critical inter-               |   |

|               | connect and the line condition from the traditional evaluation $118$                | 3 |

| Table 6.6 –   | Thickness and width of the lines and via layers from FreePDK45 tech-                |   |

|               | nology                                                                              | 9 |

| Table $6.7$ – | The modes A, B, C and D used to evaluate the $\Delta T_{PT}$                        | 1 |

| Table C.1-    | Aspect ratio, minimum wire width, and metal thickness of different tech-            |   |

|               | nologies                                                                            | 2 |

| Table G.1-    | EDA data of the Opamp paths                                                         | 3 |

| Table G.2–EDA data of the Opamp paths |  |

|---------------------------------------|--|

| Table G.3–EDA data of the Opamp paths |  |

| Table G.4–EDA data of the Opamp paths |  |

### List of Abbreviations and Acronyms

ADE Analog design environment

BEOL Back-end-of-line

CMOS Complementary metal-oxide-semiconductor

CPU Central processing unit

$C.\Delta R/R_0$  evaluation of the paths for the maximum resistance change

C.j evaluation of the paths for the maximum current density

C.jL evaluation of the paths for the Blech product

DRC Design ruler checker

DUT Device under test

EAD Electrically aware design

EM Electromigration

ESD Electrostatic discharge

Fc Cut-off frequency

FC Flip chip

FreePDK45 Open-Access-based PDK for the 45nm technology node

FEM Finite element method

FEOL Front-end-of-line

GPDK Generic process design kit

GPU Graphics processing unit

HCI Hot carrier injection

HDL Hardware description languages

IC Integrated circuit

IP Intellectual property

ITRS International Technology Roadmap for Semiconductors

JH Joule heating

LPF Lines prone to failure

LVS Layout Versus Schematic

MTTF Mean time-to-failure

NBTI Negative bias temperature instability

PBTI Positive bias temperature instability

PPF Paths prone to failure

REF Reference

SM Stressmigration

SoC System on a chip

SPICE Simulation Program with Integrated Circuit Emphasis

ST Settling time

TDDB Time-dependent dielectric breakdown

TM Thermomigration

TTF Time-to-failure

UGF Unit gain frequency

ULK Ultra low-k dielectric

ULSI Ultra large-scale integration

VBG Voltage bandgap

VHDL VHSIC Hardware Description Language

XFAB X-FAB Silicon Foundries

### List of Symbols

A Corss-sectional area of the interconnect metal

$A_b$  Cross-sectional area of the barrier layer

$A_{int}$  Area occupied by the metals in a layer

$A_m$  Constant which comprises the material properties and the geometry of

the interconnect

$a_r$  Aspect ratio, the average ratio of the length and the thickness of the

interconnect lines

$A_{via}$  Area occupied by the vias in a layer

c Concentration of atoms

D Diffusivity

$D_0$  Pre-exponential factor dependent on the diffusion mechanisms

e Elementary charge

$E_a$  Activation energy

F Fraction of diffusing atoms for the various diffusion paths

$f_c$  Cutoff frequency

$g_m$  Transconductance

h Thickness of the interconnect lines

$h_0$  BEOL total thickness

I Electrical current

j Current density

$j_{acel}$  Current density used in accelerated tests

$j_{max}$  Maximum current density

$J_E$  Flux of metal atoms due to EM

jL Blech product

$jL_c$  Blech product threshold

k Boltzmann's constant

$k_i$  Thermal conductivity of the insulator

$k_m$  Thermal conductivity of the metal

$k_{eff}^{beol}$  Effective thermal conductivity of the BEOL

$k_{eff}^{int}$  Effective thermal conductivity of the metal

$k_{eff}^{via}$  Effective thermal conductivity of the via

L Length of the interconnect lines

$L_n^{int}$  Height of the interconnects for a particular layer n

$L_n^{via}$  Height of the vias for a particular layer n

$l_v$  Length of the void

m Total number of interconnect layers

$MTTF_{acel}$  Interconnect lifetime considering the results obtained from accelerated

tests

$MTTF_{use}$  Interconnect lifetime estimated for normal use conditions

n Current density exponent

$N_{via}$  Number of vias

$P_T$  Power dissipated by transistors

T Temperature

$T_0$  Reference temperature

$T_{acel}$  Temperature used in accelerated tests

$T_{max}$  Maximum temperature in the interconnect lines

$t_b$  Diffusion barrier thicknesses

$v_{EM}$  Atomic drift velocity due to the EM driving force

$V_{int}$  Volume fraction of the metal lines

$V_{TH}$  Threshold voltage

$V_{via}$  Volume fraction of the vias

w Width of the interconnect lines

$W_i$  Calculated width of the metal lines for the maximum current density

$W_{jL}$  Calculated width of the metal lines for the Blech product

$W_r$  Calculated width of the metal lines for the maximum resistance change

$w_{min}$  Minimum width of the technology

$W_{via}$  Width of the vias

$w_b$  Width of the diffusion barrier

z Distance in the BEOL from heat source

$Z^*$  Represents the sign and the magnitude of the momentum transfer be-

tween the conducting electrons and the metal atoms

$\alpha$  Linear temperature coefficient of the metal

$\alpha_b$  Linear temperature coefficient of the barrier layer resistivity

$\eta$  Dimensionless parameter used to estimate the  $k_{eff}^{int}$

$\beta$  Dimensionless parameter used to estimate the  $k_{eff}^{int}$

$\Delta R$  Resistance variation

$\Delta R/R_0$  Resistance change ratio

$(\Delta R/R_0)_{crit}$  Critical resistance change ratio

$\Delta t$  Time variation

$\Delta T_{acel}$  variation in relation to the reference temperature

$\Delta T_{PT}$  temperature change in metallic layer due to the  $P_T$

$\Delta T_{use}$   $T_{use}$  variation in relation to the reference temperature

$\Omega$  Atomic volume

$\phi_{int}$  Volume fraction of the metal layers

$\phi_{via}$  Volume fraction of the via layers

$\rho_b$  Resistivity of the barrier layer

$\rho$  Resistivity of the interconnect metal

$\rho_0$  Resistivity at the reference temperature

$\sigma_0$  Initial stress in the metal line

$\sigma_{th}$  Maximum stress the metal line can with stand

## Contents

| Lis | st of | Figures                                                                          | 12         |

|-----|-------|----------------------------------------------------------------------------------|------------|

| Lis | st of | Tables                                                                           | 18         |

| 1   | Intr  | oduction                                                                         | 28         |

|     | 1.1   | Brief Overview of Integrated Circuits' Reliability                               | 28         |

|     | 1.2   | Integrated Circuit Scaling                                                       | 33         |

|     | 1.3   | Back-end-of-line and Front-end-of-line Structures                                | 33         |

|     | 1.4   | Electromigration Damage on the Wires                                             | 35         |

|     | 1.5   | State of the Art of Interconnects and Electromigration                           | 36         |

|     | 1.6   | Thesis Statement and Contributions                                               | 38         |

|     | 1.7   | Outline of the Thesis                                                            | 39         |

| 2   | Fun   | damentals of Electromigration                                                    | <b>4</b> C |

|     | 2.1   | The Electromigration Phenomenon                                                  | 40         |

|     | 2.2   | Impact of the Current Density                                                    | 44         |

|     | 2.3   | Impact of the Temperature                                                        | 46         |

|     |       | 2.3.1 Self-Heating from Transistors                                              | 47         |

|     |       | 2.3.2 Joule Heating in the Interconnects                                         | 48         |

|     | 2.4   | Impact of Electromigration on Wire Resistance                                    | 49         |

|     |       | 2.4.1 Interconnect Structure                                                     | 50         |

|     |       | 2.4.2 Interconnect Resistance Variation                                          | 52         |

|     | 2.5   | Interconnect Lifetime                                                            | 54         |

|     |       | 2.5.1 Time-to-Failure of Interconnects                                           | 55         |

|     |       | 2.5.2 Electromigration Statistical Distribution                                  | 58         |

|     | 2.6   | Parasitic Extraction of the Interconnects                                        | 58         |

| 3   | Met   | hodology to Evaluate the Impact of Electromigration on Chips during              |            |

|     | Des   | gn                                                                               |            |

|     | 3.1   | Traditional EM Methodology                                                       | 61         |

|     | 3.2   | Estimation of an Interconnect Resistance Change due to EM                        | 63         |

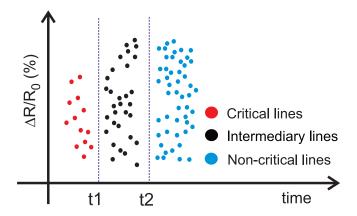

|     | 3.3   | Description of an IC Performance Change under EM                                 | 66         |

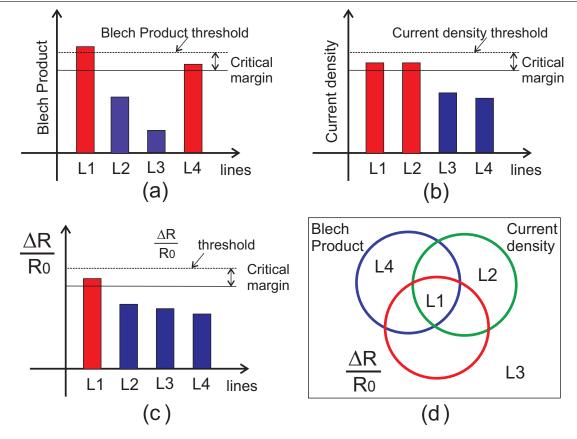

|     | 3.4   | Identification of the Critical Lines based on EM Criteria                        | 68         |

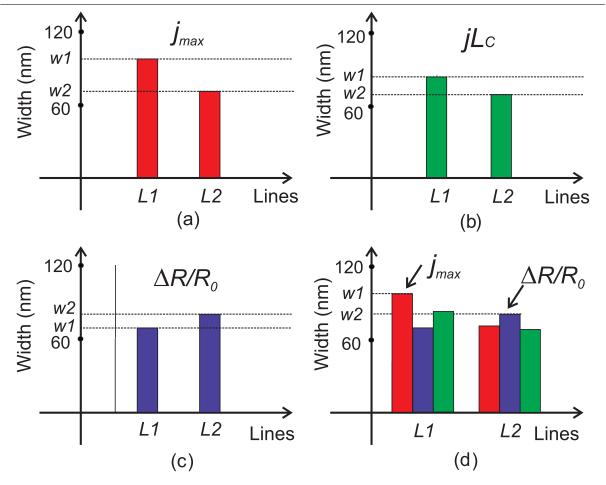

|     | 3.5   | Evaluation of Interconnects' Dimensions                                          | 70         |

|     | 3.6   | Evaluation of the EM Critical Blocks                                             | 72         |

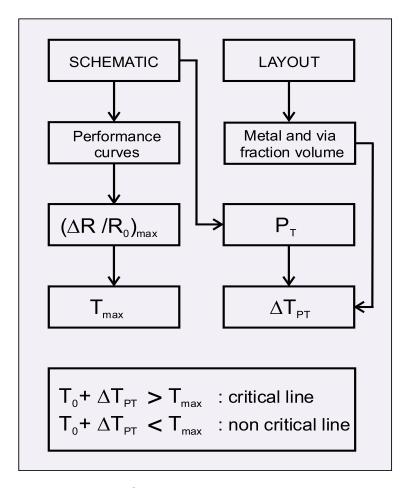

|     | 3.7   | EM Methodology Flow                                                              |            |

| 4   | Ana   | lysis of the Temperature Estimation $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 75         |

|     | 4.1   | Temperature Distribution on BEOL Interconnects                                   | 75         |

| 4.2                                               | Impact                                                                                                                              | of the Temperature Estimation on $\Delta R/R_0$                                                                                                                                                                                                                 |  |  |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 4.3                                               | Evaluat                                                                                                                             | ion of Critical Blocks based on the Temperature                                                                                                                                                                                                                 |  |  |

| Elec                                              | tromigra                                                                                                                            | ntion Evaluation Tool                                                                                                                                                                                                                                           |  |  |

| 5.1                                               | Tool De                                                                                                                             | scription                                                                                                                                                                                                                                                       |  |  |

| 5.2                                               | Tool Ap                                                                                                                             | oplication for a Line of an Operational Amplifier 89                                                                                                                                                                                                            |  |  |

| 5.3                                               | Tool Ap                                                                                                                             | oplication for an Operational Amplifier                                                                                                                                                                                                                         |  |  |

| Elec                                              | tromigra                                                                                                                            | ntion Impact on Circuits and Technology: Study Cases 102                                                                                                                                                                                                        |  |  |

| 6.1                                               | Evaluat                                                                                                                             | ion of a Ring Oscillator under Electromigration                                                                                                                                                                                                                 |  |  |

| 6.2                                               | Evaluat                                                                                                                             | ion of a Bandgap Circuit under Electromigration                                                                                                                                                                                                                 |  |  |

| 6.3                                               | Evaluat                                                                                                                             | ion of an Operational Amplifier under Electromigration 109                                                                                                                                                                                                      |  |  |

| 6.4                                               | Evaluat                                                                                                                             | ion of the Temperature in a 45nm Technology                                                                                                                                                                                                                     |  |  |

|                                                   | 6.4.1                                                                                                                               | Temperature Change of the Local Layers with Volume Fraction                                                                                                                                                                                                     |  |  |

|                                                   | 7                                                                                                                                   | Variation on a Single Layer                                                                                                                                                                                                                                     |  |  |

|                                                   | 6.4.2                                                                                                                               | Effective Thermal Conductivity of the BEOL                                                                                                                                                                                                                      |  |  |

|                                                   | 6.4.3                                                                                                                               | Temperature Change of the Local Layers with Volume Fraction                                                                                                                                                                                                     |  |  |

|                                                   | 7                                                                                                                                   | Variation on All Layers                                                                                                                                                                                                                                         |  |  |

| 6.5                                               | Compar                                                                                                                              | rision of Technologies and the State of the Art                                                                                                                                                                                                                 |  |  |

| Con                                               | clusion a                                                                                                                           | and Outlook                                                                                                                                                                                                                                                     |  |  |

| 7.1                                               | Future                                                                                                                              | work perspectives                                                                                                                                                                                                                                               |  |  |

| 7.2                                               | Publica                                                                                                                             | tions                                                                                                                                                                                                                                                           |  |  |

|                                                   |                                                                                                                                     |                                                                                                                                                                                                                                                                 |  |  |

| oliogr                                            | ranhy .                                                                                                                             |                                                                                                                                                                                                                                                                 |  |  |

| _                                                 |                                                                                                                                     | Resistance Change of a Metal Line due to EM                                                                                                                                                                                                                     |  |  |

|                                                   |                                                                                                                                     | Blech Product                                                                                                                                                                                                                                                   |  |  |

|                                                   |                                                                                                                                     | ITRS Roadmap                                                                                                                                                                                                                                                    |  |  |

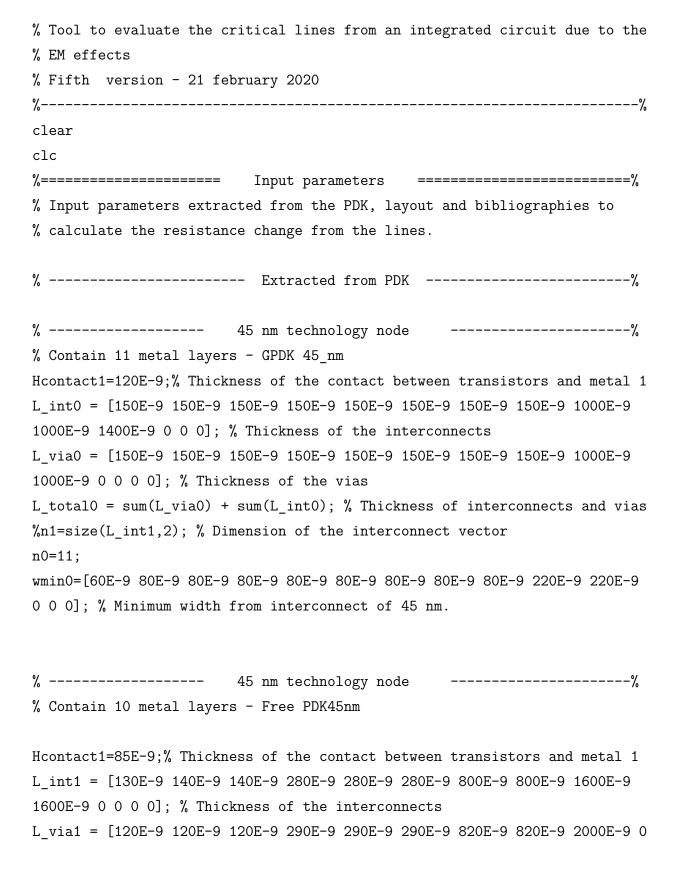

| APPENDIX D Algorithm                              |                                                                                                                                     |                                                                                                                                                                                                                                                                 |  |  |

| APPENDIX E Dual-Damascene Fabrication Process     |                                                                                                                                     |                                                                                                                                                                                                                                                                 |  |  |

| APPENDIX F $\eta$ and $\beta$ for $\Delta T_{PT}$ |                                                                                                                                     |                                                                                                                                                                                                                                                                 |  |  |

| APPENDIX G Interconnects of the Opamp             |                                                                                                                                     |                                                                                                                                                                                                                                                                 |  |  |

|                                                   | 4.3<br>Electron 5.1<br>5.2<br>5.3<br>Electron 6.2<br>6.3<br>6.4<br>6.5<br>Con 7.1<br>7.2<br>PEN PEN PEN PEN PEN PEN PEN PEN PEN PEN | 4.3 Evaluat  Electromigra 5.1 Tool De 5.2 Tool Ap 5.3 Tool Ap 6.1 Evaluat 6.2 Evaluat 6.2 Evaluat 6.4 Evaluat 6.4.1 Tool 6.4.2 Door to the conclusion of 7.1 Future of 7.2 Publicat  Diography . PENDIX A PENDIX B PENDIX C PENDIX C PENDIX C PENDIX E PENDIX F |  |  |

### 1 Introduction

In this chapter, the aspects that lead the electromigration (EM) to be a critical issue for integrated circuits (ICs) is presented. The increased importance of the EM with the technology development is described based on the International Technology Roadmap for Semiconductors (ITRS) reports. These reports have motivated the EM research resulting in an increased number of publications in leading IC magazines and conferences. As a consequence, the reliability analysis of ICs becomes more accurate at each new technology node.

### 1.1 Brief Overview of Integrated Circuits' Reliability

Reliability is the quality of being trustworthy or of performing consistently well [3]. The reliability evaluation of an IC is a complex task and should be taken into account during the design, fabrication, and test procedures. The continuous improvement of the failure rates to extend the chip lifetime intensifies the reliability evaluation complexity [4]. The semiconductor industry considers new procedures to maintain the IC reliability at each new technology node, as the EM effects and other issues become more relevant in a smaller chip with a higher density of devices [5–7].

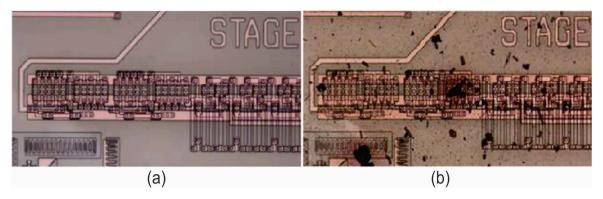

Extreme environmental conditions of radiation, pressure and temperature affect the reliability of ICs and shorten the chip lifetime. In 2016, NASA engineers evaluated an IC under a temperature (460 °C) and a pressure (9.4 MPa) similar to Venus [8]. Figure 1.1 shows that the IC was significantly deteriorated after 521 hours, but still maintained its functionality at the end of the test. The success of the interplanetary expeditions is highly dependent on the reliability of ICs.

Figure 1.1 – Electronic circuit before (a) and after (b) be evaluated under harsh conditions similar to Venus [8].

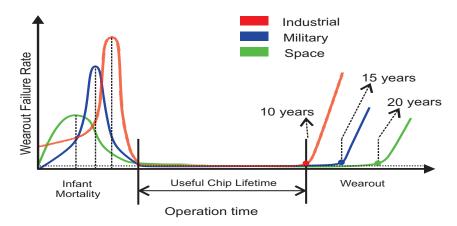

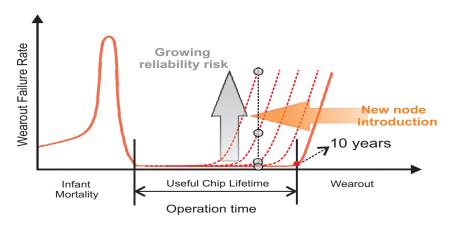

Figure 1.2 shows the three typical stages of a reliability bathtub curve of a chip. At the infant mortality stage, the failure rate increases, reaches a maximum value and then decreases [9]. During the regular operation stage, the chip suffers random failures and the failure rate is normally insignificant. It is important to note that the regular phase is longer for military and space than for commercial applications. At the wearout stage, the failure rate increases due to the aging effects. With the introduction of new technology nodes, the wear-out failure curve moves to the left, which means earlier device degradation and reduced chip lifetime, as shown in Figure 1.3 [9].

The aging effects of a chip is a consequence of different stress sources, mainly mechanical, thermal, and electrical. Nevertheless, improvements in the fabrication and design methodology minimize these effects [10–12]. In the design phase, the designer analyzes the aging effects and adjust the circuit using electronic design automation (EDA) tools. In practice, these tools allow the designer to choose the devices, architectures, geometries of the interconnects and transistors and, most fundamentally, to simulate the voltage, current, temperature and other stimuli applied to the circuit during operation. As long as the EDA tools are systematically released to incorporate new methods and models, the IC designer considers different aging effects in the circuit analysis.

Figure 1.2 – Reliability bathtub curves of a chip for different applications [9].

Figure 1.3 – Bathtub curve change with the introduction of a new technology node [9].

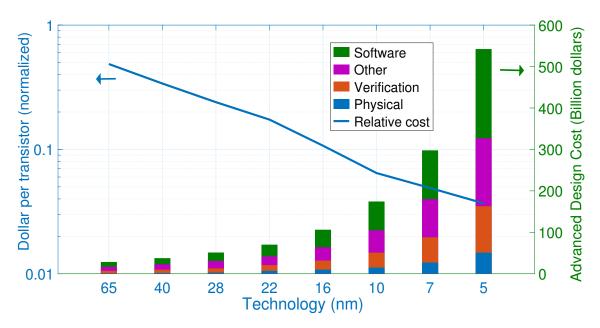

Although the cost of chip production, including the expenses with wafer, mask, test, and package increased with the technology downscaling, the relative cost to produce a transistor decreased. Figure 1.4 shows the chip cost per transistor evolution with the technology [13, 14]. Observe that the transistor cost in an advanced circuit, such as graphics processing unit (GPU), central processing unit (CPU), or system on a chip (SoC), reduced 12.5 times from 65 nm to 10 nm technology. The higher density of transistors in the new technologies compensates for the increased cost to create a new advanced circuit. As a result, the relation dollar per transistor, named relative cost, reduces in each new technology node.

The IC design corresponds to a significant percentage of the cost to create a new advanced circuit. Figure 1.4 shows the IC design evolution in four groups: software, verification, physical and other [13]. The group named other involves the prototype, validation, architecture, and intellectual property (IP) qualification. Note that the investment to design a chip depends on the technology used. While the cost to design in 40 nm is 37.7 million dollars, in 10 nm, this value increases to 174.4 million, 4.6 times more expensive. The increased investments are due to the need to guarantee the reliability of the circuits in modern technologies.

The number of publications in the leading microelectronic journals and conferences denotes the relevance of the research on IC reliability. Figure 1.5 shows the number of publications in the IC reliability field in three periods organized into three groups: device, interconnect, and the other, the latter referring to circuit-level reliability and electrostatic discharge (ESD) reliability, for example [15]. Together with the significant increase in the number of publications regarding IC reliability, the reliability of interconnects became the

Figure 1.4 – Costs of transistors and EDA tools for different technology nodes [13, 14].

Figure 1.5 – Number of papers published in leading journal and conferences related to IC reliability [15].

most studied subject, with 38% of the publications in the period 2011 to 2017.

Hot carrier injection (HCI), negative bias temperature instability (NBTI), in addition to positive bias temperature instability (PBTI) and time-dependent dielectric breakdown (TDDB) are degradation effects that cause aging in the transistors. Below 90 nm, the analysis of these effects is a requisite for design flows targeting quality and reliability [16]. These reliability effects modify essential parameters, such as the threshold voltage and the mobility factor [17]. These changes affect timing delays, power, frequency, leakage, linearity, gain, and every possible specification that may appear in digital, analog, or RF design.

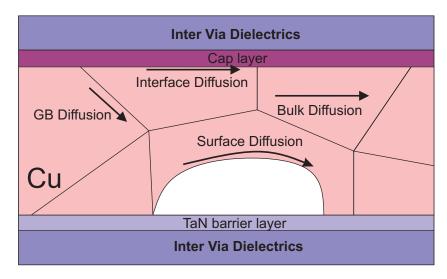

Electromigration, stressmigration, and thermomigration are aging effects in interconnects. Discovered by Gerardin in 1861, the electromigration became well-known in the 1960s, when on-chip aluminum (Al) interconnects were observed to fail in the presence of electric current [18, 19]. In the 1980s, the degradation of the interconnects due to the stress gradients became an important issue [20]. This failure mechanism, named stressmigration, is driven by the hydrostatic stress gradient generated in the lines and does not require electron flow to occur. In turn, the thermomigration is the failure mechanism due to the presence of a thermal gradient [21]. In general, the combinational effect of stressmigration, thermomigration, and electromigration cause line failure.

The semiconductor industry used different materials in the integrated circuit to boost circuit performance and reliability. Al lines were the industry standard until 1997, when IBM introduced the copper (Cu) interconnect technology [22]. With the reduction

Figure 1.6 – Evolution of the minimum interconnect width in five decades based on Intel processors, from the 10  $\mu$ m until the 10 nm technology node [24].

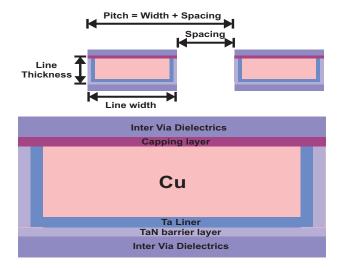

of the interconnect dimensions, Cu interconnects became more appropriate, since Cu is a better conductor than Al. Cu lines reduce the propagation delays and power consumption leading to ICs with better performance. The transition from Al to Cu leads to significant developments of the fabrication techniques, including the introduction of tantalum (Ta) and tantalum nitride (TaN) barrier metal layers to isolate the silicon from the Cu atoms [23].

Figure 1.6 shows the evolution of the minimum interconnect width in five decades based on Intel processors, from the 10  $\mu$ m until the 10 nm technology node [24]. As the metal line width was reduced, the current density through them increased. The maximum current density estimated by ITRS was 1.32 MA/cm<sup>2</sup> for 22 nm technology. For 14 nm, the maximum current density increased to 1.68 MA/cm<sup>2</sup> [25]. Although the IC's became more compact with better performance, the interconnect shrinking resulted in a more severe EM, as the elevated current density accelerates the EM damage [26–28].

The high compatibility and gain of performance with the interconnect and transistor shrinking is better observed in advanced circuits, like microprocessors. Figure 1.7 illustrates the power, frequency and number of transistors in microprocessors with the technology evolution [29]. There are two interesting points to note. First, power and frequency change became flat after 2005, with the development of the multi-core processors, an essential condition to maintain a lower temperature and improve chip reliability. Second, the transistor count still follows the exponential growth line, following Moore's Law for five decades with some adjustments.

Figure 1.7 – Evolution of power, frequency and number of transistors in microprocessors with the technology evolution [29].

#### 1.2 Integrated Circuit Scaling

The interconnect resistance increase with the metal line shrinking degrades the RC delay and the signal propagation. As the RC delay of the interconnect becomes longer than the gate delay for technologies below 100 nm, the reduction of the capacitance of the interconnects becomes a priority [30]. In order to reduce the capacitance and to achieve an RC delay target, the recent technologies employ insulators with lower dielectric constants. Ultra low-k (ULK) dielectrics applied in high-performance circuits below the 65 nm technology minimize the capacitance and, as a consequence, the RC delay and the cross-talk [31].

Besides the dielectric constant reduction, the attenuation of the RC delay increase includes the use of thinner barriers, the reduction of the line sheet resistance and the improvement in circuit design. A thinner barrier maximizes the copper volume and minimizes the line resistance increase. In turn, the use of copper alloy reduces sheet resistance in comparison to aluminum alloy. In terms of circuit design, the signal propagation along the line improves with the introduction of repeaters within the interconnects and the use of interconnect line shielding techniques [32].

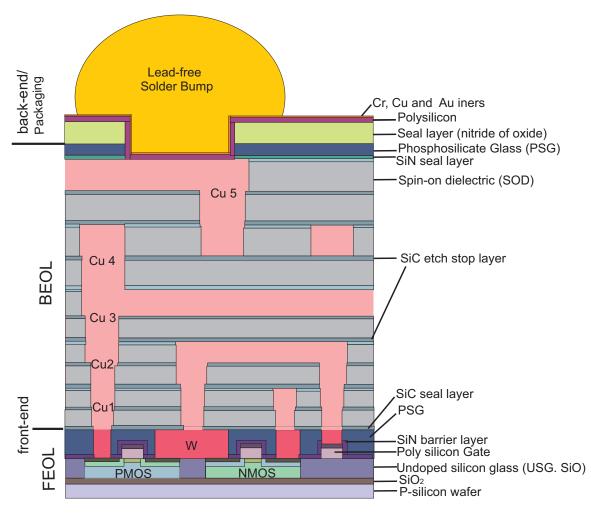

#### 1.3 Back-end-of-line and Front-end-of-line Structures

Figure 1.8 shows the front-end-of-line (FEOL) and back-end-of-line (BEOL) of a chip structure [33]. The BEOL composes the solder bump used for flip-chip (FC)

Figure 1.8 – FEOL and BEOL of a CMOS chip structure [33].

bonding, connecting the chip and substrate and also providing a heat dissipation path from the chip. Below the solder bump, a more extensive passivation layer protects the chip from the moisture and external impact. The BEOL corresponds to the region forming the interconnects layers, including dielectric insulators and metal/via layers. The FEOL corresponds to the devices in the substrate, transistors, capacitors, resistors, and inductors. The primary purpose of the BEOL is to realize the interconnection of the devices in the FEOL.

Advanced BEOL processes generally prescribe a maximum number of metalization layers, including the local, intermediate, and global lines. Each of these lines have different thicknesses based on their electrical functions. The local lines connect the circuit elements that are close to each other, and have the tightest linewidths and the roughest topography [30]. The local lines are generally subjected to the highest temperatures, since they are the nearest from the active area. In turn, the global layers distribute the supply voltage and transmit the clock and global signals of the chip. As the global lines conduct the highest currents of the circuit, these lines are fabricated with larger dimensions to avoid the EM.

While the vias connect the different metalization layers, the contact plugs connect the device in the substrate to the first metal layer. In Figure 1.8, tungsten (W) and Cu fill the contact plugs and vias, respectively. Tungsten is used to fill plugs due to the high thermal conductivity and low thermal expansion [34]. As the contact plugs are filled with a material different from the Cu interconnects, a separate step is required to fill the contact plugs. Besides via and contact layers, the BEOL contains interlayer dielectrics, barrier layers, adhesion layers, plug layers, and a passivation layer.

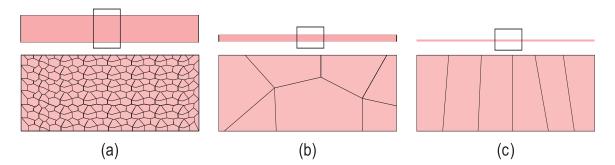

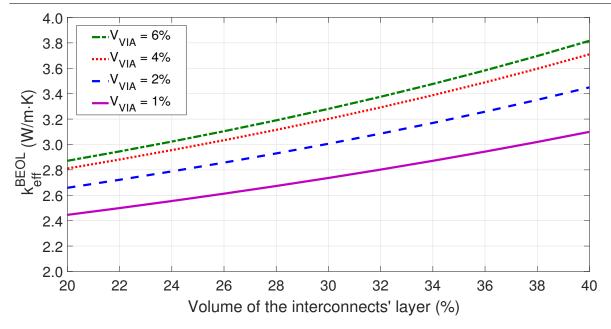

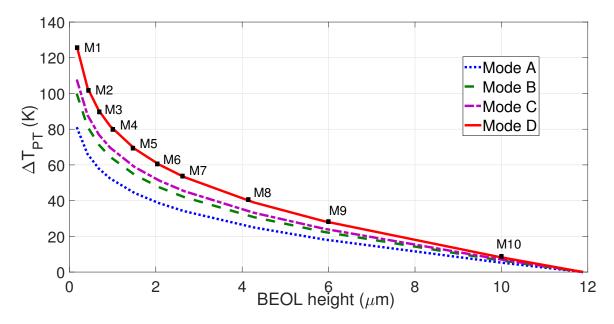

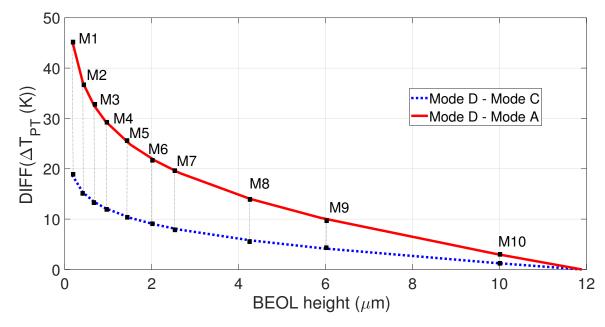

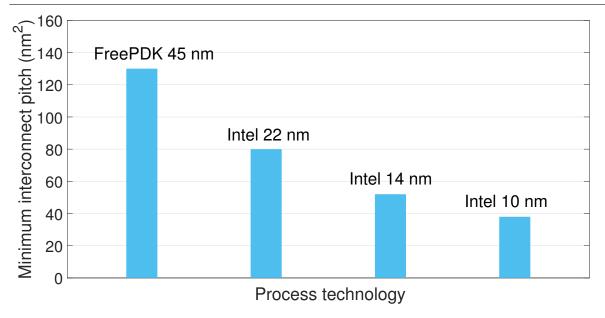

### 1.4 Electromigration Damage on the Wires