# CHARACTERISATION AND STABILITY OF MESFETS FABRICATED ON AMORPHOUS INDIUM-GALLIUM-ZINC-OXIDE

## By

## **Matthew David Whiteside**

A thesis submitted in partial fulfilment of the requirements of the degree of

# **Master of Engineering**

in

# **Electrical and Electronic Engineering**

at the

**University of Canterbury**

Christchurch, New Zealand

March 2014

#### **ACKNOWLEDGEMENTS**

I'd like to thank my supervisor Dr Martin Allen, whose guidance and support has helped keep me on track throughout my graduate studies. I'd also like to thank my office mates, Robert Heinhold, Salim Elzwawi, Tom Cronje, Alana Hyland and Max Lynam who were always willing to lighten the mood whenever nothing seemed to work. Without the assistance of postdoctoral fellow Dr Giang Dang, who was always willing to bounce around ideas and offer support whenever needed, I'm sure my results would have suffered.

The entire Nanolab group deserves my thanks for always making the working environment enjoyable, and offering moral support and technical guidance whenever required. I'd like to thank Helen Devereux and Gary Turner especially for their help in the lab, always willing to offer assistance whenever something went wrong.

Finally, I'd like to thank my friends and family, for without their encouragement and support none of this would have been possible.

#### **ABSTRACT**

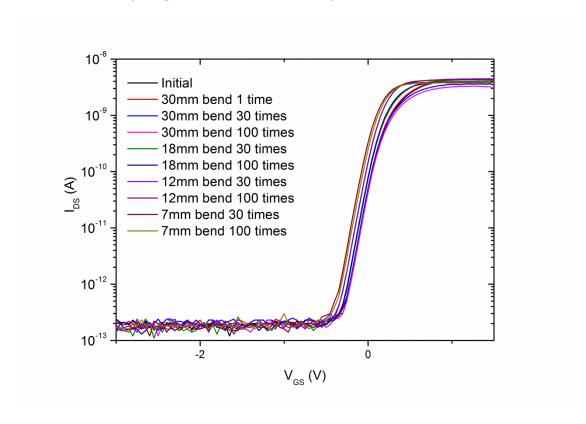

Indium-Gallium-Zinc-Oxide (a-IGZO) is an amorphous oxide semiconductor that has been attracting increasing attention for use in flat panel display and optoelectronic applications. This is largely due to IGZO's high mobility at low processing temperatures. In this thesis, IGZO films were successfully grown on polyethylene naphthalate (PEN) substrates by RF magnetron sputtering at room temperature. These films were flexible, transparent and had a good Hall mobility (5-12 cm<sup>2</sup>/Vs). High quality metal oxide Schottky contacts were fabricated on these as-grown IGZO/PEN films with on-off rectification ratios of up to 10<sup>8</sup>. These were then used as the gate contacts in transparent metal semiconductor field effect transistors (MESFETs). The performance and device stability of these IGZO/PEN MESFETs were investigated via a series of stress tests in both dark conditions and under illumination at different wavelengths in the visible spectrum. During constant voltage stress testing under illumination, the threshold voltage shifted by -0.54 V and 0.38 V for negative and positive gate biasing, respectively. These shifts proved reversible when devices were left in dark conditions for extended periods of time. The effect of persistent photoconductivity after exposure to different illumination sources was examined, with three potential passivation coatings to reduce this unwanted effect explored. Transparent IGZO/PEN MESFETs with an absolute transmission of up to 75% were achieved with the use of ITO ohmic contacts. These devices survived mechanical bending down to a radius of 7 mm with negligible variation in on-current and threshold voltage. This allows for the possibility of incorporating their use in future applications such as flexible transparent electronics.

# TABLE OF CONTENTS

| Chapter                               | Page                 |

|---------------------------------------|----------------------|

| Acknowledgements                      | ii                   |

| Abstract                              | iii                  |

| List of Tables                        | vi                   |

| List of Figures                       | vii                  |

| 1. Introduction                       | 1                    |

| 2. Background Information             | 5                    |

| 2.1 Oxide Semiconductors              | 7<br>10              |

| 3. IGZO Growth and Device Fabrication | 17                   |

| 3.1 Substrate Preparation             | 18<br>20<br>24       |

| 4. Device Characterisation            | 30                   |

| 4.1 Schottky Gate Analysis            | 34<br>35<br>38<br>42 |

| 5. MESFET Stress Testing              | 50                   |

| 5 1 Gate Rias Stress Testing          | 50                   |

| 5.2 Constant Voltage Bias Stress Testing                      | 53 |

|---------------------------------------------------------------|----|

| 5.2.1 Constant Voltage Bias Stress Testing in Dark            | 53 |

| 5.2.2 Constant Voltage Bias Stress Testing under illumination |    |

| 5.3 Possible Causes of Stress shifts                          |    |

|                                                               |    |

| 6. PPC and Passivation                                        | 62 |

| 6.1 Persistent Photoconductivity                              | 62 |

| 6.1.1 Persistent Photoconductivity Effect                     | 62 |

| 6.1.2 Attempted recovery test                                 | 65 |

| 6.2 Passivation Layers                                        | 67 |

| 6.2.1 Device fabrication                                      | 67 |

| 6.2.2 Passivation comparison                                  | 68 |

| 7. Transparent Flexible MESFETs                               | 73 |

| 7.1 Transmission                                              | 73 |

| 7.2 Transparent Devices                                       | 76 |

| 7.3 Flexibility                                               | 79 |

| 8. Conclusion and Future work                                 | 83 |

| 8.1 Conclusion                                                | 83 |

| 8.2 Future Work                                               |    |

| Bibliography                                                  | 87 |

| Appendix A                                                    | 93 |

# LIST OF TABLES

| Table                                                                                                                                                                                                                                                                                  | Page                    |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| <b>Table 3.1</b> - Growth comparison of IGZO over a range of settings. Notes: 1) in 0.14SCCM of O <sub>2</sub> was added to the growth. 2) Liquid N <sub>2</sub> was used to further records pressure. 3) The plasma for this and subsequent growths was unstable, so no fit produced. | luce the base<br>lm was |  |  |

| <b>Table 3.2 -</b> XPS results for IGZO films grown using various RF sputtering powthe nearest percent. The values of C were estimated from the valance band registering survey scans which consist of 2 to 3 data points for each linear fit                                          | ions of the             |  |  |

| Table 4.1 - Gate comparison information.                                                                                                                                                                                                                                               | 42                      |  |  |

| Table 4.2 - Gate comparison upon aging.                                                                                                                                                                                                                                                | 44                      |  |  |

| Table 7.1 - Comparison between devices fabricated using different contact thic                                                                                                                                                                                                         | cknesses77              |  |  |

# LIST OF FIGURES

| Figure Page                                                                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 1.1</b> - Publications by year with the topic 'IGZO' as reported by web of science3                                                                                             |

| <b>Figure 2.1</b> – Examples of conducting paths for a) covalent bonding such as silicon and b) ionic bonding such as IGZO [6]                                                            |

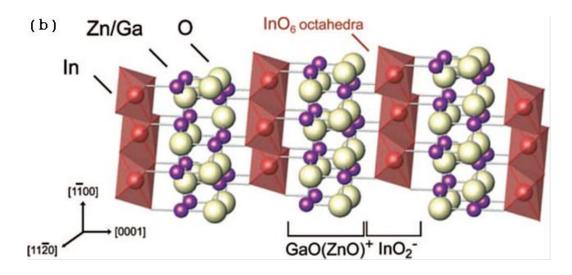

| <b>Figure 2.2</b> – a) Structure of different compositions of IGZO b) Electrical properties of IGZO Mobility (Carrier concentration 10 <sup>18</sup> ) [16] [17]                          |

| <b>Figure 2.3</b> – The structure of a) amorphous IGZO showing the dispersed nature and b) crystalline IGZO showing alternating stacked layers [20]                                       |

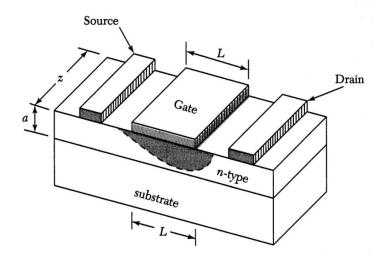

| <b>Figure 2.4</b> - Cross-section of a typical MESFET showing the linearity of the depletion region [28].                                                                                 |

| <b>Figure 3.1 -</b> Sputtering system used for the majority of depositions performed in this work                                                                                         |

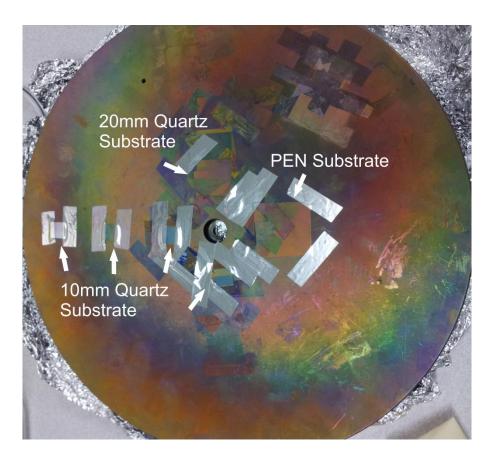

| <b>Figure 3.2 -</b> Substrate layout prior to co-sputtered deposition. The small substrates are 10x10 mm quartz while the large substrate is 30x30 mm PEN                                 |

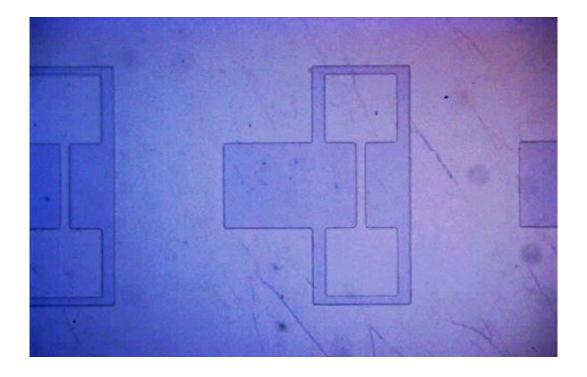

| <b>Figure 3.3 -</b> Row of devices after Mesa etching on a PEN substrate                                                                                                                  |

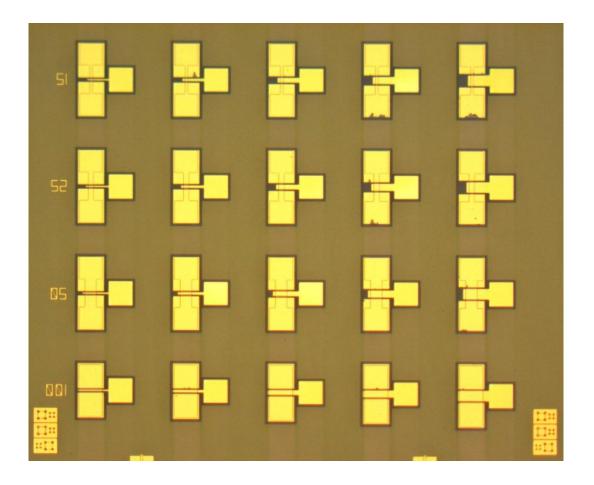

| <b>Figure 3.4</b> - Finished array of devices featuring a gold cap                                                                                                                        |

| <b>Figure 4.1</b> – Schottky diode current-voltage curve depicting forward current becoming essentially linear. The dashed line indicated the slope used to determine series resistance32 |

| <b>Figure 4.2</b> – Schottky diode current-voltage semi-log plot. The dashed line indicates the region where Equation 4.1 is valid                                                        |

| <b>Figure 4.3</b> - Output MESFET curves for the tested device                                                                                                                            |

| Figure 4.4 - Transfer curve of selected device                                                                                                                                            |

| <b>Figure 4.5 -</b> Square-root of IDS verse VGS. The intercept of the dashed line gives threshold voltage while its slope allows for mobility to be calculated                           |

| <b>Figure 4.6</b> – Comparison of Schottky diodes with channel width 100 μm and varying gate lengths and metals.                                                                          |

| Figure                                                                                                                                                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 4.7</b> – MESFET output curves and corresponding transfer curves for a) silver oxide, b platinum oxide and c) iridium oxide                                                                                              |

| <b>Figure 4.8</b> – Current-voltage characteristics of Schottky devices aged for one year under photoresist in a dark draw                                                                                                         |

| <b>Figure 4.9</b> - MESFET output curves and corresponding transfer curves after the devices were aged for 1 year for a) silver oxide, b) platinum oxide and c) iridium oxide4                                                     |

| Figure 4.10 - IV comparison of a device after aging and annealing with dimensions $W = 100$ $\mu$ m, $L = 5$ $\mu$ m.                                                                                                              |

| <b>Figure 4.11</b> – a) Transfer curves depicting initial aging and annealing of the device, b) famil of output curves for the initial device, c) the device after 4 days of aging, d) the device after annealing                  |

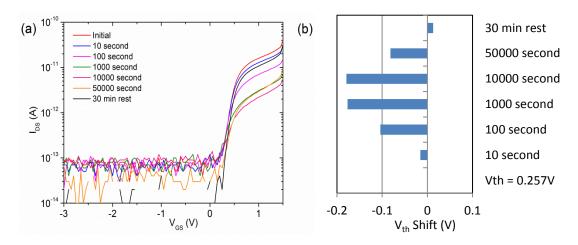

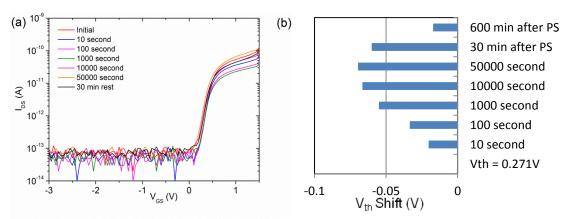

| <b>Figure 5.1</b> – Negative gate bias stress measurement results for a) transfer curves observed during stress measurements and b) threshold voltage shifts                                                                       |

| <b>Figure 5.2</b> – Positive gate bias stress measurement results for a) transfer curves observed during stress measurements and b) threshold voltage shifts                                                                       |

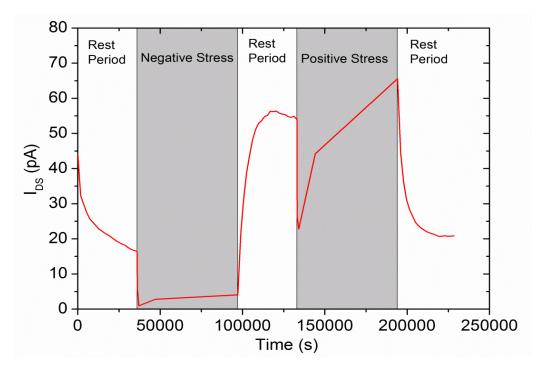

| <b>Figure 5.3</b> – On-current change over the course of the gate bias stress tests                                                                                                                                                |

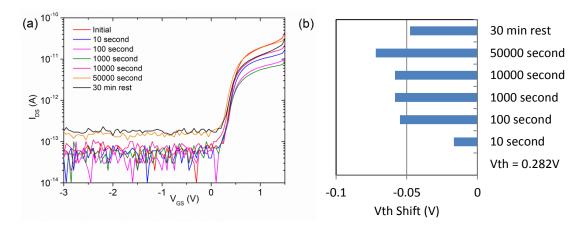

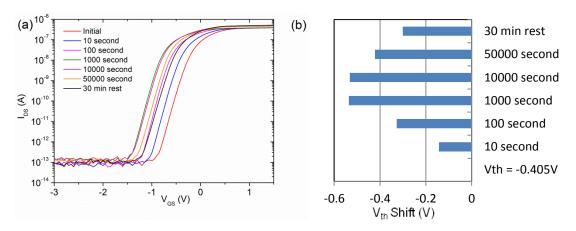

| <b>Figure 5.4</b> – Negative constant voltage bias stress measurement results for a) transfer curves observed during stress measurements and b) threshold voltage shifts                                                           |

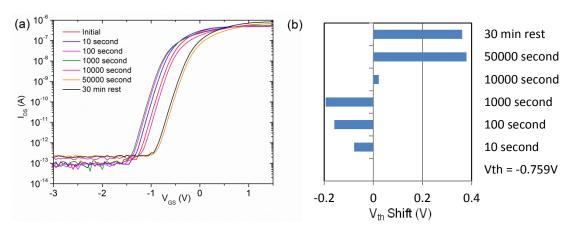

| <b>Figure 5.5</b> – Positive constant voltage bias stress measurement results for a) transfer curves observed during stress measurements and b) threshold voltage shifts                                                           |

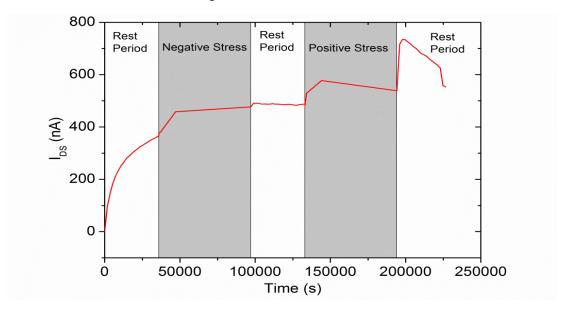

| <b>Figure 5.6</b> – On-current change over the course of the constant voltage bias stress tests5                                                                                                                                   |

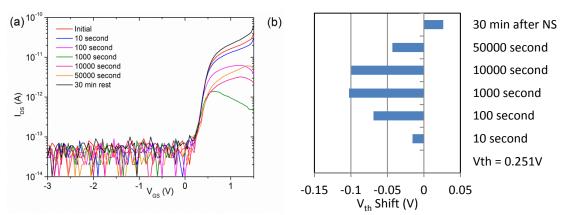

| <b>Figure 5.7</b> – Negative constant voltage bias stress while under 250 μW/cm² illumination from a 470 nm source measurement results for a) transfer curves observed during stress measurements and b) threshold voltage shifts. |

| <b>Figure 5.8</b> – Positive constant voltage bias stress while under 250 μW/cm² illumination from a 470 nm source measurement results for a) transfer curves observed during stress measurements and b) threshold voltage shifts. |

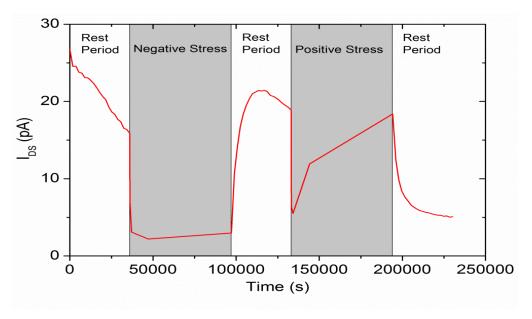

| <b>Figure 5.9</b> – Current change over the course of the constant voltage bias stress illumination tests.                                                                                                                         |

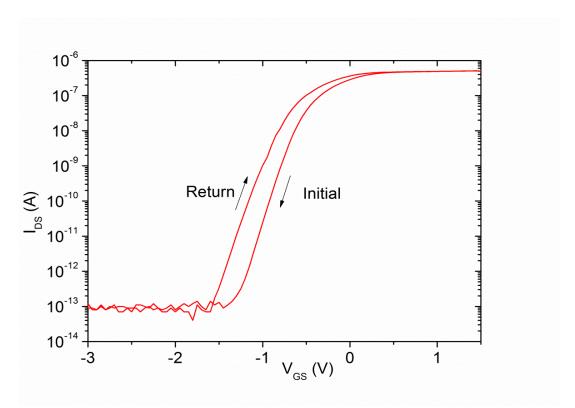

| <b>Figure 5.10</b> – Typical example of hysteresis during an illuminated constant voltage bias stress test.                                                                                                                        |

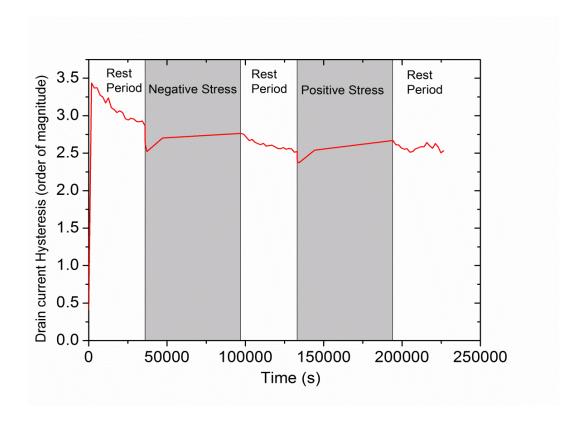

| Figure 5.11 – Maximum drain current hysteresis over time                                                                                                                                                                           |

| riguie                                                                                                                                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

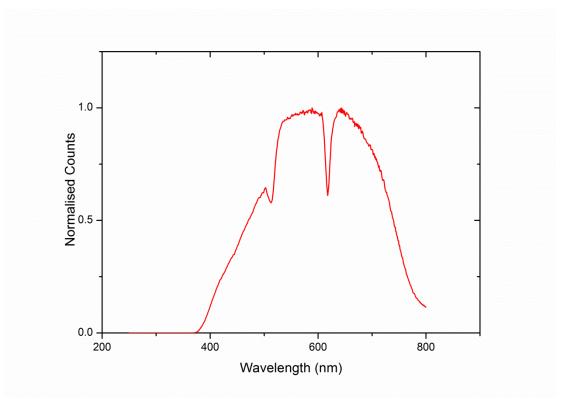

| <b>Figure 6.1</b> – Spectrum of the quartz lamp used as illumination source for PPC measurements with optical power density 20 mW/cm <sup>2</sup>                                                                |

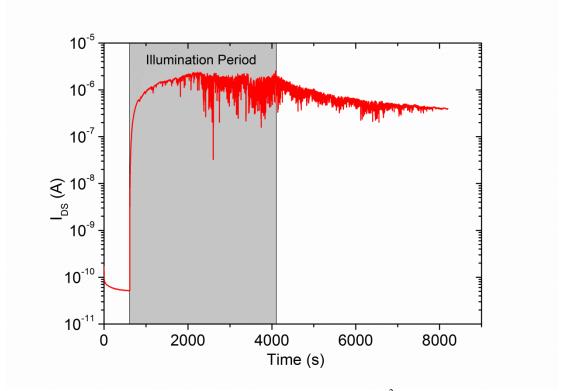

| <b>Figure 6.2</b> – Current response of a device exposed to 20 mW/cm <sup>2</sup> of illumination63                                                                                                              |

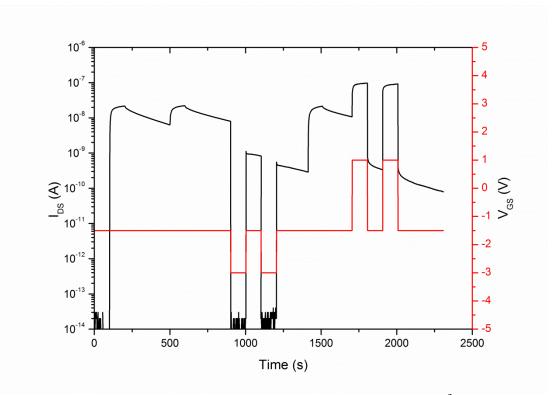

| <b>Figure 6.3</b> – Drain-source current response of a device exposed to a 20 mW/cm <sup>2</sup> illumination source, where a gate pulse is used to attempt recovery                                             |

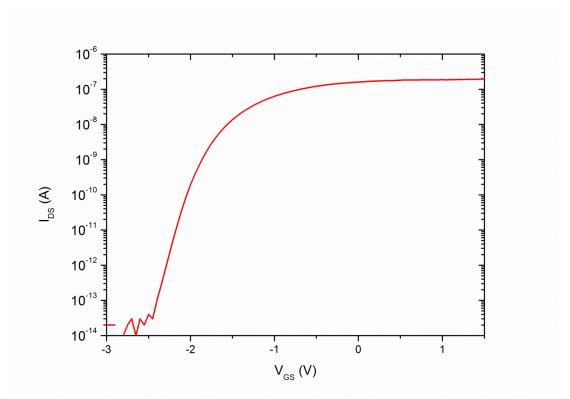

| <b>Figure 6.4</b> – Transfer curve of the device used for the recovery test                                                                                                                                      |

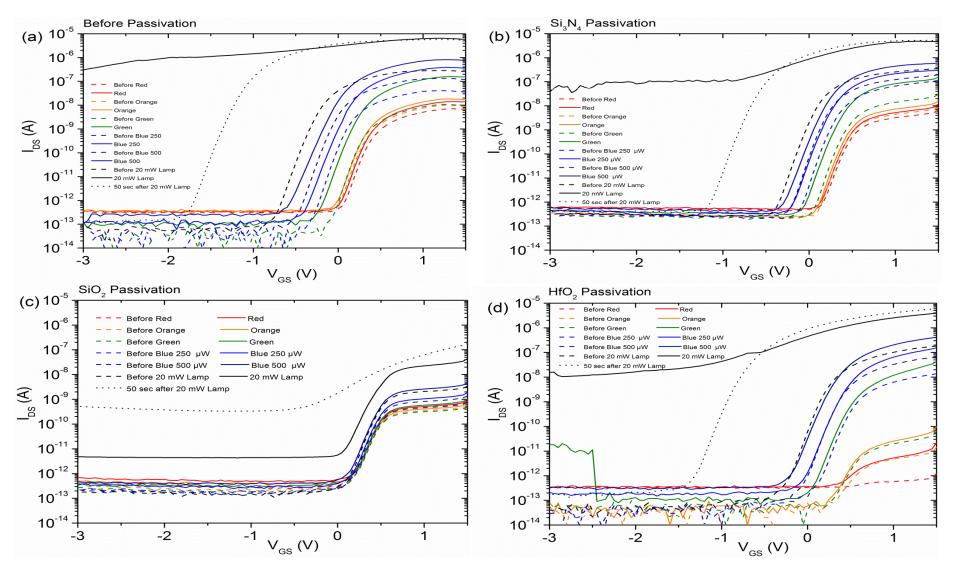

| <b>Figure 6.5</b> – Transfer curves depicting the change due to light for a) no passivation, b) Si <sub>3</sub> N <sub>4</sub> passivation, c) SiO <sub>2</sub> passivation, and d) HfO <sub>2</sub> passivation |

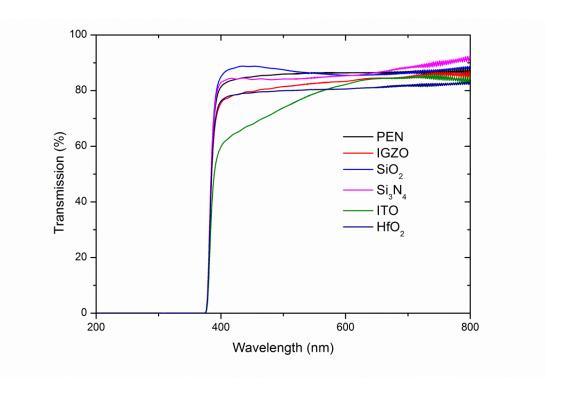

| <b>Figure 7.1 -</b> Transmission spectra of various films grown on a PEN substrate75                                                                                                                             |

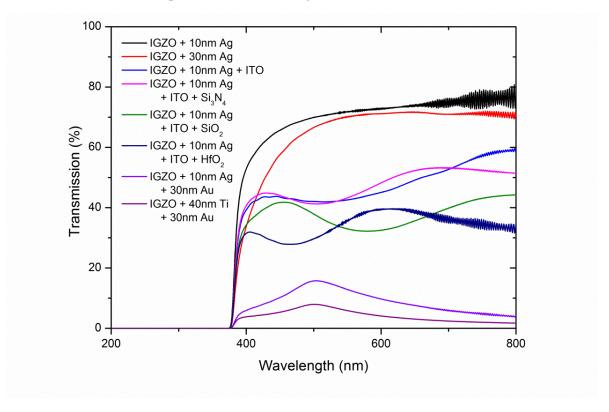

| <b>Figure 7.2</b> - Comparison between films fabricated on different thicknesses of silver. All films used a PEN substrate that fully absorbs all wavelengths below 380 nm                                       |

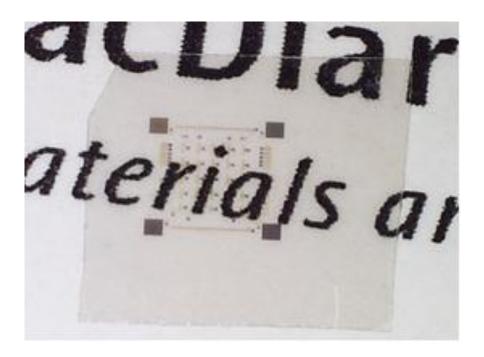

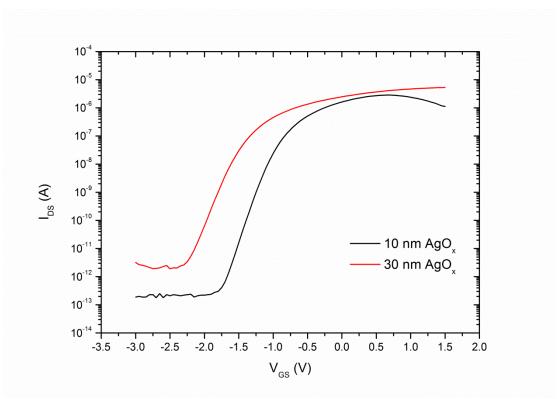

| <b>Figure 7.3</b> – Transparent MESFET devices fabricated using 10 nm AgO <sub>x</sub> Schottky gates capped with 100 nm of ITO. The drain and source contacts are 100 nm of ITO77                               |

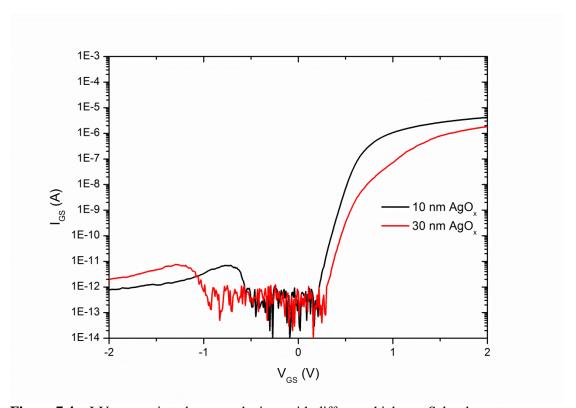

| <b>Figure 7.4</b> – I-V comparison between devices with different thickness Schottky gate contacts Devices have channel width 50 μm and Schottky gate length 5 μm                                                |

| <b>Figure 7.5</b> – Transfer curve comparison between devices with different thickness Schottky gate contacts. Devices have channel width 50 μm and Schottky gate length 5 μm                                    |

| <b>Figure 7.6</b> – Testing setup for the mechanical bending of substrates at a radius of 30 mm8                                                                                                                 |

| <b>Figure 7.7</b> – Current-voltage characteristics from flexible IGZO MESFET gate contact (with dimensions 50 μm x 10 μm) after bending at indicated radii/repetitions8                                         |

## **CHAPTER 1**

## Introduction

Today, silicon dominates the semiconductor industry. From cellular phones and laptops to TVs and dishwashers, everything runs on silicon – and for good reason, as silicon is a cheap, effective time proven technology. Consequently, considerable research and development effort is devoted to pushing silicon to its limits; however for at least one important application those limits will soon be reached: Flat-panel displays. Flat panel displays have continuously grown in size with higher and higher resolutions, and in response silicon based fabrication techniques have grown more complex to keep up with growing requirements. Unfortunately, silicon is just not able to keep up with demand.

Historically, amorphous silicon (a-Si) has been used in all flat-panel displays, and is currently still the most widely used material. While a-Si has a significantly lower mobility than polycrystalline silicon, <1 cm²/Vs [1] compared to >100 cm²/Vs [2], it is widely used because the main factors in material choice for flat-panel displays are cost and uniformity. A-Si has a reduced cost due to its fabrication at temperatures as low as 150 °C [1], unlike the high temperatures of 340 °C required for polycrystalline silicon [2]. However the main disadvantage of polycrystalline silicon that prevents its wide spread adoption are its grain boundaries that cause an unacceptable lateral variation of electrical properties, introducing uniformity issues. Unfortunately, while

its low processing temperature results in significant savings, a-Si typically has a low mobility and is unstable under both illumination and stress [3].

Silicon has served the flat-panel display industry well over the years, but nothing lasts forever. As the reign of silicon comes to an end, a new material must be sought out to fulfil the demand. The next generation of displays will be 4K screens with resolutions of at least 7680 x 4320 pixels, and high refresh rates of at least 120Hz. These requirements demand a field effect mobility of at least 3 cm<sup>2</sup>/Vs [4], which typical a-Si cannot reliably deliver. This is where amorphous oxide semiconductors (AOS) step in.

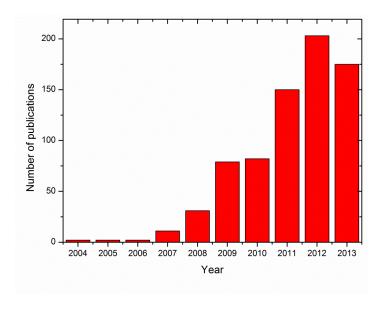

In 1996, a conducting amorphous semiconductor [5] was discovered. Since then, these semiconductors have been extensively used as transparent conducting electrodes for solar cells in the form of indium tin oxide (ITO) and zinc tin oxide (ZTO). As these transparent conductors were widely adopted, the focus of amorphous semiconductor research changed slightly; if we have transparent conductors, can we have fully transparent electronics? The first answer to this question came in 2004 when Nomura [6] first reported on the room-temperature fabrication of indiumgallium-zinc-oxide (IGZO). This opened the doors to the first potential replacement of amorphous silicon as a pixel driver for the flat-panel display industry. While initial interest in IGZO was slow, as shown in Figure 1.1, in recent years there has been a significant increase in interest. In 2012, the first IGZO LCD TV provided by Sharp [7] went into production.

Nomura [6] showed this new AOS could not only be fabricated on glass for flatpanel displays, but could also be fabricated on polymers for use in flexible electronics. Previously, the notion of transparent flexible electronics was more of a science fiction dream, but is now stepping closer to reality. Most transparent semiconductors, such as zinc oxide (ZnO), require high annealing temperatures [8] to achieve acceptable uniformity, which is not compatible with the low melting temperature of most flexible substrates. AOS's such as IGZO can be grown at room temperature with a sufficient mobility to act as a functional transistor. When combined with transparent electrodes such as ITO, it is then possible to make a fully transparent circuit.

The motivation behind this work was to fabricate and investigate the performance of metal-semiconductor field-effect transistors (MESFET) on IGZO. There has been a significant amount of research on the properties of metal-oxide-semiconductor field-effect transistors (MOSFET) fabricated on IGZO, but very little on MESFETs. By combining the transparency of thin gate layers with transparent electrodes such as ITO, a fully transparent MESFET was realised. As these devices could be fabricated at low processing temperatures, a flexible polymer was chosen as the substrate. A final goal was the production and characterisation of a fully transparent flexible MESFET.

**Figure 1.1** - Publications by year with the topic 'IGZO' as reported by web of science.

In this thesis, the following material is covered:

- Chapter 2: IGZO as a semiconductor is discussed along with its conduction mechanisms. A basic introduction into MESFETs is also given.

- Chapter 3: Covers film growth, device fabrication techniques and processes.

- Chapter 4: Several MESFET devices are characterised and their parameters are compared. There is a comparison between AgO<sub>x</sub>, IrO<sub>x</sub> and PtO<sub>x</sub> gates as well as devices fabricated on co-sputtered films.

- Chapter 5: The devices are stress tested and their stability is analysed.

- Chapter 6: Different surface passivation layers are examined and their effectiveness characterised.

- Chapter 7: Devices are fabricated on a flexible transparent substrate with transparent electrodes. The optical transmission of the devices is investigated as well as their ability to withstand bending.

## **CHAPTER 2**

## **Background Information**

## 2.1 Oxide Semiconductors

Initially, oxide semiconductors were investigated in order to find a transparent conductor for liquid crystal displays and solar panels. This led to the discovery of the first few oxide semiconductors; indium oxide (In<sub>2</sub>O<sub>3)</sub>, tin oxide (SnO<sub>2</sub>) and zinc oxide (ZnO) [9]. It wasn't until 1996 [5] that the possibility of a whole field of amorphous oxide conductors capable of delivering sufficient electrical performance to be useful in devices started to emerge. Until this point, the only amorphous oxide conductor that had attracted any attention was amorphous-In<sub>2</sub>O<sub>3</sub> [10], however its structure and properties were poorly understood.

When interest in flexible electronics increased, oxide semiconductors were considered as the semiconductor material. Polycrystalline ZnO was one obvious choice, as it was possible to produce semiconductor devices at temperatures as low as 300 °C. Unfortunately, these devices suffered from instability and uniformity issues due to grain boundaries present in the polycrystalline material. This need for better oxide semiconductors led to the discovery of 2CdO.GeO<sub>2</sub> [11], zinc tin oxide (ZTO) [12], indium zinc oxide (IZO) [13], zinc indium tin oxide (ZITO) [14] and indium gallium zinc oxide (IGZO) [6]. As these materials are amorphous semiconductors, they do not suffer grain boundary instabilities, and can be fabricated at low temperatures with high uniformity.

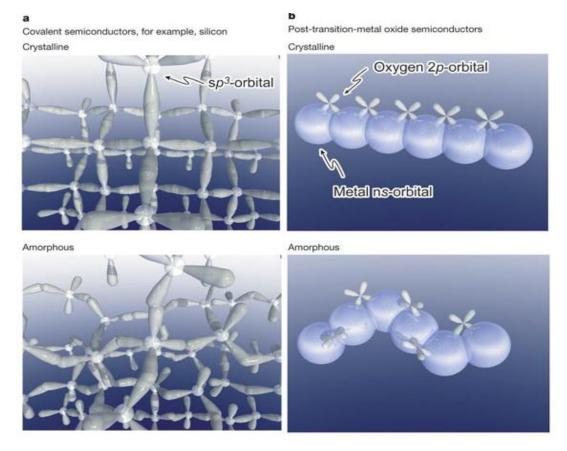

Typically, amorphous materials do not conduct nearly as well as single crystal materials, as the bonding angle usually plays an important role in the conductivity. AOSs do not suffer this malady as the conduction path is composed of the extended spherical s orbitals of heavy metal cations [5], which leads to an insensitivity to bonding angle. The special ionic bonding structure of AOSs results in a conduction path without degradation even in an amorphous state [15]. The conduction path of a-Si however is based on covalent bonding with sp3 orbitals, resulting in a strong sensitivity to bonding angle. This leads to a significant degradation of mobility when compared to single crystal silicon. These different structures are illustrated in Figure 2.1.

**Figure 2.1** – Examples of conductions paths for a) covalent bonding such as silicon and b) ionic bonding such as IGZO [6].

## 2.2 Indium-Gallium-Zinc-Oxide (IGZO)

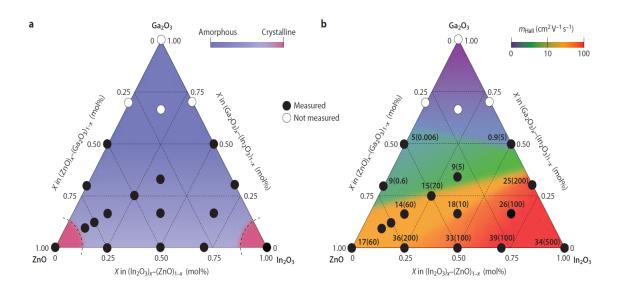

IGZO is formed from three different oxides, In<sub>2</sub>O<sub>3</sub>, Ga<sub>2</sub>O<sub>3</sub> and ZnO. In<sub>2</sub>O<sub>3</sub> and ZnO have been shown to have mobilities > 19 cm<sup>2</sup>/Vs, however when grown at room temperature both are highly polycrystalline with high carrier concentrations that are difficult to control without compensation doping [16]. Ga<sub>2</sub>O<sub>3</sub> has the opposite problem; it can be grown amorphously at room temperature but carrier doping is problematic. By combining these three materials, a conducting amorphous structure can be formed where each element plays a critical role. In<sub>2</sub>O<sub>3</sub> has a large electron density and carrier concentration that can be supressed by adding Ga<sub>2</sub>O<sub>3</sub>. ZnO has a small atomic radius, which helps disperse the conduction band energy while also promoting an amorphous structure [16]. These three components allow for the production of thin films that can be tailored for different applications, by varying the composition to control the mobility and carrier concentration, as shown in Figure 2.2.

**Figure 2.2** – a) Structure of different compositions of IGZO b) Electrical properties of IGZO Mobility (Carrier concentration 10<sup>18</sup>) [16] [17].

Initially, IGZO was investigated as a single crystal semiconductor [18], and it wasn't until 2004 [6] that IGZO became proven as an AOS. It was shown that there was a negligible difference in effective electron mobility between amorphous and crystalline IGZO [19], which supports the theory that large s-orbitals form a conduction path that is insensitive to bonding angle.

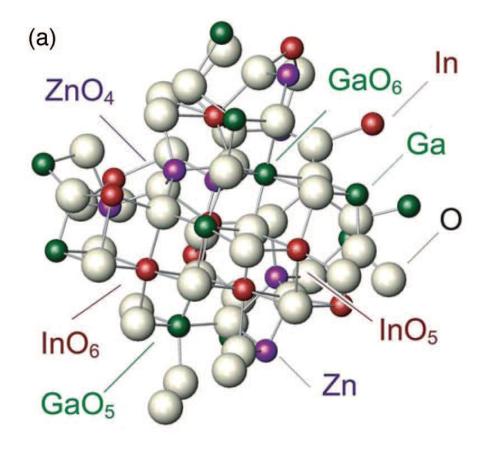

In crystalline IGZO (c-IGZO), the structure consists of alternating stacks of  $InO_2$  and GaO(ZnO)+ layers [20]. The  $InO_2$  layer found within crystalline IGZO form  $InO_6$  octahedra, with separation distances much like that found within pure  $InO_2$  crystals. The Ga and Zn ions on the other hand form trigonal-bipiramidal sites within the GaO(ZnO)+ layer. A comparison between these different structural elements can be seen in Figure 2.3. When the structure of c-IGZO was compared to that of a-IGZO, it was found that the distances between atoms were similar. It was also noted that the edge sharing network of  $InO_6$  found in c-IGZO was also present in a-IGZO. However, as the  $InO_6$  octahedra are more dispersed in a-IGZO than its crystalline counterpart, a-IGZO has a density approximately 5% lower than that of c-IGZO.

One of the issues with many AOSs such as IGZO is the photoresponse observed when exposed to photon energies above 2.3 eV, which is lower than its band gap of 3.1 eV [21]. The films become highly conductive when exposed to this illumination [22]. It is believed that this increased conductivity is due to the presence of oxygen vacancies (V<sub>0</sub>) forming gap states near the valance band. When exposed to illumination, these oxygen vacancies become ionized, generating up to two electrons that are free to roam [23]. This causes an increase in conductivity, and also serious instabilities in transistor performance such as negative threshold voltage shifts [24].

**Figure 2.3** – The structure of a) amorphous IGZO showing the dispersed nature and b) crystalline IGZO showing alternating stacked layers [20].

Both the increased conductivity and threshold voltage shift are recoverable, however the recovery time is typically very long (up to 20 hours in cases), although this can be reduced by low temperature thermal annealing [24].

#### 2.3 Field Effect Transistor

The field effect transistor (FET) is the cornerstone of modern electronics, so much so that the average person owns billions of FETs without even knowing it. While a single FET by itself is just an electronic switch that can turn a single bit on or off, when thousands or millions of these switches are connected then complex operations can be performed. This is the cornerstone of the computer industry. In accordance with Moore's Law [25], FETs have been continually shrinking in size, and thus increasing their speed. This has allowed for ever more complex circuits to be built.

As mentioned earlier, a FET is just a simple switch. The FET works by modulating a current flowing through a predefined channel by applying a voltage to a gate covering the channel. The gate voltage generates an electric field, which is then used to modulate the conductivity of the channel. In depletion mode FETs, as the name implies, a depletion region exists that is depleted of free charge carriers, leaving none to carry a current. The gate voltage can be set in such a way so that the depletion region is removed, allowing current to flow freely between the drain and the source, or by increasing the size of the depletion region so that it fully blocks the channel preventing any current from flowing.

One of the key points of a FET is to keep the gate current as low as possible, as the gate is intended to be a trigger that allows or denies current flow between the source and drain. There are several different ways of reducing this gate current, and each type of FET uses a different method. The most common transistor structure used in

the semiconductor industry today is the metal-oxide semiconductor FET (MOSFET). The MOSFET uses a physical barrier in the form of an oxide layer between the channel and the gate to prevent any current flow. While oxides are typically used, in actuality the MOSFET is just a type of metal-insulator semiconductor FET (MISFET), as any high quality insulating dielectric can be used, such as  $Ge_3N_4$  [26] or  $SiN_x$  [27].

Adding a physical barrier isn't the only way to prevent current flowing to the gate however. The junction FET (JFET) uses a reversed biased p-n junction to isolate the gate from the channel. By doping a portion of the channel with the opposite type dopant, a p-n junction is formed. Typically a JFET is normally on when no bias is applied to the gate, and when a bias is applied the depletion region formed by the p-n junction expands switching the FET off. A MESFET is similar to a JFET, except that a Schottky barrier is used instead of a p-n junction to isolate the gate. There are also several other more complicated FET configurations, however for this work MESFETs were fabricated as the FET of choice.

The MESFET has a key advantage over the more commonly used MOSFET, and that is a lower voltage operating range. The typical MOSFET has an operational voltage range of 20-40 V, while for a MESFET this can be reduced to 3-5 V. This significant reduction is due to the removal of the gate insulator, which effectively acts as a spacer for the electric field. As the electric field has to be larger in order to reach the channel to deplete it, a larger voltage is required. The MESFET also has a higher theoretical channel mobility. In a MOSFET, the charge carrier wavefunction extends into the oxide layer, and as the oxide layer is insulating, this reduces the mobility significantly. MESFETs however do not have this insulating layer and the depletion region keeps the charge carriers away from the gate interface, which can act as a

scattering centre significantly reducing mobility. This higher mobility allows for higher currents using the same cross-sectional area, as well as a higher transconductance and operational frequency of the device. However, advanced processing techniques along with improved quality films have reduced the mobility difference significantly. As with everything, the advantages of the MESFET come at a cost. While the presence of the Schottky barrier increases the mobility of the devices, it also limits the operational voltage of the device. As the gate voltage increases, it will reach a point where the gate is forward biased, which is not ideal, as current will flow through the gate as opposed to the desired drain-source route.

#### 2.4 MESFET

Typically FETs are fabricated on a bulk substrate, using doping to generate prescribed areas of allowed conduction while creating reversed biased p-n junctions where conduction is not allowed. This prevents any lateral conduction, forcing the current to flow under the gate that can be used to modulate the flow. A thin film transistor (TFT) is a device that is fabricated on a thin film that has been deposited onto an insulating substrate. By removing the bulk material and replacing it with an insulating substrate, there is no longer any concern about unwanted lateral conduction paths circumventing the desired FET structure.

The best known application of TFT devices is in LCDs, where they are used as pixel drivers. TFTs have the advantage in this application because the transistors are fabricated directly on the panel, typically glass, as opposed to being attached to the panel. This can reduce crosstalk between pixels, which leads to improved image stability.

**Figure 2.4** - Cross-section of a typical MESFET showing the linearity of the depletion region [28].

The MESFET structure, as shown in Figure 2.4, is a thin film device with a source and drain separated by a gate. Depending on the fabrication process, the channel material outside the desired path is typically removed via etching or lift-off, leaving only the channel material to be modulated by the gate. While all three contacts are shown as one solid block of metal in Figure 2.4, these contacts can actually consist of multiple layers. Each layer has its own purpose, such as promoting good adhesion with the semiconductor, preventing contact oxidation or ensuring low resistance.

The following is a brief description of MESFET operation, as can be found in any semiconductor textbook such as [28]. The operation of a MESFET is controlled by the gate, therefore the section of the device under the gate is considered. Under normal operating conditions for a normally on device, the gate voltage  $(V_G)$  is either negative or set at 0 V, while the drain voltage  $(V_{DS})$  is either set positive or 0 V. These voltages are given with respect to the source voltage. The channel has a resistance of

$$R = \rho \frac{L}{A} = \frac{L}{q\mu_n N_D Z(d-W)} \tag{2.1}$$

where L is the channel length, q is the charge of an electron,  $\mu_n$  is the electron mobility of the channel,  $N_D$  is the donor concentration, Z is the channel width, d is the channel thickness and W is the width of the depletion region which can be expressed as

$$W = \sqrt{\frac{2\varepsilon_s(V_{bi} - V_G)}{qN_D}} \tag{2.2}$$

where  $V_{bi}$  is the built-in voltage of the Schottky junction and  $\varepsilon_s$  is the permittivity of the semiconductor. At any drain voltage, the voltage across the channel increases from  $V_S$  at the source (which is usually grounded) to  $V_D$  at the drain. This causes the Schottky junction to become increasingly reversed biased towards the drain, producing a sloped depletion region as shown in Figure 2.4.

When  $V_G=0$  and  $V_D$  is small, the drain current  $I_D$  is linear and can be expressed using Ohms law as

$$I_D = \frac{V_D}{R} \tag{2.3}$$

As  $V_D$  increases, the depletion region W also increases which in turn increases the resistance in the channel. As a result, the relationship between  $I_D$  and  $V_D$  is no longer linear. If  $V_D$  is increased enough such that W = D, the drain is completely pinched off by the depletion region. This voltage is known as the saturation voltage and can be described by:

$$V_{Dsat} = \frac{qN_D d^2}{2\varepsilon_s} - V_{bi} - V_G \tag{2.4}$$

At this point, the current flowing through the channel is known as the saturation current,  $I_{Dsat}$ , and is the maximum current that will flow through the channel before it

reaches breakdown. Any drain voltage in excess of  $V_{Dsat}$  will not result in any further increase in current, because increasing  $V_D$  just moves the point where the depleted region fully depletes the channel closer to the source. At this point the voltage is always  $V_{Dsat}$ , therefore the number of electrons moving past this point per unit time remains constant, thus the current remains at  $I_{Dsat}$ .

By applying a gate voltage in order to reverse bias the gate contact the depletion width increases as shown by Equation 2.2. For small  $V_D$ , the current is given by Equation 2.3; however the channel resistance increases as the depletion width increases. By increasing the gate voltage, eventually the depletion region will reach the substrate and the device will be fully depleted. This gate voltage is called the threshold voltage and can be found by rearranging Equation 2.2 to:

$$V_T = V_{bi} - \frac{qN_D d^2}{2\varepsilon_S} \tag{2.5}$$

To calculate the current at this point, we must first consider how the voltage drops across a section dy of the channel, this is given by:

$$dV = I_D dR = \frac{I_D dy}{q \mu_N N_D Z[a - W(y)]}$$

(2.6)

The depletion width at this point is:

$$W(y) = \sqrt{\frac{2\varepsilon_S[V(y) - V_G + V_{bi}]}{qN_D}}$$

(2.7)

Since the drain current is constant and independent of distance, Equation 2.6 can be rewritten as

$$I_D dy = q \mu_n N_D Z[a - W(y)] dV$$

(2.8)

Differentiating Equation 2.7 to obtain dV gives

$$dV = \frac{qN_D}{\varepsilon_S} W dW \tag{2.9}$$

Substituting this into Equation 2.8 we obtain:

$$I_D = \frac{1}{L} \int_{W_1}^{W_2} \frac{q^2 \mu_n N_D^2 Z(a - W)}{\varepsilon_s} W dW$$

(2.10)

As W is linear with respect to y, this integration is trivial and results in:

$$I_D = \frac{Z\mu_n q^2 N_D^2}{2\varepsilon_s L} \left[ a(W_2^2 - W_1^2) - \frac{2}{3}(W_2^3 - W_1^3) \right]$$

(2.11)

This can be rewritten in terms of pinch-off voltage V<sub>P</sub> and pinch off-current I<sub>P</sub> as:

$$I_D = I_P \left[ \frac{V_D}{V_P} - \frac{2}{3} \left( \frac{V_D + V_{bi} + V_G}{V_P} \right)^{3/2} + \frac{2}{3} \left( \frac{V_G + V_{bi}}{V_P} \right)^{3/2} \right]$$

(2.12)

Where

$$I_P \equiv \frac{Z\mu_n q^2 N_D^2 a^3}{2\varepsilon_S L}, \quad V_P \equiv \frac{qN_D a^2}{2\varepsilon_S}$$

(2.13)

In the saturation region, I<sub>Dsat</sub> becomes

$$I_{Dsat} = I_P \left[ \frac{1}{3} - \left( \frac{V_{bi} + V_G}{V_P} \right) + \frac{2}{3} \left( \frac{V_G + V_{bi}}{V_P} \right)^{3/2} \right]$$

(2.14)

And the corresponding saturation voltage is

$$V_{Dsat} = V_P - V_G - V_{bi} (2.15)$$

Equation 2.5 can then be simplified to

$$V_T = V_{bi} - V_P \tag{2.16}$$

which allows us to compare the threshold voltages in a more convenient manner.

## **CHAPTER 3**

## IGZO Growth and Device Fabrication

This chapter describes the growth and fabrication processes predominantly used in this work. It is assumed that the reader has a basic understanding of the photolithography and further background reading can be found here [29].

## 3.1 Substrate Preparation

Throughout this work, two different substrates were used in every film growth. The first substrate was quartz squares of both 10 mm and 20 mm square sizes. These were used as a general purpose substrate. The second substrate was a 0.5 mm thick polyethylene naphthalate (PEN) obtained from Goodfellow Cambridge Limited cut into 30 mm squares. PEN is one of the two main substrates that are used in flexible electronics today, the other being polyethylene terephthalate (PET) [30]. Both of these substrates are transparent polymers with good solvent resistance and temperature stability. PEN was chosen because although it is slightly less transparent, it has higher temperature stability and provides a more effective barrier to oxygen [30].

As each substrate arrived in a paper sleeve, they required cleaning before each film growth to remove surface carbon contamination. This is required as any dirt or contaminant on the surface of the substrate can cause defects in the films growth. Also, contamination can cause errors in the photolithography processes used in the fabrication steps. The substrates were cleaned using common solvents; acetone,

methanol and isopropyl alcohol (IPA). An ultrasonic bath was used in conjunction with each solvent in order to maximise the removal of contaminants from the surface.

## 3.2 Sputtering

In the semiconductor industry today, the two most widely used techniques to deposit films onto a substrate are chemical vapour deposition (CVD) and physical vapour deposition (PVD). The deposition method used in this work was sputtering, which is a type of PVD. There are four main steps to the sputtering process, 1) ejection of material from the target, 2) transportation of the ejected material to the substrate, 3) reaction of the ejected material with any gases, and 4) deposition of the ejected material on to the substrate [31].

The ejection of material from the target is achieved by ion bombardment from a plasma discharge. By setting up a large potential between two electrodes, electrons are discharged into the sputtering chamber. These ejected electrons interact with the working gas in between the electrodes, usually argon (Ar) due to its price and sputtering efficiency. The ejected electrons approach an Ar atom with enough energy to ionize the atom. This leaves the Ar atom as a positively charged ion. As the Ar<sup>+</sup> ion is in an electric field, it is accelerated towards the cathode. The Ar<sup>+</sup> ion striking the surface of the cathode transfers part of its energy to the target. Depending on the amount of energy transferred, atoms, ions or clusters can be ejected from the target into the chamber. This collision also generates additional electrons which are ejected as well, allowing the glow discharge to be self-sustaining. However, not all Ar<sup>+</sup> ions reach the cathode. Some of the Ar<sup>+</sup> ions recombine with the ejected electrons in the plasma, a process which releases a photon. This gives the appearance that the plasma is glowing, which explains why it is also known as a glow discharge.

**Figure 3.1 -** Sputtering system used for the majority of depositions performed in this work.

After the material has been ejected from the target, it travels through the chamber towards the substrate. Depending on the material being sputtered, it is possible to add in reactive gases into the chamber. By adding in  $O_2$ ,  $N_2$ , or  $H_2$ , oxides, nitrides, or hydrogenated materials can be grown using this technique. Once the material reaches the substrate, it is absorbed on the surface, allowing a film to be grown.

Two different sputtering modes can be used: DC sputtering which requires a conducting target and RF sputtering with which an insulating target can also be used. Many of the targets used in the fabrication of AOS devices are insulating and if used in DC mode a positive charge build up will form on the surface of the target. This is turn means that not enough secondary electrons would be generated by the glow

discharge to allow it to be self-sustaining. This can be overcome by using a RF plasma source instead of a DC source.

RF sputtering is similar to DC sputtering in that it uses a glow discharge to bombard the surface of the target with ions in order to eject material and transport it to a substrate [32]. However, the main difference is in how the glow discharge is formed. By applying an RF frequency, typically 13.56 MHz, to the electrodes, the electron oscillations have enough energy to cause ionising collisions with the Ar atoms. As electrons have a higher mobility than the Ar<sup>+</sup> ions in the glow discharge, more electrons than ions reach the target in half a cycle. This causes a negative self-bias at the target surface, which is turn attracts more ions and repels electrons, allowing a self-sustaining sputtering process to be achieved.

Due to the different method of powering the sputtering process, RF sputtering can be achieved at a much lower pressure than DC sputtering. This lower pressure results in fewer collisions between the ejected materials and the plasma gases, resulting in a more direct path of travel between the target and the substrate. Therefore, while these two sputtering systems appear similar, the optimisation needed for each system can be significantly different.

Those interested in further reading on the subject of sputtering and recent sputtering advances can find more information on the topic at the following references [32]-[36].

#### 3.3 IGZO Film Growth

As with any fabrication process, the films grown using RF sputtering can have significantly different properties depending on the parameters used in the growth.

There are several different factors that can cause film variations, including base pressure, processing pressure, oxygen pressure, power and substrate temperature. Varying any one of these factors by a small amount can cause a significant change in the mobility and carrier concentration of the resulting film. For this work, the devices were intended to be fabricated on a plastic substrate which has a low melting point, so a room temperature growth recipe was employed.

As every sputtering system behaves differently, the parameters that produce good results for one system may not be directly reproducible in another system. Therefore, while it is useful to read the literature to determine the parameters others have used to grow successful films, it is also necessary to optimise these parameters in the sputtering system used. The first parameter to be investigated was base pressure. All the films grown in this study used a molar 1:1:1 Ga<sub>2</sub>:In<sub>2</sub>:Zn:O<sub>x</sub> target purchased from research and PVD Materials Corp (USA). The target was 3 in in diameter and ¼ in thick with a ¼ in copper backing to prevent target cracking during the sputtering process. All growths were conducted using the same RF recipe of a 3 W/min ramp to the target power, followed by a growth to a specific thickness as determined by a crystal monitor. Once the required thickness had been achieved, the power was ramped down at 3 W/min to 30 W before being turned off.

For these initial experiments, the power was 100 W, the process pressure  $3.4 \times 10^{-3}$  mbar of Ar, with no added oxygen. After several growths, it became apparent that any growth at a base pressure above that of  $7 \times 10^{-6}$  mbar, regardless of thickness, resulted in fully resistive films. It was also determined that the lower the base pressure, the greater the conductivity of the resultant film. This fact sets a maximum base pressure for all following experiments. The second parameter to be examined was oxygen

introduced during growth. It has been shown that additional oxygen can be an important tool in tuning the properties of AOS films, especially at low annealing temperatures [37], such as those used for films grown on plastic substrates. It was discovered, that even at the smallest partial pressure of O<sub>2</sub> measurable in the sputtering equipment used of 1x10<sup>-4</sup> mBar, any film regardless of thickness was fully resistive. This eliminated the use of oxygen as a tool to modulate the properties of the films grown in our system. The final parameter examined in the growth of these films was the RF power used. There was very little difference in the properties of films grown at 75 W and 100 W. Films grown below 75 W showed an increasing resistance measured diagonally across each film, with 60 W films being twice as resistive as 75 W films while 50 W films were fully resistive.

Table 3.1 shows the results of these experiments. With the exception of growths A and E, the chamber was allowed to pump down for the same amount of time. The variance in base pressure can be explained by several possible reasons; i) how long the chamber was left open while the targets were swapped which could affect the amount of water vapour in the chamber, ii) the humidity of the day, iii) the temperature, or iv) the previous use of the chamber. As these factors cannot be completely controlled in a general research environment it was not always possible to get the exact same base pressure.

The films grown as part of the power series were examined using x-ray photoelectron spectroscopy (XPS) as shown in table 3.1. A detailed explanation of how XPS is used lies outside the scope of this work. For more information on XPS a standard spectroscopy textbook such as [38] can be used.

| Growth         | Power   | Base Pressure (mbar) Resistance (Ω) |      | Thickness (nm) |  |

|----------------|---------|-------------------------------------|------|----------------|--|

| A              | RF 100W | 1.4x10 <sup>-5</sup>                | ∞    | 150            |  |

| В              | RF 100W | 6.0x10 <sup>-6</sup>                | 110K | 55             |  |

| C <sup>1</sup> | RF 100W | 5.0x10 <sup>-6</sup>                | ∞    | 46             |  |

| D              | RF 100W | 5.5x10 <sup>-6</sup>                | 42K  | 60             |  |

| $E^2$          | RF 100W | 4.6x10 <sup>-6</sup>                | 11k  | 50             |  |

| F              | RF 75W  | 5.5x10 <sup>-6</sup>                | 44K  | 60             |  |

| G              | RF 60W  | 6.0x10 <sup>-6</sup>                | 90K  | 60             |  |

| Н              | RF 50W  | 6.0x10 <sup>-6</sup>                | ∞    | 60             |  |

| I              | RF 25W  | 6.0x10 <sup>-6</sup>                | ∞    | 66             |  |

| $J^3$          | DC 100W | 6.0x10 <sup>-6</sup>                | -    | -              |  |

**Table 3.1** - Growth comparison of IGZO over a range of settings. Notes: 1) in this growth 0.14SCCM of  $O_2$  was added to the growth. 2) Liquid  $N_2$  was used to further reduce the base pressure. 3) The plasma for this and subsuquent growths was unstable, so no film was produced.

| Sample                    | C 1s | Ga 2p<br>3/2 | In 3d<br>5/2 | O 1s | Zn 2p<br>3/2 | Ga/Zn | In/Zn | O/Zn  | Ç<br>(eV) |

|---------------------------|------|--------------|--------------|------|--------------|-------|-------|-------|-----------|

| as-grown 100W             | 46   | 6            | 10           | 35   | 3            | 2.00  | 3.33  | 11.67 | 2.11      |

| annealed 100W<br>120°C 1h | 48   | 5            | 8            | 37   | 2            | 2.50  | 4.00  | 18.50 | 2.02      |

| 25W                       | 58   | 3            | 6            | 32   | 1            | 3.00  | 6.00  | 32.00 | 0.09      |

| 50W                       | 47   | 6            | 9            | 36   | 2            | 3.00  | 4.50  | 18.00 | 0.004     |

| 60W                       | 53   | 4            | 7            | 34   | 2            | 2.00  | 3.50  | 17.00 | 1.54      |

| 75W                       | 44   | 6            | 10           | 37   | 3            | 2.00  | 3.33  | 12.33 | 2.63      |

| 100W                      | 51   | 5            | 7            | 34   | 3            | 2.67  | 2.33  | 11.33 | 2.02      |

**Table 3.2** – XPS results for IGZO films grown using various RF sputtering power, rounded to the nearest percent. The values of C were estimated from the valance band regions of the survey scans which consist of 2 to 3 data points for each linear fit.

The main conclusions from the XPS quantification data is that In:Ga:Zn ratios are significantly different compared to the composition of the molar 1:1:1 target. The expected ratios of films grown using a molar 1:1:1 target would be 1:1:0.5 In:Ga:Zn. However, the extracted results from the XPS analysis showed a ratio of approximately 1.6:1:0.5 In:Ga:Zn. A possible explanation is that preferentially sputtering of In over Ga and Zn has occurred in this sputtering system.

## 3.4 Co-sputtered IGZO Films

From table 3.2, it is clear that there is comparatively less Zn in all the samples than expected compared to In and Ga. Referring back to Figure 2.2 in Section 2.2, it is predicted that the less Zn in a film relative to Ga, then the lower the resulting mobility. The sputtering system described in the previous section has the ability to simultaneously co-sputter RF and DC targets. In this experiment, IGZO films were fabricated using the same RF sputtering recipe in Section 3.3, while at the same time an Al:ZnO (2% Al) target was sputtered using DC mode at 40 W. This co-sputtering process took approximately 40 minutes to deposit 70 nm of Al:IGZO, and the substrates were rotated during this time to evenly disperse the ejected material from the two targets. The substrates were arranged in the sequence shown in Figure 3.2. After the deposition was complete, it was discovered that only the films on the inner quartz substrates were conductive, while the middle and outer quartz substrates as well as most of the PEN substrates were fully resistive. This is believed to be due to the outer samples receiving more ZnO than the inner samples, causing sections of the films to be purely polycrystalline ZnO, disrupting the current flow mechanisms of a-IGZO.

**Figure 3.2 -** Substrate layout prior to co-sputtered deposition. The small substrates are 10x10 mm quartz while the large substrate is 30x30 mm PEN.

The resultant films on the inner substrates had an initial resistivity of 112 k $\Omega$ , a measured Hall mobility of 5.5 cm<sup>2</sup>/Vs and a carrier concentration of  $4x10^{18}$  cm<sup>-3</sup>. These results were not significantly different from purely RF sputtered IGZO films, potentially indicating that there was perhaps little additional ZnO added to the film, or that the ZnO was added in a way that disrupts the IGZO structure as opposed to aiding it.

## 3.5 Device Fabrication

For this work, a simple top gate TFT structure was fabricated on one of each of the grown film. While the layout of the structure can be changed to suit the required need for a specific application, the fabrication steps remain the same.

Once the film has been deposited onto a substrate, the first step in the fabrication process is to isolate each transistor. Isolation is required to define the specific gate width and length for each individual transistor, and to prevent current leaking outside of the desired conduction channel. In a typical MOSFET transistor this is done using junction isolation, which is where each transistor is surrounded by an opposite doping type. The opposite doping is then connected to a voltage source to create a reverse diode p-n region, and the depletion region created isolates the transistor from the rest of the circuit.

However, as there are currently no reliable methods to create p-type IGZO, a different type of isolation is required. Mesa isolation is where the conducting material is etched away down to the insulating substrate layer, thus preventing lateral conduction. An example of etching can be seen in Figure 3.3. There are several different methods to etch IGZO, such as dry etching with CH<sub>4</sub> [39] or SF<sub>6</sub> [40], and wet etching with NH<sub>4</sub>Cl or HCl [41]. Each etching method has different etch rates, selectivity and ease of use, so selecting the correct etching method is important. While dry etching can give greater etch selectivity, it is a more complicated process both in the time involved and set up. Wet etching on the other hand is more suitable for mass production, and is widely used in flat-panel display fabrication lines. For these reasons, a wet etching approach was more desirable for fabricating devices used in this research.

Initial attempts with various concentrations of NH<sub>4</sub>Cl (a successful etchant for ZnO) proved unsuccessful, so a stronger acid was tried. Successful etching was achieved using a 5% HCl solution. Etch rate experiments showed that this solution has an etch rate of 2.75-3 nm/sec. It is important to get the etch time right, as over-

**Figure 3.3 -** Row of devices after Mesa etching on a PEN substrate.

etching will cause excessive undercutting, which can degrade or completely remove small features, while under-etching can cause excessive leakage of the device if the device is not fully isolated.

Once the etching has been completed, the next step is to fabricate the contacts of the MESFET. The ohmic and Schottky contacts can be fabricated in either order, however for this study the Schottky contacts were usually fabricated first as they are more sensitive to impurity contamination. The reasoning behind this is that the Schottky contact on a MESFET device is more important than the ohmic contacts in determining the ultimate performance.

The Schottky contact material used for the majority of this work was silver oxide  $(AgO_x)$ . More details about choice of this material can be found in Section 4.4. The Schottky contact was deposited using reactive RF sputtering, with an RF power of 50 W in an  $Ar/O_2$  atmosphere, at a pressure between  $1.0x10^{-5}$  and  $1.8x10^{-5}$  mbar

producing a contact thickness of either 10 nm, 30 nm or 50 nm, depending on the experiment performed. A capping layer of either indium tin oxide (ITO) or gold (Au) was then deposited on top. This capping layer was required because it achieves a lower sheet resistance for the contact, as well as providing an extra layer of protection between the measuring probes and the Schottky contact.

There are several possible materials to create ohmic contacts on IGZO [42] [43], however for the majority of this work the ohmic contacts used were a Ti/Au bi-layer. It is worth noting that in Section 7.1 ITO was used instead. The Ti/Au ohmic contacts were deposited using electron beam evaporation, while the ITO ohmic contacts were deposited using RF sputtering. In electron beam evaporation, the target crucible containing the desired metal is locally heated up above its boiling point using an electron beam. The heated target metal evaporates producing an atomic metal beam that is projected on to the semiconductor material.

For the Ti/Au bi-layer, 40 nm of titanium was deposited at a pressure range of  $1.0 \times 10^{-5}$  and  $1.8 \times 10^{-5}$  mbar. This deposition can cause the chamber temperature to increase to between 50-60 °C, however as the fabrication is intended to be at room temperature a time gap was introduced between the two depositions to allow the chamber to cool down before 30 nm of Au was deposited. As the Ti was not exposed to the atmosphere very few oxidised Ti atom impurities are initially involved in the contact, which improves the contact resistance.

In order to remove the excess metal from the areas that were not designated by the contact mask, a lift-off process was used. This was chosen as opposed to an etch based approach because the majority of the chemicals used in etching would also

**Figure 3.4** - Finished array of devices featuring a gold cap.

affect the material under the metal, potentially causing undercuts and reducing or impeding device operation. A lift-off process removes this problem. A lift-off process involves masking the semiconductor with a light sensitive polymer photoresist (AZ1518 in this case), so that the metal is deposited on top of the photoresist everywhere apart from the contact area defined by the mask. Once the contacts have been deposited, the sample is placed in an acetone solution until there is visible buckling of the excess surface metal. This shows that the photoresist below the metal has dissolved, so the metal is no longer supported. While it is possible for this process to completely remove all the excess metal, it is rare for all the unwanted material to be removed without using external agitation such as boiling the acetone or the use of an ultrasonic bath.

## **CHAPTER 4**

#### **Device Characterisation**

This chapter outlines the steps required to characterise a specific MESFET device. The specific device chosen in this case is a MESFET fabricated on a PEN substrate with an  $AgO_x$  gate. The chosen device has a width to length ratio of  $100/10~\mu m$ . There is also a comparison of the various device fabrication choices made throughout this work. These include:

- The impact made on performance of the choice between substrate between quartz and PEN,

- 2) Changing the gate material between AgO<sub>x</sub>, IrO<sub>x</sub> and PtO<sub>x</sub>,

- 3) Co-sputtered IGZO and Al:ZnO compared to pure RF grown IGZO.

All measurements were performed using a Hewlett Packard 4155B semiconductor parameter analyser. The devices were placed in a shielded probe station to prevent any outside interference such as stray electric fields and light to affect the results. The probes were positioned under illumination from a 20 mW/cm² halogen lamp. This was later discovered to cause an extreme photo-illumination effect in the devices, as discussed in Chapter 6. As the different samples were all tested in the same order and thus took approximately the same amount of setup time, this effect is believed to not have adversely affected the results gathered in this chapter.

#### 4.1 Schottky Gate Analysis

The Schottky gate plays a dominant role in the operation of MESFETs, and as such its performance characteristics provide an important diagnostic of MESFET quality. As mentioned in Section 2.4, the drain and gate of a MESFET form a Schottky diode. By applying bias voltages across this diode and measuring the resulting current, several key parameters concerning the Schottky gate can be extracted from the subsequent data. In this case, the measurements were done in two parts. First, the voltage was swept from 0 to 2 V in 10 mV steps, and then the voltage was swept from 0 to -2 V using the same increments. This was done to reduce noise integration errors introduced by the parameter analyser when measuring extremely low currents.

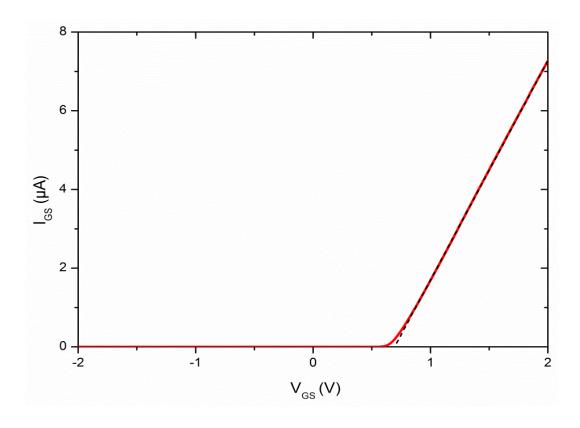

By plotting the measured data in a linear I-V curve, the first figure of merit can be extracted. Although the I-V curve initially increases as an exponential, the current is quickly limited by the total series resistance present. Figure 4.1 shows the measured I-V curve for the selected device. As expected, the linear I-V curve displays typical diode characteristics, with the current being determined by the series resistance above 0.8 V. This total series resistance can be extracted from the curve by plotting the trend line of the linear region, and extracting the inverse of the slope,  $180 \text{ k}\Omega$  in this case. Total series resistance is the combined effect of the material resistance and the contact resistance present in both the ohmic and Schottky contacts. Ideally this value should be as low as possible to ensure optimal device performance, however further attempts to reduce series resistance values were not the subject of this thesis.

The reverse leakage resistance can be calculated in a similar manner using the reverse current instead of the forward current. In the ideal case, this current would be negligible until the device reaches the breakdown region, at which point the device

**Figure 4.1** – Schottky diode current-voltage curve depicting forward current becoming essentially linear. The dashed line indicated the slope used to determine series resistance.

current would increase exponentially in the reverse direction. While not shown in Figure 4.1 as there is very little information to be gained past -2 V, until it reaches breakdown at 5.6 V. The reverse leakage resistance in this case was 220  $G\Omega$ .

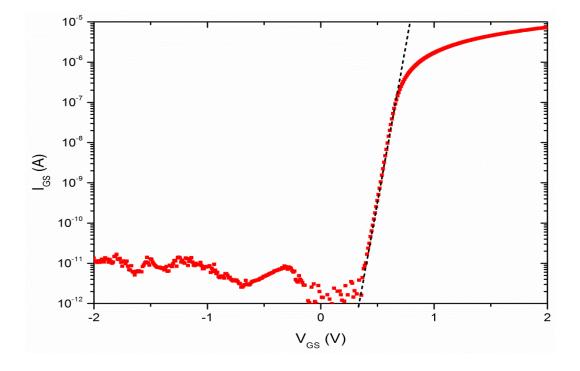

While the linear I-V curve does show typical diode behaviour, it is not the most useful representation of the data. By plotting the data in a semi-log plot, two more useful parameters can be extracted from the data; the ideality factor  $\eta$  and the effective barrier height  $\varphi_B$ . The ideality factor is effectively a comparison between how the diode is behaving in practice versus how it would behave in the ideal thermionic emission approximation without tunnelling. In the absence of tunnelling, then the ideality factor should be very close to unity. Larger ideality factors indicate compromised device performance and laterally inhomogeneous Schottky contacts.

Typically, a MESFET Schottky contact would have an ideality factor between 1 and 2; however defects in the IGZO material and device fabrication processes can cause ideality factors greater than 2. To calculate the ideality factor, we must first look at how the device would function in the ideal case by looking at the ideal Schottky diode equation, a derivation of which can be found in most semiconductor textbooks [28]. The ideal diode equation is:

$$J = J_s \left( e^{qV/kT} - 1 \right) \tag{4.1}$$

where q is the charge of an electron, V is the applied voltage, k is the Boltzmann constant, T is the temperature and  $J_s$  is the saturation current density which can be calculated by:

$$J_{s} = A^{*}T^{2}e^{-q\emptyset_{B}/kT}$$

$$(4.2)$$

where  $A^*$  is the effective Richardson constant, and  $\phi_B$  is the effective barrier height.

**Figure 4.2** – Schottky diode current-voltage semi-log plot. The dashed line indicates the region where Equation 4.1 is valid.

From Equation 4.1, the slope of the line in Figure 4.2 for the ideal case would be q/kT, and any derivation from that is included in the ideality factor  $\eta$ . The slope is  $35.39 \text{ V}^{-1}$ , which corresponds to an ideality factor of 1.1.

The intercept of the slope gives the saturation current,  $I_s$ , which can be used to calculate the saturation current density,  $J_s$ , by dividing by the contact area A. By using an effective mass of  $0.34m_e$  [19], the effective Richard constant can be calculated to be 41 Acm<sup>-2</sup>K<sup>-2</sup> [44]. Substituting these values back into Equation 4.2 and solving for  $\phi_{Bn}$  gives a barrier height of 1.07 eV for this particular diode.

#### 4.2 MESFET output curve

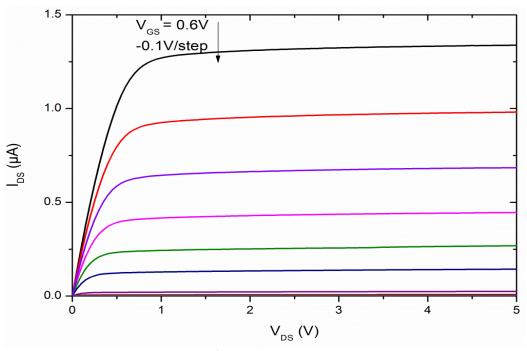

The typical method of comparing FET operations is to consider the generated set of output curves, such as those shown in Figure 4.3. This set of curves was generated by setting a specific gate voltage value and then sweeping the source-drain voltage V<sub>DS</sub> from 0 to 5 V. The gate voltage range was chosen to run the FET through all its operational modes without driving the device into breakdown. There are several key regions to this set of curves, as they show how well a device operates. The key considerations when analysing a set of FET output curves are: 1) Can the channel be completely turned off? 2) Is there a linear region? 3) Does the channel fully saturate?

To determine the functionality of this device as a MESFET, the above questions can be answered. There is a clear linear region to the MESFET curves depicted in Figure 4.3 for all visible curves. In the linear region, the current is proportional to  $V_{DS}/R_c$ , where  $R_c$  is the channel resistance. However, as  $V_{DS}$  increases, the cross-sectional area of the current path also increases, until it reaches the maximum area defined by the channel cross section. This point marks the saturation current, which for an ideal MESFET should be flat. The device shown has a positive gradient to its

Figure 4.3 - Output MESFET curves for the tested device.

saturation region, which can be accounted for by current leaking from the gate. Finally, it can be seen that as the gate voltage decreases below -1 V, there is negligible current flowing, showing that the channel is fully depleted.

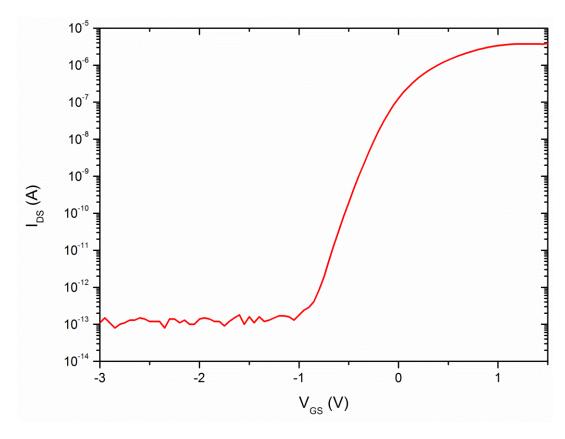

## 4.3 Transfer Curve

While the MESFET output curves give a nice visualisation to the operation of the device, it is not the most useful data set. The most useful representation of the MESFET operation is the transfer curve, in which  $V_{DS}$  is held steady at 2.5 V and the gate voltage  $V_G$  swept from 1.5 V to -3 V. The subthreshold swing (S), which is a measure of how fast the device can be switched on and off, can be extracted from the steepest region of Figure 4.4 by using the following equation:

$$S = \left(\frac{\partial \log(I_D)}{\partial V_{DS}}\right)^{-1} \tag{4.3}$$

The subthreshold swing for this device was measured to be 120 mV/dec, which is significantly lower than the 600 mV/dec of a typical a-Si MOSFET device [45] and

comparable to the 112 mV/dec and 123 mV/dec of similarly fabricated IGZO MESFETs reported by other groups [46]. This switching speed is congruent with the inherent switching advantages of MESFETs, including a reduced voltage range required to switch the device from on to off. Figure 4.4 also shows off-currents as low as  $1 \times 10^{-13}$  A and an on-off ratio of 7.5.

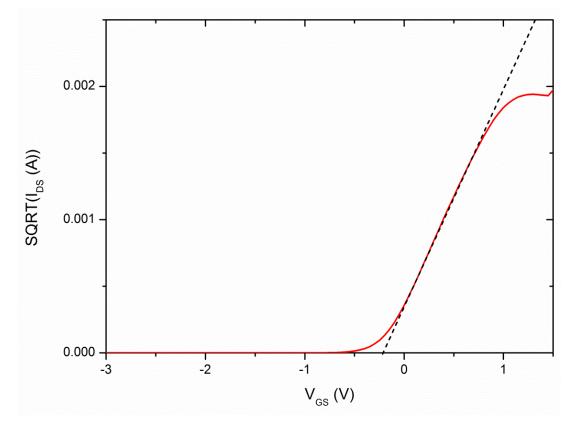

By taking the square root of the transfer curve as shown in Figure 4.5, the threshold voltage  $V_T$  and the channel mobility  $\mu_n$  can be calculated. The threshold voltage is the point at which the transistor has started to significantly move from its off state, and is given by the x-intercept of the line of best fit as shown in Figure 4.5. In this case, the threshold voltage is -0.22 V. While a negative threshold voltage typically implies that the transistor is usually on, this was only the case when these devices have been exposed to illumination, details of which are explained further in Chapter 6.

The channel mobility is an important measure of the performance of a transistor, and is typically used to compare different channel materials. While largely dependent on the material used for the channel, fabrication processes can also impact the channel mobility. The channel mobility can be calculated by analysing the current in the saturation region, using:

$$I_{Dsat} = \frac{W\mu_n \varepsilon_s}{2aL} (V_G - V_T)^2 \tag{4.4}$$

Rearranging for  $\mu_n$  gives:

$$\mu_n = \frac{2aL}{W\varepsilon_S} \left(\frac{\sqrt{I_{Dsat}}}{V_G - V_T}\right)^2 \tag{4.5}$$

where a is the channel thickness, L is the gate length, W is the gate width,  $\varepsilon_s$  is the

Figure 4.4 - Transfer curve of selected device.

$\begin{tabular}{ll} \textbf{Figure 4.5 - Square-root of $I_{DS}$ verse $V_{GS}$. The intercept of the dashed line gives threshold voltage while its slope allows for mobility to be calculated. \end{tabular}$

relative permittivity, 11.5 for IGZO [47], and the bracketed region is the slope of Figure 4.5. Substituting these values into Equation 4.5 gives a mobility of 3.1 cm<sup>2</sup>/Vs, which while lower than the Hall mobility of the IGZO material of 6 cm<sup>2</sup>/Vs, it is within the expected range and a possible explanation is that the channel mobility has been affected by material degradation during the fabrication process.

#### 4.4 Initial Gate Comparison

In this comparison, three different Schottky materials were compared; silver oxide (AgO<sub>x</sub>), iridium oxide (IrO<sub>x</sub>) and platinum oxide (PtO<sub>x</sub>). In order to reduce any potential variation in the fabrication process, the fabrication steps of each device were, where possible, performed concurrently. The IGZO material was grown on a 10 mm square quartz substrate by RF magnetron sputtering at a base pressure of 5.5x10<sup>-6</sup> mbar. The substrate was then cut into 5 mm squares, followed by the MESFET fabrication processes described in Chapter 3. The AgO<sub>x</sub> gate was deposited using RF magnetron sputtering, while the IrO<sub>x</sub> and PtO<sub>x</sub> gates were deposited using eclipse pulsed laser deposition (PLD) [48]. These depositions were performed using at a partial oxygen pressure of 100 mTorr. All three gates were capped with an Au layer to increase conduction and to increase the mechanical durability of the contact.

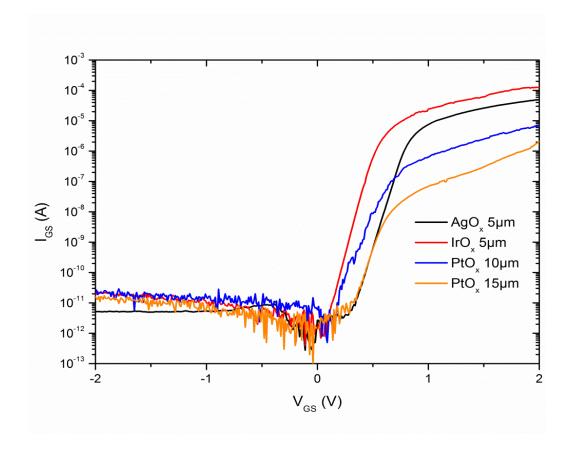

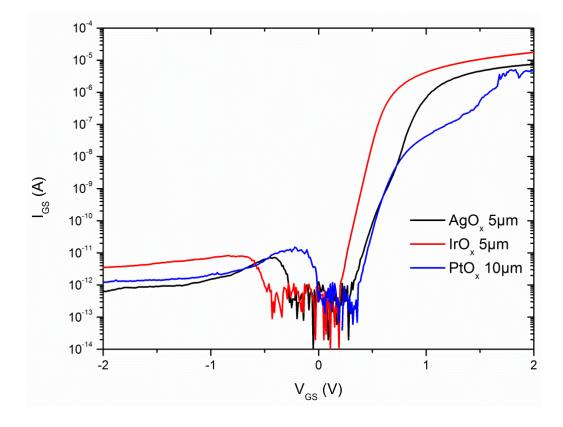

The same analysis as previously outlined was performed on the three different gate compositions. In this comparison shown in Figure 4.6, there are two examples of  $PtO_x$  gate devices but only one each of devices with  $IrO_x$  and  $AgO_x$  gates. This is due to the fact that the  $PtO_x$  gates suffered some damage during the fabrication process, producing a variation in performance. The  $PtO_x$  MESFET with the same gate dimensions as the  $IrO_x$  and  $AgO_x$  devices had a short across the contacts from an

**Figure 4.6** – Comparison of Schottky diodes with channel width 100  $\mu$ m and varying gate lengths and metals.

incomplete the lift-off process. It can be seen in Figure 4.6 that the next transistor, which has a gate length of  $10\mu m$  instead of 5  $\mu m$ , had a poor Schottky contact resulting in a noisy signal, and an ideality factor of 2.1. Transistor 53, which has a gate length of  $15\mu m$ , represents one of the better devices formed using PtO<sub>x</sub> gates, with an ideality factor of 1.6.

Comparing the series resistance values, it can be seen that the  $PtO_x$  gates have significantly higher series resistances,  $100\text{-}106~k\Omega$ , compared to those of the  $AgO_x$  and  $IrO_x$  gates at 24  $k\Omega$  and 16  $k\Omega$  respectively. This suggests that the  $PtO_x$  gates made a poor contact with the IGZO, or that the  $PtO_x$  itself is not as conductive as the other gate materials. The high series resistance of the  $PtO_x$  gates is also responsible for the lower forward currents. The ideality factors of the  $IrO_x$  and  $AgO_x$  gates, at 1.2

and 1.4 respectively, suggest that a good contact has formed with the IGZO. The calculated effective barrier height for the  $AgO_x$  gate is slightly lower than that reported earlier in this Chapter (0.97 eV vs 1.07 eV), however it is still within the range reported elsewhere [46]. Similarly, the calculated effective barrier height of 0.81 eV for the  $PtO_x$  gate device is also consistent with a reported value of 0.91 eV [49]. Currently, no IGZO devices have been published using an  $IrO_x$  Schottky gate, therefore no comparison can be made to the 0.84 eV calculated here.

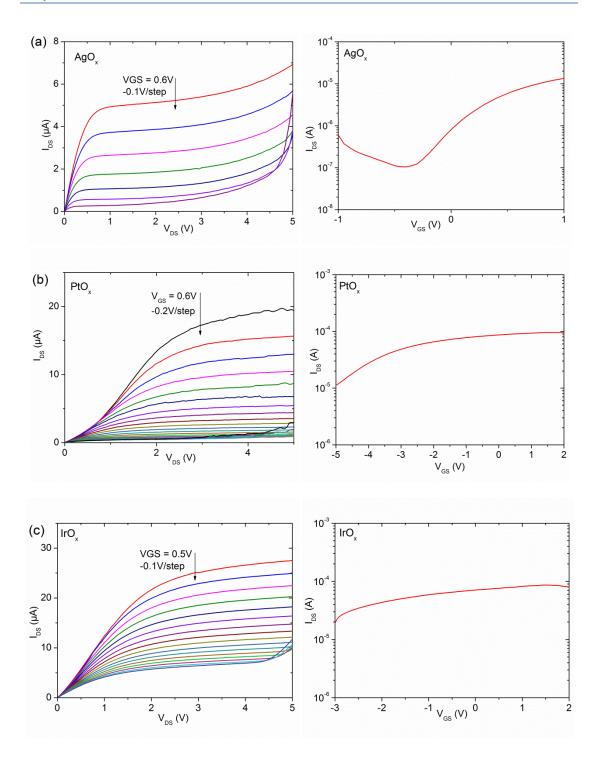

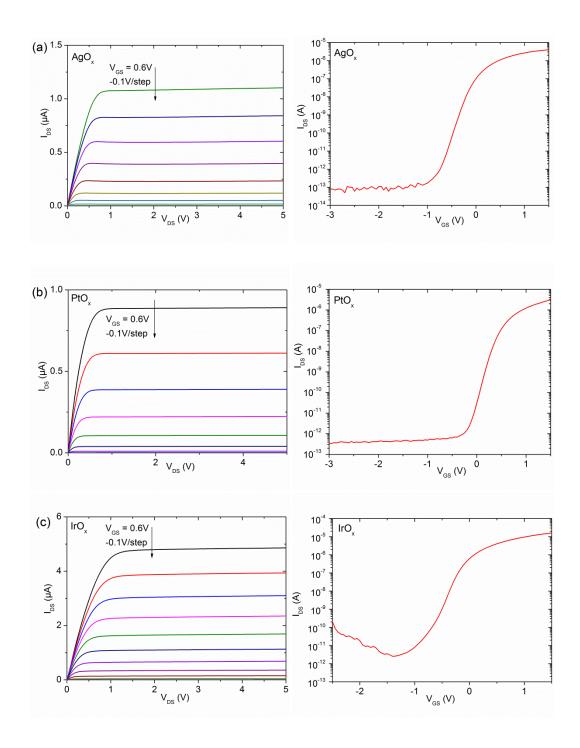

Considering the set of MESFET output curves generated for each gate type as shown in Figure 4.7, it is apparent that the underlying IGZO was too conductive for the devices to fully deplete the channel. This is most readily seen for the  $AgO_x$  and  $IrO_x$  output curves. This is also shown in the MESFET transfer curves, which have a maximum on-off ratio of 2 orders of magnitude for the  $AgO_x$  gate, and less than 1 for the  $IrO_x$  and  $PtO_x$  gates. This effectively means that the transistors cannot be turned off regardless of the gate voltage.

While not entirely useful given the poor performance of the MESFETs, the threshold voltage and channel mobility can be extracted from these devices for comparisons purposes. The channel mobility for all three gates, 1.28, 1.06 and 2.17 cm<sup>2</sup>/Vs for AgO<sub>x</sub>, IrO<sub>x</sub> and PtO<sub>x</sub> respectively, are all lower than that of the IGZO material Hall mobility of 6 cm<sup>2</sup>/Vs. This is expected as the Hall mobility is a representation of the material while the channel mobility is a representation of the completed device, which has additional contact resistances and scattering effects that lower the effective mobility. A comparison of the extracted values can be seen in Table 4.1.

**Figure 4.7** – MESFET output curves and corresponding transfer curves for a) silver oxide, b) platinum oxide and c) iridium oxide.

| Sample           | Series<br>Resistance<br>(Ω) | Ideality<br>Factor | Barrier<br>Height<br>(eV) | Threshold<br>Voltage<br>(V) | Channel<br>Mobility<br>(cm²/Vs) | Subthreshold<br>Swing<br>(mV/dec) |

|------------------|-----------------------------|--------------------|---------------------------|-----------------------------|---------------------------------|-----------------------------------|

| AgO <sub>x</sub> | 24K                         | 1.4                | 0.97                      | -0.90                       | 1.28                            | 337                               |

| IrO <sub>x</sub> | 16K                         | 1.2                | 0.84                      | -6.89                       | 1.06                            | 2449                              |

| PtO <sub>x</sub> | 100K                        | 2.1                | 0.81                      | -6.71                       | 2.17                            | 2287                              |

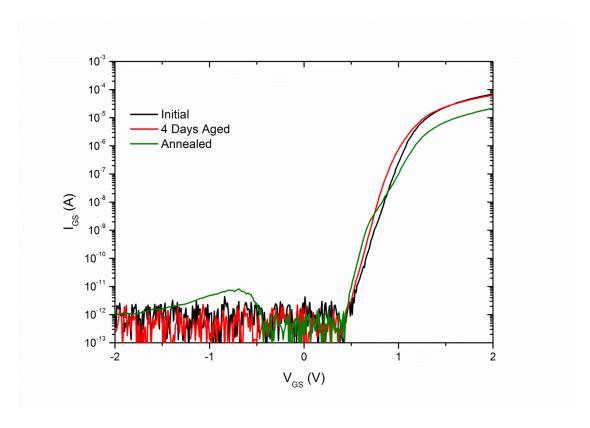

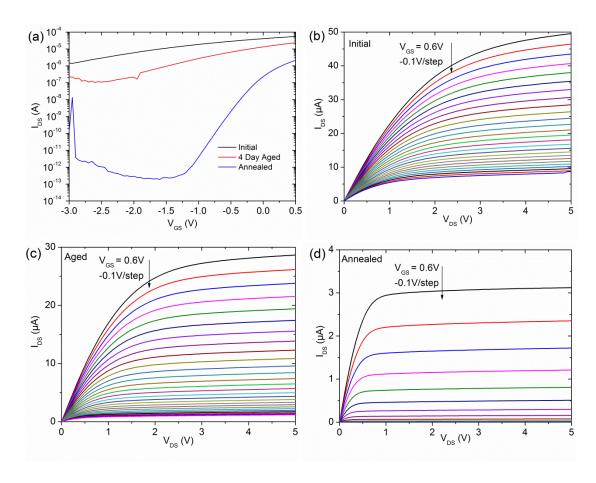

**Table 4.1 -** Gate comparison information.