# PARALLELIZATION OF A SOFTWARE BASED INTRUSION DETECTION SYSTEM - SNORT

A thesis submitted in partial fulfilment of the requirements for the Degree

of Master of Electrical and Computer Engineer

in the University of Canterbury

by Huan Zhang

University of Canterbury

2011

#### **Abstract**

Computer networks are already ubiquitous in people's lives and work and network security is becoming a critical part. A simple firewall, which can only scan the bottom four OSI layers, cannot satisfy all security requirements. An intrusion detection system (IDS) with deep packet inspection, which can filter all seven OSI layers, is becoming necessary for more and more networks. However, the processing throughputs of the IDSs are far behind the current network speed. People have begun to improve the performance of the IDSs by implementing them on different hardware platforms, such as Field-Programmable Gate Array (FPGA) or some special network processors. Nevertheless, all of these options are either less flexible or more expensive to deploy. This research focuses on some possibilities of implementing a parallelized IDS on a general computer environment based on Snort, which is the most popular open-source IDS at the moment.

In this thesis, some possible methods have been analyzed for the parallelization of the pattern-matching engine based on a multicore computer. However, owing to the small granularity of the network packets, the pattern-matching engine of Snort is unsuitable for parallelization. In addition, a pipelined structure of Snort has been implemented and analyzed. The universal packet capture API - LibPCAP has been modified for a new feature, which can capture a packet directly to an external buffer. Then, the performance of the pipelined Snort can have an improvement up to 60% on an Intel i7 multicore computer for jumbo frames. A primary limitation is on the memory bandwidth. With a higher bandwidth, the performance of the parallelization can be further improved.

Keyword: Snort, IDS, Intrusion Detection, Multicore, Parallelization, Pattern Matching.

## **Table of Contents**

| Ab  | stract.   |                                                        | i    |

|-----|-----------|--------------------------------------------------------|------|

| Ta  | ble of (  | Contents                                               | ii   |

| Lis | st of Fig | gures                                                  | iv   |

| Lis | st of Ta  | bles                                                   | vii  |

| Ac  | knowle    | edgments                                               | viii |

| Gl  | ossary.   |                                                        | ix   |

|     |           | DUCTION AND BACKGROUND                                 |      |

| 1   | Introd    | luction                                                | 1    |

|     | 1.1       | Computer Network System and Its Security               |      |

|     | 1.2       | Intrusion Detection / Prevention System                |      |

|     | 1.3       | Multi-core and Parallelization                         |      |

|     | 1.4       | Research Goals                                         |      |

|     | 1.5       | Dissertation Structure                                 |      |

| 2   |           | ground and Related Work                                |      |

| _   | 2.1       | Network Packets and "libpcap" library                  |      |

|     | 2.2       | Parallelization Algorithms                             |      |

|     | 2.3       | Pattern Matching Algorithms and Detection Engine       |      |

|     |           | 3.1. Single Pattern Matching Algorithms                |      |

|     |           | 3.2. Brute Force Algorithm                             |      |

|     |           | 3.3. Hash Algorithm                                    |      |

|     |           | 3.4. Automata Algorithm                                |      |

|     |           | e                                                      |      |

|     |           | 3.5. Sliding Window Algorithm                          |      |

|     |           | 3.6. Bit-Parallelism Algorithm                         |      |

|     |           | 3.7. Multiple String Matching Algorithms               |      |

|     |           | 3.8. Snort String Matching Algorithms                  |      |

|     | 2.4       | Current IDS (Snort) parallelization                    |      |

| тт  | 2.5       | Summary                                                |      |

|     |           | nt System Analysis                                     |      |

| 3   |           | Code Analysis                                          |      |

|     | 3.1       | Snort Overall Structure                                |      |

|     | 3.2       | Snort Variables                                        |      |

|     | 3.3       | Snort Initialisation                                   |      |

|     | 3.4       |                                                        | 46   |

|     | 3.5       | Snort Signature Rules                                  |      |

|     | 3.6       | Snort Plugins                                          |      |

|     | 3.7       | Packet defragment "frag2"                              |      |

|     | 3.8       | Detection Engine                                       |      |

| 4   |           | CAP Mechanism Analysis                                 |      |

| 5   |           | n Matching                                             |      |

|     | 5.1       | General parallelization methods                        |      |

|     | 5.2       | Reversed Bit-Parallelism Algorithm.                    |      |

|     | 5.3.      | Parallelized Aho-Corasick (PAC) Algorithm              |      |

|     | 5.4.      | Testing and Results                                    |      |

|     | 5.4       | 4.1. Single Pattern Matching in a Single-Core System   |      |

|     | 5.4       | 4.2. Multiple Pattern Matching in a Single-Core System |      |

|     | 5.4       | 4.3. Multiple Pattern Matching in a Multi-Core System  |      |

|     | 5.5.      | Conclusion                                             |      |

| 6   | Pipelin   | ne and process management system                       | 81   |

| 9   | References |                                    |     |

|-----|------------|------------------------------------|-----|

| 8   | Futu       | re Work                            | 107 |

| 7   | Conc       | clusion                            | 105 |

| IV. | CON        | NCLUSION                           | 105 |

|     | 6.9        | Summary                            | 104 |

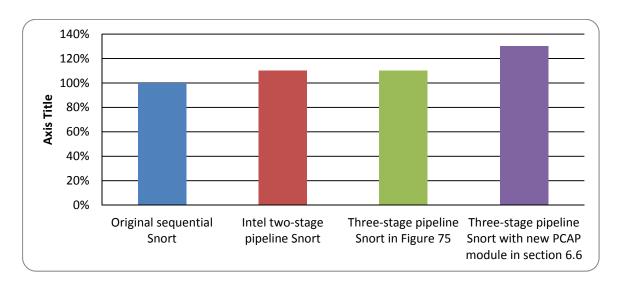

|     | 6.8        | Results Review                     | 102 |

|     | 6.7        | Test of LibPCAP external Buffer    | 101 |

|     | 6.6        | PCAP Capture Buffer                | 99  |

|     | 6.5        | Test of the Pipelined Snort        | 94  |

|     | 6.4        | Measurement on the parallel system | 91  |

|     | 6.3        | Group Management Pipeline          | 87  |

|     | 6.2        | Pipeline and Buffer                | 82  |

|     | 6.1        | Introduction                       | 81  |

# List of Figures

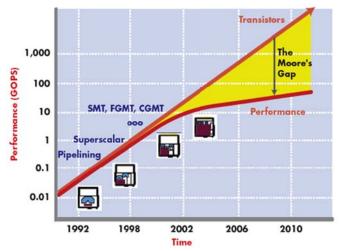

| Figure 1: The Moore's Gap. [3]                                                 | 5   |

|--------------------------------------------------------------------------------|-----|

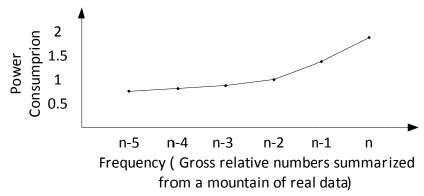

| Figure 2: CPU power consumption vs. clock frequency, "In AMD's process,        |     |

| for 200MHz frequency steps, two steps back on frequency cuts power             |     |

| consumption by ~40% from maximum frequency". [4]                               | 6   |

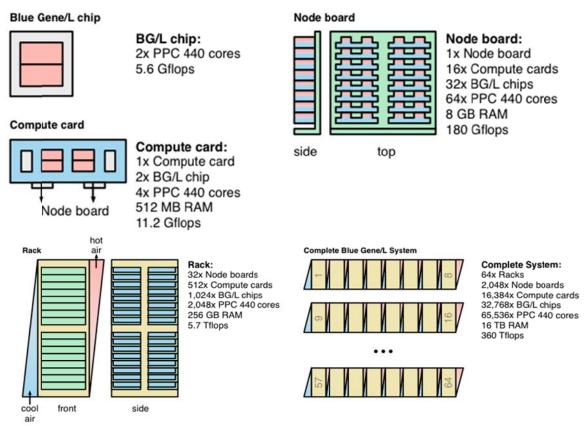

| Figure 3: The architecture of a Blue Gene/L. [5]                               |     |

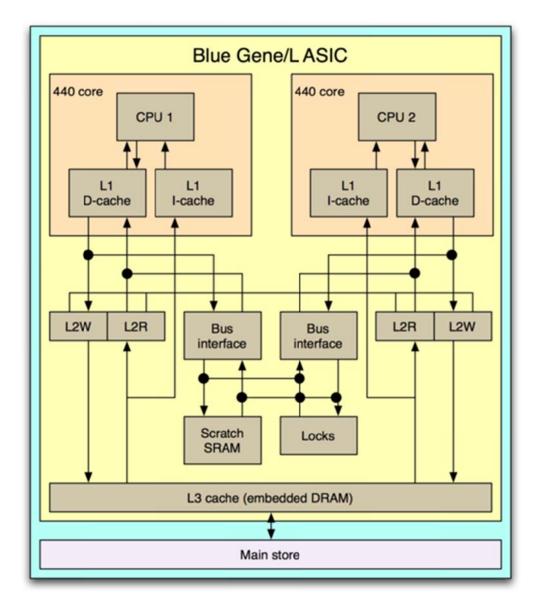

| Figure 4: The architecture of a Blue Gene/L ASIC processor. [6]                | 7   |

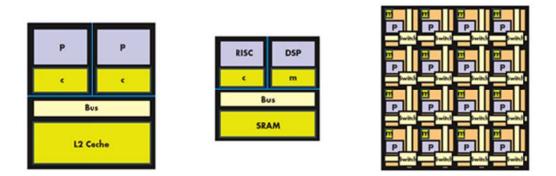

| Figure 5: Three examples of multicore implementations, one showing two         |     |

| identical CPUs, one with an RISC CPU and a DSP, and one with 16                |     |

| identical CPUs. [7]                                                            | 8   |

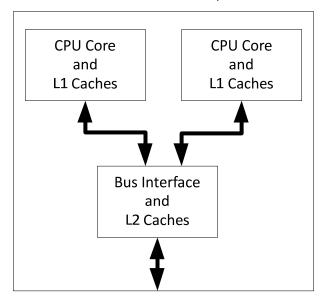

| Figure 6: Diagram of a generic dual-core processor, with CPU-local level 1     |     |

| caches, and a shared, on-die level 2 cache                                     | 9   |

| Figure 7: The ISO OSI model. [8]                                               |     |

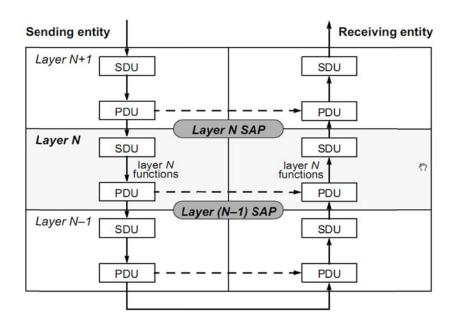

| Figure 8: PDU and SDU in a protocol stack. [9]                                 |     |

|                                                                                |     |

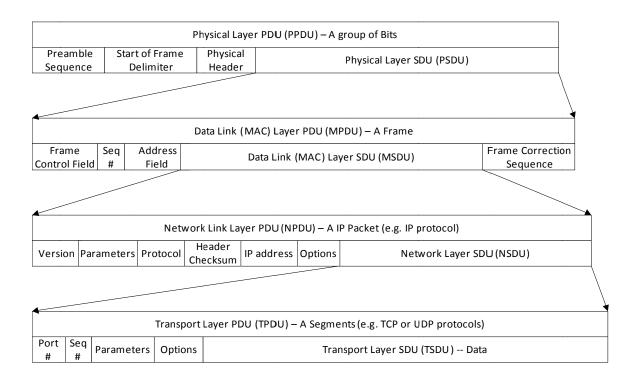

| Figure 9: The data structure of PDU and SDU in the first four OSI layers. [10] |     |

| Figure 10: An example of Data Race.                                            |     |

| Figure 11: An example of Deadlock.                                             | 18  |

| Figure 12: The data structure of the PDU and SDU in the first four OSI layers. | 20  |

| [27]                                                                           |     |

| Figure 13: The development history of pattern matching algorithms. [30]        |     |

| Figure 14: Shift in the Prefix Algorithm (Knuth-Morris-Pratt)                  |     |

| Figure 15: Shift in the Suffix Algorithm (Boyer-Moore).                        |     |

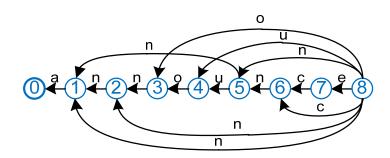

| Figure 16: A DFA built by BOM for Pattern "announce". [10]                     | 26  |

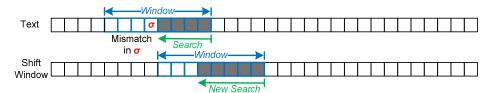

| Figure 17: Shift of the search window after the failure of the search by BOM.  |     |

| [11]                                                                           |     |

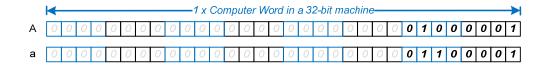

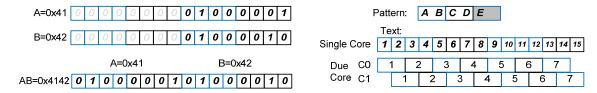

| Figure 18: Comparison of two ASCII characters in the memory                    | 27  |

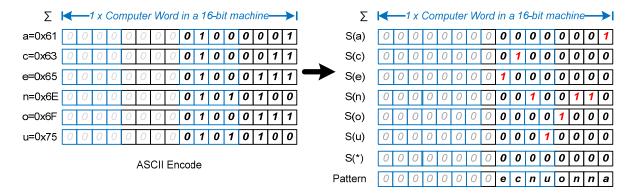

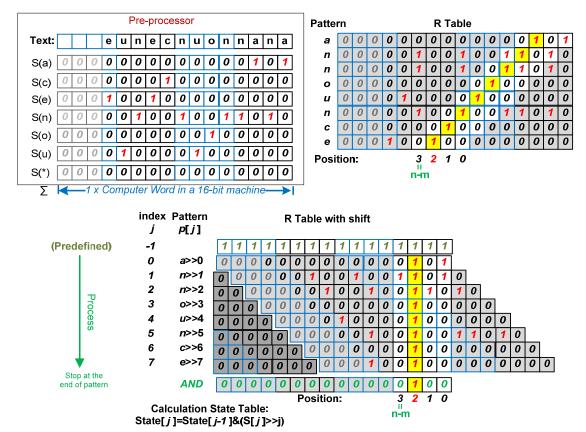

| Figure 19: Searching pattern "announce" in the text "anannouncenue" in a 16-   |     |

| bit computer by the Bit-Parallelism (Shift-AND) Algorithm.                     |     |

| Characters are encoded in ASCII                                                | 28  |

| Figure 20: An AC automaton of pattern $P = \{announce, annual, annually\}$ .   |     |

| Double-circled states are terminal. [11]                                       | 30  |

| Figure 21: The Sub linear Multi-string Matching algorithm with example         |     |

| patterns P = {announce, annual, annually}                                      | 30  |

| Figure 22: The pattern analysis of the Wu-Manber algorithm with example        |     |

| patterns P = {announce, annual, annually} and the length of the block          |     |

| = 2.                                                                           | 31  |

| Figure 23: The automaton of SBOM for example patterns $P = \{announce,$        |     |

| annual, annually. The factor oracle of the reverse set Plmin =                 |     |

| {announce, annual }. [11]                                                      | 32  |

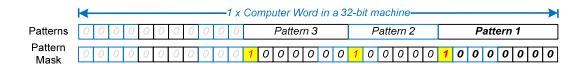

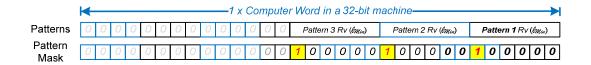

| Figure 24: Three patterns in a 32-bit computer for the MBP Algorithm.          |     |

| Figure 25: Three patterns in a 32-bit computer for the MBNDM Algorithm         |     |

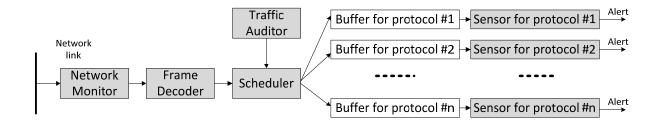

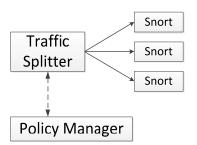

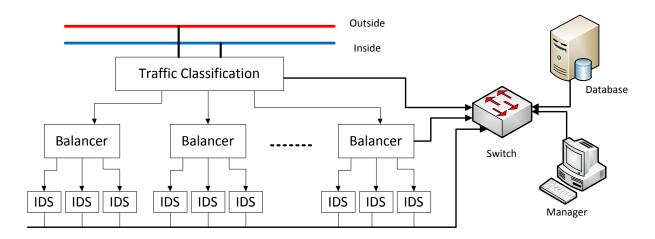

| Figure 26: The architecture of the NIDS model by Zhuojun Zhuang.[56]           |     |

| Figure 27: Adaptive Load Balancing Architecture of Snort by M. Shoaib          | 50  |

|                                                                                | 26  |

| Alam. [42]                                                                     | 30  |

| Figure 28: A Stateful Real Time Intrusion Detection System by M.               | 27  |

| Meharouech Sourour. [59]                                                       |     |

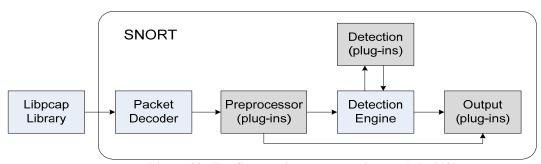

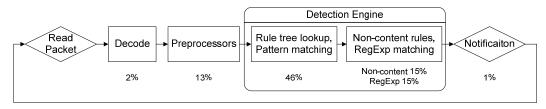

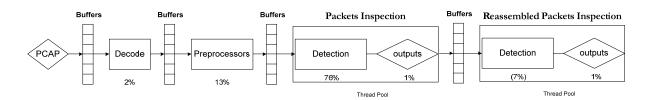

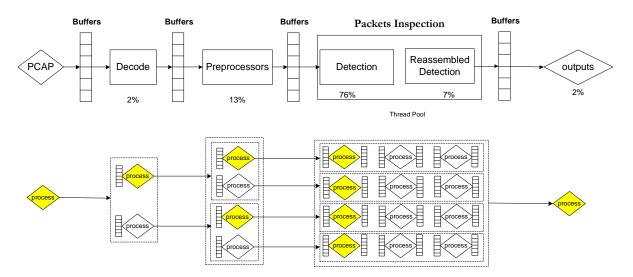

| Figure 29: The Snort primary processing module. [10]                           | 39  |

| Figure 30: The Snort packet processing loop with the percentage of time spent  | 2.2 |

| in each phase. [9]                                                             | 39  |

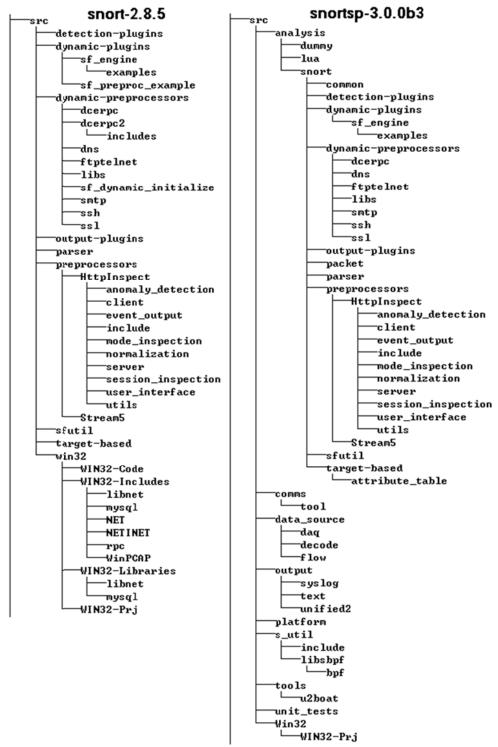

| Figure 31: The code structure of Snort for version 2.8 and 3.0beta.                         | 40 |

|---------------------------------------------------------------------------------------------|----|

| Figure 32: The "struct" of a Packet in Snort.                                               | 42 |

| Figure 33: The struct of SnortConfig in Snort.                                              | 44 |

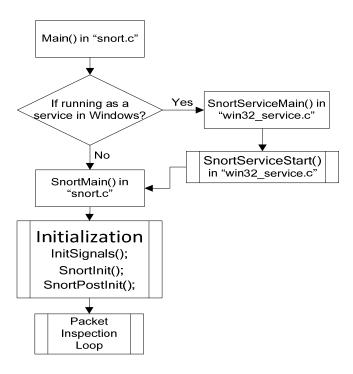

| Figure 34: The entry process of Snort.                                                      | 45 |

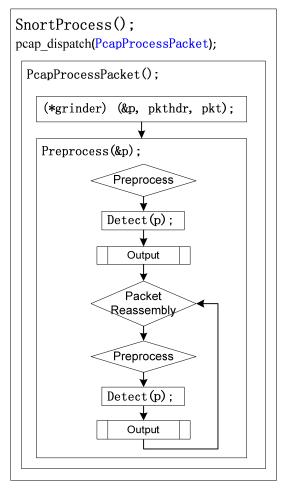

| Figure 35: The structure of the process functions of Snort                                  | 47 |

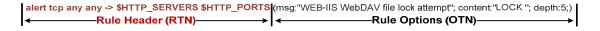

| Figure 36: An example of a Snort rule.                                                      | 49 |

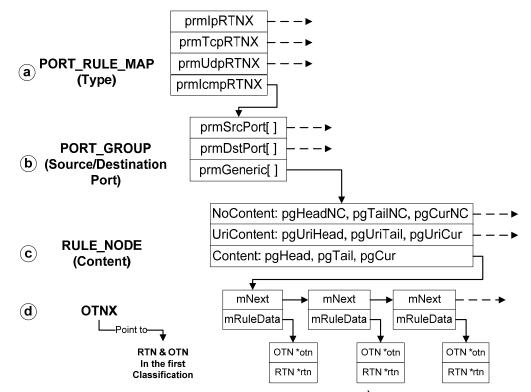

| Figure 37: The structure of the Three-Dimension Chain, 1 <sup>st</sup> Classification Rule  |    |

| Tree                                                                                        | 49 |

| Figure 38: The division of an example rule in RTN and OTN                                   | 50 |

| Figure 39: The structure of the Fast Packet Detection Chain, 2 <sup>nd</sup> Classification |    |

| Rule Tree. [14]                                                                             | 50 |

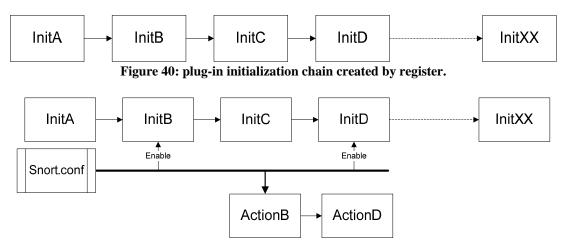

| Figure 40: Plug-in initialization chain created by register.                                | 53 |

| Figure 41: Plug-in action chain created by initialization from the plug-in                  |    |

| initialization chain.                                                                       | 53 |

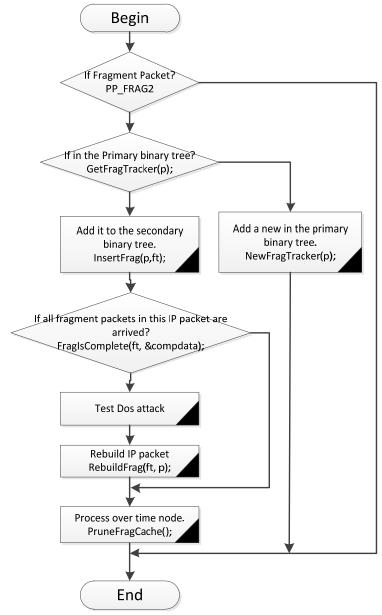

| Figure 42: The defragment process of Snort.                                                 | 55 |

| Figure 43: The struct of "OTNX MATCH DATA" in "InitMatchInfo"                               |    |

| function.                                                                                   | 56 |

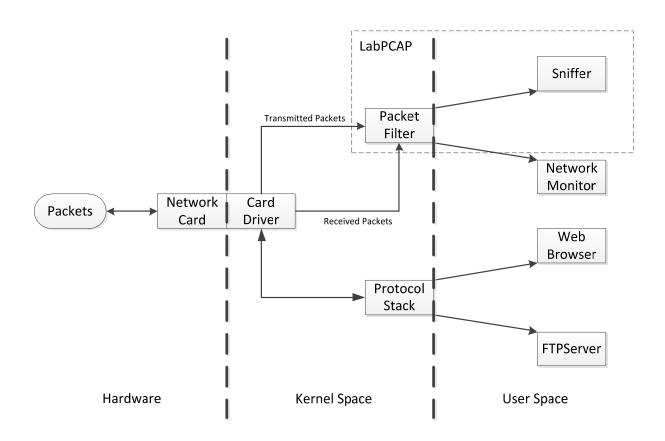

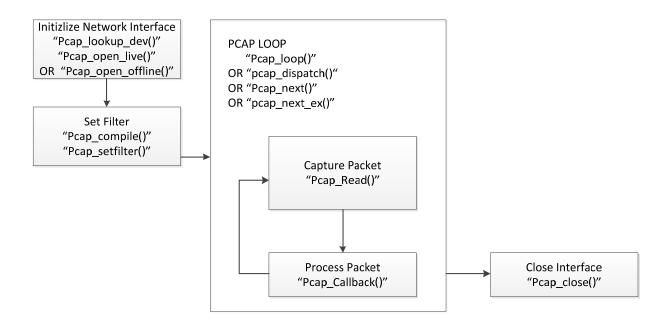

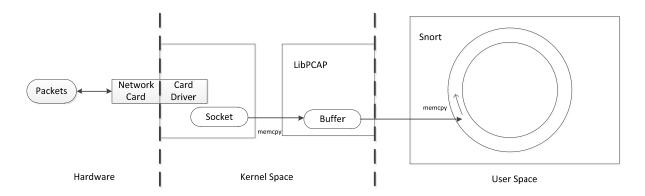

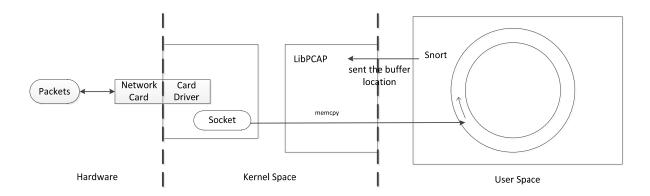

| Figure 44: The structure of packets capture. [62]                                           | 59 |

| Figure 45: The packet process structure of LibPCAP.                                         | 59 |

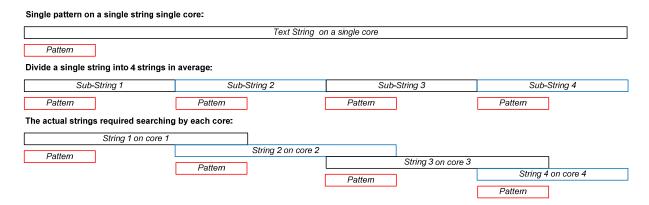

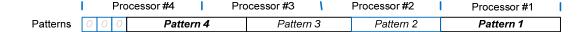

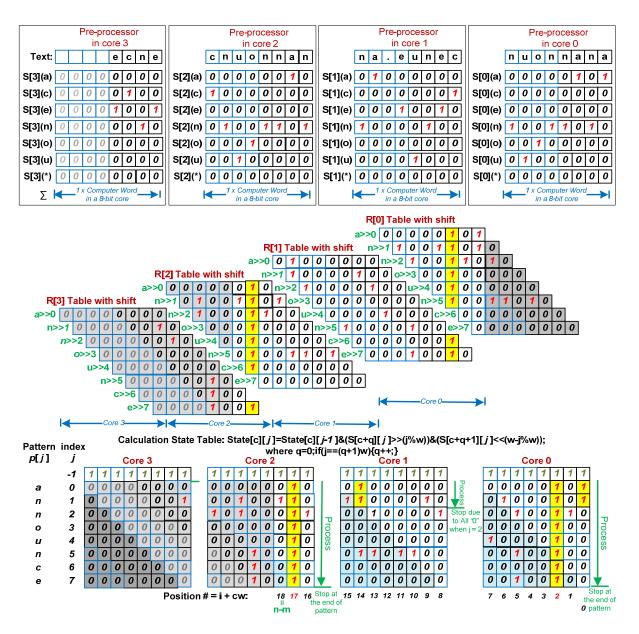

| Figure 46: Data parallelization on Window shift algorithms on 4 processor                   |    |

| cores.                                                                                      | 64 |

| Figure 47: Multiple Bit-Parallelism algorithm for multicore computers.                      | 65 |

| Figure 48: Search pattern "announce" in the text "anannouncenue" with one-                  |    |

| core in a 16-bit computer by Reversed Bit-Parallelism (Reversed                             |    |

| Shift-AND) Algorithm, $n = 13$ , $m = 10$ , $c = 1$ , $w = 16$ . Characters are             |    |

| encoded in ASCII. (Compare with Figure 7 to see the differences with                        |    |

| BP)                                                                                         | 66 |

| Figure 49: Searching pattern "announce" in the text                                         |    |

| "anannouncenue.annannouncence" with four-core in a 8-bit computer                           |    |

| by the Reversed Bit-Parallelism (Reversed Shift-AND) Algorithm, n =                         |    |

| 28, $m = 10$ , $c = 1$ , $w = 16$ . Characters are encoded in ASCII.                        | 69 |

| Figure 50: Parallelized Aho-Corasick (PAC) algorithm with 2 cores, d = 2                    | 71 |

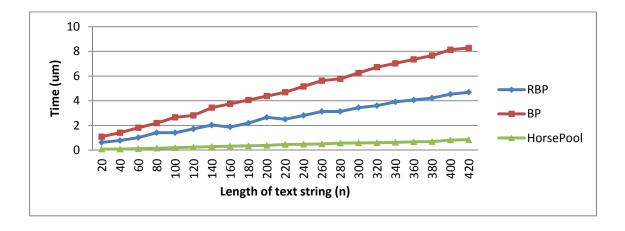

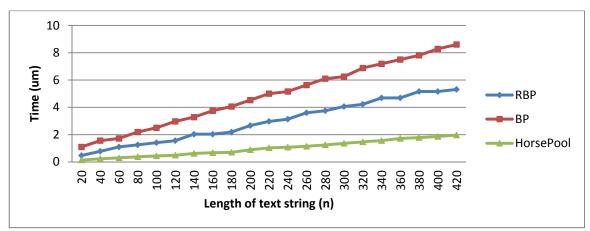

| Figure 51: The performance comparison of single pattern matching algorithms                 |    |

| when the length of pattern is 7 characters, and the length of text varies                   | 73 |

| Figure 52: The performance comparison of single pattern matching algorithms                 |    |

| when the length of the pattern is 3 characters, and the length of text                      |    |

|                                                                                             | 74 |

| Figure 53: The performance comparison of single pattern matching algorithms                 |    |

| when the length of the pattern is 64 characters, and the length of text                     |    |

| varies. There are multiple occurrences.                                                     | 74 |

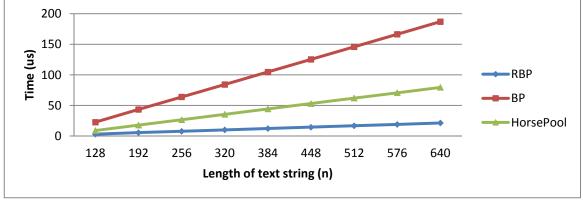

| Figure 54: The performance comparison of single pattern matching algorithms                 |    |

| when the length of text is 640 characters, and the length of pattern                        |    |

| varies. There are multiple occurrences.                                                     | 75 |

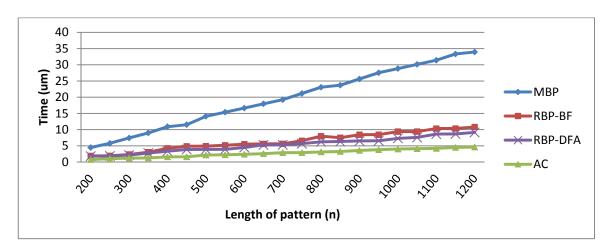

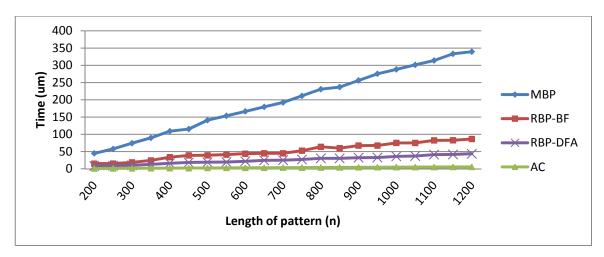

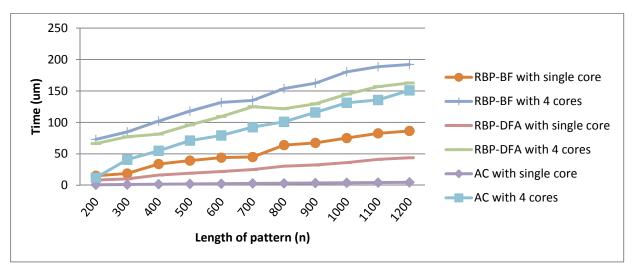

| Figure 55: The performance comparison of multiple pattern matching. There                   |    |

| are 10 different patterns, and all patterns are in the text                                 | 76 |

| Figure 56: The performance comparison of multiple pattern matching. There                   |    |

| are 100 different patterns, and all patterns are in the text.                               | 77 |

| Figure 57: The performance comparison of multiple pattern matching. There                   |    |

| are 100 different patterns, and all patterns are in the text.                               | 77 |

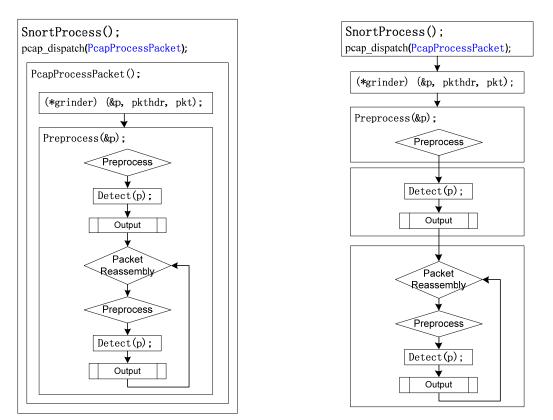

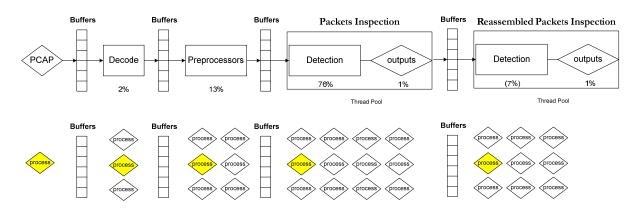

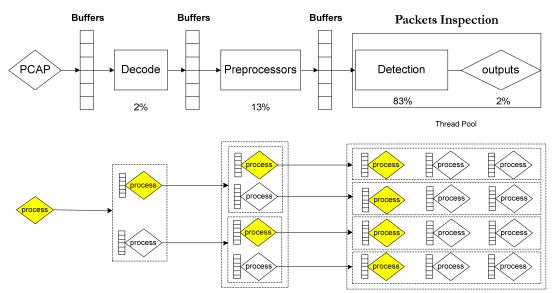

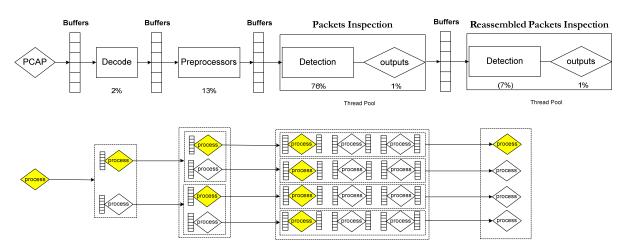

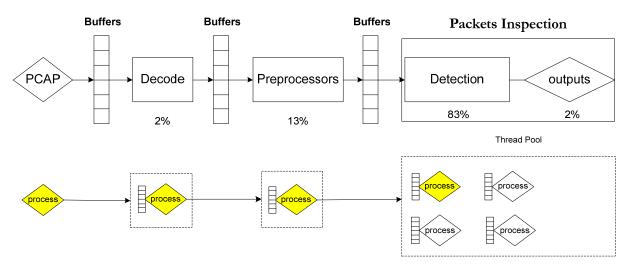

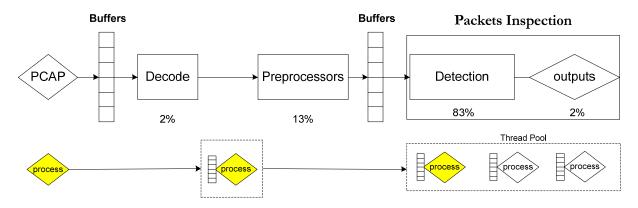

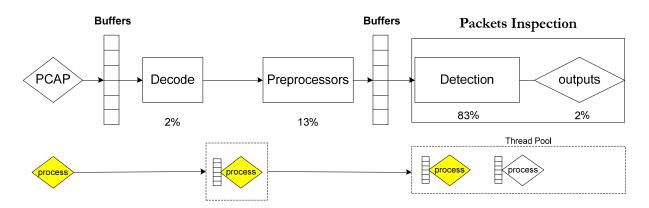

| Figure 58: The processing flowchart of Snort, the left flowchart shows the   |     |

|------------------------------------------------------------------------------|-----|

| structure of official Snort 2.8; the right flowchart shows the pipeline      |     |

| structure of Snort.                                                          |     |

| Figure 59: The pipeline process of Snort.                                    |     |

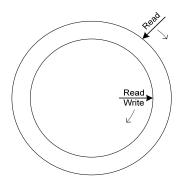

| Figure 60: The circular buffer of the pipeline.                              |     |

| Figure 61: The struct of "ePacketPack".                                      |     |

| Figure 62: The struct of a circular buffer.                                  | 86  |

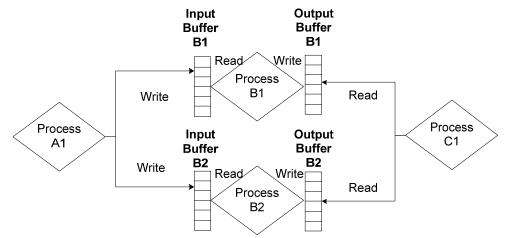

| Figure 63: The pipeline process of Snort with multiple processes in some     |     |

| pipes                                                                        | 87  |

| Figure 64: The pipeline process of Snort with multiple processes, all        |     |

| inspection and outputs are in one pipe.                                      |     |

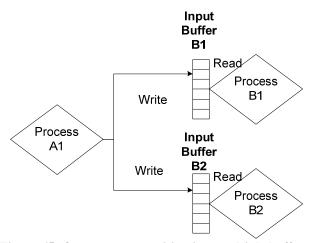

| Figure 65: One processor writing into multiple buffers.                      | 89  |

| Figure 66: The pipeline process of Snort with multiple processes. Normal     |     |

| inspection and reassembled inspection are in two different pipes.            | 89  |

| Figure 67: One processor collects (reads) data from multiple buffers.        | 90  |

| Figure 68: The pipeline process of Snort with multiple processes, All        |     |

| inspections are in one pipe and the outputs are in a different pipe          | 90  |

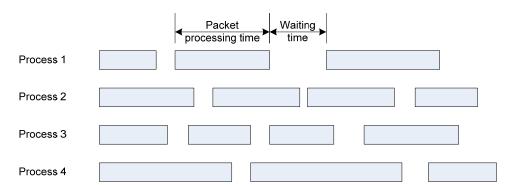

| Figure 69: The processing time and waiting time in a simple parallelized     |     |

| system.                                                                      | 91  |

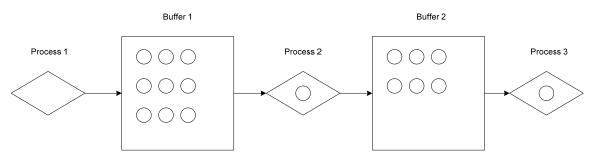

| Figure 70: An example of a buffer pipeline system.                           | 92  |

| Figure 71: Snort rules set used for the tests                                |     |

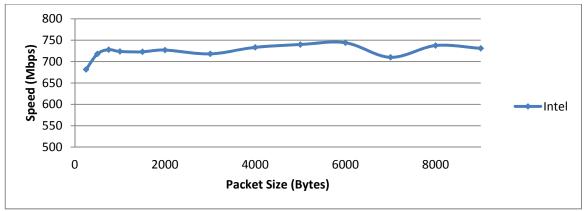

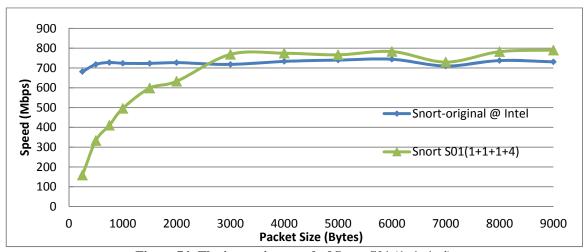

| Figure 72: The inspection speed of original sequential Snort on the Intel    |     |

| computer                                                                     | 96  |

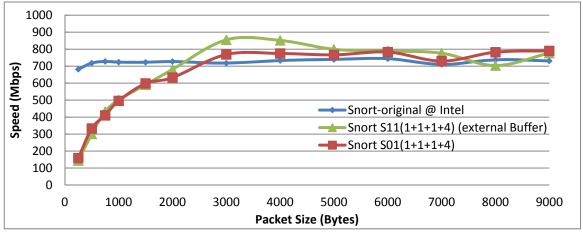

| Figure 73: Snort test structure S01 (1+1+1+4).                               | 96  |

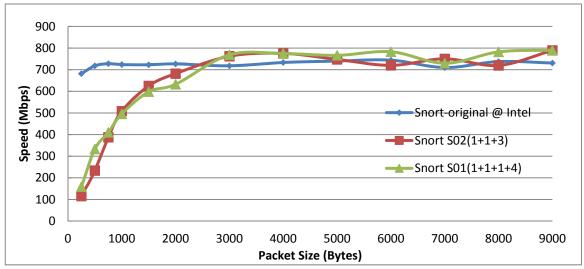

| Figure 74: The inspection speed of Snort S01 (1+1+1+4).                      | 97  |

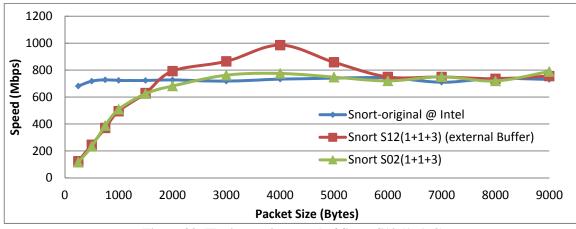

| Figure 75: Snort test structure S02 (1+1+3)                                  | 97  |

| Figure 76: The inspection speed of Snort S02 (1+1+3)                         | 98  |

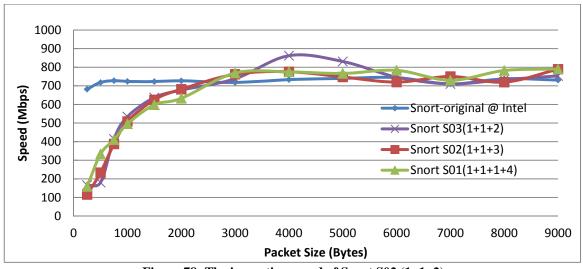

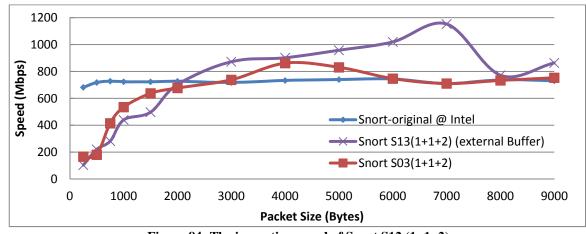

| Figure 77: Snort test structure S02 (1+1+2)                                  | 98  |

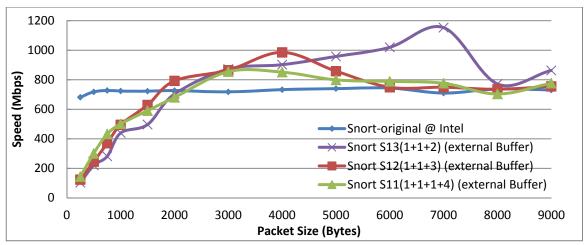

| Figure 78: The inspection speed of Snort S02 (1+1+2)                         | 99  |

| Figure 79: Packet buffer schematic of LibPCAP.                               | 99  |

| Figure 80: An external Packet buffer schematic of LibPCAP                    | 100 |

| Figure 81: A list of primary functions for the external buffer in LibPCAP    | 100 |

| Figure 82: The inspection speed of Snort S11 (1+1+1+4).                      | 101 |

| Figure 83: The inspection speed of Snort S12 (1+1+3)                         |     |

| Figure 84: The inspection speed of Snort S12 (1+1+2)                         |     |

| Figure 85: The inspection performance comparison using an external buffer in |     |

| LibPCAP                                                                      | 102 |

|                                                                              | 103 |

## List of Tables

| Table 1: An approximate speed list with data transmission on a Intel Duo-core |    |

|-------------------------------------------------------------------------------|----|

| 2.33 GHz CPU with a DDR2 667 asymmetric dual channel memory                   |    |

| system                                                                        | 16 |

| Table 2: Typical Snort Detection Plugins                                      |    |

| Table 3: RBP vs. Bit-Parallelism (BP)                                         | 69 |

| Table 4: The number of states in the automaton vs the size of "d" in the PAC  |    |

| algorithm                                                                     | 72 |

| Table 5: RBP vs. Windows-Shift (e.g. BM, KMP, Horspool)                       |    |

| Table 6: The states of circular buffer.                                       | 84 |

#### Acknowledgments

I would like to express my sincere gratitude to my supervisors, Professor Dr. Harsha Sirisena from the Electrical and Computer Department in University of Canterbury, Dr. Zhiyi Huang from the Computer Science Department in University of Otago for their guidance, invaluable support and constant encouragement. Their time and effort in providing me with research direction, research ideas and suggestions, real testing computer environment, and other uncountable aspects, is very much appreciated.

My special thanks to Professor Dr. Krzysztof Pawlikowski, Dr. Allan McInnes, Dr. Andreas Willig, and all the members in the network research group from the University of Canterbury for their enlightening advice and wonderful discussion during the weekly meeting, and all members in the system research lab from University of Otago for their help.

I am also grateful for the Electrical and Computer Engineering Department in University of Canterbury and Computer Science Department in the University of Otago for providing me an excellent work environment and equipment during the past years. And special thanks to, David van Leeuwen, Tony Dale and all other computer staffs.

I also want to express my acknowledgements to Industrial Controls South Canterbury to support my studying in different aspects.

Lastly, thanks to any other people and organizations that provide me help and support during my studying and Christchurch earthquake periods.

#### Glossary

AC algorithm Aho-Corasick algorithm Arithmetic Logic Unit ALU

**ANSI** American National Standards Institute

Application Programming Interface. It serves as an interface between API

different software programs.

**ARP** Address Resolution Protocol

American Standard Code for Information Interchange ASCII

ASIC Application-specific integrated circuit **BDM** Backward Dawg Matching Algorith

Backward Nondeterministic Dawg Matching **BNDM**

Bogo Million instructions per second, an unscientific measurement of **BogoMips**

CPU speed made by the Linux kernel when it boots, to calibrate an

internal busy-loop.

BO Back Orifice, remote administration software

Backward Oracle Matching algorithm BOM

BM algorithm Boyer-Moore, a multiple pattern matching algorithm

BP Bit-Parallelism algorithm

Cilk A general-purpose programming language designed for multithreaded

parallel computing by MIT.

CPU Central Processing Unit

Cyclic Redundancy Check, an error-detecting code Distributed Denial-of-Service attack **CRC**

**DDos DFA** Deterministic Finite Automaton

DMZDemilitarized Zone in Computer Networking

DPI Deep packet inspection DoS Denial-of-Service attack

Forward Dawg Matching Algorithm **FDM FPGA** Field-programmable Gate Array

Gigabit Ethernet **GbE**

Host-based Intrusion Detection System HIDS HIPS Host-based Prevention Detection System

HTTP Hypertext Transfer Protocol

a multiple pattern matching algorithm Horspool **ICMP** Internet Control Message Protocol

Intrusion Detection System IDS

**IEEE** Institute of Electrical and Electronics Engineers

IEEE 802.1Q Virtual LAN or VLAN

Internet Information Services, a set of Internet-based services for IIS

servers using Microsoft Windows

ΙP Internet Protocol

**IPS** Intrusion Detection System

Knuth-Morris-Pratt pattern matching algorithm **KMP**

LibPCAP An open source packet capture library

Maotai A shared memory multiprocessing programming API designed by the

University of Otago for multicore computers.

**MBNDM** Multiple BNDM algorithm Multiple Bit-Parallelism algorithm **MBP**

Massachusetts Institute of Technology in US MIT

Message Passing Interface **MPI**

MTU Maximum Transmission Unit

NFA Nondeterministic Finite Automaton

NIDS Network-based Intrusion Detection System

NIPS Network -based Prevention Detection System

Open Multi-Processing, an API that supports multi-platform shared

memory multiprocessing programming.

OS Operating System

OSI Open Systems Interconnection model

OTN Option Tree Node

PAC Parallelized Aho-Corasick algorithm

PCAP Packet Capture

PDU Protocol Data Unit in ISO OSI model

PHAC Parallelized Hashed AC

POSIX Portable Operating System Interface for Unix. It is a family of related

standards specified by the IEEE to define the API.

Qos Quality of service

RAM Random-access Memory

RBP Reversed Bit-Parallelism algorithm

RISC Reduced Instruction Set Computer

RTN Rule Tree Node

SBDM Set Backward Dawg Matching

SBOM Set Backward Oracle Matching

SDU Service Data Unit in ISO OSI model

SNMP Simple Network Management Protocol

Snort An open source IDS/IPS software, www.snort.org

SPARC Scalable Processor ARChitecture, a RISC microprocessor instruction

set architecture

SQL Structured Query Language, a database computer declarative language.

TCAM Ternary Content Addressable Memory

TCP Transmission Control Protocol

TM Transactional Memory UDP User Datagram Protocol

VODCA View-Oriented, Distributed, Cluster-based Approach

VOPP View Oriented Parallel Programming, a shared memory

multiprocessing programming API designed by the University of

Otago.

VoIP Voice over IP

Web-DAV Web-based Distributed Authoring and Versioning

#### I. INTRODUCTION AND BACKGROUND

#### 1 Introduction

#### 1.1 Computer Network System and Its Security

Communication has always been an important part of human development and a spoken language gives people the ability to have face to face communication. Later, people invented writing letters and beacon towers to solve the distance issue and from the 20<sup>th</sup> century, information gathering, processing and distribution have become the key technology. People invented the telephone and built telephone networks to have long distance and instant communication. The invention of the radio enabled communication to get rid of the cable restrictions and then, the birth and growth of the computer industry accelerated the development of information processing and communication.

Although the development of technology greatly reduces the distance of people, longer distance and more media also bring more security issues for the communicators. Usually, face to face speaking can only be bugged, but the speaker's speech cannot be modified; in letter communication, the message can also be forged by similar handwriting, but it is still difficult. The development of attacking technology came from telephone networks. In order to make unpaid calls, some people tried to find some telephone system bugs, and some experts even broke into the provider's accounting system and modified their records. In the computer network era, hackers also invent computer viruses, worms, spywares, and backdoors to destroy, steal data, block the network, advertise on, and control remote computers. On the Internet, an attacker can do almost everything they want from the other side of the earth. And they can easily hide themselves by controlling one or a group of zombie computers (usually called "Botnet").

On the other hand, most of the intruders started only from personal interest and in the pursuit of higher skills. Even so, now, because of the huge benefits, the attackers are becoming a new industrial chain. They are professional, and sell their products and services on the Internet. A person with very limited skills can buy and download some attack tools to perform attacks, or employ Botnet to storm off the network. Even an unskilled person can easily find some professional attackers to perform attacks for them on the Internet.

A study by Michel Cukier from Clark School, University of Maryland in February 2007 was "one of the first to quantify the near-constant rate of hacker attacks of computers with Internet access—every 39 seconds on average". [1]

#### 1.2 Intrusion Detection / Prevention System

Historically, because several major computer viruses have caused huge global losses, people are starting to recognise the importance of anti-virus software. How do they have the virus? Some computers have them by web browning, email and malware. However, some computers, such as servers, without internet access can also get backdoor and data stolen by attacks. A basic firewall can only block some ports on data-link layers and IP addresses on network layers, but cannot see anything on the application layer. Without seeing the detail of the packets, it is difficult to distinguish between a normal access and an attack.

The intrusion detection system (IDS) is a tool which has the ability to read the detail of the network packets. The IDS analyses network packets, captured from the network to identify attacks. The Intrusion Prevention System (IPS) will also automatically block the attacks. Now, IDS/IPS has become a necessary addition to the security infrastructure of most organizations.

Basically, an IDS/IPS can be divided into host-based and network-based. A host-based IDS/IPS (HIDS/HIPS) such as traditional anti-virus software, which operates on information collected from within each individual computer system, can be used to detect or block attacks. However, it has two disadvantages. Firstly, HIDS/HIPS spends too many CPU resources on the host computer, and the benefit can only be received by itself. Secondly, HIDS/HIPS cannot prevent attacks to the network devices such as switches and the intruder can also sniff the packets during data transmission in the network. A network-based IDS/IPS (NIDS/NIPS), which captures and analyses network packets on a network scope can be used to detect all attacks in the network, and all trust domains can receive the benefit.

In general, there are two main intrusion detection techniques: misuse detection and anomaly detection. Misuse detection identifies evidence of malicious behaviour by matching it against predefined descriptions of attacks, or signatures. It has a low false alarm rate and a high miss detection rate. Anomaly detection defines normal behaviour and attempts to identify any unacceptable deviation as possibly the result of an attack. Although anomaly detection has a low miss detection rate, and can detect new attacks, however, it has a high false alarm rate. Misuse detection usually contains a group of signatures, which are used to identify different attacks. The limitation in implementing misuse detection is the high processing load during the traffic detection, which causes a much lower packet forwarding rate in the network than the normal layer-3 switch.

Snort is a lightweight open source network intrusion prevention and detection system (IDS/IPS) developed by Sourcefire [2] and is mainly based on a misuse detection mode. It is a well-designed completed IDS and IPS (the inline mode of Snort) solution for a general purpose CPU, such as x86/x64. It supports both IPv4 and IPv6. However, because of its pure software design, it has a relatively slower processing speed compared with ASIC and FPGA.

On the other hand, it is more flexible and has a lower deployment cost, as on the ASIC platform it is almost impossible to make any update and the FPGA is also difficult to upgrade. At this point, many world famous commercial IDS/IPS products are made by a general purpose CPU, such as Cisco.

Currently, Snort is designed as a single process for the detection process, only the reload module uses a separate thread to track the modification of the configuration file and rule update. It was an excellent design last century, but has become a little old now, as the CPU frequency is hard to increase any more, and the performance of a sequential process design is also difficult to improve with the same algorithm. Parallelization is a method which can be used to increase the performance of Snort.

#### 1.3 Multi-core and Parallelization

The earliest computers were programmed by altering the electronic circuitry. In 1945, John von Neumann proposed EDVAC (Electronic Discrete Variable Automatic Computer) architecture which recommended the use of binary as the computer language, and introduced the memory system in the computer to store both instruction sets and data. Today, computers still inherit the John von Neumann architecture. Therefore, the speed of a computer is not only decided by the CPU frequency, but is also based on the speed of the memory and cache.

In 1965, Gordon E. Moore introduced the famous Moore's Law: "the number of transistors that can be placed inexpensively on an integrated circuit has doubled approximately every two years". Moore's Law applies to any semiconductor products including a processor's performance and its processing speed, memory capacity, and even the power consumption of the processor which has a similar increase period. History has proved the accuracy of Moore's Law. However, Moore's Law stopped working on the processor's operating frequency from the middle of the 20th century. On 20th October 2004, Intel CEO Dr Craig

Barrett, begged forgiveness for not making a 4GHz Pentium 4, and Intel's product roadmap was substantially revised from the higher frequency development to multi-core chips.

What about the overall increase in performance? Anant Agarwal and Markus Levy indicated a "Moore's Gap" in 2007 and Figure 1 shows the gradually expanding gap from 2002. They analyzed that "the performance scaling fell apart in 2002 due to three factors, namely diminishing returns from single CPU mechanisms such as caching and pipelining, the power envelopes (both active and leakage related), and wire delay." Their suggestions to close the Moore's Gap are multiple full-fledged cores on the same CPU and ample parallelism algorithms. [3]

Figure 1: The Moore's Gap. [3]

From the 1960s, people began to develop supercomputers. A supercomputer usually has a much higher computing power than an ordinary computer in the same era, but it does not mean it runs a program faster. A supercomputer is usually built by vector processors, or a cluster of ordinary processors, and these processors are connected not through a high speed bus, but a single processor with a super high operating frequency, instead. And the frequency may be lower than ordinary processors for power efficient reasons. Figure 2 shows the relationship of a processor's power consumption and operating frequency. It shows the processor's power consumption increases exponentially with an increase in the processor's

operating frequency. Therefore, a single sequence program may run more slowly on the super computer.

Figure 2: CPU power consumption vs. clock frequency, "In AMD's process, for 200MHz frequency steps, two steps back on frequency cuts power consumption by ~40% from maximum frequency". [4]

Figure 3: The architecture of a Blue Gene/L. [5]

For example, a Blue Gene/L has 360 TFLOPS computing power. It contains 64 racks and each rack is built by 32 node boards. Each node board includes 16 computer cards and each computer card has two duo-core PPC400 processors. Refer to Figure 3 and Figure 4. There are in total 65536 cores, and the frequency of the processor core is only 700 MHz. Each core

has 5.6 GFLOP. Compared with a supercomputer, an ordinary quad-core processor Intel Core if 965 XE has 70 GFLOPS in double precision, and each core is about three times faster than a single core in a Blue Gene supercomputer. Basically, supercomputers require the support of the parallelization in software, which can distribute a single huge job to different processors.

Figure 4: The architecture of a Blue Gene/L ASIC processor. [6]

From the history, we can see that today's super computer will be tomorrow's ordinary computer. As the processors are made smaller, it will be possible to have thousands of cores built in one single processor, and hundreds of processors in one computer. In recent years,

people have been working on integrating multiple cores into one processor to achieve a higher overall performance.

In 2002, Intel introduced its Hyper-Threading technology in Foster MP-based Xeon processors. Actually, it is not a type of multi-core processor as Hyper-Threading duplicates certain sections of the processor, in order to have two "logical" processors to the operating system, which allow the OS to schedule two threads simultaneously. However, it only has one execution unit. The scheduled threads have to queue to be executed by the single execution unit. This technology is also called "multi-thread" by some other companies, such as Sun Microsystems.

Multi-cores computers have real multiple execution units and an individual (L1) cache for each execution unit. It looks like a pizza shop in that there are two chefs but only one oven in the hyper-threading system; there are two chefs and also two ovens in the dual-core system. The multi-core processor puts a number of processors onto a single integrated circuit die, or onto multiple dies, but in a single-chip package they usually share one higher level cache between some of the processors. Some examples are shown in Figure 5 and Figure 6.

Figure 5: Three examples of multicore implementations, one showing two identical CPUs, one with an RISC CPU and a DSP, and one with 16 identical CPUs. [7]

#### **Dual CPU Core Chip**

Figure 6: Diagram of a generic dual-core processor, with CPU-local level 1 caches, and a shared, on-die level 2 cache.

Another type of computer system has multiple sockets in one system. The processors in different sockets do not share any cache, but they usually share the memory and memory bus on the same motherboard.

Because a supercomputer is also super expensive owing to the consistency of the design, a computer cluster is designed for powerful computing power. A computer cluster is built by a group of ordinary computers and connected through Ethernet or even through the Internet. A group of retired computers can also achieve very powerful computing power with computer cluster technology. People also expand its use to invent a new computing architecture, and give it a beautiful name "cloud computing". Many enterprises have super huge groups of computers, called "clouds". For example, Google had over 450,000 computer clusters in 2006.

In all of the above technology, many people thought the multi-core processor was a good solution. Now, many processor companies, such as Intel, AMD and Nvidia, try to increase the number of processor cores rather than the frequency. In the future, it will be possible to have a

very large number of cores, such as hundreds or even thousands of cores, in one single processor. However, the frequency may not change much. In order to reduce the power consumption, the frequency may be lower than the current frequency.

The running speed of a sequence program is generally decided by the frequency of the CPU. However, a multiple processors computer cannot help to increase the speed of a sequence program. Currently, because the number of processors in a single computer system is not very high, and it normally runs multiple programs simultaneously; different processors can be used to assign different programs by the operation system. With the improvement in technology, the number of processors in a single system has become much higher. Many processors will not get any work from the operation system if all programs are sequence programs. Therefore, parallelization of a sequence program is becoming more important. For many big jobs, it will be easy to parallelize them on their data level. However, for some jobs, it will be difficult to split them up into smaller parts and work on them simultaneously, such as a state machine.

#### 1.4 Research Goals

This thesis will focus on the parallelization of network deep packet inspection programs. As Snort is a world famous open source typical deep packet inspection based intrusion detection system, this thesis will use the parallelization of Snort as an example.

Currently, Snort is still a sequence program. Some types of parallelization have been implemented by researchers on FPGA and some special network processors. However, almost none of them are based on a general processor. This thesis will attempt to find and evaluate some possible methods of Snort parallelization on general computers, such as the x86, x64 and RISC systems. Also, all designs and tests have been carried out in a Linux environment with kernel version 2.6.

At the end of this thesis, the detection performance (throughput) is expected to be increased by parallelization processing. However, as this thesis will not focus on the detection method and signature design, the detection rates and false alarm rates will not change.

#### 1.5 Dissertation Structure

In the following section of this thesis, some background information and some previous work in this area will be discussed. Some mechanisms related to the design in the later chapter will be discussed in detail in Chapter 2. Then, the structure and mechanism of Snort and LibPCAP will be analysed in Chapter 3 and Chapter 4 respectively. Later, the possibility of pattern matching parallelization on a general computer will be discussed in Chapter 5 and a packet level parallelization of Snort and LibPCAP will be evaluated in Chapter 6. Finally, a conclusion of this thesis and some possible future work will be given.

#### 2 Background and Related Work

#### 2.1 Network Packets and "libpcap" library

In general, a network packet is a formatted unit of data transmitted in the computer network. It is defined by the International Organization for Standardization (ISO) in the Open Systems Interconnection model (OSI model) for the network structure. The OSI model divides a communications network system into seven layers, as shown in Figure 7. Each layer is a collection of similar functions that provide services to its upper layer and receive services from its lower layer.

| OSI Model          |          |                |                                                                                                            |  |

|--------------------|----------|----------------|------------------------------------------------------------------------------------------------------------|--|

| Data unit Layer Fu |          | Function       |                                                                                                            |  |

|                    | Data     | 7. Application | Network process to application                                                                             |  |

| Host<br>layers     |          |                | Data representation, encryption and decryption, convert machine dependent data to machine independent data |  |

| layers             |          | 5. Session     | Interhost communication                                                                                    |  |

|                    | Segments | 4. Transport   | End-to-end connections and reliability, flow control                                                       |  |

|                    | Packet   | 3. Network     | Path determination and logical addressing                                                                  |  |

| Media<br>layers    | Frame    | 2. Data Link   | Physical addressing                                                                                        |  |

| -s.y <b>01</b> 0   | Bit      | 1. Physical    | Media, signal and binary transmission                                                                      |  |

Figure 7: The ISO OSI model. [8]

The IEEE 802 standards also define the data structure in each OSI layer. In an OSI layer, a service data unit (SDU), which is a unit of data, will be passed down to a lower layer, and then be encapsulated into a protocol data unit (PDU) by the lower layer in the sending entity; and the PDU will be decapsulated into the SDU for the upper layer in the receiving entity. In most cases, the SDU corresponds to the PDU of the upper layer. However, they are different in some cases. Sometime, the SDU is bigger, and the protocol in the upper layer requires a smaller PDU, so then this SDU will be divided into multiple PDUs. When a PDU requires a bigger size than the SDU, then multiple SDUs will be combined into one single PDU. The

protocol stack is shown in Figure 8, and a one to one PDU/SDU data structure is shown in Figure 9.

Figure 8: PDU and SDU in a protocol stack. [9]

Figure 9: The data structure of PDU and SDU in the first four OSI layers. [10]

In the OSI model, layer 1 generally performs the conversion of logical digital bits and a group of signals, such as electrical signals or optical signals, and transfers it in different coding

theories. A network device usually works from layer 2 to layer 4, e.g. an unmanaged switch is working in layer 2; a router is working in layer 3; and a basic firewall is normally working in layer 4. The deep packet will work in layer 7. However, as layer 5 and layer 6 are not used in the IP protocols, the transport layer SDU is usually the application layer PDU.

Snort uses the "libpcap" library for the packet capture. The data read from the physical NIC card is the PDU of the data link layer. "Libpcap" calls the driver of NIC and gets the SDU of the data link layer. Finally, the output data of "libpcap" is the PDU of the network layer. Snort reads the packets (PDU of the network layer) one by one, and then uses its decode module to get all header parameters of the network layer, transport layer and application layer for the single packet as the header information, and the SDU of the application layer as the packet content. For the packets in which one SDU is not corresponding to a single PDU, Snort will make the packet and process it in the packet reassembly part.

As the IP protocols are the primary layer-3 protocols in the world now, only IP protocols and its family members will be considered in Snort in this thesis.

#### 2.2 Parallelization Algorithms

In general, there are two major techniques to distribute a single job into different processors: multi-processing and multi-threading. Multi-processing technology uses "fork" to create an additional separate process manually in order to execute all later code after the process has been created, like running a new program. The idea of multi-threading technology is dividing a single big job into multiple small tasks, which can be scheduled to be executed by the operating system. Although, on a single core single processor system, the tasks will still be executed by a single processor by a time-division multiplexing, multi-threading can also increase the utilization of a single processor core by leveraging thread-level and instruction-

level parallelism. On a multi-threading and multi-processor enabled system, the multiple tasks will be distributed into different processor cores.

A main difference between multi-processing and multi-threading techniques is that a program running by multi-processing is actually executed by multiple processes in the operations system; but multi-threading will only use one single process to execute the program even on multiple processors. Therefore, different processors will have their own memory and cache space for the same variable name on a multi-processing system; on a multi-threading system, several threads work on the same set of data and also share their cache by default, which has a better cache usage or synchronization on its values.

Sometimes, different processes need to exchange some information between different processor cores. There are generally two methods for this: "Message Passing" and "Shared Memory".

"Message Passing" is a kind of communication mechanism by which processes can send and receive messages from other processes. It is just like multiple people working on one job together by communicating the progress, ideas and everything related to the job. The type of message includes the form of signals, data packets and so on. Message Passing Interface (MPI) is the most famous "message passing" API for parallel computing. It works on almost any type of platform, including multi-core, multi-thread systems, supercomputers and even computer clusters.

"Shared memory" sets a piece of memory as a public area, which can be simultaneously accessed by multiple processes. It works on a very low level, as the memory operation is the responsibility of an operation system. Linux kernel natively supports some methods to set up a shared memory area, such as "IPC Shared Memory (ipc.h)" and "POSIX Shared Memory

(shm.h)" and "mmap". A shared memory system is relatively easy to use since all processes share a single view similar to memory access to the same location. However, there are some limitations to the "Shared Memory". Firstly, the current computer architecture is not cache coherent. Secondary, the data accessing by different processes will also cause a memory coherence issue. Then, the execution method of the processor will cause "Data Race" and "Deadlock".

Cache memory is a random access memory (RAM) usually on the CPU that a processor can access more quickly than a regular RAM. In the data processing, the processor looks first in the cache (from a previous reading of data), and reads the RAM if the required data is not found in the cache by spending more time. Table 1 shows a general data accessing speed in a normal computer system. Data updated by one processor may be used by other processors, and the change needs to be reflected in the other processors at the same time, otherwise the different processors will be working with incoherent data. In a system in which the cache is not shared, there is usually a delay on the cache coherence.

Table 1: An approximate speed list with data transmission on an Intel Duo-core 2.33 GHz CPU with a DDR2 667 asymmetric dual channel memory system

|                                    | Speed (ns) |

|------------------------------------|------------|

| L1 cache reference                 | 1          |

| Branch mispredict                  | 5          |

| L2 cache reference                 | 7          |

| Mutex lock/unlock                  | 50         |

| Main memory reference              | 50         |

| Read 1 MB sequentially from memory | 250,000    |

| Disk seek                          | 10,000,000 |

| Read 1 MB sequentially from disk   | 30,000,000 |

In addition, an Arithmetic Logic Unit (ALU) of the processor will also not directly use data in a cache; it needs to read the data into some register in the processor and executes them from registers. The register is a small set of data holding places that are part of a computer processor. It is the closest storage unit from the ALU in the processor. The reading and writing process by different processes from and into the same memory location will cause "Data Race". An example is shown in Figure 10.

|                         | Thread #1   | Thread #2   | Note                                   |  |

|-------------------------|-------------|-------------|----------------------------------------|--|

| C Statement             | X = X+1     | X = X+1     | Two process try to update the same "X" |  |

|                         | LOAD X,R1   |             | X = 0, R1 = 0                          |  |

|                         | INC R1      |             | R1 = 1                                 |  |

| Instructions            | STORE R1, X |             | R1 = 1, X = 1                          |  |

| in the right<br>order   |             | LOAD X,R2   | X = 1, R2 = 1                          |  |

| orde.                   |             | INC R2      | R2 = 2                                 |  |

|                         |             | STORE R2, X | R2 = 2, <b>X = 2</b>                   |  |

|                         | LOAD X,R1   |             | X = 0, R1 = 0                          |  |

|                         |             | LOAD X,R2   | X = 0, R2 = 0                          |  |

| Instructions when "Data |             | INC R2      | R2 = 1                                 |  |

| Race"                   |             | STORE R2, X | R2 = 1, X = 1                          |  |

| nacc                    | INC R1      |             | R1 = 1                                 |  |

|                         | STORE R1, X |             | R1 = 1, <b>X = 1</b>                   |  |

Figure 10: An example of Data Race.

A solution to solve "Data Race" is forcing the atomicity of a group of instructions. Currently, mutual exclusion and transactional memory (TM) [12][13][14][15] can be used to guarantee the atomicity. Mutual exclusion is a traditional pessimistic approach method. The writer has the onus to make sure the shared variables are not being used by some others. A process or thread can lock shared variables before writing or reading, and unlock them at the end of accessing. And all other processes or threads cannot access these locked variables. They usually have to wait or sleep until the designed variable is available again. In the case of more than two processes or threads working on one shared variable, the possibility of accessing crash will increase exponentially with the increase in the number of processes or threads. "Semaphore" and "Mutex" are two API of mutual exclusion. However, when locks are nested, deadlock can happen. Deadlock is a situation where threads or processes are waiting for locks that will never be released. [18] An example is shown in Figure 11.

| Note (Thread #1)           | Thread #1      | Thread #2      | Note (Thread #2)              |

|----------------------------|----------------|----------------|-------------------------------|

|                            | Acquire lock 1 | Acquire lock 2 |                               |

| Waiting for lock 2 forever |                |                | Waiting for lock 1 forever as |

| as lock 2 has already been |                |                | lock 1 has already been       |

| locked by Thread 2, but    |                |                | locked by Thread 1, but       |

| Thread 2 is also waiting.  | Acquire lock 2 | Acquire lock 1 | Thread 1 is also waiting.     |

Figure 11: An example of Deadlock.

Transactional memory (TM) is an optimistic approach which was designed in the late 1980s, and is reaching maturity now. Differently from "locking" techniques, TM allows multiple threads or processes to perform modifications to the same shared memory without regard for any other threads or processes, and it is "Data Race" and "Deadlock" free. However, it records every read and write by different threads and processes in a log. The idea is a little similar to a journal file system, such as NTFS, ext3, JFS and ReiserFS. The reader will have the onus of verifying if any others have concurrently "write" access to the same memory when it completes an entire transaction. If there is no other "write" access, then the transaction will be committed as permanent, otherwise, it will roll back, and revise the transaction. As no threads or processes are required to wait for access to any resource, multiple threads or processes can continue to work concurrently. In the case of no modification in the shared memory, the performance of TM is very high. However, there are usually quite a number of repeated transactions in the real practice. In addition, the management overhead, e.g. maintaining the log and committing transactions, is still quite high in software based TM.

In a multi-thread/ multi-process environment, it will be hard to control the progress of each thread or process. For example, when two threads are assigned a job to acquire a lock on the same shared variable at the same time, both of them will have a chance to acquire the lock first, but the shared variable can only be locked by one thread. The other has to wait. As the order of which thread locks the shared variable is random, it is called a "determinacy race".

Some synchronization methods can be used to solve this issue, such as "barrier" (or "fence" sometimes) and "messages".

As the basic pessimistic approach shared memory has a few limitations and difficulties in use, some APIs are designed to avoid the "Data Race" and "Deadlock", and simplify the synchronization process. OpenMP is an API which makes the implementation of shared memory parallel programming much easier. However, it is only designed to optimize the performance of "for" loop in the program. [11][16]

The University of Otago has designed a series of View Oriented Parallel Programming (VOPP) [17]-[22] APIs, which include VODCA [23] and Maotai [24][25]. VOPP is a process based shared memory parallel programming API, and it can automatically prevent "Data Race" and "Deadlock". VODCA is specialized for a cluster system; and Maotai is specialized for a multi-core computer.

Cilk was designed by MIT in the middle of the 1990s and is a multithreaded parallel programming language based on ANSI C. It is designed for general-purpose parallel programming, but is especially effective for exploiting dynamic, highly asynchronous parallelism, which can be difficult to write in data-parallel or message-passing style. [26]

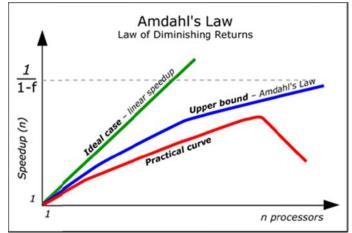

Different API and penalization methods have different performances. However, Gene Amdahl said that "the speedup of a program using multiple processors in parallel computing is limited by the time needed for the sequential fraction of the program". Amdahl's law can be used to predict the theoretical maximum speedup using multiple processors in parallel computing. Generally, the speedup of a program is limited by the time needed for the sequential fraction of the program. The formula is shown in Equation 1, and a speedup graph vs. the number of processors is shown in Figure 12.

$$Speedup = \frac{1}{1 - f} = \frac{1}{r_s + \frac{r_p}{n}}$$

Where  $r_s + r_p = 1$ ,  $r_s$  represents the ration of the sequential portion in one program, and

$$f = \left(1 - \frac{1}{n}\right) \cdot r_p.$$

**Equation 1**

Figure 12: The data structure of the PDU and SDU in the first four OSI layers. [27]

#### 2.3 Pattern Matching Algorithms and Detection Engine

Deep packet inspection is actually a type of pattern matching process and pattern matching is also the primary part of the detection engine of IDS. A highly efficient pattern matching algorithm will lead to a high performance IDS.

In general, the string matching includes exact string matching and approximate string matching (string matching allowing errors).

The one-dimensional exact string matching consists of [29] (1) Single String Matching, the most basic string matching algorithm, searches for a single pattern (p) with "m" characters in a text string (t) with the length "n". Both strings are built over a finite set of characters ( $\sigma$ ) denoted as alphabet ( $\Sigma$ ). (2) Multiple String Matching searches for a set of pattern P

simultaneously. (3) In Regular Expression Matching, the pattern is described by the regular expression. This is the most complex matching, a single regular expression can describe thousands of different normal patterns. Regular expression is now widely used in the IDS.

#### 2.3.1. Single Pattern Matching Algorithms

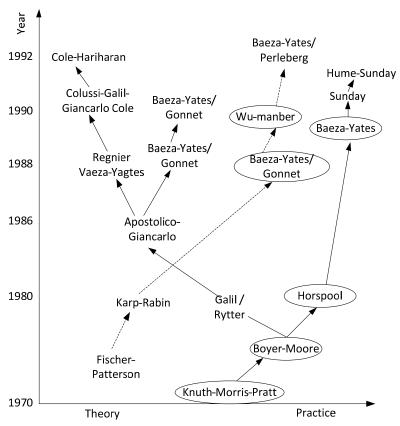

The single string matching algorithm is the kernel of the general string matching and includes regular expression matching and approximate string matching. Figure 13 shows some historical main string matching algorithms. In general, the hundreds of single string matching algorithms in the world can be classified into five categories: (1) Brute Force; (2) Hash; (3) Automata; (4) Sliding Window (Prefix & Suffix); (5) Bit-Parallelism.[29][31]

Figure 13: The development history of pattern matching algorithms. [30]

#### 2.3.2. Brute Force Algorithm

The Brute Force algorithm [31] is the most basic search algorithm. It checks the pattern at all positions in the text between 0 and n-m, and shifts the pattern by exactly one position to the right after each attempt. It has a fixed time complexity  $O(m \times n)$ .

#### 2.3.3. Hash Algorithm

Hashing provides a simple method to avoid a large number of character comparisons. Usually, a small change on the string will make a big difference to the hashing value. The Karp-Rabin algorithm [31][32], is one of the most famous search algorithms based on hashing. It calculates the hashing value of a pattern with length m and the text for every continued m characters. If two hashing values are same, it will compare every character of these two strings to confirm the match. It has a time complexity O(m x n).

#### 2.3.4. Automata Algorithm

An automaton [30][31][33] is a mathematical model for a Finite State Machine. An automaton can be represented by  $A = (Q, \Sigma, I, F, D)$ , which represents a finite state "Q" with an initial state "I" and a final state "F". Transitions between states can jump on the input of alphabet " $\Sigma$ " and empty input " $\epsilon$ ". Then the transition function " $\mathcal{D}$ " can be defined by each state  $q_k \in Q$  for each input  $\alpha \in (\Sigma \cup \epsilon)$ .

Generally, there are two types of automata: the Nondeterministic Finite Automaton (NFA) and the Deterministic Finite Automaton (DFA). If a state q can jump to multiple different states with only one input  $\alpha$ , or empty input  $\epsilon$  exists in the transition, then this automaton is NFA. The transition function  $\mathcal D$  of NFA is denoted by the set of triples  $\Delta$ . Otherwise, the automaton is DFA, and the transition function  $\mathcal D$  denoted by a partial function  $\delta$ :  $Q \times \Sigma \to Q$ . In the area of pattern matching, it is easier to obtain the NFA of a string. However, maybe there are multiple active states in an NFA and only one active state in a DFA. Therefore, DFA can usually have a faster search speed for pattern matching and all NFA can be converted into DFA. [29][33]

The Forward/Backward Dawg Matching Algorithm (FDM/BDM) [31] is a famous typical DFA based algorithm. It tries to compute the longest factor of the pattern ending at each position in the text. However, its complex process slows down its overall speed.

#### 2.3.5. Sliding Window Algorithm

The Sliding Window algorithm [29] uses a virtual window with a length m on the test to perform matching. There are two general ways to attempt the matching: (1) based on the prefix; (2) based on the suffix.

Knuth-Morris-Pratt (KMP) [31][34] and Boyer-Moore (BM) [29][31][35] are the most famous search algorithms. Many other algorithms have evolved from them. The primary difference is that KMP is a prefix based approach, and BM is a suffix based approach.

Figure 14: Shift in the Prefix Algorithm (Knuth-Morris-Pratt).

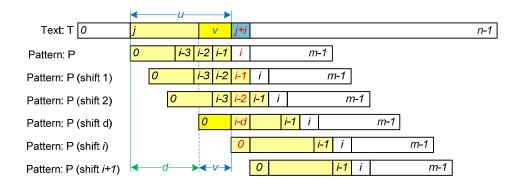

The Prefix algorithm follows a tight analysis of the Brute Force algorithm. It tries to find the length of the longest prefix of the pattern that is also a suffix of the text. Figure 14 shows it searching for a pattern p in the text T. When a window is positioned on the text T[j ... j+m-1], assume that the first mismatch occurs between T[j+1] and p[i]. Let T[j ... j+i-1] = p[0 ... i-1] = u, then the next characters  $T[j+i] \neq p[i]$ . When shifting, the Brute Force algorithm will only shift one character, but we can expect if d characters have been shifted, a prefix v = p[0 ... i-d-1] of the pattern may match some suffix of the portion u. For example, if only one character

has been shifted,  $T[j+i] \neq p[i-1]$  or T[j+i] = p[i-1] but  $T[j+i-1] \neq p[i-2]$ , it is impossible for the pattern p to match the text  $T[j+1 \dots j+i]$ . Therefore, if we can know it at the beginning, it is not necessary to waste time shifting only one character. Only if  $p[0 \dots i-d-1] = T[j+d \dots j+i-1]$ , is it possible to have  $p[0 \dots m-1] = T[j+d \dots j+d+m-1]$ . If no such border exists the length of the pattern characters can be shifted directly. Different prefix algorithms use different ways to find the best d. The best algorithm can use the easiest algorithm to find the biggest d. For example, KMP uses p[i] to calculate d. The pre-process session has time complexity O(m), and the worst case of the search phase has time complexity O(m+n). In addition, different algorithms may also have a different matching order of  $T[j \dots j+i-1]$  and  $p[0 \dots i-1]$ . For example, a general algorithm, such as KMP, will match in the order from left to right. The Apostolico-Crochemore algorithm matches the second character T[j+1] with T[i] first, and the first character T[i] with T[i] last. T[i]

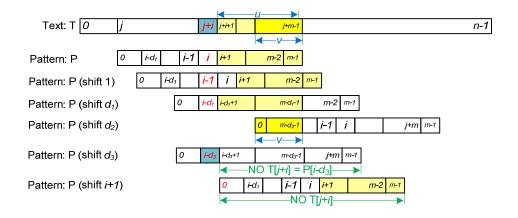

The suffix search algorithm scans the characters of the pattern from right to left and begins with the rightmost character. Similarly to the prefix algorithm, it ignores some unnecessary matches, and tries to find the biggest shifts. BM is a typical suffix based algorithm. Because it is difficult to calculate the biggest safety shift directly, BM defines three ways to shift the pattern (Figure 15), and any of them can shift the pattern without missing any occurrence. Firstly, if  $T[j+i+1 \dots j+m-1] = p[i+1 \dots m-1] = u$  and  $T[j+1] \neq p[i]$ , it tries to find a shift d1, which can have another u in  $p[0 \dots m-d1-1]$  from p[0]. Secondly, when the suffix u does not appear in any other position of pattern p, but a suffix v of u exists which is the same as the prefix of the pattern, BM will look for a shift d2, which has the longest prefix v of pattern p that is also a suffix of u. Thirdly, with a shift d3, if p[i-d3] = T[j+i] and if there is not any character equal to T[j+i] in the range  $p[i-d3+1 \dots m-1]$ , we can directly perform this shift safely. If there is not T[j+1] in the pattern, we can directly shift the pattern by i+1. All three

shifts are calculated in the pre- pre-process session and the results are stored in different tables, and then the longest shift will be used in the search process. [29][31][35]

Figure 15: Shift in the Suffix Algorithm (Boyer-Moore).

Although the first two methods may have a longer shift sometimes, they require much more time on the calculation in the pre- pre-process session. Some algorithms are designed to simplify or modify the BM algorithm, such as the Turbo-BM, the Apostolico-Giancarlo algorithm, the BM-Horspool, the Quick Search algorithm, the Tuned BM, Zhu-Takaoka algorithm, the Berry-Ravindran algorithm, the Smith algorithm and the Raita algorithm. BM-Horspool (Horspool) [29][31][36] is the most famous one. It only reserves the third shift method of BM owing to its having a good balancing on the shift length and its complexity of calculation. Therefore, it is faster in most cases. Until now, Horspool is still acknowledged as the fastest single pattern matching algorithm in general cases in the world. Currently, Snort uses BM as the default matching algorithm, and supports Horspool through plug-in.

In addition, the Backward Oracle Matching algorithm (BOM) [29][31][37] imports the automaton technique into the suffix window shift algorithm. It creates a simple DFA with m+1 states and m to 2m-1 transition in the pre- pre-process session. Figure 16 shows an example of the DFA build by BOM. The search engine is similar to BM. The search will be carried out backwards in each window following the DFA. When a mismatch (a non-existent

state in the DFA) has been detected, the window will be shifted to the next character of the mismatch, which is shown in Figure 17. Because BOM has a simpler DFA, the search speed is faster than FDM/BDM. It has a competitive speed for a large pattern length. However, the speed is still slower than the Horspool and Bit Parallel algorithms for a small size of pattern.

Figure 16: A DFA built by BOM for Pattern "announce". [10]

Figure 17: Shift of the search window after the failure of the search by BOM. [11]

# 2.3.6. Bit-Parallelism Algorithm

All the above matching algorithms have evolved from the Brute Force algorithm, which stores two characters (one from the pattern, and one from the test) into two variables, e.g. unsigned char (8 bits), unsigned int (16 bits) and unsigned long (32 bits) in ANSI C. Actually, the variables are stored as binary in the memory. For example, an English alphabet which is encoding in ASCII only uses 7 bits. An "unsigned char" is defined as 8 bits in the memory. Each unsigned char can be used to store an English character. Then the computer will compare the two variables. If the processor is 32-bit, which can process data and memory addresses with the width of registers at 32 bits, each unsigned char only uses the last 8 bits in the processor bus, the remaining 24 bits of the bus are not going to be used. Then the two 8

bits unsigned chars can be processed simultaneously, and compared all in a single operation. (Figure 18) However, it wastes 75% of the processor bus.

Figure 18: Comparison of two ASCII characters in the memory.

The Bit-Parallelism algorithm [29-[31][38] is different. Its purpose is not to look for the biggest window shift, but it tries to use the simplest and the fastest way to process all comparisons by using a bitwise technique. It uses a bit to describe if a character with any encoding format is in the position of a pattern. Therefore, it requires a size of alphabet  $\sigma \times m$  (pattern length) table to describe a single pattern.

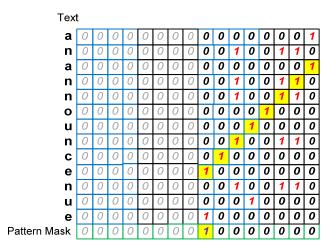

For example, the processing of searching pattern "announce" in the text "anannouncenue" in a 16-bit computer is shown in Figure 19. Firstly, the pattern will be decoded into an "S" table in the pre-process session; all the matched characters are marked by 1. By calling over each character in the text from left to right using the value in S table, a continual match ("1" with the yellow background) from the 3rd to 12th character of text can be found in Table R. Actually, it is not necessary to keep the whole Table R. By keeping one variable, the next result can be calculated by Ri+1=((Ri<<1) | 1) & Si+1 where i is the current position of the text and R0=1(word length). Then check if the result of the m (the length of pattern) bit is 1. Because the example uses one shift and one AND operation to do the matching, it is also called the Shift-AND algorithm. Similarly, by identifying the matched characters by 0 and unmatched characters by 1, the equation can be changed to Ri+1=(Ri<<1) | Si+1 where R0=0, which is called the Shift-OR Algorithm. Shift-OR may be slightly faster in some processors owing to the computation of Ri+1 having been reduced to two operations, shift and OR (without OR and 1 at the end).

Call over each character in the text from left to right using the value in S table:

Shift above table, compensate with 1 at the end, without AND:

Figure 19: Searching pattern "announce" in the text "anannouncenue" in a 16-bit computer by the Bit-Parallelism (Shift-AND) Algorithm. Characters are encoded in ASCII

However, there is a limitation on the Bit-Parallelism algorithm owing to the length of the computer word. The total pattern m cannot be longer than the computer word. For example,

the maximum pattern length that can be processed is 32 characters by a 32-bit computer, and 64 characters by a 64-bit computer. Although a longer variable can be simulated by multiple computer words, it cannot be processed simultaneously. Therefore, the simulation will slow down the whole matching process. Hence, the Bit-Parallelism algorithm is good at a short pattern with a small alphabet. With a large alphabet, the matching possibility will be low. A Sliding Window Algorithm, such as Horspool, which requires less comparing, and has a bigger window shift, will be faster.

If it is assumed that the pattern length is no longer than the computer word size, the time complexity is  $O(m+\sigma)$  for the pre-processing, and O(n) for the searching.

In addition, the Bit-Parallelism algorithm can also be processed backwards. Backward Nondeterministic Dawg Matching (BNDM) [29] uses a similar search approach with BDM, but the factor is searched by bit-parallelism. Its pre- pre-process session is the same as with the normal Bit-Parallelism algorithm (Shift-AND). However, it makes a window on the text during the search. The length of the window is the pattern length m. The first window is from the left of the text and it calls over the characters from right to left in each window. If it loses all matches in a single try (R = 0), the window will shift by m. If it finds the first character of the pattern (R = 10 (m-1)), the window will shift to the first character of the pattern. Therefore, it can have some jumping during the search. However, the expense is in the more computing operations in the search process (not just two operations: shift and OR). Hence, it is good at a slightly bigger m compared with a normal Bit-Parallelism algorithm.

# 2.3.7. Multiple String Matching Algorithms

The multiple string matching is an extension of the single string matching algorithm. It is designed to search multiple patterns simultaneously. Most techniques of multiple string matching are based on single string matching algorithms. There are some famous algorithms:

the Aho-Corasick algorithm, the Commentz-Walter algorithm, the Set Horspool algorithm, the Wu-Manber algorithm, the Set Backward Dawg Matching (SBDM) algorithm, the Set Backward Oracle Matching (SBOM) algorithm, the Multiple Bit Parallelism (MBP) algorithm and the multiple BNDM (MBNDM) algorithm. [29]

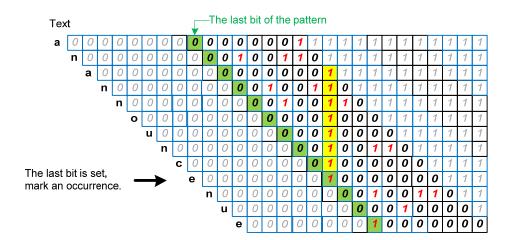

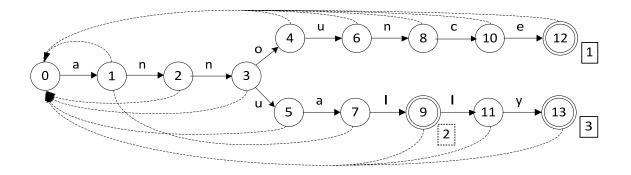

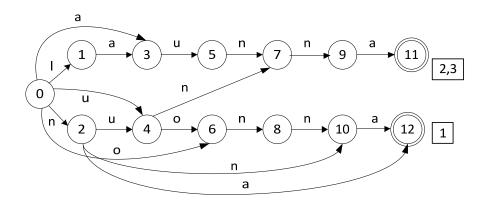

The Aho-Corasick algorithm [29][39] is an extension of the KMP algorithm. It uses an Aho-Corasick (AC) automaton as the pattern which is built by the multiple patterns. An example of an AC automaton is shown in Figure 20.

Figure 20: An AC automaton of pattern P = {announce, annual, annually}. Double-circled states are terminal. [11]

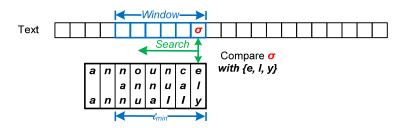

The Commentz-Walter algorithm [29] is an extension of the BM algorithm, and it is the first sub linear multistring matching algorithm. To avoid skipping any occurrence, the size of a window is set to the minimum length of all sub patterns  $l_{min}$ . An example is shown in Figure 21. The shift size of the window will be calculated in the same way as with the BM algorithm.

Figure 21: The Sub linear Multi-string Matching algorithm with example patterns  $P = \{announce, annual, annually\}.$

The Set Horspool algorithm [29] is similar to the BM-Horspool and is a simplification of the Commentz-Walter algorithm. It uses the simplified shift calculation to get the window shift which is exactly the same as the Horspool. In practice, although it has a faster speed than the Commentz-Walter algorithm, its high probability of finding each character of the alphabet in one of the patterns decreases the window shift. Then, the Wu-Manber algorithm is designed to decrease the probability based on the Set Horspool algorithm.

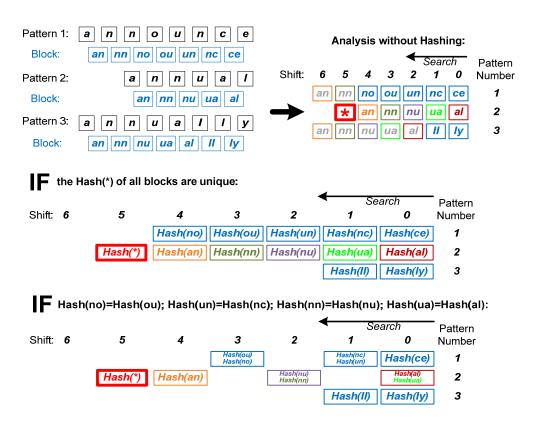

Figure 22: The pattern analysis of the Wu-Manber algorithm with example patterns  $P = \{announce, annual, annual\}$  and the length of the block = 2.

In the usual algorithm, the smallest unit is the character. Wu-Manber [29][40] groups the characters and the comparing units (not the shift unit) become a block of a few characters. Then the matching probability will decrease to  $\sigma(-B)$ , where B is the length (the number of characters) of the block. And the difficulty will increase to  $\sigma B$  different blocks, which means requiring much more memory when B is big. To solve the memory problem, Wu-Manber applies a hashing function on all possible blocks and different blocks are identified by their

hashing value. The search engine will only compare the hashing value of block and window. The shift step is still calculated in the same way as with Set Horspool, which will try to find the rightmost occurrence. The maximum shift size is  $l_{min}$ –B+1. Because the hashing value of different blocks may be equal, when an occurrence is found (shift size is 0), the block of original characters should be checked again. Then a new shift with only one step will apply on the window on the text. An example is shown in Figure 22. Wu-Manber has a fast search speed for a big alphabet (e.g. bigger than 10) with not very many multiple patterns (e.g. 100).

Figure 23: The automaton of SBOM for example patterns  $P = \{announce, annual, annually\}$ . The factor oracle of the reverse set Plmin =  $\{announce, annual\}$ . [11]