DISSERTATION

## COMPILING DATAFLOW GRAPHS INTO HARDWARE

Submitted by Robert E. Rinker Department of Computer Science

In partial fulfillment of the requirements for the Degree of Doctor of Philosophy Colorado State University Fort Collins, Colorado Fall 2005

### COLORADO STATE UNIVERSITY

October, 2005

WE HEREBY RECOMMEND THAT THE DISSERTATION PREPARED UNDER OUR SUPERVISION BY ROBERT E. RINKER ENTITLED COMPILING DATAFLOW GRAPHS INTO HARDWARE BE ACCEPTED AS FULFILLING IN PART REQUIRE-MENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY.

Committee on Graduate Work

Adviser

Department Head

#### ABSTRACT OF DISSERTATION

#### COMPILING DATAFLOW GRAPHS INTO HARDWARE

Conventional computers are programmed by supplying a sequence of instructions that perform the desired task. A reconfigurable processor is "programmed" by specifying the interconnections between hardware components, thereby creating a "hardwired" system to do the particular task. For some applications such as image processing, reconfigurable processors can produce dramatic execution speedups. However, programming a reconfigurable processor is essentially a hardware design discipline, making programming difficult for application programmers who are only familiar with software design techniques.

To bridge this gap, a programming language, called SA-C (*Single Assignment C*, pronounced "sassy"), has been designed for programming reconfigurable processors. The process involves two main steps - first, the SA-C compiler analyzes the input source code and produces a hardware-independent intermediate representation of the program, called a *dataflow graph* (DFG). Secondly, this DFG is combined with hardware-specific information to create the final configuration.

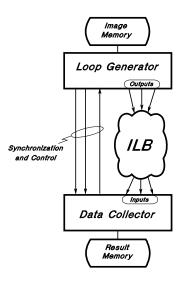

This dissertation describes the design and implementation of a system that performs the DFG to hardware translation. The DFG is broken up into three sections: the data generators, the inner loop body, and the data collectors. The second of these, the inner loop body, is used to create a computational structure that is unique for each program. The other two sections are implemented by using prebuilt modules, parameterized for the particular problem. Finally, a "glue module" is created to connect the various pieces into a complete interconnection specification.

The dissertation also explores optimizations that can be applied while processing the

DFG, to improve performance. A technique for pipelining the inner loop body is described that uses an estimation tool for the propagation delay of the nodes within the dataflow graph. A scheme is also described that identifies subgraphs with the dataflow graph that can be replaced with lookup tables. The lookup tables provide a faster implementation than random logic in some instances.

> Robert E. Rinker Department of Computer Science Colorado State University Fort Collins, Colorado 80523 Fall 2005

## ACKNOWLEDGMENTS

I would like to first thank my advisor, Dr. Walid Najjar, and the members of my committee, Dr. Wim Böhm, Dr. Dale Grit, and Dr. Anura Jayasumana, for putting up with me over all these years. You have all provided me with invaluable counsel throughout my term as a PhD student.

Next, thanks to all my fellow students who worked on the Cameron project, for providing such an amazing work environment. To Jeff Hammes - I will always remember and relish our cubicle discussions. To Margaret Carter, who implemented an amazing DFG to VHDL translator. To Amit Patel, who did some incredible work on the VHDL reduction operator library. To Monica Chawathe, who was always there, ready to fix bugs in the translator code. To Charlie Ross, whose incredible coding expertise I will always admire. To Harish Kantemneni and Dave McClure, who put together and maintained the DFG viewer. And to Danny Kulkarni, who worked on the DFG space estimator. It was all of you who made this project so enjoyable!

Finally, I would like to thank my colleagues at the University of Idaho for their support while I was writing my dissertation, and especially Dr. John Munson and Dr. Bob Hiromoto, for struggling through some of the early drafts, and providing invaluable suggestions on how to improve them.

# DEDICATION

I dedicate this dissertation to my family, including my parents, Ed and Phyllis Rinker, and my children, Jeff, Gina, and Jodi, for providing the moral support that I needed to follow through with this project. You will never know how much that support means to me. Thanks!

# TABLE OF CONTENTS

| 1 | Intr | roducti | ion                                                               | 1  |

|---|------|---------|-------------------------------------------------------------------|----|

|   | 1.1  | The S   | A-C Compiler                                                      | 2  |

|   | 1.2  | Purpos  | se of this Dissertation                                           | 3  |

| 2 | Bac  | kgrour  | nd                                                                | 6  |

|   | 2.1  | FPGA    | Technology and Evolution                                          | 7  |

|   | 2.2  | Survey  | of Reconfigurable Computing Hardware which Use Off-the-Shelf FPGA |    |

|   |      | Chips   |                                                                   | 11 |

|   |      | 2.2.1   | The Splash-2 Reconfigurable Computing Board                       | 11 |

|   |      | 2.2.2   | The Wildforce Reconfigurable Computing Board                      | 13 |

|   |      | 2.2.3   | The SLAAC-1 Reconfigurable Computing Board                        | 15 |

|   |      | 2.2.4   | The Annapolis Wildstar Reconfigurable Computing Family            | 16 |

|   | 2.3  | Custor  | n-Designed Reconfigurable Computing Boards                        | 18 |

|   |      | 2.3.1   | Morphosys                                                         | 19 |

|   |      | 2.3.2   | The RAW Project                                                   | 20 |

|   |      | 2.3.3   | PipeRench                                                         | 22 |

|   |      | 2.3.4   | Field Programmable Processor Array                                | 24 |

|   | 2.4  | Softwa  | re Development for Reconfigurable Computing                       | 26 |

|   |      | 2.4.1   | The RAW Compiler Project                                          | 29 |

|   |      | 2.4.2 PipeRench and DIL                                                   | 30 |

|---|------|---------------------------------------------------------------------------|----|

|   |      | 2.4.3 $$ Reconfigurable Computing and High Level Application Environments | 31 |

|   | 2.5  | The Cameron Project and SA-C                                              | 32 |

|   | 2.6  | Summary                                                                   | 34 |

| 3 | A F  | Preliminary Project - Manual Implementation of an RCS Design              | 35 |

|   | 3.1  | Background - the Prewitt algorithm                                        | 36 |

|   | 3.2  | The Wildforce-XL Board Architecture                                       | 37 |

|   | 3.3  | The Inner Loop Body of the Prewitt Algorithm                              | 38 |

|   | 3.4  | Distribution of Image Data from Host to the PEs                           | 40 |

|   | 3.5  | Conclusions Drawn from the Manual Prewitt Designs                         | 47 |

| 4 | An   | Automated Translation from Compiler-Generated Dataflow Graphs             |    |

|   | to V | /HDL                                                                      | 49 |

|   | 4.1  | The SA-C Compiler and Optimizations                                       | 50 |

|   | 4.2  | An Abstract Architecture for Reconfigurable Computing                     | 53 |

|   | 4.3  | Implementation on the AMS Wildforce Board                                 | 54 |

|   | 4.4  | Translating DFGs to VHDL                                                  | 55 |

|   | 4.5  | Classification of DFG Nodes                                               | 55 |

|   | 4.6  | Translation of the ILB                                                    | 57 |

|   | 4.7  | Implementation of the Other Components in a Design                        | 58 |

|   |      | 4.7.1 The ConstGrabber Component                                          | 58 |

|   |      | 4.7.2 The Data Generator Components on CPE0                               | 60 |

|   |      | 4.7.3 The Data Generator Components on PEx                                | 62 |

|   |      | 4.7.4 The Collector Component                                             | 64 |

|   |      | 4.7.5 The MemArb Component                                                | 65 |

|   | 4.8  | An Automated Prewitt Implementation on the AMS Wildforce Board            | 65 |

|   | 4.9  | Performance of the Level 1 Benchmark Routines                             | 68 |

| 5 | Pip  | elining the Inner Loop Body                                               | 75 |

|   | 5.1  | Introduction                                                              | 75 |

|   | 5.2 | Estimating the Propagation Delays of the Dataflow Graph Nodes | 78  |

|---|-----|---------------------------------------------------------------|-----|

|   | 5.3 | Pipelining the Inner Loop Body                                | 84  |

|   | 5.4 | Pipelining Performance                                        | 87  |

|   | 5.5 | Improvements to the Estimation Model                          | 92  |

| 6 | Usi | ng Lookup Tables to Implement Dataflow Graph Segments         | 96  |

|   | 6.1 | Introduction                                                  | 96  |

|   | 6.2 | Time and Space Requirements of Synthesized Lookup Tables      | .00 |

|   | 6.3 | Algorithm 1 - A Global Mincut through the DFG                 | .02 |

|   | 6.4 | Mincut Algorithm Results                                      | .07 |

|   | 6.5 | Algorithm 2 - Local Subgraphs and the "Flood" Algorithm       | .09 |

|   | 6.6 | Flood Algorithm Results                                       | .13 |

| 7 | Cor | nclusion and Future Work 1                                    | 17  |

|   | RE  | FERENCES 1                                                    | 21  |

# LIST OF TABLES

| 3.1 | Results in terms of space (CLB usage) and maximum clock rate for pre-      |    |

|-----|----------------------------------------------------------------------------|----|

|     | Place and Route (as reported by the Synplify VHDL compiler), and post-     |    |

|     | Place and Route (reported by the Xilinx M1 tools) for several of the FIFO- |    |

|     | based designs described in this report.                                    | 43 |

| 3.2 | Results in terms of space (CLB usage) and maximum clock rate for pre-      |    |

|     | Place and Route (as reported by the Synplify VHDL compiler), and post-     |    |

|     | Place and Route (reported by the Xilinx M1 tools) for several of the       |    |

|     | memory-based designs described in this report.                             | 45 |

| 3.3 | Performance results for the memory designs, for several image sizes        | 46 |

|     |                                                                            |    |

| 4.1 | Statistics for the Wildforce implementation of the Prewitt algorithm using |    |

|     | the SA-C compiler/translator                                               | 67 |

| 4.2 | Space required by several of the Level 1 benchmarks. The table shows       |    |

|     | the number of F-Maps, H-Maps, and register (Flip/Flop) bits required for   |    |

|     | CPE0 and PEx for each routine, along with the percentage of CLBs within    |    |

|     | each PE that is used. Also, the operating frequency for each program is    |    |

|     | shown.                                                                     | 70 |

| 4.3 | Continuation of Table 4.2                                                  | 71 |

| 4.4 | Execution times of several of the Level 1 benchmarks. The table shows sep-       |     |

|-----|----------------------------------------------------------------------------------|-----|

|     | arate times for the array write to the Wildforce local memory, the computa-      |     |

|     | tion, and the reading of result data back to the host, for three different-sized |     |

|     | images. For comparison purposes, the execution time of the same program          |     |

|     | on the host computer is also shown.                                              | 72  |

| 4.5 | Continuation of Table 4.4                                                        | 73  |

| 4.6 | Continuation of Table 4.4                                                        | 74  |

| 5.1 | Nodes that have simple, single-valued model parameters                           | 85  |

| 5.2 | Nodes that represent multiple-cycle operations                                   | 86  |

| 5.3 | Nodes that are modeled as a family of curves                                     | 86  |

| 5.4 | Comparison of actual vs. estimated propagation delays for a representative       |     |

|     | set of SA-C benchmark programs                                                   | 88  |

| 5.5 | Original size (in terms of CLB FMAPs and Register bits) and clock speed          |     |

|     | vs. pipelined size and speed for the SA-C benchmark programs $\ . \ . \ .$ .     | 90  |

| 6.1 | Results of the subgraph algorithm                                                | 115 |

# LIST OF FIGURES

| 1.1  | Overview of the SA-C Compilation process                                                  | 2  |

|------|-------------------------------------------------------------------------------------------|----|

| 2.1  | Architecture of an FPGA. In the picture, $\tt LC$ stands for logic cell, $\tt I/O$ stands |    |

|      | for an I/O block, and the small black squares represent programmable con-                 |    |

|      | nection points.                                                                           | 7  |

| 2.2  | Two types of logic cells used in FPGAs. (a) Gate-based logic cell. (b)                    |    |

|      | Lookup table-based logic cell                                                             | 8  |

| 2.3  | Simplified Architecture of the Splash-2 Configurable logic board                          | 11 |

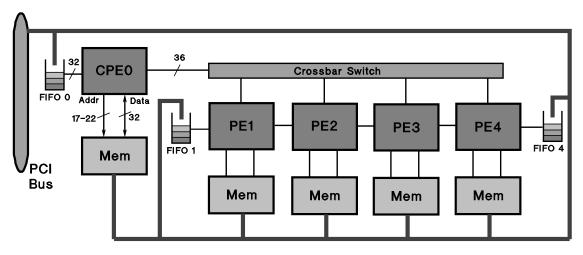

| 2.4  | Simplified Architecture of the Wildforce Configurable logic board                         | 13 |

| 2.5  | Architecture of the SLAAC Configurable Logic Board                                        | 15 |

| 2.6  | Block diagram of the Annapolis Wildstar Reconfigurable Computing board                    | 17 |

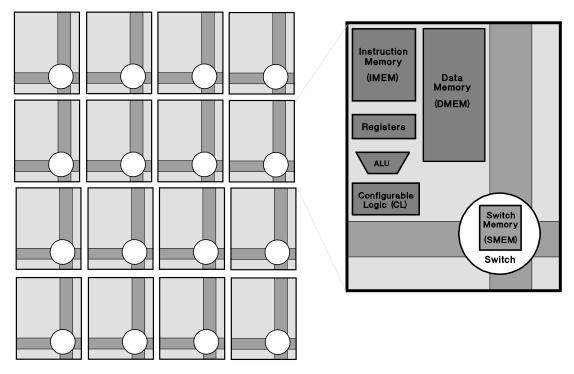

| 2.7  | Architecture of the Morphosys Architecture. One of the Reconfigurable                     |    |

|      | Cells (RC) within the RC Array is shown                                                   | 19 |

| 2.8  | Architecture of the RAW Architecture, showing a portion of the tile array,                |    |

|      | and the details of one of the tiles                                                       | 21 |

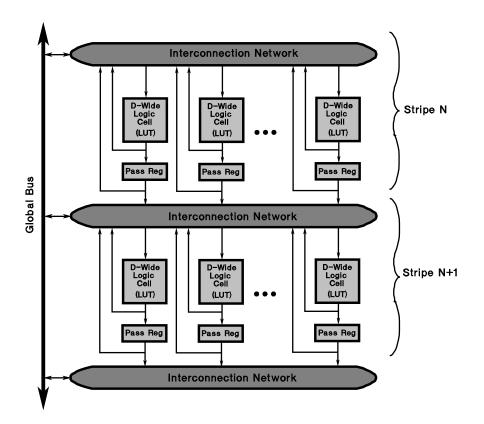

| 2.9  | Architecture of the PipeRench Architecture, showing two stripes                           | 22 |

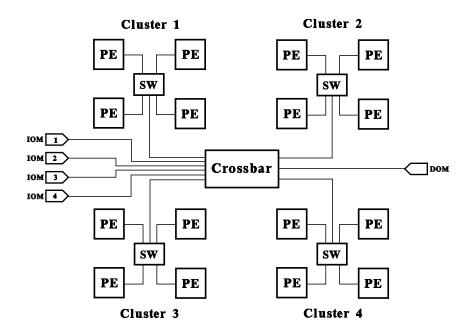

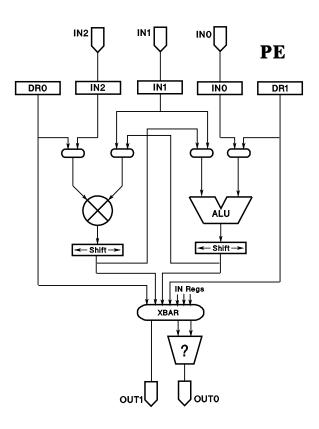

| 2.10 | FPPA architecture overview                                                                | 25 |

| 2.11 | Organization of each FPPA Processing Element                                              | 26 |

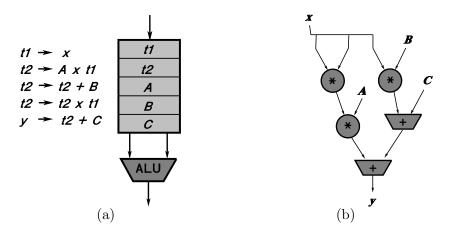

| 2.12 | A comparison of (a) temporal vs. (b) spatial computation for the equation                 |    |

|      | $y = Ax^2 + Bx + C  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $       | 27 |

| 3.1 | Constant convolution masks for the Prewitt algorithm. (a) the X gradient             |

|-----|--------------------------------------------------------------------------------------|

|     | mask, and (b) the Y gradient mask                                                    |

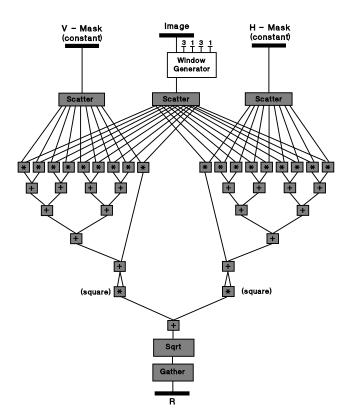

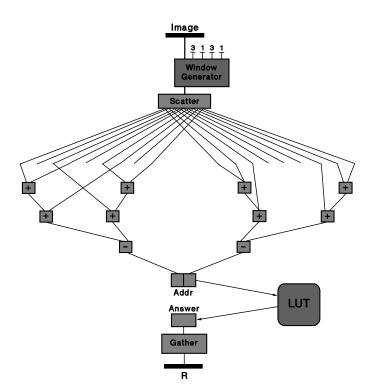

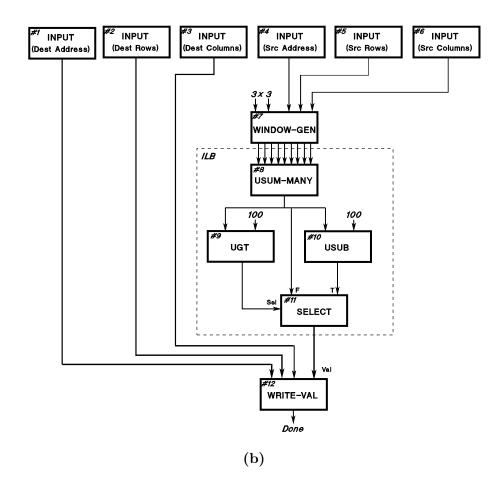

| 3.2 | Dataflow graph of the unoptimized Prewitt algorithm inner loop body $\ldots$ 38      |

| 3.3 | Dataflow graph of the optimized Prewitt algorithm inner loop body $\ldots$ 40        |

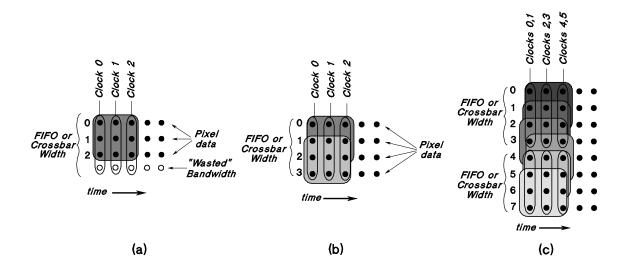

| 3.4 | Three data transfer schemes: (a) Single instance of the convolution calcu-           |

|     | lation, (b) two instances, and (c) six instances                                     |

| 3.5 | A pictorial representation of the entire Prewitt implementation, using two           |

|     | inner loop bodies per processing element                                             |

| 4.1 | Overview of the SA-C Compilation process                                             |

| 4.2 | (a) A simple SA-C program, and (b) the resulting dataflow graph 51                   |

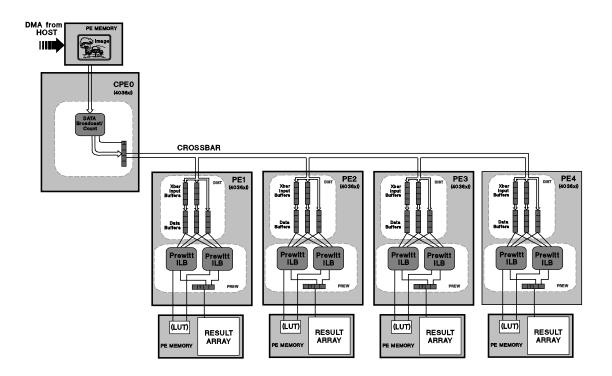

| 4.3 | Architecture of the Wildforce-XL Reconfigurable Computing Board, show-               |

|     | ing that part of the board being utilized by the DFG-to-VHDL translator $\ . \ 54$   |

| 4.4 | Structure of the VHDL code generated by the DFG-to-VHDL translator $55$              |

| 4.5 | The generated VHDL for the ILB of Figure 4.2(b) (some declarations and               |

|     | type casting have been omitted for clarity)                                          |

| 4.6 | Location of components in the 2 PE model                                             |

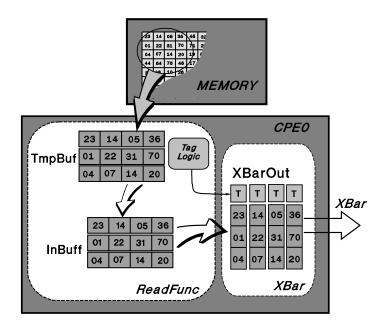

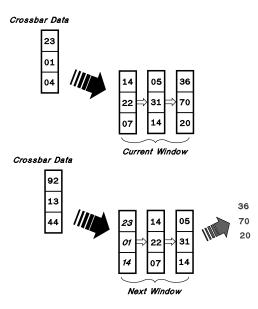

| 4.7 | Diagram of the read window generator function                                        |

| 4.8 | Pictorial representation of a $3\times 3$ sliding window generator for the current,  |

|     | and then next windows                                                                |

| 4.9 | The Prewitt edge-detection algorithm, written in SA-C                                |

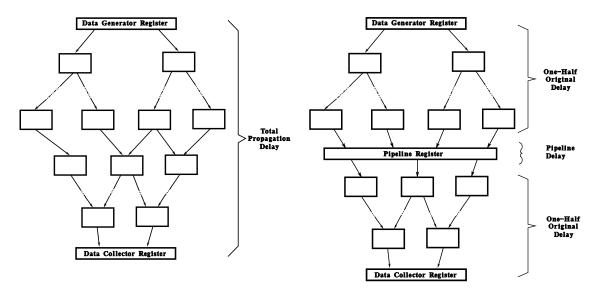

| 5.1 | A non-pipelined vs a pipelined DFG                                                   |

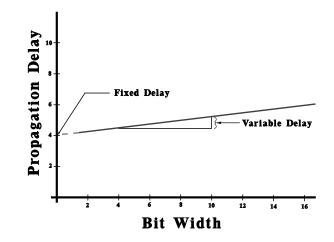

| 5.2 | Linear graph of bit-width vs propagation delay                                       |

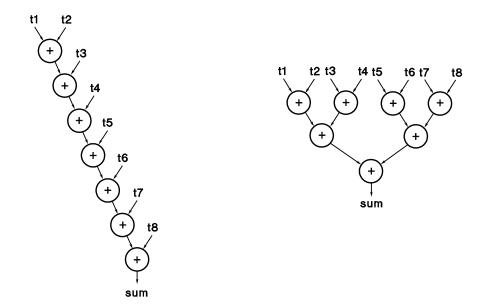

| 5.3 | Linear vs binary tree implementation of the USUM-MANY node $\ldots \ldots \ldots 83$ |

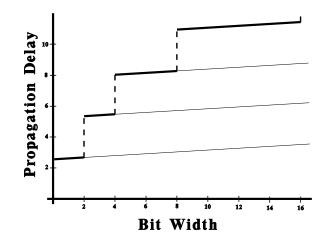

| 5.4 | A "family of curves" graph, characteristic of a binary tree implementation           |

|     | of the MANY nodes                                                                    |

| 5.5 | SA-C compilation process, modified to include pipelining of the DFG $89$             |

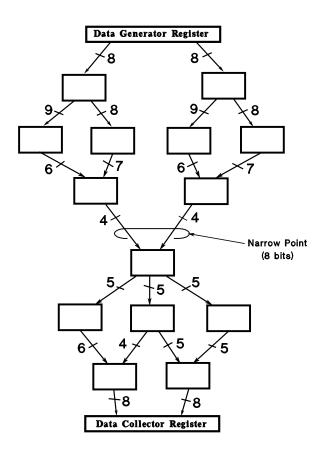

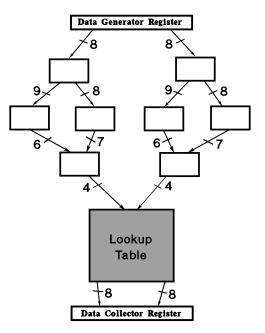

| 6.1 | Dataflow graph showing a narrow point in the graph                                   |

| 6.2 | Dataflow graph with the lower portion replaced with a lookup table $\ldots$ 98       |

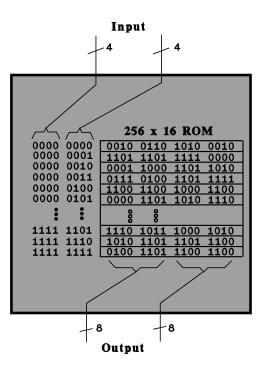

| 6.3 | A lookup table node                                                                       |

|-----|-------------------------------------------------------------------------------------------|

| 6.4 | An optimized implementation of a lookup table with repeating zeroes $\ldots$ 101          |

| 6.5 | A graph partitioned into two parts, with a mincut between them $\ldots \ldots \ldots 103$ |

| 6.6 | The Ford-Fulkerson mincut algorithm                                                       |

| 6.7 | a) A mincut found within a DFG by the original mincut algorithm, and b)                   |

|     | The modified version that eliminates control lines from the mincut $\ldots \ldots 109$    |

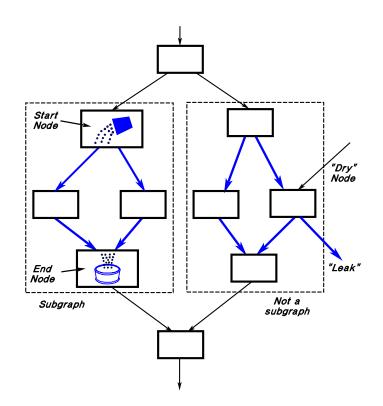

| 6.8 | Pictorial view of two subgraph candidates. The one on the left is a sub-                  |

|     | graph; the one on the right is not                                                        |

# Chapter 1 Introduction

A conventional processor operates by executing a sequence of instructions (a "program") on a fixed configuration of hardware - the "datapath." Each instruction generates a set of signals that controls the function of this fixed datapath; since the datapath is fixed, each instruction must specify a similar sequence of steps, usually in synchronization with a clock that determines a common execution speed for each instruction. By contrast, a Reconfigurable Computer System (RCS) consists of a set of hardware resources that can be interconnected to solve a specific calculation. In an RCS, the "program" consists of this interconnection specification. The advantage of this approach is that the resulting configuration can be optimized for the particular problem - the speed is determined by the propagation delay of the resulting circuit, rather than a fixed clock. As a result RCS's promise significant performance gains over conventional processors, especially for highly parallel applications like image processing.

However, current design environments for RCS's require a considerably different skill set than the typical application programmer possesses. Instead of a programming language such as C, or even assembly language, RCS's usually require an intimate knowledge of the hardware characteristics, including specific timing information. In a coprocessor-based system, both software knowledge for the host–based part of the application and hardware knowledge for the reconfigurable computing system. The lack of this dual knowledge generally requires that the design be partitioned quite early in the design process into software and hardware parts, and the two parts handed off to two different skill groups. This early partitioning requires that a significant amount of effort be placed into the interface between the two, even before all the tradeoffs are known.

The Cameron project Draper, Böhm, Beveridge 1998. (Najjar, and www.cs.colostate.edu/cameron) is a project whose goal is to integrate these two parts into a single design system, and to allow the design to be carried out entirely by the application programmer, without requiring intimate knowledge of hardware, timing or interface details. The project involves the design of a language which is particularly suited for translation into hardware, called SA-C (Single Assignment C, pronounced "sassy"). This dissertation describes a portion of the work done in the design and implementation of this language.

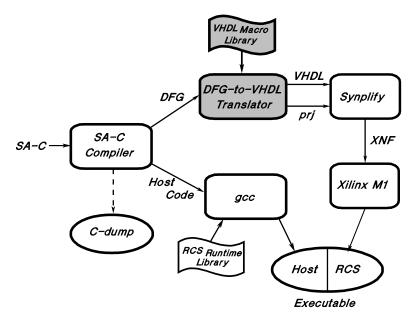

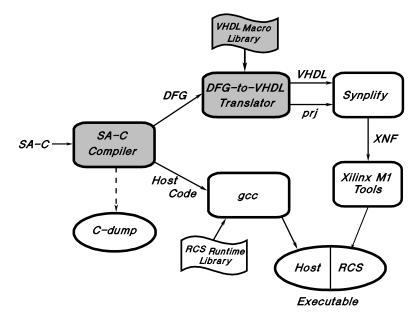

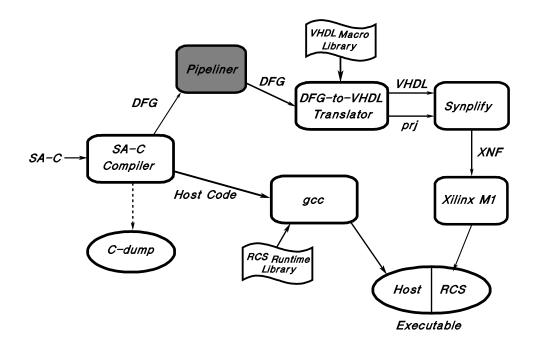

Figure 1.1: Overview of the SA-C Compilation process

## 1.1 The SA-C Compiler

An overview of SA-C the compilation system is shown in figure 1.1. The compiler accepts SA-C source programs and compiles them, producing two main outputs. The first is the host code - a program that runs on the host workstation; its main purpose is to initialize and control the operation of the attached RCS. The second output is an intermediate form called a Dataflow Graph (DFG). The DFG is a graphical representation of that part of the SA-C program that executes on the RCS. It shows the relationship between the processing

elements required for the calculation in a hardware independent form, and without any timing information.

The SA-C compiler performs numerous aggressive optimizations, some of which are typical compiler optimizations and some which are unique to its role as a compiler designed to target RCS systems, before it creates the DFG. Some more information about the compiler is provided later; a more detailed description of the compiler and its implementation is provided in Hammes 2000.

To produce a complete RCS program, the DFG is further processed by a DFG-to-VHDL translator. VHDL (VHSIC Hardware Description Language, where VHSIC stands for Very High Speed Integrated Circuit) is a standard hardware specification language that is used as the starting point by chip designers to describe their hardware designs. Its use requires a thorough understanding of the hardware that it is describing - application programmers typically do not possess these skills. The DFG-to-VHDL translator incorporates these details into the VHDL, so the programmer can create an application without having to be concerned with them.

The resulting VHDL code is synthesized and place-and-routed, using commercial software tools, to create the binary executable for the RCS. A final RCS program, therefore, consists of the host executable and the binary code that programs the RCS.

## 1.2 **Purpose of this Dissertation**

While the SA-C compiler is aggressive in its optimizations, it works with no specific knowledge of the hardware it is targeting. The DFG it produces is intentionally designed to be hardware independent; it is analogous to the "front end" (i.e., the lexical scanner and semantic analyzer) of a traditional compilation system. The DFG serves as the intermediary between this front end and the "back end," or code generator. This dissertation focuses on the back end. In particular, it focuses on the implementation and optimizations of the DFG-to-VHDL translator; this portion of the process is highlighted in figure 1.1. Again, comparing the process with a traditional compiler, where the back end produces assembly language that can be converted to an executable using the system's assembler and linker/loader, here the "assembly language" is VHDL, which is converted to an executable using commercial synthesis tools.

The first requirement for any compiler, and for the DFG-to-VHDL translator in particular for this project, is that it produce correct configurations from the DFG. Thus, this dissertation first concerns itself with that task.

In addition to the hardware independent optimizations performed by the SA-C compiler itself, there are other hardware dependent optimizations that can be applied at the DFG level to improve the performance of the final design. Pipelining allows a DFG that has a long propagation delay to be executed in segments, thereby reducing the delay through each segment and allowing an increase in the overall clock speed. Unlike a conventional processor, where the execution pipeline is fixed, in an RCS the pipeline can be created as part of the hardware configuration. It is the responsibility of the compiler to determine the best way to implement the pipeline.

Lookup tables have long been used to implement complicated calculations for high speed and with a minimum of hardware. In fact, lookup tables are used at the very lowest level in Field Programmable Gate Arrays (FPGAs), a technology that is frequently used in RCS's. It may be possible to improve the performance of a design by substituting lookup tables for DFG segments.

The remainder of this dissertation is organized as follows. Chapter 2 presents an overview of the field of reconfigurable computing, including some background, and a short survey of pertinent hardware and software research in the field. The third chapter describes a manual (not automated) implementation of a popular image processing algorithm - the Prewitt edge detecting algorithm - on the Annapolis Microsystems Wildforce board. This manual implementation helped in better understanding the behavior of the hardware, the software design tools, and allowed some experimentation with different design methods that would later become important when the process was automated. The manual implementation also provides a performance target for the automated system to achieve. Chapter 4 describes the design and implementation of the first automated compilation system, which translates the DFG representation into VHDL. Chapter 5 describes the work done to determine propagation delay estimates for each DFG node, and the results of using these estimates to pipeline the inner loop body. Chapter 6 describes research done in replacing appropriate sections of the inner loop body with a lookup table, in order to increase execution performance. Finally, chapter 7 concludes and suggests future work.

When incorporated into the rest of the SA-C compilation system, the work described in this dissertation allows an application programmer to transform a SA-C source program into an executable for an RCS in a single operation. Using the compiler requires no particular hardware knowledge of the underlying RCS. However, optimizations provided by the compiler front-end, as well as the optimizations described here, allow the programmer considerable freedom to experiment with the final design to improve performance. Using the SA-C compiler to produce a design, including optimizations, only requires a few days of work, compared with the several months that are required using manual methods.

# Chapter 2 Background

The idea of configurable hardware is not new. Estrin (Estrin 1963) describes a Variable Structure Computer System in 1963; an IBM 7090 computer (the "fixed structure" computer) was outfitted with an array of plug boards on which could be placed flip-flops and diode-based logic functions. He recognized the parallelism that existed in certain computations, and predicted a speedup of from 2.5 to 1000 in certain numerical operations when using the proper configurable system. His idea was that the configurable part of the system would come wired with a "standard state" which would compute things like square root and trigonometric functions; once the computational bottlenecks in a program were discovered, this standard state could be modified to more specifically compute the results for the problem being solved. The idea of using plug boards for the variable structure computer came from the "wire programs" that many computers of the time were still using to perform their tasks; the "stored program" concept was still relatively novel at the time. Many of the concepts proposed by Estrin's work were far ahead of its time; many are resurfacing now because technology exists that can support them.

Modern reconfigurable computing came about with the advent of the Field Programmable Gate Array (FPGA) in 1984 (Xilinx, Inc., San Jose, CA. 1998). This technology marries the electrically programmable capability of digital logic chips which implement simple AND-OR logic functions, such as PROMS (Programmable Read Only Memories, which contain a fixed AND array and a programmable OR array) and PALs (Programmable Array Logic, with a programmable AND array and fixed OR array), with the more complex gate array, which consist of hundreds or thousands of gates that can be

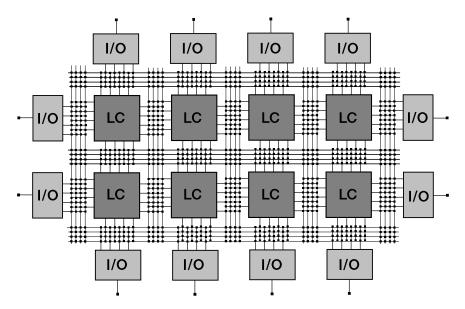

Figure 2.1: Architecture of an FPGA. In the picture, LC stands for logic cell, I/O stands for an I/O block, and the small black squares represent programmable connection points.

interconnected in any configuration by designing a custom interconnection mask.

FPGAs are the basis for many of the reconfigurable computing engines in use or being planned today; other designs incorporate FPGA-like features along with other integrated circuit technology, such as RISC or special-purpose processors. The rest of this chapter provides a survey of current reconfigurable research. In Section 2.1, the basic structure of the FPGA and its evolution are discussed. Section 2.2 reviews several hardware implementations which use commercially-available FPGAs. A couple of custom reconfigurable computing projects are described in Section 2.3. Finally, Section 2.4 discusses some software-oriented reconfigurable computing projects.

## 2.1 FPGA Technology and Evolution

Figure 2.1 shows the basic architecture of an FPGA. There are three types of circuit components inside the FPGA:

- Logic blocks, laid out in a two-dimensional array, that can be programmed to perform a certain logic function.

- I/O blocks, around the outside of the chip, that provide the interface between the

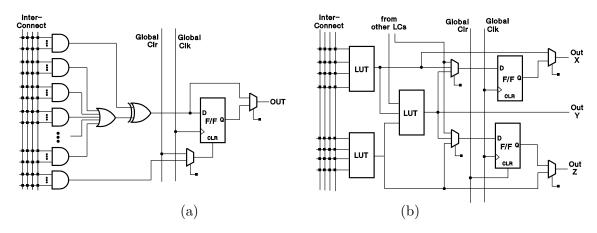

Figure 2.2: Two types of logic cells used in FPGAs. (a) Gate-based logic cell. (b) Lookup table-based logic cell.

interior and exterior of the chip.

• An interconnection grid, that can be used to connect the logic blocks to each other.

Each logic block consists of a small amount of digital logic; it is the organization of this logic block that distinguishes one manufacturer's chip, or even one family of chips from the same vendor, from another. The makeup of this logic block falls into one of two types. The first type consists of a simple fixed logic function (usually some variation of an AND-OR array) whose specific logic function – the exact interconnection within the function – can be programmed. This type is common in lower capacity chips – it has proven to be a significant technological challenge to use this type of logic block for more dense designs. The second type of logic block uses a lookup table, where a Boolean function of several variables can be specified. The logic block also contains one or more Flip Flops, so the value generated by the logic can be stored. This type has proven to be more scalable, due to the inherent circuit regularity of the lookup table. An example of the two main types of logic blocks are pictured in Figure 2.2.

I/O blocks can be programmed to be inputs, outputs or both. They provide the interface to external circuits, and can be configured to provide different electrical characteristics to the external circuit (pull-up resistors, rise time limits). Finally, they can provide latches between the internal and external connections. The interconnection network between logic and I/O blocks is accomplished by specifying the state (either connected or unconnected) of the points on the interconnection grid. Usually several types of interconnect between blocks are available – short lines for connecting local logic blocks, long lines for connecting logic blocks that are far apart on the chip, and global (buffered) lines that attempt to minimize propagation delays across the chip (usually used for clock signals). Manufacturers try to provide a versatile interconnect, since the routing of signals within a chip is a very time-consuming process, often taking hours even when automated.

The first FPGAs were programmed via *antifuses*, which are small fusible links that are initially placed everywhere a possible connection may be needed. The programming consists of an electrical procedure that literally "blows up" those connections that are not desired, leaving only the desired connections. These FPGAs can only be programmed once, since the fuses that have been disconnected cannot be restored. As such, this type of FPGA is not well suited for reconfigurable purposes. Due to the destructive nature of the programming, fuse-programmable FPGAs are usually limited in circuit density literally, space must be placed around the fuse to prevent unintended circuit destruction around the fuse.

The second method of programming is to use static RAM (SRAM) cells for the programming. In this situation, the SRAM cell is set to 0 or 1, depending upon whether the connection is to be made or not. The SRAM cell is more compatible with surrounding circuitry, so much higher densities can be achieved. The FPGA is programmed by supplying a string of bits – one for each SRAM cell – to the FPGA while it is in a special "program" mode. This string is supplied either by an external ROM chip, or in the case of a reconfigurable system, by a host computer. Since the programming process is nondestructive, the chip can be reprogrammed any number of times simply by changing the sequence of bits that is downloaded.

In the last few years, the evolution in FPGAs has followed much the same path as microprocessors, partly because the same technology benefits each type of chip. Within the same family of FPGA chips, the size of the logic block matrix has increased. New families of FPGAs have also been developed, offering an order of magnitude increase in both size and speed over previous family. For example, the Xilinx Virtex (Xilinx, Inc. 1999) is the successor to the Xilinx XC4000 (Xilinx, Inc., San Jose, CA. 1998) series. The high end of this new series contains 10 times the number of configurable logic blocks (CLBs, Xilinx's name for its logic blocks) and can operate at 4 times the speed (200 vs 50 MHz) as the XC40150, the high end of the previous generation. This increase in performance has a profound impact on the weighting that needs to be applied to the various criteria within a given design.

One unfortunate aspect of FPGAs, insofar as reconfigurable computing is concerned, is that their primary application is **not** reconfigurable computing. The primary market for FPGAs is to serve as "glue logic" in circuit designs as prototype "breadboards" to test circuit designs before they are committed to a more permanent form such as a custom chip or Application Specific Integrated Circuit (ASIC). They are not optimized for use in reconfigurable applications. This fact is particularly evident during reprogramming. The usual method of programming is to supply the programming bits, in bit serial fashion, to the FPGA. Only one pin is used for this programming, thereby providing more pins for I/O between the FPGA and external circuits. Also, for the most part the entire chip must be reconfigured – partial reconfigurability is not usually possible, even if only a portion of the chip is being used or needs to be reconfigured. The total reprogramming time is in the order of milliseconds; this can be a dominating amount of time when considering the entire amount of time required for complete execution of an application. One series of chips that was designed specifically for reconfigurable computing, the XC6200, allowed the configuration array to be accessed like normal random access memory, 16 bits at a time. However, it has not been successful in the marketplace. This circumstance is reflected in some of the compromises that appear in reconfigurable computing designs using these commercial chips.

Figure 2.3: Simplified Architecture of the Splash-2 Configurable logic board

# 2.2 Survey of Reconfigurable Computing Hardware which Use Off-the-Shelf FPGA Chips

In spite of the limitations, several reconfigurable computing boards have been designed using commercially available FPGA chips (Sanchez, Sipper, Haenni, Beuchat, Stauffer, and Perez-Uribe 1999); this class of boards is sometimes referred to as *netlist architecture* (Mangione-Smith 1997b), since a primary intermediate form for specifying the programming of such boards is an interconnection specification called a netlist. The sub-sections that follow discuss several of these systems; the designs span more than a 10 year period (roughly from 1990 through 2002), and represent a considerable evolution in design. All of the designs represent a coprocessor paradigm - the reconfigurable board is attached via a high speed bus to a standard processor, which acts as the control and management unit for the coprocessor board. They are of particular interest here because this type of hardware is the target for the work described in this dissertation.

### 2.2.1 The Splash-2 Reconfigurable Computing Board

One of the first reconfigurable processing boards, at least in the modern era, The Splash-2 (Buell, Arnold, and Kleinfelder 1996) was developed in 1991, and has been used in several different applications. A simplified diagram of the Splash-2 is shown in Figure 2.3.

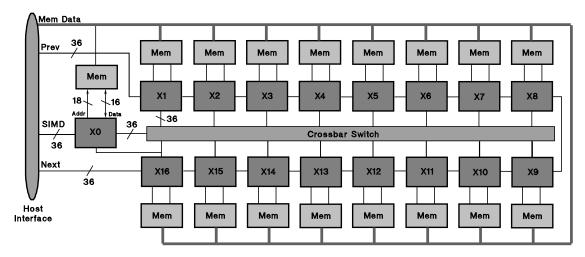

The Splash-2 utilizes 16 Xilinx XC4010 FPGAs (Processing Elements, or PEs, labeled

X1 through X16), connected to each other via a 36 bit bus (intended to be used as 32 bits of data, plus 4 user-definable tag bits) in a linear array. Each PE is also connected to its own 512K byte local memory, organized as 16 bit words. One additional FPGA (X0) serves as the control processor – its main job is to control the *crossbar*, a programmable, bidirectional 36 bit interconnect which is connected to the other processing elements. This crossbar can be reconfigured as often as every clock cycle, if desired, by specifying one of eight pre-determined configurations. Each configuration allows a PE to broadcast data to one or more of the others; the data paths can be configured in four-bit chunks.

The system is attached to a Sun SPARCstation host processor, via the processor's S-Bus. The host is responsible for downloading the FPGA configurations, setting the board frequency and controlling the clock, and passing data to and from the ends of the linear array. The host can also load data into each local PE memory. The role of the host can either be synchronous, directly controlling the Splash-2 while it is operating, or asynchronous, allowing the Splash-2 to function independent from the host, once initialized.

The system can be expanded by adding additional boards. The additional PEs are connected so they add to the length of the linear array.

A variety of applications have been implemented on the Splash-2, including searching (Hoang 1993; Pryor, Thistle, and Shirazi 1993), pattern matching (Ratha, Jain, and Rover 1996), convolution (Ratha, Jain, and Rover 1995) and image processing (Athanas and Abbott 1994). The speedups of these applications compared with similar applications executing on conventional processors can be impressive, with a range of from less than 1 (no speedup) to over 1000, relative to an algorithm executing on a conventional processor. Not surprisingly, the speedup in general depends upon how closely the application matches the processing strengths of the Splash-2. Since the Splash-2 consists of 16 fairly small-size FPGAs (the XC4010 contains a matrix of  $20 \times 20$ , or 400 total, CLBS, for a total of 6800 CLBs on each board), those applications which can be partitioned into up to 16-deep pipeline stages, with each stage doing a simple operation that can fit into one of the FPGA chips, achieve good speedups over sequential processors. Similarly, applications which perform small bit-width operations, which exploit the fine-grain nature of FPGAs,

Figure 2.4: Simplified Architecture of the Wildforce Configurable logic board

and would be inefficient on a byte-at-a-time processor, do very well. For example, the largest speedup was reported on a bit matching application that also used the PEs on Splash very effectively as a systolic array. Other applications which involve complicated operations, or more sequential processing steps, do not perform as well. Some of the compromises made during the design of the Splash-2, such as a narrow 16 bit memory data bus (a limitation imposed by a lack of I/O pins on the FPGAs), limit its effectiveness in some applications.

The Splash-2 was one of the first implementations of a reconfigurable computing board. It showed impressive performance in a wide range of applications, and sparked considerable interest in reconfigurable computing. Even more importantly, it has provided a platform to experiment with reconfigurable computing architectures. Many of the "good" features of the Splash-2 have been carried over in new designs, and some of its limitations have been eliminated or otherwise addressed in newer architectures.

### 2.2.2 The Wildforce Reconfigurable Computing Board

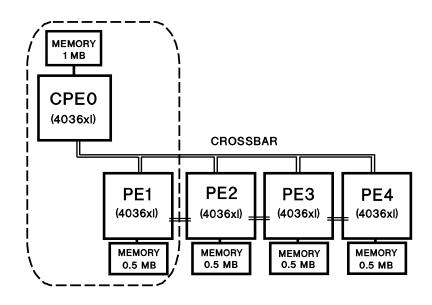

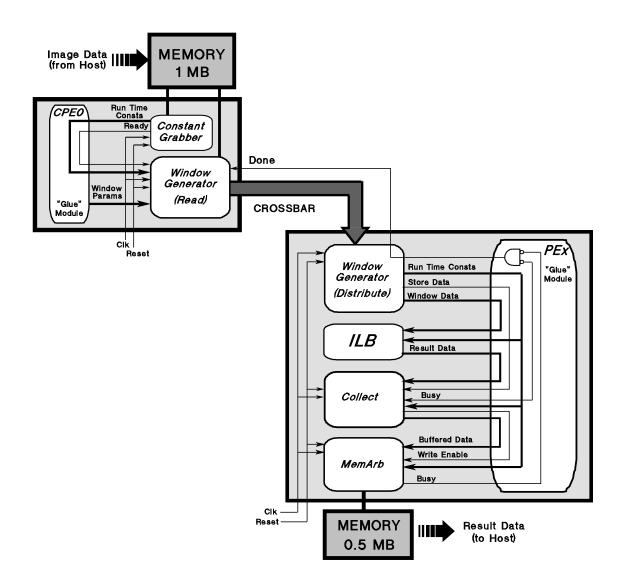

The Annapolis Micro Systems Wildforce<sup>TM</sup> Computing Board (Annapolis Micro Systems, Inc., Annapolis, MD 1997) draws considerable inspiration from the Splash-2. It is one of a family of commercially-available boards which also utilize off-the-shelf components. It was introduced in 1997. A simplified diagram of its architecture is shown in Figure 2.4. The Wildforce processing board includes a control processor (called CPE0) which controls a crossbar with similar capabilities to that of the Splash-2. The main processing on the board is again done with a linear array of FPGAs (PE1 - PE4), each with its own local memory. The primary data paths, this time including the memory data bus, are all 36 bits each.

However, there are also significant differences with the Splash-2. The control processor and PEs are implemented with later and much larger members of the Xilinx XC4000 family, with a choice from the XC4025 (a  $32 \times 32$  matrix, 1024 CLBs) up to the XC4085 (56, or 3136 CLBs) for each PE. Because of the increased logic density, a smaller number of chips (4 vs 16) can be used for the linear array, but the total number of CLBs available is on par, and in some cases, much larger than, the total number on the Splash-2. (For example, the mid-size Wildforce board owned by Colorado State University contains five XC4036 chips, which contain a  $36 \times 36$  CLB matrix, for a total of 1296 CLBs on each chip, and 6480 total CLBS, comparable to the 6800 CLBs on the Splash-2.) The higher density chips reduce the number of interfaces required in the linear array, and allow the Wildforce to be used for shallower, but more complex, pipeline designs. Yet, nothing precludes the placement of several pipeline stages on each FPGA, thereby allowing Splash-2 applications to be mapped to the Wildforce.

New features facilitate the movement of data between the host and the Wildforce. The PCI bus interface allows DMA mode, which supports bandwidths up to 132 MB/Sec between host memory and the board. Three hardware FIFOs, each 512 words deep, are also implemented in hardware; they facilitate the streaming of data to and from the host. Finally, an external I/O interface can be connected to the board, allowing data to be sent to/from the board without any host intervention.

Since this board is the target of some of the work described in this dissertation, a few observations about its strengths and limitations, along with performance data on several applications developed during the work described in this dissertation, will be presented later.

Figure 2.5: Architecture of the SLAAC Configurable Logic Board

### 2.2.3 The SLAAC-1 Reconfigurable Computing Board

The SLAAC-1 processor continues the evolutionary path from the Splash-2 to new technology. SLAAC (Systems Level Applications of Adaptive Computing) project (Schott, Crago, C., Czarnaski, French, Hom, Tho, and Valenti ) is a comprehensive research project which defines its mission to be:

- 1. To define an open, distributed, scalable, adaptive computing systems architecture.

- 2. To design, develop, and evolve scalable reference platform implementations of this architecture, and

- 3. To validate the approach by deploying technology in multiple defense application domains.

As part of the project, the SLAAC-1 reconfigurable computing board has been developed. A diagram of the SLAAC-1 board is shown in Figure 2.5.

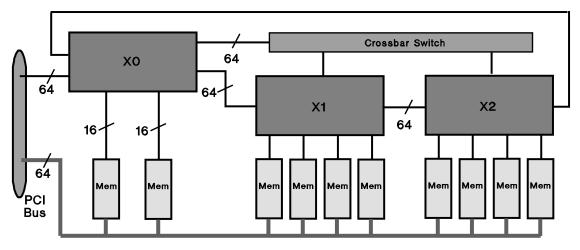

The SLAAC-1 represents another step in the evolution of the architecture initiated by the Splash-2. It is composed of 3 XC40150 chips, each of which containing a matrix of  $72 \times 72$  (5184 total) CLBS, for a system total of 15552 CLBS – roughly 2.5 times that of the Splash-2. A second generation of the board is also being developed using the newer Virtex family of FPGAs (the XCV10000); this will increase the total CLB count to over 18,000, and should allow up to a four-fold increase in processing speed. The concept of one FPGA (X0) serving as the control processor is carried over from the Splash-2, as does the crossbar between the FPGAs. The linear array connections continue to exist, although now the control processor is connected to the linear array from both ends, forming a ring among the three PEs.

All of the datapaths on the SLAAC-1 have been increased to 64 bits, with the crossbar and linear array buses expanded to 72 bits (64 bits plus 8 tag bits). The memory access bottleneck that exists in both the Splash-2 and Wildforce has been mitigated by allowing the memories to be treated either as a single 64 bit wide memory (32 bits for X0), or as four separate 16 bit memories (two for X0). The memories allow reads to occur in one cycle, versus two cycles for Splash-2 and Wildforce.

The SLAAC-1 continues the evolutionary path from the Splash-2 to new technology. It appears that with faster chips, 64 bit datapaths, and a more versatile memory structure, it will provide performance several times that of previous reconfigurable systems. It also continues the trend toward the use of fewer, denser chips, which reduces the number of external interfaces the programmer must contend with.

#### 2.2.4 The Annapolis Wildstar Reconfigurable Computing Family

The next generation of reconfigurable computing boards developed by Annapolis Micro Systems is called Wildstar<sup>TM</sup>. The name refers to a family of boards, as well as one of the members of the family. The processors consist of one or more Xilinx Virtex FPGAs. This chip provides up to a two order of magnitude increase in the number of logic elements (CLBs) when compared with the Xilinx XC4000 series chips, as well as a factor of four or more improvement in clock speed over the previous generation Xilinx XC4000 series chips. Continuing the evolutionary trend in FPGA-based computing boards mentioned earlier, this allows a dramatic improvement in the size of problem that can be computed on the board, yet reduces the number of external interconnections between chips, thereby reducing the task of partitioning a problem amongst several separate chips.

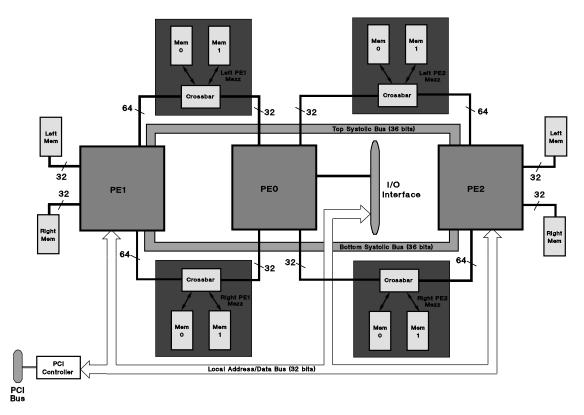

The block diagram of the largest member of the Wildstar family, also called the Wildstar (Annapolis Micro Systems, Inc., Annapolis, MD 1999b), is shown in Figure 2.6. It

Figure 2.6: Block diagram of the Annapolis Wildstar Reconfigurable Computing board

consists of three Virtex FPGAs, each containing logic equivalent to 1 million gates. The architecture is symmetric around elements PE1 and PE2, while PE0 is primarily used to communicate with a possible input/output board that can be connected to the I/O interface. PE1 and PE2 each connect to two local memories, where data that doesn't need to be shared with the other processing elements can be stored. Additional memories, expandable via the use of mezzanine cards, sit between the processing elements; these memories can hold data that either needs to be accessible to more than one PE at a time, or that needs to be communicated between two PEs. A crossbar switch controls which PE has access to a given memory at a given time. Data can also be communicated between PE1 and PE2 via two 36 bit systolic busses.

A host processor can communicate both commands and data to the board via its PCI bus, which connects to the Local Address and Data (LAD) Bus within the Wildstar; this bus is connected to PE1 and PE2. Because of the many separate data paths between the processing elements and the various memories, a very impressive aggregate data bandwidth between PEs and memory of 6.4GHz is possible.

A couple of smaller boards are also part of the Wildstar family, the Starfire board (Annapolis Micro Systems, Inc., Annapolis, MD 1999a) consists of a single Virtex Processing element - essentially PE1 in Figure 2.6 above. This board only contains a third of the number of CLBs as the Wildstar board. Nonetheless, when outfitted with a Virtex XCV10000 chip it provides about 30 times the number of equivalent gates as the entire earlier generation Wildforce board. A Starfire board was available during the latter portions of the research described in this dissertation, and it was used to run some of the larger optimization experiments. More specific information concerning the architecture of this board is discussed later in conjunction with these experiments.

Finally, a third member of the family, called Starfire-II, contains two processing elements - essentially PE0 and PE1 in Figure 2.6. This model is useful if a significant amount of I/O processing, performed by PE0, needs to be performed, but the full size of the Wildstar board is not required.

## 2.3 Custom-Designed Reconfigurable Computing Boards

While the technology used in commercially-available FPGAs has seen considerable improvement over the course of the last decade, and provides a much quicker and cheaper solution in the design of reconfigurable computing boards, nonetheless it offers some severe compromises in the design. There are two major problems with the off-the-shelf systems:

- They must be connected to the host processor via an external bus (such as VME or PCI), which limits data transfers between host and board to at most a few hundred megabytes/sec. Reconfigurable computing could benefit from bandwidths similar to that currently available between host and main main memory, perhaps in the gigabyte range.

- The currently available FPGA chips are not primarily designed for reconfigurable computing, and therefore are not optimized for reconfigurable applications. In particular, it requires milliseconds to download new configurations, and in general the

Figure 2.7: Architecture of the Morphosys Architecture. One of the Reconfigurable Cells (RC) within the RC Array is shown.

entire chip must be reconfigured, rather than only small portions as might be useful in reconfigurable applications. The ability to store multiple contexts in the chip at the same time is not possible.

Several projects are ongoing to develop custom reconfigurable systems A small survey of some of these systems, chosen to be representative of current research and development in the reconfigurable computing area, follows. Other projects are described in the literature (Hauser and Wawrzynek 1997).

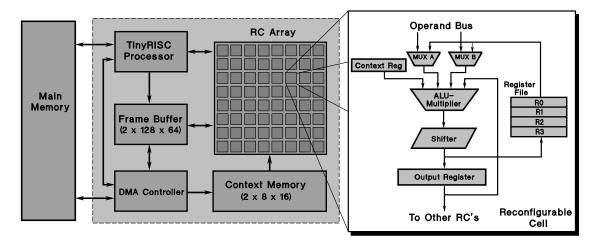

### 2.3.1 Morphosys

The Morphosys project (Lu, Singh, Lee, Bagherzadeh, and Kurhadi 1999) is creating a new chip design that provides a CPU coupled with a specialized reconfigurable matrix of *reconfigurable cells* (the RC array). The overall architecture is shown in Figure 2.7. At first glance, the configuration looks similar to that of the attached processors discussed earlier; however, in this case, the processor is considerably more tightly coupled with the RC array, in that it can change the configuration context of the RC array as often as every clock cycle. Also, the results from the RC array are available immediately in the *frame buffer*, which is an integral component along the processor's data path.

In contrast to the fine-grain capabilities of the simple logic cells available in an FPGA, the RC array within Morphosys consists of a matrix of considerably coarser grained units called Reconfigurable Cells (RC). A diagram of an RC is also shown in Figure 2.7. It consists of a preconnected set of components, including an ALU-Multiplier, a shift unit, input MUXs, a register file, and a context register. In short, each RC contains the essential component of a small processor. This type of reconfigurable hardware is referred to as a *chunky* architecture (Mangione-Smith 1997b), and stands in contrast to the more "fine grain" characteristics of the *netlist* architectures represented by conventional FP-GAs. Instead of connecting gates together to implement low-level logic functions, the programming of the RC array within Morphosys is more analogous to connecting processor functional units together to perform custom operations. Programming should be relatively quick, since it is being done at a much higher level than traditional FPGAs. The RC array consists of an  $8 \times 8$  matrix, a total of 64 components instead of the thousands of logic cells in a conventional FPGA.

The first implementation of the Morphosys architecture is called the M1. The second round of implementation, the M2 chip, is currently running in simulation at 450MHz.

### 2.3.2 The RAW Project

The RAW Project (Waingold, Taylor, Srikrishna, Sarkar, Lee, Lee, Kim, Frank, Finch, Barua, Babb, Amarasinghe, and Agarwal 1997) is a comprehensive project which involves the development of both hardware and software for reconfigurable computing; the hardware component will be highlighted here.

The RAW architecture is pictured in Figure 2.8. It marries a CPU and configurable logic together in a single unit called a *tile*, in an attempt to minimize the distance between the host and reconfigurable logic that plagues the attached processors. The tiles are then replicated into a matrix on a single chip, with an interconnection network between them.

Each tile consists of several components: an instruction memory (IMEM), similar to the instructions executed by a conventional processor, data memory (DMEM), a fairly conventional ALU, the configurable logic (CL), and a programmable switch along with its associated program memory (SMEM). The placement of the configurable logic into the tile's primary datapath allows data to be transformed in custom ways as it is being

Figure 2.8: Architecture of the RAW Architecture, showing a portion of the tile array, and the details of one of the tiles.

processed by the tile. Another way of viewing this intimate relationship of the configurable logic to the ALU is that it allows the compiler to generate new specialized instructions, and insert them into a data stream that is being processed by the "normal" instructions built into the ALU.

The RAW Architecture is extremely versatile. The additional of the programmable network in the chip provides the capability of systolic-array architectures. The ability to process several parts of a data stream through different tiles, with either the same program (as in Intel MMX-type (Peleg, Wilkie, and Weiser 1997) instructions) or different ones provides a VLIW-like capability. If the ALU does NOPs, so that the data stream is processed entirely by the reconfigurable section, a fine grained FPGA-like capability results. In fact, the RAW architecture contains characteristics of virtually every processor configuration, allowing it to emulate any of these efficiently.

The downside of such a versatile architecture is the heavy burden placed on the programmer and/or compiler to effectively utilize the available resources. As a result, a

Figure 2.9: Architecture of the PipeRench Architecture, showing two stripes.

significant effort is being placed on the compilation system to go along with the hardware development; some aspects of the compilation process is discussed later. Also, since the entire system's throughput depends upon properly balancing the amount of chip space devoted to the various components within each tile, extensive simulations are being done to determine the optimal sizing. To date, no actual implementations have been completed, although a detailed specification of the prototype has been developed(Taylor 2004).

### 2.3.3 PipeRench

In contrast to the chunky architectures described above, the PipeRench Project (Goldstein, Schmit, Moe, Budiu, Cadambi, Taylor, and Laufer 1999) is more fine grained in nature, although not as fine grained as netlist architectures. The main characteristics of the PipeRench architecture are shown in Figure 2.9.

PipeRench is built around a pipeline scheme – each pipeline stage is called a *stripe*. Several stripes are connected together, with the top and bottom connected together to form a ring. The set of stripes in a system is called the *fabric* - the exact number of stripes in a given system is implementation dependent. Each stripe contains a number of small reconfigurable (lookup table based) PEs. The usual situation is for the inputs of one PE to come from the outputs produced by the previous stripe, and for the outputs of the PE to be connected to the inputs of the next stripe. However, a set of global busses along each edge of the fabric also allow non-contiguous stripes to communicate with one another.

A PipeRench program is written in a single-assignment, pipeline oriented language called DIL (Goldstein and Budiu 1999). The compiler translates the program into a set of pipeline stages; at the same it does the synthesis and place-and-route operations. This is in contrast to other netlist-based compilation systems, which may require hours to perform these tasks. It is possible to do in reasonable time here because of the relatively simple interface structure between the stripes. The execution behavior is rather novel; the run time part of the compiler maps the first n ( $n \ll$  the number of stripes) pipeline stages onto the PipeRench fabric. Since it is likely that more pipeline stages are required than the fabric contains, once a stripe has been executed, it is replaced with another one; the effect is a "rolling" execution through a circular buffer of stripes, like the tread on an army tank, with stripes that have just executed being reprogrammed with code that will soon be executed.

At first glance, it would seem that this process would be inefficient, since it is possible that a stripe that occurs in a long loop (one that has more pipeline stages than the fabric) will need to be loaded multiple times. This is true; however, the loading of new stripes occurs while other stripes are executing; thus, the cost of the reconfiguration can be completely hidden by the execution time of the currently loaded stripes.

Several things are interesting about the PipeRench architecture:

- The compiler required to translate DIL into stripes is simple. Unlike some other architectures, which hope that their compilers can handle a very unwieldy task in producing efficient code for a complicated architecture, the DIL compiler is simple and straight-forward.

- Because of the simplicity of the interface between stripes, the compiler also performs

the synthesis and place-and-route. This eliminates some of the most time-consuming steps involved in producing reconfigurable programs.

• The architecture is extremely extensible. A code can operate on a fabric with any number of stripes. If a larger fabric is available, the same program will operate without recompilation on the larger fabric, with the benefit that more of the complete program will fit on the fabric, thereby reducing the amount of context switching required. The width of stripes (i.e., the number of data bits in each pipeline stage) can also be changed, although this requires a recompilation for the new width.

A first implementation has been fabricated, and it currently being tested. A second second iteration on the design has started (Goldstein and Schmit 1999), with a focus on enhancing I/O performance, and to provide a shared memory capability between stripes. Also, a piperench chip has been fabricated and tested, using 0.18 micron technology(Schmit, Whelihan, Tsai, Moe, Levine, and Taylor 2002).

#### 2.3.4 Field Programmable Processor Array

Another architecture whose granularity falls between the very fine-grained netlist and coarse-grained chunky architectures is called the Field Programmable Processor Array (FPPA)(Donohoe, Buehler, and Bruder 2000b). It is being implemented using radiationtolerant design techniques, so that it can be used in satellite and other outer space applications.

An overview of the architecture is shown in Figure 2.10. It consists of sixteen identical *Processing Elements* (PEs), organized into four groups of four called *clusters*. The switch within the cluster allows any PE output to be connected to any other PE input with the cluster. A central crossbar allows each cluster can be connected either to other clusters, or to any of five Input/Output Ports (IOPs) or a Dedicated Output Port (DOP).

Each PE contains an ALU, multiplier, shifters and a comparator that can be connected in numerous ways to implement a function. The PE inputs are registers that can be updated at each clock pulse. In general, all datapaths are 16 bits; however, logic has been included so that the PEs in a cluster can be connected in parallel to create a wider

Figure 2.10: FPPA architecture overview

datapath when necessary. Figure 2.11 shows the simplified block diagram of each PE.

Due to its medium-grain design, a relatively small number of bits is required to fully specify the interconnection within a PE. A total of 70 bits specifies the interconnection of each PE. Similarly, the interconnect between clusters requires only 114 bits. A complete configuration of the FPPA therefore requires only about 1K (actually 1234) bits. Finally, each PE can be independently configured; it is not necessary to reconfigure the entire chip at once. Thus a typical application will generally require fewer than the maximum number of bits.

At a minimum, an FPPA "program" consists of a configuration that specifies the interconnection within the PEs and between PEs, and a "runtime sequence" that specifies when new values are to be loaded into the input registers of each PE. A program "executes" by first loading a configuration into the PEs, and then executing the runtime sequence to determine when, and which, input registers are updated. For example, several PEs might be connected in series to create a pipeline; in such a configuration, a pipeline stage consists of the PEs input registers, followed by the interconnected logic within the PE. Alternately, the PEs in a cluster can be connected in parallel to accommodate data paths that are wider than 16 bits.

Figure 2.11: Organization of each FPPA Processing Element

Several applications have been coded for the FPPA and currently run in simulation (Sabde, Buehler, and Donohoe 2003). The architecture has been influenced by the requirements for these applications, as well as an effort to develop a fixed-point arithmetic capability for the processor(Buehler, Donohoe, and Yeh 2004; Buehler 2004). Of particular note for the subject of this dissertation, an effort is being initiated to re-target the SA-C compiler for the FPPA(Rinker, Nathan, Buehler, and McConaghy 2005).

# 2.4 Software Development for Reconfigurable Computing

Perhaps even more important than the novel hardware being developed for reconfigurable computing is the challenge of software support. The best, fastest hardware will not be utilized unless software exists that can exploit the hardware resources.

In a look ahead at the future of reconfigurable systems, Hauck (Hauck 1998) states that:

"... if reconfigurable computing is to be successful it must create a methodology

Figure 2.12: A comparison of (a) temporal vs. (b) spatial computation for the equation  $y = Ax^2 + Bx + C$

to automatically map from standard programming languages to the hardware system. Just as general-purpose computing has moved away from assembly language programming, future users of reconfigurable computing will either insist on such a mapping tool suite, or will abandon this technique."

This is a daunting challenge, due to the significant differences in the execution behavior of the target machine for reconfigurable computing versus general processors. This difference is illustrated in Figure 2.12.

General-purpose sequential processors perform *temporal computation* (DeHon and Wawrzynek 1999) – a set of instructions is executed in sequence over time. In its simplest form, one instruction is in execution at any instance, and the order of instructions is fixed. A clock determines the point at which one instruction is finished executing and the next instruction starts. In contrast, reconfigurable computing exhibits *spatial computation*, where the computation is performed by a uniquely connected circuit, and is able to proceed as quickly as the underlying technology allows. This new execution model motivates several important features of the nature of reconfigurable computing:

• The computation is no longer bound by a clock and a sequential ordering of instructions. Instead, the order of operations involved in the computation is defined by the interconnection pattern in the computation circuit. This behavior, in the context of digital logic, is called a *combinational circuit*, or a combinational computation. The "answer" for a given set of inputs appears at the bottom as quickly as the circuits can respond to that input (i.e., the propagation delay of the circuit), rather than being regulated by a clock.

- Spatial computation is naturally parallel, since all parts of the circuit are "computing" at the same time.

- The computation can be characterized by a flow of information from the top of the computational circuit down to the bottom the speed and order with which the computation proceeds is determined entirely by the interconnections of the circuit and the propagation delay inherent in the implementing technology. This characterization is embodied in the *dataflow graph* described earlier reconfigurable computing appears to be a nearly perfect practical implementation of the abstract dataflow execution model.

A very important feature of temporal computing - that of loops, does not exist in purely spatial computing. The effect of loops is produced in one of two ways:

- 1. By unrolling the loop, which transforms the temporal concept of an iteration to an entirely spatial entity, or,

- 2. By introducing a *state machine* which controls the generation of input values, which are presented to the inner loop body as a data stream. The circuit is no longer strictly combinational, since the state machine introduces the notion of time back into the computation. However, the execution behavior is still different from the traditional processor in that the inner loop body is allowed to compute as quickly as the circuits can respond, and the operation remains inherently parallel. The speed at which the computation proceeds is limited by the propagation delay of the inner loop circuits.

Standard languages, such as C, are designed to represent a temporal style of computing – as such, they are ill-suited for expressing spatial computing. A considerable amount of effort must be spent to determine unnecessary sequentialness specified by the language and to expose the parallelism that exists in a calculation, so that a spatial representation of the problem can be formed. Often this involves severely limiting the subset of the language that can be used for reconfigurable computing. Nonetheless, there is considerable motivation to start with a standard language, since it is familiar to the application programmers who might effectively utilize reconfigurable computing.

The next sections provide an overview of several software-related research efforts in reconfigurable computing.

#### 2.4.1 The RAW Compiler Project

Coupled with the RAW hardware project discussed earlier is a significant compiler effort (Agarwal, Amarasinghe, Barua, Frank, Lee, Sarkar, and Srikrishna 1997). The goal is to provide a C compiler which targets the RAW architecture. In some respects, the compiler is fairly conventional, since the components that make up each tile of the architecture (a RISC CPU with data and instruction memory, a regular interconnection network, and an intelligent data switch) are relatively conventional. It is unique, however, in that all of the resources of RAW reside on a single chip, and therefore the compiler can assume a very regular array of resources. This is in contrast to other networked resources such as WAN or networks of workstations, where the interconnection network is irregular (both in interconnection and in communication latency) and changeable, and communication costs are high. The compiler can exploit this regularity, for example by "ganging" several tiles together to perform a highly parallel or wide datapath operation. This produces the effect of a VLIW machine with a variable-width instruction tailored to a specific application, and with the further flexibility that the processors do not have to stay in lock-step during execution.

Similar flexibility exists in the scheduling of communication events. With a regular, low-cost communication network that contains intelligent switches, both static and dynamic routing can be accommodated simultaneously.

The current compiler implementation is called RAWCC, and it compiles both C and Fortran Programs (Lee, Barua, Frank, Srikrishna, Babb, Sarkar, and Amarasinghe 1998). It operates in three phases:

- Traditional high-level program analysis and transformation, including memory disambiguation, loop unrolling, and a scheme which encapsulates the control flow within a basic block into a single unit for resource scheduling purposes.

- A basic block orchestrator, which decomposes a single basic block into a set of basic blocks that can be executed in parallel on separate tiles. This involves both time and space scheduling of each basic block on a set of tiles.

- Code generation for the processors and switches.

Results show that the speedup ranges on common benchmarks from 9 to 38 on a 32 processor RAW simulator, as compared to a single processor. The superscalar speedup occurs due to scalar optimizations exposed during loop unrolling, a phenomenon more related to the highly parallel nature of the code than on inherent qualities within the RAW architecture.

#### 2.4.2 PipeRench and DIL

The PipeRench architecture described earlier is programmed with a language called DIL (*Dataflow Intermediate Language*) (Goldstein and Budiu 1999). DIL is intended to be an intermediate language between a high level language such as C and the PipeRench hardware description. DIL is designed specifically to describe the interconnections possible within stripes of the PipeRench architecture – the language and the architecture are a perfect match for each other. Because of this, DIL can be compiled almost directly into an interconnect specification for PipeRench; very little effort is required in place and route operations after compilation.

DIL is a single assignment language - a variable can be assigned a value only once. Thus, there is a one-to-one correspondence between variables in DIL and wires in the hardware, one of the reasons for the close tie between language and hardware. The delays required between expression evaluation and variable assignment is also explicit; for example:

```

var <n= expression;</pre>

```

indicates that var is to be assigned the value of expression after n clock cycles. This statement is implemented by using one stripe to calculate the expression, and then connecting the output of the stripe (possibly via the global bus) to the input of the n-th stripe following it.

Different from C, data types have no inherent size (i.e., bit width) associated with them – data sizes are either specified by the user, or are inferred by the compiler from the input and/or output sizes (the user must specify these). This owes from the fact that reconfigurable hardware (including PipeRench) usually has no inherent bit size restrictions, except to have some maximum size determined by I/O or other architectural interfaces. In particular, considerable size and sometimes speed efficiency can be gained by using minimum bit widths for calculations.

DIL is intriguing due to its simplicity, and to its close correspondence to the hardware which is its target. It is also dataflow-like in nature, which means that, within the limitations of high-level languages to express parallel operations, it should be relatively straight-forward to translate these high level languages to DIL.

#### 2.4.3 Reconfigurable Computing and High Level Application Environments

A couple of research projects which use higher level application environments as a front-end for reconfigurable computing are ongoing. The first, called MATCH (Banerjee, Shenoy, Choudhary, Hauck, Bachmann, Chang, Haldar, Joisha, Jones, Kanhare, Nayak, Periyacheri, and Walkden 1999; Periyayacheri, Nayak, Jones, Shenoy, Choudhary, and Banerjee 1999), involves the use of MATLAB as its input language. The project is developing a MATLAB compiler and a set of library modules that implement the various MATLAB functions. They have reported a two orders of magnitude increase in computation rate of certain MATLAB benchmarks over the C versions of the libraries.

The second project, called CHAMPION (Natarajan, Levine, Tan, Newport, and Bouldin 1999), involves a similar approach, except it uses Khoros as the input language. Khoros glyphs are written VHDL, and then they are mapped onto hardware. This project is of particular interest here, since the problem description is very similar to that of Cameron, at least on the surface, and the two projects are currently targeting the same hardware. The main difference is that the Khoros glyphs are written in VHDL in Champion, and in SA-C in Cameron. The focus of effort in Champion has been on the rewriting of the glyphs in VHDL, and the partitioning and mapping of this code onto the hardware, whereas in Cameron the effort has been focused on compiler development and automation of the development process, in order to provide an environment in which to develop glyphs that run on hardware. The orthogonal approaches between the two projects suggest that the two could benefit from collaborating with one another – Champion could utilize the SA-C compiler to develop their glyph code, and Cameron could take advantage of the problem partitioning that has been developed by Champion.

#### 2.5 The Cameron Project and SA-C

The Cameron Project (Najjar, Draper, Böhm, and Beveridge 1998; Hammes, Rinker, Böhm, Najjar, Draper, and Beveridge 1999) is a software project whose goal is to provide a hardware-independent environment for reconfigurable computing application development. Its primary application domain is image processing, although the environment is general enough to be suitable for other areas as well. Since the research described in this dissertation is being performed in conjunction with the Cameron project, its description has been saved for last. This section also serves as an introduction to the SA-C language and compilation system that will be described in more detail later.

Central to the project is the design of a language called SA-C (*Single Assignment C*, pronounced "sassy") (Hammes, Draper, and Böhm 1999; Hammes and Böhm 1999). It consists of an optimizing compiler which produces as its intermediate form a dataflow graph (DFG), a translator which converts the DFG into VHDL, and some ancillary programs which aid in debugging and program verification. As the name implies, SA-C is a derivative of C – the language shares its operator syntax and precedence, and the available data types have been extended from C. However, many of the features of C which would require considerable analysis for reconfigurable computing targets have been removed or modified.

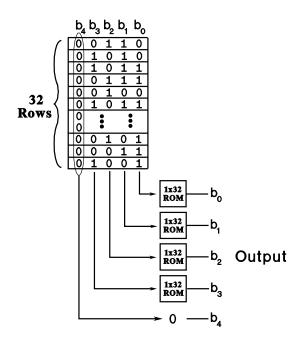

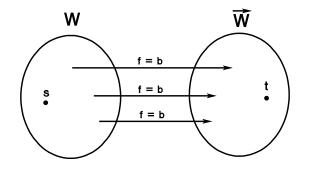

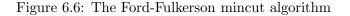

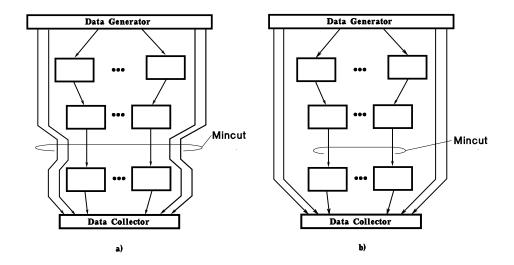

SA-C shares some similarities to DIL, due to their common heritage as hardware generation languages. Like DIL, SA-C is single assignment, and uses both user specification and size inference to try to minimize the bit widths required for calculations. In contrast to DIL, SA-C is a considerably higher level language, and is designed to be independent of the particular hardware that is used (indeed, SA-C can be compiled to run only on the host).