# Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

Summer 2020

# Accurate modeling techniques for power delivery

Jingdong Sun

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Electrical and Computer Engineering Commons Department: Electrical and Computer Engineering

### **Recommended Citation**

Sun, Jingdong, "Accurate modeling techniques for power delivery" (2020). *Doctoral Dissertations*. 2921. https://scholarsmine.mst.edu/doctoral\_dissertations/2921

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

## ACCURATE MODELING TECHNIQUES FOR POWER DELIVERY

by

## JINGDONG SUN

#### A DISSERTATION

Presented to the Graduate Faculty of the

## MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

## DOCTOR OF PHILOSOPHY

in

## ELECTRICAL ENGINEERING

2020

Approved by:

Jun Fan, Advisor DongHyun Kim Victor Khilkevich Chulsoon Hwang Yaojiang Zhang

© 2020

Jingdong Sun

All Rights Reserved

#### PUBLICATION DISSERTATION OPTION

This dissertation consists of the following three articles, formatted in the style used by the Missouri University of Science and Technology:

Paper I, found on pages 7–39, is conditionally accepted with major revisions in *IEEE Transactions on Electromagnetic Compatibility*.

Paper II, found on pages 40–72, has been submitted to *IEEE Transactions on Power Electronics*.

Paper III, found on pages 73–116, has been published in *IEEE Transactions on Power Electronics*, vol. 35, no. 8, pp. 7840-7852, Aug. 2020.

#### ABSTRACT

Power delivery is essential in electronic systems to provide reliable power from voltage sources to load devices. Driven by the ambitious user demands and technology evolutions, the power delivery design is posed serious challenges. In this work, we focus on modeling two types of power delivery paths: the power distribution network (PDN) and the wireless power transfer (WPT) system.

For the modeling of PDN, a novel pattern-based analytical method is proposed for PCB-level PDN impedance calculations, which constructs an equivalent circuit with oneto-one correspondences to the PCB's physical structure. A practical modeling methodology is also introduced to optimize the PDN design. In addition, a topology-based behavior model is developed for the current-mode voltage regulator module (VRM). This model includes all the critical components in the power stage, the voltage control loop, and the current control loop of a VRM device. A novel method is also proposed to unify the modeling of the continuous and discontinuous conduction modes for transient load responses. Cascading the proposed VRM model with the PCB-level PDN model enables a combined PDN analysis, which is much needed for modern PDN designs.

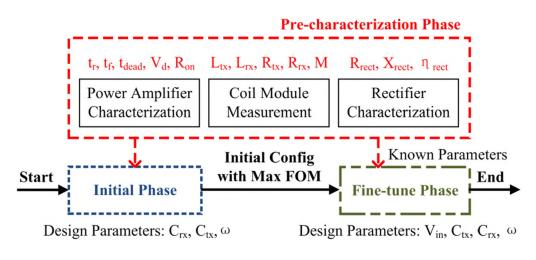

For the modeling of WPT system, a system-level model is developed for both efficiency and power loss of all the blocks in WPT systems. A rectifier characterization method is also proposed to obtain the accurate load impedance. This model is capable of deriving the power capabilities for both the fundamental and higher order harmonics. Based on the system model, a practical design methodology is introduced to simultaneously optimize multiple system parameters, which greatly accelerates the design process.

#### ACKNOWLEDGMENTS

Throughout my doctoral studies and writing of this dissertation, I have received a great deal of support and assistance from my mentors, collaborators, family, and friends.

I would like to express my deepest gratitude to my advisor, Dr. Jun Fan, for his guidance, encouragement, and trust of my study. Dr. Fan not only gave me insightful comments on my research projects, but also helped me develop growth mindsets and positive attitudes towards my future career.

I would like to thank Dr. DongHyun Kim, Dr. Victor Khilkevich, Dr. Chulsoon Hwang, and Dr. Yaojiang Zhang for serving on my doctoral committee and providing helpful feedbacks on my research work.

In addition, I would like to extend my appreciation to all the faculty members and staffs in the UMR/MST EMC Lab. I would like to specially thank Dr. James Drewniak for inspiring my career path. My sincere thanks also go to Dr. Jonghyun Cho, Dr. Heegon Kim, and Dr. Hongseok Kim for their advice and assistance in my projects. I truly appreciate the help and coorperation from the students in the EMC lab, in particular Anfeng Huang, Xin Yan, Ze Sun, Shengxuan Xia, and Nicholas Erickson.

Finally, I am deeply grateful to my parents, Fengwu Sun and Xiuhong Wang for their constant support. I would like to express my love for my girlfriend, Wei Li, who provides me continuous encouragements in the past six years. This dissertation would not have been possible without their love and endless support.

This dissertation is based upon work supported partially by the National Science Foundation (NSF) under Grant No. IIP-1916535.

## **TABLE OF CONTENTS**

| Page                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------|

| PUBLICATION DISSERTATION OPTIONiii                                                                                         |

| ABSTRACTiv                                                                                                                 |

| ACKNOWLEDGMENTS                                                                                                            |

| LIST OF ILLUSTRATIONS                                                                                                      |

| LIST OF TABLES                                                                                                             |

| SECTION                                                                                                                    |

| 1. INTRODUCTION                                                                                                            |

| 1.1. POWER DISTRIBUTION NETWORK                                                                                            |

| 1.2. WIRELESS POWER TRANSFER SYSTEM                                                                                        |

| 1.3. CONTENTS AND CONTRIBUTIONS                                                                                            |

| PAPER                                                                                                                      |

| I. A PATTERN-BASED ANALYTICAL METHOD FOR IMPEDANCE<br>CALCULATION OF THE POWER DISTRIBUTION NETWORK IN MOBILE<br>PLATFORMS |

| ABSTRACT                                                                                                                   |

| 1. INTRODUCTION                                                                                                            |

| 2. PATTERN FORMULATION AND CALCULATION 12                                                                                  |

| 2.1. PATTERN FORMULATION                                                                                                   |

| 2.2. PATTERN CALCULATION                                                                                                   |

| 2.3. SIMULATION STUDIES ON ACCURACY AND EDGE-EFFECT 22                                                                     |

| 3. PDN MODELING METHODOLOGY                                                                                                |

| 3.1. PCB DIVISION                                                                                                          | 27 |

|----------------------------------------------------------------------------------------------------------------------------|----|

| 3.2. PATTERN IDENTIFICATION                                                                                                | 28 |

| 3.3. CIRCUIT RECONSTRUCTION                                                                                                | 29 |

| 3.4. DESIGN OPTIMIZATION                                                                                                   | 31 |

| 4. VALIDATION                                                                                                              | 31 |

| 4.1. WHOLE STRUCTURE COMPARISON                                                                                            | 33 |

| 4.2. REGION-BY-REGION-COMPARISON                                                                                           | 35 |

| 5. CONCLUSION                                                                                                              | 36 |

| REFERENCES                                                                                                                 | 37 |

| II. TOPOLOGY-BASED ACCURATE MODELING OF CURRENT-MODE<br>VOLTAGE REGULATOR MODULES FOR POWER DISTRIBUTION<br>NETWORK DESIGN | 40 |

| ABSTRACT                                                                                                                   | 40 |

| 1. INTRODUCTION                                                                                                            | 41 |

| 2. VRM TOPOLOGY                                                                                                            | 44 |

| 3. TOPOLOGY-BASED GENERIC BEHAVIOR MODEL                                                                                   | 47 |

| 3.1. VOLTAGE CONTROL LOOP                                                                                                  | 47 |

| 3.2. CURRENT CONTROL LOOP                                                                                                  | 50 |

| 3.3. POWER STAGE                                                                                                           | 53 |

| 3.4. MODEL IMPLEMENTATION                                                                                                  | 54 |

| 4. CHARACTERIZATION AND VALIDATION                                                                                         | 56 |

| 4.1. MEASUREMENT SETUP                                                                                                     | 57 |

| 4.2. PARAMETER OPTIMIZATION                                                                                                | 58 |

| 4.3. MODEL VALIDATION                                                                                                      | 62 |

vii

| 5. CONCLUSION                                                                                                               | 68  |

|-----------------------------------------------------------------------------------------------------------------------------|-----|

| APPENDIX                                                                                                                    | 68  |

| REFERENCES                                                                                                                  | 70  |

| III. ACCURATE RECTIFIER CHARACTERIZATION AND IMPROVED<br>MODELING OF CONSTANT POWER LOAD WIRELESS POWER<br>TRANSFER SYSTEMS |     |

| ABSTRACT                                                                                                                    |     |

| 1. INTRODUCTION                                                                                                             | 74  |

| 2. TOPOLOGY AND PREINVESTIGATION                                                                                            |     |

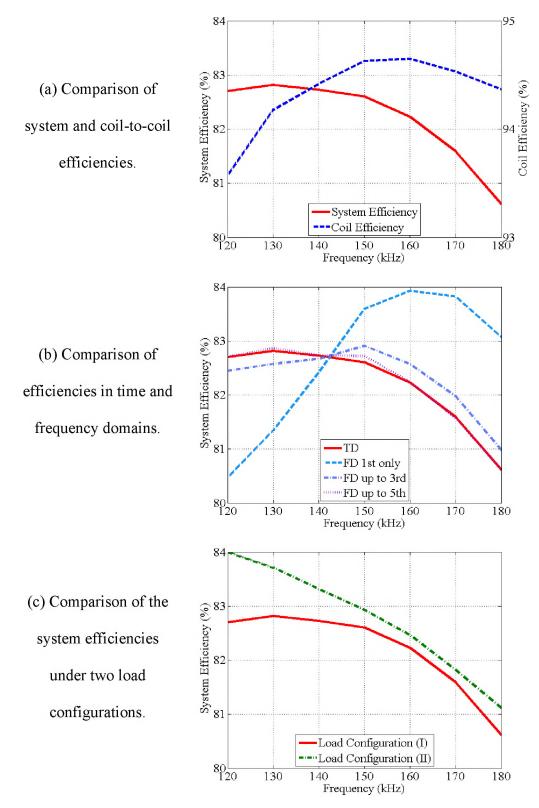

| 2.1. INVESTIGATION OF SYSTEM AND COIL EFFICIENCY                                                                            | 81  |

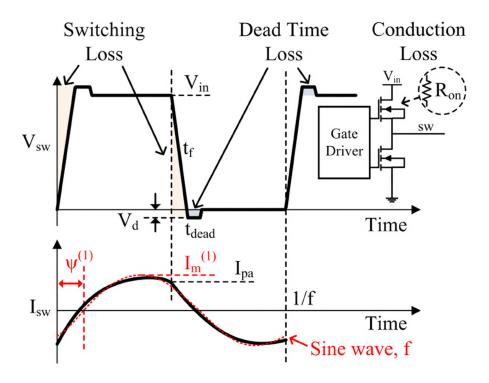

| 2.2. INVESTIGATION OF HARMONIC FREQUENCY                                                                                    | 81  |

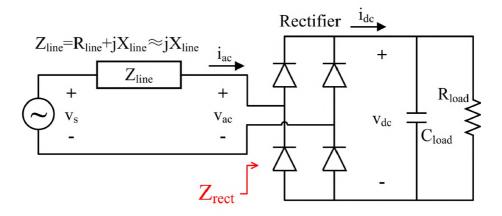

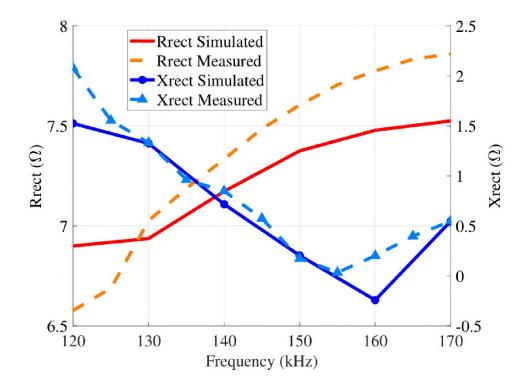

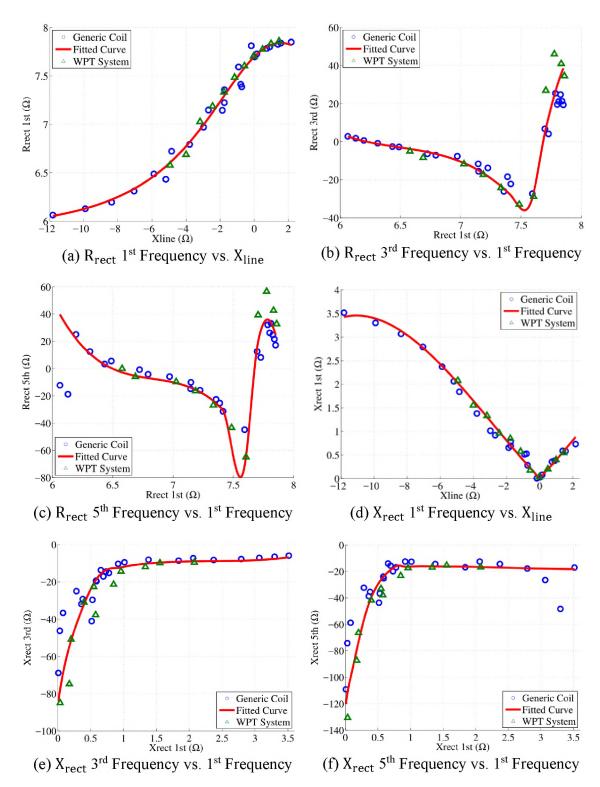

| 2.3. INVESTIGATION OF RECTIFIER IMPEDANCE                                                                                   | 83  |

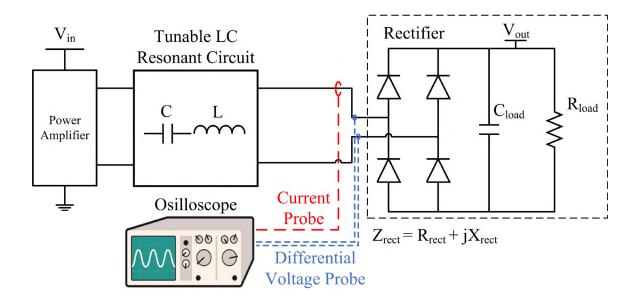

| 3. ACCURATE RECTIFIER CHARACTERIZATION                                                                                      | 84  |

| 4. IMPROVED MODELING AND DESIGN METHODOLOGY                                                                                 |     |

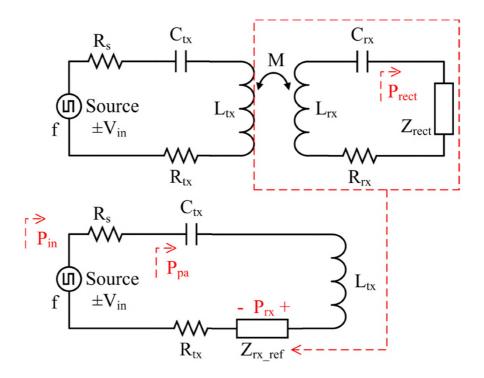

| 4.1. IMPROVED MODELING OF THE WPT SYSTEM                                                                                    |     |

| 4.2. PRACTICAL DESIGN METHODOLOGY                                                                                           | 100 |

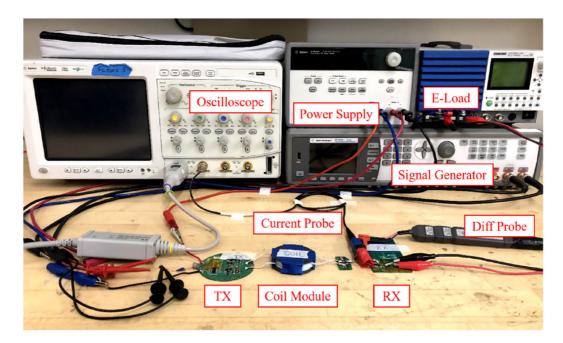

| 5. EXPERIMENT AND VALIDATION                                                                                                | 102 |

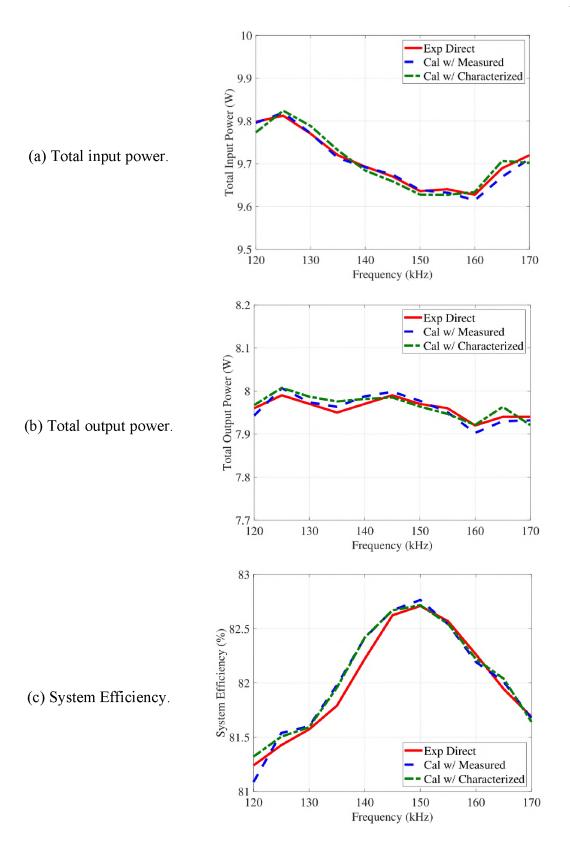

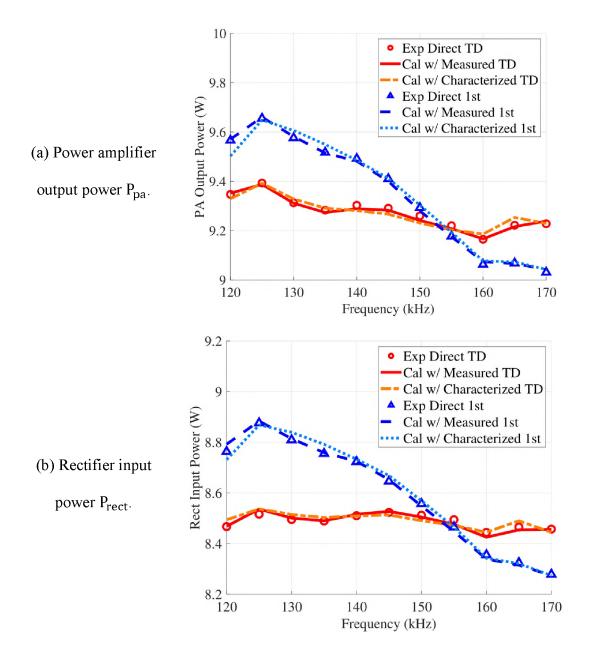

| 5.1. VALIDATION ON CHARACTERIZATION AND MODELING                                                                            | 104 |

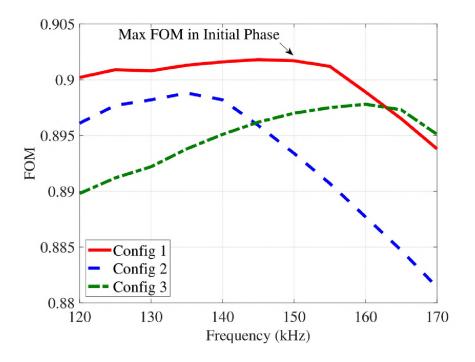

| 5.2. VALIDATION ON DESIGN METHODOLOGY                                                                                       | 108 |

| 6. CONCLUSION                                                                                                               | 110 |

| APPENDIX                                                                                                                    | 110 |

| REFERENCES                                                                                                                  | 113 |

## SECTION

| 2. CONCLUSIONS | 117 |

|----------------|-----|

| BIBLIOGRAPHY   | 119 |

| VITA           | 122 |

## LIST OF ILLUSTRATIONS

| SECTION                                                                          | Page |

|----------------------------------------------------------------------------------|------|

| Figure 1.1. Power delivery paths in electronic devices.                          | 1    |

| PAPER I                                                                          |      |

| Figure 1. Comparison of PCB in mobile platforms and PCB in other platforms       | 9    |

| Figure 2. Major improvements of the proposed pattern-based analytical method     | 12   |

| Figure 3. Localized via pattern around the power via.                            | 13   |

| Figure 4. Formulated via patterns of two categories                              | 14   |

| Figure 5. Magnetic flux though the loop formed by adjacent vias                  | 16   |

| Figure 6. Illustration of the magnetic flux for an arbitrary via pattern         | 18   |

| Figure 7. Arbitrary via patterns for validation                                  | 21   |

| Figure 8. Comparison of via inductance for different patterns and distances.     | 23   |

| Figure 9. Simulation results of via inductance for different via lengths         | 24   |

| Figure 10. Flow diagram of the modeling methodology.                             | 25   |

| Figure 11. Physical geometry and region division of the mobile phone PCB         | 26   |

| Figure 12. The equivalent circuit corresponding to the PCB under investigation   | 27   |

| Figure 13. Selection of the optimal pattern size.                                | 29   |

| Figure 14. Calculation of the equivalent inductance and resistance in one region | 30   |

| Figure 15. Photograph and diagram of the shunt-thru measurement setup            | 32   |

| Figure 16. Comparison of the PDN impedance for the whole PCB structure           | 34   |

| PAPER II                                                                         |      |

|                                                                                  |      |

| Figure 2. System-level PDN performance                                          | 43   |

|---------------------------------------------------------------------------------|------|

| Figure 3. Diagram of an open-loop dc-dc buck converter                          | 45   |

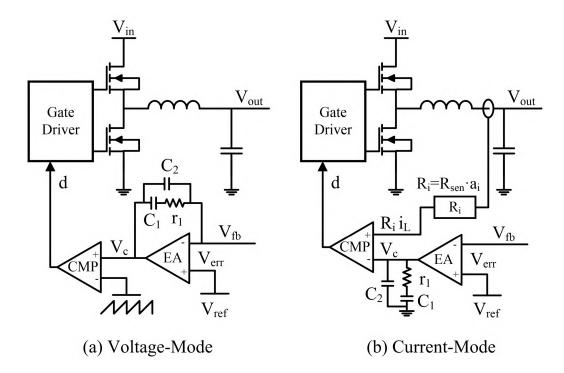

| Figure 4. Typical feedback control topologies in VRM.                           | 45   |

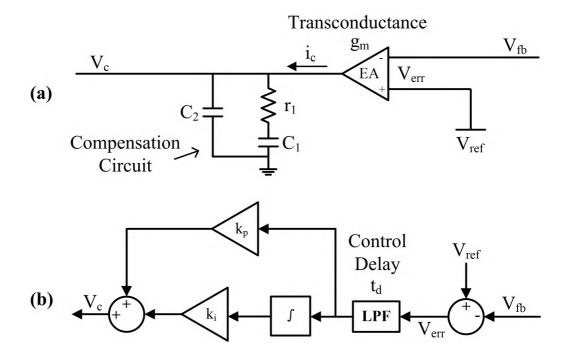

| Figure 5. Modeling of the voltage control loop.                                 | 49   |

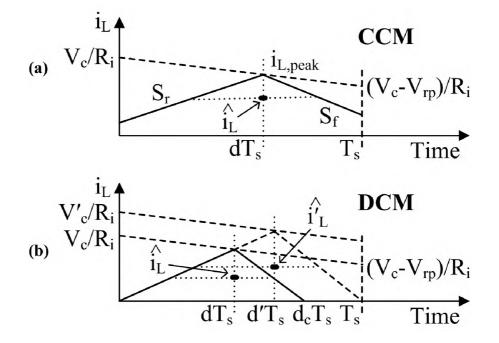

| Figure 6. The inductor current in one switching period                          | 51   |

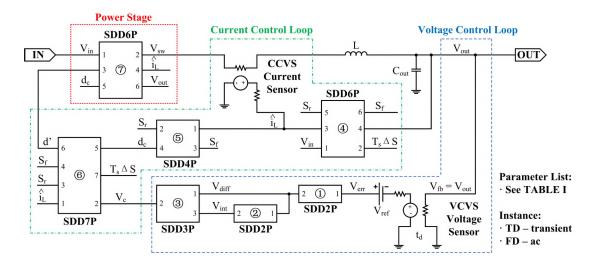

| Figure 7. Schematic of the behavior model in the circuit simulator              | 55   |

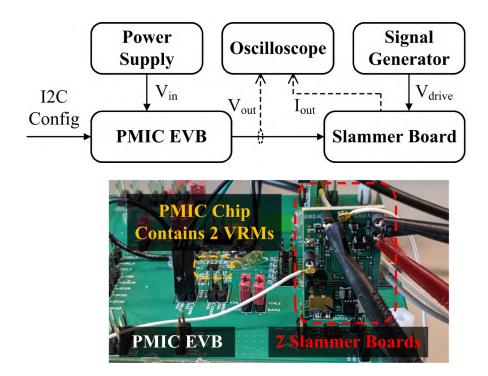

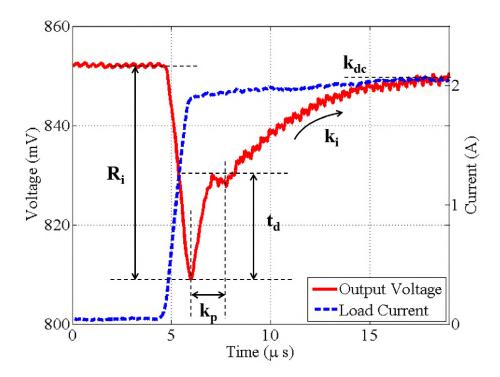

| Figure 8. Diagram and photograph of the measurement setup.                      | 58   |

| Figure 9. Measured voltage and current waveforms for characterization.          | 59   |

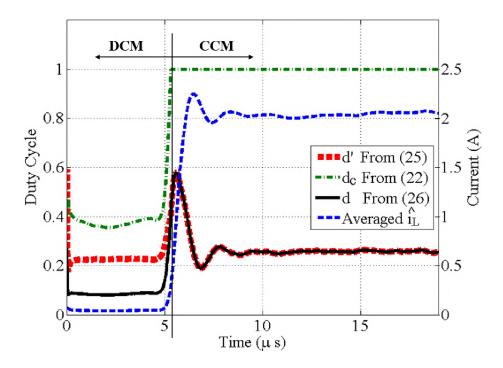

| Figure 10. Validation of the unified equations for the CCM and DCM              | 63   |

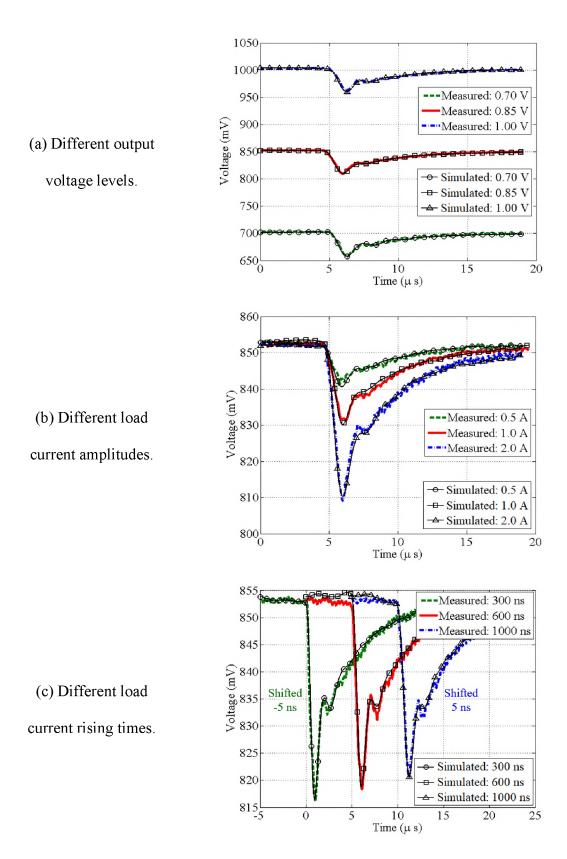

| Figure 11. Comparison of voltage droop waveforms for single-phase VRM           | 65   |

| Figure 12. Comparison of voltage droop waveforms for 3-phase VRM.               | 66   |

| Figure 13. Comparison of simulated and measured impedance for single-phase VRM. | . 67 |

| PAPER III                                                                       |      |

| Figure 1. Typical WPT system with the SS topology                               | 74   |

| Figure 2. Diagram of the circuit model for preinvestigation.                    | 78   |

| Figure 3. Simulation results of the circuit model                               | 80   |

| Figure 4. Circuit model of a full-wave diode rectifier                          | 85   |

| Figure 5. Comparison of simulated and measured rectifier impedance              | 86   |

| Figure 6. Measurement-based rectifier impedance characterization setup          | 89   |

| Figure 7. Rectifier impedance characterization and validation results           | 91   |

| Figure 8. Formulation for the improved modeling of the WPT system               | 94   |

| Figure 9. Time-domain voltage and current waveforms at the switching node       | 97   |

| Figure 10. Flowchart of the design methodology                                  | 101  |

|                                                                                 |      |

| Figure 11. Photograph of the experimental prototype.           | 103 |

|----------------------------------------------------------------|-----|

| Figure 12. Comparison of dc power and efficiency               | 105 |

| Figure 13. Comparison of intermediate ac powers                | 107 |

| Figure 14. FOM calculation in the initial phase.               | 109 |

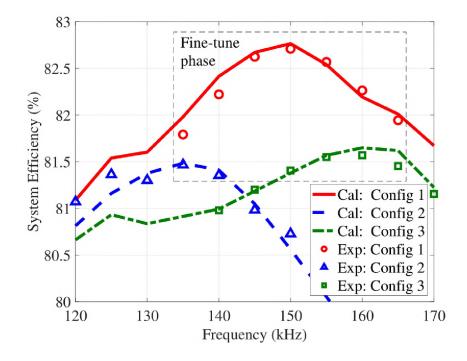

| Figure 15. System efficiency comparison in the fine-tune phase | 109 |

## LIST OF TABLES

| PAPER I                                                              | Page |

|----------------------------------------------------------------------|------|

| Table 1. Region-by-region comparison of parasitic elements.          | 35   |

| PAPER II                                                             |      |

| Table 1. VRM behavior model parameters.                              | 56   |

| Table 2. Characterized single-phase and 3-phase VRM models.          | 61   |

| PAPER III                                                            |      |

| Table 1. Coil parameters for characterization and validation setups. | 89   |

| Table 2. Categories of the WPT system model parameters               | 93   |

## **1. INTRODUCTION**

Power delivery is essential in electronic systems to provide reliable power from voltage sources to load devices. Driven by the ambitious user demands and technology evolutions, the operation voltage of active devices is progressively lower to meet faster and more efficient data processing requirements [1]. In addition, modern integrated circuits (ICs) are dealing with more sophisticated scenarios. As a result, the amplitude and slew rate of load currents keep increasing while the voltage tolerance margin becomes tighter [2]. Therefore, the power delivery design is posed new challenges in efficiency, stability, and impedance optimizations [3-5].

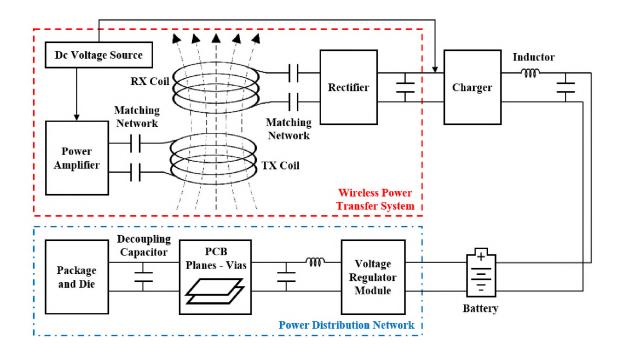

Figure 1.1. Power delivery paths in electronic devices.

As depicted in Figure 1.1, the power delivery paths consist of various components, such as power converters, inductors, decoupling capacitors, power-ground planes in printed circuit boards (PCBs), and vias between PCB layers. It is desired to accurately model all the key components and propose pratical optimization methodologies. In this dissertation, we focus on modeling two common types of power delivery paths: the power distribution network (PDN) and the wireless power transfer (WPT) system. This section introduces the background of the study, the state-of-the-art modeling methods, and the major contributions of the included articles.

#### **1.1. POWER DISTRIBUTION NETWORK**

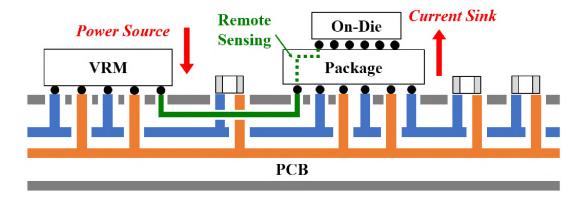

The primary objective of the PDN design is to ensure normal IC operations by minimizing voltage fluctuations. As shown in the blue dot-dashed block of Figure 1.1, the end-to-end PDN has four main parts: (1) voltage regulator module (VRM); (2) PCB-level PDN; (3) package-level PDN; and (4) on-die PDN. The high frequency response is mainly determined by the package/die parasitics (usually above 100 MHz), the middle frequency response is affected by the PCB design (usually 300 kHz  $\sim$  100 MHz), and the low frequency response is typically dominated by the VRM (usually below 300 kHz). With the increasingly complicated load current profile, a successful PDN design needs to optimize all the parts and satisfy the target impedance from dc to high frequencies.

In the past few decades, the modeling of PDN has been extensively studied. For the VRM modeling, the simple first-order linear resistor-inductor (RL) or the second order 4element RL circuits were commonly used to fit the output impedance [6]. However, these discrete passive elements are not able to represent the control loop behaviors of modern

VRMs. A behavior model was proposed by simplying the control loop as a boost converter [7]. This unrealistic simplication has no physical meaning and leads to inaccurate results. A losed-loop mathematical model was developed to calculate the output impedance of VRMs [8], but this approach is purely mathematical and not intuitive to provide insights to improve the VRM design. The VRM vendors could provide encrypted device models using the commercial circuit simulators, such as SIMPLIS [9]. However, this model is only applicable to a specific device and the detailed implementations are confidential. For the PCB-level and package-level PDNs modeling, the fast transmission-line method (TLM) [10] and cavity model method [11-13] were commonly used to model the multilayered PCB. The partial-element equivalent circuit (PEEC) could also be applied to the chippackage hierarchical PDN structures [14-16]. In addition, full-wave electromagnetic modeling methods, including the finite-difference time-domain (FDTD) [17], the finiteelement method (FEM) [18], and the method-of-moments (MOM) [19], were integrated into simulations tools for PCB and package PDN impedance. However, the existing methods may either become impractical or have limitations to model the PDN impedance in some new applications, such as the PCB design in the mobile platform.

#### **1.2. WIRELESS POWER TRANSFER SYSTEM**

WPT is an emerging technology that brings great convenience to charging a large variety of electronic devices. As shown in the red dashed block of Figure 1.1, a typical WPT system consists of four parts: (1) the power amplifier which converts dc voltage to ac power; (2) the transmitter (TX) coil with its matching network; (3) the receiver (RX) coil with its matching network; and (4) the rectifier which inversely regulates ac power to

dc output voltage. There are also industrial standards for WPT applications to improve the safety and interoperability, such as Wireless Power Consortium (WPC) Qi for consumer wireless charging devices and Society of Automotive Engineers (SAE) J2954 for wireless charging vehicles. In addition to the standards and regulations, it is crucial to minimize the power loss and improve the efficiency of WPT systems.

Various studies have been carried out to investigate WPT designs at both coil and system levels. A magnetic coil design method was presented in [20]. Other system parameters, such as the input voltage level, the coil matching networks, the operating frequency, and the load impedance, are also critical for efficiencies. The power transfer efficiency and capability were analyzed under different matching networks in [21] and [22]. However, the output load of the coils was assumed to be purely resistive and the nonlinear effects of the rectifier was not considered. The impacts of rectifier impedance were discussed in [23] and [24], but the authors only focused on the resonant condition and ignored the nonlinearity caused by the line-commutation process. Analytical expressions of coil-to-coil efficiency for both frequency and voltage tuning WPT systems were developed in [25]. However, the derivations were based on the First Harmonic Approximation (FHA), which becomes inaccurate when the system is operating at offresonant frequency or the load quality factor is decreasing. In sum, it is desired to overcome the impractical assumptions of existing methods and develop an accurate system-level model for WPT applications.

#### **1.3. CONTENTS AND CONTRIBUTIONS**

This dissertation presents accurate modeling techniques for PDN and WPT systems. The outlines and contributions of this dissertation are summarized.

In the first paper, a novel pattern-based analytical method for PDN impedance calculation is proposed. This method focuses on the localized patterns formulated by adjacent vias. Therefore, it can easily decompose the complicated PCB structures in mobile platforms and avoid the extensive workload to identify the absolute positions of all the vias and decoupling capacitors at different layers. In addition, the proposed method uses analytical equations to calculate the impedance based on the localized via patterns, which provides more flexibility to optimize the PDN design compared to the complicated numerical solutions, especially in the pre-design stage. A practical modeling methodology is also developed based on the pattern-based analytical model to optimize the PCB-level PDN design. It constructs an equivalent circuit with one-to-one correspondences to the PCB's physical geometry, which is helpful to identify the most critical component contributing to the total impedance and improve the overall PDN design.

In the second paper, a topology-based generic behavior model is developed for the VRM in PDN design. This model includes all the interior topology-level components in the power stage, the voltage control loop, and the current control loop of a VRM device. Thus, it is helpful to provide more insights of the VRM's operations to improve the PDN design. A novel method is proposed to unify the modeling of the continuous and discontinuous current modes (CCM and DCM) for different load conditions. It enables a simplified procedure to implement the current control loop. In addition, a measurement-based characterization method is proposed to optimize the model parameters. This method

can be applied to any provided VRM devices to bypass the confidential concerns. By cascading the proposed VRM model with the PCB-level, the package-level, and the on-die PDN models, a combined PDN analysis integrating the VR control can be established, which is much needed for modern PDN designs.

In the third paper, a system-level model is developed for both dc-to-dc efficiency and power loss of each interior part in WPT systems. This model is capable of deriving the power capability for both the fundamental and higher order harmonics analytically, without the impractical assumptions used by the existing methods. A rectifier characterization method is also proposed to obtain the accurate load impedance for the system-level model. This method is flexible and applicable to any provided rectifier devices. Based on the proposed WPT model, a practical design methodology is introduced to simultaneously optimize multiple system parameters, which greatly accelerates the design process compared with the conventional trial-and-error method. They will become powerful tools to improve the system performance and the thermal design of WPT applications.

#### PAPER

## I. A PATTERN-BASED ANALYTICAL METHOD FOR IMPEDANCE CALCULATION OF THE POWER DISTRIBUTION NETWORK IN MOBILE PLATFORMS

#### ABSTRACT

Power distribution network (PDN) is essential in electronic systems to provide reliable power for load devices. With faster load transient current and lower voltage tolerance margin for the microprocessors in mobile platforms, it is crucial to optimize the PCB design to satisfy the strict target impedance. The conventional modeling methods become impractical in mobile platforms due to the characteristics of high density interconnect PCB and limited layout space. To overcome these issues, a pattern-based analytical method for the PDN impedance calculation is presented. Based on the localized patterns formulated by the relative relationships between the adjacent vias, the parasitic elements are analytically determined for different regions of the entire PCB structure. With the assistance of this method, a practical modeling methodology is developed to construct an equivalent circuit with one-to-one correspondence to the PCB's physical geometry. As a result, the PDN design can be efficiently optimized especially for the pre-design stage to accelerate the development process. Finally, the proposed method is validated through measurements and full-wave simulations using a real mobile phone PCB in production.

#### **1. INTRODUCTION**

Power distribution network (PDN) is essential in electronic systems to provide reliable power for load devices [1]. The primary objective of the PDN design is to ensure normal IC operations by minimizing voltage fluctuations [2]. With the evolution in technologies, modern active devices are being designed with lower voltage to meet faster and more efficient data processing demands. As a result, the current draw and slew rate keep increasing, while the voltage tolerance margin becomes tighter [3]. The mobile platform, being a typical industrial application that follows these trends, is posed serious challenges on the PDN design. Driven by the ambitious user requirements, more aggressive architectures for mobile processors have been deployed to provide significant performance improvements [4]. However, it also results in a fast transient current and a strict target impedance at both dc and higher frequencies [5]. Furthermore, the high density interconnect (HDI) PCB is commonly used in mobile platforms to increase the circuitry density. The complicated interconnect structure brings non-negligible parasitic effects. In addition, the slim form factor of mobile phones limits the layout space and the number of surface mount decoupling capacitors, which causes difficulties to lower the PDN impedance. Thus, the PCB-level PDN design, including the parasitic elements associated with vias/power-ground planes and the decoupling capacitors, becomes more and more critical for mobile platforms.

Over the past few decades, PDN modeling has been extensively investigated. First, full-wave electromagnetic modeling methods were applied to study this problem, including the finite-difference time-domain method (FDTD) [6], the finite-element method (FEM) [7], the method-of-moments (MOM) [8], and the partial-element equivalent circuit (PEEC) [9]–[11]. In addition, a fast and straightforward transmission-line method (TLM) compatible for SPICE implementation was developed to model planes with bypass capacitors [12]–[14]. Another fast method based on the cavity model was commonly used to calculate the input impedance between the power-ground planes [15], [16]. The reduction techniques for cavity model were also proposed to combine parasitic via inductance and generate equivalent circuits [17], [18]. However, due to the characteristics of the PCB in mobile phones, the existing methods either become impractical or have limitations to model the PDN in mobile platforms.

## **PCB in Mobile Platforms**

## **PCB in Other Platforms**

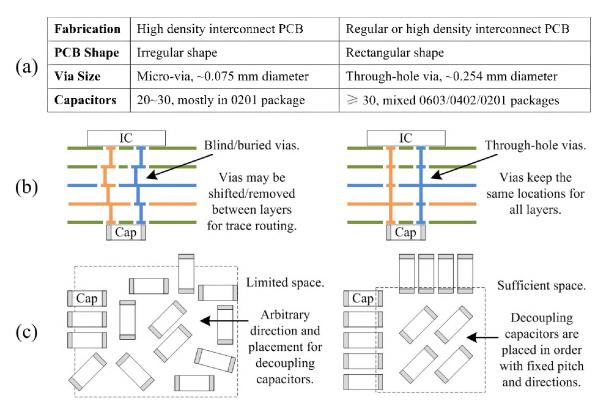

Figure 1. Comparison of PCB in mobile platforms and PCB in other platforms.

Figure 1 compares the PCBs in mobile platforms and other common platforms, such as server or personal computer. The interconnect structure of PCB can be very complicated, especially for the HDI PCB in mobile platforms. As shown in Figure 1 (a), the 0.075 mm diameter micro-vias in mobile platform PCB could result in a huge number of mesh cells for full-wave electromagnetic modeling methods. Hence, the computational burden is heavy and the simulation time is long. Similarly, due to the complexity of the geometry, the TLM model has to use a large number of circuit elements to converge with good simulation accuracy. Figure 1 (b) illustrates the difference in via types. All the vias in mobile platform PCB are blind/buried, while those in regular PCB are through-hole. The cavity model method, which requires the positions of all the vias as the model's ports, is only suitable for the through-hole case. For through-hole vias, the port locations for all the cavities formed by different plane pairs are exactly the same. Thus, the positions only need to be identified once using one cavity, then they can be applied to other cavities for further calculation. However, the blind/buried vias may be removed or shifted between cavities to make room for routing traces within a limited layout space. In this case, the via positions have to be determined separately for every cavity, which significantly increases the workload. In addition, the cavity model method cannot handle the "dog-bone" traces between the blind/buried vias easily. Another factor related to the port locations is depicted in Figure 1 (c). Since the decoupling capacitors should be placed close to the power/ground vias to minimize the parasitic inductance, the positions of decoupling capacitor's power/ground pads can be used to identify the port locations of the cavity model. For the regular PCB with sufficient layout space, the decoupling capacitors are placed in order with fixed pitch size and the same direction, so their positions can be easily determined. But for the mobile platform PCB with limited layout space, the decoupling capacitors are arbitrarily placed with random directions. It is difficult to find the absolute positions for all the decoupling capacitors. Therefore, the cavity model method is impractical to model the PCB in mobile platforms. At last, technical change and new product proliferation have made the mobile phone industry extremely dynamic [19], which places greater demands on accelerating the development process. In spite of the existing methods that only focus on the post-validation stage (PCB layout is completed), the PDN design and modeling in the pre-design stage are rarely investigated. Thus, it is desired to develop a PDN modeling method that is suitable for mobile platforms and applicable in the pre-design stage.

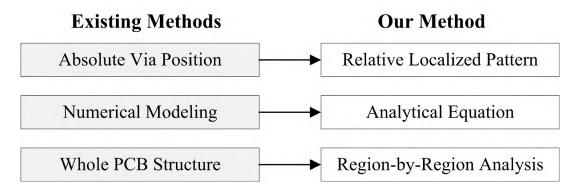

To overcome the limitations of the existing methods for the PCB in mobile platforms, a novel pattern-based analytical method is proposed for PDN impedance calculation. Our method aims to achieve three major improvements, as shown in Figure 2. Firstly, instead of using the absolute positions of all the vias and decoupling capacitors, the parasitic elements are calculated based on the localized patterns. The formulation of pattern and its benefits are discussed in Section 2. Secondly, the complicated numerical solutions lack flexibility in the pre-design stage, so we integrate the analytical equations and introduce a modeling methodology applicable to both pre-design and post-validation stages in Section 3. Thirdly, in addition to modeling the whole PCB structure, our method is capable of conducting region-by-region analysis. These regions still maintain one-to-one correspondences to the physical geometry. So it is helpful to identify the dominant factors in PDN design. In Section 4, our method is validated by both whole structure and regionby-region comparisons using a real mobile phone PCB in production. Section 5 concludes this article.

Figure 2. Major improvements of the proposed pattern-based analytical method.

#### 2. PATTERN FORMULATION AND CALCULATION

A novel approach to calculate the parasitic elements of vias is presented in this section based on the localized via patterns. Compared with the conventional methods using the absolute via positions, our method possesses better flexibility to handle the complicated PCB structures in mobile platforms. The accuracy of our method is validated through RF simulations under various conditions. Since the via pattern is a 2-D structure, the sensitivity of the edge-effect is also investigated.

#### **2.1. PATTERN FORMULATION**

As discussed earlier, the conventional PDN modeling methods become impractical in mobile platforms. It is desired to develop a new modeling method based on the characteristics of the mobile platform PCB. With the limited layout space and tight trace routing restriction, the via-in-pad technique is extensively used for space optimizations. As a result, the relative relationships (distance and angle) between the adjacent vias on the top and bottom layers can be directly obtained from the IC's pinout and decoupling capacitor's footprint. If the blind/buried via is shifted or removed on the internal layers, only the moved via needs to establish new relative distance and angle with its adjacent vias, while the relative relationships of all other vias remain the same. Therefore, the relative distances and angles of the power and ground vias can be easily determined across all layers. Another attribute of the mobile platform PCB, as shown in Figure 1 (a), is the usage of decoupling capacitors with the same package. Restricted by the limited space, almost all the surface mount decoupling capacitors use the small 0201 package. It not only simplifies the PCB layout, but also reduces the variations of the relative distance between the power and ground vias for all the decoupling capacitors.

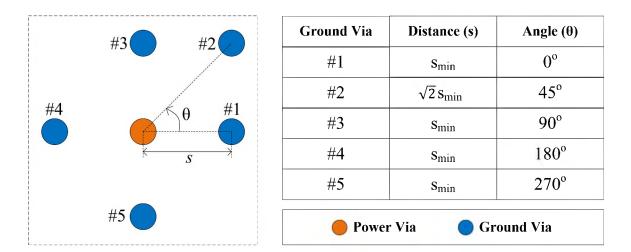

Figure 3. Localized via pattern around the power via.

To represent the relative relationships between the adjacent vias, the localized via pattern is defined to include each power via and its surrounding ground vias. To effectively identify each via's position, the via pattern records the distance s and angle  $\theta$  between each ground via and the centered power via, as illustrated in Figure 3. Note that the zero-degree

axis can be defined from any ground via, because we only care about the relative relationships of the vias. Based on the information in Figure 3, the distance between any two ground vias can be further calculated. Thus, the relative positions of the included vias can be uniquely determined by the via pattern.

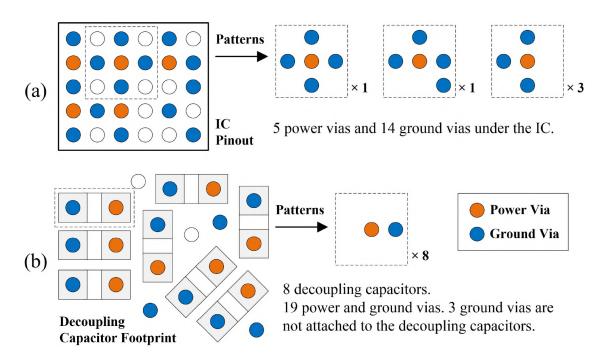

Figure 4. Formulated via patterns of two categories.

Depending on the connected components, there are mainly two categories of vias on the top and bottom layers: the IC vias and the decoupling capacitor vias. Examples of these two categories are depicted in Figure 4.

• For the IC vias in Figure 4 (a), three patterns are formulated based on the IC pinout. Since the pads under IC are well organized with the fixed pitch size, by applying the via-in-pad technique, the distances between the power and ground vias can be easily determined by either 1 or  $\sqrt{2}$  times of the pitch size. The angles are simply multiples of  $45^{\circ}$ .

• For the decoupling capacitor vias in Figure 4 (b), only one pattern is needed to represent all eight decoupling capacitors in the same package. This pattern is formulated by the two vias in each capacitor's power and ground pads, as it provides the least impedance path for the current. Even though these capacitors are randomly placed and the absolute via positions are difficult to determine, the relative distance between the power and ground vias in each pattern is identical because of the same package size.

At last, if the blind/buried vias are moved on the internal layers, the via patterns need to be adjusted accordingly based on the formulated patterns from the top or bottom layers.

This pattern formulation approach assumes the power and ground vias in the IC region are alternately placed, as illustrated in Figure 4 (a). It is because the alternating via placement achieves lower parasitic via inductance than the grouped via placement [20], [21]. As a result, the magnetic flux is confined between the power via and its surrounding ground vias, so the coupling among the power vias can be neglected in practical PCB designs. The examples in Figure 4 demonstrate the flexibility of our pattern-based method to handle the complicated PCB structures in mobile platforms. The localized via patterns serve as the fundamental units to calculate the parasitic via inductance and resistance for the entire PCB structure.

#### **2.2. PATTERN CALCULATION**

One of the most critical parasitic elements in the PDN design is the via inductance. It is caused by the current induced magnetic flux penetrating through the loop formed by the adjacent power and ground vias.

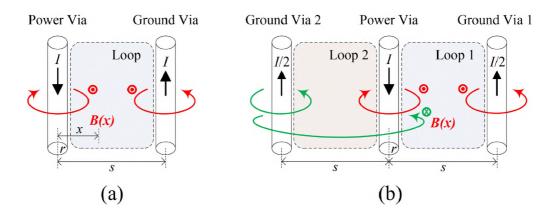

Figure 5 (a) shows a simple case that contains one power via carrying current I and one ground via with the same return current. h is the via length, s is the distance between these two vias, and r is the via radius. Since the power and ground vias are typically placed between paralleled planes, they can be regarded as relatively long straight wires based on the image theory (equivalent to the h  $\gg$  r condition) [22]. From the Biot- Savart law for this case, the magnetic flux density B around the power via can be calculated as:

$$B(x) \approx \frac{\mu I}{2\pi x},\tag{1}$$

where  $\mu$  is the magnetic permeability, and x is the distance to the power via. Note that the return current flowing on the ground via equally contributes to the magnetic flux penetratin through the loop. So the total magnetic flux  $\Phi$  is:

Figure 5. Magnetic flux though the loop formed by adjacent vias.

$$\Phi^{(a)} = 2 \int_0^h \int_r^s B(x) dx dz = \frac{\mu I h}{\pi} \ln\left(\frac{s}{r}\right), \qquad (2)$$

The per-unit-length (PUL) inductance for this simple case is:

$$L_{\rm pul}^{(a)} = \frac{\Phi^{(a)}}{Ih} = \frac{\mu}{\pi} \ln\left(\frac{s}{r}\right). \tag{3}$$

For a more complicated case, the power via may be surrounded by multiple ground vias, as shown in Figure 5 (b). In loop 1, the induced magnetic flux of ground via 2 has an opposite direction from that of ground via 1 and power via. It implies that the presence of ground via 2 reduces the total magnetic flux in loop 1. With the same distance s to the power via, the return current is evenly distributed on the two ground vias (I/2 on each ground via). The total magnetic flux in loop 1 can be calculated as:

$$\Phi_{\text{loop},1}^{(b)} = \frac{3}{2} \int_0^h \int_r^s B(x) dx dz - \frac{1}{2} \int_0^h \int_s^{2s} B(x) dx dz = \frac{\mu I h}{2\pi} \left[ \frac{3}{2} \ln\left(\frac{s}{r}\right) - \frac{1}{2} \ln(2) \right].$$

(4)

Symmetrically, the total magnetic flux in loop 2 is equal to the total magnetic flux in loop 1:  $\Phi_{loop,2}^{(b)} = \Phi_{loop,1}^{(b)}$ . Then, the PUL inductance for this case is determined by the magnetic flux of these two paralleled loops:

$$L_{\text{pul}}^{(b)} = \frac{\Phi_{\text{loop},1}^{(b)}}{\frac{1}{2}Ih} \left\| \frac{\Phi_{\text{loop},2}^{(b)}}{\frac{1}{2}Ih} - \frac{\mu}{2\pi} \left[ \frac{3}{2}\ln\left(\frac{s}{r}\right) - \frac{1}{2}\ln(2) \right].$$

(5)

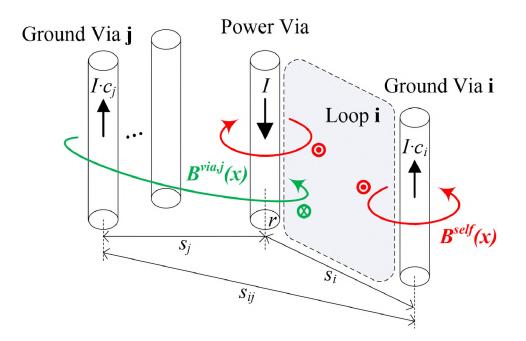

The derivations of (3) and (5) demonstrate the fundamental principles to calculate the PUL inductance based on the two simple cases. However, a real PCB structure may contain more complicated patterns. Therefore, a generalized equation for PUL inductance calculation needs to be developed based on an arbitrary via pattern. Suppose a via pattern has N ground vias and the via radius is r, as illustrated in Figure 6. For each ground via i where  $i \in [1, N]$ , its distance to the power via is  $s_i$ . To maintain the law of current conservation, the total returning current I is distributed among all the ground vias. The ground via with longer distance to the power via shares less current. So a current coefficient  $c_i$  is defined to represent the portion of the current flowing on ground via i, where  $\sum_{i=1}^{N} c_i = 1$ . From (3), the impedance to the ground via is proportional to the logarithm of its distance ln(s). Therefore, the current coefficient  $c_i$  can be estimated based on the inverse logarithmic relationship of the distance as:

$$c_{i} = \frac{1}{\ln(s_{i}) \cdot \sum_{k=1}^{N} \frac{1}{\ln(s_{k})}}.$$

(6)

Figure 6. Illustration of the magnetic flux for an arbitrary via pattern.

Similar with (2), in the loop formed by ground via i and power via, the magnetic flux contributed by these two vias is:

$$\Phi_{\text{loop,i}}^{\text{self}} = (1+c_i) \int_0^h \int_r^{s_i} B^{\text{self}}(x) dx dz$$

=  $\frac{\mu I h}{2\pi} \left[ (1+c_i) \ln \left(\frac{s_i}{r}\right) \right].$  (7)

The magnetic flux induced by other ground vias should also be considered. For a different ground via j where  $j \in [1, N]$  and  $j \neq i$ , its distances to the power via and ground via i are  $s_j$  and  $s_{ij}$ , respectively. The current coefficient of ground via j is  $c_j$ . The magnetic flux, induced by ground via j and penetrates through the loop formed by ground via i and power via, is calculated as the integral of magnetic flux density from  $s_{ij}$  to  $s_j$ :

$$\Phi_{\text{loop,i}}^{\text{via,j}} = c_j \int_0^h \int_{s_{ij}}^{s_j} B^{\text{via,j}}(x) dx dz$$

=  $\frac{\mu I h}{2\pi} \left[ c_j \ln \left( \frac{s_j}{s_{ij}} \right) \right].$  (8)

Note that the sign of  $\Phi_{loop,i}^{via,j}$  is determined by the ratio of  $s_j$  and  $s_{ij}$ , which implies that other ground via's impact on the total magnetic flux is dependent on the relative positions of the vias.

Combining (7) and (8), the total magnetic flux in the loop formed by ground via i and power via is:

$$\Phi_{\text{loop,i}} = \Phi_{\text{loop,i}}^{\text{self}} + \sum_{j=1, j \neq i}^{N} \Phi_{\text{loop,i}}^{\text{via,j}}$$

$$= \frac{\mu I h}{2\pi} \left[ (1+c_i) \ln\left(\frac{s_i}{r}\right) + \sum_{j=1, j \neq i}^{N} c_j \ln\left(\frac{s_j}{s_{ij}}\right) \right].$$

(9)

Applying (9) to all the ground vias, the total magnetic flux in the N loops can be obtained, respectively. Following the same principle of (5), the PUL inductance for the generalized via pattern is calculated based on the magnetic flux of all the loops connected in parallel:

$$L_{\text{pul}} = 1 \Big/ \left( \sum_{i=1}^{N} \frac{c_i I h}{\Phi_{\text{loop,i}}} \right)$$

$$= \frac{\left(\frac{\mu}{2\pi}\right)}{\sum_{i=1}^{N} \frac{c_i}{(1+c_i) \ln\left(\frac{s_i}{r}\right) + \sum_{j=1, j \neq i}^{N} c_j \ln\left(\frac{s_j}{s_{ij}}\right)}.$$

(10)

Another parasitic element is the via resistance, which has a secondary effect on the PDN impedance mainly at dc and the resonant frequencies. Depending on the frequency f, the skin depth  $\delta$  is calculated as:

$$L_{\text{pul}} = 1 \Big/ \left( \sum_{i=1}^{N} \frac{c_i I h}{\Phi_{\text{loop,i}}} \right)$$

$$= \frac{\left(\frac{\mu}{2\pi}\right)}{\sum_{i=1}^{N} \frac{c_i}{(1+c_i) \ln\left(\frac{s_i}{r}\right) + \sum_{j=1, j \neq i}^{N} c_j \ln\left(\frac{s_j}{s_{ij}}\right)}.$$

(11)

where  $\rho$  is the resistivity and  $\mu$  is the permeability of the conductor material. For a standard-size via when the via radius  $r \gg \delta$ , the effective conduction area  $A_{eff}$  can be determined using a simplified equation:  $A_{eff} = \pi [r^2 - (r - \delta)^2]$ . However, the dimension of the micro-via used in mobile platform PCB is comparable with the skin depth within our frequency range of interest (300 kHz ~ 300 MHz). Hence, a more accurate method using the "truncated exponential decay" approach [23] is used to derive the modified skin depth  $\delta'$  for the via resistance calculation:

$$\delta' = \delta(1 - e^{-\frac{r}{\delta}}). \tag{12}$$

The asymptotically correct formula for the effective area is:

$$A_{\text{eff}} = \pi [2r\delta' - \delta'^2] \cdot (1+y), \qquad (13)$$

where (1 + y) is a divisor correction coefficient based on a Modified Lorentzian function y. The fitted expression of y is also provided in [23]:

$$y = \frac{0.19}{(1+0.27 \cdot [z^{1.83} - z^{-0.99}]^2)^{1.09}}$$

$$z = 0.62 \frac{r}{\delta}.$$

(14)

Finally, the PUL resistance for a single via is calculated as:

$$R_{\rm pul} = \frac{\rho}{A_{\rm eff}}.$$

(15)

Figure 7. Arbitrary via patterns for validation.

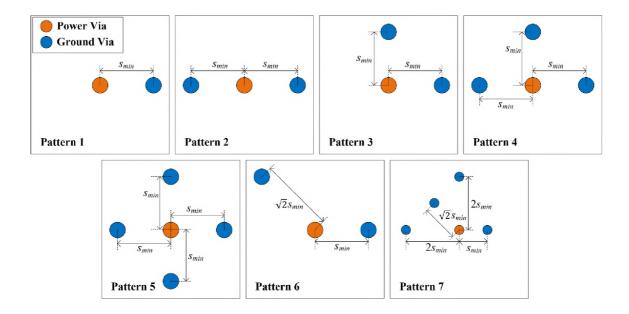

#### 2.3. SIMULATION STUDIES ON ACCURACY AND EDGE-EFFECT

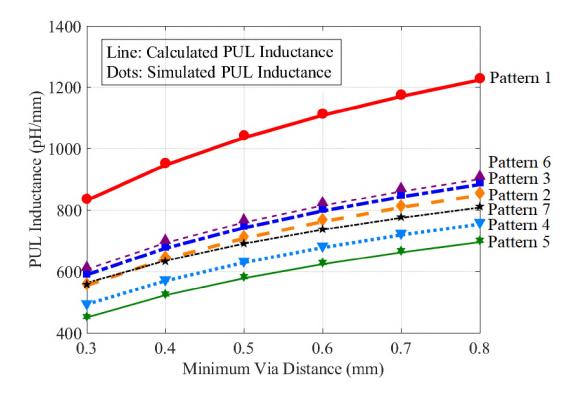

The pattern-based analytical equation (10) can be applied to an arbitrary via pattern. Here a commercial RF simulation tool, ANSYS 2D Extractor, was used to validate this equation for various via patterns and distances. As illustrated in Figure 7, seven patterns were built in the simulation tool with different numbers and positions of the ground vias. The via diameter was 0.075 mm. The minimum via distance  $s_{min}$  was sweeping from 0.3 mm to 0.8 mm for all the patterns. These values were chosen based on the typical specification of the HDI PCB in mobile platforms. The simulated PUL via inductance, obtained using the ANSYS 2D Extractor, and the calculated PUL via inductance, obtained based on the proposed analytical equation, are compared in Figure 8. Good correlations are observed for all the cases where the largest difference between the calculated and simulated PUL inductances is 9.54 pH/mm (with a maximum discrepancy of 1.1%). It verifies the accuracy of our proposed analytical equation for an arbitrary via pattern. Equation (15) for the PUL via resistance is validated in Section 4.2.

Since the pattern is a 2-D structure, the vias are equivalently treated as relatively long wires during the calculation of the PUL parasitic elements. Therefore, the edge-effect, such as the fringing fields at the end of the vias or the proximity to the plane edges, may affect the accuracy of our method. To investigate the impact of the edge-effect, another 3-D electromagnetic field simulation tool, CST Studio, was used to simulate the via inductance of different lengths. "Pattern 1", "Pattern 5", and "Pattern 7" in Figure 7 were evaluated to check the smallest, median, and largest PUL inductance cases. The minimum via distance s min was fixed to 0.35 mm and the plane size was 2 mm by 2 mm. As shown in Figure 9, a port was added to the power via, the ground via(s) were shorted to provide a return path for the injected current. The minimum via distance s min was fixed to 0.35 mm. The via length varied from 0.02 mm to 0.10 mm. The edge-effect causes additional parasitic PUL inductance when the via length is smaller than 0.04 mm. For a mobile platform PCB, the typical dielectric thickness between layers is  $0.045 \sim 0.060$  mm. In other words, the error introduced by the edge-effect is negligible in this application. The modeling of the edge-effect is beyond the scope of this article.

Figure 8. Comparison of via inductance for different patterns and distances.

Figure 9. Simulation results of via inductance for different via lengths.

### **3. PDN MODELING METHODOLOGY**

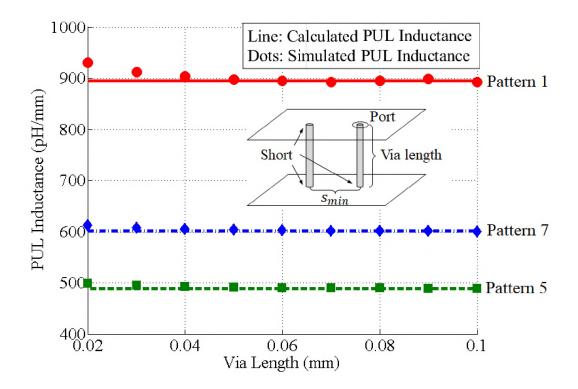

With the assistance of this pattern-based analytical method, a practical modeling methodology is proposed to calculate the PDN impedance of the entire PCB. The flow diagram is depicted in Figure 10. On the left side of this diagram, the "Via Pattern Database" indicates that the via patterns from the previous projects can be stored and adapted for future designs. It is not only useful to determine the impedance of a known PCB structure, but also helpful to improve the layout especially in the pre-design stage. The dashed arrow lines represent the interactions with this database. On the right side of this diagram, the main workflow is divided into four steps. The first three steps, including "(1) PCB division", "(2) pattern identification", and "(3) circuit reconstruction", construct

an equivalent circuit with one-to-one correspondences to the PCB physical geometry. Then, the PDN impedance can be obtained from the circuit simulations. If the target impedance is not satisfied for the initial design, an iteration process is conducted to further improve the impedance in the "(4) design optimization" step.

Figure 10. Flow diagram of the modeling methodology.

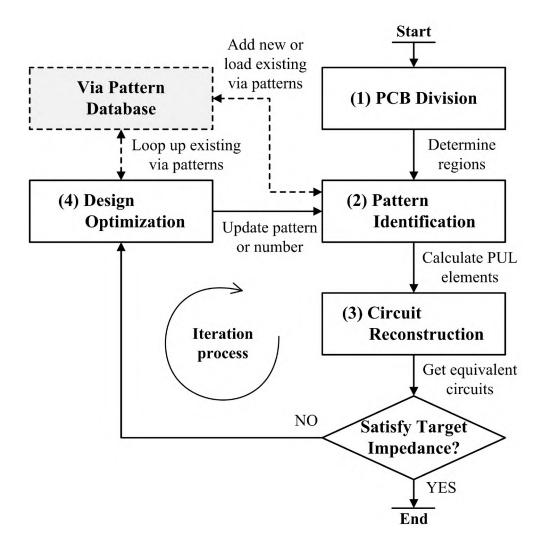

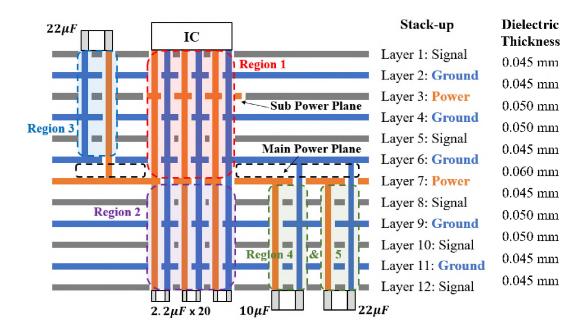

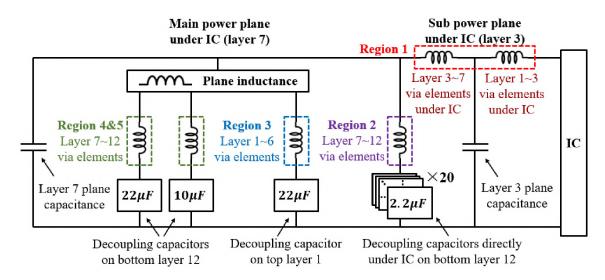

Following the modeling methodology, a real mobile phone PCB, illustrated in Figure 11, is investigated as an example. Among the total 12 layers, the 7<sup>th</sup> layer is the main power plane connecting all the decoupling capacitors and IC, and the 3<sup>rd</sup> layer is the sub power plane to unify the voltage under the IC. The ground planes are located on the  $2^{nd}$ , 4<sup>th</sup>, 6<sup>th</sup>, 9<sup>th</sup>, and 11<sup>th</sup> layers. The copper thickness is 0.023 mm for the top and bottom layers, and 0.018 mm for all the internal layers. There are 0402 package (22  $\mu$ F, 10  $\mu$ F) and 0201 package (2.2  $\mu$ F) decoupling capacitors placed on both the top and bottom layers. All of the 0201 package capacitors are placed directly under the IC, while the other 0402 package capacitors are placed besides the IC due to the space limitation.

Figure 11. Physical geometry and region division of the mobile phone PCB.

Figure 12. The equivalent circuit corresponding to the PCB under investigation.

# **3.1. PCB DIVISION**

Seen at the input port of the load IC, the current in the PDN is always flowing along the power vias from the decoupling capacitors and returning along the nearby ground vias. By tracing the current flow path, the multilayered PCB structure can be divided vertically into different regions between the main power plane and the ground plane. For the target PCB in Figure 11, there are five regions associated with the physical geometry. "Region 1" and "Region 2" correspond to the vias directly under the IC from the top and bottom layers to the main power plane, respectively. "Region 2" also connects to the multiple 2.2  $\mu$ F decoupling capacitors on the bottom layer. "Region 3", "Region 4", and "Region 5" correspond to the vias between the 0402 package decoupling capacitors and the main power plane. Since these capacitors are located besides the IC, we should include the plane inductance to reflect the current distribution on the main power plane. The mutual inductance among different regions are negligible because the distance between regions is relatively larger than the distance from the power via to the nearby ground vias [24]. Within each region, the parasitic elements of the vias can be merged into the equivalent inductance and resistance. The equivalent circuit of the entire PCB structure is depicted in Figure 12.

## **3.2. PATTERN IDENTIFICATION**

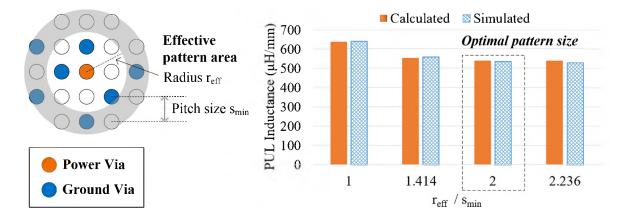

The pattern formulations for the IC and decoupling capacitor vias are introduced in Section 2. Accordingly, the patterns in "Region 1" are identified based on the IC pinout, and the patterns in other regions are identified based on the packages of the decoupling capacitors. Furthermore, an optimal pattern size needs to be selected for practical purposes. It is because a larger pattern includes more nearby ground vias, which leads to a more accurate result but also increases the complexity in pattern formulation. For the IC region shown in Figure 13, the pitch size s min is fixed to 0.35 mm and the radius of the effective pattern area r eff is investigated using 1,  $\sqrt{2}$ , 2, and  $\sqrt{5}$  times  $s_{min}$ . When  $r_{eff} = s_{min}$ , only two ground vias are included in this pattern, but it yields a falsely high PUL via inductance of 635 µH/mm. By increasing  $r_{eff}$ , the PUL via inductance converges to 537 µH/mm. The optimal pattern size is achieved when  $r_{eff} = 2s_{min}$  as it provides an accurate result with the simplest structure. This experimental-based conclusion can be verified using other via patterns. Therefore, it is suggested to include the ground vias whose relative distance is within two pitch sizes into the pattern.

Figure 13. Selection of the optimal pattern size.

# **3.3. CIRCUIT RECONSTRUCTION**

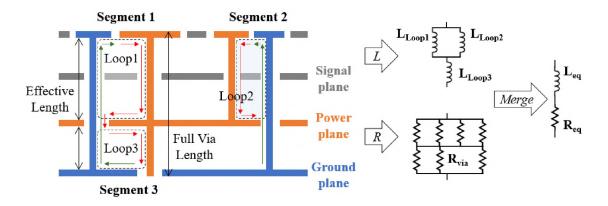

This step aims to determine all the components of the equivalent circuit in Figure 12. The PUL via inductance and resistance of the identified patterns can be calculated based on the analytical equations (10) and (15). Then, the inductance of a via segment is obtained by multiplying the PUL inductance by the effective length of this segment, and the resistance is obtained by multiplying the PUL resistance by the full segment length. Compared with the full length, the effective length excludes the layer thickness of the power and ground planes. It is because the inductance is related to the loop formed by the adjacent vias. The signal planes can also be ignored since they do not affect the impedance of the power nets. As illustrated in Figure 14, the inductance and resistance of multiple segments in the same region can be merged depending on their series or parallel relationship. As a result, one equivalent inductance and one resistance are generated to represent the parasitic elements for each region.

Figure 14. Calculation of the equivalent inductance and resistance in one region.

The plane capacitance is insignificant for the mobile phone PCB because of the limited layout space, so the simple parallel-plate capacitor equation is sufficient to estimate the plane capacitance:

$$C_{\text{plane}} = \frac{\varepsilon A}{d},\tag{16}$$

where  $\varepsilon$  is the dielectric permittivity, A is the plane area, and d is the dielectric thickness between the plane pair. The total inductance between the main power plane pair ("Plane inductance" in Figure 12) is obtained based on the cavity model [15]–[18]. By merging the vias of the same region, the cavity model can be simplified by setting one port located at the center of each region instead of identifying the absolute positions for all the vias. At last, "Region 2", "Region 3", "Region 4", and "Region 5" connect to the decoupling capacitors on the top and bottom layers. For high accuracy, the SPICE model of the decoupling capacitor is employed in the circuit simulation since it includes both the parasitics, such as the equivalent series inductance/resistance (ESL/ESR) and the derating effects. Similar with the via inductance and resistance, the decoupling capacitors in the same region are in parallel and can be merged together.

#### **3.4. DESIGN OPTIMIZATION**

With the constructed equivalent circuit, the PDN impedance can be assessed by the circuit simulations. If the target impedance is not satisfied, an iteration process is conducted to further optimize the PDN design. The divided regions are helpful to identify the most critical component contributing to the total impedance. A common optimization method is to apply more decoupling capacitors, which can be easily implemented as increasing the number of the decoupling capacitor via pattern in our modeling methodology. Adding more ground vias is another feasible solution to reduce the parasitic via inductance, which is equivalent to changing the via pattern in design. The proposed pattern-based analytical equation is capable of predicting the PUL via inductance accurately, in order to provide quantitative guidance for the system designer. For instance, Figure 8 shows the PUL inductance with different via distances of the seven patterns in Figure 7. According to the calculated results, the designer is able to achieve lower impedance level with better utilization of the layout space for the new design. So our modeling methodology is especially useful in the pre-design stage when the PCB layout is not fully completed.

## 4. VALIDATION

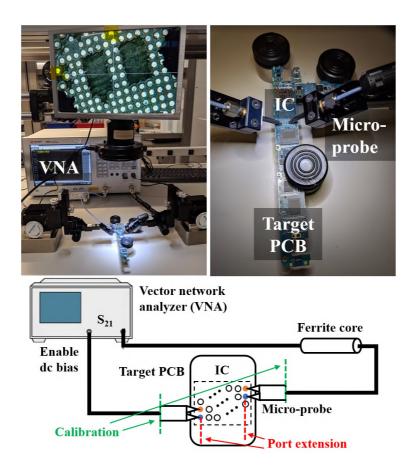

The PDN impedance of the mobile phone PCB in Figure 11 was measured to validate our modeling methodology. The shunt-thru method was used to achieve the accurate m $\Omega$  impedance measurement [25], as depicted in Figure 15. By landing the two micro-probes (PacketMicro GR201504) between the IC's power and ground pads, the transmission coefficient S<sub>21</sub> was measured by the vector network analyzer (Keysight

E5061B). Then, the impedance of the entire PCB structure can be derived from the measured S-parameter:  $Z_{PDN} = 25 \cdot S_{21}(1 - S_{21})$ . To avoid the mutual coupling between the micro-probes, the landing locations were separated at the opposite sides of the IC pinout. Full 2-port calibration and port extension were applied to move the reference planes to the micro-probe tips. Ferrite cores were attached to the test cable to eliminate the measurement error caused by the cable ground loop [26]. To include the derating effects of the decoupling capacitors, 0.75 V dc bias voltage was enabled in the vector network analyzer. The frequency range in this measurement was from 300 kHz to 300 MHz.

Figure 15. Photograph and diagram of the shunt-thru measurement setup.

The layout of this mobile phone PCB was also imported into a board-level electromagnetic field solver, Cadence Sigrity PowerSI. In addition to the total PDN impedance, the parasitic inductance and resistance of each region were simulated by manually setting the ports at different locations and layers. As a result, the accuracy of our modeling methodology can be validated by both whole structure and region-by-region comparisons.

# 4.1. WHOLE STRUCTURE COMPARISON

The impedance for the whole structure is contributed by all the components embedded in the PCB. However, different components have dominant effects at different frequencies. For example, capacitance usually dominates at a lower frequency and the via inductance is typically critical at a higher frequency. Therefore, it is desired to achieve good correlations with the simulations and measurements for the entire frequency range.

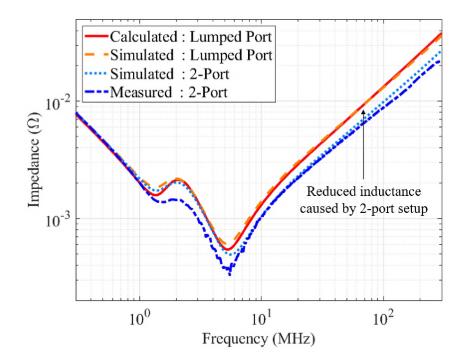

The calculated result based on our modeling methodology was using one lumped port grouping all the IC vias on the top layer. However, it is unrealistic to implement this lumped port in the measurement setup. As discussed above, the measured result was converted from the 2-port S-parameter, which resulted in lower IC via inductance and caused lower impedance at higher frequencies. So the calculated and measured results could not be compared directly. To solve this issue, two simulated results obtained using the Cadence Sigrity PowerSI were added with the lumped port and 2-port configurations, respectively. Then, the four types of results could be divided into two groups: the lumped port group including the calculated and simulated results; and the 2-port group including the simulated and measured results. Two criteria are evaluated to validate our modeling method: the resonant frequencies and the magnitude of the PDN impedance. As shown in Figure 16, the impedance curves in the same configuration group agree well with each other. The three resonant frequencies, located at 1.5 MHz, 2.0 MHz, and 5.5 MHz, are all accurately captured with less than 100 KHz difference. The maximum variations of the impedance magnitude are within 0.26 m $\Omega$  and 0.33 m $\Omega$  for the lumped and 2-port configurations, respectively. Between the two groups, we can indirectly compare the calculated and measured results with respect to the difference of the two simulated impedance. The good correlations across the entire frequency range validates the accuracy of our modeling methodology for the whole PCB structure.

Figure 16. Comparison of the PDN impedance for the whole PCB structure.

| Location   | Parasitic  | Calculation | Simulation |

|------------|------------|-------------|------------|

| Region 1   | Inductance | 2.10 pH     | 2.39 pH    |

| Layer 1~3  | Resistance | 0.05 mΩ     | 0.06 mΩ    |

| Region 1   | Inductance | 4.81 pH     | 5.48 pH    |

| Layer 3~7  | Resistance | 0.14 mΩ     | 0.14 mΩ    |

| Region 2   | Inductance | 13.51 pH    | 12.93 pH   |

| Layer 7~12 | Resistance | 0.20 mΩ     | 0.19 mΩ    |

| Region 3   | Inductance | 289 pH      | 285 pH     |

| Layer 1~6  | Resistance | 2.95 mΩ     | 4.10 mΩ    |

| Region 4   | Inductance | 312 pH      | 312 pH     |

| Layer 7~12 | Resistance | 3.62 mΩ     | 4.00 mΩ    |

| Region 5   | Inductance | 242 pH      | 240 pH     |

| Layer 7~12 | Resistance | 3.62 mΩ     | 4.00 mΩ    |

Table 1. Region-by-region comparison of parasitic elements.

# 4.2. REGION-BY-REGION-COMPARISON

Since the proposed modeling methodology is built on the basis of the divided regions, it is important to validate the equivalent inductance and resistance for each region. The calculated and simulated parasitic elements for different regions are compared in Table 1. "Region 1" is split into two parts because of the sub power plane on the layer 3. Other regions have only one set of equivalent inductance and resistance. The via resistance are obtained at the 6 MHz resonant frequency.

The error between the calculated and simulated parasitic inductance is within 12.2% for the IC vias and within 1.4% for the decoupling capacitor vias. The good agreement shows this methodology can not only estimate the via inductance accurately, but also identify the critical components contributing to the total PDN impedance. The calculated parasitic resistance generally correlate well with the simulated results (with a

discrepancy of 9.5%), except for "Region 3" (with a discrepancy of 28.0%). It is because there are multiple paralleled vias laid closely in the same pad of the decoupling capacitor in this region. Thus, the increased proximity effect causes higher ac resistance. However, the impedance curve is not significantly affected since the via resistance has a secondary impact mainly at dc and the resonant frequencies. So the current accuracy level for the resistance calculation is acceptable. The proximity effect modeling is not the focus of this article and will be discussed in future studies.

# 5. CONCLUSION

In this article, the limitations of the existing PDN modeling methods are discussed with the focus on mobile platform applications. To overcome these issues, a novel patternbased analytical method is proposed for the impedance calculation. By utilizing the relative relationships between the adjacent vias, the localized via patterns are formulated based on the physical geometry. Then, the parasitic via inductance and resistance are analytically derived for arbitrary via patterns. It can be shown that our method has better flexibility to handle the complicated PCB structure in mobile platforms. In addition, a practical modeling methodology is developed to model and guide the PDN design. With the capability of accurate and layout-free impedance estimation, this methodology is especially useful for the pre-design stage to accelerate the development process. Finally, the proposed analytical equations and the modeling methodology have been extensively validated through the measurements and simulations on a real mobile phone PCB. Good agreements can be observed from both whole structure and region-by-region comparisons.

# REFERENCES

- M. Swaminathan, J. Kim, I. Novak, and J. P. Libous, "Power distribution networks for system-on-package: Status and challenges," IEEE Transactions on Advanced Packaging, vol. 27, no. 2, pp. 286–300, 2004.

- [2] W. D. Becker, J. Eckhardt, R. W. Frech, G. A. Katopis, E. Klink, M. F. McAllister, T. G. McNamara, P. Muench, S. R. Richter, and H. Smith, "Modeling, simulation, and measurement of mid-frequency simultaneous switching noise in computer systems," IEEE Transactions on Components, Packaging, and Manufacturing Technology: Part B, vol. 21, no. 2, pp. 157–163, 1998.

- [3] X. Zhou, P.-L. Wong, P. Xu, F. C. Lee, and A. Q. Huang, "Investigation of candidate vrm topologies for future microprocessors," IEEE Transactions on Power Electronics, vol. 15, no. 6, pp. 1172–1182, 2000.

- [4] M. Halpern, Y. Zhu, and V. J. Reddi, "Mobile CPU's rise to power: Quantifying the impact of generational mobile cpu design trends on performance, energy, and user satisfaction," in 2016 IEEE International Symposium on High Performance Computer Architecture (HPCA). IEEE, 2016, pp. 64–76.

- [5] L. D. Smith, R. E. Anderson, D. W. Forehand, T. J. Pelc, and T. Roy, "Power distribution system design methodology and capacitor selection for modern cmos technology," IEEE Transactions on Advanced Packaging, vol. 22, no. 3, pp. 284– 291, 1999.

- [6] I. Erdin and M. Nakhla, "Mixed circuit/electromagnetic analysis of field coupling to high speed interconnects in inhomogenous medium," in 1999 IEEE International Symposium on Electromagnetic Compatability. Symposium Record (Cat. No. 99CH36261), vol. 1. IEEE, 1999, pp. 446–449.

- [7] M. Feliziani and F. Maradei, "Circuit-oriented fem: Solution of circuit-field coupled problems by circuit equations," IEEE Transactions on Magnetics, vol. 38, no. 2, pp. 965–968, 2002.

- [8] E.-X. Liu, X. Wei, Z. Z. Oo, E.-P. Li, and L.-W. Li, "Modeling of advanced multilayered packages with multiple vias and finite ground planes," in 2007 IEEE Electrical Performance of Electronic Packaging. IEEE, 2007, pp. 275–278.

- [9] A. E. Ruehli, "Inductance calculations in a complex integrated circuit environment," IBM journal of research and development, vol. 16, no. 5, pp. 470–481, 1972.

- [10] A. E. Ruehli and P. A. Brennan, "Efficient capacitance calculations for threedimensional multiconductor systems," IEEE Transactions on Microwave Theory and Techniques, vol. 21, no. 2, pp. 76–82, 1973.

- [11] A. E. Ruehli, "Equivalent circuit models for three-dimensional multiconductor systems," IEEE Transactions on Microwave Theory and Techniques, vol. 22, no. 3, pp. 216–221, 1974.

- [12] P. Johns, "The art of modelling," Electronics & Power, vol. 25, no. 8, pp. 565–569, 1979.

- [13] W. J. Hoefer, "The transmission-line matrix method-theory and applications," IEEE Transactions on Microwave Theory and Techniques, vol. 33, no. 10, pp. 882– 893, 1985.

- [14] K. Lee and A. Barber, "Modeling and analysis of multichip module power supply planes," IEEE Transactions on Components, Packaging, and Manufacturing Technology: Part B, vol. 18, no. 4, pp. 628–639, 1995.

- [15] J. Kim, L. Ren, and J. Fan, "Physics-based inductance extraction for via arrays in parallel planes for power distribution network design," IEEE Transactions on Microwave Theory and Techniques, vol. 58, no. 9, pp. 2434–2447, 2010.

- [16] J. Kim, J. Fan, A. E. Ruehli, J. Kim, and J. L. Drewniak, "Inductance calculations for plane-pair area fills with vias in a power distribution network using a cavity model and partial inductances," IEEE Transactions on Microwave Theory and Techniques, vol. 59, no. 8, pp. 1909–1924, 2011.

- [17] J. Kim, K. Shringarpure, J. Fan, J. Kim, and J. L. Drewniak, "Equivalent circuit model for power bus design in multi-layer pcbs with via arrays," IEEE Microwave and Wireless Components Letters, vol. 21, no. 2, pp. 62–64, 2011.

- [18] K. Shringarpure, S. Pan, J. Kim, B. Achkir, B. Archambeault, J. Drewniak, and J. Fan, "Formulation and network reduction to a physics based model for analysis of the power distribution network in a production level multi-layered printed circuit board," IEEE Transactions on Electromagnetic Compatibility, vol. 58, no. 3, pp. 849–858, 2016.

- [19] G. Cecere, N. Corrocher, and R. D. Battaglia, "Innovation and competition in the smartphone industry: Is there a dominant design?" Telecommunications Policy, vol. 39, no. 3-4, pp. 162–175, 2015.

- [20] K. Shringarpure, "Printed circuit board power distribution network modeling, analysis and design, and, statistical crosstalk analysis for high speed digital links," 2015.

- [21] B. Archambeault, B. Zhao, K. Shringapure, and J. Drewniak, "Design tips," IEEE Electromagnetic Compatibility Magazine, vol. 4, no. 2, pp. 106–107, 2015.

- [22] T. H. Hubing, T. P. Van Doren, and J. L. Drewniak, "Identifying and quantifying printed circuit board inductance," in Proceedings of IEEE Symposium on Electromagnetic Compatibility. IEEE, 1994, pp. 205–208.

- [23] D. W. Knight, "Practical continuous functions for the internal impedance of solid cylindrical conductors," G3YNH info, 2016. [Online]. Available: http://www. g3ynh.info/zdocs/comps/Zint.pdf.

- [24] B. Zhao, "A physics-based approach for power integrity in multi-layered pcbs," Master's thesis, Missouri University of Science and Technology, 2017.

- [25] Keysight. (2014) Evaluating dc-dc converters and pdn with the e5061b lf-rf network analyzer. [Online]. Available: http://literature.cdn.keysight.com/litweb/ pdf/5990-5902EN.pdf.

- [26] I. Novak, Y. Mori, and M. Resso, "Accuracy improvements of pdn impedance measurements in the low to middle frequency range," Proc. DesignCon 2010, pp. 1–4, 2010.

# II. TOPOLOGY-BASED ACCURATE MODELING OF CURRENT-MODE VOLTAGE REGULATOR MODULES FOR POWER DISTRIBUTION NETWORK DESIGN

## ABSTRACT

Power distribution network (PDN) is essential in electronic systems to provide reliable power for load devices. Thus, modeling of PDNs in printed circuit board and package has been extensively studied in the past few decades. However, the voltage regulator module (VRM), which serves as the ultimate voltage source, was not thoroughly investigated. The conventional VRM model is either represented by a simple resistorinductor equivalent circuit or implemented with simple assumptions. It lacks of accuracy for modern VRM devices. In this work, a generic behavior model, including both the power stage and control loops, is developed for the current-mode buck VRM. A novel method is also proposed to synthesize the continuous and discontinuous conduction modes for transient load responses. Through the measurement-based characterization, the model parameters are optimized to match with the actual design. Furthermore, this model can be applied to both the time-domain and frequency-domain circuit simulations to predict the voltage droop and output impedance, respectively. The accuracy of the model is validated using an evaluation board containing the single-phase and multiphase VRMs. It is demonstrated that the proposed model for VRM with control loops can be easily integrated into the PDN analysis and optimization.

#### **1. INTRODUCTION**

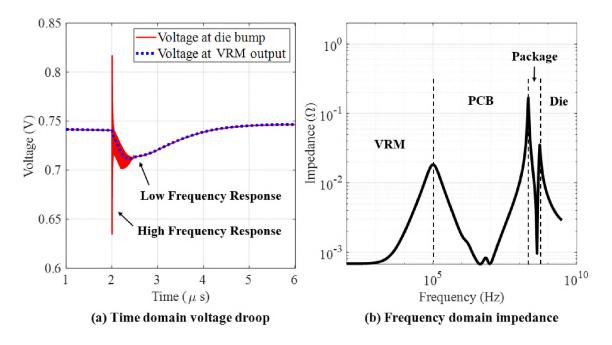

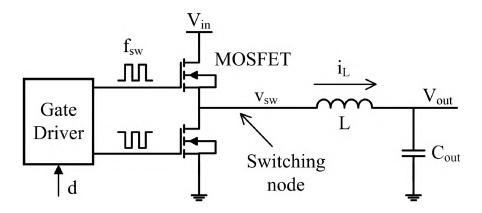

Power distribution network (PDN) is essential in electronic systems to provide reliable power for load devices [1]. The primary objective of the PDN design is to minimize the voltage fluctuations caused by the load current in order to maintain normal integrated circuit (IC) functions [2]. As depicted in Figure 1, a typical PDN consists of four main parts: voltage regulator module (VRM), printed circuit board (PCB)-level PDN, packagelevel PDN, and on-die PDN. When the transient current draws at the die bumps, a voltage droop may occur and affect the system's stability. The voltage droop in the time-domain and the PDN impedance in the frequency-domain are tightly related with each other, as shown in Figure 2. The high frequency response is mainly determined by the package/die parasitics (usually above 100 MHz) or the PCB design (usually 300 kHz ~ 100 MHz), and the low frequency response is typically dominated by the VRM (usually below 300 kHz). However, driven by ambitious user demands, modern ICs are dealing with more sophisticated scenarios while the voltage tolerance margin becomes progressively tighter [3]. To compensate for a large droop, the voltage sensing location is preferred to be closer to or even directly at the die bumps, so the voltage regulation (VR) control gains an increased open-loop bandwidth to react to faster transient events. This can introduce more coupling between the VR control and the PDN. An extreme case is the in-package integrated voltage regulator, where the control loop directly affects the first droop. Thus, influence of the VRM on the PDN design becomes increasingly more significant, especially in the high switching frequency and wide bandwidth applications.

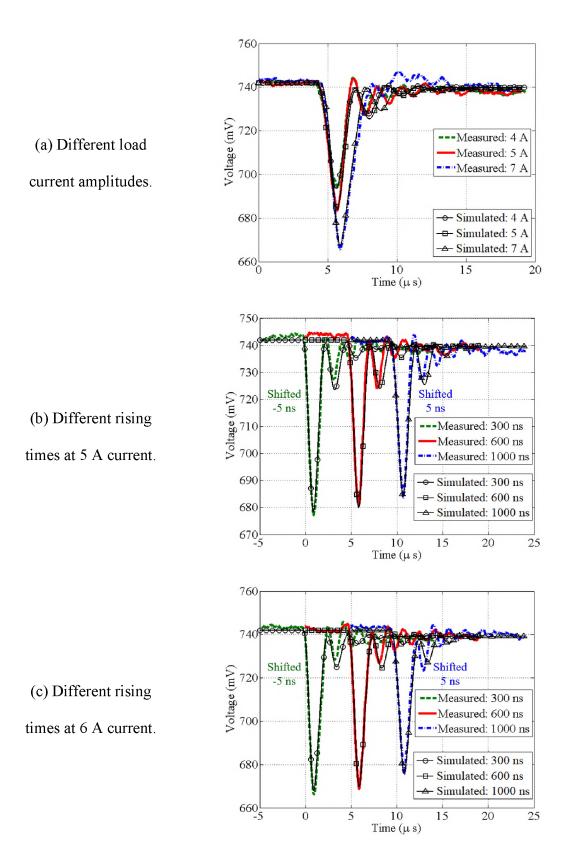

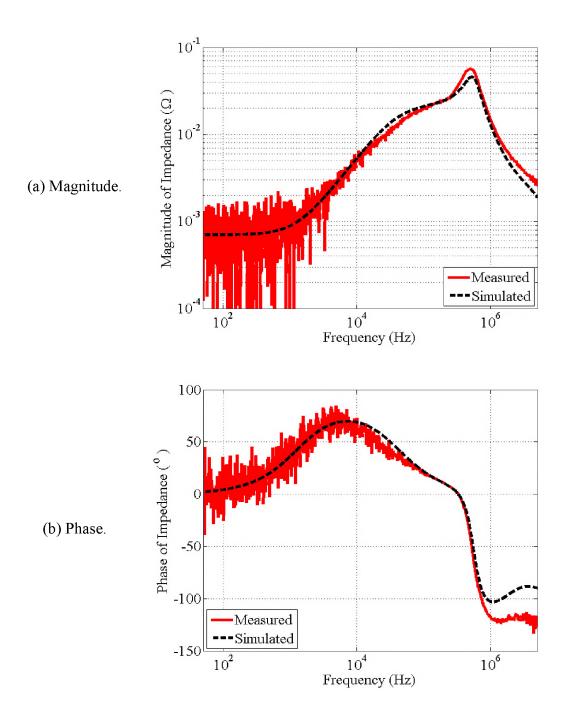

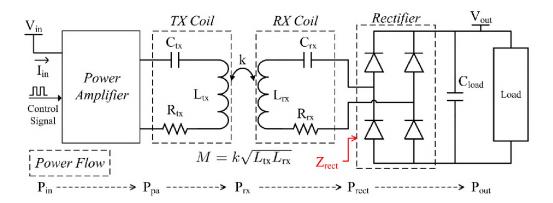

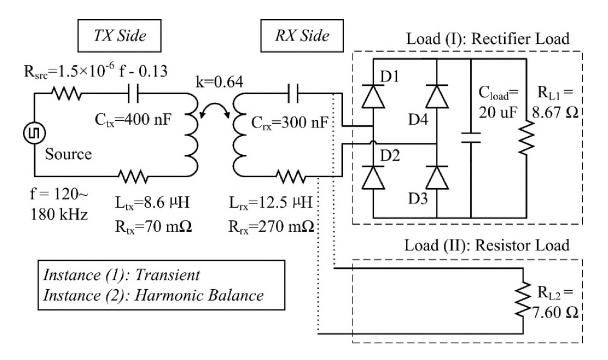

Figure 1. Main elements in the end-to-end PDN.