### New Jersey Institute of Technology

### Digital Commons @ NJIT

**Dissertations**

**Electronic Theses and Dissertations**

12-31-2019

## Bio-inspired learning and hardware acceleration with emerging memories

Shruti R. Kulkarni New Jersey Institute of Technology

Follow this and additional works at: https://digitalcommons.njit.edu/dissertations

Commons

Part of the Artificial Intelligence and Robotics Commons, and the Electrical and Computer Engineering

### **Recommended Citation**

Kulkarni, Shruti R., "Bio-inspired learning and hardware acceleration with emerging memories" (2019). Dissertations. 1450.

https://digitalcommons.njit.edu/dissertations/1450

This Dissertation is brought to you for free and open access by the Electronic Theses and Dissertations at Digital Commons @ NJIT. It has been accepted for inclusion in Dissertations by an authorized administrator of Digital Commons @ NJIT. For more information, please contact digitalcommons@njit.edu.

## **Copyright Warning & Restrictions**

The copyright law of the United States (Title 17, United States Code) governs the making of photocopies or other reproductions of copyrighted material.

Under certain conditions specified in the law, libraries and archives are authorized to furnish a photocopy or other reproduction. One of these specified conditions is that the photocopy or reproduction is not to be "used for any purpose other than private study, scholarship, or research." If a, user makes a request for, or later uses, a photocopy or reproduction for purposes in excess of "fair use" that user may be liable for copyright infringement,

This institution reserves the right to refuse to accept a copying order if, in its judgment, fulfillment of the order would involve violation of copyright law.

Please Note: The author retains the copyright while the New Jersey Institute of Technology reserves the right to distribute this thesis or dissertation

Printing note: If you do not wish to print this page, then select "Pages from: first page # to: last page #" on the print dialog screen

The Van Houten library has removed some of the personal information and all signatures from the approval page and biographical sketches of theses and dissertations in order to protect the identity of NJIT graduates and faculty.

#### ABSTRACT

## BIO-INSPIRED LEARNING AND HARDWARE ACCELERATION WITH EMERGING MEMORIES

### by Shruti R. Kulkarni

Machine Learning has permeated many aspects of engineering, ranging from the Internet of Things (IoT) applications to big data analytics. While computing resources available to implement these algorithms have become more powerful, both in terms of the complexity of problems that can be solved and the overall computing speed, the huge energy costs involved remains a significant challenge. The human brain, which has evolved over millions of years, is widely accepted as the most efficient control and cognitive processing platform. Neuro-biological studies have established that information processing in the human brain relies on impulse like signals emitted by neurons called action potentials. Motivated by these facts, the Spiking Neural Networks (SNNs), which are a bio-plausible version of neural networks have been proposed as an alternative computing paradigm where the timing of spikes generated by artificial neurons is central to its learning and inference capabilities. This dissertation demonstrates the computational power of the SNNs using conventional CMOS and emerging nanoscale hardware platforms.

The first half of this dissertation presents an SNN architecture which is trained using a supervised spike-based learning algorithm for the handwritten digit classification problem. This network achieves an accuracy of 98.17% on the MNIST test data-set, with about 4× fewer parameters compared to the state-of-the-art neural networks achieving over 99% accuracy. In addition, a scheme for parallelizing and speeding up the SNN simulation on a GPU platform is presented. The second half of this dissertation presents an optimal hardware design for accelerating SNN inference and training with SRAM (Static Random Access Memory) and nanoscale

non-volatile memory (NVM) crossbar arrays. Three prominent NVM devices are studied for realizing hardware accelerators for SNNs: Phase Change Memory (PCM), Spin Transfer Torque RAM (STT-RAM) and Resistive RAM (RRAM). The analysis shows that a spike-based inference engine with crossbar arrays of STT-RAM bit-cells is 2× and 5× more efficient compared to PCM and RRAM memories, respectively. Furthermore, the STT-RAM design has nearly 6× higher throughput per unit Watt per unit area than that of an equivalent SRAM-based (Static Random Access Memory) design. A hardware accelerator with on-chip learning on an STT-RAM memory array is also designed, requiring 16 bits of floating-point synaptic weight precision to reach the baseline SNN algorithmic performance on the MNIST dataset. The complete design with STT-RAM crossbar array achieves nearly 20× higher throughput per unit Watt per unit mm² than an equivalent design with SRAM memory.

In summary, this work demonstrates the potential of spike-based neuromorphic computing algorithms and its efficient realization in hardware based on conventional CMOS as well as emerging technologies. The schemes presented here can be further extended to design spike-based systems that can be ubiquitously deployed for energy and memory constrained edge computing applications.

## BIO-INSPIRED LEARNING AND HARDWARE ACCELERATION WITH EMERGING MEMORIES

by Shruti R. Kulkarni

A Dissertation

Submitted to the Faculty of

New Jersey Institute of Technology – Newark

in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering

Helen and John C. Hartmann Department of Electrical and Computer Engineering

December 2019

Copyright © 2019 by Shruti R. Kulkarni  ${\rm ALL~RIGHTS~RESERVED}$

### APPROVAL PAGE

## BIO-INSPIRED LEARNING AND HARDWARE ACCELERATION WITH EMERGING MEMORIES

### Shruti R. Kulkarni

| Dr. Bipin Rajendran, Dissertation Advisor                                                                     | Date |

|---------------------------------------------------------------------------------------------------------------|------|

| Associate Professor, Department of Electrical and Computer Engineering, New<br>Jersey Institute of Technology | V    |

|                                                                                                               |      |

| Dr. Ali N. Akansu, Committee Member                                                                           | Date |

| Professor, Department of Electrical and Computer Engineering, New Jersey Institute of Technology              |      |

|                                                                                                               |      |

| Dr. Durgamadhab Misra, Committee Member                                                                       | Date |

| Professor, Department of Electrical and Computer Engineering, New Jersey<br>Institute of Technology           |      |

|                                                                                                               |      |

| Dr. Horacio G. Rotstein, Committee Member                                                                     | Date |

| Professor, Math Bio & Computational Neuroscience, Biological Sciences, New Jersey Institute of Technology     |      |

|                                                                                                               |      |

| Dr. Osvaldo Simeone, Committee Member                                                                         | Date |

| Professor, Information Engineering, King's College, London                                                    |      |

#### BIOGRAPHICAL SKETCH

Author: Shruti R. Kulkarni

**Degree:** Doctor of Philosophy

Date: December 2019

### Undergraduate and Graduate Education:

Doctor of Philosophy in Electrical Engineering,

New Jersey Institute of Technology, Newark, NJ, USA, 2019

- Master of Technology in Electrical Engineering, Indian Institute of Technology Bombay, Mumbai, India, 2012

- Bachelor of Engineering in Electronics and Communication Engineering, RNS Institute of Technology, Bengaluru, India, 2010

Major: Electrical Engineering

#### Presentations and Publications:

- S. R. Kulkarni, B. Rajendran, "Spiking Neural Networks for Handwritten Digit Recognition – Supervised Learning and Network Optimization," *Neural Networks*, vol. 103, pp. 118-127, July 2018.

- S. R. Nandakumar, S. R. Kulkarni, A. V. Babu, B. Rajendran, "Building Brain-Inspired Computing Systems: Examining the Role of Nanoscale Devices," *IEEE Nanotechnology Magazine*, vol. 12, no. 3, pp. 19-35, Sept 2018.

- S. R. Kulkarni, D. V. Kadetotad, S. Yin, J-s. Seo, B. Rajendran, "Neuromorphic Hardware Accelerator for SNN Inference based on STT-RAM Crossbar Arrays," accepted at *IEEE International Conference on Electronics, Circuits and Systems (ICECS)*, Genova, Nov 2019.

- S. R. Kulkarni, D. V. Kadetotad, J. Seo, B. Rajendran, "Well-Posed Verilog-A Compact Model for Phase Change Memory," Proceedings of International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), pp. 369-373, Austin, TX, Sept 2018.

- S. R. Kulkarni, A. V. Babu, B. Rajendran, "Acceleration of Convolutional Networks Using Nanoscale Memristive Devices," *Proceedings of 19th International Conference on Engineering Applications of Neural Networks (EANN)*, pp. 240–251, Springer, Cham, Bristol, U.K., Sept 2018.

- S. R. Kulkarni, J. M. Alexiades, B. Rajendran, "Live Demonstration: Image Classification Using Bio-inspired Spiking Neural Networks," *Proceedings of IEEE International Symposium on Circuits and Systems (ISCAS)*, pp. 1-1, Florence, May 2018.

- S. R. Kulkarni, J. M. Alexiades, B. Rajendran, "Learning and Real-Time Classification of Hand-written Digits with Spiking Neural Networks," Proceedings of 24th IEEE International Conference on Electronics, Circuits and Systems (ICECS), pp. 128-131, Batumi, Georgia, Dec 2017.

- S. R. Kulkarni, A. V. Babu, B. Rajendran, "Spiking Neural networks Algorithms, Hardware Implementations and Applications," *Proceedings of 60th IEEE International Midwest Symposium on Circuits and Systems (MWSCAS)*, Invited paper, pp. 426-431, Boston, MA, Aug 2017.

- S. R. Kulkarni, B. Rajendran, "Scalable CMOS Digital Architecture for Spike Based Supervised Learning", *Proceedings of 16th International conference on Engineering Applications of Neural Networks (EANN)*, CCIS 517, pp. 149 158, Island of Rhodes, Greece, Sept 2015.

- C. Shetty, S. Nitchith, R. Rawat, S.R. Nandakumar, P. Shah, S. Kulkarni, B. Rajendran. "Live demonstration: Spiking Neural Circuit Based Navigation Inspired by C. Elegans Thermotaxis," Proceedings of IEEE International Symposium on Circuits and Systems (ISCAS), pp. 1905-1905, Lisbon, Portugal, May 2015.

#### ACKNOWLEDGMENT

I take this opportunity to thank all the people without whose support I would not have reached so far in my research work. First of all, I thank my advisor Dr. Bipin Rajendran for providing me with the opportunity to work in the exciting area of neuromorphic engineering. It is because of his invaluable guidance and discussions that I have been able to push myself to reach the end of my Ph.D. research.

I also to thank Dr. Ali N. Akansu, Dr. Osvaldo Simeone, Dr. Horacio G. Rotstein, and Dr. Durgamadhab Misra for having kindly agreed to be part of my dissertation committee and providing me with their invaluable feedback that has improved this dissertation.

I also acknowledge the funding agency, Semiconductor Research Corporation (SRC) for having funded my research work on the non-von Neumann hardware design with Non-Volatile Memory technologies. I also gratefully acknowledge our collaborators on this project from the Arizona State University, Dr. Jae-sun Seo, Shihui Yin and Deepak V. Kadetotad. I also acknowledge the Teaching Assistantship funding from the department of Electrical and Computer Engineering (ECE) during my first two years at NJIT. The first one and a half years of my Ph.D. research were completed at the Indian Institute of Technology Bombay, where I was supported by the Teaching Assistantship from the department of Electrical Engineering and Intel fellowship. I also take this opportunity to thank all the faculty members from IIT Bombay who helped in both technical and non-technical issues I faced in the initial year of my research programme and in developing my scientific temperament. Most importantly, I would also like to mention all my colleagues and friends at IIT Bombay who have also played a significant role in my research journey.

Last, but not the least, I also take this opportunity to thank my family, friends and colleagues who have been constantly supporting me throughout my

journey of Ph.D. I also gratefully acknowledge the valuable discussions with my colleagues at the Intelligent Computing Lab, Anakha V. Babu, Alireza Bagheri, Bleema Rosenfeld, Nandakumar S. R. and Vinay Joshi. I also thank the interns and undergraduate students who worked with me at our lab during the summers, and have also contributed to some of the work in this dissertation. The staff and faculty from the ECE department, NJIT have also been very helpful and supportive throughout my Ph.D. program. I also acknowledge the dissertation document review feedback from Ms. C. Gonzalez and Dr. G. Ziavras from the office of Graduate Studies, NJIT and also in helping me out with the degree completion paperwork.

In short, my Ph.D. dissertation would not have been successfully completed had it not been for the direct or indirect contributions of the faculty, staff, colleagues, friends, and family.

### TABLE OF CONTENTS

| $\mathbf{C}$ | hapte | er      |                                                  | Page |

|--------------|-------|---------|--------------------------------------------------|------|

| 1            | INT   | RODU    | CTION                                            | 1    |

|              | 1.1   | Motiv   | ration and Overview                              | 1    |

|              | 1.2   | Organ   | nization of the Dissertation                     | 4    |

| 2            | BIO   | -INSPI  | RED COMPUTING AND HARDWARE DESIGN                | 6    |

|              | 2.1   | Artific | cial Neural Networks                             | 6    |

|              | 2.2   | Bio-in  | aspired Computing                                | 8    |

|              |       | 2.2.1   | Spiking Neuron Models                            | 9    |

|              |       | 2.2.2   | Spike-based Learning Rules from Biology          | 17   |

|              |       | 2.2.3   | Supervised Learning in SNNs                      | 18   |

|              |       | 2.2.4   | Remote Supervised Method (ReSuMe)                | 21   |

|              |       | 2.2.5   | Normalized Approximate Descent (NormAD) Rule     | 23   |

|              | 2.3   | Summ    | nary                                             | 26   |

| 3            |       |         | ITTEN DIGIT RECOGNITION WITH SPIKING NEURAL ORKS |      |

|              | 3.1   | Netwo   | ork Architecture                                 | 29   |

|              |       | 3.1.1   | Input Encoding                                   | 29   |

|              |       | 3.1.2   | Convolutional Feature Extraction                 | 30   |

|              |       | 3.1.3   | Learning Layer                                   | 31   |

|              |       | 3.1.4   | Lateral Inhibition at the Output Layer           | 32   |

|              | 3.2   | Нурег   | r-parameter Tuning Experiments                   | 32   |

|              |       | 3.2.1   | Training Methodology                             | 33   |

|              |       | 3.2.2   | Accuracy Metrics in Spike Domain                 | 34   |

|              |       | 3.2.3   | Learning Rate Schedule Optimization              | 35   |

|              |       | 3.2.4   | Network Parameter Optimization                   | 36   |

|              |       | 3.2.5   | MNIST Accuracy Results                           | 37   |

# TABLE OF CONTENTS (Continued)

| C | hapte | $\mathbf{er}$ |                                             | Page |

|---|-------|---------------|---------------------------------------------|------|

|   | 3.3   | Netwo         | ork Optimization                            | . 39 |

|   |       | 3.3.1         | Low Precision Weight Encoding               | . 40 |

|   |       | 3.3.2         | Approximating Neuronal Dynamics             | . 42 |

|   | 3.4   | GPU           | Implementation of the SNN Training          | . 43 |

|   | 3.5   | Real-t        | time Inference on User Data                 | . 46 |

|   |       | 3.5.1         | Image Preprocessing                         | . 47 |

|   |       | 3.5.2         | Real-time Simulator                         | . 48 |

|   | 3.6   | Sumn          | nary                                        | . 49 |

| 4 | CON   | MPAC7         | T MODELS FOR NON-VOLATILE MEMORY DEVICES    | . 51 |

|   | 4.1   | Phase         | Change Memory                               | . 52 |

|   |       | 4.1.1         | Device Physics and Operation                | . 54 |

|   |       | 4.1.2         | Compact Model                               | . 54 |

|   |       | 4.1.3         | Simulation Results                          | . 57 |

|   |       | 4.1.4         | Reliability in PCM Devices                  | . 60 |

|   | 4.2   | Spin 7        | Transfer Torque RAM                         | . 63 |

|   |       | 4.2.1         | STT-RAM: Device Physics                     | . 63 |

|   |       | 4.2.2         | Previous Compact Models for STT RAM Devices | . 66 |

|   |       | 4.2.3         | Compact Model for STT-RAM Device            | . 68 |

|   |       | 4.2.4         | Simulation Results                          | . 70 |

|   |       | 4.2.5         | Stochastic Switching                        | . 71 |

|   |       | 4.2.6         | Modeling Reliability in STT-RAM Devices     | . 72 |

|   | 4.3   | Resist        | sive RAM                                    | . 74 |

|   |       | 4.3.1         | Previous Compact Models for RRAM Devices    | . 74 |

|   |       | 4.3.2         | Model Design                                | . 75 |

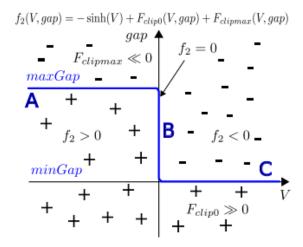

|   |       | 4.3.3         | Clipping Functions                          | . 77 |

|   |       | 4.3.4         | Simulation Results                          | . 79 |

## TABLE OF CONTENTS (Continued)

| $\mathbf{C}$ | hapto | er     |                                                            | Page  |

|--------------|-------|--------|------------------------------------------------------------|-------|

|              |       | 4.3.5  | Transient Analysis                                         | . 81  |

|              |       | 4.3.6  | RRAM Reliability Modeling                                  | . 82  |

|              | 4.4   | Sumn   | nary and Future Scope                                      | . 84  |

| 5            |       |        | NEUMANN COGNITIVE HARDWARE FOR SPIKING NEUR                |       |

|              | 5.1   | Netwo  | ork Architecture for ReSuMe Training                       | . 86  |

|              |       | 5.1.1  | Network Optimization Analyses                              | . 87  |

|              |       | 5.1.2  | Digital Architecture                                       | . 90  |

|              |       | 5.1.3  | Power and Area Requirements                                | . 92  |

|              |       | 5.1.4  | Learning Capability of the Architecture                    | . 94  |

|              | 5.2   | Accele | erating Spiking Neural Networks with Memristive Hardware . | . 95  |

|              |       | 5.2.1  | Network Optimization for Hardware                          | . 97  |

|              |       | 5.2.2  | Restricting ON-OFF Ratios of Synaptic Weights              | . 97  |

|              |       | 5.2.3  | Hardware Architecture                                      | . 99  |

|              |       | 5.2.4  | Synapses Using Memristive Devices                          | . 99  |

|              |       | 5.2.5  | Sequential and Parallel Convolution                        | . 100 |

|              |       | 5.2.6  | Programming Variability                                    | . 101 |

|              |       | 5.2.7  | Results                                                    | . 102 |

|              | 5.3   | Digita | al Cognitive Hardware Design with NVM Crossbar Arrays      | . 105 |

|              |       | 5.3.1  | NVM array for SNN Inference Engines                        | . 106 |

|              |       | 5.3.2  | Memory Array Design                                        | . 109 |

|              |       | 5.3.3  | Design Evaluation Across NVM Devices                       | . 111 |

|              |       | 5.3.4  | STT-RAM NVM Array for BASNN                                | . 112 |

|              |       | 5.3.5  | Learning on NVM Array                                      | . 117 |

|              | 5.4   | Sumn   | nary and Discussion                                        | . 125 |

| 6            | COI   | NCLUS  | ION AND FUTURE OUTLOOK                                     | . 127 |

# TABLE OF CONTENTS (Continued)

| Chapter     |                             | P | age |

|-------------|-----------------------------|---|-----|

| APPENDIX A  | SIMULATION PARAMETERS       |   | 129 |

| APPENDIX B  | NVM DEVICE MODEL PARAMETERS |   | 131 |

| BIBLIOGRAPI | HY                          |   | 133 |

### LIST OF TABLES

| Tabl | le I                                                                          | Page |

|------|-------------------------------------------------------------------------------|------|

| 3.1  | Learning Rate Schedules                                                       | 36   |

| 3.2  | MNIST Classification Accuracy Comparison                                      | 40   |

| 3.3  | Confusion Matrix for the SNN's Predicted Output                               | 41   |

| 5.1  | Power Estimates in $\mu W$ for 65 nm and 10 nm                                | 94   |

| 5.2  | Area Estimates (in $\mu m^2$ ) for 65 nm and 10 nm                            | 94   |

| 5.3  | Communication Power in $\mu W$ for 65 nm and 10 nm Node                       | 94   |

| 5.4  | Network Accuracy during Inference with Limited On-Off Ratio of $10$           | 98   |

| 5.5  | Read and Write Circuits for NVM Devices Designed in $65\mathrm{nm}$ Node      | 110  |

| 5.6  | Evaluation of Neurosynaptic Core Design Across Three Different NVMs           | 111  |

| 5.7  | Post-synthesis Numbers for the STT-RAM-based Neuro-synaptic Core $$ .         | 114  |

| 5.8  | Performance Comparison Between SRAM and STT-RAM Architectures                 | 116  |

| 5.9  | Post-synthesis Numbers for Floating-Point Digital Logic Blocks                | 122  |

| 5.10 | Comparison of SRAM and STT-RAM Architectures for Training $\ \ldots \ \ldots$ | 122  |

| 5.11 | Average Spike Statistics per Layer per Core in the SNN during Training        | 124  |

| 5.12 | Performance Comparison Between SRAM and STT-RAM Designs                       | 125  |

| A.1  | Simulation Parameters for NormAD                                              | 129  |

| A.2  | Simulation Parameters for ReSuMe                                              | 130  |

| B.1  | Parameters used in the PCM Compact Model                                      | 131  |

| B.2  | Parameters used in the STT-RAM Compact Model                                  | 131  |

| B.3  | Parameters used in the RRAM Compact Model                                     | 132  |

### LIST OF FIGURES

| Page | Figure                                                                                                                                                                                                                                                                                                                                                             | Figu |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

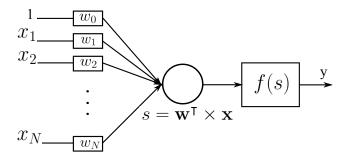

| 7    | 2.1 Model of a neuron used in second generation ANNs. The neuron shown above computes the weighted sum of all its inputs in $s$ , which is then applied to an activation function $f$ to generate the final output. The neuron additionally has a bias line (of weight $w_0$ ) for which the input is kept at unity                                                | 2.1  |

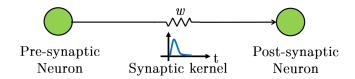

| 14   | A simple case of two neurons connected by a synapse of strength 'w' The synapse transforms the incoming spike into an equivalent current through a kernel, which is presented as input to the post-synaptic neuron.                                                                                                                                                | 2.2  |

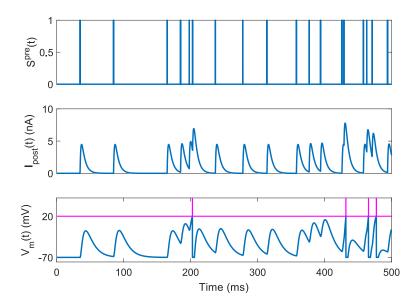

| 15   | 2.3 Spikes input to a neuron (top). Evolution of the synaptic current (middle) and membrane potential (bottom). The membrane potential at point where the threshold is crossed is artificially set to a higher value (40 mV), for the sake of clarity                                                                                                              | 2.3  |

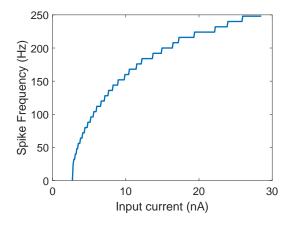

| 15   | 2.4 Spike frequency of an LIF neuron excited by a constant input current exhibits a strong non-linear dependence.                                                                                                                                                                                                                                                  | 2.4  |

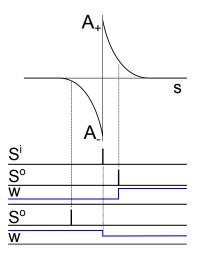

| 18   | 2.5 Weight modification in Spike Timing Dependent plasticity (STDP)                                                                                                                                                                                                                                                                                                | 2.5  |

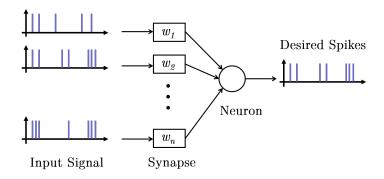

| 19   | 2.6 Goal of supervised learning is to determine the set of weights $\mathbf{w}$ that transform the incoming spike trains into the desired spike train shown                                                                                                                                                                                                        | 2.6  |

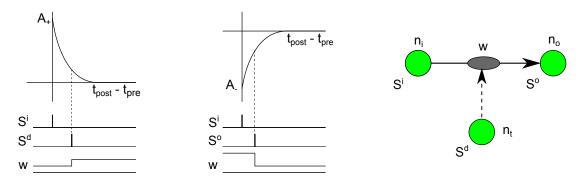

| 22   | 2.7 Weight update process in ReSuMe follows from the timing principles of the STDP rule, where, the weight update is proportional to the timing difference between the pre- and post-synaptic spike times. However unlike the unsupervised STDP rule, here, the weight update happens only when there is a spike at the post-synaptic neuron (desired or observed) | 2.7  |

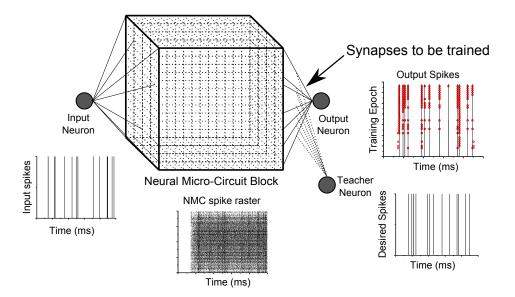

| 23   | 2.8 ReSuMe network and training process. A single input spike train is applied to an NMC block creating a rich set of spike trains. These spike trains are then applied to the trainee neuron to create the desired set of spikes                                                                                                                                  | 2.8  |

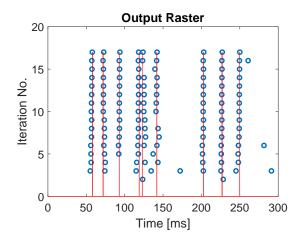

| 25   | 2.9 Demonstration of NormAD training over successive training iterations (on y-axis). The solid red lines are the desired spikes (with interspike times Poisson distributed), while the blue circles represent the trainee neuron's spikes over a period of 300 ms. It can be seen that the algorithm converges in just 17 training iterations                     | 2.9  |

| Page | ure 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Figu |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

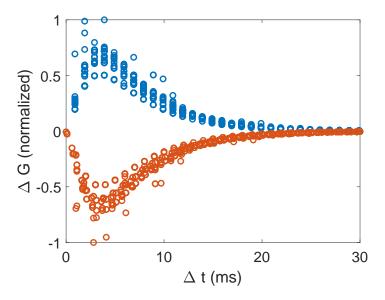

| 25   | While the NormAD is an analytically derived rule, using the neuronal and synaptic dynamics show that the synaptic weight update $\Delta G$ has a dependence on $\Delta t$ similar to biological STDP. Here, $\Delta t = t_o - t_i$ , where $t_i$ is the spike time from the input neuron and $t_o$ is the time of spike observed/expected from the output neuron. The curve with blue circles represent synaptic potentiation, when a spike is expected on the output neuron, while the red circles represent the synaptic depression.                                                | 2.10 |

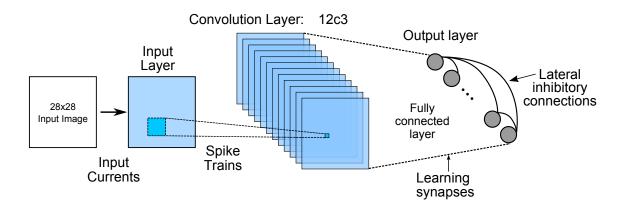

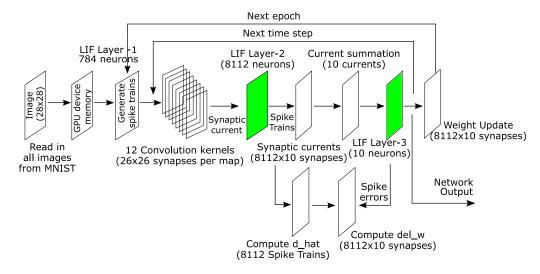

| 29   | The proposed spiking neural network architecture for handwritten digit classification. The spike trains from the input layer with $28 \times 28$ neurons are spatially convolved with twelve filters (or convolution kernels) of size $3 \times 3$ , resulting in the twelve feature maps of size $26 \times 26$ . The synapses connecting the 8112 convolution layer neurons and the 10 output layer neurons are tuned during training. There is a fixed winner-take-all (WTA) lateral inhibition between the neurons in the output layer                                            | 3.1  |

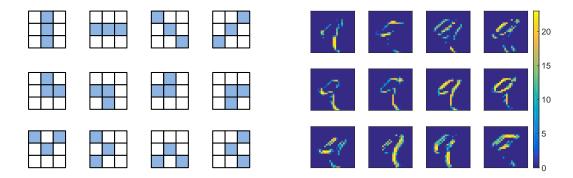

| 31   | (a). (left) Convolution filters used in our SNN are of size $3\times3$ pixels. The blue pixels are the excitatory weights, while white pixels are inhibitory values. The magnitude of the excitatory weight is 1.6 times that of the inhibitory weight. (b). (right) The twelve spike count feature maps corresponding to these filters obtained when an exemplary image of digit '9' was presented to the network. The color intensities in the 2D map depict the number of spikes generated by the neurons of the hidden layer when the input was presented for $T=100\mathrm{ms.}$ | 3.2  |

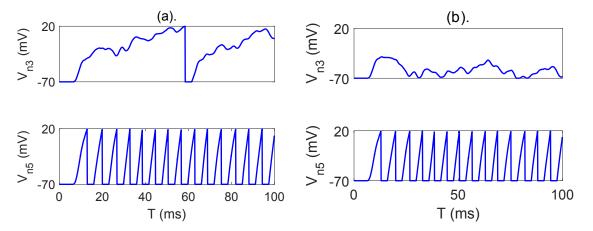

| 33   | Membrane potential of two output layer neurons '3' and '5', when an input image of digit '5' was presented to the network. (a) (left) Membrane potential without lateral inhibition and (b) (right) with lateral inhibition. It can be seen that lateral inhibition has suppressed the incorrect neuron '3' from issuing a spike                                                                                                                                                                                                                                                      | 3.3  |

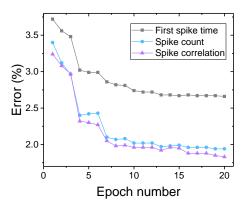

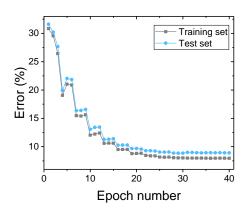

| 34   | (a). (left) The 3-layer SNN error on the MNIST test data-set based on the count, correlation and first-spike-time metrics. It can be seen that the network classification error in terms of first neuron to spike (in gray) during the presentation interval $T$ , is worse by almost 1% compared to either count (blue) or the correlation metric (magenta). (b). (right) For a 2-layer SNN without the hidden layer, the error saturates to about 8%, even at 40 epochs of training, illustrating the importance of the hidden layer.                                               | 3.4  |

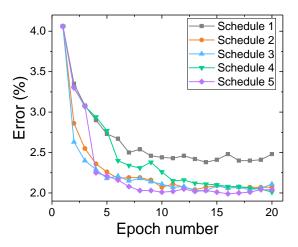

| 36   | Network error on the validation set for five different rate schedules listed in Table 3.1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3.5  |

| Figu | ıre                                                                                                                                                                                                                                                                                                                                                                                                                             | Page |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

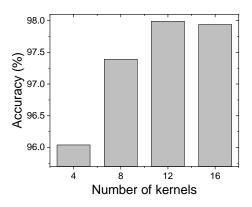

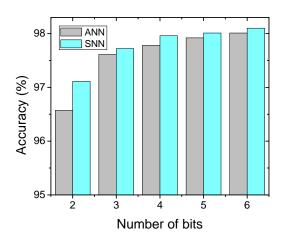

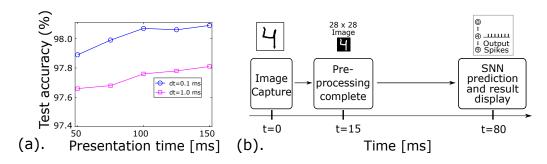

| 3.6  | (a). (left) Classification accuracy on the MNIST test set as a function of the number of convolutional kernels; (b). (right) the presentation duration, $T$ . The network accuracy is optimized with 12 kernels and a presentation duration of $T=100\mathrm{ms}$                                                                                                                                                               |      |

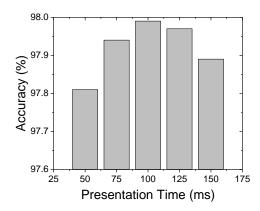

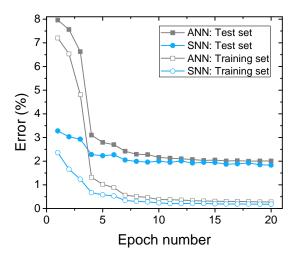

| 3.7  | Comparison of the MNIST error for the 3-layer SNN and an equivalent ANN with the same network structure during 20 epochs of training. The SNN performance (0.18% error for training set and 1.83% error for test set at convergence) is slightly better than that of the ANN (0.28% error for training set and 2.0% for test set at convergence).                                                                               |      |

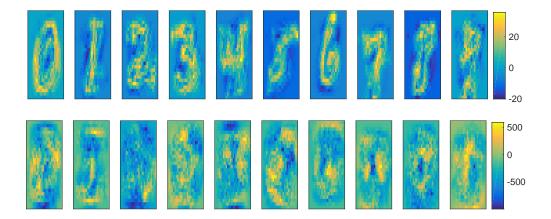

| 3.8  | Average of the trained weights (in pS) from the 12 kernels in the hidden layer to the 10 neurons in the output layer is the effective internal representation of the digits learned by the network. (Top) The average weights in the output layer of the SNN after 100 images presented once for training (when the test set accuracy was only 65.8%) and; (Bottom) average weights after training (i.e., with 98.17% accuracy) |      |

| 3.9  | Test accuracy as a function of the precision of the trained weights in the SNN and ANN. Even at 2-bit precision, the SNN accuracy is only about 1% lesser than the floating point baseline. Further, the SNN accuracy is better than the corresponding ANN especially at low bit-precision.                                                                                                                                     |      |

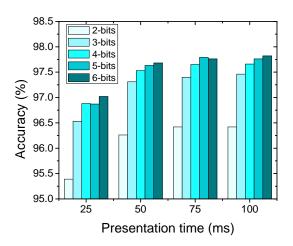

| 3.10 | MNIST test accuracy (count metric) as a function of bit-precision of weights and the presentation time $T$ , when the neuronal dynamics is approximated with a larger integration time step of 1 ms. Even at 3-bits of precision and with $T=50\mathrm{ms}$ , the drop in accuracy is within 1% of the baseline.                                                                                                                |      |

| 3.11 | Diagram showing the different variables of the network being computed each time step and how the signals flow across different layers. The dimensions within the brackets are the sizes of those variables and their respective CUDA kernels.                                                                                                                                                                                   |      |

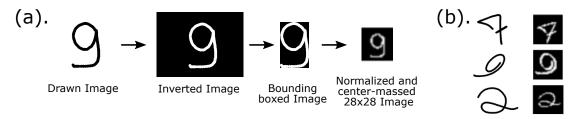

| 3.12 | (a). Preprocessing steps used to convert the user input to a $28 \times 28$ image that is fed to the network. (b). Examples of user input (left) and the pre-processed $28 \times 28$ pixel images fed to the SNN (right)                                                                                                                                                                                                       |      |

| 3.13 | (a). MNIST test-set accuracy as a function of presentation time and the integration time step $\Delta t$ . (b) Various stages of classifying a user's input: the image pre-processing takes 15 ms and the 75 ms SNN emulation is completed in real-time.                                                                                                                                                                        |      |

| Page | Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

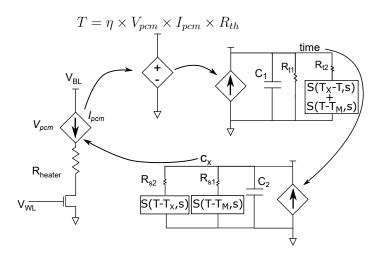

|      | Schematic of the continuous compact Verilog-A model for the PCM device. This model is inspired from the one in Ventrice, et al., 2007, and also satisfies the guidelines for compact model development specified in Wang, et al. 2016.                                                                                                                                                                                                                                                                                                                                                                                  | 4.1 |

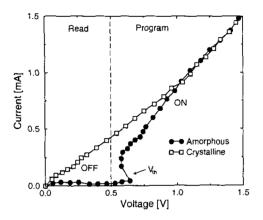

|      | Typical experimental I-V characteristics of PCM device (reproduced from Pirovano, et al., 2002)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4.2 |

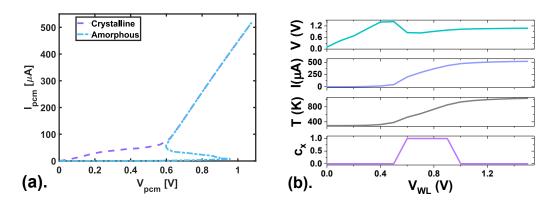

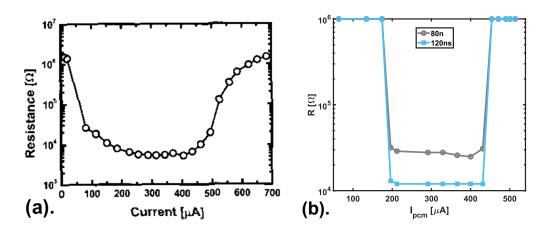

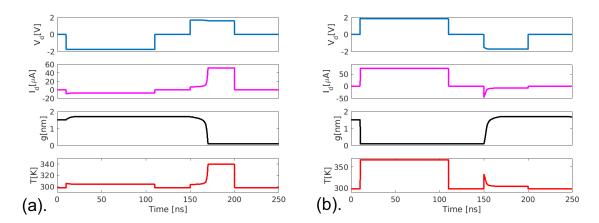

| ;    | (a). I-V response of the well-posed PCM Verilog-A model. The behavior was captured by applying a voltage ramp at the Word Line $(WL)$ , i.e., the gate of the access NMOS for the two states of initialization (SET and RESET). (b). DC behavior of the PCM device from HSPICE simulations. From top to bottom: the waveforms of the PCM voltage drop $(V)$ , current $(I)$ , temperature $(T)$ and the crystalline fraction $(c_x)$ as a function of $V_{WL}$                                                                                                                                                          | 4.3 |

|      | (a). Experimental resistance vs. programming current characteristics of a PCM device (reproduced from Pellizzer, et al., 2004). (b). The R-I curve obtained using the model for programming pulse widths of 80 ns and 120 ns                                                                                                                                                                                                                                                                                                                                                                                            | 4.4 |

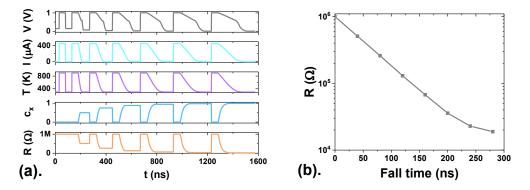

|      | (a). Simulated device parameters as a function of duration of the falling edge of the input pulse. Application of each pulse initially resets the device and then brings the final resistance to an intermediate value below $R_{reset}$ depending on the duration of the falling edge. From top to bottom: the waveforms of the PCM voltage drop $(V)$ , current $(I)$ , device temperature $(T)$ , crystalline fraction $(c_x)$ and the device resistance $(R)$ . (b). Final resistance of the PCM device as a function of falling edge of input pulse, plotted from the resistance values as shown in Figure 4.5(a). | 4.5 |

|      | (a). Gradual conductance change by application of a series of low amplitude partial SET pulses. From top to bottom: the waveforms of the PCM voltage drop $(V)$ , current $(I)$ , device temperature $(T)$ , crystalline fraction $(c_x)$ and the device resistance $(R)$ . (b). PCM resistance as a function of the number of partial SET pulses, plotted from the resistance values as shown in $(a)$                                                                                                                                                                                                                 | 4.6 |

| Page | ure I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Figu |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

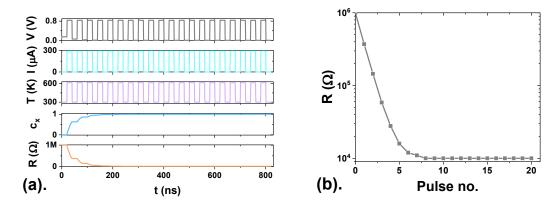

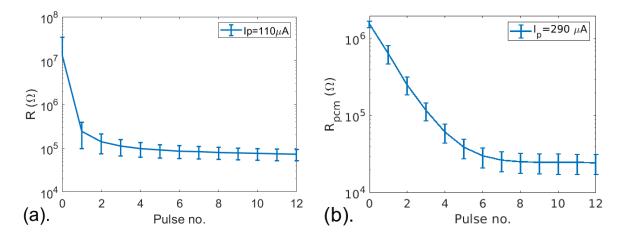

| 61   | (a). Resistance distribution in the IBM's PCM device for programming current of $I_p=110\mu\text{A}$ and pulse width of 50 ns long programming pulses, as reported in Nandakumar, et al., 2017. (b). PCM model showing intermediate resistance states between the high and low resistance state, when applied with partial SET programming pulses starting from a RESET state. The programming pulses were applied to 100 instances with $I_p=290\mu\text{A}$ and pulse width of 20 ns                                                                               | 4.7  |

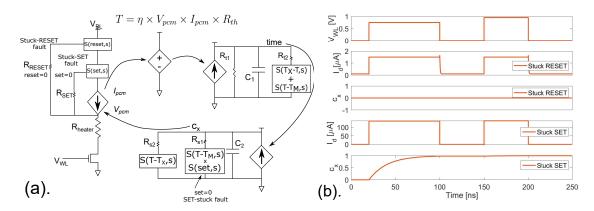

| 62   | (a). PCM model modifications showing the incorporation of stuck-set and stuck-reset faults. The fault variables set and reset are passed from the SPICE netlist. (b). HSPICE simulation waveforms showing the stuck-SET and stuck-RESET schemes. The first voltage pulse (top panel) is a SET programming pulse followed by a RESET programming pulse. It can be seen in the second and third panels that the current remains low and crystalline fraction at 0 indicating the device is stuck-at RESET state. The last two panels show the case for stuck-SET fault | 4.8  |

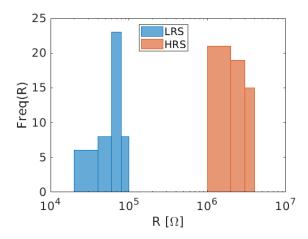

| 62   | Device resistances in an array of 100 devices, with 60% showing stuck-at RESET fault. Similar scheme can be applied to simulate stuck-at SET faults or both versions of faults in a large array of PCM devices                                                                                                                                                                                                                                                                                                                                                       | 4.9  |

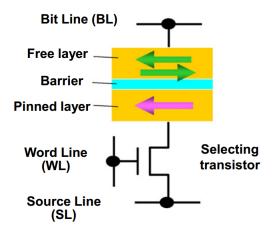

| 64   | Basic structure of a memory cell with an in-plane STT-MTJ device. The alignment of magnetization in the free layer which is controlled by applying appropriate programming currents decides the overall resistance (reproduced from Kawahara, et al., 2012)                                                                                                                                                                                                                                                                                                          | 4.10 |

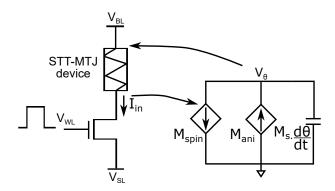

| 69   | Compact model of the STT-RAM device, with bit cell connected in a 1T-1MTJ configuration. The magnetization angle $\theta$ of the device is calculated by the auxiliary circuit and is used to evaluate the device's final resistance $R$ . This model is adapted from the one described in Xu, $et\ al.$ , 2014                                                                                                                                                                                                                                                      | 4.11 |

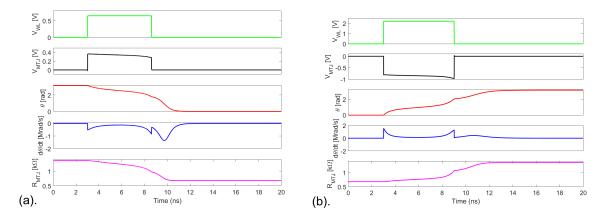

| 70   | (a). Simulation waveforms when the input is above the critical point, with $V_{WL} = 0.70 \mathrm{V}$ and $t_{pw} = 6 \mathrm{ns}$ causing a deterministic switching from a high $(R_{AP})$ to low resistance $(R_P)$ state. The signal $d\theta/dt$ is always less than zero. (b). Simulation waveforms for input above the critical point, with $V_{WL} = 2.2 \mathrm{V}$ and $t_{pw} = 6 \mathrm{ns}$ causing a deterministic switching from a low $(R_P)$ to high resistance $(R_{AP})$ state. The signal $d\theta/dt$ is always greater than zero               | 4.12 |

## LIST OF FIGURES (Continued)

| Figu |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

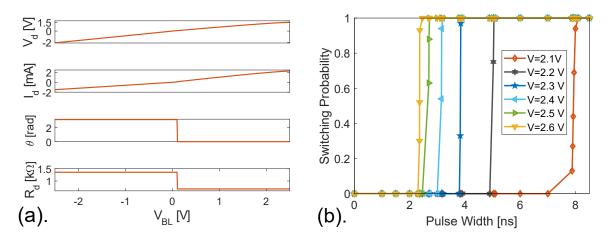

| 4.13 | (a). Steady state response of the STT-RAM compact model obtained by varying the bitline voltage. Under this condition, the state variable $\theta$ and the device resistance remain at either high or low states when the applied voltage is negative or positive, respectively. (b). Probability of stochastic switching in the compact model, which varies with the applied input and pulse width                                                                                                                                             | 71   |

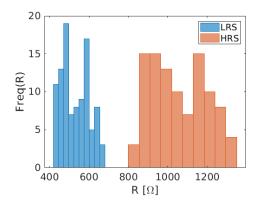

| 4.14 | Resistance distribution for the two states of the STT-RAM model, mean high resistance at $1.35\mathrm{k}\Omega$ and mean low resistance at $677\Omega$                                                                                                                                                                                                                                                                                                                                                                                          | 72   |

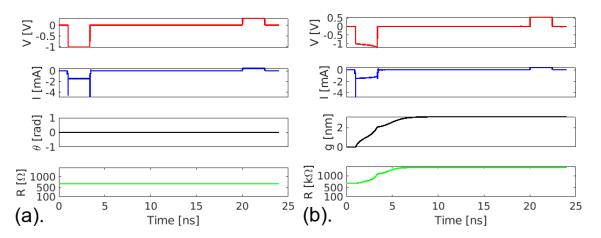

| 4.15 | (a). Stuck-at 0 (low) faults simulation in the STT-RAM model. The first pulse is applied to change the initial state to HRS, and the subsequent pulse programs the device in LRS. It can be seen that the model remains at LRS throughout the entire simulation duration. (b). Stuck-at 1 (high) fault simulation in the STT-RAM model. The first pulse is applied to change the initial state to HRS, and the subsequent pulse programs the device in LRS. It can be seen that the model remains at HRS even after the second pulse is applied | 73   |

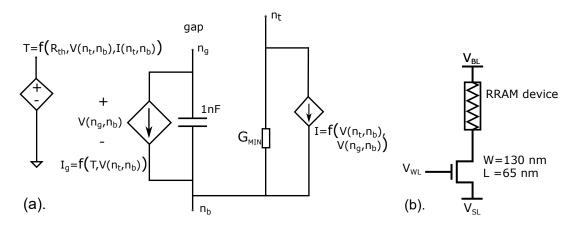

| 4.16 | (a). Detailed schematic of the Verilog-A model of a RRAM cell. The model circuit is based on the one described in Wang, $et\ al.$ , 2016. The nodes $n_t$ and $n_b$ represent the top and bottom terminals of the RRAM device. The node $n_g$ represents the internal gap variable. (b). High level schematic of circuit used for simulating the PCM model. We use the 65 nm NMOS transistor from the PTM library to simulate the access device                                                                                                 | 78   |

| 4.17 | Desired steady state (DC analysis) response of the gap variable of the model, as a function of the applied voltage across the RRAM device. (Reproduced from Wang, et al., 2016.)                                                                                                                                                                                                                                                                                                                                                                | 79   |

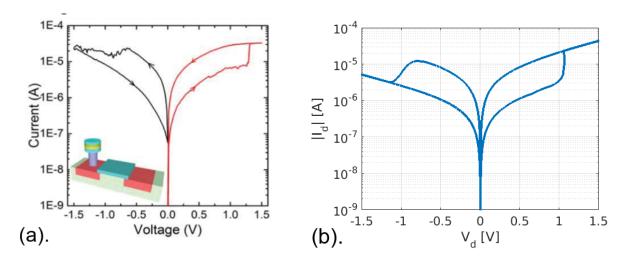

| 4.18 | (a). I-V characteristics of an experimental $\text{TaO}_x$ -HfO $_x$ RRAM device used in a large memory array, as reported in Huang, $et~al.$ , 2015. (b). I-V characteristics of the RRAM model. It can be seen that the ON-OFF ratio of the model is around 10, which matches that of the device data.                                                                                                                                                                                                                                        | 80   |

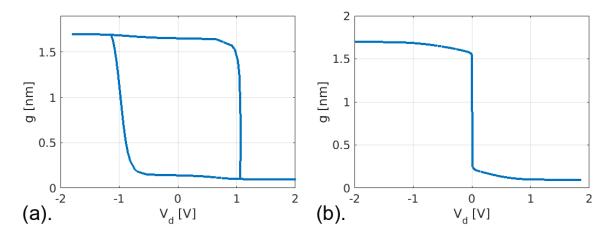

| 4.19 | (a). Variation of gap, $g$ , as a function of the applied voltage across the device. The gap shows hysteresis, which is the basis of memory storage capability. (b). DC analysis by varying the bitline voltage from -2V to 2V. The curve deviates slightly from the ideal behavior as in Figure 4.17 at voltage values close to zero.                                                                                                                                                                                                          | 81   |

## LIST OF FIGURES (Continued)

| Figure |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Page |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

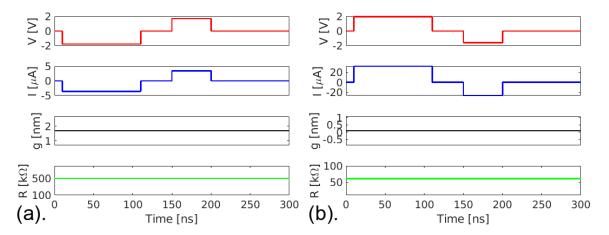

| 4.20   | Transient simulation to programming for SET. A reset pulse is applied to the source-line $V_{SL}$ for 100 ns and then the actual SET programming pulse of duration 50 ns is applied to the bit line $V_{BL}$ . It can be seen that $g$ switches from its maximum value to minimum value within about 30 ns. (b). Transient simulation to programming for RESET. A set pulse is applied to the bit-line $V_{BL}$ for 100 ns and then the actual RESET programming pulse of duration 50 ns is applied to the source line $V_{SL}$ . It can be seen that $g$ switches from its minimum value to maximum value within about 10 ns | 81   |

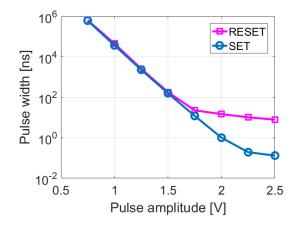

| 4.21   | Pulse width as a function of applied programming pulse amplitude. It can be seen that there is an exponential dependence of the switching time as a function of amplitude for both SET and RESET                                                                                                                                                                                                                                                                                                                                                                                                                              | 82   |

| 4.22   | (a). RRAM model permanently stuck at its high resistance state. We apply an initial RESET programming pulse followed by a SET programming pulse. However, it can be seen that even after the second pulse, the resistance of the model remains at a high value $(512\mathrm{k}\Omega)$ . (b). (Right) RRAM model permanently stuck at its low resistance state. We apply an initial SET programming pulse followed by a RESET programming pulse. However, it can be seen that even after the second pulse, the resistance of the model remains at a low value $(61\mathrm{k}\Omega)$                                          | 84   |

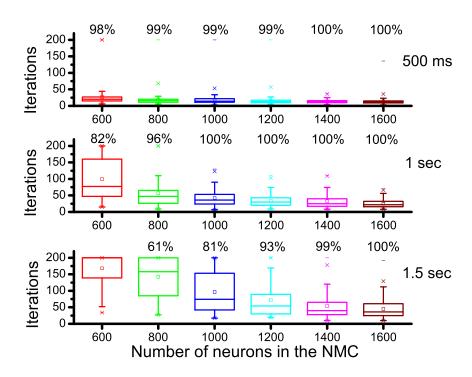

| 5.1    | Training performance of ReSuMe at different network sizes and at varying spike train durations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 88   |

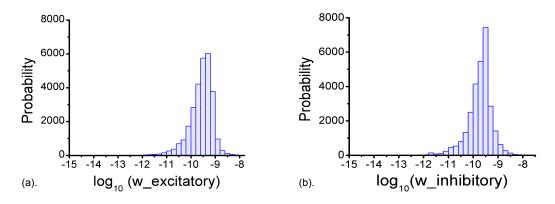

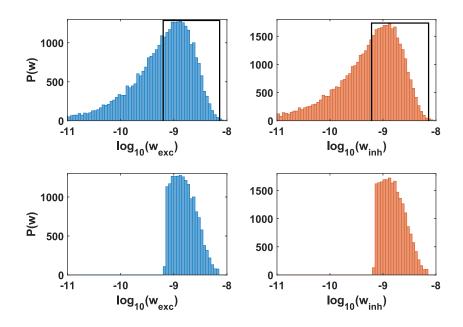

| 5.2    | Histograms of logarithm of absolute values of the weights (a). Excitatory and (b). Inhibitory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 89   |

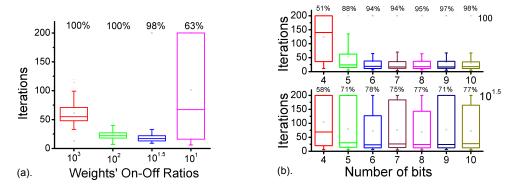

| 5.3    | Training performance of ReSuMe at different on-off ratios and bit-precisions of the synaptic weights                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 90   |

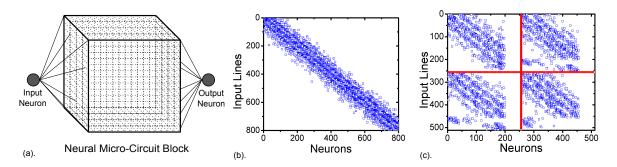

| 5.4    | Partitioning of the NMC block on $256 \times 256$ sized cores                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 91   |

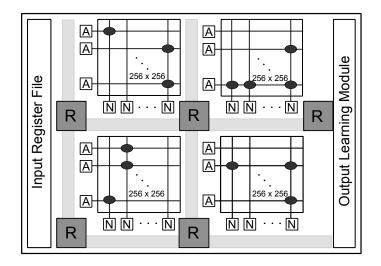

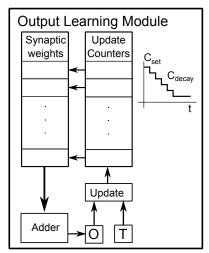

| 5.5    | Digital architecture for ReSuMe learning. (Left) High level crossbar architecture realizing the NMC block. (Right) Learning module for calculating the weight update for the output neuron                                                                                                                                                                                                                                                                                                                                                                                                                                    | 92   |

| 5.6    | Software trained weights (upper panel) having a large range of values, are clipped such that the ratio of maximum value to minimum value (on-off ratio) of the excitatory and inhibitory weights is restricted to 10. This range of values resulted in the test accuracy to drop to 98.07% from the baseline value of 98.17% in the SNN. For the ANN, there was no drop in the test accuracy.                                                                                                                                                                                                                                 | 98   |

# LIST OF FIGURES (Continued)

| Figu | ire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Page        |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

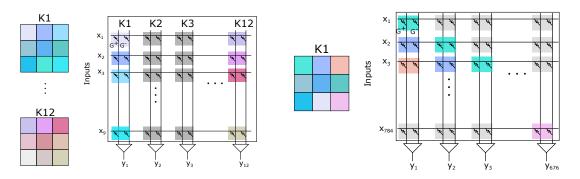

| 5.7  | (Left) Sequential convolution in memristive crossbar array with $9 \times 12 \times 2$ devices to represent the 12 kernels used in the convolution layer, each having a $3 \times 3$ sized weight matrix. These matrices are unrolled as vectors of size $(9 \times 1)$ . The inputs need to be presented in sections of 9 elements to obtain the output of the convolution operation. (Right) Parallel convolution in memristive crossbar array with $784 \times 676 \times 2$ devices. Each neuron in the convolution layer has 9 incoming synapses so every column in the array has only 9 active connections. The crosspoints in gray are inactive connections. | 3           |

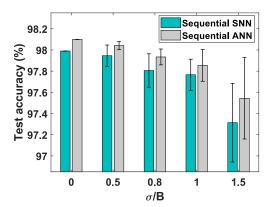

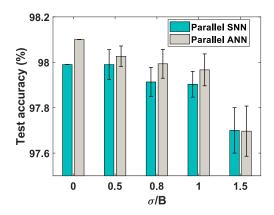

| 5.8  | Accuracy of the spiking and non-spiking networks for sequential (left) and parallel (right) convolution as a function of the device conductance level variations, defined as the ratio $\sigma/B$ , where $\sigma$ is the standard deviation of the zero mean Gaussian noise and $B$ is the bin-width of the conductance levels. In both the cases, the average classification accuracy of the SNN is close to that of the ANN within 0.1%                                                                                                                                                                                                                          |             |

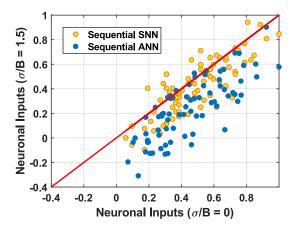

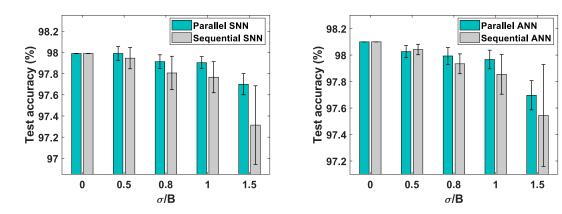

| 5.9  | The incoming currents to the output layer neurons of both SNN and ANN for $\sigma/B = 1.5$ . The x-axis corresponds to the baseline network without any programming variability ( $\sigma/B = 0$ ), while the y-axis represents the networks with variability $\sigma/B = 1.5$ . It can be seen that for SNN, input currents deviated more from the baseline when compared to ANN, resulting in the slightly higher accuracy drop                                                                                                                                                                                                                                   | ;<br>3<br>- |

| 5.10 | Comparison of networks' inference accuracy for sequential and parallel convolution architectures with memristive arrays in SNNs (left) and ANNs (right)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |

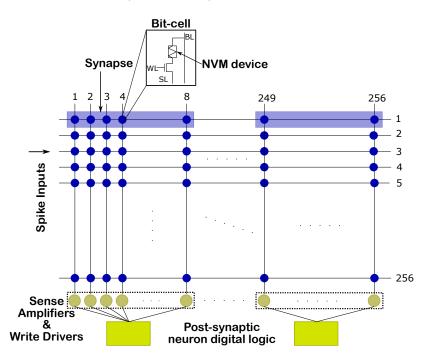

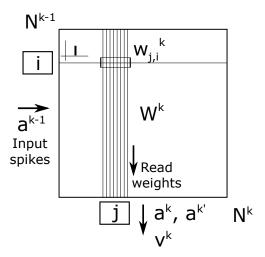

| 5.11 | Neuro-synaptic crossbar array based hardware with 256 inputs lines, 32 output neurons and 8-bit synapses. Each output layer neuron on the post-synaptic side of the array is connected to 8 bitlines and can access the associated devices for the selected row (wordline)                                                                                                                                                                                                                                                                                                                                                                                          | )<br>}      |

| 5.12 | Scheme for forward propagation of input signals through the STT-RAM crossbar array. At any given time-step, a set of spikes from the layer $k-1$ arrive at the core input (WL). Each of the wordlines are processed sequentially at the respective output neurons, which read and accumulate the synaptic weights                                                                                                                                                                                                                                                                                                                                                   | );<br>);    |

| 5.13 | (a). Single neuro-synaptic core and its five main components. (b) Multiple cores tiled together for realizing large SNNs. The on-chip router communicates binary spikes to different cores of the chip. The address decoder translates the received spike information into binary spikes for the corresponding wordlines of the crossbar array                                                                                                                                                                                                                                                                                                                      | )<br>}      |

| Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

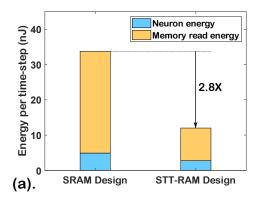

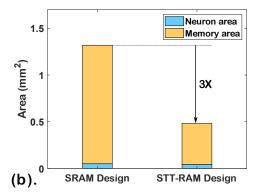

| 5.14 Performance comparison between an SRAM based design and STT-RAM based design for 256 neurons and 1156×256 synapses. (a). Comparison of the neuronal and memory read energies for a time-step in the SRAM (described in Yin et al., 2017) and STT-RAM designs. The additional glue logic in the SRAM based design results in slightly higher power for the neurons, while such circuitry is not required in the STT-RAM crossbar array, as the neurons directly connect to the synaptic array as in Figure 5.11. (b). Comparison of the neuronal logic area and the memory area between the two designs for a single layer of 256 neurons                                                                          |  |

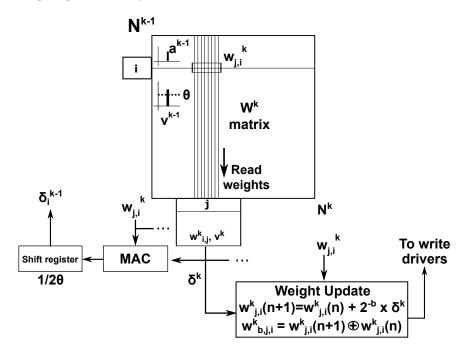

| 5.15 Scheme for performing back-propagation of error gradients and weight update                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

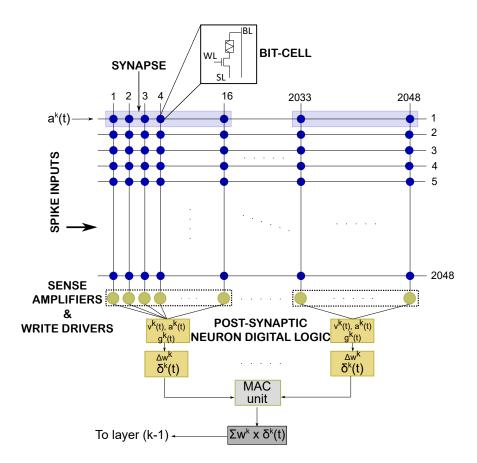

| 5.16 A $2048 \times 2048$ crossbar array supporting access to $2048$ inputs and $128$ outputs at a time. Each synaptic weight is represented by 16 devices on a row. The peripheral digital logic consists of blocks to update the neuron membrane potential, the error derivative $\delta$ and the weight update terms $\Delta w$ . Similar to the design for inference (Figure 5.13), when multiple cores are tiled together, the inter-core spike communication takes place through the routers and spikes are presented to the memory array via address decoders. To support fan-out larger than 128, multiple wordlines can be accessed in a time-multiplexed manner for every batch of 128 post-synaptic neuron. |  |

#### CHAPTER 1

#### INTRODUCTION

#### 1.1 Motivation and Overview

Cognitive processing capabilities of the human brain are far superior than any supercomputer till date. Apart from their processing ability, they are extremely efficient in the number of operations being performed, with some neuro-biological studies showing that the brain is able to carry out close to 100,000 billion FLOPS per unit of Watt, while today's latest supercomputer can achieve only around 10 billion FLOPS per unit Watt [1, 2]. The superior computational efficiency of biological systems has inspired the quest to reverse engineer the brain in order to develop intelligent computing platforms that can learn to execute a wide variety of data analytics and inference tasks [3]. However, in spite of several decades of research, the principles of information processing in the brain is not yet fully understood, and efforts to mimic its power efficiency and fault-tolerance in computing systems remain unfulfilled. The ongoing quest towards understanding the functioning of the brain has propelled research towards reverse engineering the brain for various neurological studies, through computational neuroscience techniques [4]. Additionally, the field of artificial intelligence has also taken inspiration from the neural architecture of the brain, with the result of Deep Learning framework emerging as the state-of-the-art for various cognitive and data processing tasks. In particular, inspired by the Nobel prize winning work of Hubel and Weisel on elucidating the mechanisms of information representation in the visual cortex [5], multi-layer convolutional neural networks have shown impressive performance for a wide variety of applications such as image recognition, natural language processing, speech recognition and video analytics [6–15].

The field of neuromorphic engineering tries to mimic the key computational aspects of biological computations in silicon circuits. Earliest works by Carver Mead at Caltech describe sub-threshold VLSI circuit designs mimicking the neuron's membrane potential dynamics [16]. During the last decade, there have been a number of demonstrations of sensory data acquisition systems inspired by the cochlea, retina, etc. [17–20]. To make neural networks more biologically plausible, a new generation of learning models have emerged called the spiking neural networks (SNNs). These models mimic event based data processing and communication aspects of biological neurons. Neuro-biological studies have also shown that the rate of spikes in the brain is very small, 0.1 to 300 Hz [21]. This low operational firing rate has been postulated to be one of the reasons for the brain's high energy efficiency.

Inspired by this brain-inspired asynchronous computing paradigm, several neuromorphic hardware designs have been demonstrated with significant computational efficiency improvements [22–25]. These neuromorphic SNN accelerator architectures closely integrate the memory and logic units in order to minimize the cost of data transfers associated with conventional von Neumann architectures. However, these digital hardware platforms make use of on-chip SRAM to store the network parameters which has limited density. For running larger neural network models, these platforms have to make use of larger density DRAMs (which are primarily off-chip). Additionally, DRAMs are slower in access and consume more power as they need to be refreshed periodically. For building efficient and compact hardware accelerators, there is a need for memory technologies with smaller form factor and faster accesses.

Research over the last decade has led to the development of several nanoscale non-volatile memory devices such as phase change memory (PCM), spin-transfer torque RAM (STT-RAM), and resistive RAMs (RRAM), ideally suited for in-memory or near-memory computing with a crossbar based architecture. The conductance

states of these devices could be used to represent synaptic weights of large neural networks. Design studies suggest that memristive neural network accelerators with analog memory storage can potentially achieve significantly higher throughput compared to GPUs, provided several challenges typically associated with nanoscale devices can be addressed [26–33]. In particular, the crucial challenges include the variability and stochasticity associated with the device conductance, and the additive noise from the peripheral circuitry such as Analog to Digital converters (ADCs) and Digital to Analog Converters (DACs) [26, 34–36].

In this dissertation, we start by discussing the principles to encode and train a system using just binary spikes, akin to the action potentials seen in the brain. We explore two of the existing spike based supervised learning algorithms - Remote Supervised Method (ReSuMe) and the Normalized Approximate Descent (NormAD), in terms of optimizing them for efficient hardware realizations. As the NormAD algorithm is shown be be faster at its convergence, we apply this rule to train an SNN for solving the problem of handwritten digit classification [37]. We also show that this spike based algorithm performs similar to an equivalent network with non-spiking neurons (ANNs) in terms of its classification accuracy. We also discuss the various insights from our network training and optimization studies for an eventual efficient implementation. This part of the research was carried out by developing a CUDA (Compute Unified Device Architecture) simulator to be run on a GP-GPU (General Purpose Graphical Processing Unit) card.

Building better hardware for realizing SNNs has also been emphasized by the research community, as is demonstrated by the chips of IBM, Intel, etc. [22,23,25]. In this direction, we present the basic units of designing an ASIC (Application Specific Integrated Circuit) for hardware acceleration of SNNs, which forms the second part of this dissertation. The key studies and contributions of this work are as following:

- 1. Network optimization in terms of spike based temporal features for a supervised learning algorithm, and their comparison with existing class of networks.

- 2. Architectural framework using existing and emerging memory devices for realizing spike based learning on hardware.

- 3. Development of mathematically well-posed compact models for non volatile memory (NVM) devices with reliability features.

- 4. Hardware design and throughput comparison of STT-RAM based accelerator for SNNs.

### 1.2 Organization of the Dissertation

The research work described in this dissertation is comprised of two parts. The first part focuses on SNN algorithms and second part on the hardware design.

Chapter 2 presents a background on bio-inspired computing and the learning mechanism observed in neuro-biological studies. We then present the SNN developed for solving the handwritten digit classification problem in Chapter 3. We also present CUDA based software acceleration of this SNN on a GP-GPU.

Chapter 4 presents the compact models for the NVM devices that we built and use in our further architecture development and analysis. We also present the process of introducing conductance variabilities and faults in the model simulation. We discuss the design of three models: Phase Change Memory (PCM), Spin Transfer Torque RAM (STT-RAM), and Resistive RAM (RRAM) devices.

In Chapter 5, we present the non-von Neumann architecture design for accelerating neural networks, specifically the SNNs. Here, we discuss a CMOS (Complementary Metal-Oxide Semiconductor)-based digital design for an SNN along with the spike based Remote Supervised Method (ReSuMe) training rule [38]. We then present the prospects of using an NVM crossbar array with near-memory compute approach for accelerating SNNs. We explore the analog (multiple levels in a single device) and digital (two levels within a device) storage arrays with NVM devices. For the digital NVM array, we compare the design realization with PCM,

RRAM, and STT-RAM memory arrays. Finally, we present the STT-RAM based design for learning and inference, and also compare its inference performance with an equivalent SRAM based design. Chapter 6 summarizes and concludes the dissertation. We also present a discussion on the future trends in this area of research and the challenges that need to be addressed.

Appendix A gives the details of the ReSuMe and NormAD algorithm parameters and the simulation procedures. Appendix B lists the parameters used in developing the compact models for the three NVM devices (PCM, STT-RAM, and RRAM) discussed in this dissertation in Chapter 4.

#### CHAPTER 2

#### BIO-INSPIRED COMPUTING AND HARDWARE DESIGN

Nature has always been a inspiration for various fields of engineering, ranging from mechanical to computing [39]. Studies on the human visual cortex system have inspired the development of deep convolution neural networks (CNNs) [5,6]. The ground breaking work by Yann LeCun on training CNNs [6], followed by the ILSVRC-2012 challenge winning CNN by Alex Krizhevksy [40] has led to the development of many improved network architectures and training techniques to develop deep networks with super-human level accuracy [7,9–13,41].

Parallel to artificial neural networks, the third generation of neural networks called Spiking Neural Networks (SNNs) have also been emerging as a potential computing framework to solve machine learning problems. Similar to the time-based information encoding using action potential transmitted by nerve cells, SNNs operate by making use of precise timings of all-or-none spikes transmitted between neurons [42, 43]. These networks, which are capable of employing the temporal dimension through memory based neuronal dynamics and synaptic delays, have been successfully shown to emulate the different spike-firing dynamics in the brain [44].

Throughout this dissertation, we use the term artificial neural networks (ANNs) to denote the non-spiking networks. The background details of these two different types of neural networks will be discussed in the following sections.

#### 2.1 Artificial Neural Networks