**Raúl Martínez Moráis**

## PROVIDING QUALITY OF SERVICES IN SYSTEMS BASED ON ADVANCES SWITCHING

I.S.B.N. Ediciones de la UCLM 978-84-8427-641-8

Cuenca, 2008

### UNIVERSIDAD DE CASTILLA-LA MANCHA DEPARTAMENTO DE SISTEMAS INFORMÁTICOS

## Providing Quality of Service in Systems Based on Advanced Switching

Tesis Doctoral presentada al Departamento de Sistemas Informáticos de la Universidad de Castilla-La Mancha para la obtención del título de Doctor en Informática

> Presentada por: Raúl Martínez Moráis

Dirigida por:

Dr. D. Francisco José Alfaro Cortés Dr. D. José Luis Sánchez García

Albacete, Julio de 2007

## Agradecimientos

Esta tesis es fruto de un trabajo que no hubiera sido posible sin el apoyo y ayuda de muchas personas. Quiero aquí dedicarles mi más sincero agradecimiento.

En primer lugar quiero darle las gracias a mis tutores, Paco y José Luis, por su guía, apoyo, paciencia y amistad durante estos años. Sin duda este trabajo no hubiera sido posible sin ellos.

Quiero agradecer también a la gente del Departamento de Sistemas Informáticos, especialmente al grupo de Redes y Arquitecturas de Altas Prestaciones (RAAP), su apoyo material y financiero, pero sobre todo humano.

No puedo olvidarme de mis compañeros becarios del RAAP y del Instituto de Investigación en Informática de Albacete (I3A), especialmente de Alejandro, por su compañerismo, apoyo y ayuda durante estos años.

Por último, quiero dar mi más cariñoso agradecimiento a mis padres, Emilio y Cristina. Esta tesis es también fruto de su esfuerzo, sacrificio y amor incondicional. Y también a mi familia y amigos, especialmente a Alfonso, por todo el apoyo y cariño que me han dado, a pesar de todo el tiempo que la tesis me ha impedido dedicarles. Gracias por compartir conmigo los buenos y malos momentos.

A todos gracias, sin vosotros no hubiera sido posible llegar hasta aquí.

## Resumen

Advanced Switching (AS) es una tecnología de red basada en PCI Express. PCI Express es la nueva generación PCI, la cual está ya reemplazando el extensivamente usado bus PCI. AS es una extrapolación de PCI Express que toma prestadas sus dos capas arquitecónicas de más bajo nivel e incluye una capa de transacciones optimizada para permitir nuevas capacidades como la comunicación *peer-to-peer*. Mientras que PCI Express ya ha empezado a reformar una nueva generación de ordenadores personales y servidores tradicionales, una red de interconexión común con la industria de las comunicaciones parece lógico y necesario. Así pues, AS estaba pensado para proliferar en los entornos de multiprocesadores, sistemas *peer-to-peer* en las comunicaciones, almacenamiento, redes de interconexión, servidores y plataformas empotradas.

Por otro lado, la calidad de servicio (Quality of Service, QoS) se está convirtiendo en una característica importante para las redes de altas prestaciones. Proporcionar QoS en entornos de computación y comunicaciones es actualmente el centro de muchos esfuerzos de investigación por parte de la industria y en el ámbito académico. AS incorpora mecanismos que pueden ser usados para proporcionar QoS. En concreto, AS permite utilizar Canales Virtuales (Virtual Channels, VCs), arbitraje en los puertos de salida y un mecanismo de control de admisión. Además, AS proporciona un control de flujo a nivel de enlace y VC. Estos mecanismos nos permiten agregar el tráfico con características similares en un mismo VC y proporcionar a cada VC un tratamiento diferenciado en base a sus requisitos.

El objetivo principal de la tesis ha sido el estudio de los diferentes mecanismos de AS con el fin de proponer un marco general para proporcionar QoS a las aplicaciones sobre esta tecnología de red. En este sentido, el foco principal del trabajo, dada su importancia para proporcionar QoS, ha sido sido el estudio de los mecanismos de planificación de AS. Nuestro objetivo ha sido implementarlos de una manera eficiente, teniendo en cuenta tanto sus prestaciones como su complejidad. Para conseguir estos objetivos, hemos propuesto varias posibles implementaciones del planificador de mínimo ancho de banda de AS. Hemos propuesto modificar el planificador basado en tabla de AS con el objetivo de solucionar los problemas de éste para proporcionar requisitos de QoS con tamaños de paquete variable. Hemos también propuesto cómo configurar el planificador basado en tabla resultante para desacoplar las asignaciones de ancho de banda y latencia. Además, hemos llevado a cabo un diseño *hardware* de los diferentes planificadores para obtener estimaciones sobre el tiempo de arbitraje y el área de silicio que requieren. Además, hemos desarrollado nuestro propio simulador para evaluar las prestaciones de nuestras propuestas.

### Summary

Advanced Switching (AS) is a network technology based on PCI Express. PCI Express is the next PCI generation, which is already replacing the extensively used PCI bus. AS is an extrapolation of PCI ExpressSummary that borrows its lower two architectural layers and includes an optimized transaction layer to enable new capabilities like peer-to-peer communication. Whereas PCI Express has already begun to reshape a new generation of PCs and traditional servers, a common interconnect with the communications industry seems logical and necessary. In this way, AS was intended to proliferate in multiprocessor, peer-to-peer systems in the communications, storage, networking, servers, and embedded platform environments.

On the other hand, Quality of Service (QoS) is becoming an important feature for high-performance networks. The provision of QoS in computing and communication environments is currently the focus of much discussion and research in industry and academia. AS provides mechanisms that can be used to support QoS. Specifically, an AS fabric permits us to employ Virtual Channels (VCs), egress link scheduling, and an admission control mechanism. Moreover, AS performs a link-level flow control in a per VC basis. These mechanisms allow us to aggregate traffic with similar characteristics in the same VC and to provide each VC with a different treatment according to its requirements.

The main objective of this thesis has been to study the different AS mechanisms in order to propose a general framework for providing QoS to the applications over this network technology. In this line, the main focus of this work, due to its importance for the QoS provision, is the study of the AS scheduling mechanisms. Our goal has been to implement them in an efficient way, taking into account both their performance and their complexity. In order to achieve these objectives, we have proposed several possible implementations for the AS minimum bandwidth egress link scheduler taking into account the link-level flow control. We have proposed to modify the AS table-based scheduler in order to solve its problems to provide QoS requirements with variable packet sizes. We have also proposed how to configure the resulting table-based scheduler to decouple the bandwidth and latency assignations. Moreover, we have performed a hardware design of the different schedulers in order to obtain estimates on the arbitration time and the silicon area that they require. We have also developed our own network simulator in order to evaluate the performance of our proposals.

## Contents

| 1        | $\operatorname{Intr}$ | oducti   | lon                                                                                                   | 1               |

|----------|-----------------------|----------|-------------------------------------------------------------------------------------------------------|-----------------|

|          | 1.1                   | QoS in   | n High-Performance Networks                                                                           | 1               |

|          | 1.2                   | Advan    | ced Switching                                                                                         | 2               |

|          | 1.3                   | Motiva   | ation and Objectives                                                                                  | 3               |

|          | 1.4                   | Organ    | ization of the Thesis                                                                                 | 6               |

| <b>2</b> | Hig                   | h-Perf   | ormance Networks                                                                                      | 9               |

|          | 2.1                   | Netwo    | rk classification                                                                                     | 10              |

|          |                       | 2.1.1    | Shared medium networks                                                                                | 10              |

|          |                       | 2.1.2    | Direct networks                                                                                       | 10              |

|          |                       | 2.1.3    | Indirect networks                                                                                     | 11              |

|          | 2.2                   | Switch   | ning techniques                                                                                       | 11              |

|          |                       | 2.2.1    | Circuit switching                                                                                     | 12              |

|          |                       | 2.2.2    | Packet switching                                                                                      | 12              |

|          |                       | 2.2.3    | Wormhole switching                                                                                    | 14              |

|          | 2.3                   | Switch   | architecture                                                                                          | 14              |

|          |                       | 2.3.1    | Central buffer                                                                                        | 15              |

|          |                       | 2.3.2    | Output queuing                                                                                        | 16              |

|          |                       | 2.3.3    | Input queuing                                                                                         | 16              |

|          |                       | 2.3.4    | Combined input and output queuing                                                                     | 17              |

|          |                       | 2.3.5    | Combined input-crosspoint queuing                                                                     | 18              |

|          | 2.4                   | Lossy    | versus lossless networks                                                                              | 18              |

|          |                       | 2.4.1    | Lossy networks                                                                                        | 19              |

|          |                       | 2.4.2    | Lossless networks                                                                                     | 19              |

| 3        | QoS                   | in Hi    | gh-Performance Networks                                                                               | 23              |

| 0        | 3.1                   |          | 0                                                                                                     | <b>2</b> 4      |

|          | 3.2                   |          | $c$ classes $\ldots$ | 26              |

|          | 3.3                   |          | w versus per class QoS provision                                                                      | $\frac{20}{28}$ |

|          | 3.4                   |          |                                                                                                       | 30              |

|          | 0.1                   | 3.4.1    | 0                                                                                                     | 31              |

|          |                       | 3.4.2    | Policing/Shaping                                                                                      | 31              |

|          |                       | <b>.</b> | $O_{i}$ - $r$ - $O$                                                                                   |                 |

|          |              | 3.4.3            | Packet scheduling                          | 32         |

|----------|--------------|------------------|--------------------------------------------|------------|

|          |              | 3.4.4            | HOL blocking elimination techniques        | 32         |

|          |              | 3.4.5            | QoS routing                                | 33         |

|          |              | 3.4.6            | Admission control                          | 33         |

|          |              | 3.4.7            | Network planning                           | 35         |

|          | 3.5          | Schedu           | lling algorithms                           | 36         |

|          |              | 3.5.1            | Fair queuing algorithms                    | 38         |

|          |              | 3.5.2            | Table-based schedulers                     | 46         |

| 4        | Adv          | anced            | Switching Review                           | 49         |

|          | 4.1          |                  | uction                                     | 49         |

|          | 4.2          |                  | architecture                               | 52         |

|          |              | 4.2.1            | Physical layer                             | 53         |

|          |              | 4.2.2            | Link layer                                 | 54         |

|          |              | 4.2.3            | Transaction layer                          | 54         |

|          | 4.3          | Packet           | format and routing                         | 55         |

|          |              | 4.3.1            | Unicast packets                            | 56         |

|          |              | 4.3.2            | Path building header                       | 58         |

|          |              | 4.3.3            | Protocol interface                         | 59         |

|          | 4.4          | Virtua           | l channels and traffic classes             | 60         |

|          | 4.5          |                  | stion management                           | 63         |

|          |              | 4.5.1            | Local status-based flow control            | 65         |

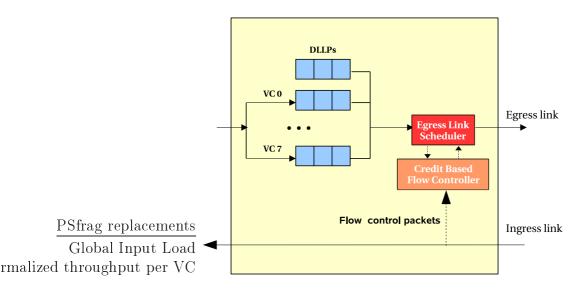

|          |              | 4.5.2            | Egress link scheduling                     | 66         |

|          |              | 4.5.3            | Endpoint source or injection rate limiting | 69         |

|          |              | 4.5.4            | Packet dropping                            | 70         |

|          |              | 4.5.5            | Admission control                          | 70         |

|          |              | 4.5.6            | Adaptation                                 | 70         |

| <b>5</b> | Imn          | lomont           | ting the MinBW Scheduler                   | 73         |

| J        | 5.1          |                  | uction                                     | <b>7</b> 3 |

|          | $5.1 \\ 5.2$ |                  | ted fair queuing credit aware (WFQ-CA)     | 79         |

|          | $5.2 \\ 5.3$ |                  | ocked fair queuing credit aware (SCFQ-CA)  | 81         |

|          | $5.3 \\ 5.4$ |                  | round robin credit aware (DRR-CA)          | 83         |

|          | $5.4 \\ 5.5$ |                  | ary                                        | 85         |

| 6        | The          | Dofie            | t Table Scheduler                          | 87         |

| 0        | 6.1          |                  | Table scheduling mechanism                 | 88         |

|          | 6.2          |                  | ling QoS with the DTable scheduler         | 00<br>91   |

|          | 6.3          |                  | ing the AS table scheduler                 | 91<br>97   |

|          | 0.0          | 6.3.1            | Using a constant value for all the entries | 97<br>98   |

|          |              | 6.3.2            | Using the 3-bit reserved field             | 98<br>98   |

|          |              | 0.3.2<br>6.3.3   |                                            | 90<br>101  |

|          |              | $0.3.3 \\ 6.3.4$ |                                            | L01<br>L03 |

|          |              | 0.0.4            | Using only one weight per VC               | LUO        |

|   | C 1 | 6.3.5 Final considerations                                             | 104          |

|---|-----|------------------------------------------------------------------------|--------------|

|   | 6.4 | Summary                                                                | 104          |

| 7 | Har | rdware implementation study of the schedulers                          | 107          |

|   | 7.1 | Handel-C and the DK design suite                                       | 108          |

|   | 7.2 | Modelling the egress queuing system                                    | 111          |

|   | 7.3 | Hardware implementation of the MinBW scheduler                         | 113          |

|   |     | 7.3.1 The DRR-CA scheduler                                             | 114          |

|   |     | 7.3.2 The SCFQ-CA scheduler                                            | 115          |

|   |     | 7.3.3 The WFQ-CA scheduler                                             | 116          |

|   |     | 7.3.4 Hardware estimates for the DRR-CA and SCFQ-CA schedulers         | 118          |

|   | 7.4 | Hardware implementation of the DTable scheduler                        | 121          |

|   |     | 7.4.1 Hardware estimates for the DTable scheduler                      | 122          |

|   | 7.5 | Comparing the MinBW and DTable schedulers                              | 127          |

|   | 7.6 | Summary                                                                | 131          |

| 8 | Cor | nfiguration of the AS mechanisms to provide QoS                        | 133          |

| Ŭ | 8.1 | Traffic classification                                                 | 133          |

|   | 8.2 | Scheduler configuration                                                | 135          |

|   | 0.2 | 8.2.1 Configuring the MinBW scheduler                                  | 136          |

|   |     | 8.2.2 Configuring the fixed weighted DTable scheduler                  | 136          |

|   |     | 8.2.3 Configuring the fully DTable scheduler                           | 137          |

|   | 8.3 | Admission control                                                      | 138          |

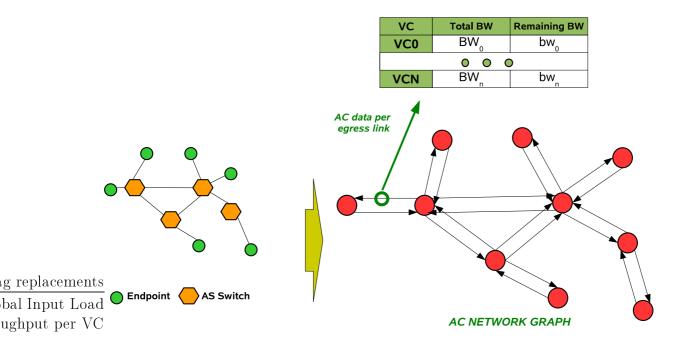

|   |     | 8.3.1 The bandwidth broker mechanism                                   | 140          |

|   |     | 8.3.2 Brokered and unbrokered traffic                                  | 141          |

|   |     | 8.3.3 Path selection and load balancing                                | 143          |

|   | 8.4 | Schedulers and bandwidth broker management                             | 144          |

|   | 8.5 | Summary                                                                | 145          |

| 0 | ъ   |                                                                        | 1 4 57       |

| 9 |     | formance evaluation                                                    | 147          |

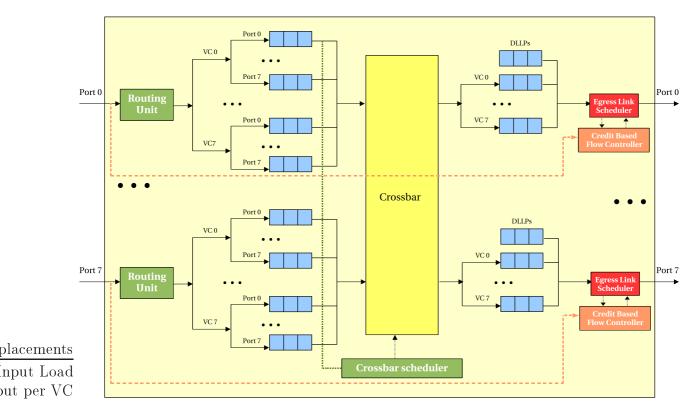

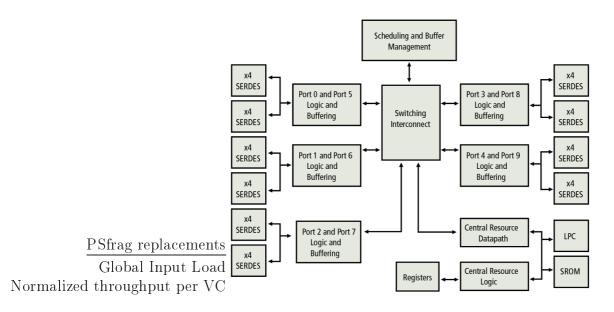

|   | 9.1 | Simulated architecture                                                 | 147          |

|   | 9.2 | Performance metrics                                                    | 149<br>151   |

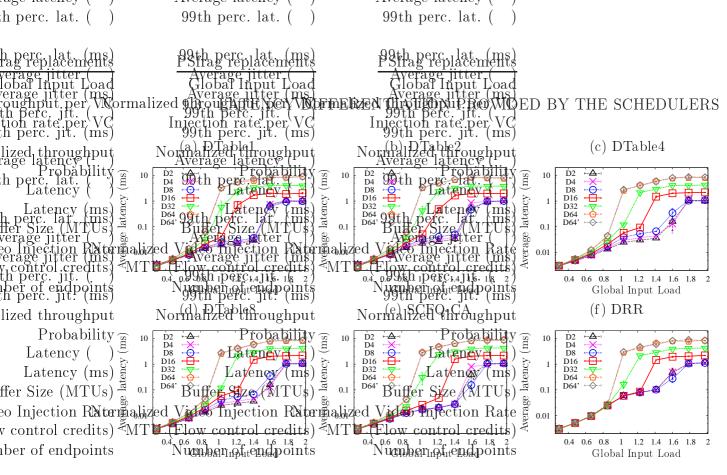

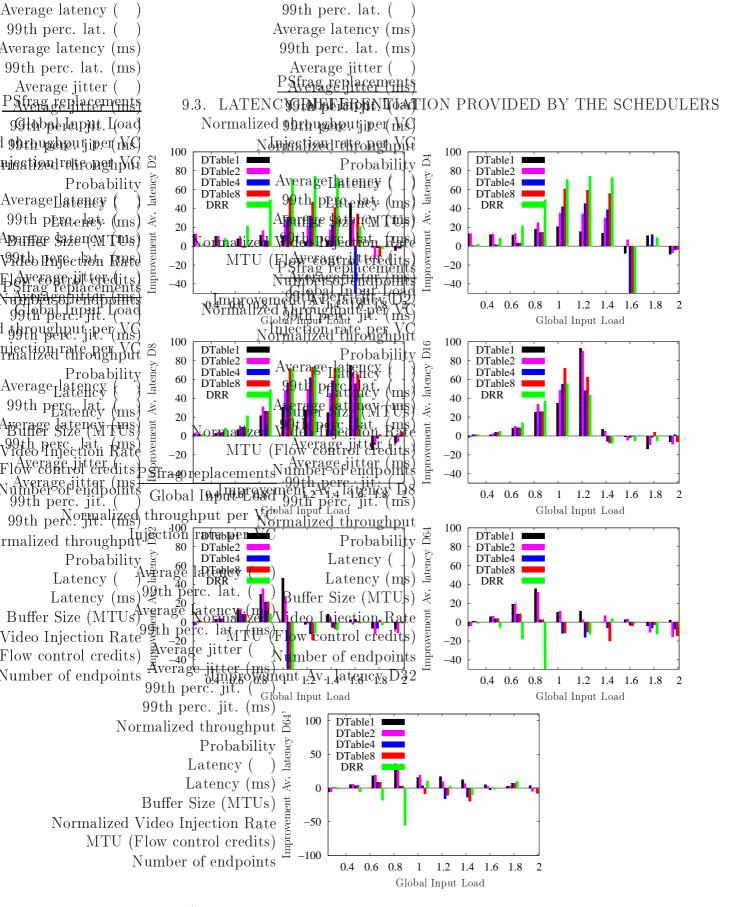

|   | 9.3 | Latency differentiation provided by the schedulers                     | 151          |

|   |     | <ul><li>9.3.1 Simulated scenario and scheduler configuration</li></ul> | 151<br>152   |

|   | 0.4 |                                                                        | 153<br>159   |

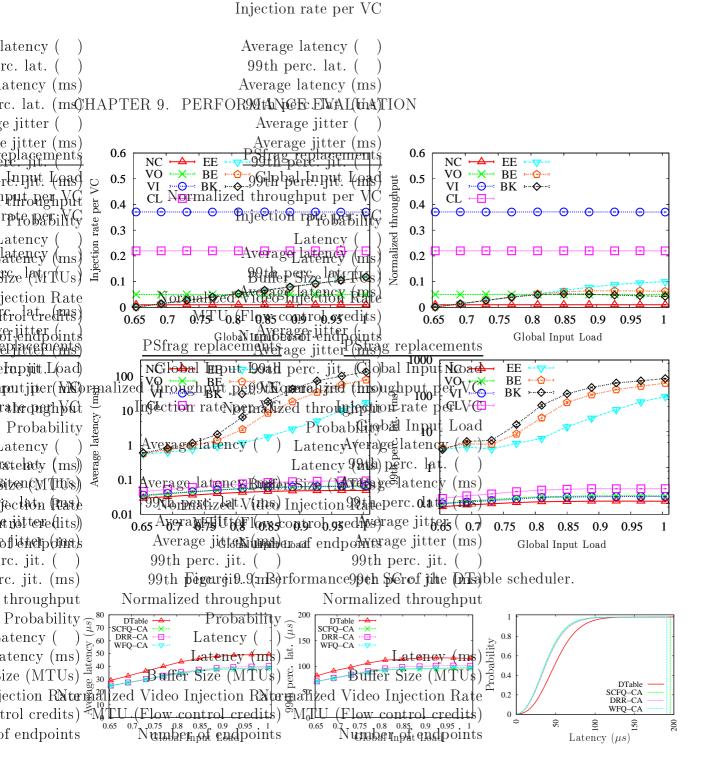

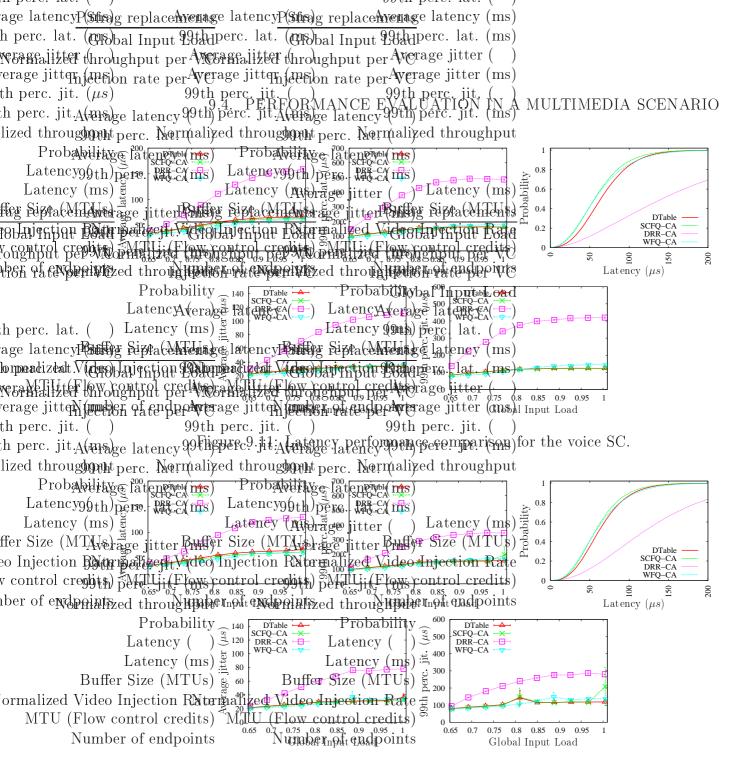

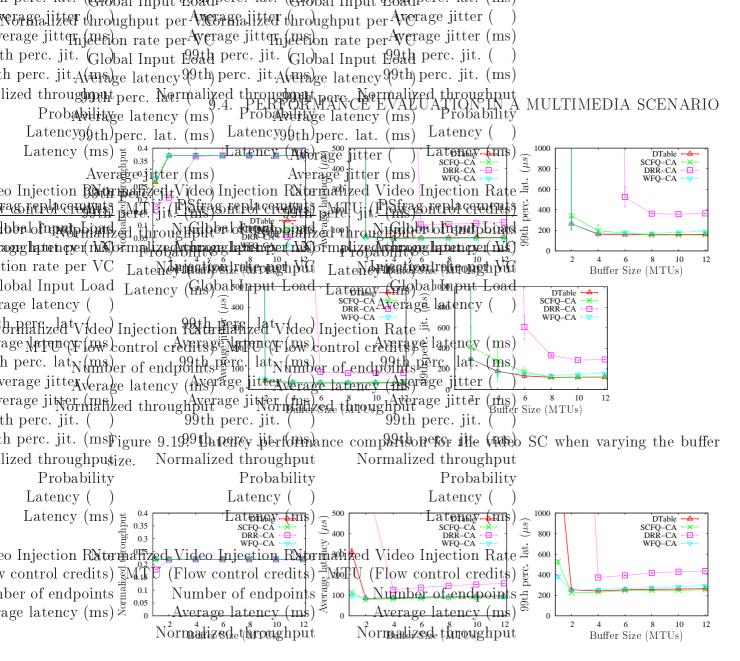

|   | 9.4 | Performance evaluation in a multimedia scenario                        | 158<br>159   |

|   |     | 9.4.1 Traffic model                                                    | $158 \\ 150$ |

|   |     | 9.4.2 Simulated scenario and scheduler configuration                   | 159<br>162   |

|   |     | 9.4.3 Simulation results of the basic multimedia scenario              | 163<br>167   |

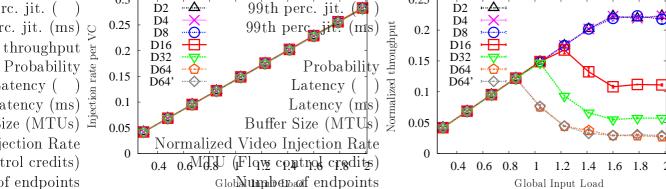

|   |     | 9.4.4 Effect of the video injection rate                               | 167          |

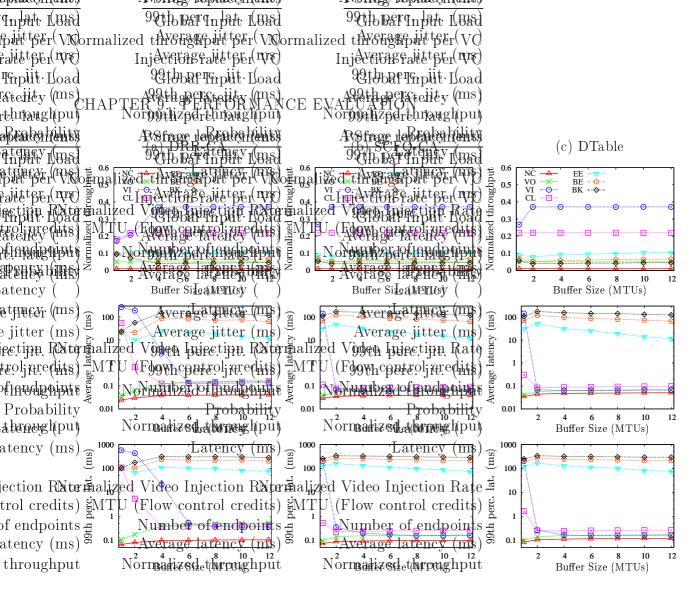

|   |     | 9.4.5 Effect of the buffer size                                        | 171<br>174   |

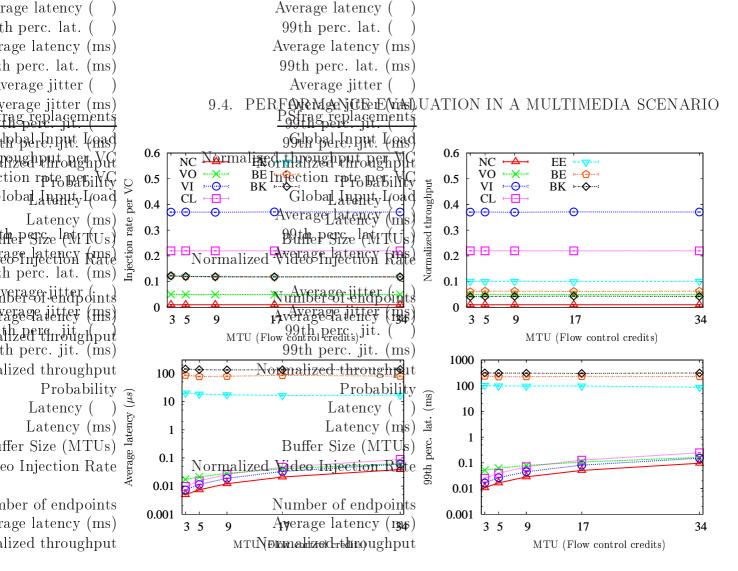

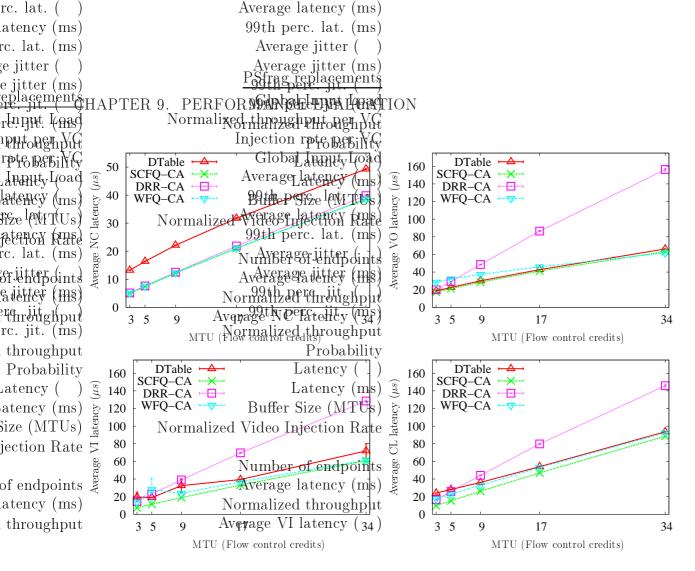

|   |     | 9.4.6 Effect of the MTU size                                           | 174<br>176   |

|   |     | 9.4.7 Effect of the network size                                       | 176          |

| 9.5 Conclusions                                                               | 178 |

|-------------------------------------------------------------------------------|-----|

| 10 Conclusions and future work                                                | 181 |

| 10.1 Conclusions and contributions                                            | 181 |

| 10.2 Applicability of our proposals in other technologies                     | 183 |

| 10.3 Publications                                                             | 184 |

| 10.3.1 International journals                                                 | 184 |

| $10.3.2$ International conference with proceedings published by LNCS $\ldots$ | 185 |

| 10.3.3 International conference with proceedings published by IEEE            | 185 |

| 10.3.4 Other international publications                                       | 186 |

| 10.4 Future Work                                                              | 187 |

| Bibliography                                                                  | 191 |

# List of Figures

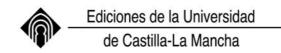

| 2.1  | Elements of stop and go flow control                                                                                         |

|------|------------------------------------------------------------------------------------------------------------------------------|

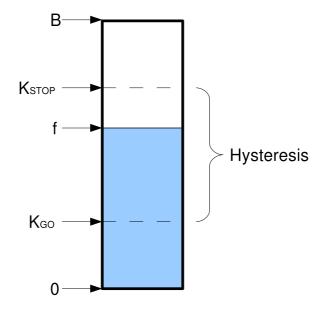

| 2.2  | Elements of credit-based flow control                                                                                        |

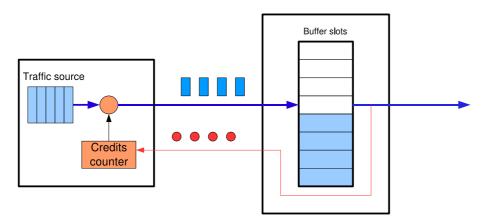

| 3.1  | Packet latency probability density                                                                                           |

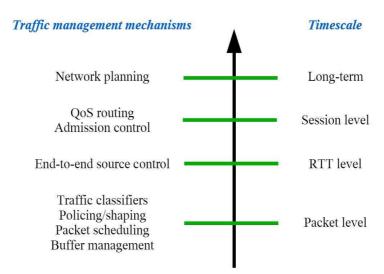

| 3.2  | Time scale hierarchy of QoS control mechanism                                                                                |

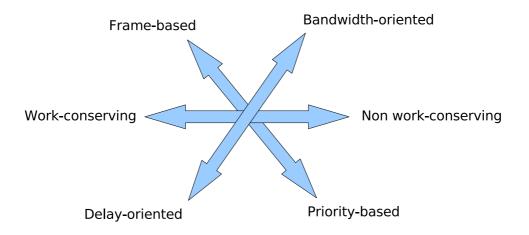

| 3.3  | Scheduler classification                                                                                                     |

| 3.4  | GPS fluid model                                                                                                              |

| 3.5  | Pseudocode of the SCFQ scheduler                                                                                             |

| 3.6  | Pseudocode of the DRR scheduler                                                                                              |

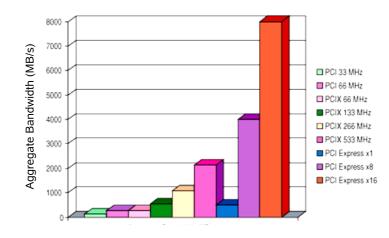

| 4.1  | PCI, PCI-X, and PCI Express bandwidth comparisons                                                                            |

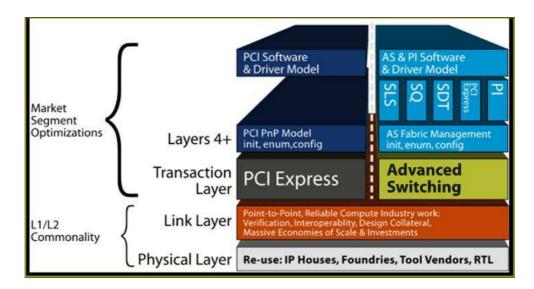

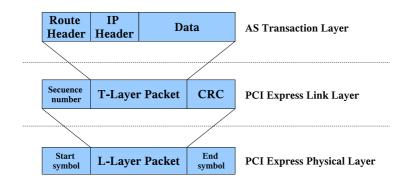

| 4.2  | AS layer architecture                                                                                                        |

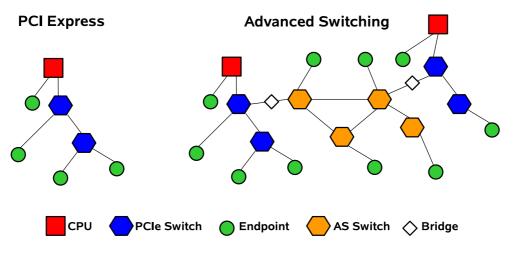

| 4.3  | PCI Express and AS example topologies                                                                                        |

| 4.4  | Structure of an Advanced Switching packet                                                                                    |

| 4.5  | Unicast route header format                                                                                                  |

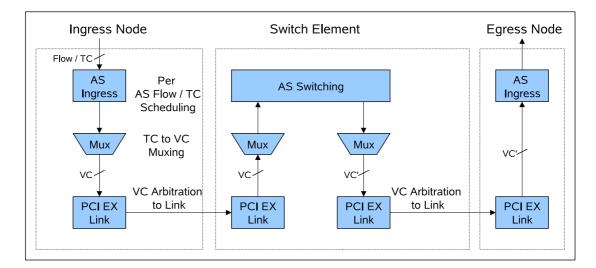

| 4.6  | TC to VC Aggregation Model                                                                                                   |

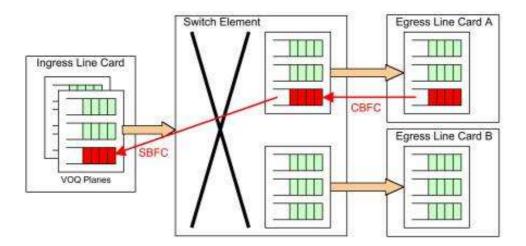

| 4.7  | SBFC and CBFC interaction example                                                                                            |

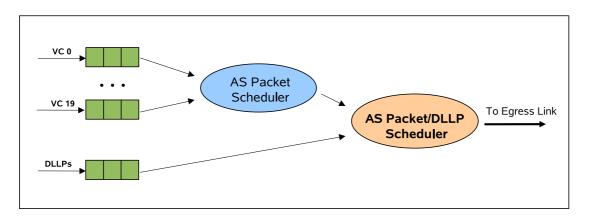

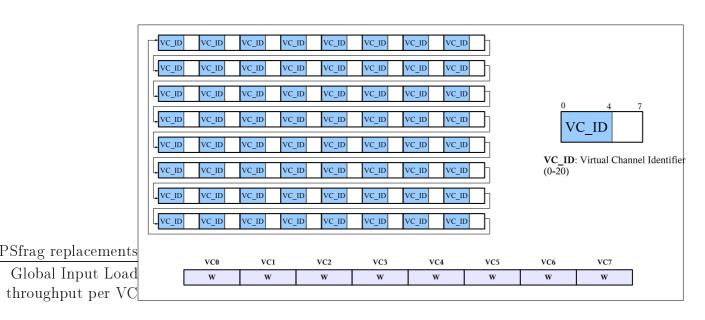

| 4.8  | Structure of an egress link scheduler for a port with 20 VCs                                                                 |

| 4.9  | Example of an arbitration table with 64 entries                                                                              |

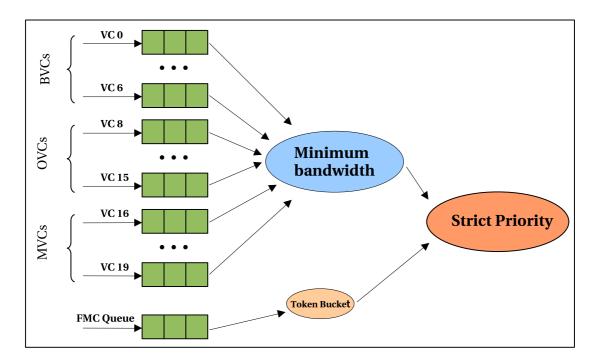

| 4.10 | Structure of the MinBW scheduler. Example with 20 VCs                                                                        |

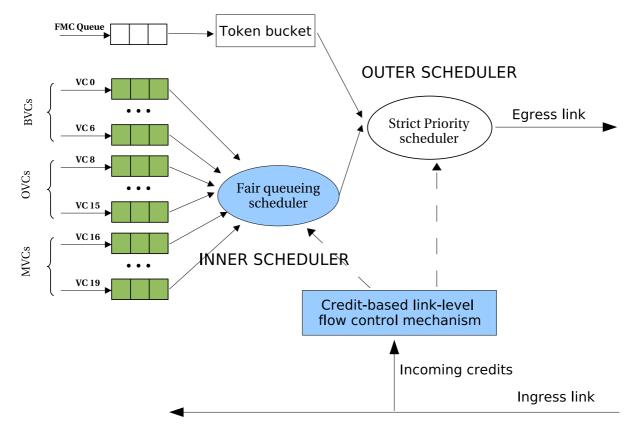

| 5.1  | Minimum bandwidth egress link scheduler                                                                                      |

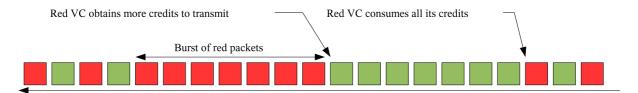

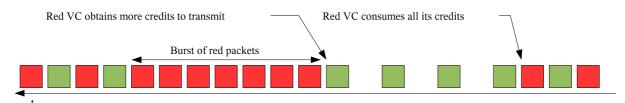

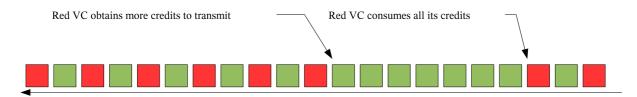

| 5.2  | Example of a VC taking advantage of the time it has been blocked. Well behaved VC uses bandwidth left over by the blocked VC |

| 5.3  | Example of a VC taking advantage of the time it has been blocked. Well                                                       |

|      | behaved VC does not use bandwidth left over by the blocked VC                                                                |

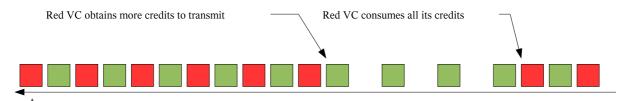

| 5.4  | Example of a VC that does not takes advantage of the time it has been                                                        |

|      | blocked. Well behaved VC uses bandwidth left over by the blocked VC 78                                                       |

| 5.5  | Example of a VC that does not takes advantage of the time it has been                                                        |

|      | blocked. Well behaved VC does not use bandwidth left over by the blocked                                                     |

|      | VC                                                                                                                           |

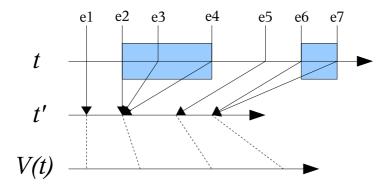

| 5.6  | Time line in the MinBW WFQ-CA implementation                                                                                 |

| 5.7  | Pseudocode of the SCFQ-CA scheduler                                                                                          |

| 5.8  | Pseudocode of the improved SCFQ-CA scheduler                                                                                 |

| 5.9         | Pseudocode of the DRR-CA scheduler                                                                               | 85           |

|-------------|------------------------------------------------------------------------------------------------------------------|--------------|

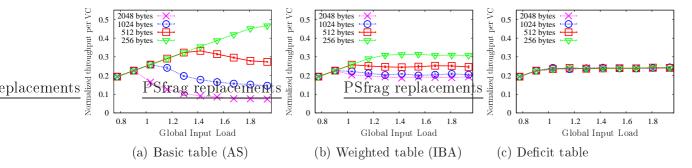

| 6.1         | Performance of several table-based schedulers for flows with different packet                                    |              |

| 6.2         | size                                                                                                             | 88<br>89     |

| 6.3         | Pseudocode of the DTable scheduler                                                                               | - 89<br>- 90 |

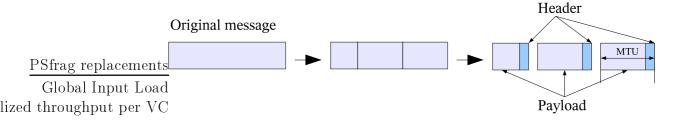

| 6.4         | Process of message fragmentation into packets.                                                                   | 97           |

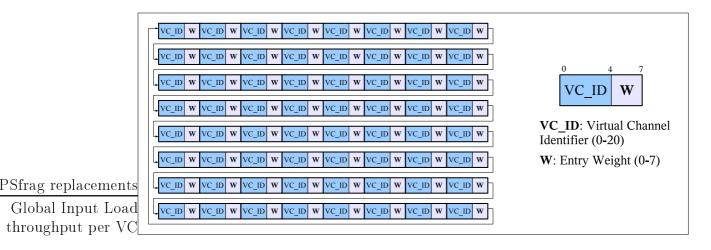

| 6.5         | Example of using the 3-bit reserved field                                                                        | 99           |

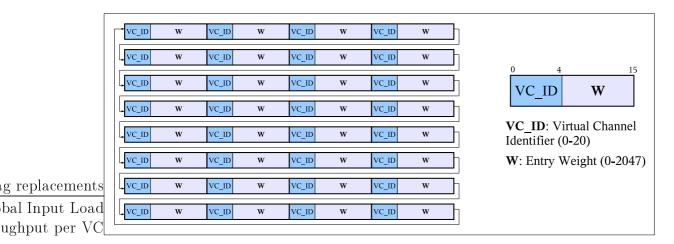

| 6.6         | Example of modifying the arbitration table format.                                                               | 102          |

| 6.7         | Example of using one weight per VC                                                                               | 103          |

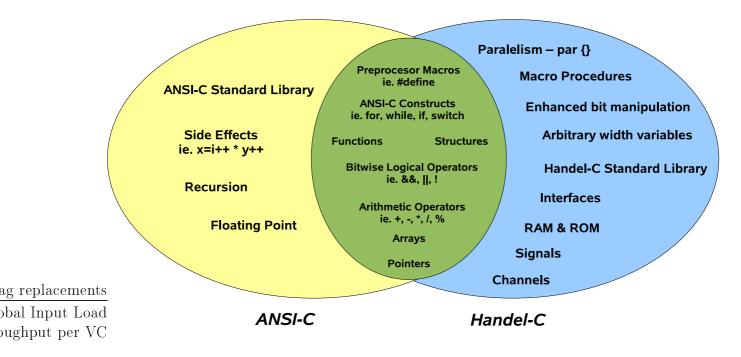

| 7.1         | ANSI-C / Handel-C comparison.                                                                                    | 109          |

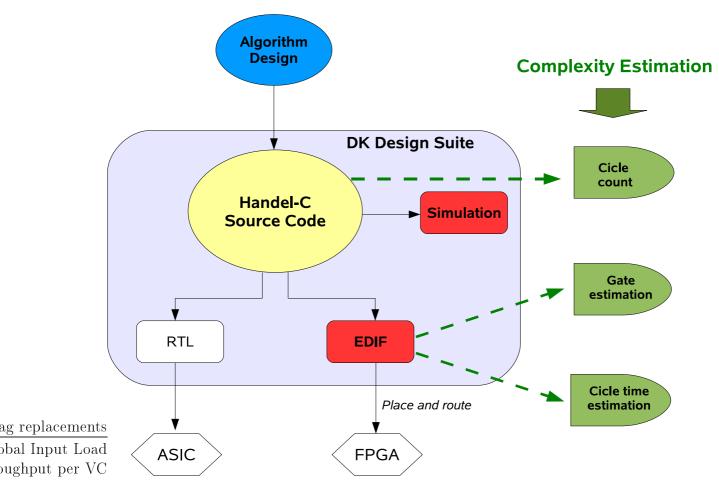

| 7.2         | Design flow with DK employing Handel-C                                                                           | 111          |

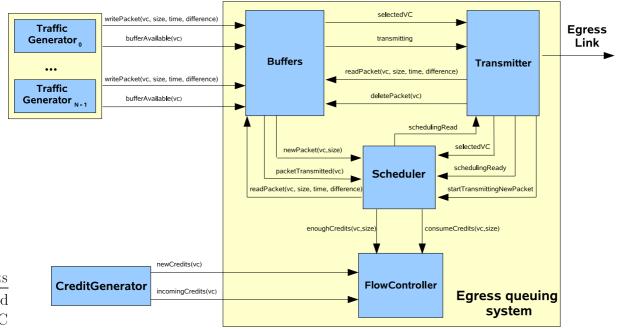

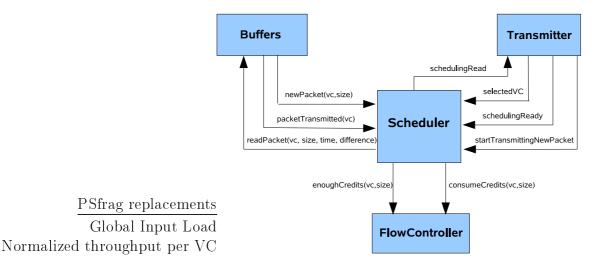

| 7.3         | Egress link queuing system modules.                                                                              | 112          |

| 7.4         | Scheduler module                                                                                                 | 113          |

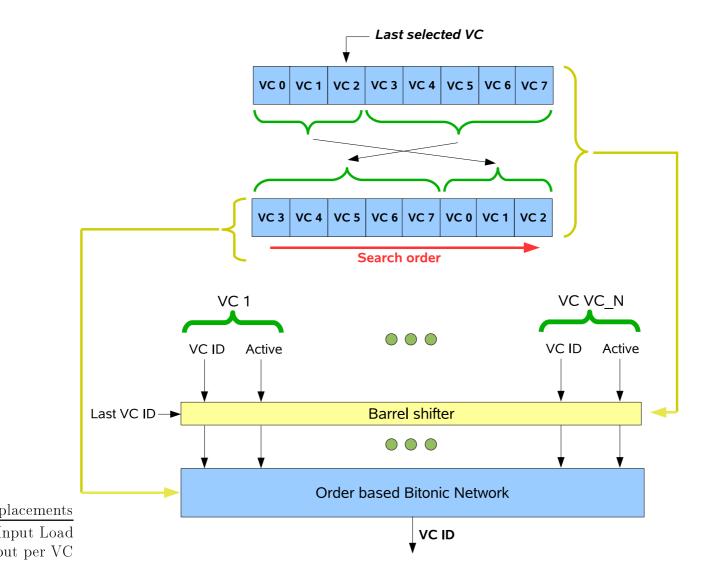

| 7.5         | Structure of the module that selects the next VC to transmit in the DRR-CA scheduler.                            | 114          |

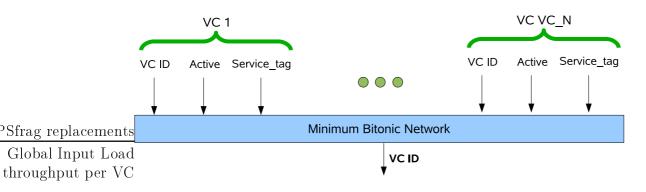

| 7.6         | Structure of the selector module for the SCFQ-CA scheduler                                                       | 116          |

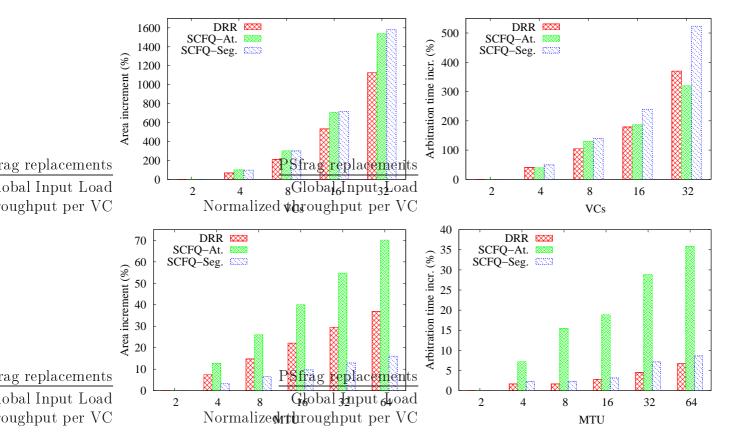

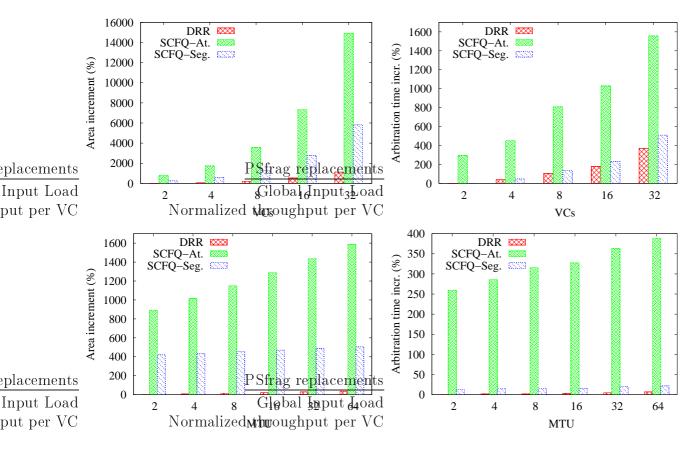

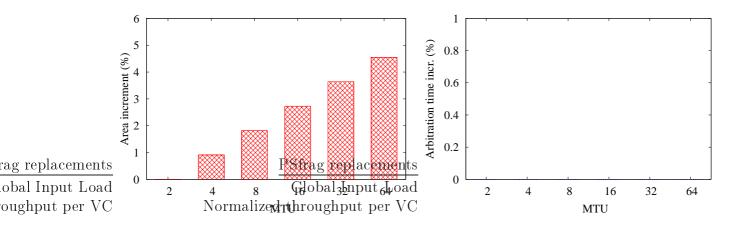

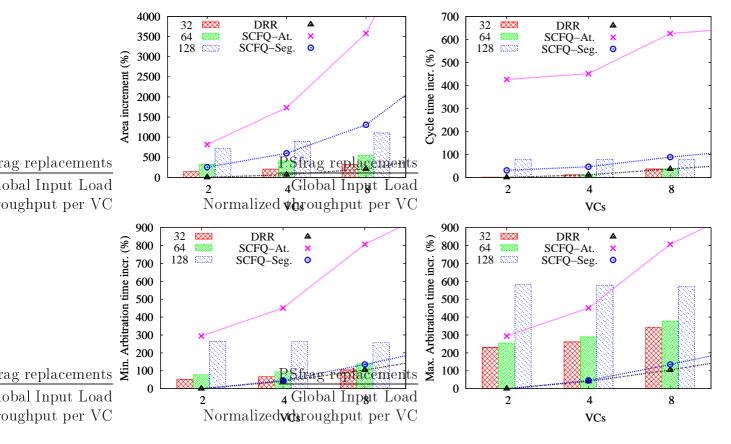

| 7.7         | Effect of the number of VCs and MTU over the silicon area and arbitration                                        |              |

|             | time required by the DRR-CA and the SCFQ-CA schedulers                                                           | 119          |

| 7.8         | Comparison of the silicon area and arbitration time required by the DRR-                                         |              |

|             | CA and the SCFQ-CA schedulers                                                                                    | 120          |

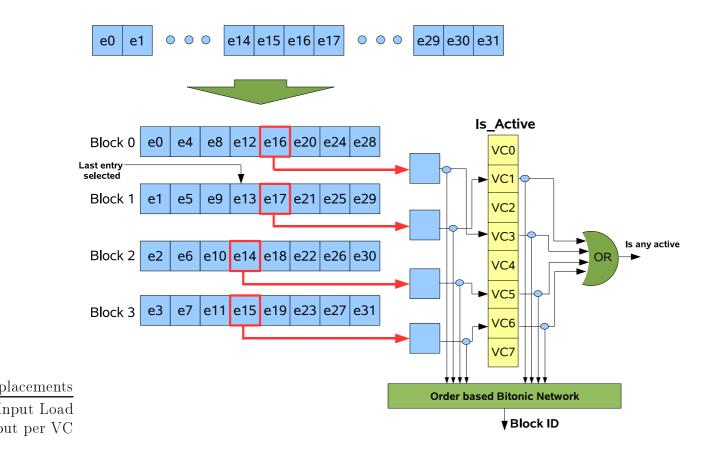

| 7.9         | Structure of the selector module for the parallel table scheduler.                                               | 122          |

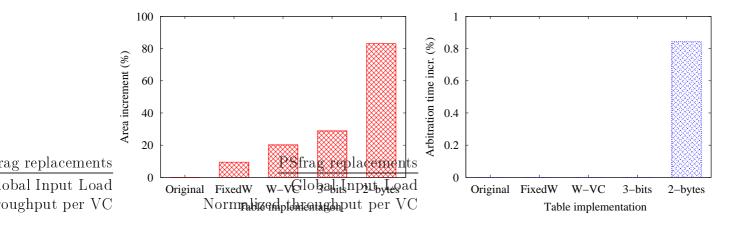

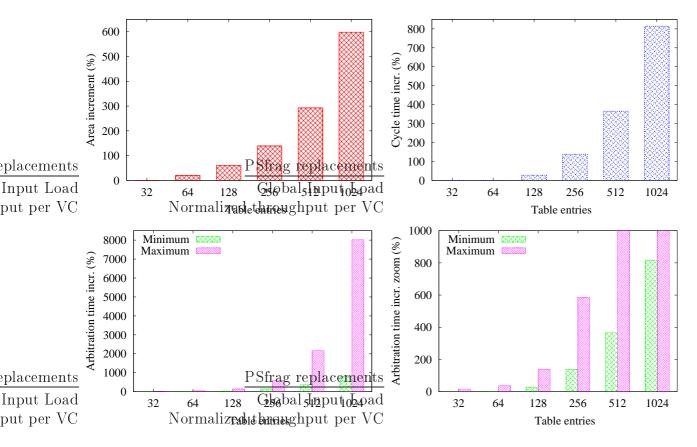

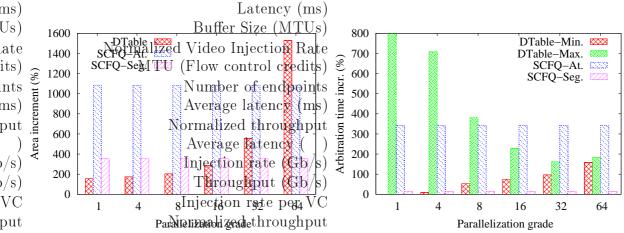

| 7.10        | Complexity comparison of the different possible implementations of the DTable scheduler.                         | 123          |

| 7 11        | Effect of the number of VCs over the silicon area and arbitration time re-                                       | 120          |

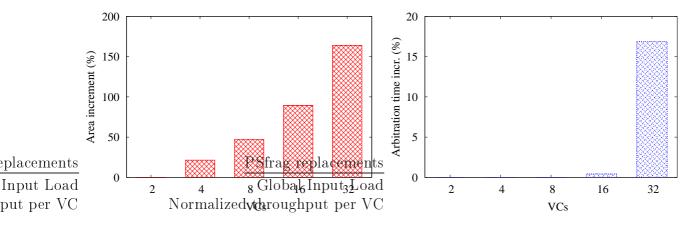

| 1.11        | quired by the DTable scheduler.                                                                                  | 124          |

| 7.12        | Effect of the number of the MTU over the silicon area and arbitration time                                       |              |

|             | required by the DTable scheduler                                                                                 | 125          |

| 7.13        |                                                                                                                  |              |

| <b>∀</b> 14 | time required by the DTable scheduler                                                                            | 126          |

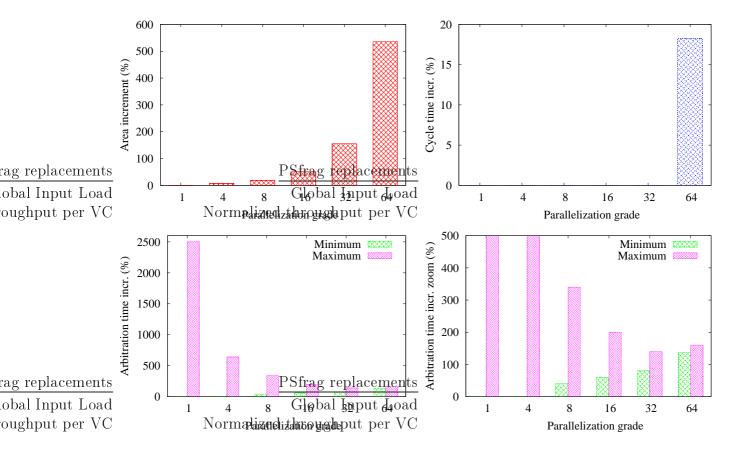

| (.14        | Effect of the parallelization grade over the silicon area and arbitration time required by the DTable scheduler. | 127          |

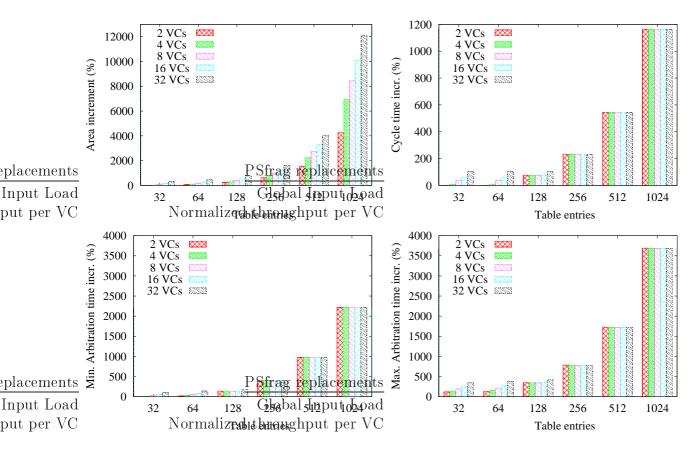

| 7 15        | Silicon area and arbitration time increment for the combined effect of the                                       | 121          |

| 1.10        | number of table entries and number of VCs for the DTable scheduler                                               | 128          |

| 7.16        | Silicon area and arbitration time comparison of the different schedulers with                                    |              |

|             | a small number of VCs                                                                                            | 129          |

| 7.17        | 1                                                                                                                |              |

|             | a high number of VCs                                                                                             | 130          |

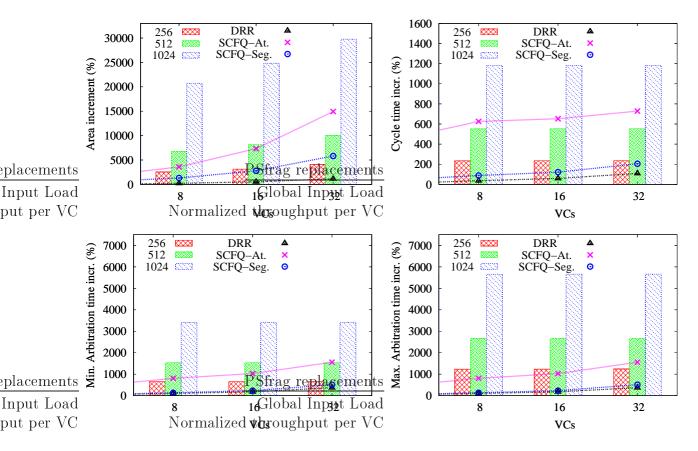

| 8.1         | Example of the graph required by the bandwidth broker                                                            | 140          |

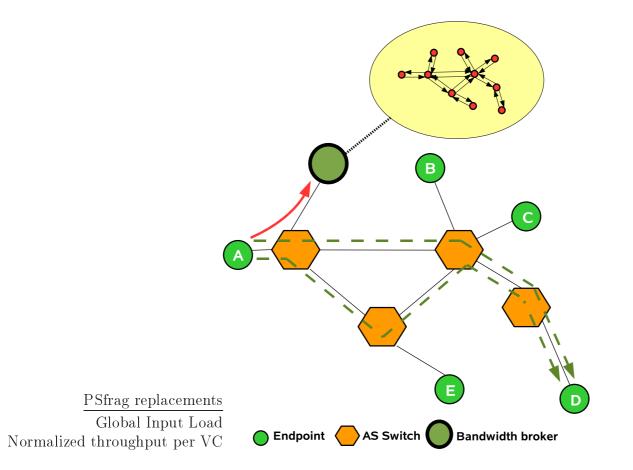

| 8.2         | Example of a centralized bandwidth broker AC mechanism                                                           | 141          |

| 8.3         | Example of a network with different number of VCs it its links                                                   | 142          |

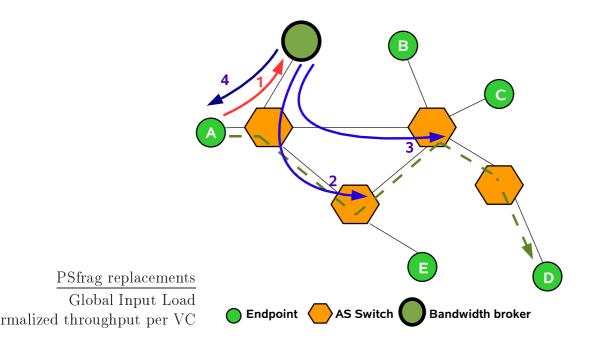

| Example of multiple possible paths to the same destination.               | 143                                        |

|---------------------------------------------------------------------------|--------------------------------------------|

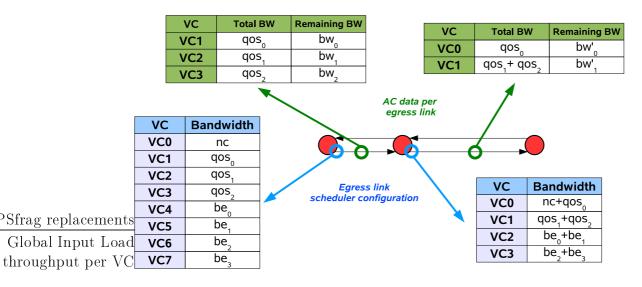

| Example of dynamic bandwidth distribution                                 | 144                                        |

|                                                                           | 1 10                                       |

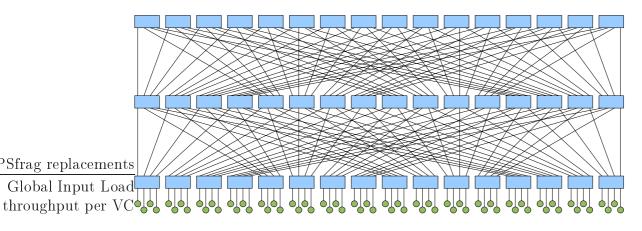

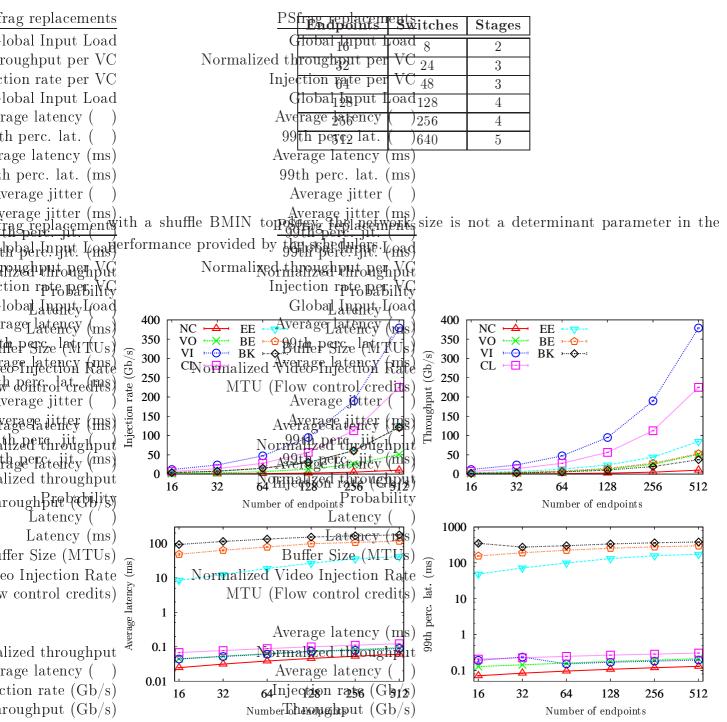

|                                                                           | 148                                        |

|                                                                           | 148                                        |

| 8                                                                         | 149                                        |

|                                                                           | 150                                        |

| · · · · · · · · · · · · · · · · · · ·                                     | 154                                        |

|                                                                           | 155                                        |

|                                                                           |                                            |

|                                                                           | 157                                        |

| 0                                                                         | 161                                        |

|                                                                           | 164                                        |

|                                                                           | 164                                        |

| Latency performance comparison for the voice SC                           | 165                                        |

| Latency performance comparison for the video SC                           | 165                                        |

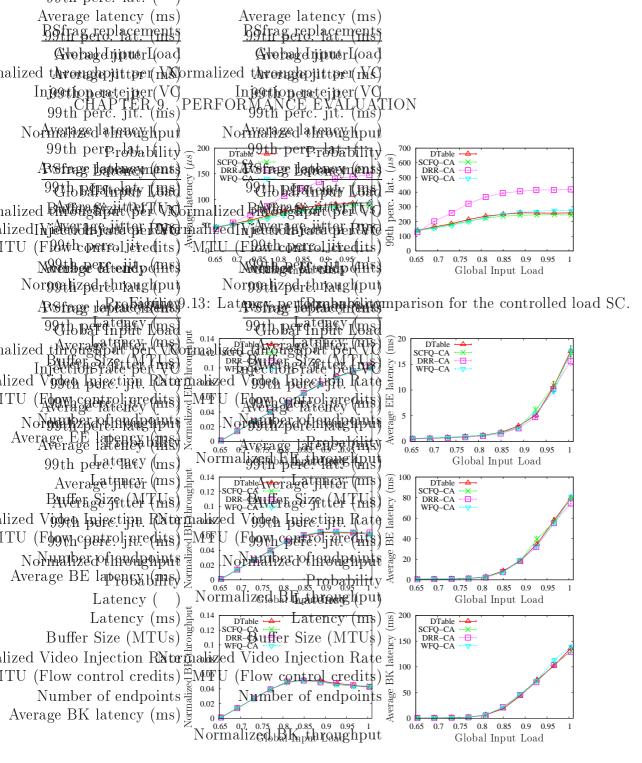

| Latency performance comparison for the controlled load SC                 | 166                                        |

| Latency performance comparison for the best-effort SCs                    | 166                                        |

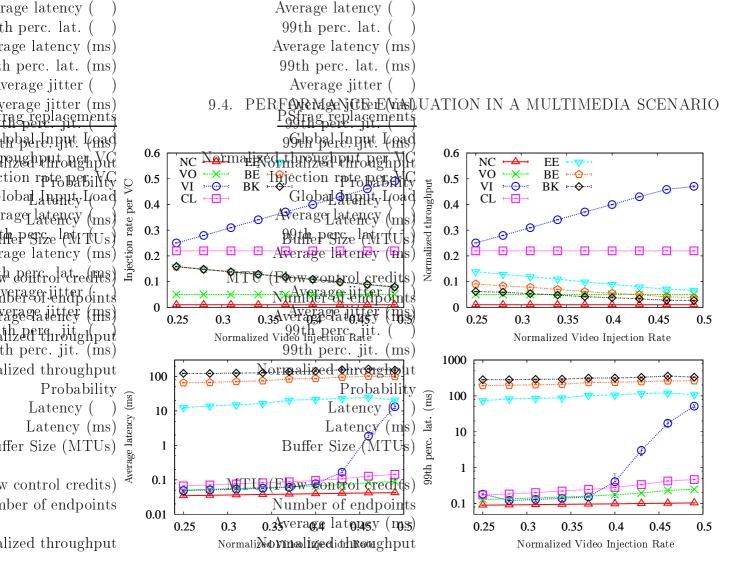

| Performance per SC of the SCFQ scheduler when varying the VI SC injection |                                            |

| rate and employing the <i>Paris</i> sequence                              | 169                                        |

| Latency performance comparison for the video SC when varying the VI SC    |                                            |

| injection rate.                                                           | 170                                        |

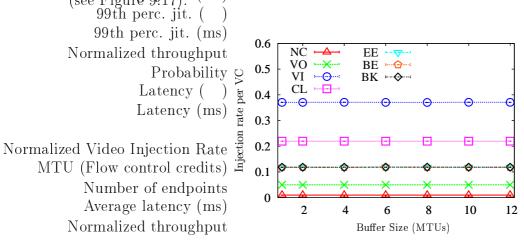

| Injection rate per SC when varying the buffer size                        | 171                                        |

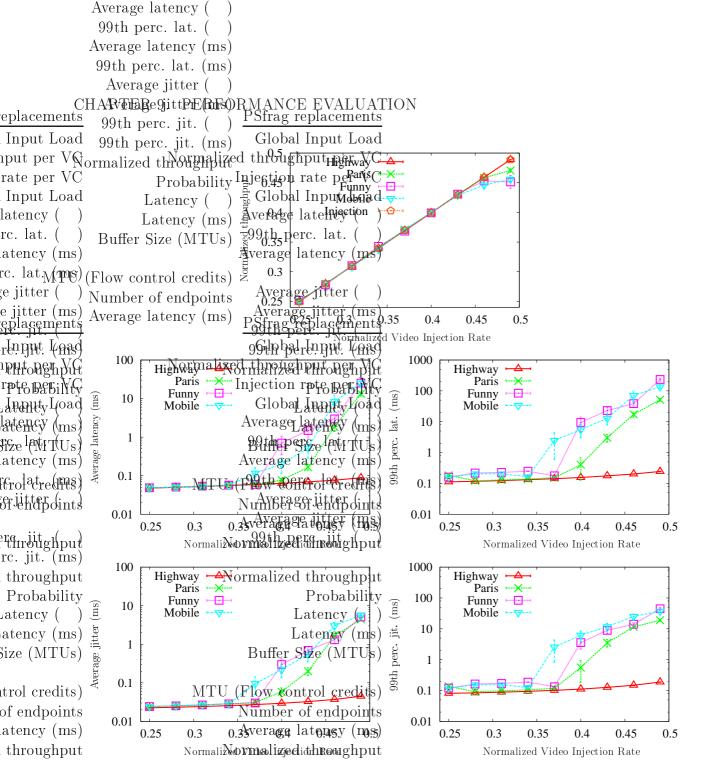

| Performance per SC of the DRR, SCFQ, and DTable schedulers when vary-     |                                            |

| ing the buffer size.                                                      | 172                                        |

| Latency performance comparison for the video SC when varying the buffer   |                                            |

| size                                                                      | 173                                        |

| Latency performance comparison for the controlled load SC when varying    |                                            |

| the buffer size                                                           | 173                                        |

|                                                                           | .175                                       |

|                                                                           |                                            |

|                                                                           | 176                                        |

|                                                                           | 177                                        |

|                                                                           |                                            |

| 8 VCs                                                                     | 179                                        |

|                                                                           | Example of dynamic bandwidth distribution. |

# List of Tables

| Traffic types suggested by the standard IEEE 802.1D-2004                                                                                          | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Protocol interface identifiers                                                                                                                    | 61<br>62<br>64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Arbitration table parameters.                                                                                                                     | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Table configuration example with all the VCs having the same MTU                                                                                  | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Table configuration example with VCs having different MTUs                                                                                        | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Value of the $m$ parameter with different combinations of $GMTU'$ and $GMTU$                                                                      | .100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Value of other configuration aspects when using the 3-bit option                                                                                  | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Number of bits assigned to the weight.                                                                                                            | 102                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Summarized properties of the different possibilities to adapt the original AS table scheduler into the DTable scheduler.                          | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Arbitration time in cycles for the DRR-CA and SCFQ-CA schedulers<br>Arbitration time in cycles for sequential and parallel implementations of the | 118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DTable scheduler.                                                                                                                                 | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Combination of values for the table entries and parallelization grade and arbitration time in cycles.                                             | 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DTable4 and DTable8 configuration scenarios                                                                                                       | 152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                   | 152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Bandwidth configuration of the DTable scheduler scenarios                                                                                         | 152                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                   | 156                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                   | 159                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ±                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                   | 160                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                   | 162                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                   | 163                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Video sequences for performance evaluation.                                                                                                       | 168                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                   | 168                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Characteristics of the networks considered                                                                                                        | 177                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |