# SUPERSCALAR RISC-V PROCESSOR WITH SIMD VECTOR EXTENSION

A Thesis Submitted to the College of Graduate and Postdoctoral Studies in Partial Fulfillment of the Requirements for the Degree of Master of Science in the Department of Electrical and Computer Engineering University of Saskatchewan Saskatoon, Saskatchewan, Canada

By

Jiongrui He

© Jiongrui He, August 2020. All rights reserved.

## Permission to Use

In presenting this thesis in partial fulfilment of the requirements for a Postgraduate degree from the University of Saskatchewan, I agree that the Libraries of this University may make it freely available for inspection. I further agree that permission for copying of this thesis in any manner, in whole or in part, for scholarly purposes may be granted by the professor or professors who supervised my thesis work or, in their absence, by the Head of the Department or the Dean of the College in which my thesis work was done. It is understood that any copying or publication or use of this thesis or parts thereof for financial gain shall not be allowed without my written permission. It is also understood that due recognition shall be given to me and to the University of Saskatchewan in any scholarly use which may be made of any material in my thesis.

Requests for permission to copy or to make other use of material in this thesis in whole or part should be addressed to:

Head of the Department of Electrical and Computer Engineering 3B48 Engineering Building University of Saskatchewan 57 Campus Drive Saskatoon, Saskatchewan S7N 5A9 Canada

#### Or

Dean of College of Graduate and Postdoctoral Studies 116 Thorvaldson Building University of Saskatchewan 110 Science Place Saskatoon, Saskatchewan S7N 5C9 Canada

## Abstract

With the increasing number of digital products in the market, the need for robust and highly configurable processors rises. The demand is convened by the stable and extensible open-sourced RISC-V instruction set architecture. RISC-V processors are becoming popular in many fields of applications and research.

This thesis presents a dual-issue superscalar RISC-V processor design with dynamic execution. The proposed design employs the global sharing scheme for branch prediction and Tomasulo algorithm for out-of-order execution. The processor is capable of speculative execution with five checkpoints. Data flow in the instruction dispatch and commit stages is optimized to achieve higher instruction throughput.

The superscalar processor is extended with a customized vector instruction set of singleinstruction-multiple-data computations to specifically improve the performance on machine learning tasks. According to the definition of the proposed vector instruction set, the scratchpad memory and element-wise arithmetic units are implemented in the vector co-processor.

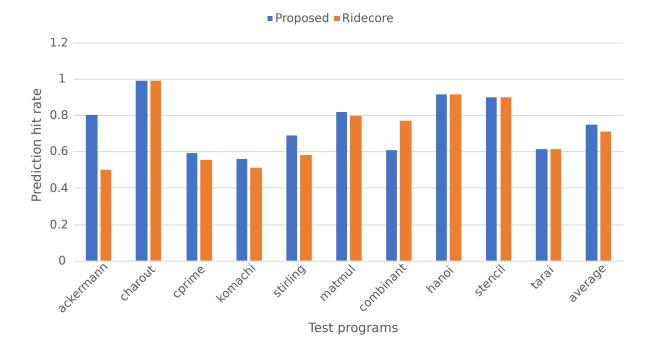

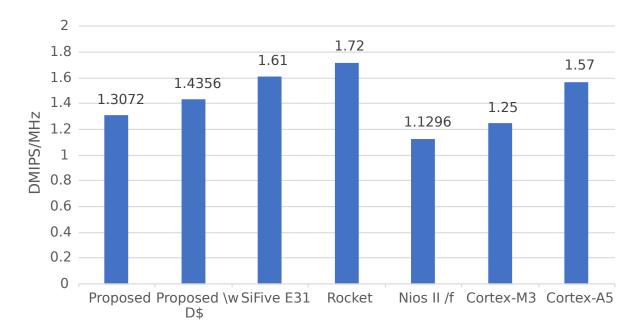

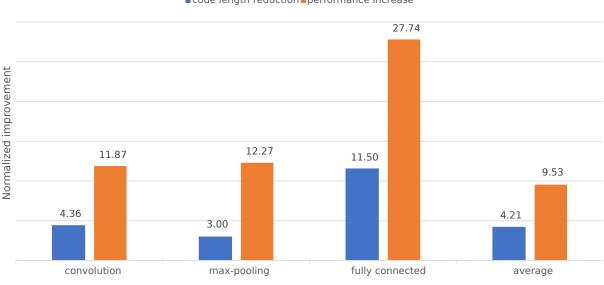

Different test programs are evaluated on the fully-tested superscalar processor. Compared to the reference work, the proposed design improves 18.9% on average instruction throughput and 4.92% on average prediction hit rate, with 16.9% higher operating clock frequency synthesized on the Intel Arria 10 FPGA board.

The forward propagation of a convolution neural network model is evaluated by the standalone superscalar processor and the integration of the vector co-processor. The vector program with software-level optimizations achieves  $9.53 \times$  improvement on instruction throughput and  $10.18 \times$  improvement on real-time throughput. Moreover, the integration also provides  $2.22 \times$  energy efficiency compared with the superscalar processor along.

## Acknowledgements

First of all, I would like to express thanks to my family. Their understanding and emotional care support me to complete my study.

Moreover, I would like to show sincere appreciation to my supervisor, Dr. Seokbum Ko, for all of his support and mentorship during my master program. Whenever I face a challenge, I know that Dr. Ko is sitting in the office and willing to provide guidance. At the beginning of my master program, Dr. Ko gave me the freedom to select the research topic. I am lucky to study on this topic that I am really interested in. Dr. Ko's patience and knowledge motivate me to accomplish this work.

Especially, I would like to appreciate Dr. Dongdong Chen. We have a great period of the corporation since the beginning of my master program. His experience in both research and industry really helped me understand the computer architecture and the IC design flow.

Thanks to my committee members Dr. Anh Dinh, Dr. Dwight Makaroff, and Dr. Francis Bui for their efforts to review and improve my thesis.

I also would like to thank all colleagues in Dr. Ko's lab. Their impressive research topics and progress have broadened my perspective. In particular, I am grateful to Hao Zhang and Yi Wang for their comments and helping me solve the technical issues of the development software and tools.

Thank you for all your encouragement.

## Contents

| Permis  | sion to Use                                                             |

|---------|-------------------------------------------------------------------------|

| Abstra  | ${f ct}$                                                                |

| Acknow  | wledgements                                                             |

| Conter  | ${ m its}$                                                              |

| List of | Tables                                                                  |

| List of | Figures                                                                 |

| List of | Abbreviations                                                           |

| Chapte  | $er 1  Introduction  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  1$ |

| 1.1     | Introduction                                                            |

| 1.2     | Objective                                                               |

| 1.3     | Organization                                                            |

| Chapte  | er 2 Background                                                         |

| 2.1     | RISC-V ISA                                                              |

| 2.2     | Parallelism in Hardware                                                 |

|         | 2.2.1 Instruction-Level Parallelism                                     |

|         | 2.2.2 Data-Level Parallelism                                            |

| 2.3     | SIMD Extension                                                          |

|         | 2.3.1 Standard V-Extension                                              |

|         | 2.3.2 Cambricon ISA                                                     |

| 2.4     | Summary                                                                 |

| Chapte  | er 3 Superscalar Processor                                              |

| 3.1    | Overview                                                                                                  | 22 |

|--------|-----------------------------------------------------------------------------------------------------------|----|

| 3.2    | Instruction Fetch                                                                                         | 23 |

|        | 3.2.1 Gshare Branch Prediction                                                                            | 24 |

| 3.3    | Instruction Decode                                                                                        | 25 |

|        | 3.3.1 Speculation Tags                                                                                    | 27 |

| 3.4    | Data Dispatch                                                                                             | 28 |

|        | 3.4.1 Renaming File Backups                                                                               | 29 |

| 3.5    | Reservation Stations                                                                                      | 31 |

| 3.6    | Execution Units                                                                                           | 34 |

| 3.7    | Instruction Completion                                                                                    | 34 |

| 3.8    | Summary                                                                                                   | 35 |

|        |                                                                                                           |    |

| Chapte | er 4 Vector Co-processor                                                                                  | 37 |

| 4.1    | Instruction Set                                                                                           | 37 |

| 4.2    | Integration                                                                                               | 40 |

| 4.3    | Wrapped Memory                                                                                            | 42 |

| 4.4    | Vector Instruction Board                                                                                  | 43 |

| 4.5    | Processing Units                                                                                          | 46 |

| 4.6    | Summary                                                                                                   | 49 |

|        |                                                                                                           |    |

| Chapte | er 5 Software Work-flow                                                                                   | 50 |

| 5.1    | Test Environment                                                                                          | 50 |

|        | 5.1.1 ISA tests $\ldots$ | 52 |

|        | 5.1.2 Toolchain-flow                                                                                      | 53 |

|        | 5.1.3 C programs                                                                                          | 55 |

| 5.2    | Vector Software                                                                                           | 58 |

|        | 5.2.1 Layer kernels                                                                                       | 60 |

|        | 5.2.2 Optimizations                                                                                       | 61 |

| 5.3    | Summary                                                                                                   | 64 |

| ~      |                                                                                                           |    |

| Chapte | er 6 Results and Analysis                                                                                 | 65 |

| 6.1    | Superscal | lar Proces | ssor. |     | • • | <br> | • | <br>• | <br>• | •   | • |  | • |  |   |   | • | <br>• | 65 |

|--------|-----------|------------|-------|-----|-----|------|---|-------|-------|-----|---|--|---|--|---|---|---|-------|----|

|        | 6.1.1 Pe  | erformand  | e     |     |     | <br> | • | <br>• | <br>• | •   | • |  | • |  |   |   | • |       | 66 |

|        | 6.1.2 Sy  | ynthesis   |       |     | ••• | <br> | • | <br>• | <br>• | • • |   |  | • |  |   | • | • |       | 71 |

| 6.2    | Vector C  | o-process  | or    |     | ••• | <br> | • | <br>• | <br>• | •   |   |  | • |  |   |   | • |       | 73 |

|        | 6.2.1 Pe  | erformand  | e     | • • |     | <br> | • | <br>• | <br>• | •   |   |  |   |  |   |   | • |       | 73 |

|        | 6.2.2 Sy  | ynthesis   |       |     | ••• | <br> | • | <br>• | <br>• | •   |   |  | • |  |   |   | • |       | 77 |

| Chapte | er 7 Cor  | nclusion   |       |     |     | <br> |   | <br>• | <br>• |     |   |  |   |  | • | • | • | <br>• | 80 |

| 7.1    | Conclusio | on         |       | • • |     | <br> |   | <br>• | <br>• | •   | • |  |   |  | • |   | • |       | 80 |

| 7.2    | Future W  | Vork       |       |     |     | <br> | • | <br>• | <br>• | •   | • |  | • |  |   |   | • |       | 81 |

| Refere | nces      |            |       |     |     | <br> |   |       |       |     |   |  |   |  |   |   |   |       | 83 |

## List of Tables

| 1.1 | Comparison between general CISC and RISC                   | 2  |

|-----|------------------------------------------------------------|----|

| 2.1 | RISC-V base opcode map, for opcode[1:0]=11                 | 9  |

| 2.2 | Definition of new vector control and status registers      | 17 |

| 2.3 | Overview of Cambricon ISA (From: Table 1 Chen et al. [1])  | 19 |

| 3.1 | Key parameters of the processor                            | 22 |

| 4.1 | ISA summary                                                | 40 |

| 5.1 | CNN structure                                              | 59 |

| 6.1 | Log files of software execution on different test programs | 66 |

| 6.2 | FPGA synthesis reports                                     | 71 |

| 6.3 | Machine cycles to finish each layer                        | 74 |

| 6.4 | Throughput of MAC operations                               | 76 |

| 6.5 | FPGA synthesis reports with vector co-processor            | 77 |

| 6.6 | Performance and energy efficiency over the LeNet-5 model   | 79 |

## List of Figures

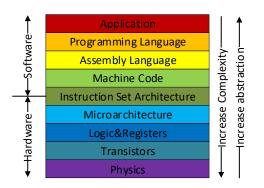

| 1.1  | Layers of Abstraction.                                                           | 2  |

|------|----------------------------------------------------------------------------------|----|

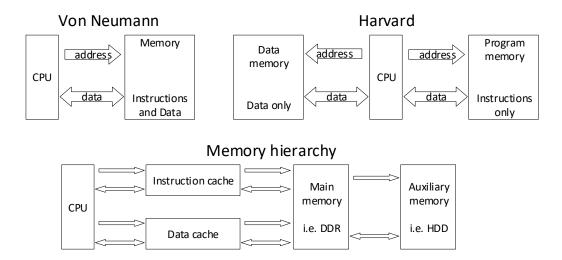

| 1.2  | Von Neumann Architecture, Harvard Architecture and Memory Hierarchy. $\ . \ .$   | 3  |

| 2.1  | 32-bit RISC-V instruction formats. The sub-field of each immediate indicates the |    |

|      | bit position of the produced immediate value.                                    | 9  |

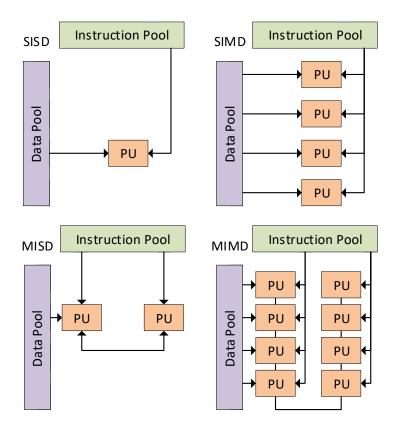

| 2.2  | Flynn Taxonomy in computer architecture                                          | 11 |

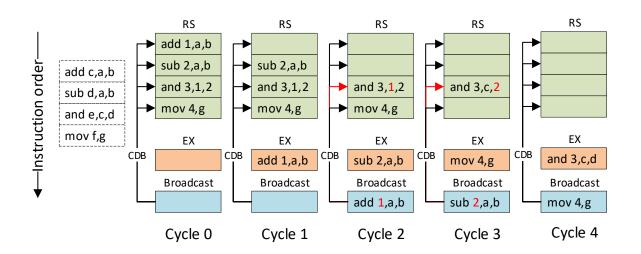

| 2.3  | Example of dynamic scheduling following Tomasulo algorithm                       | 13 |

| 2.4  | Vector operation of packed four vs scalar operation                              | 15 |

| 2.5  | Process of 2D convolution in a convolution layer.                                | 16 |

| 2.6  | Matrix Multiply Vector instruction and its data arrangement                      | 20 |

| 2.7  | Vector Greater Than Merge instruction with the max pooling flow                  | 21 |

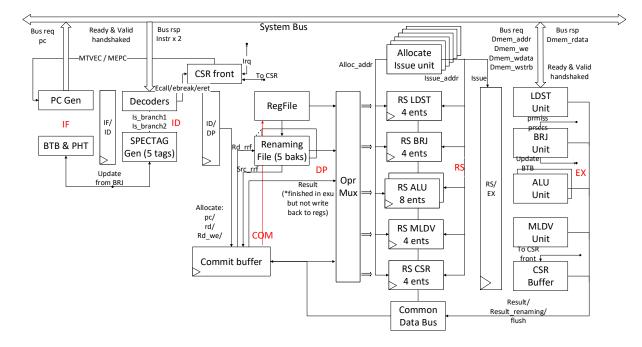

| 3.1  | Top level diagram of the processor.                                              | 23 |

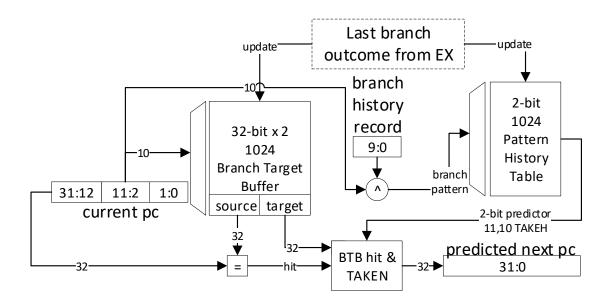

| 3.2  | Branch prediction module.                                                        | 25 |

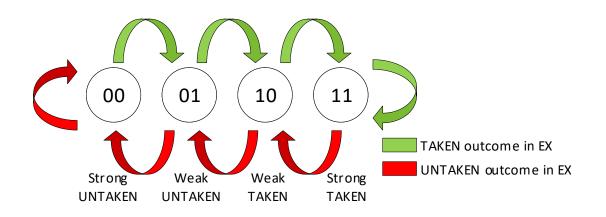

| 3.3  | 2-bit adaptive predictor encoding scheme.                                        | 26 |

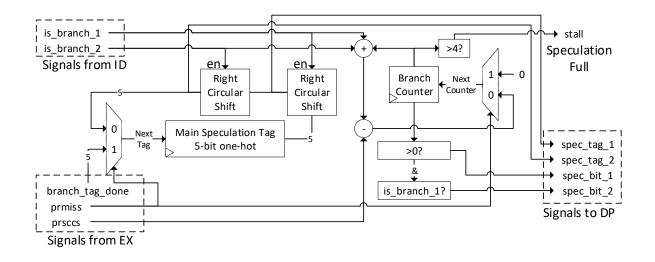

| 3.4  | Speculation tag generator module.                                                | 27 |

| 3.5  | Data structure of register file, renaming files and commit buffer                | 28 |

| 3.6  | Control of renaming file backups according to speculation status.                | 30 |

| 3.7  | Renaming file handling in prediction miss cycle and prediction hit cycle         | 31 |

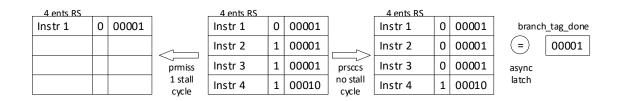

| 3.8  | Allocation and issue process of a reservation station with 4 entries             | 32 |

| 3.9  | Behavior of reservation stations according to the prediction outcome             | 33 |

| 3.10 | Structure and flow of the commit buffer                                          | 35 |

| 4.1  | Encoding of vector transfer instructions.                                        | 38 |

| 4.2  | Encoding of vector arithmetic instructions                                       | 39 |

| 4.3  | Encoding of vector multiply matrix instruction.                                  | 39 |

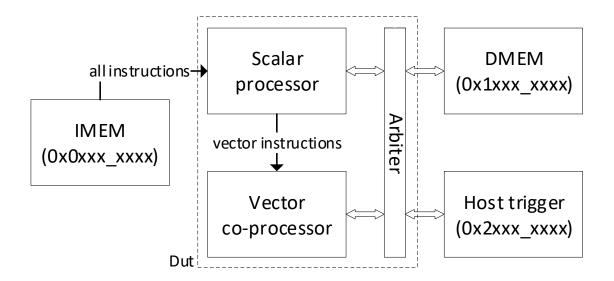

| 4.4  | Overview of the hardware implementation                                          | 41 |

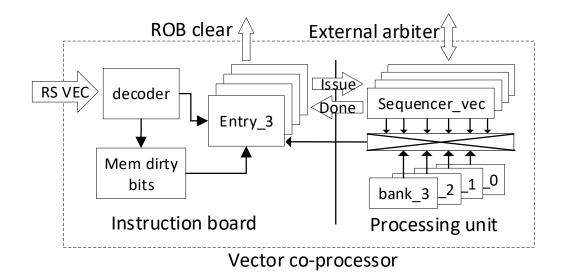

| 4.5  | Top-level diagram of the vector co-processor                                     | 43 |

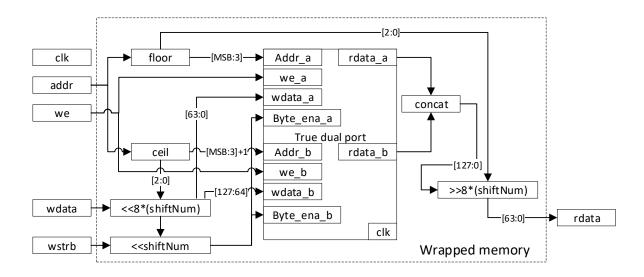

| 4.6 | Structure of each memory bank                                | 44 |

|-----|--------------------------------------------------------------|----|

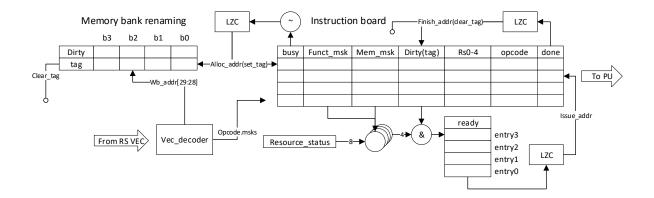

| 4.7 | Structure of vector instruction board                        | 45 |

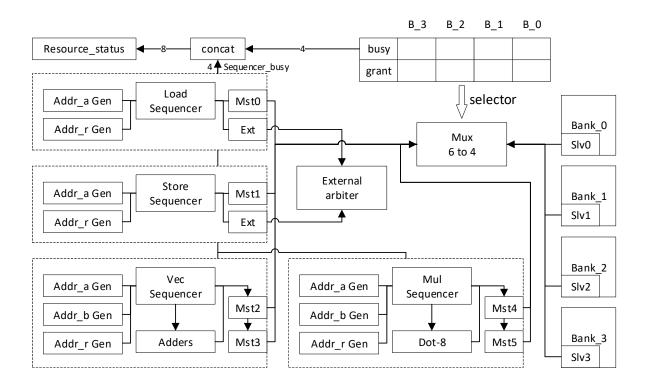

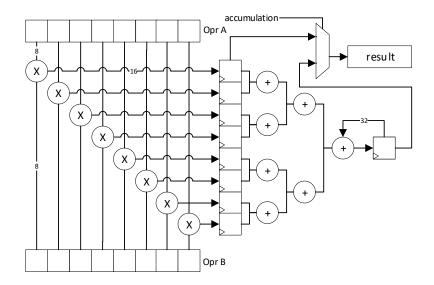

| 4.8 | Structure of processing units.                               | 47 |

| 4.9 | Structure of dot-product unit.                               | 48 |

| 5.1 | Hardware arrangement in test-bench                           | 50 |

| 5.2 | Console outputs of ISA tests.                                | 53 |

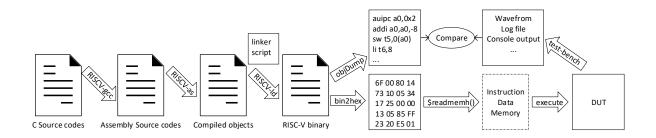

| 5.3 | Work-flow from software code to hardware output.             | 54 |

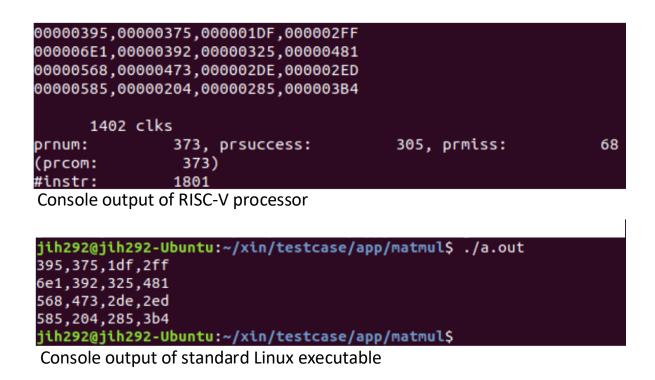

| 5.4 | RISC-V program result vs standard program result             | 58 |

| 5.5 | Data flow of convolution computation.                        | 59 |

| 5.6 | Generalized assembly kernels for convolution and max-pooling | 60 |

| 5.7 | Data flow of double buffering.                               | 62 |

| 5.8 | Comparison between dot-product and element-multiplication    | 63 |

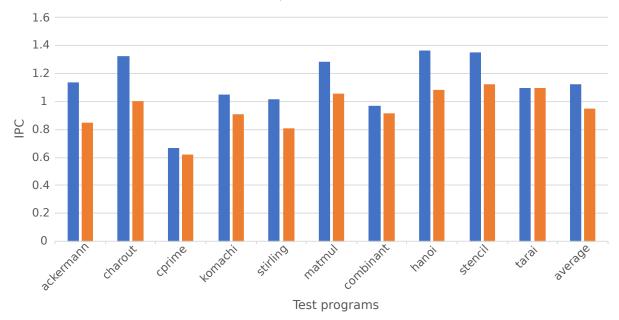

| 6.1 | Comparison of instructions per cycle                         | 67 |

| 6.2 | Comparison of prediction hit rates.                          | 68 |

| 6.3 | Dhrystone benchmarks of several commercial processors        | 70 |

| 6.4 | Normalized improvements in CONV, Max-pooling and FC layers   | 75 |

## List of Abbreviations

| AI                   | Artificial Intelligence          |

|----------------------|----------------------------------|

| ALM                  | Adaptive Logic Module            |

| ALU                  | Arithmetic Logic Unit            |

| BTB                  | Branch Target Buffer             |

| CDB                  | Common Data Bus                  |

| CISC                 | Complex Instruction Set Computer |

| CNN                  | Convolution Neural Network       |

| COM                  | Commit                           |

| CPU                  | Central Processing Unit          |

| $\operatorname{CSR}$ | Control and Status Register      |

| DLP                  | Data-Level-Parallelism           |

| DP                   | Data Dispatch                    |

| DUT                  | Device Under Test                |

| EX                   | Execution                        |

| $\mathbf{FC}$        | Fully-Connected                  |

| FPGA                 | Field-Programmable Gate Array    |

| FPU                  | Floating-Point Unit              |

| GPU                  | Graphic Processing Unit          |

| ID                   | Instruction Decode               |

| IF                   | Instruction Fetch                |

| ILP                  | Instruction-Level-Parallelism    |

| IPC                  | Instruction Per Cycle            |

| ISA                  | Instruction Set Architecture     |

| MMV                  | Matrix Multiply Vector           |

| MSB                  | Most Significant Bit             |

| PC                   | Program Counter                  |

| PHT                  | Pattern History Table            |

|                      |                                  |

| PU   | Processing Unit                  |

|------|----------------------------------|

| RISC | Reduced Instruction Set Computer |

| RS   | Reservation Station              |

| SIMD | Single-Instruction Multiple-Data |

| SPM  | ScratchPad Memory                |

| VGTM | Vector Greater Than Merge        |

| VLIW | Very-Long-Instruction-Word       |

# Chapter 1 Introduction

### **1.1** Introduction

Past decades have witnessed the rapid advancement of computer hardware related to ARM and x86 processors, which have become the foundation of global semiconductor markets. Processors are pervasive from cores of supercomputers to controllers of embedded chips. The processor is a digital circuit that handles a simple step of operation on a certain instruction, which takes its origin from the Turing Machine. The combination of numerous simple instructions can reproduce different types of algorithms. There are two major categories of processors, general-purpose processors and single-purpose processors. The general-purpose processor, also known as a microprocessor, can support many different applications by only programming the software, such as the central processing units (CPU) in personal computers and mobile phones. The single-purpose processor usually has better performance in speed, power, and area, however, its utilization is limited to a certain type of application, such as the graphic processing unit (GPU) and artificial intelligence (AI) accelerators.

The functionality of microprocessors is defined by the instruction set architecture (ISA). The instruction set describes the instruction that the microprocessor can execute. According to the layers of abstraction in computers, which is presented in Figure 1.1, an ISA is a bridge between software and hardware and it is the specification of microprocessor design.

There are also two categories of ISA, the complex instruction set computer (CISC) and the reduced instruction set computer (RISC). Table 1.1 shows the major differences between CISC architecture and RISC architecture. X86 is a typical CISC ISA, which instructions are complex and capable of operating directly upon memory address. However, RISC instructions are treated as an improvement over CISC by simplifying the instruction format and the op-

Figure 1.1: Layers of Abstraction.

eration of each instruction. RISC microprocessors often execute one instruction per machine cycle so that it is easier to pipeline the design to achieve higher clock frequency. However, the simple operations in RISC instructions bring the complexity in software compilers. The difference between CISC and RISC is explained by the basic performance equation:

$$\frac{seconds}{program} = \frac{instructions}{program} \times \frac{cycles}{instruction} \times \frac{seconds}{cycle}$$

(1.1)

| ISA                        | CISC              | RISC           |

|----------------------------|-------------------|----------------|

| Number of instructions     | Extended          | Reduced        |

| Duration of an instruction | Multiple cycles   | One cycle      |

| Instruction length         | Variable          | Fixed          |

| Memory access              | Many instructions | Load and Store |

| Registers                  | Unique            | Multiple       |

| Complexity                 | In compiler       | In hardware    |

Table 1.1: Comparison between general CISC and RISC

CISC architecture emphasizes the efficiency in instructions per program while RISC architecture emphasizes the efficiency in cycles per instruction. There is a trade-off in terms of performance. However, the booming market of smartphones and embedded projects brings people's concern about power consumption. Because complex CISC instructions require more logic and transistors to delay with more power consumption, RISC ISA is dominating the market of mobile devices nowadays.

A typical microprocessor consists of arithmetic logic units (ALU), control unit, and data storage unit. The microprocessor takes instruction from the external memory. Then the control unit, based on that instruction, reconnects datapath to feed the operands to ALU and selects the corresponding function in ALU to finish one operation. If the instruction and data are stored at two different places, it is considered as the Harvard Architecture. On the other hand, the instruction and data share single storage in the Von Neumann Architecture. Under Harvard Architecture, microprocessors can access instructions and data, from the program memory and the data memory simultaneously, to release the Von Neumann bottleneck. Those two basic architectures are presented in Figure 1.2. However, most of the modern microprocessors fetch instruction and data, from the instruction cache and data cache respectively, which is recognized as the Harvard Architecture from the core perspective. The two caches are connected to the main memory in the memory hierarchy. Instructions and data eventually are stored in hard disks, which is recognized as the Von Neumann Architecture from the system perspective. Therefore, the boundary between the two architectures is blurred [2].

Figure 1.2: Von Neumann Architecture, Harvard Architecture and Memory Hierarchy.

#### 1.2 Objective

Many applications require a controller to monitor the peripherals and handle the analogto-digital conversion [3–5]. Using a general-purpose processor can significantly shorten the period of research, compared with developing a task-specific controller. Thanks to the upgrading field-programmable gate arrays (FPGA), soft cores can be programmed in an FPGA project without exceeding the onboard resource limitation. An open-source and customizable microprocessor brings flexibility to developers, which can rapidly change the design, such as, adding new task-specific instructions, extending with a co-processor, and investigating a new bus protocol. Therefore, an open-source microprocessor can accelerate the hardware design flow by providing different configurations to developers. However, both ARM and x86 ISA are proprietary leading to high research costs for hardware designers. Thankfully, RISC-V, an open-source ISA, is becoming popular in industry because of the maturity of its software ecosystem and toolchains.

Many RISC-V core designs have relatively short pipeline stages focusing on energy and area efficiency in the literature. PicoRV32 [6] is a decent compact core with a general sequencer to process every instruction so that its average instruction per cycle is only approximately 0.25. Hummingbird E203 [7] also focuses on low power and small area. It has two-stage in-order pipelines to improve the performance. Similarly, Zero-riscy [8] with a two-stage pipeline, orients to the energy efficiency for Internet-of-Thing applications and Micro-riscy [8], based on Zero-riscy, aggressively halves the register file to further reduce the area.

On the other hand, performance-oriented cores also bring interests to researchers and designers. Riscy [9] is integrated with customized instructions to support Zero Overhead Loops and packed single instruction multiple data (SIMD) computation. Ariane [10] and Rocket core [11], with the similar six-stage pipeline and single-issue architecture, are capable of outof-order execution by the Scoreboarding method. Ridecore [12] is a dual-issue superscalar core and follows the Tomasulo Algorithm to handle dynamic execution.

The motivation for this research is to understand the modern architectures inside of CPU cores to improve the performance, and the compilation flow to connect the software and the

hardware. The goals of this thesis are summarized below:

- A general-purpose processor design is proposed following the RISC-V ISA specification. The proposed design supports the basic 32-bit RISC-V instruction set with the integer multiplication/division extension.

- Modern processors' features including branch prediction, superscalar architecture, and out-of-order execution are implemented in the proposed design to improve the performance.

- The proposed design must pass the RISC-V ISA regression test to verify its functionality. Several testcases and benchmarks are evaluated to compare the performance.

- A customized vector instruction set is proposed to efficiently support the SIMD computation. The extended instruction set is mapped to the standard 32-bit RISC-V format.

- A vector co-processor, with scratchpad memory, address sequencers, and the dotproduct unit, is proposed to support the vector instructions and SIMD computation.

- The vector co-processor is coupled with the previous general-purpose processor. An inference of a convolution neural network (CNN) is evaluated to reveal the performance increase of SIMD computation.

- The proposed designs are implemented on the Intel Arria 10 FPGA board.

### 1.3 Organization

This thesis is organized as follows. Chapter 2 discusses the standard RISC-V ISA and extended SIMD instructions based on Cambricon [1]. Modern processors' flow and parallelism in hardware are also included in this Chapter. Chapter 3 describes the hardware implementation of the main microprocessor, while, Chapter 4 describes the hardware implementation of the SIMD vector co-processor. Chapter 5 documents the compiling flow of the RISC-V GNU toolchain for the RISC-V microprocessor and optimizations of assembly codes for the vector co-processor. Chapter 6 compares performance results and synthesis reports to summarize what has been achieved during this research. Chapter 7 reflects the summary of the proposed design with several potential future improvements and advancements in the proposed work.

# Chapter 2 Background

## 2.1 RISC-V ISA

RISC-V is an open-source ISA and it has brought a huge amount of momentum since the first release in 2010 by the University of California Berkeley [13]. RISC-V ISA has its origin in a computer architecture project in education. Now, RISC-V ISA brings more and more attention to not only academia but also industry, because of the maturity of the software ecosystem and toolchains. RISC-V International is managing the RISC-V specification and the community released the ratified version of the privileged specification in June 2019 [14]. The latest specification defines the solid machine-level and supervisor-level ISA, which guarantees that hardware is compatible with all RISC-V software and operating systems. Moreover, unlike the proprietary ISA, like ARM and x86, the RISC-V ISA offers the possibility to modify and customize the architecture, without requesting the permission or subscribing the license in other expensive commercials ISAs.

The latest specification of RISC-V ISA can be found on the website of RISC-V International.<sup>1</sup> According to the preface part in the specification, a typical standard RISC-V processor is started by defining the number of general-purpose registers and the data length of both addresses and data. The base integer ("I") ISA varies among 32-bit, 64-bit, and 128bit. The 32-bit processor represents that its addresses and data have the data size of 32-bit. The base ISA is followed by some optional standard extensions, which further enhances the generality and flexibility in RISC-V ISA. Some of the most common and useful extensions are listed below:

<sup>&</sup>lt;sup>1</sup>https://riscv.org/

- "Zifencei", instruction-fetch fence,

- "Zicsr", control and status register instructions,

- "M", standard extension for integer multiplication/division instructions,

- "A", standard extension for atomic instructions,

- "F", standard extension for single-precision floating-point instructions,

- "D", standard extension for double-precision floating-point instructions,

- $\bullet\,$  "Q", standard extension for quad-precision floating-point instructions, and

- "C", standard extension for compressed instructions.

The RISC-V instruction set is organized by a combination of the base integer ISA and optional extensions. For example, the ISA, "RV32IM", indicates that this instruction set supports the 32-bit base integer instructions and integer multiplication/division instructions. The "Zifencei" defines the FENCE.I instruction that synchronizes the instruction and data streams. A FENCE.I instruction guarantees that the following instruction fetches on a RISC-V core will see the latest content in the memory, by stalling the processor until the previous STORE instruction is finished. The "Zicsr" defines an additional address space of 4096 control and status registers with associative instructions that modify and control those registers (CSR). The usage of CSRs is described in the privileged specification. Examples include interrupt handlers, exceptions, and memory virtualization.

The coding formats of the 32-bit RISC-V instructions are presented in Figure 2.1. These precise formats place the register fields in the same position to simplify the hardware decoding logic. Besides, the top-bit in the immediate fields is always placed in the most significant bit (MSB) of instructions, which reduces the sign extension case during the expansion of the immediate value. The operations of RISC-V instructions are primarily grouped by the opcodes. Table 2.1 shows the opcode map of the instruction set. The "opcode[1:0]=11" marks the 32-bit instruction, while, other bits combination is reserved for the "C" extension of the compressed 16-bit instructions. The gray column is reserved for instructions which lengths are greater than 32-bit. The four free opcodes, noted as  $custom_{-}[0,1,2,3]$ , give fully

empty encoding space for customized instructions, which provides the basis for specialized instruction set extension and customized accelerators.

| 31 30 25<br>funct7 | 24 20 1<br>rs2 | 9 15<br>rs1 | <u>14 12</u><br>funct3 | 11 8 7<br>rd     | 6 0<br>opcode | R-type |

|--------------------|----------------|-------------|------------------------|------------------|---------------|--------|

| imm[11:0]          |                | rs1         | funct3                 | rd               | opcode        | I-type |

| imm[11:5]          | rs2            | rs1         | funct3                 | imm[4:0]         | opcode        | S-type |

| imm[12] imm[10:5]  | rs2            | rs1         | funct3                 | imm[4:1] imm[11] | opcode        | B-type |

| in                 | ım[31:12]      |             |                        | rd               | opcode        | U-type |

| imm[20] imm[10:1]  | imm[11]        | imm[        | 19:12]                 | rd               | opcode        | J-type |

Figure 2.1: 32-bit RISC-V instruction formats. The sub-field of each immediate indicates the bit position of the produced immediate value.

| opcode[4:2] | 000    | 001      | 010           | 011      | 100    | 101      | 110              | 111        |

|-------------|--------|----------|---------------|----------|--------|----------|------------------|------------|

| opcode[6:5] | 000    | 001      | 010           | 011      | 100    | 101      | 110              | >32b       |

| 00          | LOAD   | LOAD_FP  | $custom_{-}0$ | MISC_MEM | OP_IMM | AUIPC    | OP_IMM_32        | 48b        |

| 01          | STORE  | STORE_FP | $custom_{-}1$ | AMO      | OP     | LUI      | OP_32            | 64b        |

| 10          | MADD   | MSUB     | NMSUB         | NMADD    | OP_FP  | reserved | $custom_2/rv128$ | 48b        |

| 11          | BRANCH | JALR     | reserved      | JAL      | SYSTEM | reserved | custom_3/rv128   | $\geq 80b$ |

Table 2.1: RISC-V base opcode map, for opcode[1:0]=11

### 2.2 Parallelism in Hardware

Pipelining the design is a powerful and straightforward technique to speedup the throughput. In the field of microprocessors, pipelining partitions each instruction into multiple stages. Pipelining usually brings data dependency hazard in microprocessor. The instruction may need the result of the previous instruction, which is ready in the ALU but not in the registers. In another word, the previous instruction is not fully completed, but the current instruction requires the latest output because of the deep pipeline stages. The data hazard can be solved by a control unit to forward the latest output to the required stage directly. Such control unit does not affect the throughput by providing the correct results, however, introduces the hardware complexity. The instruction throughput of microprocessors is defined as:

$$\frac{instructions}{second} = \frac{cycles}{second} \times \frac{instructions}{cycle},$$

(2.1)

where the first term indicates the operating frequency, or clock frequency, and the second term indicates how many instructions can handle in each stage.

However, in reality, the improvement of increasing the pipeline stages decreases as the stages go deeper and deeper. One of the biggest problems is that it is hard to exactly equally split the task. For example, a full datapath of one instruction takes 50ns, including 10ns in decoding, 20ns in operands fetch, and 20ns in computation, which can operate under the clock frequency no more than 20Mhz. To double the clock frequency, the perfect pipeline scheme is to split the datapath by two, 25ns latency in each stage. However, the datapath can only divided by two in the form of *decoding+operands fetch* (30ns) and *computation* (20ns). Just like the shortest stave in a barrel, the clock frequency is limited by the first 30ns latency so that the frequency cannot reach higher than 33.33Mhz. On the other hand, the branch miss penalty increases as the pipeline stage go deeper.

Branch instructions are very common in programs. The program counter (PC), or the address of instructions, increases sequentially by the default. The branch instruction may cause the PC to jump to another address for a new sequence of instructions. The condition, whether to jump or not, usually is ready after the computation stage. At the same time, the instructions related to the wrong PC path are already processing in previous pipeline stages.

To avoid that situation, the most simple solution is to suspend the processor until the branch instruction is finished, which decreases the second term in the equation of throughput, instructions per cycle (IPC). There are many branch prediction techniques that can detect and predict the branch condition at the early stage, which does not cause stall cycles on the successful prediction. However, as long as the rate of successful prediction is not 100%, the branch miss penalty exists and increases as the pipeline stages increase, which makes traditional pipelined microprocessors to have less than one IPC. No matter of the depth of the pipelined processor, it belongs to the single-instruction-single-data architecture in Flynn Taxonomy [15], which is presented in Figure 2.2.

Parallel computing can further improve the throughput besides pipelining. The paral-

Figure 2.2: Flynn Taxonomy in computer architecture.

lelism in hardware consists of multi-instructions, multi-data, multi-cores, and multi-computers. The design is focused on instruction-level parallelism (ILP) and data-level parallelism (DLP) within the scope of a single core problem.

#### 2.2.1 Instruction-Level Parallelism

Superscalar and very-long-instruction-word (VLIW) are two models in computer architecture to execute multiple instructions in one clock cycle within a single processor. Unlike the SISD processors, a superscalar processor can dispatch multiple instructions to their targeting processing units (PU).

The superscalar processor requires the data dependency check not only on the different stages, like pipelined processors, but also on the same clock cycle. The multiple instructions fetched and decoded at the same clock cycle may not be dispatched or finished at the same time. The dependency check logic brings complexity in hardware, but the superscalar approach raises the roofline IPC to the number of multiple instructions from one compared to the conventional pipelined processor. In other words, regardless of how deeper the pipeline stages go, the highest IPC of the pipelined processor is limited to one. Whereas, with the multiple instructions processing in the same clock cycle, the superscalar processor increase its highest IPC to the number of the paralleled instructions.

VLIW processors also can execute multiple instructions in one clock cycle and there is no dependency check logic. VLIW approach heavily depends on the compiler side, which resolves all data dependency conflicts in machine codes. This approach is also called static scheduling. The VLIW architecture comes after the superscalar architecture and tries to retain the same throughput while reducing the hardware complexity. So far, the RISC-V toolchain does not support VLIW because the static scheduling has failed in general-purpose computing. Major drawbacks include unpredictable branches, code size explosion, and compiler complexity.

#### Tomasulo Algorithm

In contrast to VLIW processors, superscalar processors dynamically resolve data dependencies in hardware that brings the capability of out-of-order execution. The Tomasulo algorithm [16] was developed by Robert Tomasulo and it has become the basic structure in many modern processors. According to the algorithm, hardware register renaming, reservation stations, and a common data bus (CDB) for broadcasting are introduced to computer microarchitecture.

Hardware register renaming abstracts the physical address of destination registers to the logical address based on the order of the incoming instructions, which is essential to perform the out-of-order execution correctly. Reservation stations (RS) are the unified scheduler regarding on each processing unit. Every processing unit has its own reservation station to temporarily hold instructions. The reservation station dispatches the instruction to the targeting processing unit if all source operands are ready and the processing unit is free. The oldest instruction in the reservation station has the highest priority to be dispatched if multiple instructions are ready at the same time. When the instruction is finished in the processing unit and the result is ready, the common data bus takes the value and renamed

address to broadcast to every reservation station. The renamed addresses are also called as tags to differentiate which instruction in the reservation station needs the latest results.

Figure 2.3 shows the example of out-of-order execution to solve the read-after-write data hazard. Before four instructions allocate to the reservation station, their destination addresses are renamed to "1,2,3,4" from "c,d,e,f", in the sequence of instructions. The third AND instruction has registers "c,d" as the source operands. At the time of the third instruction entering the reservation station, registers "c,d" already set busy by the ADD and SUB instructions, and the values in registers "c,d" are no longer valid. Therefore, the AND instruction copies the renamed addresses "1,2" as the tags and waits for the latest data from the common data bus. The AND instruction depends on the latest results of ADD and SUB instructions, which is a typical read-after-write data hazard.

Figure 2.3: Example of dynamic scheduling following Tomasulo algorithm.

In the period of Cycle 0, the "ADD, SUB, MOV" instructions are ready to be dispatched. Because the ADD instruction is the oldest ones in the reservation, it is dispatched to the processing unit in the next clock cycle. In the period of Cycle 2, the result of the first instruction, that is required by the AND instruction as the latest value in resister c, enters the common data bus. The AND instruction saves the result as the correct operand by matching the tag 1. At the same time, the reservation station dispatches the MOV instruction to the processing unit even though the previous AND instruction is not executed, which dynamically schedules the dispatching scheme and keeps the processing unit working to provide higher utilization.

The example shows the case of one reservation station with one processing unit. In a real implementation, there are multiple reservation stations with processing units that each of them is responsible for one specific type of function. Different processing units and reservation stations are interconnected by the common data bus. Although the bus-type connection cause hardware complexity, processing units are isolated with each other so that they can have different pipeline stages so that processing units with different length of the datapath are easy to concatenate together.

For example, integer arithmetic units (ALU) always have much shorter datapath than floating-point units (FPU). There are two choices in traditional pipelined processors to add a new FPU datapath. One is to directly insert the FPU, but lower the clock frequency. The other one is to remake the integer ALU to align with the pipelined FPU. However, in out-of-order processors, FPU with multiple stages operate correctly with integer ALU with one stage without impact on the clock frequency. In summary, by considering reservation stations as the instruction pool, processing units in superscalar processors agree with the multiple-instruction-single-data architecture.

#### 2.2.2 Data-Level Parallelism

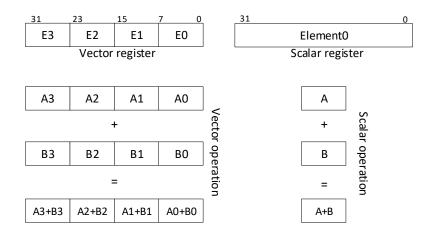

In contrast to ILP, DLP refers to single-instruction-multiple-data (SIMD) architecture. The most common approach of SIMD is to use the packed data in registers. In vector processors, the values in each vector register are divided into multiple elements and the vector operation computes individually on each element instead of the full-width data, demonstrated in Figure 2.4. In the example, one vector instruction finish four operations compared to the common scalar instruction. The number of packed elements varies according to the application.

DLP brings tremendous speedup of applications that require massive and continuous data, including video decoding, image processing, and solving linear algebra. One graphic processing unit (GPU) in modern graphic cards is a common implementation of DLP. The graphic driver software vectorizes image processing tasks into several SIMD vector instructions that

Figure 2.4: Vector operation of packed four vs scalar operation.

are executed by GPUs to deliver the output. The vector instructions in modern commercial GPUs are also proprietary.

Similar to the VLIW, challenges of DLP also involve the difficulty in general-purpose computing and compilers. However, many commercial ISAs have the vector extension instruction set to remain general-purpose computing with the basic instruction set while boosting the performance of specific tasks with the vector extension. Examples include SSE in Intel x86 and NEON extension in ARM. To fully exploit the SIMD instructions, the throughput heavily relies on software optimization and task-specific fine-tuning. Some general techniques are data alignment, loop unrolling, and prefetching. With respect to the hardware, the functionality and architecture simply follow the vector instruction set specification.

#### 2.3 SIMD Extension

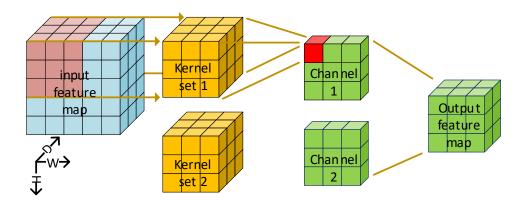

Artificial Intelligence (AI) is a trending topic today. Some important applications include image classification, object segmentation, and natural language processing, based on the structure of convolution neural networks (CNN). A typical CNN structure usually consists of convolution layers, pooling layers, activation layers, and fully-connected (FC) layers. The majority of the computations occur in the convolution layer, which uses a three-dimensional input feature map, one set of 3D parameters, to generate one channel of two-dimensional results, aligned with the same depth of the input feature map. All channels of results are concatenated together to produce the final result in the convolution layer. The 2D convolution is a process of sliding a 3D filter matrix through the input layer. The 3D filter only shifts in two directions, width (W) and height (H) of the input feature map.

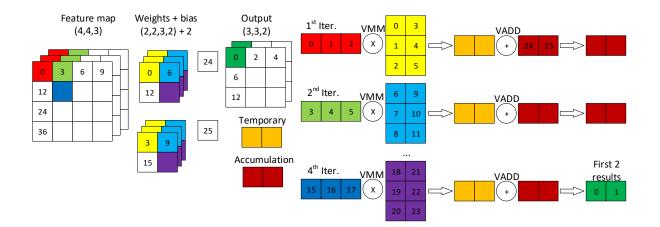

Conventionally, the size of 3D feature maps is noted as (width,height,depth) while the size of convolution kernels is noted as (width,height,input depth,output depth). Figure 2.5 represents a 2D convolution with the (5,5,3) feature map and the (3,3,3,2) weights to generate the (3,3,2) output. 2D convolution requires intensive computation resources and data bandwidth in hardware realizations, therefore, it is a good benchmark to evaluate the performance of SIMD extension.

Figure 2.5: Process of 2D convolution in a convolution layer.

#### 2.3.1 Standard V-Extension

The standard RISC-V vector extension is still a work in progress. The Ara [17], a 64-bit vector processor, is the well-known hardware implementation of the RISC-V vector extension based on the v0.5 draft. According to the latest specification, 7 new CSRs and a new set of 32 architectural registers are extended to the base RV32I instruction set. The extended vector CSRs are responsible to change the number of elements, vector length, rounding modes, which can be directly modified by Zicsr instructions during runtime. Some important CSRs are selected from the RISC-V specification and are presented in Table 2.2. Values in the new vector register file are arranged as packed elements. The packing format varies upon the value in vector CSRs. Each 32-bit vector register can store the combination of 1 four-byte element, 2 two-byte elements, and 4 one-byte elements with the respective configuration in VTYPE. Leftover elements during the calculation are masked out by the value in vector register v0. The v0 register always supplies the byte-wise mask bits of masked vector instructions. Vector instructions are grouped into 5 categories:

| Address | Privilege | Name   | Description                        |

|---------|-----------|--------|------------------------------------|

| 0x008   | URW       | vstart | vector start position              |

| 0x009   | URW       | vxsat  | fix point saturate flag            |

| 0x00A   | URW       | vxrm   | fix point rounding mode            |

| 0x00F   | URW       | vcsr   | vector control and status register |

| 0xC20   | URO       | vl     | vector length                      |

| 0xC21   | URO       | vtype  | vector data type register          |

| 0xC22   | URO       | vlenb  | vector register length in bytes    |

Table 2.2: Definition of new vector control and status registers

- Vector load instructions including addresses increment with pattern unit-stride, strided and indexed,

- Vector store instructions including addresses increment with pattern unit-stride, strided and indexed,

- Vector atomic memory operations instructions to support synchronization between multi-cores,

- Vector arithmetic instructions including operations between scalar-vector, vector-vector and vector-matrix, and

- Vector configuration instructions.

The format and length of vectors change dynamically by the vector configuration-setting instructions to achieve high throughput on mixed-width operations in a single loop. The runtime configuration brings great versatility in the instruction set level.

#### 2.3.2 Cambricon ISA

Cambricon ISA [1] is a machine learning specific instruction set and it has been proved effective among different kinds of machine learning techniques, including K-means [18], multilayer perception [19] and convolution neural network [20]. There are three guidelines of Cambricon ISA and Cambricon-based hardware.

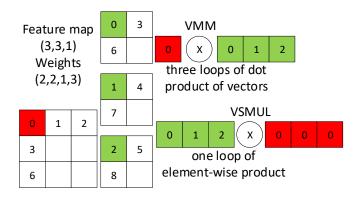

- Data-Level Parallelism As mentioned before, machine learning tasks usually consist of massive data transmission and intensive computation. Thankfully, data flow trends to have a uniform and symmetric pattern. Weights in 2D convolution share the same factor with either input feature maps or output feature maps. The convolution can be vectorized by a factor of the input depth or the output depth. Either way brings the opportunity for SIMD architecture to leverage the performance while compressing the code density.

- Customized Vector/Matrix Instructions Most of the convolution flow can be factorized as a loop of tensor operations. The 2D convolution can be unrolled into multiplying multiple vectors by matrices. Different types of layers can be abstracted to combinations of vector-matrix operations. The studied vector/matrix instructions are efficient for machine learning tasks.

- Using On-chip Scratchpad Memory One of the biggest drawbacks of the standard vector register file is that the width of vector registers are fixed. Although multiple vector registers can be grouped together as a larger register to store longer vectors, it is more straightforward to use a block of memory as the storage. The 2D convolution often needs massive and continuous vector/matrix data with various sizes. The vector registers may not best suit the machine learning tasks due to their relatively smaller sizes, but higher costs. Moreover, because the sizes of vector/matrix are now defined

in each instruction, the limitation of fetching size caused by the fixed-width vector registers is also eliminated by using scratchpad memory.

As shown in Table 2.3, the Cambricon ISA follows the reduced instruction set computer (RISC) architecture that only has specific data transfer instructions to contact the external memory. All computing kernels initiate with vector/matrix load instruction to bring the necessary operands into the scratchpad memory. Processing units fetch operands from the scratchpad memory and also write the result back to it.

**Table 2.3:** Overview of Cambricon ISA (From: Table 1 Chen et al. [1])

| Instruction type |        | Example                                                                                                                                                                   | Operands                                                   |

|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| Control          |        | jump, conditioanl branch                                                                                                                                                  | register (scalar value), immediate                         |

| Data transfer    | Matrix | matrix load/store/move                                                                                                                                                    | register (matrix address/size,<br>scalar value), immediate |

|                  | Vector | vector load/store/move                                                                                                                                                    | register (vector address/size, scalar value), immediate    |

|                  | Scalar | scalar load/store/move                                                                                                                                                    | register (scalar value), immediate                         |

| Computational    | Matrix | vector multiply matrix, matrix multiply scalar,<br>outer product, matrix add/sub matrix                                                                                   | register (matrix/vector<br>address/size, scalar value)     |

|                  | Vector | vector element-wise arithmetic (add/sub, multiply/divide),<br>vector transcendental functions (exponential logarithmic),<br>dot product, random vector generator, max/min | register (matrix/vector<br>address/size, scalar value)     |

|                  | Scalar | scalar arithmetic/transcendental                                                                                                                                          | register (scalar value)                                    |

| Logical          | Vector | vector compare (greater than, equal),<br>vector logical operations(and, or, inverter),<br>vector greater than merge                                                       | register (vector address/size, scalar)                     |

|                  | Scalar | scalar compare, scalar logical operations                                                                                                                                 | register (scalar), immediate                               |

The scratchpad memory is a small size of memory near the processing unit to handle quick access. Unlike the cache memory, the scratchpad memory does not belong to the memory hierarchy and only serves as a temporary storage space. The content in scratchpad memory must store to the external memory to reveal the latest data. The capacity of internal scratchpad memory is fixed to have 64KB for vector scratchpad memory and 768KB for matrix scratchpad memory.

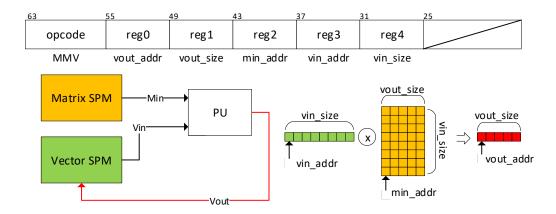

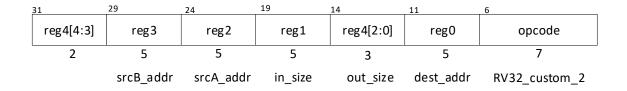

The vector operands and matrix operands locate in the respective internal memories with different address spaces. The format of matrix multiply vector (MMV) instruction, presented in Figure 2.6, includes five source registers to provide three addresses and two sizes. Values in the Reg2 and Reg3 may be identical. However, because vector addresses and matrix addresses are fixed by the ISA format, they refer to different memory spaces, whether matrix scratchpad memory (SPM) or vector SPM. As a result, the processing unit can only get sources and write the result back to the corresponding location.

Figure 2.6: Matrix Multiply Vector instruction and its data arrangement.

Cambricon ISA assumes that the width of each element in a vector/matrix is fixed during runtime. It does not support mix-width computation to avoid data alignment issues in the scratchpad memory. Because the size of vectors is counted in terms of the number of elements, dynamically changing the element width significantly increases the logic control overhead to calculate the starting address of a vector/matrix.

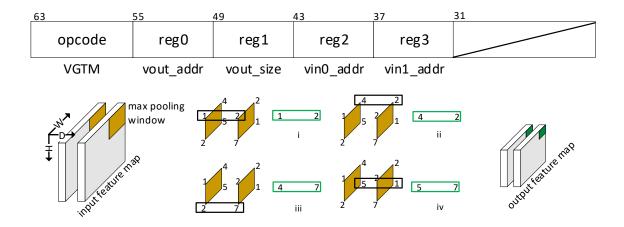

Another great contribution of Cambricon ISA is that it introduces the vector greater than merge (VGTM) instruction, which is effective for max-pooling layers in CNNs. The instruction compares two vector element-wisely and keeps the larger value as one result. A max-pooling layer is commonly placed between convolution layers in CNNs. The purposes of max-pooling include to reduce the sizes of feature maps, to decrease sizes of parameters, and to prevent over-fitting by only keeping the largest value in a spatial region, as demonstrated in Figure 2.7. The max-pooling flow iterates along with the max pooling window with VGTM instructions. Each VGTM instruction recursively compares values in depth-wise with the previous results and finally keeps the largest value across the window.

This generalized instruction set covers different scenarios among machine learning techniques. Changing machine codes to realize a new algorithm are much easier than modifying

Figure 2.7: Vector Greater Than Merge instruction with the max pooling flow.

the hardware implementation. As a result, because of the rapid architecture change in the machine learning area [21–23], instruction-based accelerators [17,24] are preferred over application-based accelerators for future-proofing.

#### 2.4 Summary

This chapter introduces the background information that is related to this thesis work. The format and different extensions in RISC-V ISA are discussed firstly. It is an open-source ISA based on the RISC principles to deliver general-purpose computation. Developers can easily extend the instruction set with standard extensions and customized extensions to enhance performance. Then, the concept of parallel computing is presented. The two schemes of instruction-level parallelism, VLIW and superscalar, are compared with each other. Tomasulo algorithm, as a method to achieve the out-of-order execution, is explained with an example. Data-level parallelism is discussed as the approach to speed up data-intensive computing. In the end, the standard RISC-V vector extension and Cambricon ISA are included as two typical SIMD instruction sets. Convolution layers and max-pooling layers are shown as examples of SIMD processes.

# Chapter 3 Superscalar Processor

### 3.1 Overview

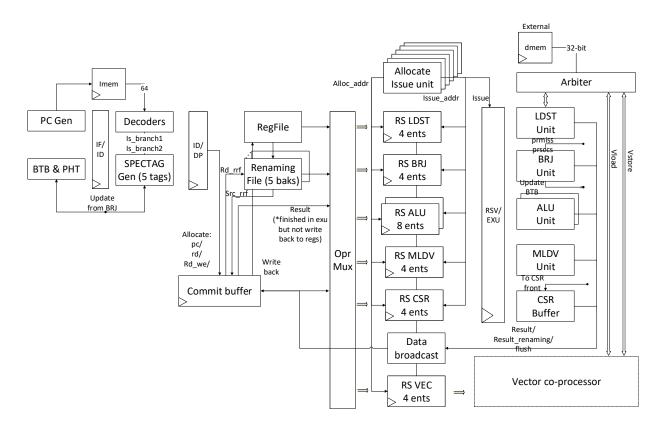

The architecture of the processor is based on *Modern Processor Design: Fundamentals of Superscalar Processors* [25] and Ridecore [12] with several modifications to enhance the performance and support machine-level privileged instructions.

The key specification is provided in Table 3.1. The proposed design supports 32-bit RISC-V machine mode with integer multiplication and division extension, RV32IM + Zicsr + Zifencei, which is compatible with the standard GNU toolchain with "march=rv32im" flag. The 6 reservation stations (RS) match the number of execution units that include 1 load/store unit, 2 arithmetic units (ALU), 1 integer multiplication/division unit, 1 control and status registers (CSR) buffer, and 1 branch unit.

Figure 3.1 illustrates the top-level diagram of the proposed design. There are six stages of pipeline, including instruction fetch (IF), instruction decode (ID), data dispatch (DP),

| Instruction Set Architecture | RV32IM | Data Width                  | 32-bit |

|------------------------------|--------|-----------------------------|--------|

| Address Width                | 32-bit | No. of LDST Entires         | 4      |

| No. of GPRs                  | 32     | No. of ALU Entires          | 16     |

| No. of Commit Entries        | 64     | No. of MUL Entires          | 4      |

| No. of Speculations          | 5      | No. of CSR Entires          | 4      |

| Branch History Width         | 10-bit | No. of BRJ Entires          | 4      |

| Ways of Superscalar          | 2      | No. of Reservation Stations | 6      |

Table 3.1: Key parameters of the processor

Figure 3.1: Top level diagram of the processor.

reservation stations (RS), execution (EX), and commit (COM). IF, ID, and DP can process two instructions at the same clock cycle. RS and EX can handle out-of-order execution following the Tomasulo Algorithm. The final COM re-orders the finished instructions and writes results back to registers sequentially.

### 3.2 Instruction Fetch

Program Counter (PC) is the address of the instruction that is currently executing. The current PC sends out to the system bus to fetch the corresponding instructions. Because the width of instructions in RV32IM is 32-bit, to match the 2-way superscalar, the instruction memory is implemented as 64-bit width so that each reading operation provides 2 instructions. As a result, the PC increases with the step of 8-byte by default. PC[31:3] is connected to the instruction memory as the true address to fetch the corresponding 2 instructions.

Due to the possible outcome of branch and jump instructions, the PC may be aligned to 4-byte. In that case, PC[31:3] still sends out as the instruction address, however, only the second instruction is valid. Based on the PC[2] bit, the invalid bit regarding the first instruction toggles high to invalidate the first instruction for the following stages. For example, if the PC jumps to 0b1100, the 0b1 becomes the address of instruction memory. The fetched two instructions are at 0b1000 and 0b1100 respectively. The current PC[2] bit of 1 yields an invalid bit to remove the behavior of first instruction at 0b1000. The PC increases with the step of 4-byte in this case to match the 8-byte alignment. As a result, the fetch width varies between 1 instruction and 2 instructions.

#### **3.2.1** Gshare Branch Prediction

A high-quality branch prediction algorithm improves pipeline throughput significantly. Unlike static branch prediction, such as always TAKEN for backward branch, dynamic branch prediction has a much better hit rate by visiting the past branch history to detect the correlated branches.

Gshare [26] technique is implemented in the design. The branch history register (BHR) is defined as 10-bit length generating  $2^{10}$  numbers of 2-bit adaptive predictors. The 2-bit saturating counter has proven to have consistently good prediction performance [27].

Figure 3.2 shows the Gshare branch prediction module. A small direct mapping cache, called branch target buffer (BTB), is placed in the branch prediction logic to store pairs of the branch PC address and branch target address. The pattern history table (PHT) holds the set of predictors. The BHR indicates the record of the last 10 branch outcomes, in which the bit of 1 shows TAKEN and the bit of 0 shows UNTAKEN.

The current PC[11:2] is exclusive-or-ed with the BHR bit-wisely to generate a branch pattern. Based on the pattern, a 2-bit predictor is selected from PHT to predict the outcome of the current PC. If both the current PC hits in BTB and the predictor yields TAKEN, the matched target address in BTB becomes to the speculative PC in the next cycle. All predictors are initialized to weak TAKEN.

Both branch predictors and BTB update as soon as the branch and jump instructions finish in the execution stage. As a result, compared with updating those two parts after the commit stage, the branch prediction module can provide a better prediction hit rate based on more recent branch results. The value in the BTB can be traced back by the PC of branch instructions. The corresponding target address in BTB changes to the target address based on branch outcomes. The BHR also propagates with branch instructions through pipelines to

Figure 3.2: Branch prediction module.

guarantee that the same predictor can be located in the PHT, and updated based on branch outcomes, following the sequence in Figure 3.3.

# 3.3 Instruction Decode

There are two decoders in the ID stage to simultaneously handle two instructions coming from the instruction memory. Each decoder generates essential information related to one instruction for later stages. Some of the most important information is listed below.

- rs1, rs2, rd: They hold the register numbers of the first source operand, the second source operand, and the destination.

- imm\_type: It indicates the encoding format of the immediate value.

- alu\_op: It indicates the required arithmetic operation of the instruction, such as addition, shift-right, and signed-division.

- rd\_we: It indicates whether the current instruction requires writing the final result back to the destination register, i.e., modifying the content in the register file. It enables the

Figure 3.3: 2-bit adaptive predictor encoding scheme.

renaming process on the destination register.

- target\_rs: It indicates which reservation station the current instruction is heading to.

- dmem\_op: It indicates the data length of load/store instructions, including 4-byte,

2-byte, and 1-byte. It also determines the extension scheme, either sign-extend or zero-extend, regarding 2-byte and 1-byte data.

- system\_op: It indicates types of system instructions, including FENCE.I, ECALL, and EBREAK. System instructions enable the CSR front module to trigger the exception handling logic.

- csr\_id: It holds the CSR id that the current instruction is operating with.

- is\_branch: It indicates that the current instruction is branch/jump and enables the speculation tag generator module to add a new speculative routine.

- inv: It indicates that the current instruction is not defined and supported in this processor. It disables the current instruction.

## 3.3.1 Speculation Tags

Two instructions in ID are padded with speculation bits and speculation tags. The speculation tag generator module is presented in Figure 3.4. Five sets of speculations and checkpoints are implemented by considering the worst-case scenario that 4 branch instructions are in the reservation station and 1 branch instruction is in the execution stage.

Figure 3.4: Speculation tag generator module.

The branch counter increases based on the incoming new branch instructions in ID and decreases based on the finished branch instruction from EX. The non-zero value represents that there are branch instructions in the pipeline but not executed yet. On the other hand, the incoming instructions are not speculative if the branch counter is equal to 0. If the branch counter is larger than 4, a stall signal is sent out to pause the IF stage to wait for the completion of previous branch instructions.

The speculation tag is encoded as 5-bit one-hot format. Those tags circularly shift right when new branch instructions are in this stage. The main speculation tag constantly shifts enabled by every new branch instruction. It rolls back to the speculation tag of the finished branch instruction, which restores its value before the prediction is performed.

The current design does not support out-or-order branch execution to simplify the recovery logic. When branch miss prediction happens, all speculative instructions, with high speculation bit, are removed in every stage. When branch prediction hits, all the speculation bits toggle down asynchronously by matching the correct speculation tag (branch\_tag\_done) from the branch execution unit to remove the original speculative status.

# 3.4 Data Dispatch

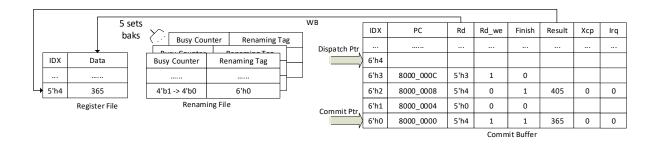

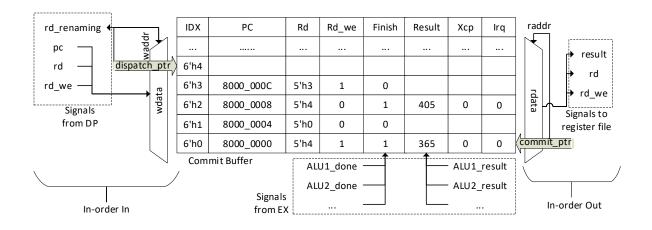

Data dispatch and commit buffer are combined to achieve out-of-order execution. General RISC-V instructions consist of two source registers, rs1 rs2, and one destination register, rd. To handle the two-way issue and write back, the register file is programmed as 4-read-2-write memory. Figure 3.5 demonstrates the data structure of the register file, renaming files, and commit buffer.

Figure 3.5: Data structure of register file, renaming files and commit buffer.

The register file consists of 32 general-purpose registers; while each renaming file consists of 32 entries of 4-bit busy counters and renaming destination to match with the register file. The 5 backups of renaming files match with each speculation tag.

The common busy vectors are replaced by the busy counters in this design, which represents that data is invalid if the respective counter is not equal to zero. For each instruction after ID, the counter increases by one, and the renaming destination (dispatch\_ptr) is copied from commit buffer matching with the destination register. The counter decreases by one when the final result is written back to the register file from the commit buffer.

Each renaming file only contains busy counters and renaming tags. The temporary results in the traditional renaming register file are merged into the result column in the commit buffer to simplify the hardware. The finish bit represents the instruction is done and the result is ready. There are three cases for source registers to take the right value in the DP stage:

- 1. Data is valid in the register file. Allocate the data to the target reservation station.

- 2. Data is invalid in both the register file and the commit buffer, i.e., the previous instruction is in the reservation station and wait to be issued. Allocate the renaming destination to the target reservation station and catch the result from the common data bus by matching the renaming destination.

- 3. Data is invalid in register file but ready in commit buffer, i.e., the result of previous instruction is ready in commit buffer, but it is not written back to register file yet. Take renaming destination as the address to get the result in the commit buffer and allocate the data to the target reservation station.

The dispatch pointer in the commit buffer is related to the DP stage instead of the COM stage. The instruction in DP takes dispatch pointer as its renaming destination, and allocates its PC and destination register to commit buffer, where is the beginning of the dynamic execution.

## 3.4.1 Renaming File Backups

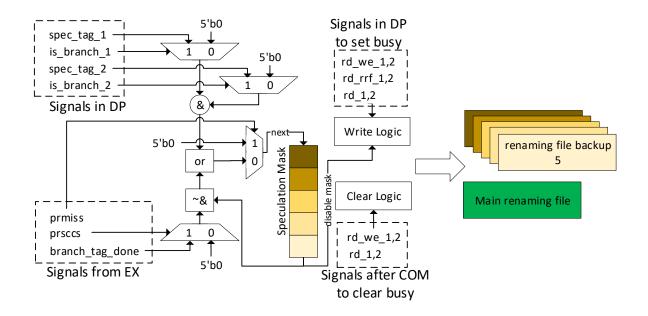

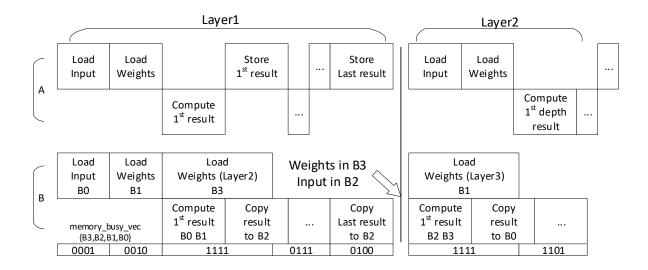

Figure 3.6 shows the control of all backups. The main renaming file is always the latest renaming file that contains every dispatched instruction. By default, five backups are modified together with the main renaming file, and their content is the same as the main renaming file until branch instructions arrive at the DP stage.

The speculation mask indicates which speculation tags are activated in the processor. Once a branch instruction is issued from the dispatch stage, the corresponding bit in the speculation mask toggles up to freeze one backup renaming file as a checkpoint of this branch instruction. The corresponding bit in the speculation masks toggles down when that branch instruction is finished.

For example, the speculation mask of 5'b00110 indicates that two branch instructions, with tags of 5'b00100 and 5'b00010, are executing after the DP stage. The two frozen backups of 00100 and 00010 bypass the write logic of the following speculative instructions, but keep clearing the busy status, because all committed instructions are not speculative.

Figure 3.6: Control of renaming file backups according to speculation status.

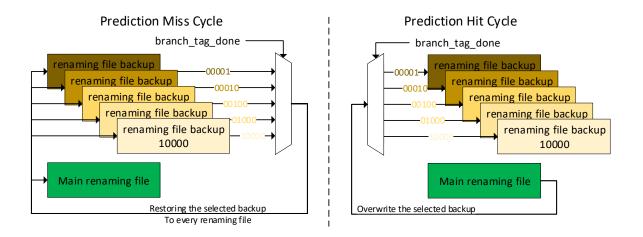

Once the branch instruction is finished, two outcomes bring two different flows to treat the renaming files. In Figure 3.7, the left side shows the behavior of miss prediction, while, the right side shows the behavior of hit prediction.

In the prediction miss cycle, the corresponding backup that matches the completed speculation tag (branch\_tag\_done) is selected as the source sheet. This selected sheet overwrites back to the main renaming file and the rest of the backups to restore them before the branch instruction is dispatched. Because the processor handles branch instructions in-order, the oldest miss prediction causes the following predictions incorrect. As a result, the restoration happens not only in the main renaming file but also in every backup file.

On the other hand in the prediction hit cycle, the corresponding backup that matches the speculation tag is released. The main renaming file, with the latest busy counters and renaming destinations, is selected as the source sheet. The main renaming file overwrites the corresponding backup file.

Figure 3.7: Renaming file handling in prediction miss cycle and prediction hit cycle.

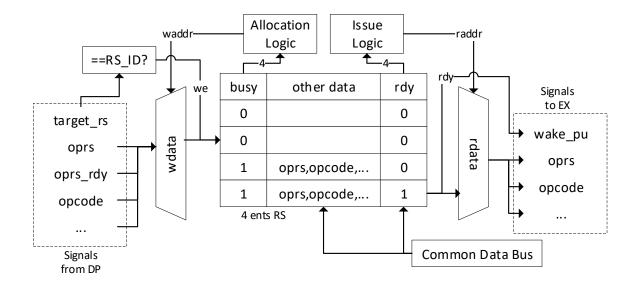

## 3.5 Reservation Stations

There are two control logic blocks in each reservation station, instruction allocation, and issue. Instructions from the DP stage are allocated to entries of reservation stations according to their target\_rs. Instructions in reservation stations with all operands ready are issued to their target processing unit in the EX stage. Figure 3.8 shows this process of the pair of one reservation station and one allocate/issue unit. For the sake of simplicity, the figure only shows the allocation of one instruction. However, dual dispatched instructions may lead to the same target reservation station so that the allocation width is doubled in the real implementation.

Instructions coming from DP are fully connected to every reservation station as the write data. However, only the write enable bit (we) of the matched reservation station toggles up. The identifiers are mapped as

- "0" for ALU: integer arithmetic instructions, such as ADDI, SLLI, AUIPC, ...

- "1" for BRJ: branch/jump instructions, such as BEQ, JALR, ...

- "2" for MLDV: integer multiplication/division instructions, such as MUL, DIVU, ...

- "3" for LDST: load/store instructions, such as LBU, SB, ...

Figure 3.8: Allocation and issue process of a reservation station with 4 entries.

• "4" for CSR: CSR instructions, such as CSRRW, CSRRCI, ...

According to the busy vector, the allocation logic assigns a write address (waddr) to determine which entry to go. Similarly, according to the ready vector, the issue logic assigns a read address (raddr) to determine which instruction to be executed. The entry clears as soon as the instruction is issued to the processing unit. Only instructions with all operands ready can leave the RS stage. Every unready instruction, whose operands are renaming values instead of actual values, constantly monitors the result in the common data bus to find its operand.

There are two allocation and issue schemes in the RS stage to handle different kinds of instructions.

1. In-order scheme. The BRJ, LDST, and CSR reservation stations are programmed to issue the instruction in-order. The reason is that those types of instructions modify another space of memory, such as the external memory and the CSR buffer. Out-oforder computing causes potential synchronization issues in external memory. The inorder scheme turns each reservation station to a first-in, first-out buffer. The allocation address increases one dispatched instruction at a time, and the issue address increases one issued instruction a time. The issue address therefore always points to the entry that has the oldest instruction. As long as the oldest instruction is not ready, the in-order reservation station does not issue any instruction to the processing unit, even though there are multiple ready instructions in the reservation station. As a result, from the perspective of the load/store unit, the load/store instructions come in as the order in the assembly code.

2. Out-of-order scheme. The ALU and MLDV reservation stations can handle out-oforder distribution. Because those instructions only modify the register file and the synchronization issue of the register file is already solved by register renaming, the out-of-order reservation station can always issue the ready instruction to increase the throughput. If there are multiple ready instructions available, the oldest instruction has the highest priority by comparing the renaming destination, because the later instruction always has a larger renaming destination.

Both schemes are limited in scope to their specific reservation stations. From the view of the whole processor, even though several load instructions are executed sequentially in their order, the rest of ALU instructions between those load instructions are executed potentially out-of-order in parallel. The commit buffer still must re-order those instructions and complete them in the original order.

Figure 3.9 shows the flush and clear logic in each reservation station based on the prediction outcome. As it is mentioned in the previous section, the processor does not support out-of-order branch. Therefore, as soon as the miss prediction happens, speculative instructions are flushed away no matter their speculation tags. RS stage suffers one clock cycle to remove those instructions and restore allocation/issue addresses. If the prediction yields success, reservation stations asynchronously clear the speculation bit with the matched speculation tag to remove the speculative status of the corresponding instructions.

Figure 3.9: Behavior of reservation stations according to the prediction outcome.

# **3.6** Execution Units