# Realization and Optimization of Metal-Semiconductor Field-Effect Transistors and Integrated Circuits based on Amorphous Zinc Tin Oxide

Von der Fakultät für Physik und Geowissenschaften der Universität Leipzig genehmigte

#### DISSERTATION

zur Erlangung des akademischen Grades

\*Doctor rerum naturalium\*\*

Dr. rer. nat.,

vorgelegt von M. Sc. Sofie Vogt, geb. Bitter geboren am 16.03.1989 in München

Gutachter: Prof. Dr. Marius Grundmann (Universität Leipzig)

Prof. Dr. Martin W Allen (University of Canterbury)

Tag der Verleihung: 20.07.2020

### Bibliographische Beschreibung

Vogt, geb. Bitter, Sofie:

Realization and Optimization of Metal-Semiconductor Field-Effect Transistors and Integrated Circuits based on Amorphous Zinc Tin Oxide

Universität Leipzig, Dissertation

163 Seiten, 118 Zitate, 71 Abbildungen, 6 Tabellen

#### Referat:

Im ersten Teil der vorliegenden Arbeit werden die physikalischen Eigenschaften, insbesondere die elektrische Leitfähigkeit, von Zink-Zinn-Oxid Dünnschichten sowie darauf basierenden Schottky-Dioden in Abhängigkeit von der Kationenkomposition bestimmt. Zur Herstellung dieser Dünnschichten wurde ein Verfahren genutzt, welches die Herstellung von kontinuierlichen Kompositiongradienten im Rahmen eines gepulsten Laserabscheidungsprozesses bei Raumtemperatur ermöglicht. Erster Schwerpunkt der Diskussion ist die Abhängigkeit elektrischer Eigenschaften der Dünnschichten sowie die Diodeneigenschaften vom Kationenverhältnis. Des Weiteren wird die Langzeitstabilität der Schottky-Dioden und der Einfluss der Sauerstoffzufuhr während der Kontaktherstellung auf die Eigenschaften der Schottky-Dioden herausgestellt. Die Ergebnisse tiefenaufgelöster Röntgenphotoelektronenspektroskopie werden diskutiert und ein Mechanismus, welcher zu einer Verbesserung der Schottky-Dioden über die Zeit führt, wird vorgestellt.

Die Erkenntnisse über die optimale Kationenkomposition und den Einfluss des Sauerstoffs auf die Eigenschaften von Schottky-Dioden wurden genutzt, um Metall-Halbleiter-Feldeffekttransistoren herzustellen, welche im zweiten Teil der vorliegenden Arbeit beschrieben werden. In einem ersten Schritt wurden hierfür die Abscheidebedingungen in der Sputterkammer optimiert und eine neue Abscheiderezeptur für die Herstellung von Feldeffekttransistoren eingeführt. Auch hier finden alle Abscheidungen bei Raumtemperatur statt. Die Abscheidung mittels Sputtern wurde gewählt, da diese Abscheidemethode größere industrielle Relevanz als die gepulste Laserabscheidung hat. Metall-Halbleiter-Feldeffekttransistoren mit zwei verschiedenen Gate-Typen werden vorgestellt und jeweils der Einfluss der Kanalschichtdicke auf die Transistoreigenschaften untersucht. Der Einfluss des durch die Herstellung erzeugten Sauerstoffreservoirs in dem Schottky-Gate Kontakt auf die Eigenschaften der Feldeffekttransistoren wird ebenso gezeigt wie der Einfluss eines thermischen Ausheizprozesses auf die Schaltgeschwindigkeit der Feldeffekttransistoren. Außerdem werden einfache Inverter, welche auf zwei gleichartigen Feldeffekttransistoren basieren, vorgestellt. Ebenfalls werden Schottky-Dioden Feldeffekttransistoren Logik basierte Inverter vorgestellt und charakterisiert.

Abschließend werden Ringoszillatoren, aufgebaut aus mehreren in Reihe geschalteten Schottky-Dioden Feldeffekttransistoren Logik basierten Invertern vorgestellt. Der Einfluss der Kanalschichtdicke und der Gate-Geometrie auf die Oszillationsfrequenz wird diskutiert.

#### Abstract

Vogt, geb. Bitter, Sofie:

Realization and Optimization of Metal-Semiconductor Field-Effect Transistors and Integrated Circuits based on Amorphous Zinc Tin Oxide

Universität Leipzig, Dissertation

163 pages, 118 citation, 71 figures, 6 tables

#### Abstract:

In the first part of the present work the physical properties, especially the electrical properties, of zinc tin oxide thin films as well as Schottky diodes based thereon are determined as a function of the cation composition. For film growth, a room temperature pulsed laser deposition process was used, which allows the realization of a continuous composition gradient within one sample. First focus of the discussion is the dependence of electrical properties of thin films as well as diode properties on the cation ratio. Furthermore, the long-term stability of the Schottky diodes and the influence of the oxygen supply during contact fabrication on the properties of the Schottky diodes are highlighted. The results of depth-resolved X-ray photoelectron spectroscopy measurements are discussed and a mechanism leading to an improvement of the Schottky diodes over time is elucidated.

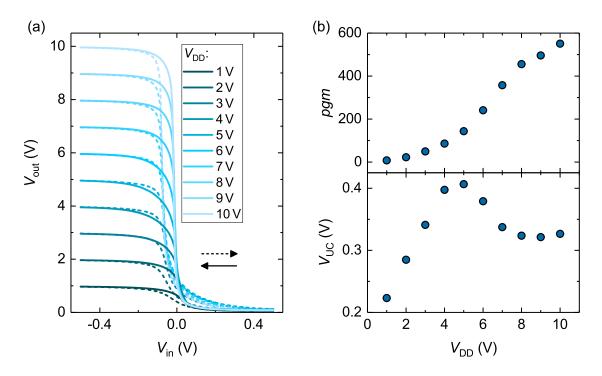

The findings on the optimal cation composition and the influence of oxygen on the properties of Schottky diodes were used to produce metal-semiconductor field-effect transistors, which are described in the second part of this thesis. In a first step, the deposition conditions in the sputter chamber were optimized and a new deposition recipe for the fabrication of field effect transistors was developed. Here, too, all depositions take place at room temperature. Sputter deposition was chosen because this deposition method has greater industrial relevance than pulsed laser deposition. Metal-semiconductor field-effect-transistors with two different gate types are presented and the influence of the channel layer thickness on the transistor properties is investigated. The influence of the oxygen reservoir in the Schottky gate contact on the properties of the field-effect-transistors is shown as well as the influence of a thermal annealing process on the switching speed of the field-effect-transistors. In addition, simple inverters based on two identical field-effect-transistors are demonstrated. Also Schottky diode field-effect-transistor logic based inverters are presented and characterized.

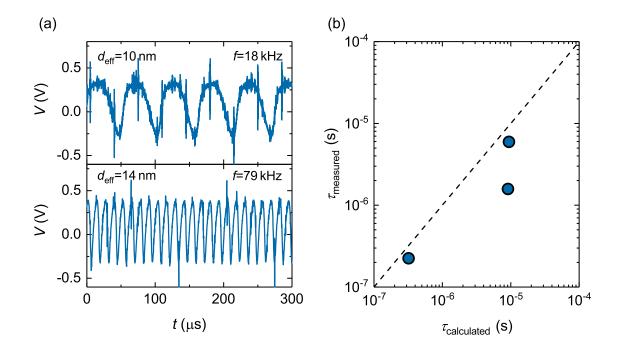

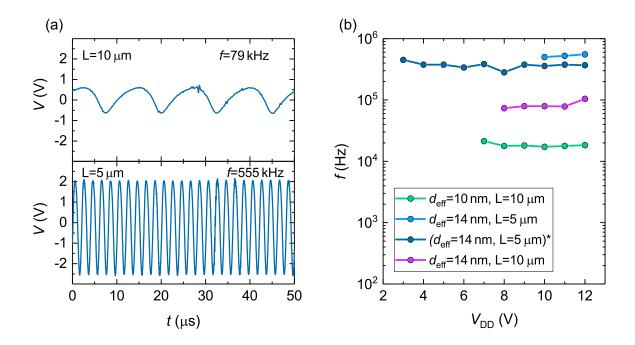

Finally, ring oscillators consisting of several series-connected Schottky diode field-effect-transistor logic based inverters are presented. The influence of channel layer thickness and gate geometry on the oscillation frequency is discussed.

#### Zusammenfassung der Dissertation

Realization and Optimization of Metal-Semiconductor Field-Effect Transistors and Integrated Circuits based on Amorphous Zinc Tin Oxide

Der Fakultät für Physik und Geowissenschaften der Universität Leipzig eingereicht von M. Sc. Sofie Vogt, geb. Bitter angefertigt am Felix-Bloch-Institut für Festkörperphysik Leipzig, Abteilung Halbleiterphysik 06/2019

Amorphous oxide semiconductors (AOSs) form a promising field of study in material research, driven by potential applications such as transparent and bendable electronic circuits. A prominent example, indium gallium zinc oxide, is nowadays already used in organic light emitting diode (OLED) displays as thin film transistors driving the individual pixel. Since indium is rare and has a high risk index [1], the investigation of alternative materials is of interest. A compound that comprises only naturally abundant elements, is zinc tin oxide (ZTO) [1]. As is typical for the group of AOSs, it exhibits a comparably high electrical conductivity and electron mobility even in the amorphous state [2-4]. The high potential of ZTO as pixel driver has been shown in 2006 by Görrn et al. using ZTO channels in metal-insulator-semiconductor field-effect transistors (MISFETs) as pixel drivers of OLEDs [5]. In literature, there are numerous reports on ZTO based MISFETs, which typically have the drawback of high voltage ranges required to switch the device from on to off. In 2017, Dang et al. presented the first ZTO based metal-semiconductor field-effect transistor (MESFET), which requires smaller voltages to switch the device [6]. However, an annealing of the ZTO channel was required to achieve a field-effect.

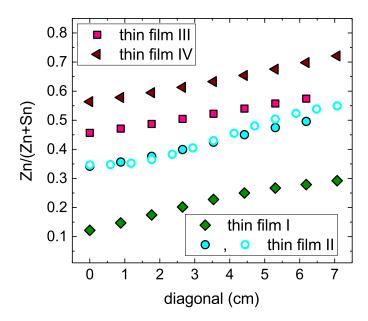

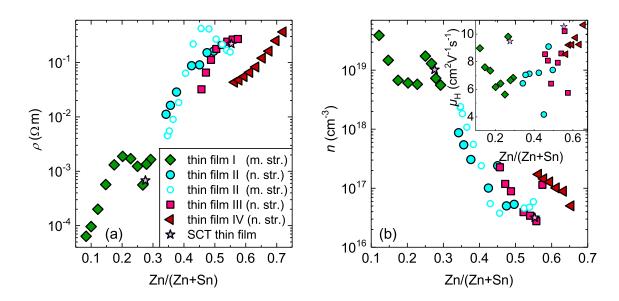

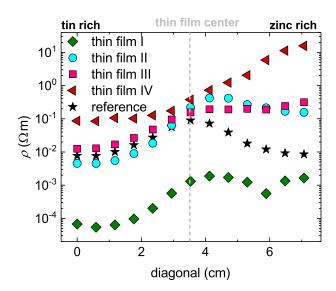

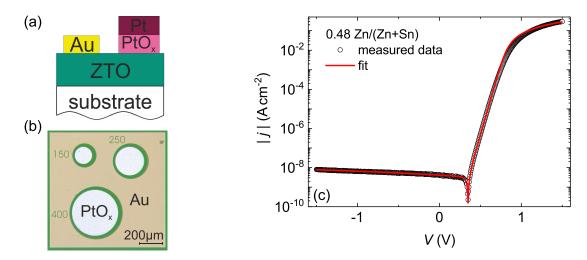

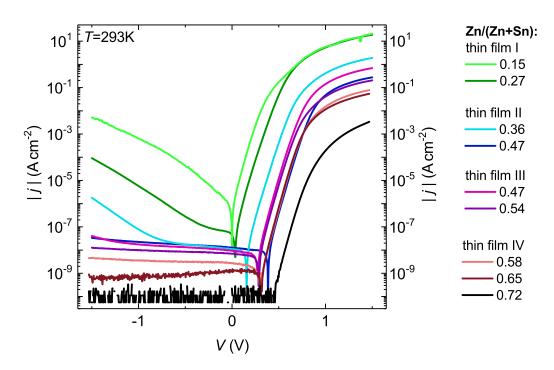

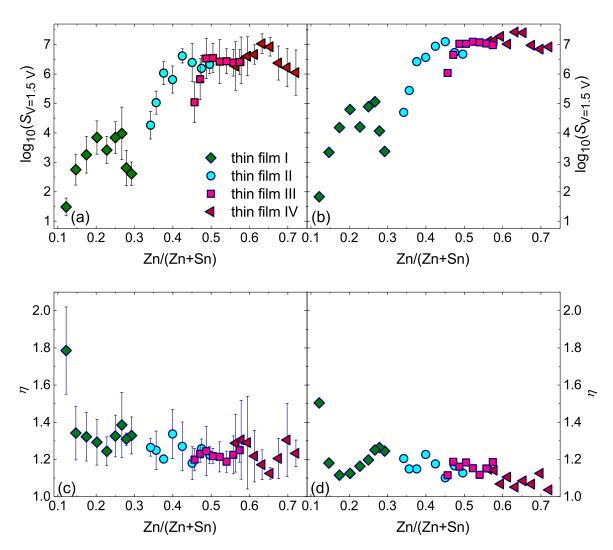

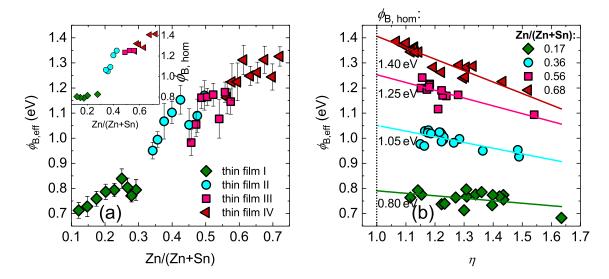

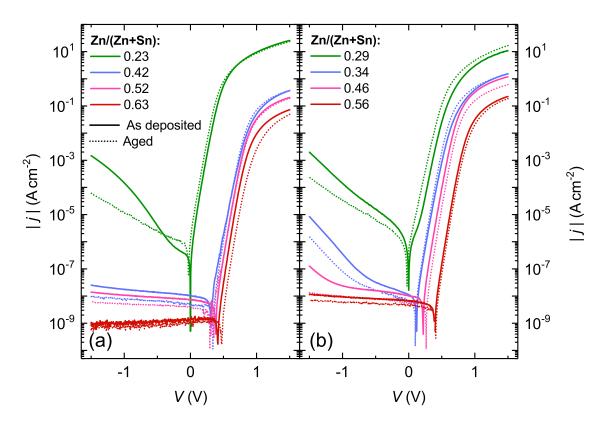

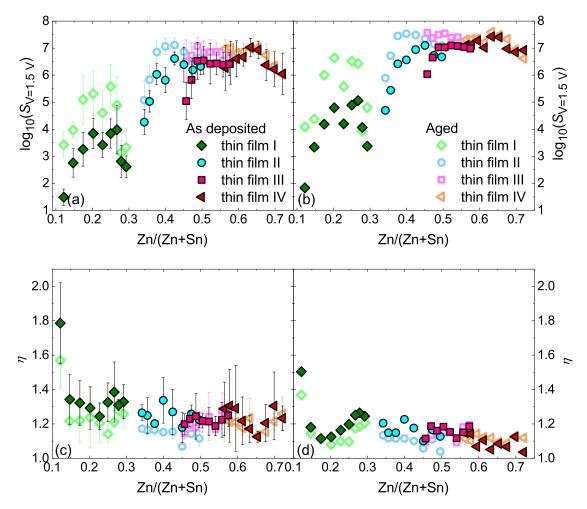

The aim of this work was the realization of MESFETs and integrated circuits based on amorphous ZTO deposited at room temperature. In the first part of this thesis the physical properties, especially the electrical properties, of ZTO thin films and of Schottky barrier diodes based on them are discussed in dependence on the cation ratio. A continuous composition spread approach for pulsed laser deposition (PLD) was used to achieve a large range of cation compositions within one deposition step [7]. A tuning of the free carrier density from  $3.9 \times 10^{19}$  cm<sup>-3</sup> for low zinc contents to  $0.5 \times 10^{17}$  cm<sup>-3</sup> for high zinc contents was achieved. An increase of the rectification ratio with increasing zinc content in the thin films was measured for the platinum oxide Schottky barrier diodes. A maximum current rectification ratio of  $2.7 \times 10^7$  was obtained for a zinc

content of  $0.63 \, \mathrm{Zn/(Zn+Sn)}$ . The increase of the rectification ratio with increasing zinc content is mainly due to a decrease of the reverse diode current, where the largest changes were observable for  $\mathrm{Zn/(Zn+Sn)} < 0.5$ .

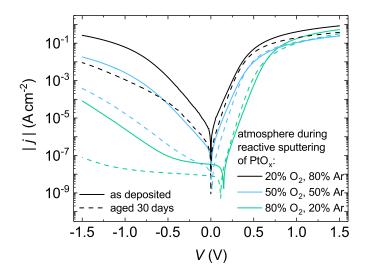

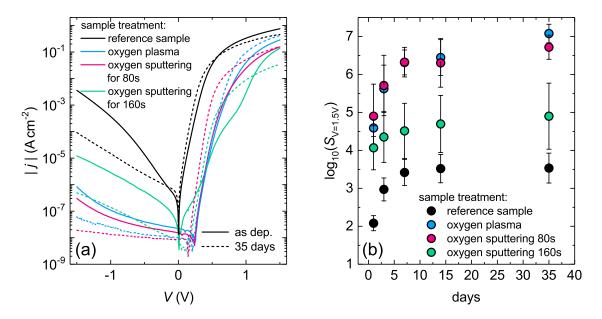

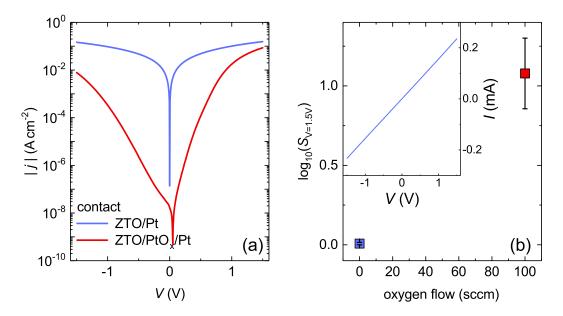

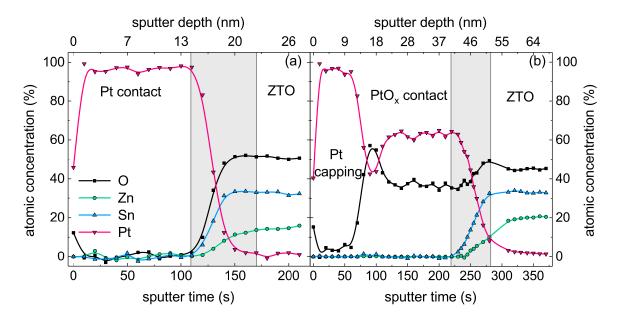

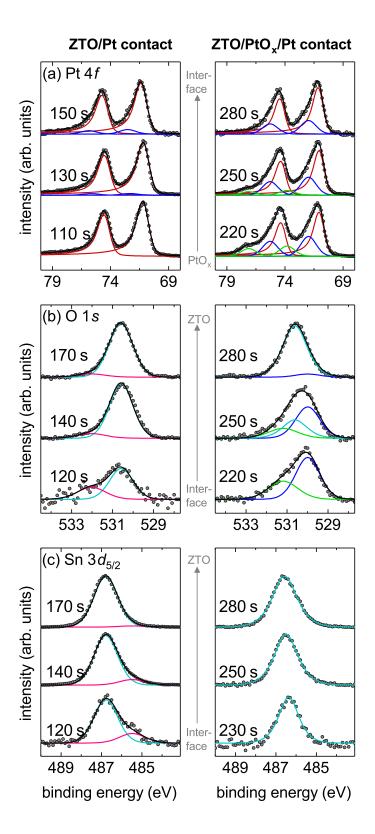

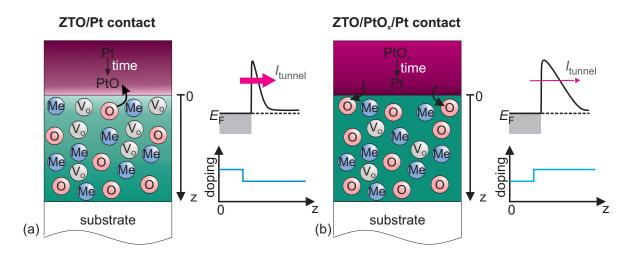

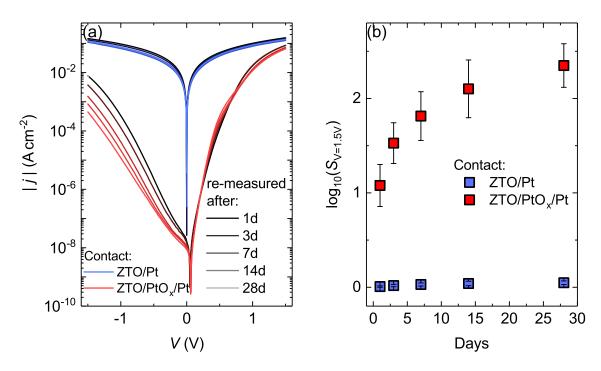

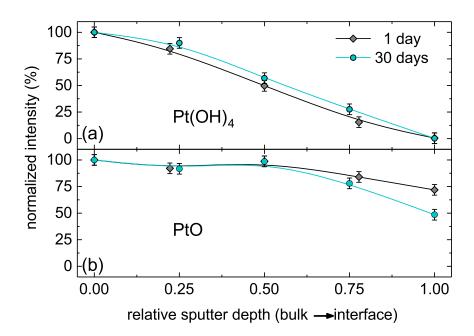

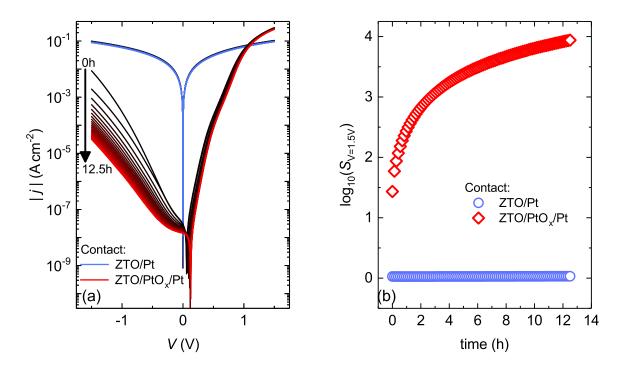

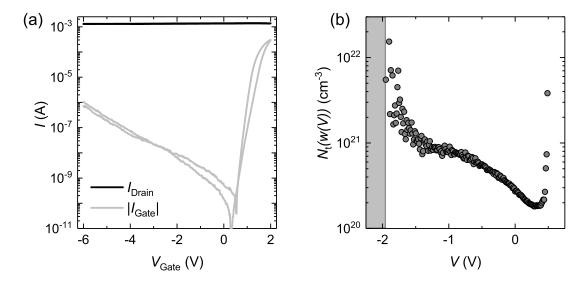

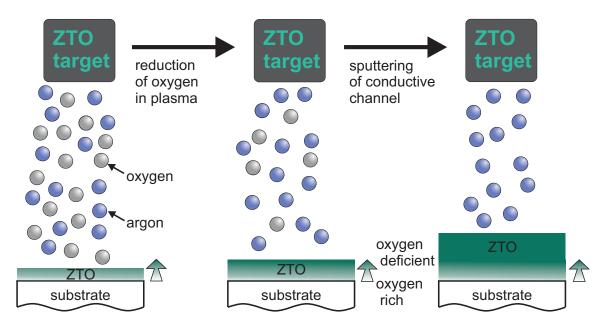

The long term stability of the Schottky barrier diodes was investigated. A decrease of the reverse diode current over time was observed, resulting in an increase of the rectification ratio. The forward current as well as the Schottky barrier height remained unaltered. It is known that oxygen plays a crucial role for the formation of Schottky barrier contacts to oxide semiconductors [8]. This leads to the hypothesis that oxygen diffuses from the noble metal oxide into the semiconductor. To investigate this, an experiment was conducted in which the extent of the oxygen reservoir in the Schottky barrier contact was varied. A higher oxygen reservoir led to higher rectification ratios in the as deposited state and a major improvement of the diodes over time. Using current-voltage measurements the time development of the improvement was investigated. Simultaneously, depth resolved X-ray photoelectron spectroscopy measurements were performed by Thorsten Schultz at the Humboldt Universität Berlin to study the spatial diffusion of oxygen. A diffusion of oxygen from the semiconductor into the metal contact was found as origin of the ohmic behavior of platinum/ZTO contacts. In contrast, a diffusion of oxygen from the metal oxide into the semiconductor was found to decrease the the reverse current of the platinum oxide/ZTO diodes.

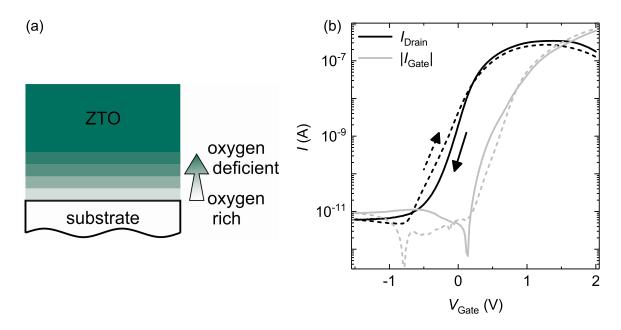

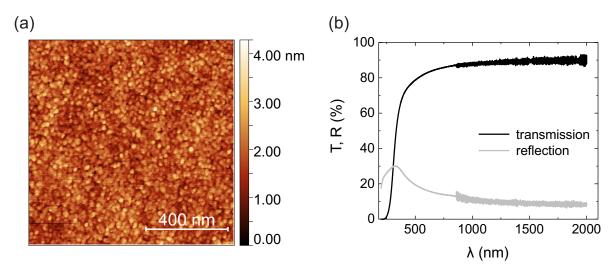

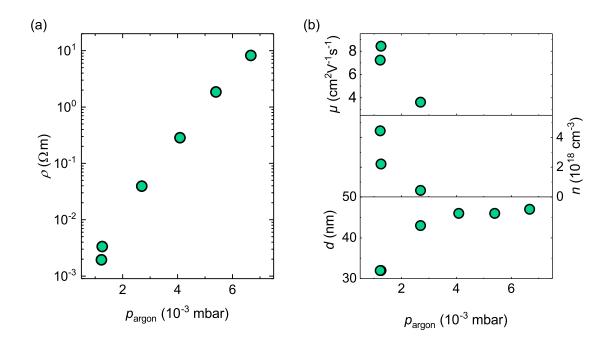

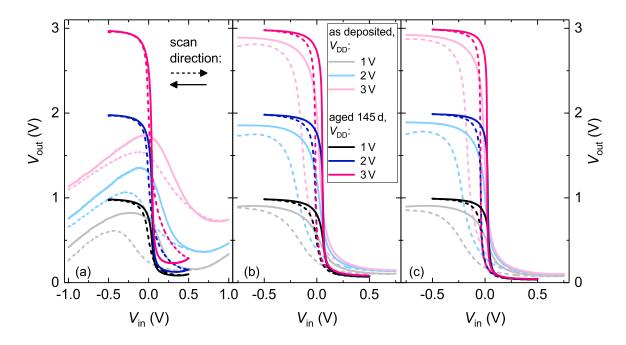

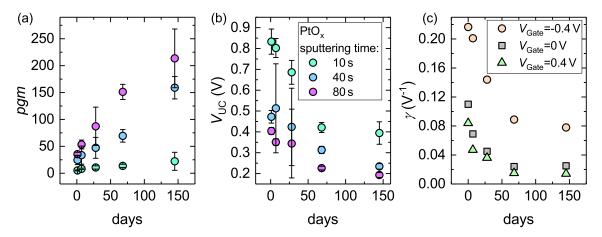

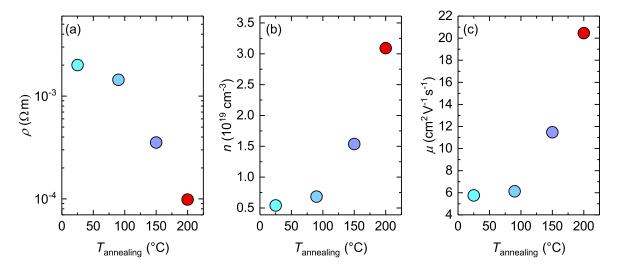

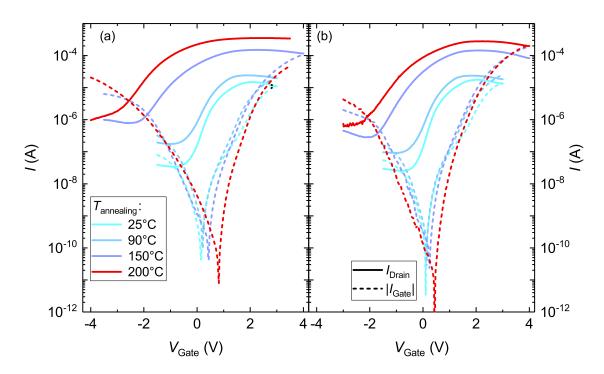

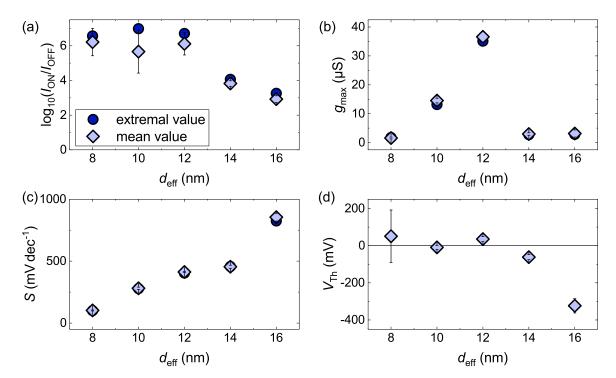

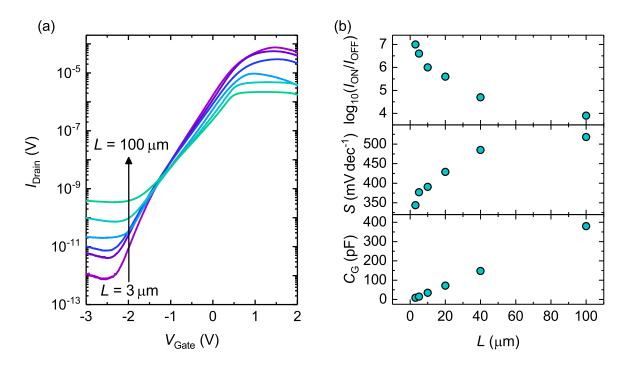

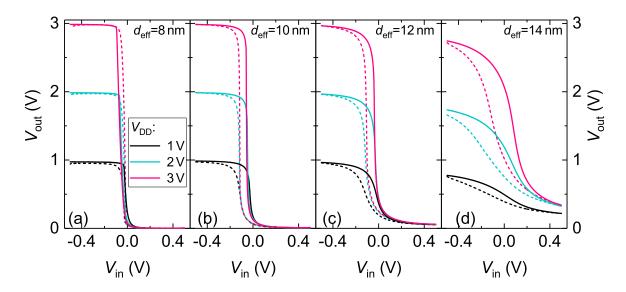

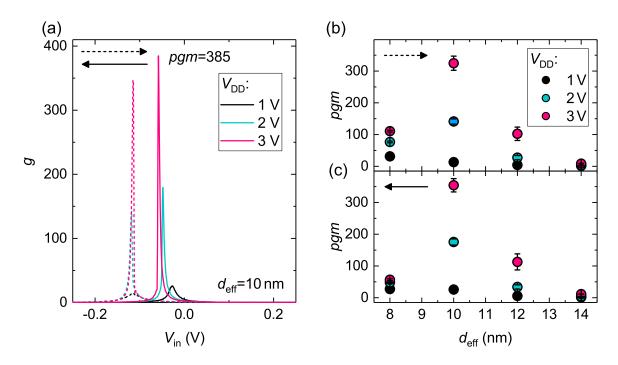

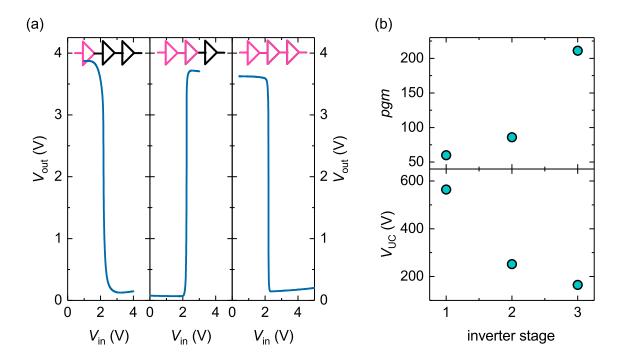

These results were used as a basis for the fabrication of MESFETs. Room temperature sputtering was chosen as deposition technique because it has a higher industrial relevance than PLD. A new sputtering recipe was developed, which allows the reproducible fabrication of MESFETs. Two different gate contact types were investigated:  $PtO_x/Pt$  and intrinsic  $(i-)ZTO/PtO_x/Pt$  gate contacts. The advantage of the first are sub-threshold swings as low as  $109\,\mathrm{mV}\,\mathrm{dec}^{-1}$ , whereas the latter exhibit drain current on-to-off ratios as high as  $1\times10^7$ . An optimization of the devices was sought by a variation of the channel thickness. This was used to tune the threshold voltage. Simple inverters were investigated for both gate types. For the  $PtO_x/Pt$  gate contacts, a peak gain magnitude (pgm) as high as 263 was measured after a storage of the device for 145 days in ambient condition. Simple inverters based on MESFETs with  $i-ZTO/PtO_x/Pt$  gate contacts have pgm values as high as 385.

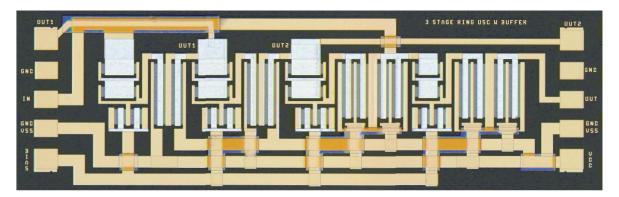

Schottky diode FET logic (SDFL) inverters were fabricated with  $i-\text{ZTO/PtO}_x/\text{Pt}$  gate contacts and a signal shift was achieved. Three stage ring oscillators based on SDFL inverters were characterized. A strong dependence of the oscillation frequency on the channel thickness and the gate geometry was observed. A maximum oscillation frequency of 555 kHz was obtained, which is comparable to values reported in literature for annealed ZTO channels [8,9].

#### **Bibliography**

- [1] P. Schlupp *et al.*: All Amorphous Oxide Bipolar Heterojunction Diodes from Abundant Metals, Adv. Electron. Mater., **1**, 1400023 (2015).

- [2] S. D. Brotherton: Introduction to Thin Film Transistors: Physics and Technology of TFTs, Springer International Publishing (2013).

- [3] H. Hosono *et al.*: Working hypothesis to explore novel wide band gap electrically conducting amorphous oxides and examples, J. Non. Cryst. Solids, **198-200**, 1, 165-169 (1996).

- [4] H. Hosono *et al.*: Novel oxide amorphous semiconductors: Transparent conducting amorphous oxides, J. Non. Cryst. Solids, **203**, 334-344 (1996).

- [5] P. Görrn *et al.*: Towards see-through displays: Fully transparent thin-film transistors driving transparent organic light-emitting diodes, Adv. Mater., **18**, 6, 738-741 (2006).

- [6] G. Dang *et al.*: Zinc tin oxide metal semiconductor field effect transistors and their improvement under negative bias (illumination) temperature stress, Appl. Phys. Lett., **110**, 7, 073502 (2017).

- [7] H. von Wenckstern *et al.*: Continuous Composition Spread Using Pulsed-Laser Deposition with a Single Segmented Target, CrystEngComm, **15**, 46, 10020-10027 (2013).

- [8] A. M. Hyland *et al.*: Giant improvement in the rectifying performance of oxidized Schottky contacts to ZnO, J. Appl. Phys., **121**, 2, 024501 (2017).

- [9] K. H. Kim *et al.*: Fast and stable solution-processed transparent oxide thin-film transistor circuits, IEEE Electron Device Lett., **32**, 4, 524-526 (2011).

- [10] B. Kim *et al.*: High-speed, inkjet-printed carbon nanotube/zinc tin oxide hybrid complementary ring oscillators, Nano Lett., **14**, 6, 3683-3687 (2014).

## Contents

| 1 | Introduction                                    |                                                                          |                                                                 |    |  |  |  |  |  |

|---|-------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------|----|--|--|--|--|--|

| 2 | Theoretical Descriptions                        |                                                                          |                                                                 |    |  |  |  |  |  |

|   | 2.1                                             | .1 The Amorphous Semiconductor Zinc Tin Oxide                            |                                                                 |    |  |  |  |  |  |

|   | 2.2                                             | Schott                                                                   | tky Barrier Diodes                                              | 6  |  |  |  |  |  |

|   | 2.3                                             | Field-                                                                   | Effect Transistors                                              | 12 |  |  |  |  |  |

|   | 2.4                                             | Invert                                                                   | er                                                              | 16 |  |  |  |  |  |

|   | 2.5                                             | Invert                                                                   | er Chain and Ring Oscillator                                    | 21 |  |  |  |  |  |

| 3 | Me                                              | $	ext{thods}$                                                            |                                                                 | 25 |  |  |  |  |  |

|   | 3.1                                             | Growt                                                                    | h and Structuring Techniques                                    | 25 |  |  |  |  |  |

|   |                                                 | 3.1.1                                                                    | Pulsed Laser Deposition                                         | 25 |  |  |  |  |  |

|   |                                                 | 3.1.2                                                                    | Sputtering Deposition                                           | 28 |  |  |  |  |  |

|   |                                                 | 3.1.3                                                                    | Photolithography                                                | 30 |  |  |  |  |  |

|   | cterization Techniques                          | 30                                                                       |                                                                 |    |  |  |  |  |  |

|   |                                                 | 3.2.1                                                                    | Hall Effect Measurements                                        | 30 |  |  |  |  |  |

|   |                                                 | 3.2.2                                                                    | XRD and XRR Measurements                                        | 31 |  |  |  |  |  |

|   |                                                 | 3.2.3                                                                    | Static and Dynamic Current-Voltage Measurements                 | 31 |  |  |  |  |  |

|   |                                                 | 3.2.4                                                                    | Further Characterization Techniques                             | 31 |  |  |  |  |  |

| 4 | Physical Properties of Amorphous Zinc Tin Oxide |                                                                          |                                                                 |    |  |  |  |  |  |

|   | 4.1                                             | Chara                                                                    | cterization of Pulsed Laser Deposited Zinc Tin Oxide Thin Films |    |  |  |  |  |  |

|   |                                                 | Havin                                                                    | g a Continuous Composition Spread                               | 34 |  |  |  |  |  |

|   | 4.2                                             | 2 Properties of Schottky Barrier Diodes in Dependence on the Cation      |                                                                 |    |  |  |  |  |  |

|   |                                                 | Comp                                                                     | osition                                                         | 39 |  |  |  |  |  |

|   | 4.3                                             | Long                                                                     | Term Stability of Schottky Barrier Diodes                       | 46 |  |  |  |  |  |

|   | 4.4                                             | Important Role of Oxygen for the Formation of Highly Rectifying Contacts |                                                                 |    |  |  |  |  |  |

|   | 4.5                                             | Processes Governing the Long Term Stability                              |                                                                 |    |  |  |  |  |  |

| 5                                                                 | Demonstration and Characterization of Zinc Tin Oxide Based De- |                                                                              |                                                                  |     |  |  |  |  |              |      |     |  |     |

|-------------------------------------------------------------------|----------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------|-----|--|--|--|--|--------------|------|-----|--|-----|

|                                                                   | vices                                                          |                                                                              |                                                                  |     |  |  |  |  |              |      |     |  |     |

|                                                                   | 5.1                                                            | Imple                                                                        | mentation of a New Sputtering Recipe                             | 64  |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                | 5.1.1                                                                        | Characterization and Electrical Optimization of the Zinc Tin Ox- |     |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                |                                                                              | ide Thin Films                                                   | 67  |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                | 5.1.2                                                                        | Optimization of the Gate Contact                                 | 72  |  |  |  |  |              |      |     |  |     |

|                                                                   | 5.2                                                            | Device                                                                       | es with ${\rm PtO}_x/{\rm Pt}$ Gate Contact                      | 76  |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                | 5.2.1                                                                        | Variation of the Channel Thickness                               | 76  |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                | 5.2.2                                                                        | Influence of the Oxygen Reservoir on the Performance and Long    |     |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                |                                                                              | Term Stability of Devices                                        | 82  |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                | 5.2.3                                                                        | Tuning of the Electron Mobility                                  | 89  |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                | 5.2.4                                                                        | Frequency Dependent Switching of Transistors                     | 92  |  |  |  |  |              |      |     |  |     |

|                                                                   | 5.3                                                            | Devices with $i\text{-}\mathrm{ZTO}/\mathrm{PtO}_x/\mathrm{Pt}$ Gate Contact |                                                                  |     |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                | 5.3.1                                                                        | Transistors with Varying Channel Thickness                       | 95  |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                | 5.3.2                                                                        | Simple Inverter                                                  | 99  |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                | 5.3.3                                                                        | SDFL Inverter                                                    | 103 |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                | 5.3.4                                                                        | Inverter Chain                                                   | 105 |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                | 5.3.5                                                                        | Ring Oscillators                                                 | 107 |  |  |  |  |              |      |     |  |     |

|                                                                   | 5.4                                                            | Comp                                                                         | arison to Literature                                             | 111 |  |  |  |  |              |      |     |  |     |

| 6                                                                 | Sun                                                            | Summary and Outlook                                                          |                                                                  |     |  |  |  |  |              |      |     |  |     |

| $\mathbf{A}$                                                      | bbre <sup>,</sup>                                              | viation                                                                      | ıs                                                               | 117 |  |  |  |  |              |      |     |  |     |

| List of Symbols Bibliography List of Own and Contributed Articles |                                                                |                                                                              |                                                                  |     |  |  |  |  |              |      |     |  |     |

|                                                                   |                                                                |                                                                              |                                                                  |     |  |  |  |  | $\mathbf{A}$ | ppen | dix |  | 137 |

### Chapter 1

### Introduction

In recent years, the use of amorphous oxide semiconductors (AOSs) as an alternative to silicon based technologies for use in displays has gained in importance. In the field of displays, AOSs discloses the possibility to realize energy saving and faster displays for mobile phones and other technical applications. The currently most common displays are based on liquid crystals, which require back-lightning and switch comparatively slow. A promising alternative is the use of organic light emitting diodes (OLEDs), which are self-luminous and have higher switching speeds than displays based on liquid crystals. The control of OLEDs in displays is more efficiently done by using AOSs compared to amorphous silicon, as their electron mobility exceeds that of amorphous silicon [1]. Therefore, the outstanding advantages of AOSs based technologies are lower fabrication costs and performance, e.g. a faster switching of devices, compared to amorphous silicon electronics. In addition, large scale deposition at low temperatures is possible.

The high electron mobility of AOSs compared to amorphous silicon is due to the electronic structure of this material group. The conduction band minimum is predominantly formed by the large, spherical s orbitals of the metal cations [2,3]. This leads to an insensitivity against small variations in the bond angle, which are typical for amorphous materials. Electron mobilities 10 to 50 times higher than those of amorphous silicon were reported [1]. In addition, AOSs may be deposited at low or even room temperatures which allows the use of thermally unstable substrates, such as flexible plastic substrates [4]. As mentioned above, field-effect transistors (FETs) based on AOSs may be used to control OLED pixels in displays. As of today, amorphous [! ([!)3]IGZO is used for this purpose [5,6]. However, a disadvantage of [! ([!)3]IGZO is the use of rare and expensive indium [7]. An alternative, less studied material is amorphous [! ([!)3]ZTO. It consists of naturally abundant and non-toxic elements only [7]. For room temperature deposited [! ([!)3]ZTO, electron mobilities exceeding

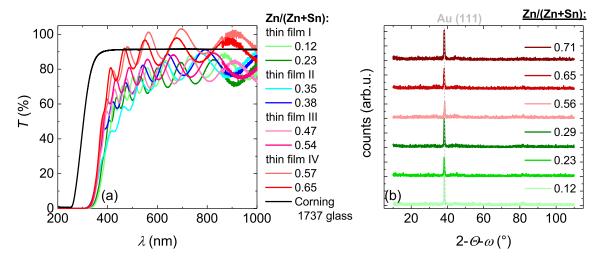

12 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> [8] and optical band gaps around 2.8 eV have been reported [9]. In 2006, Görrn et al. demonstrated the use of [! ([!)3]ZTO based FETs for the control of OLED pixels on a transparent substrate [10,11]. Up to now, most [! ([!)3]ZTO based devices in literature are metal-insulator-semiconductor field-effect transistors (MISFETs), which have the disadvantage of large voltage ranges which are typically required to switch the devices from the on to the off state. Moreover, an annealing of the channel and/or a deposition at elevated temperatures are often required to improve the performance and stability of the devices [12,13]. The influence of the stoichiometry on the performance of devices and the stability against bias stress has been discussed [13].

Recently, the first [! ([!)3]MESFET based on amorphous [! ([!)3]ZTO has been demonstrated [14]. In comparison to MISFETs, a smaller voltage range is required to switch the device from on to off. However, a deposition at elevated temperatures and an annealing at more than 400°C is required to achieve a field-effect. This is incompatible with the use of bendable organic substrates, where the temperature must not exceed 350°C [1].

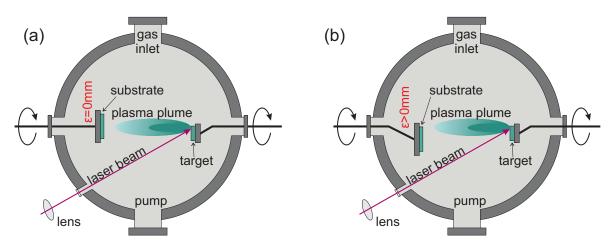

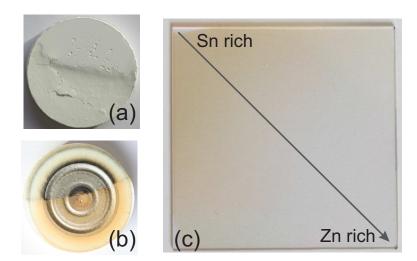

The goal of this work was the realization and characterization of metal-semiconductor field-effect transistors (MESFETs) and integrated circuits based on amorphous [! ([!)3]ZTO deposited at room temperature. After a short summary of the theoretical descriptions of the devices that were investigated, a recapitulation of the deposition and characterization methods is given. The experimental part of this work is split into two parts. The first part concentrates on physical properties of [! ([!)3]ZTO thin films and Schottky barrier diodes based thereon. The second part is dedicated to the fabrication of MESFETs and integrated circuits based on these MESFETs, using the results from the first part. In chapter 4, the dependence of the physical properties of amorphous [! ([!)3]ZTO are investigated in dependence on the cation composition. To obtain a large range of cation compositions within one deposition process and at the same deposition parameters, a [! ([!])3] CCS approach for [! ([!])3] PLD was used for the deposition of thin films. Hall effect measurements were conducted to obtain their electrical properties and Schottky barrier diodes were investigated. A strong influence of the cation composition on the performance of platinum oxide Schottky barrier diodes was observed. Additionally, the performance of the Schottky barrier diodes could be further influenced by the oxygen content provided during the deposition of the metal oxide Schottky contacts.

The long term stability of the Schottky barrier diodes and in particular the crucial role of oxygen for the long term stability are discussed. With the help of depth resolved [! ([!)3]XPS measurements, an explanation for the origin of the absent long term stability is sought.

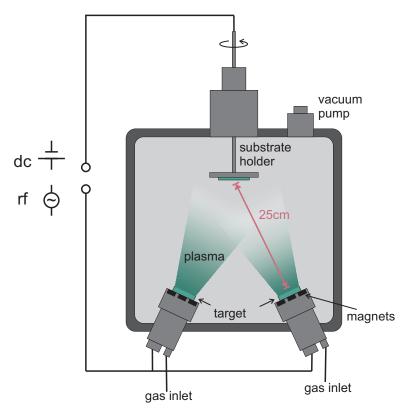

Based on the results discussed in the previous chapter, MESFETs and integrated circuits are reported in chapter 5. A deposition by sputtering was chosen, as this method is already used commercially and large scale depositions are possible. As for the deposition by [! ([!)3]PLD, all thin films were fabricated at room temperature. An optimization of the deposition conditions as well as the proposal of a new sputtering recipe for the fabrication of FETs is presented. With this sputtering recipe the fabrication of MESFETs at room temperature is possible. An optimization of the gate contact was performed, using two different approaches for the realization of a functional platinum oxide gate contact. The first gate contact is without and the second with an additional intrinsic [! ([!)3]ZTO layer [8] between the conductive channel and the gate contact. An investigation of the influence of the channel thickness is presented for both gate types. For the contacts without intrinsic [! ([!)3]ZTO layer, the important role of oxygen for the formation of the rectifying gate contact is again investigated for the sputtered thin films. In addition, the switching speed of MESFETs is discussed. Using the second contact type, MESFETs and simple inverters based thereon as well as [! ([!)3]SDFL inverters are reported. These devices represent the first step towards integrated circuits. An inverter chain as well as ring oscillators based on the [! ([!)3]SDFL inverters are discussed. Further, a maximization of the oscillation frequency is sought by a variation of the channel thickness and contact geometry.

Additionally, the results are compared to devices reported in literature based on amorphous [! ([!)3]ZTO.

In the last part of this thesis a summary of the presented results is given and an outlook on possible further investigations is presented.

Annotation: This work was prepared in the semiconductor physics group of the Felix-Bloch-Institut of the Universität Leipzig. Contributions by third parties are marked in the text and are by current or former members and students of the Universität Leipzig. The only exception is a contribution by Thorsten Schultz, who works at Humboldt Universität Berlin. References to publications with own contribution are marked with 'E'.

### Chapter 2

### Theoretical Descriptions

### 2.1 The Amorphous Semiconductor Zinc Tin Oxide

In this work, devices based on amorphous [! ([!)3]ZTO are presented. Therefore, a short summary of the most important material properties and advances in research regarding this material system is given.

Amorphous [! ([!)3]ZTO belongs to the group of amorphous oxide semiconductors (AOSs). This group contains oxides of heavy cations which have an electronic configuration of  $(n-1)d^{10}ns^0$ , n>3 [3]. Common to this material group is that the conduction band minimum is formed by the s orbitals of the metal cations. In the bound state of the metal oxides, these s orbitals are unoccupied. The s orbitals are extensive and spherical with a large spatial overlap, which renders them insensitive to variations of the bond angle, which are typical for amorphous oxide semiconductors. This leads to the comparably large conductivity and electron mobility of the AOS [2,3].

The most commonly used metal cations with this electronic configuration are indium, gallium, zinc and tin. Consisting of these elements, the well studied AOS [! ([!)3]IGZO and [! ([!)3]ITO are already used commercially [15-17]. The drawback of [! ([!)3]IGZO and [! ([!)3]ITO are that they contain the rare and expensive element indium [7]. An alternative consisting of readily available and cheaper components only is zinc tin oxide [7].

The high electron mobility can even be achieved for room temperature depositions [9]. In combination with the large optical band gap of [! ([!)3]ZTO (2.8 eV reported in ([9])), this material is an interesting candidate for future transparent device applications on bendable, organic substrates.

Most studies on amorphous [! ([!)3]ZTO concentrate on the use of the material as channel layer in transistors and integrated circuits. Numerous reports<sup>1</sup> deal with the optimization of crucial material properties of amorphous zinc tin oxide by employing a variety of different

<sup>&</sup>lt;sup>1</sup>Only a small overview over publications is given and no complete list of publications on amorphous [! ([!)3]ZTO.

deposition methods among which are [! ([!)3]PLD [8,9,18] [E1], sputter deposition [19,20], solution processing [21,22] and [! ([!)3]CVD [14]. For [! ([!)3]PLD and sputter deposited [! ([!)3]ZTO, the possibility of tuning the electrical and optical properties by a variation of the deposition conditions has been reported [8,9,18,20]. Electron mobilities as high as  $12.7 \,\mathrm{cm}^2 \,\mathrm{V}^{-1} \,\mathrm{s}^{-1}$  were achieved [8] as well as the possibility to tune the free carrier density over six orders of magnitude [9].

The investigation of the cation ratio of the ternary compound [! ([!)3]ZTO with the aim to optimize the electrical and optical properties has received special attention. Therefore, studies on the influence of the cation ratio on the material properties and the device performance were conducted for deposition methods such as [! ([!)3]PLD [9,13] [E2], sputter deposition [23-27] and solution processing [21,22,28,29].

The vast majority of publications concerning amorphous [! ([!)3]ZTO concentrate on the investigation of zinc tin oxide for the use as channel material in metal-insulator-semiconductor field-effect transistors (MISFETs). The first [! ([!)3]ZTO based MISFET was presented in 2005 by Chiang et al. [12]. Since then, numerous studies<sup>2</sup> on [! ([!)3]ZTO based MISFET have followed [10,11,22,29-33] and the first integrated circuits [21,32,34-36] were demonstrated. For all but the devices presented by Görrn et al. [10], a deposition at elevated temperatures (above 150°C) or an annealing step were required after the [! ([!)3]ZTO channel deposition to achieve high quality FETs.

Complementary to the MISFET devices based on [! ([!)3]ZTO, heterojunction and Schottky barrier diodes based on amorphous [! ([!)3]ZTO were investigated with the aim to fabricate junction field-effect transistors (JFETs) and MESFETs. The first heterojunction and Schottky barrier diodes based on amorphous pulsed laser deposited [! ([!)3]ZTO were reported by Schlupp et al. in 2014 and 2017, respectively [7,37]. Rectification ratios as high as seven orders of magnitude were reported. Also in 2017, the first [! ([!)3]MESFET based on amorphous [! ([!)3]ZTO was presented by Dang et al. [14] using reactively sputtered silver oxide as Schottky barrier gate material. The ZŢO was deposited by mist-chemical vapor deposition and drain current on-to-off ratios as high as five orders magnitude were achieved.

In this work, investigations on [! ([!)3]ZTO thin films deposited by [! ([!)3]PLD and sputter deposition as well as devices based on these thin films are discussed.

### 2.2 Schottky Barrier Diodes

Ohmic and rectifying contacts are required for almost all electronic devices. The most commonly used forms of rectifying contacts are based on pn-(hetero)junctions and metal-semiconductor contacts. In this chapter, a short summary on the theory of metal-semiconductor contacts is given, as all devices in this work will be based on this contact type. More detailed derivations can be found in [38,39]. Metal-semiconductor contacts are also called Schottky

<sup>&</sup>lt;sup>2</sup>Only a small overview over studies on amorphous [! ([!)3]ZTO based devices is given here.

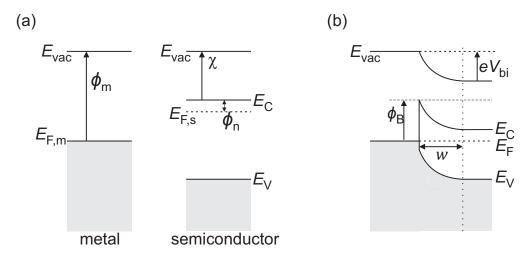

**Figure 2.1:** Schematic drawing of a metal and a *n*-type semiconductor before (a) and after (b) they are brought in contact.

barrier contacts, or diodes, after a first model proposed for the description of these contacts by W. Schottky and N. Mott [40-42].

As a n-type semiconductor is used in this work, all discussions are given for this configuration. The descriptions for p-type semiconductors are analogous.

Formation of a Barrier In general, a metal and a semiconductor have different Fermi levels  $E_{\rm F}$  and vacuum levels  $E_{\rm vac}$ . In Figure 2.1 (a), these levels are shown for metal and semiconductor, for the case that they are not in contact. The distance between conduction band minimum and Fermi level in the semiconductor is denoted by  $\phi_{\rm n}$  and  $\mathcal{X} = E_{\rm vac} - E_{\rm C}$  denotes the electron affinity, where  $E_{\rm C}$  is the conduction band minimum. If a metal with a work function  $\phi_{\rm m} = E_{\rm vac} - E_{\rm F,m}$  is brought into contact with a n-type semiconductor with the electron affinity  $\mathcal{X}$ , the Fermi levels of the two materials align. To achieve this, the bands in the semiconductor bend near the interface. If the work function of the metal is larger than the electron affinity of the n-type semiconductor, electrons flow from the conduction band of the semiconductor into the metal. The band bending continues until the Fermi levels have aligned. On the metal side electrons accumulate, while on the semiconductor side the ionized donors lead to a positive charge. This region is called space charge region or depletion region width w. The electrical field induced by the charge accumulation in the metal and the semiconductor inhibits the further diffusion of charges.

In Figure 2.1 (b), the case after the metal and semiconductor are brought in contact is shown. The barrier, which forms due to the aligning of the Fermi levels and the therefor necessary band bending, has a height of

$$\phi_{\rm B} = \phi_{\rm m} - \mathcal{X} \ . \tag{2.1}$$

The potential difference, which arises on the semiconductor side, is called built-in potential  $V_{\rm bi}$ , with

$$eV_{\rm bi} = \phi_{\rm B} - \phi_{\rm n} , \qquad (2.2)$$

where e is the elementary charge.

If an external voltage is applied between metal and semiconductor, the Fermi level in the semiconductor is shifted by eV. A negative voltage applied at the Schottky metal shifts the Fermi level in the semiconductor down, a positive voltage shifts it up. The application of a positive voltage is called forward regime. In this case, the applied voltage reduces the built-in potential. If the applied voltage is as large as  $V_{\rm bi}$ , the bands are flat and electrons may flow freely from the semiconductor into the metal. For negative applied voltages, electrons flowing from metal to semiconductor see a constant barrier, whereas electrons flowing from semiconductor to metal see an increased barrier. As a negative voltage is applied at the metal, electrons flowing from metal to semiconductor dominate the current flow and the current stays constant in the reverse regime.

To describe the band diagram in dependence on the applied voltage, the Poisson equation

$$\frac{\mathrm{d}^2\phi}{\mathrm{d}x^2} = -\frac{1}{\epsilon_r \epsilon_0} \varrho(x) \tag{2.3}$$

has to be solved, where  $\epsilon_{\rm r}$  and  $\epsilon_0$  are the relative dielectric constant and the vacuum permittivity, and  $\phi$  is the electric potential.  $\varrho$  is the carrier density. This equation has to be solved in the regime  $0 \le x \le w$ , where x-axis is perpendicular to the metal semiconductor interface. The interface is located at x = 0. In the abrupt approximation the carrier density is given as

$$\varrho = \begin{cases}

eN_{\mathcal{D}} & \text{for } 0 \le x \le w \\

0 & \text{for } x > w

\end{cases}$$

(2.4)

With the boundary conditions  $\phi(x=0) = -eV_{bi}$  and  $\phi(x=w) = 0$ , and the condition that  $\frac{d\phi}{dx}(w) = 0$ , the Poisson equation can be solved by integrating twice. For a constant doping  $N_D$ , the potential in dependence on the position is

$$\phi(x) = -\phi_{\rm B} + \frac{e^2 N_{\rm D}}{\epsilon_{\rm r} \epsilon_0} \left( wx - \frac{1}{2} x^2 \right)$$

(2.5)

with

$$w = \sqrt{\frac{2\epsilon_{\rm r}\epsilon_0}{eN_{\rm D}}(V_{\rm bi} - V)}$$

(2.6)

as solution. V is, as described above, the externally applied voltage.

**Depletion Region Capacitance** The charge Q in the depletion region is

where  $A_0$  is the contact area. Using the charge Q, the capacitance of the depletion region can be calculated as

$$C = \left| \frac{\mathrm{d}Q}{\mathrm{d}V} \right| = \frac{\epsilon_{\mathrm{r}}\epsilon_{0}A_{0}}{w} \ . \tag{2.8}$$

The metal surface is an equipotential surface, which leads to an image charge effect. An electron at a distance x from the equipotential surface interacts with it as though a positive charge is located at -x. An attractive image force  $F_{\text{IF}}$

$$F_{\rm IF} = -\frac{e^2}{16\pi\epsilon_{\rm r}\epsilon_0 x^2} \tag{2.9}$$

acts on the electron in the semiconductor. This reduces the barrier by  $\Delta\phi$

$$\Delta \phi = \frac{e^2}{2\pi \epsilon_{\rm r} \epsilon_0} \sqrt{\frac{N_{\rm D} w}{\pi}} \ . \tag{2.10}$$

Due to w, this equation depends on the external voltage V. This effect is called image force lowering or Schottky effect.

Transport at the Barrier Depending on the barrier height and the energy of the electrons, there exist different transport mechanism over and through the barrier [38]. Typically, one transport mechanism dominates. The transport can be limited by diffusion, which is due to a carrier concentration gradient within the depletion region. Another transport mechanism, where the electrons transport takes place over the barrier is thermionic emission, which is possible due to the energy distribution of the electrons. Even at low temperatures, single electrons have energies high enough to overcome the barrier. In (thermionic) field emission, the electrons tunnel through the barrier. To enable the tunneling of electrons through the barrier, the barrier has to be thin enough and electron energies have to be sufficiently high. Further transport mechanisms are recombination in the depletion layer and hole injection from the metal [38]. In the case of amorphous [! ([!)3]ZTO, it is assumed that thermionic emission is the dominating transport mechanism [37] [E2]. It has to hold that the barrier height is larger than  $k_{\rm B}T$  and the mobility of the electrons has to be large enough that the mean free path is large against the depletion region width. The equation for the current density for the case of thermionic emission was first presented by A. Bethe [43] and later on refined by E. Rhoderick and R. Williams [44]. The current density can be written as

$$j = j_{\rm s} \exp\left(\frac{eV}{\eta k_{\rm B}T}\right) \left[1 - \exp\left(-\frac{eV}{k_{\rm B}T}\right)\right] ,$$

(2.11)

where  $j_s$  is the saturation current density and V the external voltage applied at the contact. T denotes the temperature,  $k_B$  the Boltzmann constant and  $\eta$  the ideality factor. The saturation

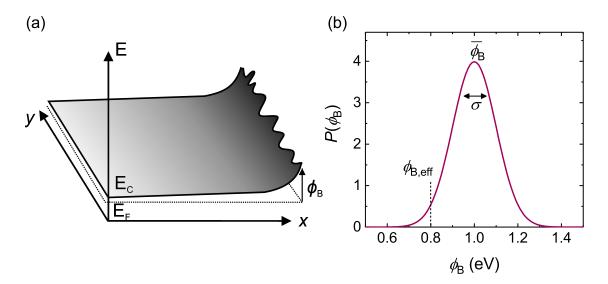

**Figure 2.2:** Schematic drawing of a fluctuating barrier height (a) and distribution of the barrier height for  $\sigma = 0.1 \, \text{eV}$ ,  $\phi_{\text{mean}} = 1 \, \text{eV}$  and  $\phi_{\text{eff}} \approx 0.8 \, \text{eV}$ . Adopted from [45, 46].

current density can be calculated as

$$j_{\rm s} = A^* T^2 \exp\left(-\frac{\phi_{\rm B,0}}{k_{\rm B} T}\right) ,$$

(2.12)

where  $\phi_{B,0}$  is the barrier height without an externally applied voltage and  $A^*$  is the Richardson constant, which can be calculated as

$$A^* = \frac{4\pi e m_{\text{eff}} k_{\text{B}}^2}{h^3} , \qquad (2.13)$$

with the effective electron mass  $m_{\text{eff}}$ . The ideality factor  $\eta$  is a measure for the voltage dependence of the barrier height and is given by

$$\eta = 1 + \frac{1}{e} \frac{\partial \phi_{\rm B}}{\partial V} \ . \tag{2.14}$$

As shown above, the image charge effect has a non-linear voltage dependence, which leads to an increase of the minimal achievable ideality factor from 1 to a slightly higher value (e.g.  $\eta = 1.02$  for crystalline Ga<sub>2</sub>O<sub>3</sub>) [38].

Non-Idealities in Real Diodes In real, non-ideal diodes, fluctuations in the barrier height may arise due to e.g. a rough interface between metal and semiconductor or local fluctuations in the free carrier density. In Figure 2.2 (a) the barrier height fluctuations are schematically drawn in a direction parallel to the sample surface.

The Schottky contact can be regarded as several diodes connected in parallel, each with a different barrier height. This was, amongst others, discussed by Yearian *et al.* [47,48]. J. Werner and H. Güttler [45] developed a model based on the assumption of a Gaussian barrier

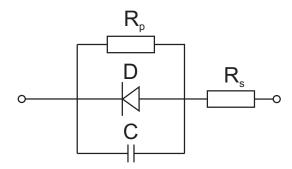

**Figure 2.3:** Equivalent circuit of a real diode with capacitance C, parallel resistance  $R_p$ , series resistance  $R_s$  and ideal diode D.

height distribution by:

$$P(\phi_{\rm B}) = \frac{1}{\sqrt{2\pi}\sigma} \exp\left(-\frac{(\overline{\phi}_{\rm B} - \phi_{\rm B})^2}{2\sigma^2}\right) , \qquad (2.15)$$

where  $\overline{\phi}_{B}$  is the mean barrier height and  $\sigma$  the standard deviation of the barrier height distribution. An exemplary distribution is shown in Figure 2.2 (b). The total current density is calculated by a weighted integration of the currents for each barrier height:

$$j = \int P(\phi_{\rm B}) j_{\phi}(\phi_{\rm B}) d\phi_{\rm B} . \qquad (2.16)$$

For thermionic emission an analytic solution exists [45]. Therefor the barrier height in equation 2.12 is replaced by the effective barrier height  $\phi_{B,eff}$ . The effective barrier height is always smaller than the mean barrier height, as current paths with smaller barrier heights are preferred. The effective barrier height can be written as:

$$\phi_{\rm B,eff} = \overline{\phi}_{\rm B,0} - \frac{\sigma_0^2}{2k_{\rm B}T} \ .$$

(2.17)

In general, the barrier parameters are voltage dependent.

Tung et al. [49] describe the current transport in Schottky diodes by thermionic emission with regions with smaller and larger barrier heights within the contact area. Regions with larger barrier heights have almost no contribution to the total current transport and are therefore disregarded [49]. Schmitsdorf et al. could show that a correlation exists between ideality factor and effective barrier height [50,51]. For ideality factors that are nearly 1, a linear dependence exists. Using this correlation, the homogeneous barrier height can be evaluated by a linear extrapolation of the plot of the effective barrier height against the ideality factor down to the smallest possible ideality factor. The minimal ideality factor is 1 in the ideal case but in reality slightly higher due to image charge effects [38]. If large ideality factors are used for this extrapolation, the obtained homogeneous barrier height  $\phi_{\rm B,hom}$  underestimates the real barrier height.

A second important reason for the non-ideal behaviors of real Schottky diodes are the influence of the resistance of the semiconductor and the metal over which part of the applied voltage V drops. These resistances are combined in the series resistance  $R_{\rm s}$ . Furthermore, an ohmic surface or grain boundary conduction may exist for non ideal Schottky contacts, over which current flows. This is taken into account in the parallel resistance  $R_{\rm p}$ . Additionally, the capacitance C of the depletion region has to be taken into account, which is done by an additional charging current  $I_{\rm C}$ . A schematic circuit diagram of a real diode is shown in Figure 2.3.

The equation for a current flow through a non-ideal diode with thermionic emission as dominating current transport can be written as:

$$I = A_0 A^* T^2 \exp\left(-\frac{\phi_{B,eff}}{k_B T}\right) \left[ \exp\left(e\frac{V - IR_s}{\eta k_B T}\right) - 1 \right] + \frac{V - IR_s}{R_p} + I_C.$$

(2.18)

Ohmic Contacts Ohmic contacts are characterized by a linear dependence of the current on the applied voltage. In the ideal case, they have a negligible contact resistance, which means that the voltage drop over the contact is small in comparison to the voltage drop over the semiconductor. Ohmic contacts can be realized by either a small work function of the metal compared to the electron affinity of the semiconductor ( $\phi_{\rm m} < \mathcal{X}$ ) or by such a high net doping (small depletion region width) that the current flow in the forward and the reverse regime is dominated by the series resistance. For the case of a high net doping density as origin of the ohmic contact, a tunneling current dominates the current flow. A high defect density within the semiconductor may also lead to the formation of an ohmic contact.

### 2.3 Field-Effect Transistors

A field-effect transistor consists of three contacts: a source, drain and gate contact. The current flow can be controlled by a current as is done in bipolar transistors or by a voltage as is done in field-effect transistors (FETs). In this work, field-effect transistors are investigated and all descriptions will therefore concentrate on this device type. The source and drain contact of FETs are ohmic, whereas the gate contact is a rectifying contact. If a Schottky barrier contact is used as gate contact, the device is called [! ([!)3]MESFET. The field effect is achieved by a tuning of the depletion layer width by the voltage applied at the Schottky barrier contact. For pn-heterojunctions, it is called [! ([!)3]JFET. The heterojunction leads to the formation of a depletion region and and the working principle is similar as for MESFETs. If an insulator is brought between semiconductor and metal, the device is called [! ([!)3]MISFET. A variation of the MISFET is the [! ([!)3]MOSFET, where the insulator is realized by an oxide. The channel may be n- or p-type. FETs are unipolar devices, meaning they have only one majority carrier type. Most commonly used are MISFETs, which have the disadvantage that

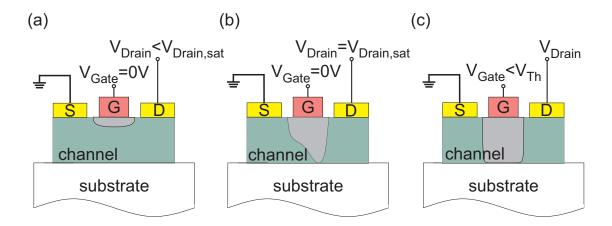

**Figure 2.4:** Schematic side view of a FET and the varying extension of the depletion region in the channel for different applied voltages at the gate and drain contact.

part of the voltage drops over the gate insulator and therefore higher voltages are required for tuning of the current flow.

In this work investigations on MESFETs are discussed and therefore all descriptions will concentrate on this FET type.

Working Principle In the following descriptions, a n-type channel of thickness d shall be assumed and the gate contact shall be realized by a Schottky barrier contact. Source and drain contact are ohmic. In Figure 2.4 (a), a schematic side view of a FET is depicted. If no voltage is applied between source and drain ( $V_{\text{Drain}} = 0 \text{ V}$ ) and no voltage is applied at the gate ( $V_{\text{Gate}} = 0$ ), the transistor is in equilibrium. The depletion region below the gate contact is due to the Schottky metal-semiconductor contact.

If the source-drain voltage is continuously increased, while the gate contact is kept at 0 V, the current over the channel increases linearly. The depletion region expands due to the positive voltage applied at the drain contact, which leads to a reverse bias of the Schottky barrier contact. The voltage drops over the length of the channel and the depletion region deforms. When the depletion region reaches the substrate (w = d) (compare Figure 2.4 (b)), the pinch-off is reached and the current through the channel saturates. The drain voltage at which the pinch-off occurs is called saturation voltage  $V_{\text{Drain,sat}}$ . If the drain voltage is further increased, the gate-drain diode is biased more negatively and at a certain point breakdown occurs, which leads to a strong increase of the source-drain current.

The source-drain current for a constant source-drain voltage can be tuned by the voltage applied at the gate. A reverse voltage at the gate leads to a decrease of the saturation current and a saturation at lower drain voltages. The reason for that is that by applying a negative bias at the gate contact, an extension of the depletion region can be achieved. For a certain applied gate voltage, called threshold voltage  $V_{\text{Th}}$ , the depletion region expands over the total channel thickness d (compare Figure 2.4 (c)).

The pinch-off voltage  $V_P$  is defined as the sum of the built-in and applied voltages at the

point, where the depletion region extents over the total channel thickness, as shown in Figure 2.4 (b).

**Static Calculations** If the gate length L is large compared to the channel thickness d, the depletion region width w can be calculated in dependence on the position x between source and drain using equation 2.6 and adding the voltage V(x), which is caused by the voltage applied at the drain contact

$$w(x) = \sqrt{\frac{2\epsilon_{\rm r}\epsilon_0}{eN_{\rm D}} \left(V_{\rm bi} - V_{\rm Gate} + V(x)\right)} \ . \tag{2.19}$$

This assumes the abrupt approximation, and a homogeneous doping. If w = d, it holds that  $V_{\text{bi}} - V_{\text{Gate}} + V_{\text{Drain}} = V_{\text{P}}$  and the pinch-off voltage can be written as

$$V_{\rm P} = \frac{eN_{\rm D}a^2}{2\epsilon_{\rm r}\epsilon_0} \ . \tag{2.20}$$

In contrast, the threshold voltage  $V_{\text{Th}}$  is defined as the voltage that is required to be applied at the gate to deplete the channel for  $V_{\text{Drain}} > 0 \text{ V}$ .

Assuming current conservation, the current flowing from source to drain can be calculated by integrating the channel conductance along the channel width [38,52]. The current is then calculated as

$$I_{\text{Drain}} = I_{\text{P}} \left[ \frac{3V_{\text{Drain}}}{V_{\text{P}}} - 2\left(\frac{V_{\text{bi}} - V_{\text{Gate}} + V_{\text{Drain}}}{V_{\text{P}}}\right)^{3/2} + 2\left(\frac{V_{\text{bi}} - V_{\text{Gate}}}{V_{\text{P}}}\right)^{3/2} \right] . \tag{2.21}$$

With the current  $I_{\rm P}$  is calculated as

$$I_{\rm P} = \frac{e^2 \mu N_{\rm D}^2 W a^3}{6L \epsilon_{\rm r} \epsilon_0} , \qquad (2.22)$$

where W is the gate width and  $\mu$  the electron mobility.  $I_{\rm P}$  depends only on the material and geometrical properties and is therefore constant. In the case that  $V_{\rm bi} - V_{\rm Gate} + V_{\rm Drain} \geq V_{\rm P}$ , the drain current is independent of the drain voltage and is written as

$$I_{\text{Drain}} = I_{\text{P}} \left[ 1 - \frac{3(V_{\text{bi}} - V_{\text{Gate}})}{V_{\text{P}}} + 2\left(\frac{V_{\text{bi}} - V_{\text{Gate}}}{V_{\text{P}}}\right)^{3/2} \right]$$

(2.23)

If this equation is expanded around  $V_{\text{Gate}} = V_{\text{Th}}$ , equation 2.23 simplifies to

$$I_{\text{Drain}} \approx \frac{3I_{\text{P}}}{4V_{\text{P}}^2} \left( V_{\text{Gate}} - V_{\text{Th}} \right)^2 . \tag{2.24}$$

The transistor may be either normally-on or normally-off. Normally-on transistors have a conductive channel and normally-off transistors have a non-conductive channel at 0 V gate voltage. A measure for normally-on or -off is the threshold voltage, which is  $V_{\rm Th} < 0 \, {\rm V}$  or  $V_{\rm Th} > 0 \, {\rm V}$ , respectively.

Characteristic Parameters The FETs in this work were characterized by three different current-voltage measurements: measuring (i) the gate-source and gate-drain diode characteristics, (ii) the transfer characteristic and (iii) the output characteristic. For (i) a variable voltage was applied at the gate contact and the resulting current flow was measured at the source and accordingly the drain contact. This measurement is important to verify the rectifying behavior of the gate contact, which is required to obtain a voltage tuning. The second measured characteristic is the transfer characteristic (ii), which is measured by connecting the source contact to ground and applying a constant positive voltage at the drain contact (typically 2 V in this work). The voltage at the gate contact is varied in a predefined voltage range and the resulting drain current and gate leakage current are measured. The drain current should, if a field-effect exists, be tunable by the voltage applied at the gate contact. The gate voltage is chosen in such a way that for small or negative voltages, the channel is depleted and no current flow is measured over the channel and for high positive voltages, the depletion region is completely dissipated and the saturation current flows. The transfer characteristics are used for the determination of the characteristic parameters of the transistor. A third measurement is the output characteristic (iii), in which the drain voltage is varied between 0 V and higher positive voltages for a constant gate voltage. This measurement is repeated for different gate voltages.

From the transfer characteristics different parameters of the transistor can be calculated. One parameter is the drain current on-to-off ratio, which is calculated as the maximum drain current divided by the minimum drain current during the transfer measurement

on-to-off ratio =

$$\frac{\max(I_{\text{Drain}})}{\min(I_{\text{Drain}})}$$

. (2.25)

The sub-threshold swing S gives the minimum voltage that is required to switch the drain current by one decade

$$S = \min\left(\left[\frac{\mathrm{d}\log_{10}\left(I_{\mathrm{Drain}}\right)}{\mathrm{d}V_{\mathrm{Gate}}}\right]^{-1}\right) . \tag{2.26}$$

The theoretical minimum of the sub-threshold swing can be calculated by  $\ln(10)\frac{k_{\rm B}T}{e}$ , which is  $\approx 60 \,\mathrm{mV}\,\mathrm{dec}^{-1}$  at room temperature.

Using equation 2.24, the threshold voltage can be determined by a linear fit on the plot of  $\sqrt{I_{\text{Drain}}}$  in dependence on the gate voltage. Another important parameter is the maximal transconductance  $g_{\text{max}}$ , which is defined as the maximum of the derivative of the drain current with respect to the gate voltage:

$$g_{\text{max}} = \max\left(\frac{\mathrm{d}I_{\text{Drain}}}{\mathrm{d}V_{\text{Gate}}}\right) = \frac{eN_{\text{t}}d\mu_{\text{Ch}}W}{L}$$

(2.27)

It has to be considered that non-idealities often lead to smaller values of  $g_{\text{max}}$  obtained from the characteristics [53] as compared to the values obtained by a calculation from the geometric and electrical parameters of the device. Using equation 2.27 and the net doping density  $N_{\text{t}}$ ,

the channel (field-effect) mobility  $\mu_{\rm Ch}$  can be estimated for the investigated devices.

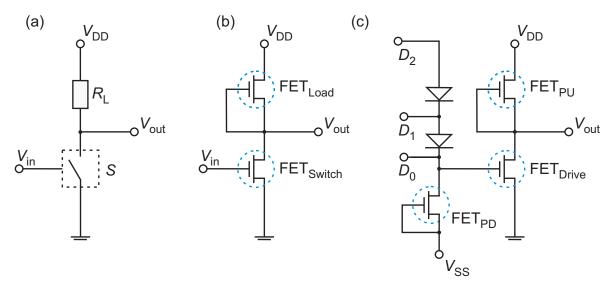

#### 2.4 Inverter

An inverter is a simple logic element, which can switch between two states: e.g. on and off or 1 and 0. It can, in its simplest form be realized by a series connection of a switch S and a resistance  $R_{\rm L}$  as shown in Figure 2.5 (a). If the switch is open, the operating voltage  $V_{\rm DD}$  drops over the switch and  $V_{\rm out} = V_{\rm DD}$ . If the switch is closed, the ground potential is applied at the output and  $V_{\rm out} = 0$  V is measured. The switch is typically controlled by an input voltage  $V_{\rm in}$ .

In this work two identical FETs are used instead of a switch and a resistance. In the following, two different inverter designs are shortly explained: the simple inverter design and the [! ([!)3]SDFL inverter design.

A more detailed discussion on inverters can be found in [54].

Simple Inverter The circuit diagram of a simple inverter is shown in Figure 2.5 (b). An input voltage is applied to the gate contact of the switch transistor FET<sub>switch</sub>, whose source contact is connected to ground. The drain contact of the switch transistor is short-circuited with the source and gate contact of the load transistor FET<sub>load</sub>. The output voltage is measured at this (combined) contact. Due to the shortening of the gate and source contact of the load transistor, this transistor always works at the same point. The operating voltage is supplied at the drain contact of the load transistor.

For a negative input voltage, the channel of the switch transistor is depleted and has a large resistance compared to the load transistor. The output voltage is therefore approximately the operating voltage  $V_{\text{out}} \approx V_{\text{DD}}$ .

In contrast, a positive input voltage at the switch transistor leads to a reduction and subsequent vanishing of the depletion region in this device. The switch transistor therefore has a lower resistance than the load transistor in this case, and the output voltage becomes, as for the closed switch, nearly zero  $V_{\rm out} \approx 0$ .

The inverters investigated here switch between 0 V as low level and  $V_{\text{DD}}$  as high level, which is in contrast to a full inverter, where an exchange of two complementary voltage levels is achieved.

Schottky Diode FET Logic Inverter The basic working principle of this inverter type is the same as for the simple inverter. The difference lies in a pull down transistor FET<sub>PD</sub> and a variable number of diodes (zero to two in this design), which are connected in front of the gate contact of the switch transistor of the simple inverter as shown in Figure 2.5 (c). The load transistor is now called pull-up transistor FET<sub>PU</sub> and the switch transistor is called drive transistor FET<sub>Drive</sub>.

Figure 2.5: Equivalent circuit of an inverter consisting of a switch and a resistance (a) and of two transistors (b). In (c) the equivalent circuit of an inverter in [! ([!)3]SDFL design is shown.

The input signal of the inverter is strongly influenced by the pull-down transistor, at which a negative constant voltage is applied. This voltage, called supply voltage  $V_{\rm SS}$  is chosen in such a way that the pull-down transistor works in saturation. Typically a voltage of  $V_{\rm SS} = -2\,\mathrm{V}$  is chosen. The gate length of the pull-down transistor is chosen in such a way, that it is 1/2 the gate length of the drive and pull-up transistor to ensure a smaller current flow and a smaller voltage drop over this transistor.

In the design used in this work, it is possible to chose between zero diodes  $D_0$ , one diode  $D_1$  and two diodes  $D_2$  as input port. In the case of one and two diodes, the pull down transistor works as current supply for the diodes. The combination of pull-down transistor and diodes is called level-shifter.

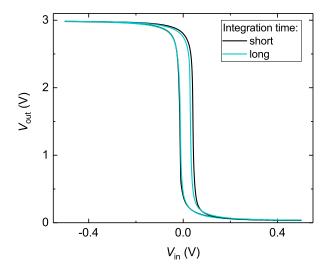

The level-shifter leads to a voltage shift  $V_{\rm shift}$  of the gate voltage of the switch transistor  $V'_{\rm in}$  by the voltage drop across the N diodes, which is  $V_{\rm x}$  per diode. This can be formulated as  $V'_{\rm in} = V_{\rm in} - NV_{\rm x}$ . As a result, the voltage transfer characteristic of the [! ([!)3]SDFL inverter is shifted to positive input voltages for one and two diodes.

If this design is adopted in such a way that the level-shifter is connected behind the simple inverter, the design is called [! ([!)3]FL. In this case, a y-axis voltage shift of the output voltage is achieved. This is used to ensure positive and negative input voltages of a subsequent inverter. A detailed description on this design, which was adopted from the GaAs-MESFET technology is given in reference [54,55].

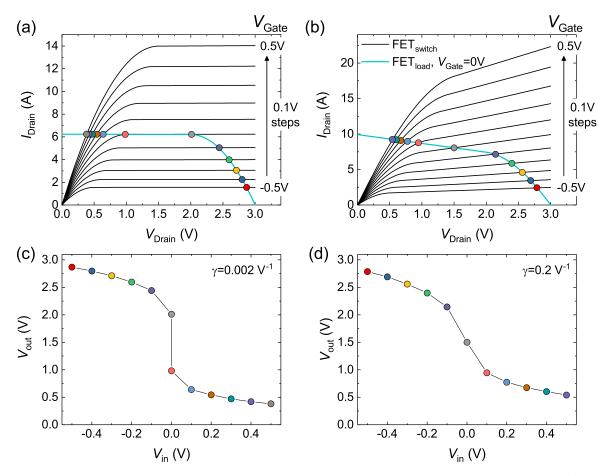

Voltage Transfer Characteristics of an Inverter The voltage transfer characteristic of an inverter can be directly related to the output characteristic of the load and switch transistors. In this thesis, both FETs are identical and therefore their output characteristics

**Figure 2.6:** Simulation of output characteristics of a MESFET for (a)  $\gamma = 0.002 \,\mathrm{V}^{-1}$  and (b)  $\gamma = 0.2 \,\mathrm{V}^{-1}$  and the resulting voltage transfer characteristics, which are shown in (c) and (d).

are also assumed to be identical for simplicity<sup>3</sup>.

To construct the voltage transfer characteristic of a simple inverter, the output characteristics of the switch transistor are plotted. The output characteristic of the load transistor at  $V_{\rm Gate} = 0\,\rm V$  is mirrored on the x-axis in such a way, that it starts at  $V_{\rm DD}$  (see Figure 2.6 (a,b)). Following Kirchhoff's law, the drain voltages and the operating voltage are connected by

$$V_{\text{out}} = V_{\text{Drain-Source,switch}} = V_{\text{DD}} - V_{\text{Drain-Source,load}}$$

(2.28)

The intersections of both output characteristics, where both FETs carry the same current, give the working points of the inverter, marked by the dots in Figure 2.6 (a-d):

$$I_{\text{Drain,switch}}(V_{\text{in}}, V_{\text{Drain-Source,switch}}) = I_{\text{Drain,load}}(0, V_{\text{Drain-Source,load}}),$$

(2.29)

if gate currents are neglected. As both transistors have the same resistance at  $V_{\text{Gate,switch}} = V_{\text{Gate,load}} = 0 \,\text{V}$ , the switching point of the inverter is at  $V_{\text{in}} = 0 \,\text{V}$  in the ideal case.

<sup>&</sup>lt;sup>3</sup>However, a certain variance is always present in real devices.

**Table 2.1:** Fixed simulation parameters used during the simulation with the *Simulink* tool of *MATLAB*.

| Parameter | Σ                           | $I_{ m sat}$        | T                    | $R_{ m ohmic}$     | $C_{\rm j}$ |

|-----------|-----------------------------|---------------------|----------------------|--------------------|-------------|

|           | $\mathrm{S}\mathrm{V}^{-1}$ | A                   | $^{\circ}\mathrm{C}$ | Ω                  | nF          |

|           | 6.2                         | $5 \times 10^{-11}$ | 25                   | $1 \times 10^{-5}$ | 0.3         |

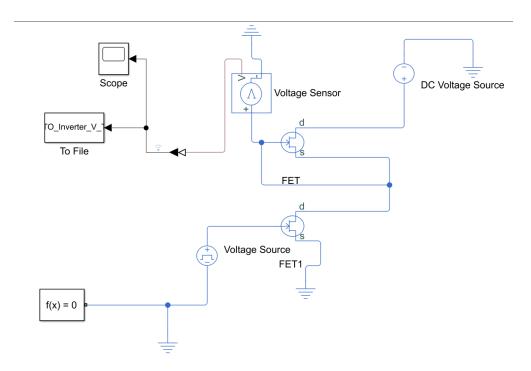

The output characteristics, and all further data in this section, were simulated using the Simulink tool by MATLAB in the layout of a simple inverter. Two JFETs with tunable transconductance  $\Sigma$ , saturation current  $I_{\text{sat}}$ , threshold voltage  $V_{\text{Th}}$ , saturation factor of the output characteristics  $\gamma$ , temperature T, ohmic contact resistance  $R_{\text{ohmic}}$  and junction capacitance  $C_{\text{j}}$  were used. All parameters that were kept fixed during the simulations are listed in Table 2.1. The equivalent circuit used for the simulation is depicted Figure A1 in the Appendix. For the modeling of inverters, it is does not matter whether a JFET or MESFET is used as model block, as both devices are assumed to be unipolar and all characteristic properties of the FET could be adjusted within the program.

In the ideal case, the output characteristics exhibit a saturation of the drain current for  $V_{\text{Drain}} > V_{\text{Drain,sat}}$ . This case is shown in Figure 2.6 (a). The resulting voltage transfer characteristic of the inverter is infinitely steep in the transition regime and therefore ideal as shown in Figure 2.6 (c). If the drain current does not saturate, but rather exhibits a finite slope, the resulting voltage transfer characteristics become non-ideal. This effect is described by the parameter  $\gamma$  in the simulations, which can be obtained from a linear fit on the finite slope of the output characteristics for  $V_{\text{Drain}} > V_{\text{Drain,sat}}$ . The equation for the linear fit is

$$I_{\text{Drain.sat}} = a + bV_{\text{Drain}}$$

, (2.30)

where a is the intercept with the y-axis and b the slope.  $I_{\text{Drain,sat}}$  has a finite slope in this case. The parameter  $\gamma$  is defined as one divided by the intercept with the x-axis and therefore  $\gamma = |-b/a| \, V^{-1}$ . In Figure 2.6 (b), the output characteristics are depicted for  $\gamma = 0.2 \, V^{-1}$ . The finite slope of the saturation current is very well visible. A voltage transfer characteristic for the case of a finite slope of the saturation current is shown in Figure 2.6 (d). If one compares the voltage transfer characteristics for  $\gamma = 0.002 \, V^{-1}$  and  $\gamma = 0.2 \, V^{-1}$ , the less steep increase of the voltage transfer characteristics for a larger  $\gamma$  is immediately visible.

In literature the value  $\gamma$  is typically replaced by the drain output resistance  $r_0$  [54]

$$r_0 = \frac{1}{\gamma I_{\text{Drain}}} \ . \tag{2.31}$$

The additional drain current is interpreted as current flowing through a drain output resistor  $r_0$ .

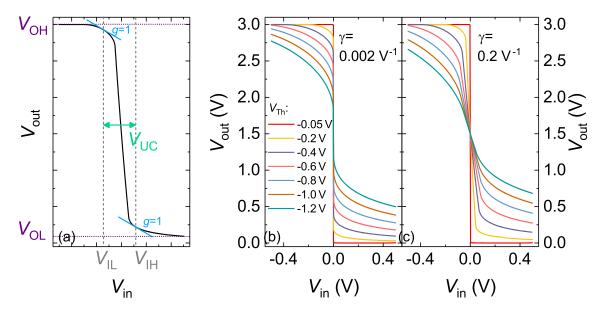

The influence of the transconductance parameter and the saturation current is visible in the logic off regime only and is not shown in this work. A non-ideality in these parameter leads to

Figure 2.7: Characteristic parameters of an inverter (a) and simulation of voltage transfer characteristics for different threshold voltages and a factor  $\gamma$  of 0.002 V<sup>-1</sup> (b) and 0.2 V<sup>-1</sup> (c).

gate lag currents and therefore an increase of the output voltage for positive input voltages. If the transconductance is smaller than a critical value, which is dependent on the geometry and the threshold voltage, it is no longer possible to achieve the operating voltage for negative input voltages.

Inverters are typically described by a number of parameters. The gain g, which is calculated as

$$g = -\frac{\partial V_{\text{out}}}{\partial V_{\text{in}}} \tag{2.32}$$

is used to determine the steepest point of the voltage transfer characteristic, i.e. the point with maximum gain. This point is called peak gain magnitude pgm. Additionally, the uncertainty level is determined as the difference in voltage for the two points where the gain is 1. The input and output voltage for which the point g=1 is reached are called input high voltage  $V_{\rm IH}$  and input low voltage  $V_{\rm IL}$  for the input voltage and output high voltage  $V_{\rm OH}$  and output low voltage  $V_{\rm OL}$  for the output voltage as depicted in Figure 2.7 (a). The uncertainty level  $V_{\rm UC}$  is calculated as the difference of input high and low voltage  $V_{\rm UC}=V_{\rm IH}-V_{\rm IL}$ . In the optimal case, the inverter switches between  $V_{\rm DD}$  and 0 V. In this case, the logic swing is equal to the operating voltage. In the non-ideal case, the logic swing is smaller and calculated as  $V_{\rm OH}-V_{\rm OL}$ .

In Figure 2.7 (b,c), the voltage transfer characteristic for two different values of  $\gamma$  and a variation of the threshold voltage are simulated. A requirement of the simple inverter set-up is that the threshold voltage has to be close to zero or below for the inverters to work well. This can be seen very well in the simulated data. The more negative the threshold voltage becomes, the smaller the logic swing becomes. Additionally, it is visible that for the non-

ideal case, where  $\gamma = 0.2 \, \mathrm{V}^{-1}$ , the slope of the voltage transfer characteristics increases with increasing threshold voltage.

For positive input voltages very close to 0 V, a voltage inversion is observed for the device. An increase of the threshold voltage to higher positive voltages leads to a lowering of the output high voltage and therefore of the logic swing. This is due to a high resistance of switch and load transistor in the regime  $V_{\rm in} < 0 \text{ V}$ , which leads to a voltage drop over the switch transistor as well as over the load transistor. Additionally, the switching point of the inverter shifts to higher input voltages due to the higher threshold voltage of the transistors.

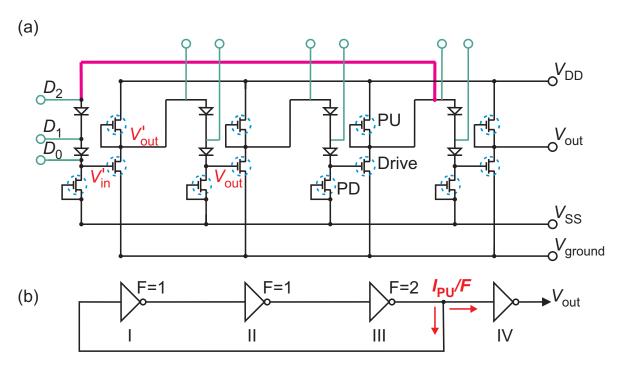

### 2.5 Inverter Chain and Ring Oscillator

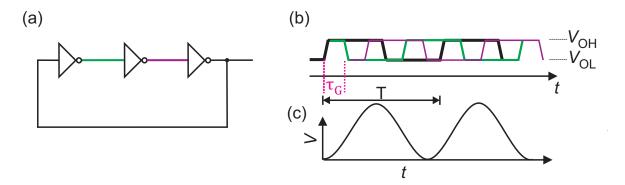

A further step towards integrated circuits is the series connection of inverters, which is called inverter chain or ring oscillator, depending if a shortening of the output of the last inverter with the input of the first inverter of the circuit is performed or not. An exemplary use of ring oscillators is as test structures for the propagation delay in logic elements [56,57].

Inverter Chain In Figure 2.8 (a) an inverter chain is drawn. The pink line, which represents the connection of the circuit to a ring oscillator, has to be erased for the inverter chain. The green lines denote the possible measurement contacts. If the signal is measured between  $D_2$  and  $V'_{\text{out}}$ , it is equal to the [! ([!)3]SDFL design and a shift of the signal on the  $V_{\text{in}}$ -axis is achieved, whereas if the signal is measured between  $V'_{\text{in}}$  and  $V_{\text{out}}$  the layout corresponds to a FET logic inverter and the signal is shifted on the  $V_{\text{out}}$ -axis. Therefore it is possible to shift the output signal of an inverter in such a way that negative output voltages are achieved and the next inverter can be driven.

Each inverter leads to an inversion of the signal of 180°. Thus the first inverter leads to the expected signal of high output for negative input voltages and low output for positive input voltages. If the signal is read-out after the second inverter, a low output signal is measured for negative input voltages and a high output level for positive input voltages, and so on. Therefore, an odd number of inverters leads to the same signal orientation as obtained for one inverter.

Ring Oscillator A ring oscillator is a cascading of an odd number of inverters, which are shortened in such a way, that the signal of the last inverters is fed into the first inverter. An additional inverter is used to read out the signal. A more detailed explanation on ring oscillators can be found in [58, 59]. The descriptions and derivations given in this chapter follow the argumentation by Klüpfel et al. [58].

Three conditions have to be fulfilled to enable the detection of an oscillation:  $V_{\rm SS}$  has to be chosen in such a way that the pull down transistor works in saturation and acts as current supply,  $V_{\rm DD}$  has to exceed the voltage shift of the level shifter and last but not least, a constant ground potential has to be applied to the circuit.

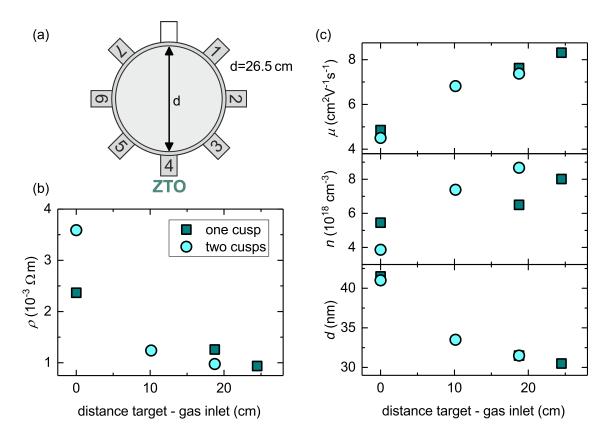

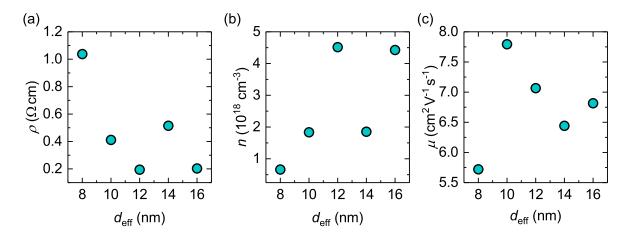

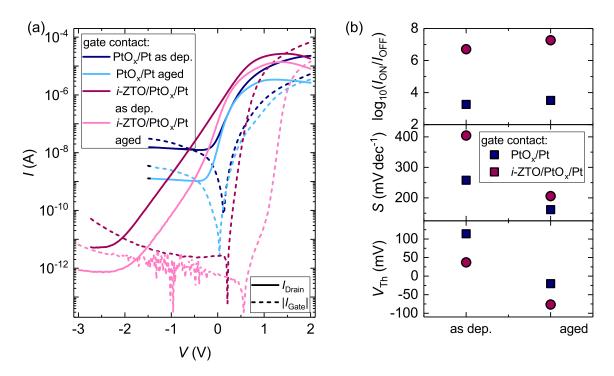

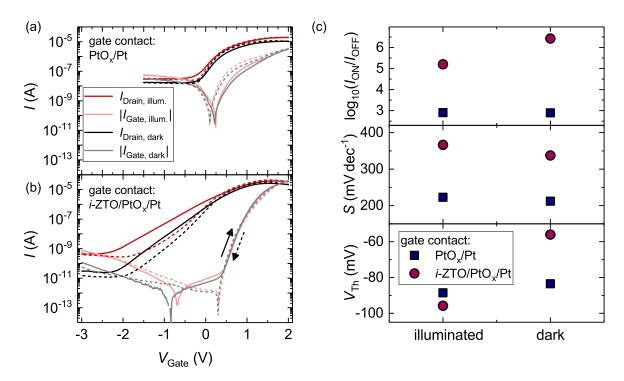

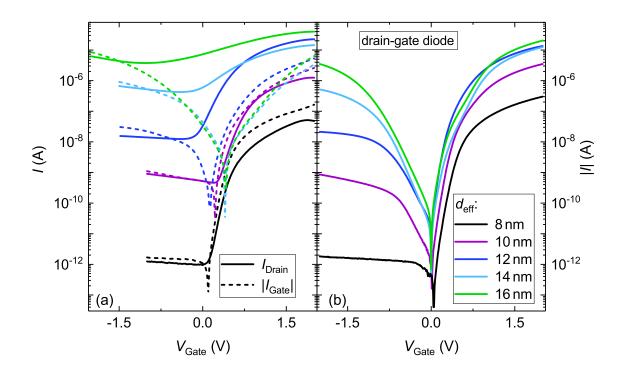

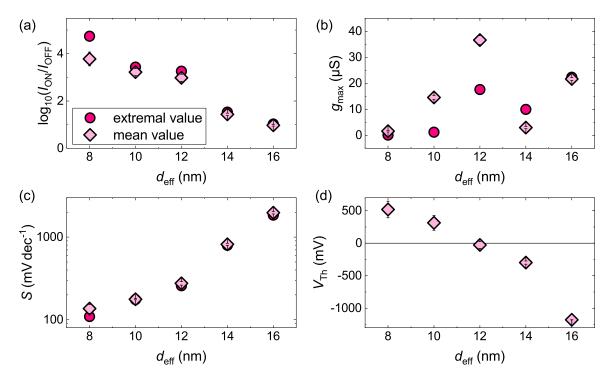

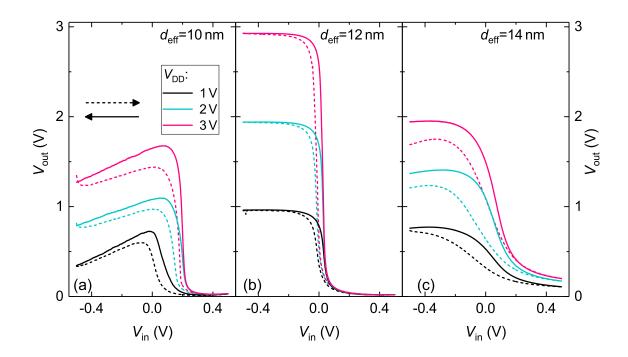

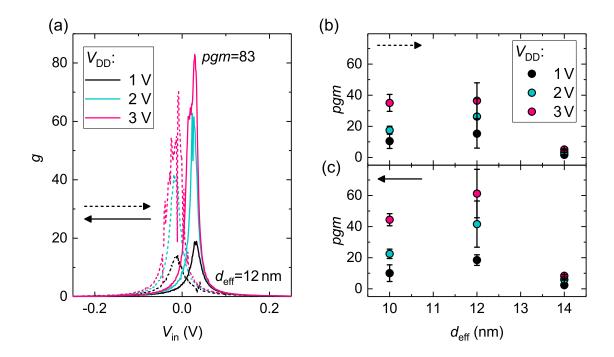

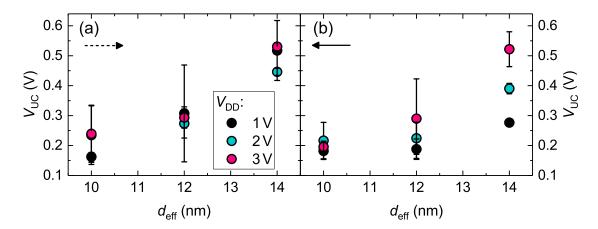

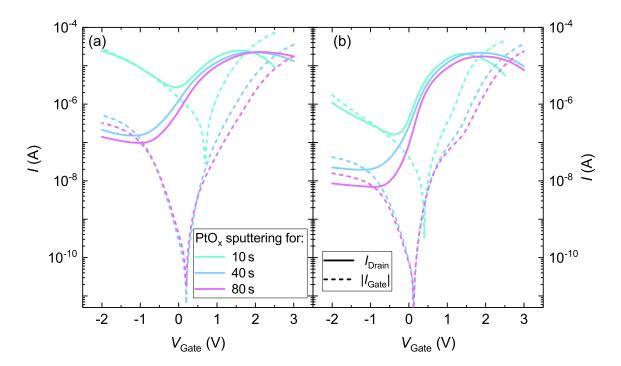

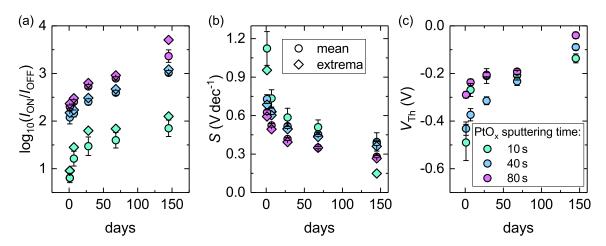

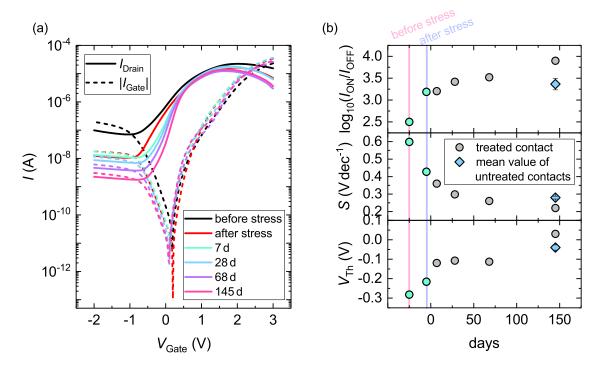

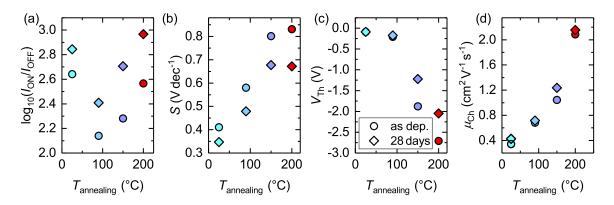

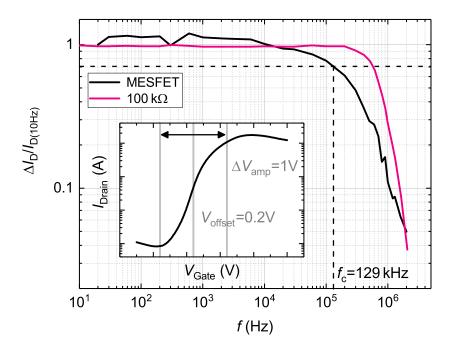

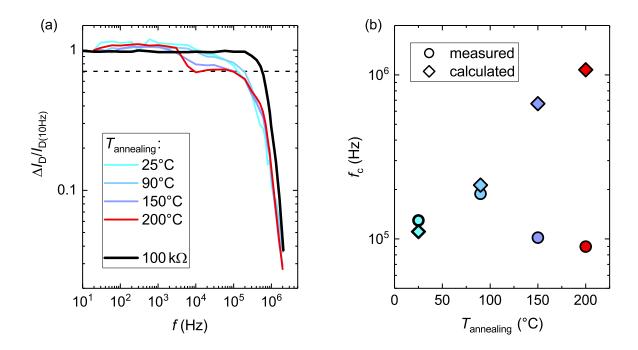

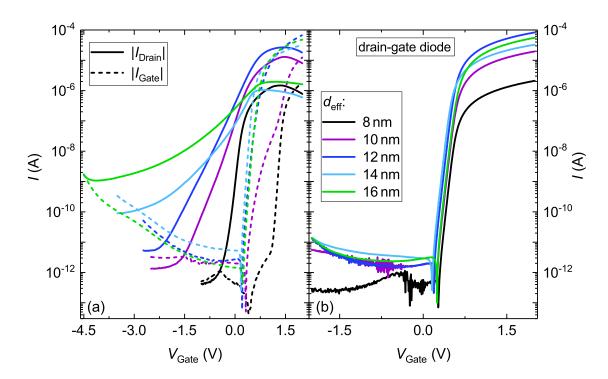

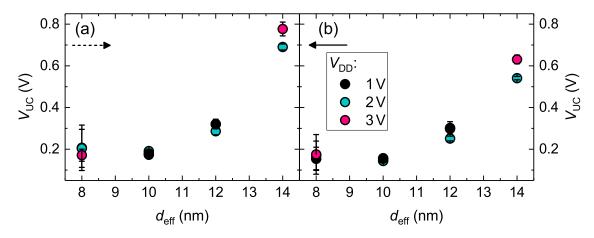

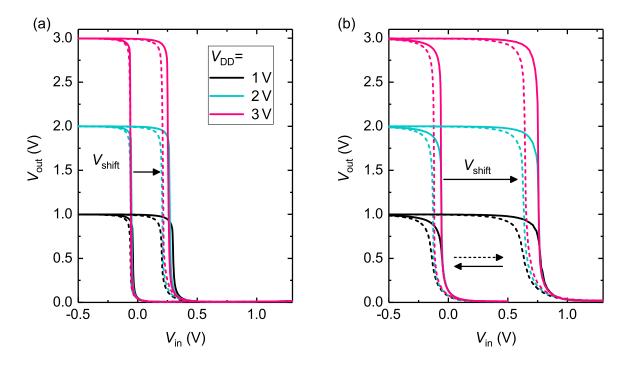

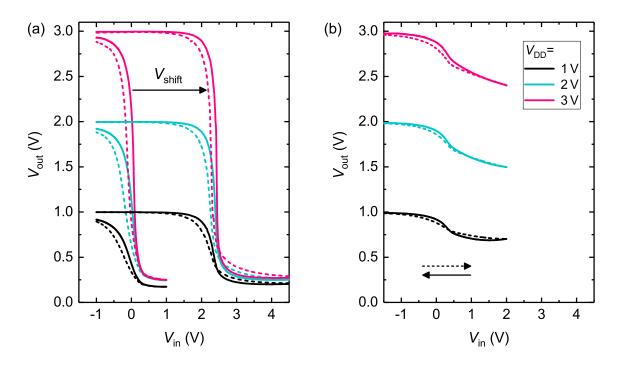

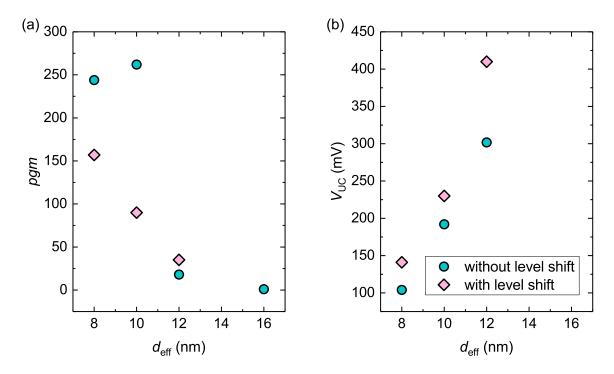

**Figure 2.8:** Schematic drawing of an (a) inverter chain (without the pink line) and a ring oscillator (with pink connection) and (b) schema of a ring oscillator with three stages and an out-coupling inverter stage. The pull-up FET is denoted by PU, the pull-down FET by PD and the driving FET by Drive.