Journal of Scientific & Industrial Research Vol. 79, May 2020, pp. 418-423

# Design of a Low Offset, Low Noise Amplifier for Neural Recording Applications

N M Laskar, S Nath, K Guha\*, P K Paul and K L Baishnab

Department of ECE, National Institute of Technology Silchar-788 010, India

Received 12 March 2019; revised 7 May 2019; accepted 20 January 2020

The design of a capacitive feedback based neural recording amplifier is presented. The prime design requirements in case of neural amplifiers includes low noise, high gain, high CMRR, low power, low area and low offset voltage. However, there is an inherent trade-off between noise-power and area-offset in the design process which needs to be addressed. A Recycling Folded Cascode based Operational Transconductance Amplifier (RFC-OTA) topology is employed to realize the amplifier as it offers better gain and offset voltage as compared to other topologies. The sizing of the transistors has been done with the primary objective of low random offset voltage while meeting other design criteria within the specified range subject to all inherent trade-offs. Simulations have been done in Cadence Virtuoso using SCL 180 nm technology and comparative analysis with other reported designs reveals that the proposed RFC-OTA based neural amplifier design achieves a low random offset voltage of 1.4 mV with a low input noise of 1.38  $\mu$ V as compared to most of the reported design.

Keywords: Neural Amplifier, Recycling Folded Cascode, Low Random Offset Voltage, High Gain, Area-Offset trade-off, Capacitive Feedback

### Introduction

Neural Amplifiers are high gain bio-potential amplifiers used for amplifying weak neural signals.<sup>1,2</sup> Being battery-operated and implantable, low area and low power are major design requirements.<sup>3</sup> Furthermore, to minimize noise due to both electronics and external sources, a very low input noise and high CMRR is desirable.<sup>1–5</sup> However, an inherent trade-off exists between low noise and low power.<sup>4</sup> Apart from these, the need of low offset voltage is also desired as it impacts the accuracy and precision.<sup>6</sup> Random offset voltage arises due to random mismatch in device parameters<sup>7</sup> and can be improved at the cost of higher area.

Numerous works have been reported in design of neural recording amplifiers. However, most of the reported works<sup>2-4,8-12</sup> fail to meet the low noise and low power criteria along with high gain because of the various trade-off between design specifications. They also do not take into account the need of a low offset voltage. The proposed work aims at designing a neural recording amplifier to overcome such limitations by determining optimal sizing of MOS transistors for minimum random offset voltage subject to all design specifications as constraints using swarm intelligence based meta-heuristic algorithms<sup>13</sup> due to their easy

search mechanism and ability to find global optimum, which is a major contribution of the proposed work. To realize the amplifier, a RFC OTA is employed as it offers better gain, offset voltage, input noise<sup>14</sup> in comparison to a basic folded cascode. Simulations, investigation of temperature variation and comparative analysis with state of art design reveals significant improvement in input noise and random offset voltage with a value of 1.38  $\mu$ V and 1.452 mV respectively.

### Proposed Neural Amplifier design

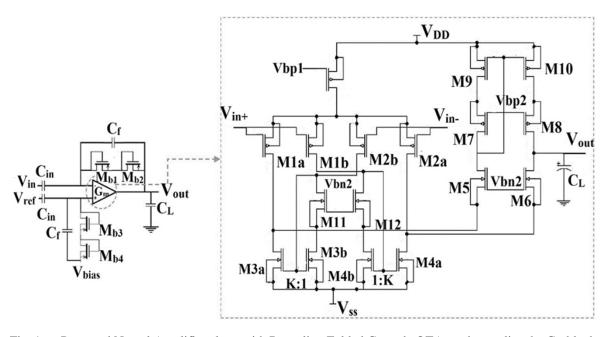

The proposed design consists of a capacitive feedback neural recording amplifier comprising of an input dc blocking capacitor,  $C_{in}$  and feedback capacitor,  $C_{f}$  which mainly control the mid-band gain as defined by (- $C_{in}/C_{f}$ ) as shown in Fig. 1. There are two diode connected pseudo resistors,  $M_{b1}$  and  $M_{b2}$  in the feedback network which together with the capacitors, defines the transfer function of the system, H(s) as given by Eq. (1).

$$H(s) = \frac{v_{out}(s)}{v_{in}(s)} = -\frac{c_{in}}{c_f} \cdot \frac{sR_P c_L}{1+sR_P c_L} \qquad \dots (1)$$

Where  $C_L$  is the load capacitance and  $R_p$  realizes the contribution of  $C_L$   $M_{b1}$  and  $M_{b2}$ .

A capacitive feedback amplifier is preferred over an open loop one as it offers lower input noise and can also be easily reproduced without large tuning.<sup>11</sup> The OTA stage ( $G_m$ ) which controls the gain is realized using a RFC OTA as shown in Fig. 1. It is an improved

<sup>\*</sup>Author for Correspondence

E-mail: koushikguha2009@gmail.com

Fig. 1 — Proposed Neural Amplifier along with Recycling Folded Cascode OTA used to realize the G<sub>m</sub> block

variant of conventional folded cascode OTA and offers large improvement in gain, input noise, offset voltage etc. under same power and area budget.<sup>14</sup> It is achieved by reusing the idle currents and devices. As seen from Fig. 1, the input differential pair M1 and M2 is split in the ratio of half each in M1a, M1b, M2a and M2b, while the current sinks M3 and M4 are split in the ratio of K:1 where K is the recycling factor. M7 to M10 represents the cascode current mirror load. Furthermore, to improve the systematic offset voltage, two new transistors M11 and M12 are incorporated in the design which maintains the drain potentials for better matching.<sup>14</sup> The modelling of the proposed amplifier is performed and the small signal gain  $(A_v)$ and input referred thermal noise spectral density  $(S_n(f))$ is given by Eq. (2) and Eq. (3) respectively.

$$A_{v} = g_{m1a}(1+K)g_{m6}r_{06}(r_{02a}||r_{04a})||g_{m6}r_{08}r_{010}...(2)$$

$$S_n(f) = \frac{16KT}{3g_{m1a}} \left[ \frac{(1+K^2)}{(1+K)} + \frac{g_{m3a}}{g_{m1a}} + \frac{g_{m9}}{(1+K)g_{m1a}} \right] \qquad \dots (3)$$

Where  $g_{mx}$  is the transconductance of transistor Mx and  $r_{ox}$  is the output resistance of transistor Mx.

The mismatch analysis is further performed and the contribution of the various drain current mismatches of the transistors at the output is divided by the input transconductance to achieve the random offset voltage ( $V_{OS,RFC}$ ) of the proposed RFC-OTA as shown in Eq. (4).

$$V_{OS, RFC} = 2 \frac{A_{VTH,P}^2}{W_{1a}L_{1a}(1+K)} \left[ \frac{(1+K)^2}{1+K} + \frac{3\mu_N A_{VTH,N}^2}{\mu_P A_{VTH,P}^2} \left( \frac{L_{1a}}{L_{3a}} \right)^2 + \frac{2}{(1+K)} \left( \frac{L_{1a}}{L_9} \right)^2 \right] \qquad \dots (4)$$

Where  $A_{VTH,P}$  and  $A_{VTH,N}$  are constants for area matching for PMOS and NMOS respectively.

The sizing of the MOS transistors and the values of other design parameters have been determined by formulating the random offset voltage shown in Eq. (4) as an objective function and using the modelling of other design parameters such as gain and input noise defined by Eq. (2) and Eq. (3) respectively, other specifications such as CMRR, power dissipation, slew rate and also area defined by  $\sum_{k=0}^{12} W_k L_k$  as design constraints and solving the objective function for minimum random offset voltage using swarm intelligence based algorithms<sup>13</sup> due to the reasons mentioned previously. The use of such meta-heuristics has also become prominent due to existence of tradeoffs among the various design specifications which makes the manual sizing of the transistors a computationally inefficient approach. One such example of trade-off would be the opposite dependency of  $S_n(f)$  and  $V_{OS}$  on  $L_9$  as seen from Eq. (3) and Eq. (4) respectively. Thus, to minimize both  $S_n(f)$  and  $V_{OS}$ , an optimum  $L_9$  has to be determined, which becomes difficult to be addressed manually without compromising on one of them and thus to achieve

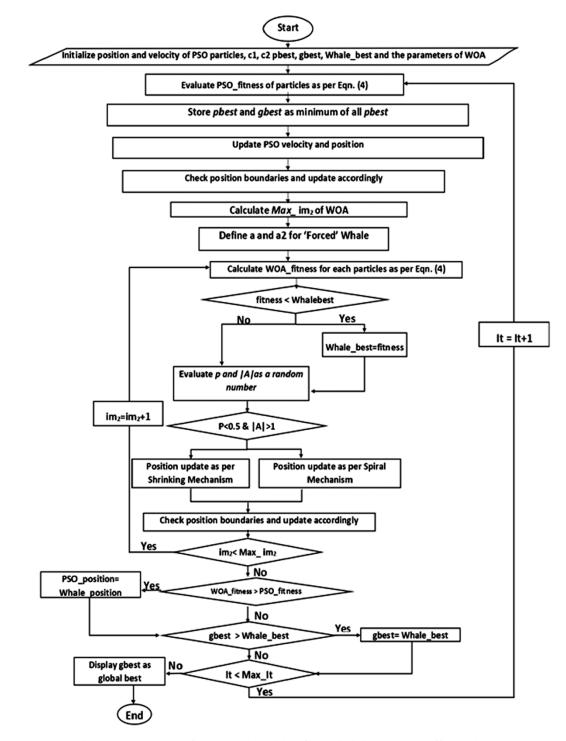

optimum values of both these design specifications the use of meta-heuristics comes into play. The algorithm used to optimize the random offset voltage here is an improved hybrid swarm intelligence-based algorithm namely the Hybrid Whale Particle Swarm Optimization (HWPSO).<sup>13</sup> It is basically a hybrid variant of two popular swarm intelligence algorithms namely the Whale Optimization Algorithm (WOA) and the Particle Swarm Optimization (PSO). The flowchart of the approach is shown in Fig. 2. The design parameters obtained are shown in Table 1. For the input and feedback capacitors MIM capacitors are

Fig. 2 — Flowchart of HWPSO algorithm for optimizing random offset voltage

used as they have higher density and lower parasitic effects.<sup>11</sup> The mid-band gain of the neural amplifier is mainly controlled using the  $C_{in}$  and  $C_{f}$  ratio and has to meet the desired specification also as it is lower than the dc gain of the OTA defined by Eq. (2). Thus, to maximize the mid-band gain, the  $C_{in}$  has to be higher while  $C_{f}$  has to be lower. However, the size of the capacitors also impacts the area of the amplifier which also needs to be lower. Additionally, there is also a limit imposed on the value of the capacitors as imposed by the technology bound constraints. So, keeping in view all these trade-offs, the values of the MIM capacitors have been optimized as shown in Table 1.

|                                | parameters of proposed neural |

|--------------------------------|-------------------------------|

| ampin                          | fier used                     |

| Design Parameter               | Values                        |

| $I_{bias}(\mu A)$              | 2                             |

| $W_{1a}/L_1$                   | 30/30                         |

| $W_{1b}/L_1$                   | 30/30                         |

| $W_{2b}/L_2$                   | 30/30                         |

| $W_{2b}/L_2$                   | 30/30                         |

| $W_{3a}/L_3$                   | 21/21                         |

| $W_{3b}/L_3$                   | 7/21                          |

| $W_{4a}/L_4$                   | 21/21                         |

| $W_{4b}/L_4$                   | 7/21                          |

| W <sub>5</sub> /L <sub>5</sub> | 28/28                         |

| W6/L <sub>6</sub>              | 28/28                         |

| $W_{7}/L_{7}$                  | 50/40.49                      |

| $W_{8}/L_{8}$                  | 50/40.49                      |

| $W_{9}/L_{9}$                  | 50/40.49                      |

| $W_{10}/L_{10}$                | 50/40.49                      |

| $W_{11}/L_{11}$                | 14/14                         |

| $W_{12}/L_{12}$                | 14/14                         |

| $W_0/L_0$                      | 40/40                         |

| C <sub>in</sub> (pF)           | 12                            |

| $C_{f}$ (fF)                   | 100                           |

|                                |                               |

# **Simulation Results and Analysis**

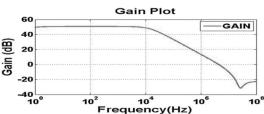

The performance of the proposed design is validated by designing a capacitive feedback neural amplifier in Cadence Virtuoso using SCL 180 nm technology. Simulations have been performed and comparison with other reported designs are done. The results are illustrated in Table 2 and Fig. 3 and Fig. 4. The AC analysis for gain plot of the proposed RFC-OTA based neural amplifier is shown in Fig. 3 from where it is seen that the mid-band gain of the proposed neural amplifier is found to be 50.5 dB with an input capacitor of 12 pF and feedback capacitor of 100 fF which rolls of at -20 dB/decade. The OTA open loop gain is equal to approximately 70 dB contributed mainly by the M1a, M6 and M8 in accordance to Eq. (2). The use of feedback capacitors decreases the open loop gain to 50 dB as per ratio governed by Eq. (1). The input referred noise of the

Fig. 3 — AC analysis plot for mid-band gain of proposed neural amplifier

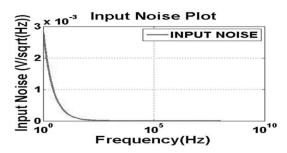

Fig. 4 — Noise analysis plot for input noise of proposed neural amplifier

| Work                                      | able 2 — Comp<br>Technology<br>(μm) | Gain<br>(dB) | CMRR<br>(dB) | en proposed design<br>Power<br>dissipation (μW) | Input<br>Noise (µV) | rted works<br>Bandwidth<br>(KHz) | Random Offset<br>Voltage (mV) |

|-------------------------------------------|-------------------------------------|--------------|--------------|-------------------------------------------------|---------------------|----------------------------------|-------------------------------|

| Wattanipanitch <i>et al.</i> <sup>3</sup> | 0.5                                 | 40.85        | 66           | *NR                                             | 3.06                | 5.3                              | *NR                           |

| Chaturvedi <i>et al.</i> <sup>4</sup>     | 0.13                                | 37           | *NR          | 1.5                                             | 5.5                 | 7                                | *NR                           |

| Amaya <i>et al.</i> <sup>2</sup>          | 0.13                                | 46           | 85           | 1.92                                            | 3.8                 | 7.3                              | *NR                           |

| Feng et al. <sup>8</sup>                  | 0.5                                 | 58.4         | 154.4        | *NR                                             | 21.06               | 10.2                             | *NR                           |

| Ng <i>et al.</i> <sup>9</sup>             | 0.065                               | 52.1         | >80          | 3.28                                            | 4.13                | 8.2                              | *NR                           |

| Kim et al. <sup>10</sup>                  | 0.18                                | 54.5         | *NR          | $62.5^{**}$                                     | $10.2^{**}$         | 5.8                              | *NR                           |

| Laskar <i>et al</i> . <sup>11</sup>       | 0.18                                | 61.52        | 104.52       | 3.345                                           | 3.3                 | 13.4                             | 7.2                           |

| Proposed Neural Amplifier                 | 0.18                                | 50.5         | 124.07       | 4.68                                            | 1.38                | 13.1                             | 1.452                         |

| *NR= Not Reported; **inclu                | iding the ADC                       |              |              |                                                 |                     |                                  |                               |

proposed design is illustrated in Fig. 4, which is very low and equal to  $1.38 \mu V$ . As seen from Fig. 4, the flicker noise is dominant at lower frequency ranges and it decreases as the frequency increase. The flat frequency response following the corner frequency indicates that thermal noise is dominant which is mostly contributed by M1a, M3 and M9 as indicated by Eq. (3). Table 2 further indicates that the proposed design reports a lower input referred noise as compared to the other reported designs. The use of RFC-OTA architecture plays a significant role in this as none of the reported designs mentioned has utilized it to realize a neural amplifier. The sizing of the MOS transistors was further done by formulating the input noise as a design constraint for low random offset which also resulted in such a low value. This is evident from Eq. (4) which shows that to achieve a low random offset voltage, a lower g<sub>mla</sub> is required which also results in a low input noise as shown in Eq. (3). To achieve the random offset voltage, Monte Carlo analysis is performed and the standard deviation of the sample values is noted for a variation in process parameters which is found to be equal to 1.452 mV. This is better than the high swing cascode current mirror load based folded cascode OTA used to realize a neural amplifier as reported by Laskar *et al.*<sup>11</sup> indicated by Table 2. However, a small increase in power dissipation is reported as compared to other designs. This is due to the inherent noise-power tradeoff and higher  $I_{bias}$  required for minimum design specifications to be met.

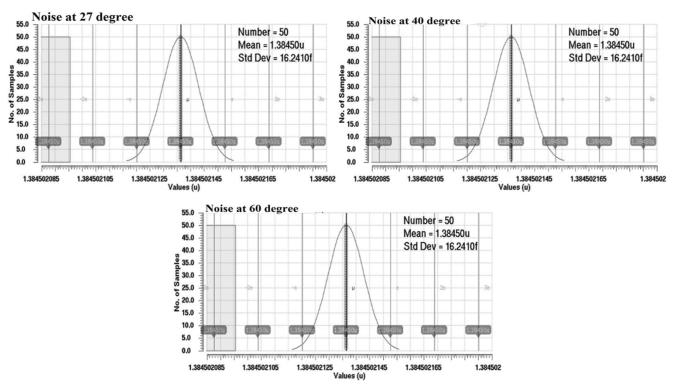

In order to test the robustness and reliability of the amplifier's performance, the Monte Carlo analysis is performed for a variation in temperature from room temperature i.e.  $27^{\circ}$ C to  $60^{\circ}$ C, by considering a sample size of 50 each. The results are shown in Table 3 and Fig. 5, from which it is evident that value of mean gain as well as mean input noise is very low with a value of around 50.4 dB and  $1.38\mu$ V respectively with a very low standard deviation of around 600 mdB and 16.42 fV for a wide variation of temperature from  $27^{\circ}$ C to  $60^{\circ}$ C.

|                          | Table 3 — Pert | formance of the pr | coposed design for | variation in temp | erature |        |

|--------------------------|----------------|--------------------|--------------------|-------------------|---------|--------|

| Parameter                | 27             | °C                 | 40°C               |                   | 60°C    |        |

| _                        | Mean           | SD                 | Mean               | SD                | Mean    | SD     |

| Gain (dB)                | 50.48          | 642m               | 50.45              | 339m              | 50.42   | 109.4m |

| Input Referred Noise (V) | 1.384µ         | 16.24f             | 1.384µ             | 16.24f            | 1.384µ  | 16.24f |

Fig. 5 — Monte Carlo Analysis of Input Noise for variation in temperature from 27°C to 60°C

## Conclusions

A low random offset, low noise neural amplifier design using capacitive feedback topology is reported. The proposed design utilizes the RFC-OTA to realize the amplifier. The modelling of the amplifier is done and the sizing of MOS transistors are performed considering a low random offset voltage as the design objective and all other design specifications such as gain, noise, power, CMRR, bandwidth, slew rate as design constraints which are to be met within the desired range. Simulations, Monte Carlo analysis for temperature variation have been performed and comparison with other reported designs illustrated a significant improvement in input noise and random offset voltage with a low standard deviation, while all other design specifications are within the required ranges for use in neural recording systems. The proposed design can be extended to include a programmable gain amplifier and ADC to design a complete neural recording system, which is a future enhancement to the proposed work.

### Acknowledgement

The authors would like to acknowledge the support provided by Ministry of Electronics Information Technology (MeitY), Govt. of India and SCL Mohali by providing necessary funding, EDA Tools and technology files under SMDP-C2SD Project.

### References

- 1 Bharucha E, Sepehrian H & Gosselin B, A Survey of Neural Front End Amplifiers and their Requirements Toward Practical Neural Interfaces, *J low power electron appl*, **4** (2014) 268–291.

- 2 Ruiz-Amaya J, Rodriguez-Perez A & Delgado-Restituto M, A Low Noise Amplifier for Neural Spike Recording Interfaces, *Sensors*, **15** (2015) 25313–25335.

- 3 Wattanapanitch W, Fee M & Sarpeshkar R, An Energy-Efficient Micropower Neural Recording Amplifier, *IEEE Trans Biomed Circuits Syst*, **1** (2007) 136–147.

- 4 Chaturvedi V & Amrutur B, An Area-Efficient Noise-Adaptive Neural Amplifier in 130 nm CMOS Technology, *IEEE Trans Emerg Sel Topics Circuits Syst*, **1** (2011) 536–545.

- 5 Ng K A, Greenwald E, Xu Y P & Thakor N V, Implantable Neurotechnologies: AReview of Integrated Circuit Neural Amplifiers, *Med Biol Eng Comput*, **54** (2016) 45–62.

- 6 Gholami B, Design and Simulation of a Low Voltage Low Offset Operational Amplifier, *Int J Adv Comput Sci Appl*, **7** (2016)337–339.

- 7 Lakshmikumar K R, Hadaway R A & Copeland M A, Characterization and Modelling of Mismatch in MOS Transistors for Precision Analog Design, *IEEE J Solid-St Circ*, SC-21 (1988) 1057–1066.

- 8 Feng Y, Zhigong W & Xiaoying L, A Multi-Channel Analog IC for In-Vitro Neural Recording, J Semicond, 37 (2016) 025007.

- 9 Ng K A & Xu Y P, A Low-Power, High CMRR Neural Amplifier System Employing CMOS Inverter-Based OTAs with CMFB through Supply Rails, *IEEE J Solid-St Circ*, **51** (2016) 724–737.

- 10 Kim S, Na S I, Yang Y, Kim H, Kim T, Cho J S & Kim S, A 4× 32-Channel Neural Recording System for Deep Brain Stimulation Systems, J Semicond Technol Sci, 17 (2017) 129–140.

- 11 Laskar N M, Guha K, Nath S, Chanda S, Baishnab K L, Paul P K & Rao K S, Design of High Gain, High Bandwidth Neural Amplifier IC considering Noise-Power Trade-Off, Accepted in *Microsyst Techn, Springer*.

- 12 Bhamra H, Lynch J, Ward M & Irazoqui P, A Noise-Power-Area Optimized Biosensing Front End for Wireless Body Sensor Nodes and Medical Implantable Device, Accepted in *IEEE Transon VLSI Syst.*

- 13 Laskar N M, Guha K, Chatterjee I, Chanda S, Baishnab K L & Paul P K, HWPSO: A New Hybrid Whale-Particle Swarm Optimization Algorithm and its application in Electronic Design Optimization Problems, *Appl Intell*, **49** (2019) 265–291.

- 14 Assad R S & Martinez J S, The Recycling Folded Cascode: A General Enhancement of the Folded Cascode Amplifier, *IEEE J Solid-St Circ*, 44 (2009) 2535–2542.