#### University of Huddersfield Repository

Amsdon, Timothy John

Implementation of a VLC HDTV Distribution System for Consumer Premises

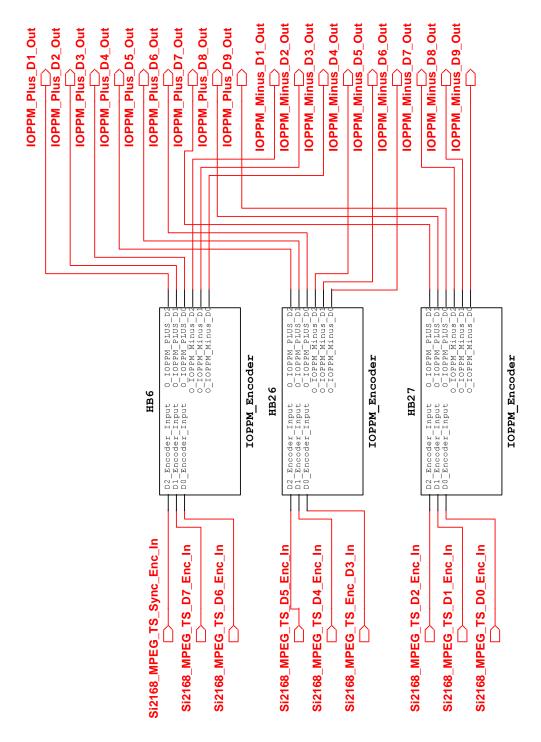

#### Original Citation

Amsdon, Timothy John (2020) Implementation of a VLC HDTV Distribution System for Consumer Premises. Doctoral thesis, University of Huddersfield.

This version is available at http://eprints.hud.ac.uk/id/eprint/35240/

The University Repository is a digital collection of the research output of the University, available on Open Access. Copyright and Moral Rights for the items

on this site are retained by the individual author and/or other copyright owners

Users may access full items free of charge; copies of full text items generally can be reproduced, displayed or performed and given to third parties in any format or medium for personal research or study, educational or not-for-profit purposes without prior permission or charge, provided:

- The authors, title and full bibliographic details is credited in any copy;

- A hyperlink and/or URL is included for the original metadata page; and

- The content is not changed in any way.

For more information, including our policy and submission procedure, please contact the Repository Team at: E.mailbox@hud.ac.uk.

http://eprints.hud.ac.uk/

# IMPLEMENTATION OF A VLC HDTV DISTRIBUTION SYSTEM FOR CONSUMER PREMISES

#### TIMOTHY JOHN AMSDON

BEng (Hons), CEng, SMIEEE, FIET, FHEA

A thesis submitted to the University of Huddersfield in partial fulfilment of the requirements for the degree of Doctor of Philosophy

19 July 2020

## **Copyright Statement**

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns any copyright in it (the Copyright) and s/he has given The University of Huddersfield the right to use such copyright for any administrative, promotional, educational and/or teaching purposes.

- ii. Copies of this thesis, either in full or in extracts, may be made only in accordance with the regulations of the University Library. Details of these regulations may be obtained from the Librarian. This page must form part of any such copies made.

- iii. The ownership of any patents, designs, trademarks and any and all other intellectual property rights except for the Copyright (the Intellectual Property Rights) and any reproductions of copyright works, for example graphs and tables (Reproductions), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property Rights and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property Rights and/or Reproductions.

## **Permissions**

The Silicon Labs tuner and DVB-T/T2/C demodulator EVB used in this work was kindly provided by Silicon Labs Inc., Texas, USA, under the conditions contained in a non-disclosure agreement (NDA) shown in Appendix C.1. Information presented in this thesis relating to the EVBs hardware, software and characterisation data is either in the public domain, or is published here under the reprint permission from Silicon Labs Inc. shown in Appendix C.2.

## **Publications**

This work has produced two publications; these are listed in chronological order below:

- Distribution of SDTV and HDTV Using VLC Techniques for Domestic Applications, T. J. Amsdon, M. J. N. Sibley, P. J. Mather, Wireless Satellite Systems, 8th International Conference, WiSATS 2016 Cardiff, UK, September 19–20, 2016 Proceedings, ISBN 978-3-319-53849-5.

- Theoretical Concepts and MATLAB Modelling of VLC Based MIMO Systems,

T. J. Amsdon, M. J. N. Sibley, CERC, University of Huddersfield, December 2013, ISBN 978-1-86218-121-2.

#### **Abstract**

A unidirectional, visible light communication (VLC) system intended for the distribution of Digital Video Broadcasting (DVB), high-definition television (HDTV) content to DVB compatible TVs within consumer premises is presented.

The system receives off-air HDTV content through a consumer grade DVB-T/T2 terrestrial set-top-box (STB) and re-encodes its Moving Picture Experts Group (MPEG) transport stream (TS) using a pulse position modulation (PPM) scheme called inversion offset PPM (IOPPM). The re-encoded TS is used to intensity modulate (IM) a blue light-emitting diode (LED) operating at a wavelength of 470 nm. Directed line-of-sight (DLOS) transmission is used over a free-space optical (FSO) channel exhibiting a Gaussian impulse response. A direct-detection (DD) receiver is used to detect the transmitted IOPPM stream, which is then decoded to recover the original MPEG TS. A STB supporting a high-definition multimedia interface (HDMI) is used to decode the MPEG TS and enable connectivity to an HD monitor.

The system is presented as a complementary or an alternative distribution system to existing Wi-Fi and power-line technologies. VLC connectivity is promoted as a safer, securer, unlicensed and unregulated approach. The system is intended to enable TV manufacturers to reduce costs by, firstly, relocating the TV's region specific radio frequency (RF) tuner and demodulator blocks to an external STB capable of supporting DVB reception standards, and, secondly, by eliminating all input and output connectors interfaces from the TV. Given the current trend for consumers to wall-mount TVs, the elimination of all connector interfaces, except the power cable, makes mounting simpler and easier.

The operation of the final system was verified using real-world, off-air broadcast DVB-T/T2 channels supporting HDTV content. A serial optical transmission at a frequency of 66 MHz was achieved. The system also achieved 60 Mbit/s, error free transmission over a distance of 1.2 m without using error correction techniques.

The methodology used to realise the system was a top-down, modular approach. Results were obtained from electrical modelling, simulation and experimental techniques, and using time-domain and FFT based measurements and analysis. The modular approach was adopted to enable design, development and testing of the subsystems independently of the overall system.

## Acknowledgements

There are a number of people I have to thank for my development and advancement as a student of engineering, as a professional engineer in industry, and as a researcher in academia, without the encouragement and teachings of those mentioned herein, I would not have been able to achieve the many wonderful things I have in my career, nor would I have been able to start, let alone complete this thesis.

The beginning of my life-long passion for all things electrical and electronic began the day my father, Ronald William Amsdon, removed the rear panel of a Philips G11 Colour TV to adjust its convergence circuits. As a curious nine year old, I peered inside the open TV and to my astonishment, discovered a fascinating new world. My father must have seen my eyes widen, because he enthusiastically explained what each circuit of the TV did in order to bring pictures and sound into our living room. I was captivated, and knew I wanted to know more about this intriguing new world.

In later years, as an experienced engineer, I have recalled my father's summary of the G11 chassis, and marvelled at how much he knew. My father was not trained as an engineer, but as a salesman, he was more accustomed to selling TV's than repairing them, but he had the mind and spirit of an engineer. He learnt from service technicians at the now long since defunct British Relay, and read service manuals to further his knowledge and understanding. From this rudimentary education, he was able to read and understand circuit schematics and layouts, as well as fault-find and fix to component level. Through practice, he also developed excellent soldering skills. I am eternally grateful to him for introducing me to electronics.

An immeasurable amount of thanks also goes to my mother, Jean Amsdon, for purchasing my first computer, a ZX Spectrum 48K, back in the Christmas of 1984. At first she was sceptical about my interest in this emerging technology, but she quickly realised I had a passion and aptitude for computing and programming, and encouraged my fascination by purchasing books and magazines on these subjects. My 48K was my pride and joy, providing me with a gateway into digital electronics and programming.

Heartfelt thanks goes to my long suffering fiancée, Rebecca Denise Knoebel, to whom I owe a great deal. She has supported and encouraged me throughout the highs and lows of being a professional engineer and postgraduate researcher. She has been of great comfort during tough times, and without her love and support I would not have been able to stay the course.

I would also like to thank my sister, Deborah Stephenson, and brother-in-law, John Edward Stephenson, for buying me my first DC variable power supply for my eighteenth birthday. It helped me a great deal with my academic studies at college and university, and also with various hobby circuits I designed. I would also like to give

additional thanks to John for teaching me about domestic electrical wiring and plumbing throughout my teenage years'.

My deepest respect and thanks goes to my supervisors Dr Martin Sibley and Dr Peter Mather for their support, encouragement and commitment to mentoring me both as an undergraduate student in the late 1990s and as a postgraduate researcher since 2013. I owe them both a debt of gratitude for keeping my spirits up and moving me along. I hope we remain friends beyond this work.

Special thanks to Silicon Labs Inc. for providing me with the Si2147 DVB low-IF tuner and Si2168 DVB-T/T2 demodulator evaluation board, without which this work would not have been possible. I would like to specifically thank for their support: Rick Bosworth, Terry Dickey, Eric Garlepp, Rob King, Brian Mirkin, Alessandro Piovaccari, Ramin Poorfard, Bill Simcoe, James Stansberry and Tyson Tuttle.

Many thanks to Red Embedded Consulting Ltd for putting consultancy work my way to help pay the bills. Thanks in particular to: Peter Garrett, Jon Ledbury, Matthew Lewis, Darren Longhorn, Rahul Mehra, and Andrew Stewart. I would like to give special thanks to David Taylor whom gave me with a useful summary of consumer power-line technologies.

I would like to thank a number of other people who have supported and encouraged my research, and also provided me with paid teaching work over the past six years'. These people are namely: Dr Violeta Holmes, Mr Roland Clarke, Prof. Robert Kelsall, Prof. Andrew Kemp and Mr Stephen Zimmer.

I would like to thank my friends and fellow electronics junkies, whom have supported me throughout my research, namely: Dr Maythem Ali, Dr Sanjin Berberkic and Dr David Upton. Thank you for all meaningful conversations, as well as the fun and laughter.

Last, but certainly not least, I would like to thank the following individuals whom have been influential in my career through their teaching, advice and support. Some of these individuals have also entrusted and empowered me, giving me opportunities I never dreamt I would have. Specifically, and in alphabetical order by surname: Mark Appel, Ian Clark, Peter Coe, Terry Cox, John Dean, Mr Garside, Jean-Marc Guyot, David Hanam, Tony Hargreaves, Ian Hunter, Mr Illingworth, Steve Jenkins, Rob Kirk, Andy Lee, Harry Lahmers, Tony Laycock, Giuseppe Mastrangelo, Rebinder Panesar, Carey Ritchey, Kurt Richter, Maurice Shephard, Joanne Shiel, Albert (Bud) Taddiken, Dariusz Wanatowski, and Greg Zancewicz.

I dedicate this thesis to my father, Ronald William Amsdon (1925–1999). I only wish he had lived to see all the things that I have achieved, all because I saw the inside of a Philips G11 Colour TV when I was nine years' old.

# **Contents**

| Copyright Statement                          |

|----------------------------------------------|

| Permissionsi                                 |

| Publicationsii                               |

| Abstractiv                                   |

| Acknowledgementsv                            |

| Γable of Figuresxvi                          |

| Glossaryxxv                                  |

| Acronymsxxv                                  |

| Notationxxxii                                |

| Constantsxxxvii                              |

| 1 Introduction                               |

| 1.1 Background                               |

| 1.1.1 TV Interconnects                       |

| 1.1.2 Flat-panel TV Wall-mounting Challenges |

| 1.1.3 Digital TV Trends                      |

| 1.1.4 All-Digital TV and DVB MPEG TS         |

| 1.1.5 New All-Digital Architecture           |

| 1.1.6 Wi-Fi                                  |

| 1.1.7 Power-Line                             |

| 1.2 VLC                                      |

| 1.2.1      | System Architecture                       | 19 |

|------------|-------------------------------------------|----|

| 1.2.2      | Advantages of VLC Systems                 | 21 |

| 1.2.3      | Physical Arrangement                      | 24 |

| 1.2.4      | Proof-of-Concept System                   | 26 |

| 1.3 Ai     | ms and Objectives                         | 27 |

| 1.3.1      | Aims                                      | 27 |

| 1.3.2      | Objectives                                | 27 |

| 1.4 Or     | riginal Work                              | 28 |

| 1.5 Th     | nesis Structure                           | 29 |

| 2 Literatu | are Review and Theory                     | 31 |

| 2.1 DV     | VB MPEG TS Bus                            | 31 |

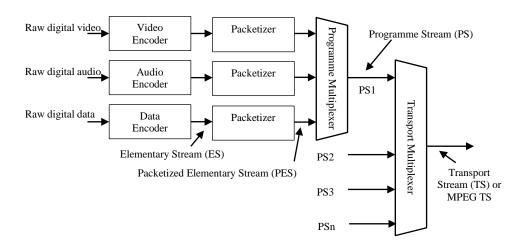

| 2.1.1      | DVB Transmit Path                         | 32 |

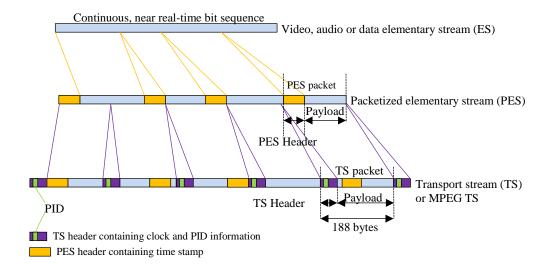

| 2.1.2      | Source Encoding and Multiplexing: MPEG TS | 39 |

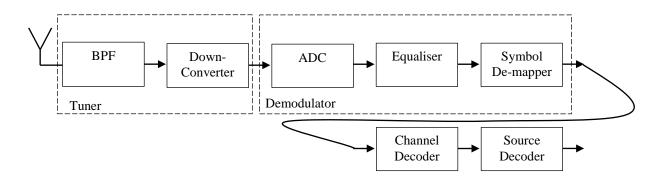

| 2.1.3      | DVB Receive Path                          | 43 |

| 2.1.4      | MPEG TS Demultiplexing and Decoding       | 45 |

| 2.1.5      | Real-world DVB-T/T2 Receiver Architecture | 48 |

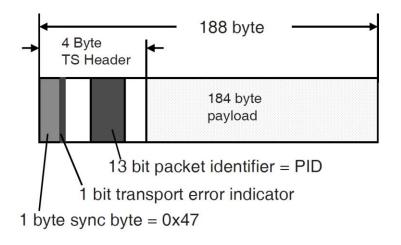

| 2.1.6      | MPEG TS Physical Layer                    | 49 |

| 2.2 VI     | LC Overview                               | 53 |

| 2.2.1      | Semiconductor LEDs                        | 54 |

| 2.2.2      | Blue LEDs                                 | 55 |

| 2.2.3      | White-Light LED and Solid-State Lighting  | 57 |

| 2.2.4  | Line-of-sight and Diffuse Transmission               | 59 |

|--------|------------------------------------------------------|----|

| 2.3 V  | LC Systems                                           | 63 |

| 2.3.1  | Intensity Modulation and Direct-Detection            | 63 |

| 2.3.2  | White LED Bandwidth and Blue Optical Filtering       | 65 |

| 2.3.3  | RGB and Single Colour LED Bandwidth                  | 67 |

| 2.4 Tı | ansmission Model                                     | 69 |

| 2.4.1  | Lambertian Emission                                  | 69 |

| 2.4.2  | DLOS Transmission Model                              | 70 |

| 2.5 In | tensity Modulation and Direct Detection Architecture | 73 |

| 2.5.1  | Channel Model                                        | 75 |

| 2.5.2  | Optical Channel Impulse Response                     | 76 |

| 2.5.3  | ISI and Pulse Shaping                                | 78 |

| 2.5.4  | Pulse Bandwidth                                      | 79 |

| 2.6 O  | WC System Electrical Modelling                       | 81 |

| 2.6.1  | TCA                                                  | 81 |

| 2.6.2  | LED                                                  | 83 |

| 2.6.3  | PD                                                   | 85 |

| 2.6.4  | Pre-amplifier                                        | 87 |

| 2.6.5  | Equalisation                                         | 88 |

| 2.6.6  | Post-amplifier                                       | 89 |

| 2.6.7  | Pre-detection Filter                                 | 90 |

|   | 2.6.8    | Comparator                             | 91  |

|---|----------|----------------------------------------|-----|

|   | 2.7 Dig  | gital Modulation Scheme                | 93  |

|   | 2.7.1    | Offset PPM                             | 93  |

|   | 2.7.2    | OPPM Errors                            | 97  |

|   | 2.7.3    | OPPM Encoder/Transmitter (MPEG TS)     | 99  |

|   | 2.7.4    | OPPM On/Off LED Driver                 | 102 |

|   | 2.7.5    | OPPM Receiver/Decoder (MPEG TS)        | 103 |

|   | 2.8 Co   | nclusions                              | 104 |

| 3 | Propose  | d Coding Scheme                        | 109 |

|   | 3.1 Inv  | version OPPM                           | 109 |

|   | 3.1.1    | IOPPM Encoding (MPEG TS)               | 109 |

|   | 3.1.2    | IOPPM Encoder and Decoder Logic        | 113 |

|   | 3.1.3    | IOPPM Encoder/Transmitter (Single LED) | 115 |

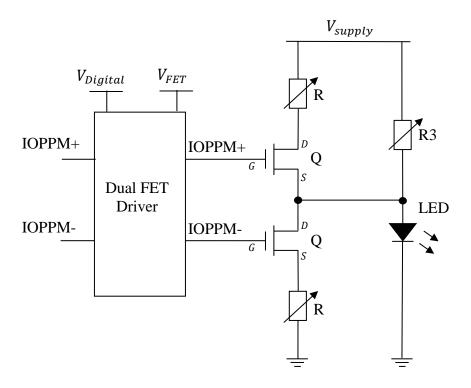

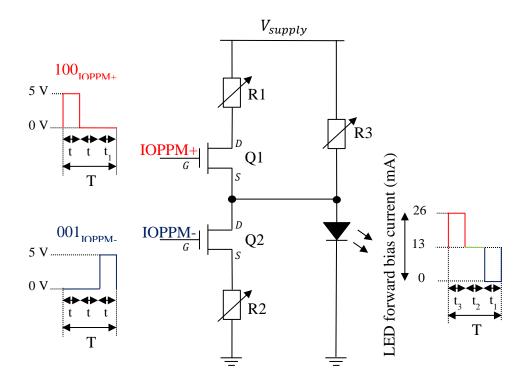

|   | 3.1.4    | IOPPM On/Off Driver (Single LED)       | 118 |

|   | 3.1.5    | IOPPM Receiver/Decoder (Single LED)    | 122 |

|   | 3.1.6    | IOPPM Encoder/Transmitter (Dual LEDs)  | 129 |

|   | 3.1.7    | IOPPM On/LED Drive (Dual LEDs)         | 131 |

|   | 3.1.8    | IOPPM Receiver/Decoder (Dual LEDs)     | 132 |

|   | 3.1.9    | IOPPM Path Calibration                 | 134 |

|   | 3.1.10   | Conclusions                            | 134 |

| 4 | Device ( | Characterisation and Analysis          | 137 |

| 4.1 MI | PEG TS Data Source and Sink Characterisation and Analysis | 137 |

|--------|-----------------------------------------------------------|-----|

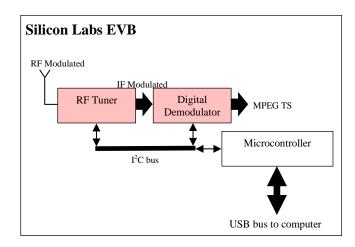

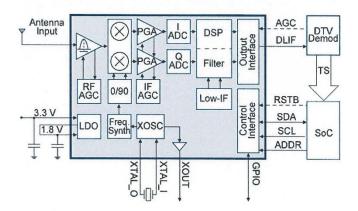

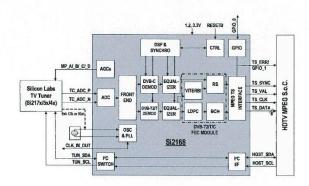

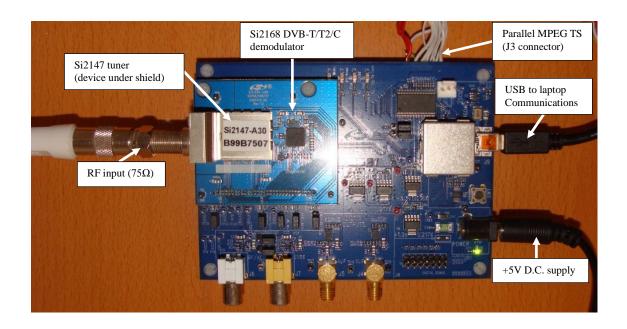

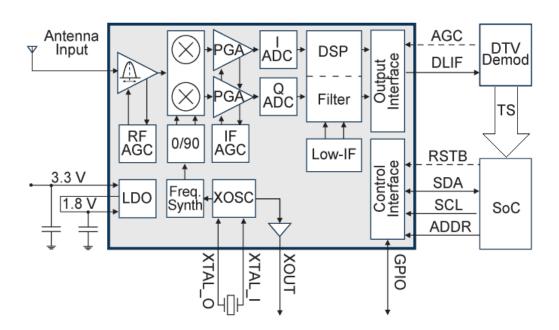

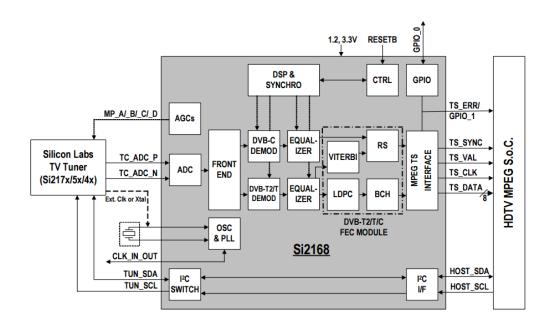

| 4.1.1  | Silicon Labs Evaluation Board Overview                    | 139 |

| 4.1.2  | EVB MPEG TS Characterisation and Analysis                 | 140 |

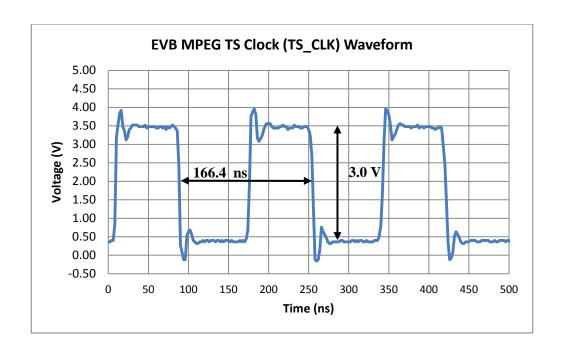

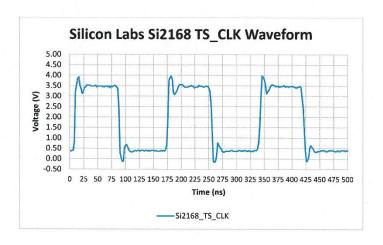

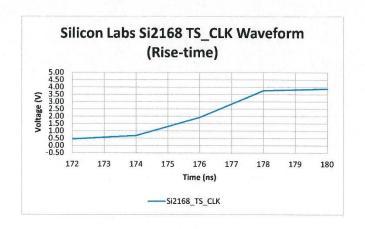

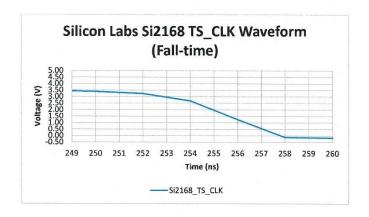

| 4.1.3  | EVB MPEG TS Clock (TS_CLK)                                | 141 |

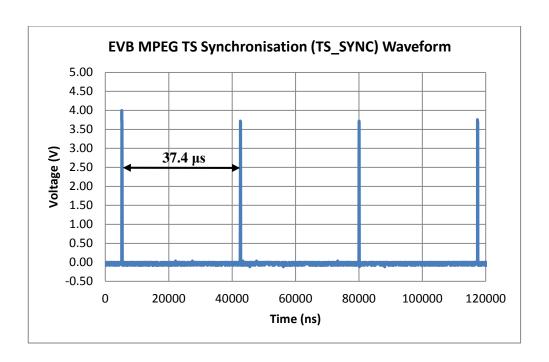

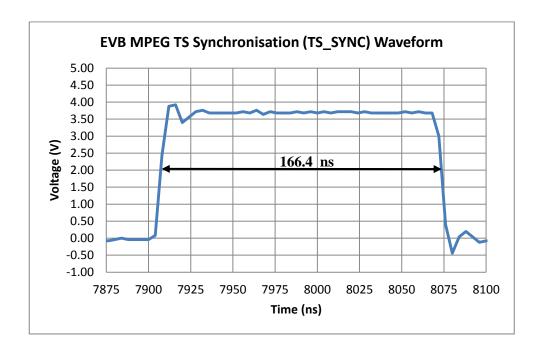

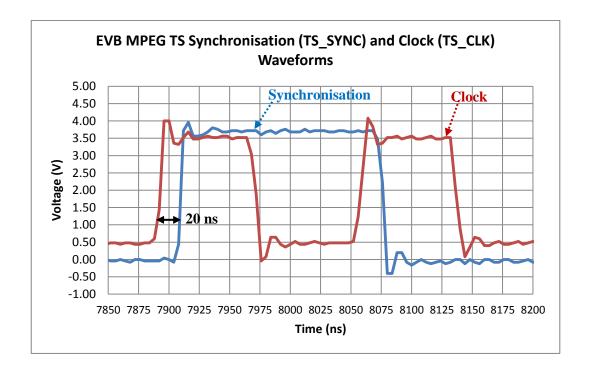

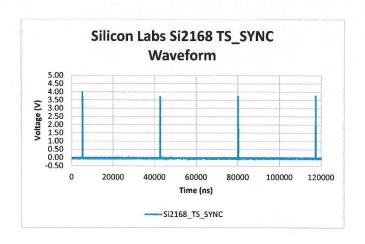

| 4.1.4  | EVB MPEG TS Synchronisation (TS_SYNC)                     | 142 |

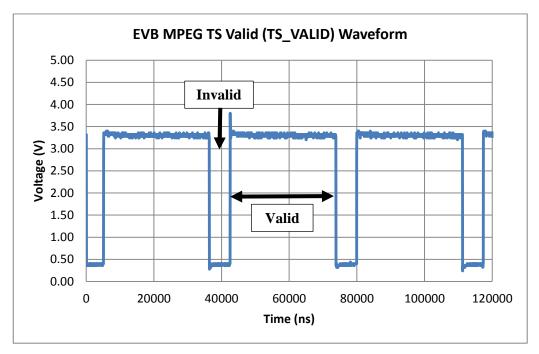

| 4.1.5  | EVB MPEG TS Valid (TS_VALID)                              | 146 |

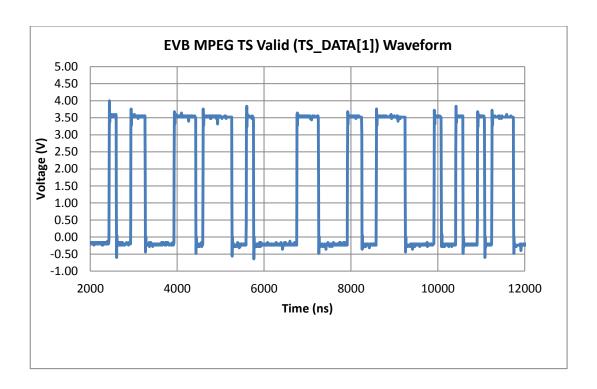

| 4.1.6  | EVB MPEG TS Data (TS_DATA[1])                             | 146 |

| 4.1.7  | EVB MPEG TS Summary                                       | 147 |

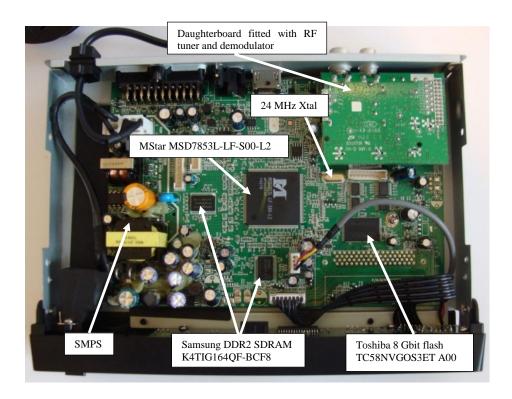

| 4.1.8  | Bush DH2636 STB Overview                                  | 149 |

| 4.1.9  | STB MPEG TS Characterisation and Analysis                 | 150 |

| 4.1.10 | STB MPEG TS Clock (TS_CLK)                                | 150 |

| 4.1.11 | STB MPEG TS Synchronisation (TS_SYNC)                     | 151 |

| 4.1.12 | STB MPEG TS Valid (TS_VALID)                              | 154 |

| 4.1.13 | STB MPEG TS Data (TS_DATA[1])                             | 155 |

| 4.1.14 | STB MPEG TS Summary                                       | 156 |

| 4.1.15 | Data Source and Sink End-to-End Compatibility             | 158 |

| 4.1.16 | Conclusions                                               | 161 |

| 4.2 LE | ED Characterisation and Analysis                          | 163 |

| 4.2.1  | White LED Overview                                        | 163 |

| 4.2.2  | White LED Characterisation and Analysis                   | 164 |

| 4.2.3  | Blue (470 nm) LED Overview                                | 168 |

|   | 4.2.4  | Blue (470 nm) LED Characterisation and Analysis | 169 |

|---|--------|-------------------------------------------------|-----|

|   | 4.2.5  | Conclusions                                     | 173 |

| 5 | System | : Design and Simulation                         | 176 |

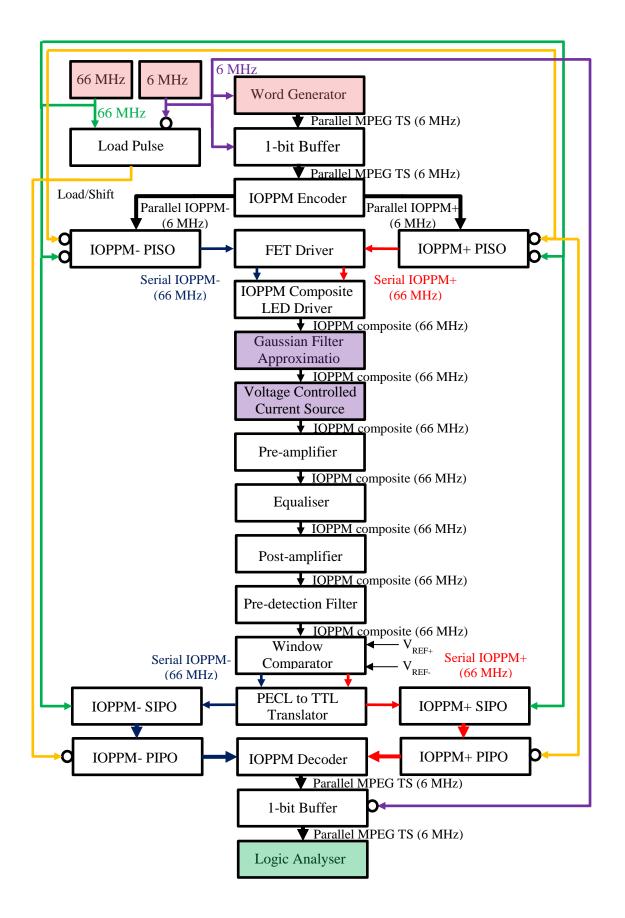

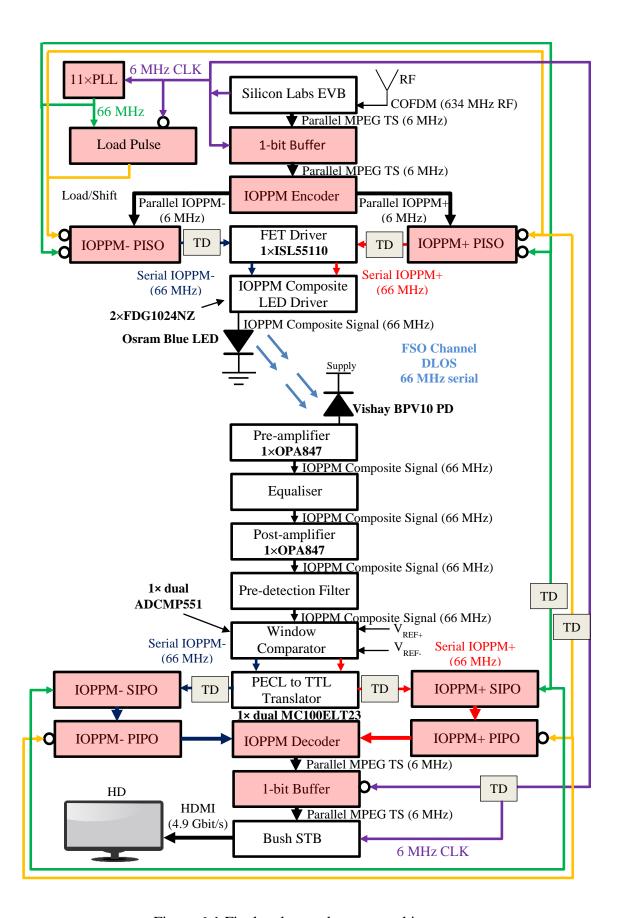

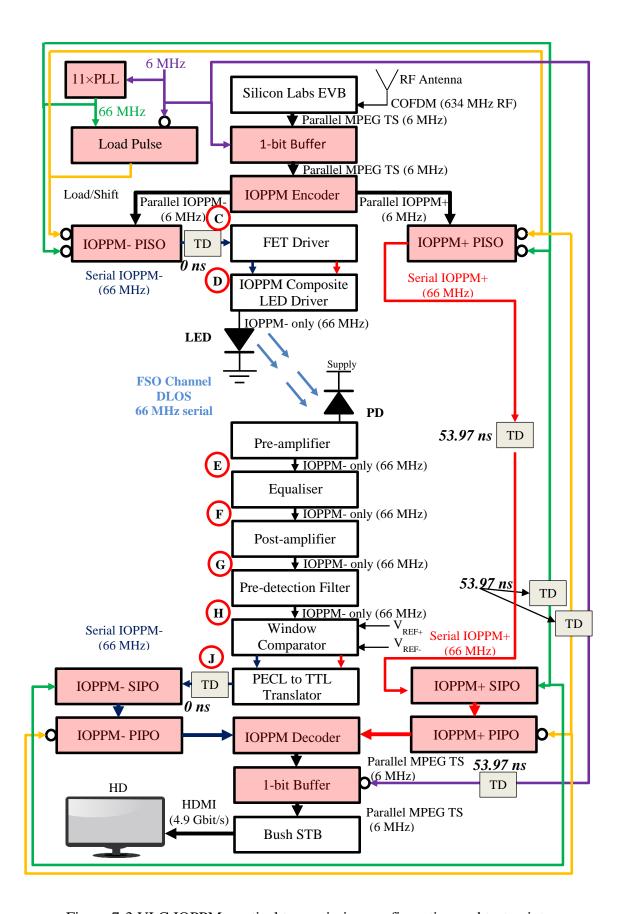

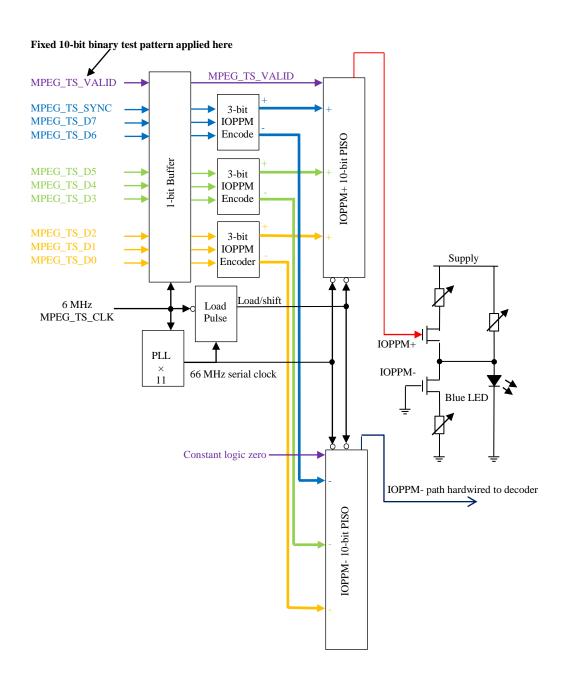

|   | 5.1 To | pp-level Architecture (IOPPM Single LED)        | 176 |

|   | 5.1.1  | System Operation                                | 178 |

|   | 5.2 Di | gital Subsystems                                | 185 |

|   | 5.2.1  | 1-bit Buffer (Tx)                               | 185 |

|   | 5.2.2  | IOPPM Encoder (Tx)                              | 185 |

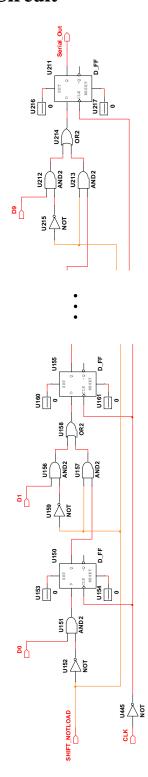

|   | 5.2.3  | 10-bit PISO (Tx)                                | 187 |

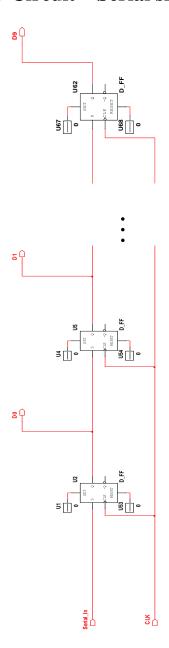

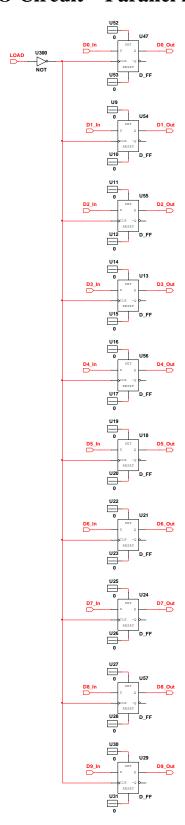

|   | 5.2.4  | 10-bit SIPO (Rx)                                | 190 |

|   | 5.2.5  | IOPPM Decoder (Rx)                              | 192 |

|   | 5.2.6  | 1-bit Buffer (Rx)                               | 194 |

|   | 5.3 Ar | nalogue Subsystems                              | 194 |

|   | 5.3.1  | IOPPM Composite LED Driver (Tx)                 | 195 |

|   | 5.3.2  | Pre-Amplifier (Rx)                              | 201 |

|   | 5.3.3  | Equaliser (Rx)                                  | 207 |

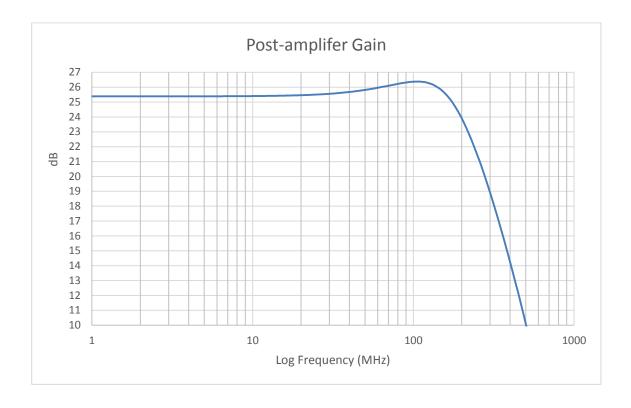

|   | 5.3.4  | Post-Amplifier (Rx)                             | 213 |

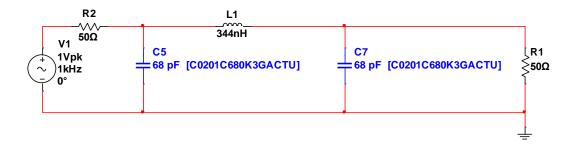

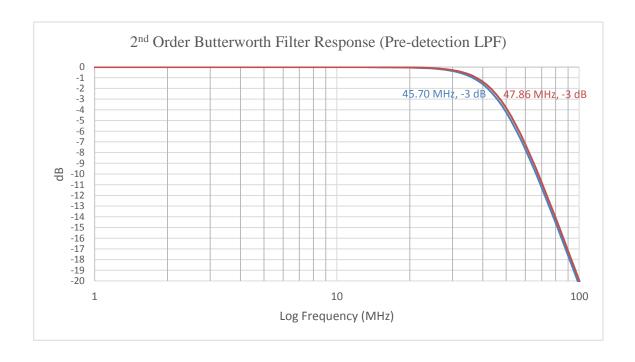

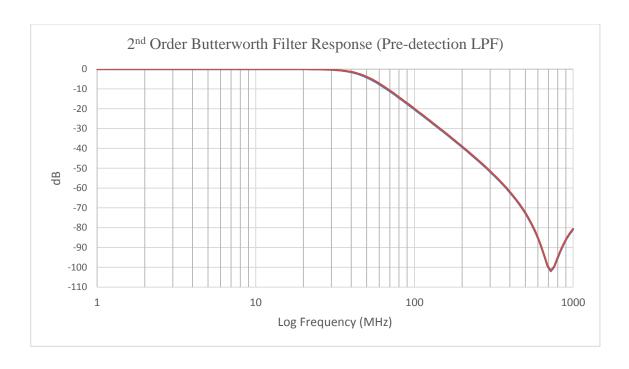

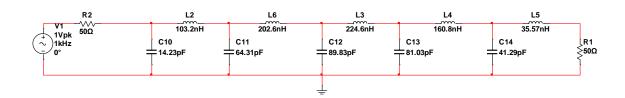

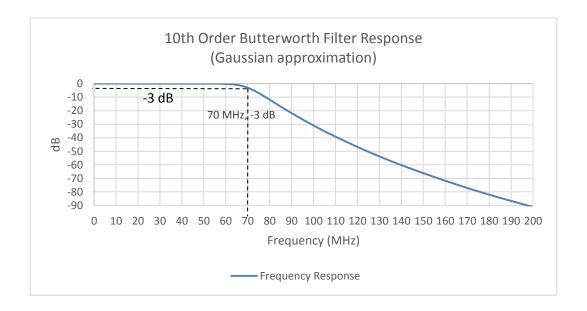

|   | 5.3.5  | Pre-Detection LPF (Rx)                          | 216 |

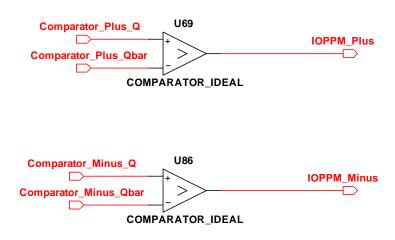

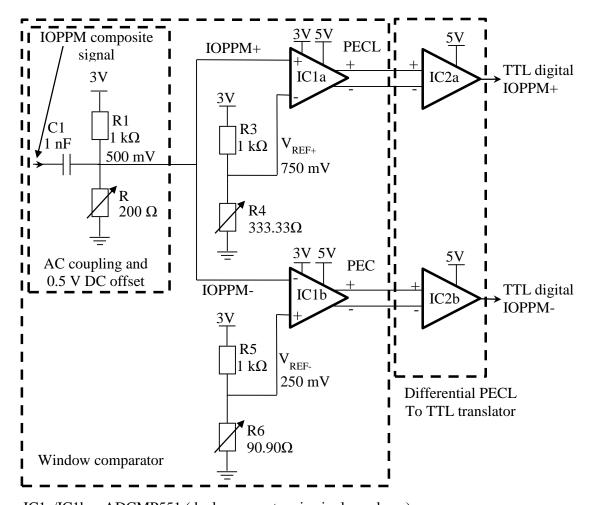

|   | 5.3.6  | Comparator (Rx)                                 | 218 |

|   | 5.3.7  | VLC System Electrical Model                     | 226 |

|   | 5.3.8  | Conclusions                                     | 230 |

| 6 | Sys  | tem:  | Implementation                                    | 233 |

|---|------|-------|---------------------------------------------------|-----|

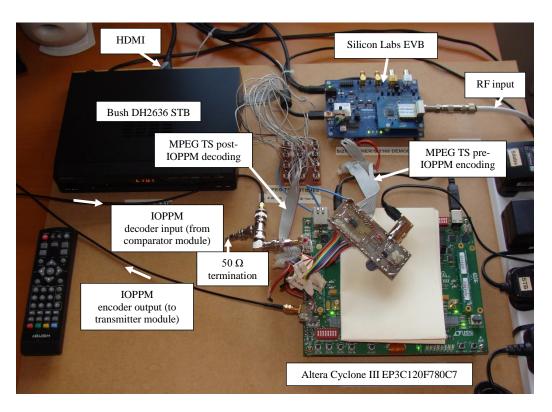

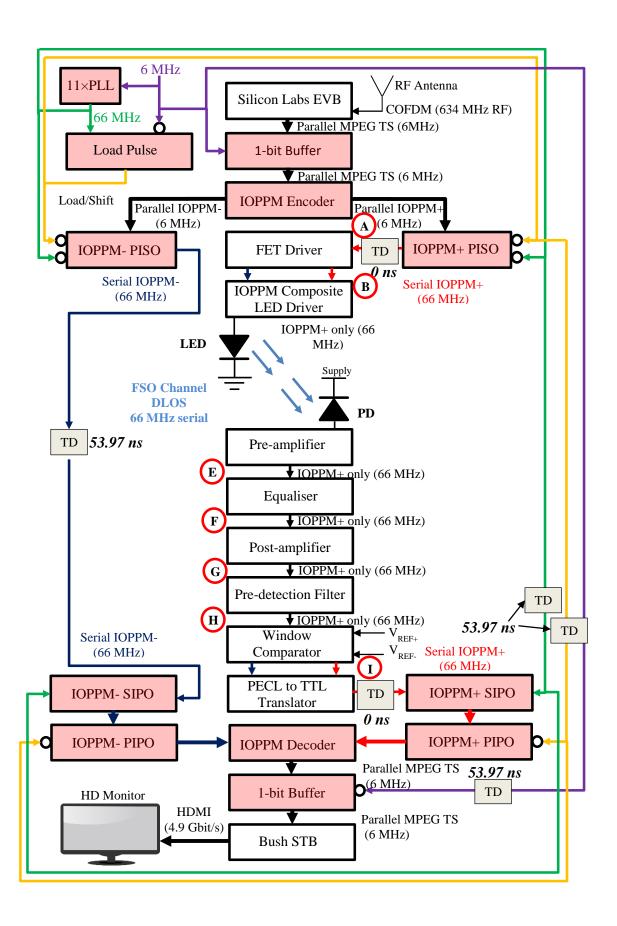

|   | 6.1  | En    | d-to-End VLC System Architecture (Single LED)     | 233 |

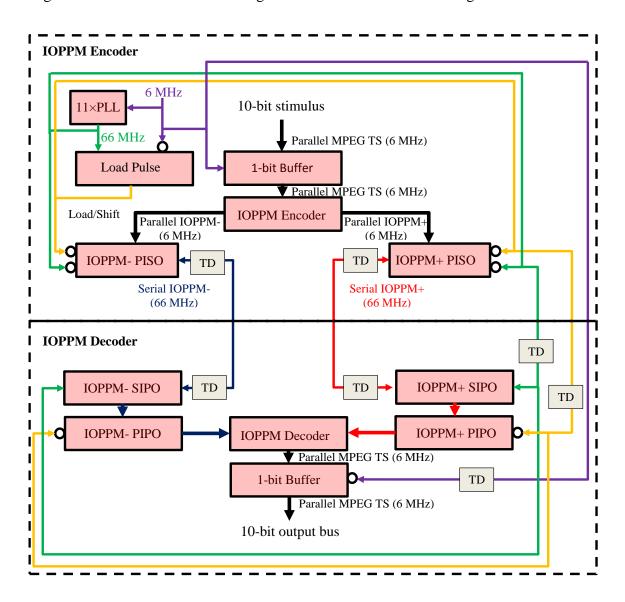

|   | 6.2  | Dig   | gital Subsystem Implementation                    | 236 |

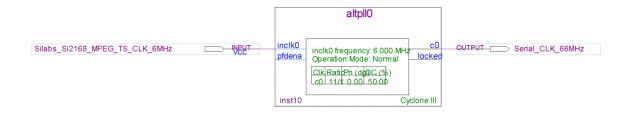

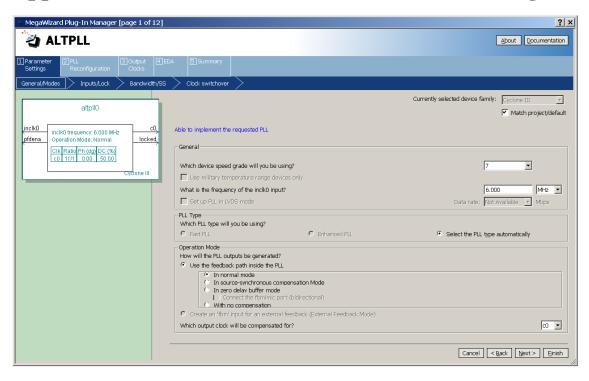

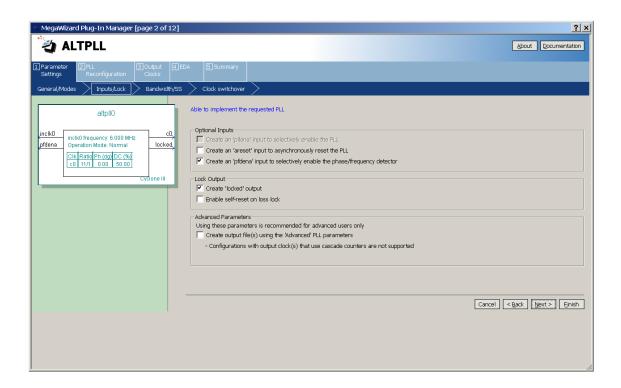

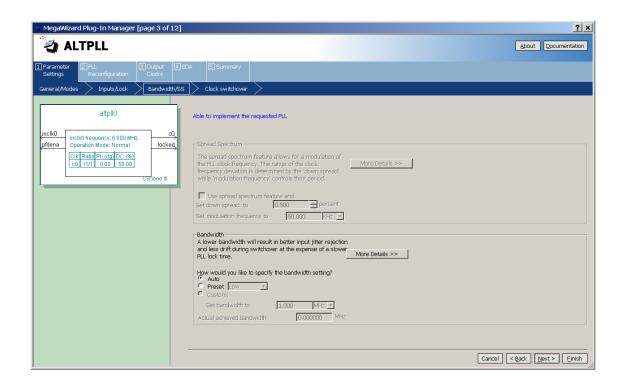

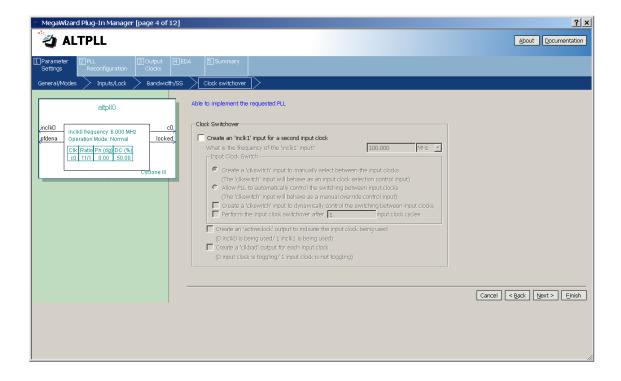

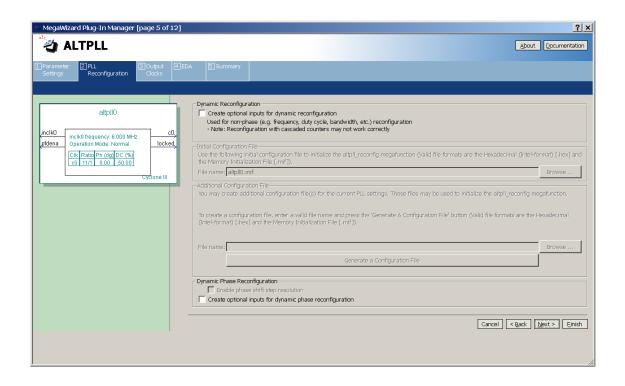

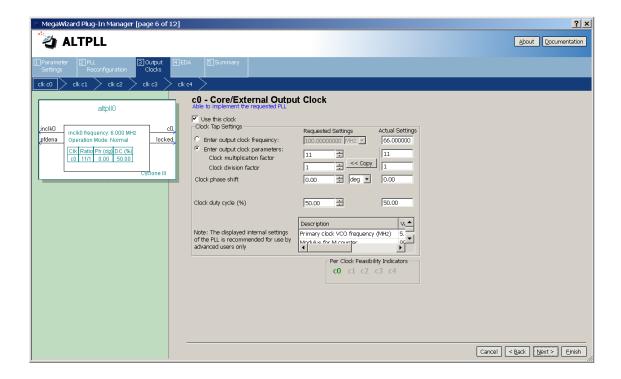

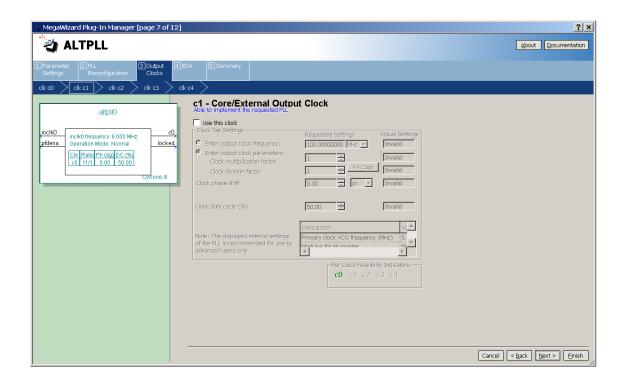

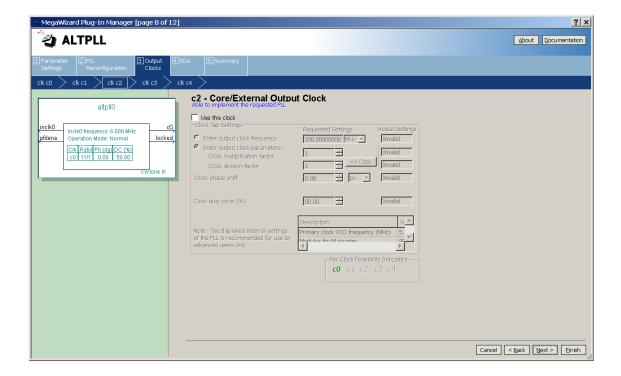

|   | 6.2. | .1    | PLL                                               | 237 |

|   | 6.2. | .2    | Digital Path Delay Calibration                    | 238 |

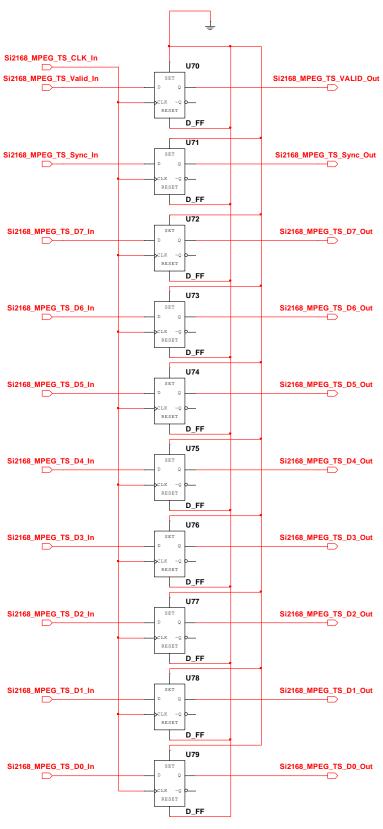

|   | 6.2. | .3    | Parallel MPEG TS and FPGA Compatibility           | 239 |

|   | 6.3  | An    | alogue Subsystem Implementation                   | 241 |

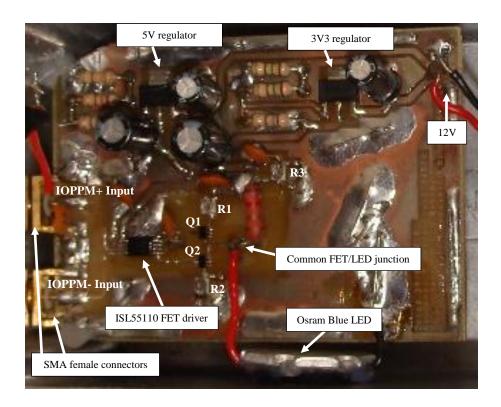

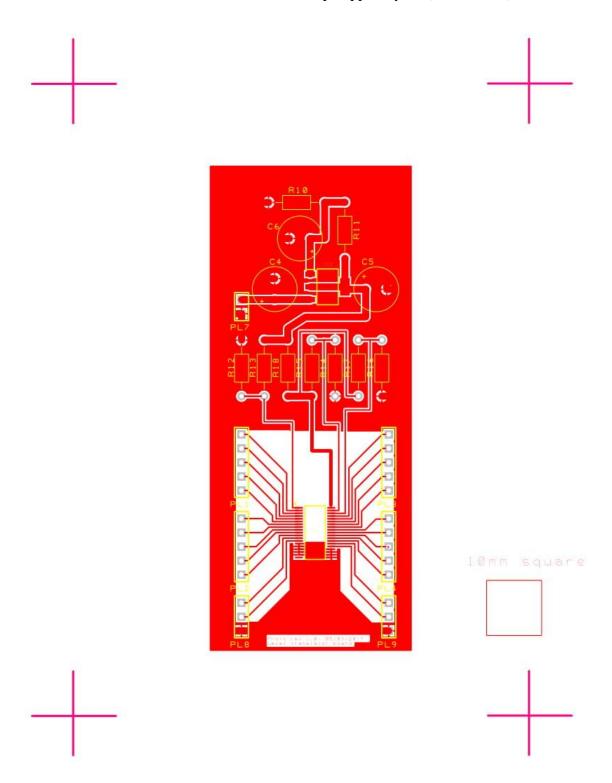

|   | 6.3. | .1    | Transmitter Module                                | 242 |

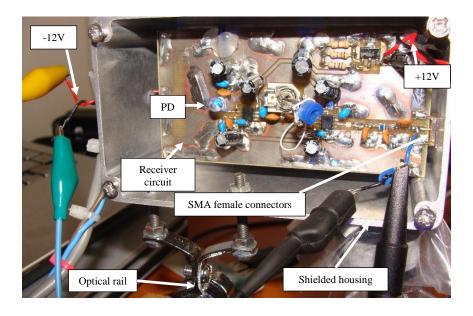

|   | 6.3. | .2    | Receiver Module                                   | 246 |

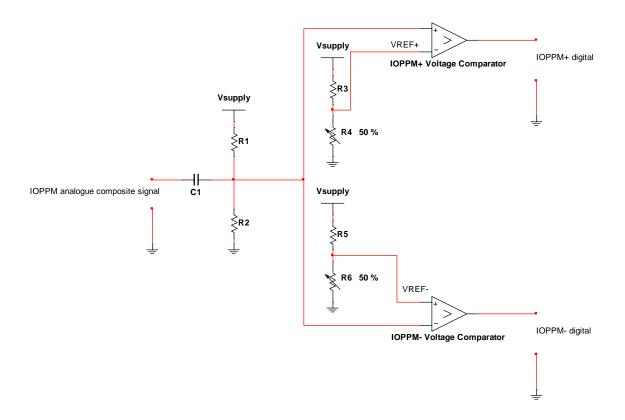

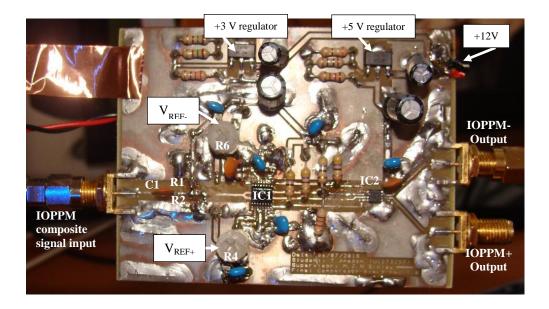

|   | 6.3. | .3    | Comparator Module                                 | 250 |

|   | 6.4  | Ph    | ysical VLC System Integration                     | 253 |

|   | 6.5  | DL    | OS Optical Rail                                   | 255 |

|   | 6.6  | Pat   | h Calibration                                     | 255 |

|   | 6.7  | Co    | nclusions                                         | 259 |

| 7 | Res  | sults | and Analysis                                      | 261 |

|   | 7.1  | Tir   | ne Domain Measurements and Analyses               | 261 |

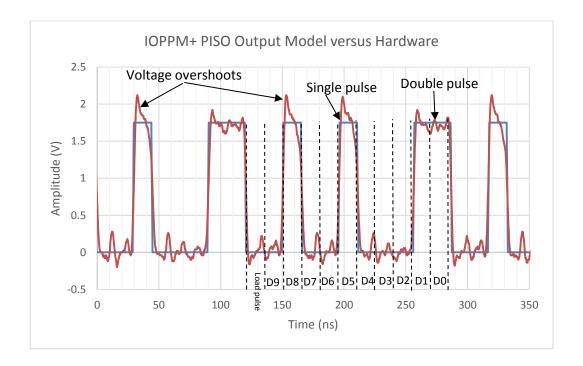

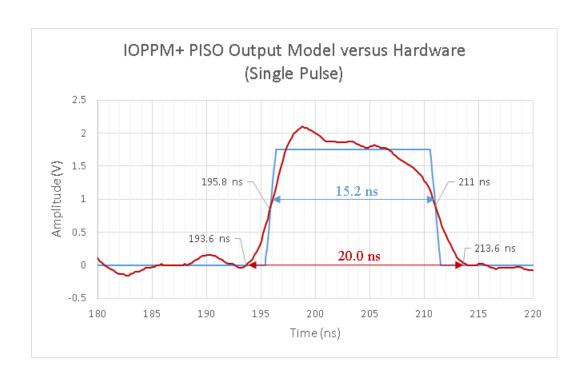

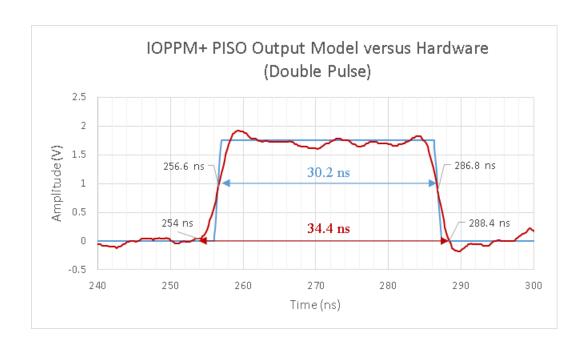

|   | 7.1. | .1    | FPGA IOPPM Output Timing (Test points A and C)    | 266 |

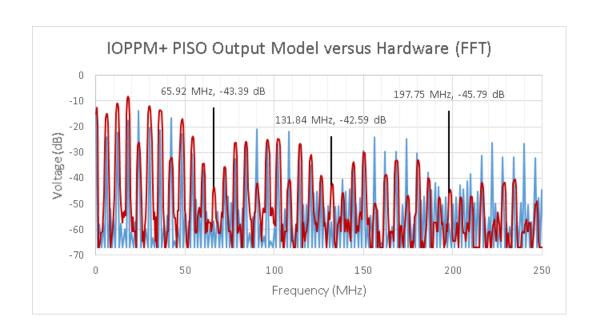

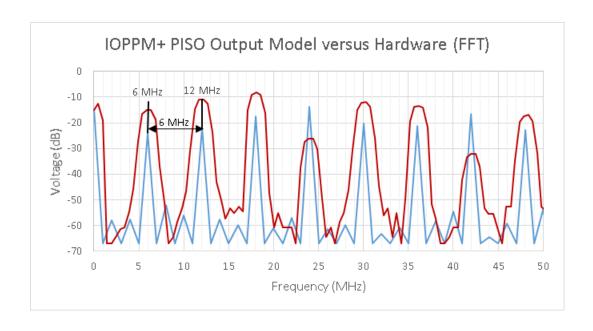

|   | 7.1. | .2    | FPGA IOPPM Frequency Domain (Test points A and C) | 269 |

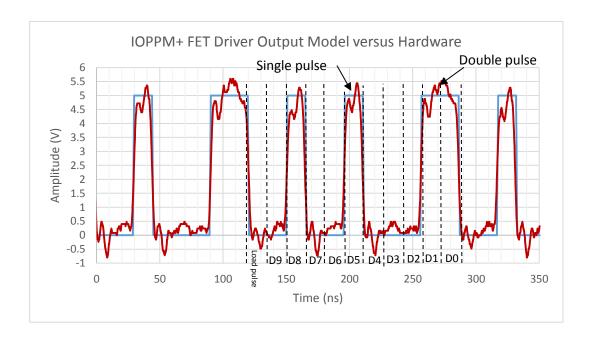

|   | 7.1. | .3    | FET Driver Output (Test points B and D)           | 272 |

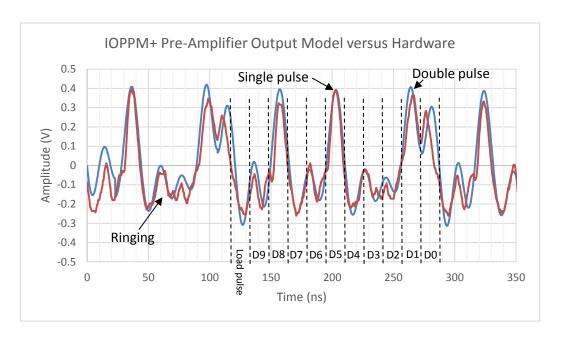

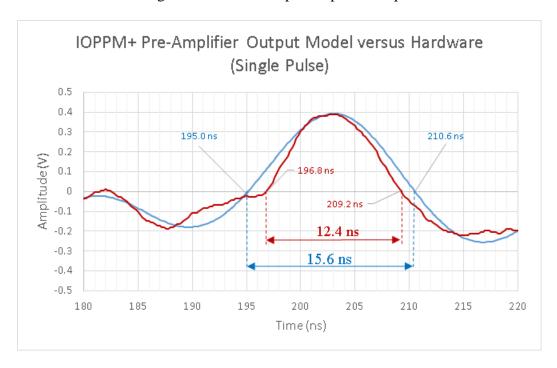

|   | 7.1. | .4    | Pre-amplifier Output (Test point E)               | 273 |

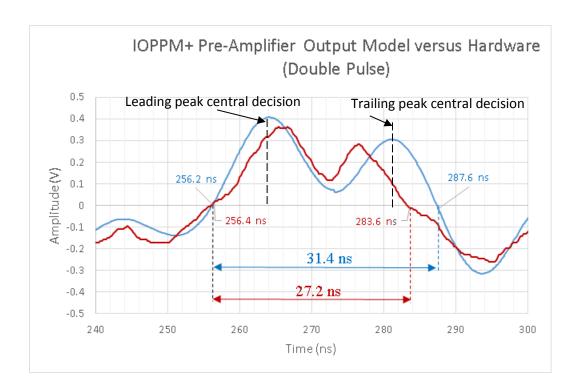

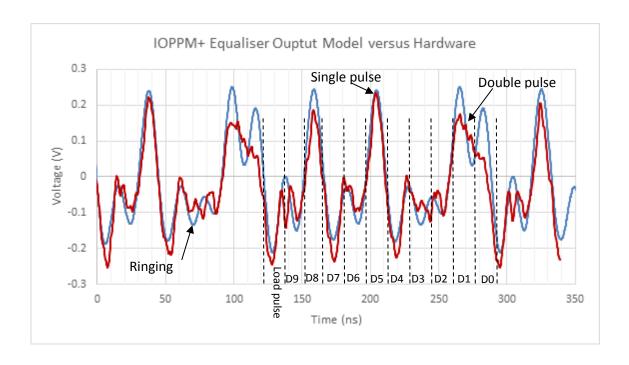

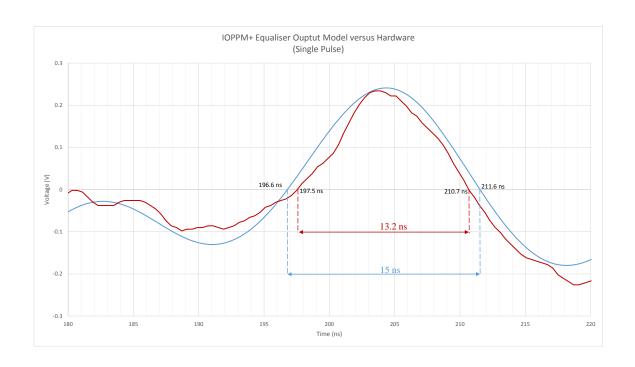

|   | 7.1. | .5    | Equaliser Output (Test Point F)                   | 277 |

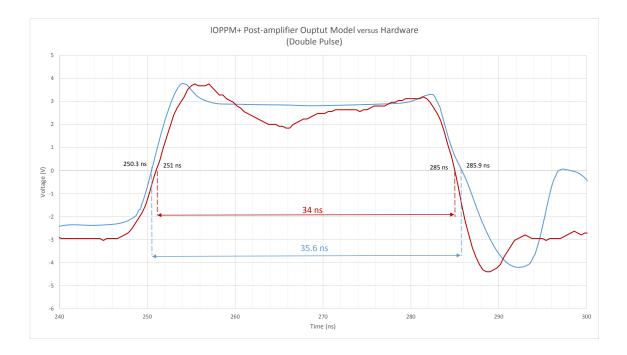

| 7.1.6      | Post-amplifier Output (Test Point G)                 | 281 |

|------------|------------------------------------------------------|-----|

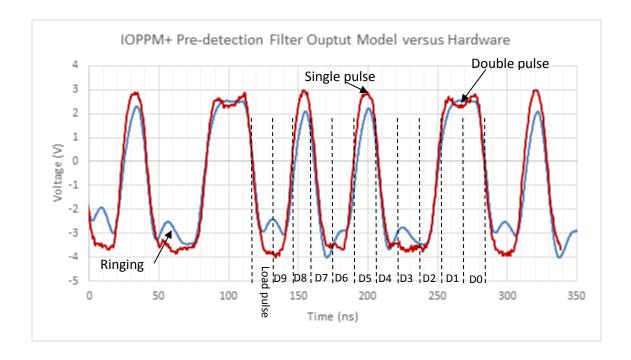

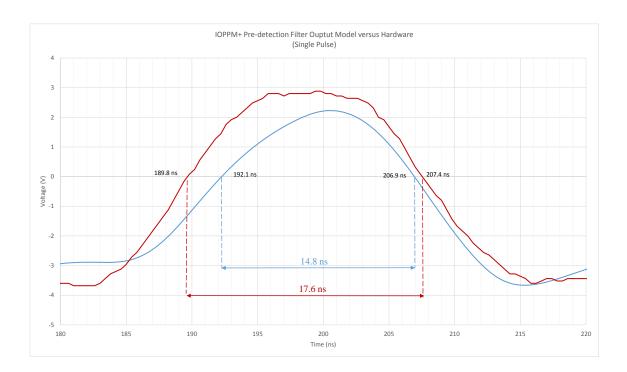

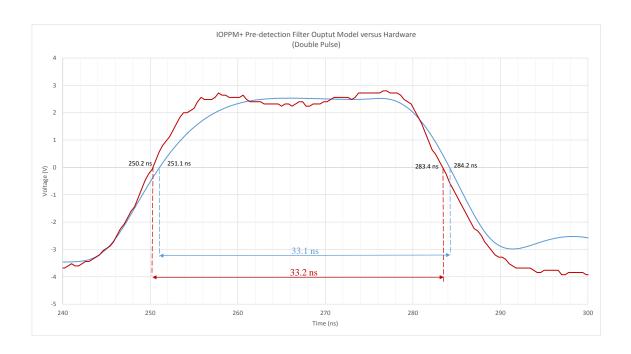

| 7.1.7      | Pre-detection Filter Output (Test Point H)           | 284 |

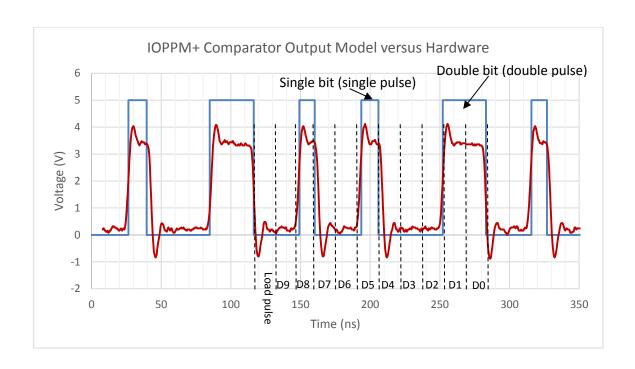

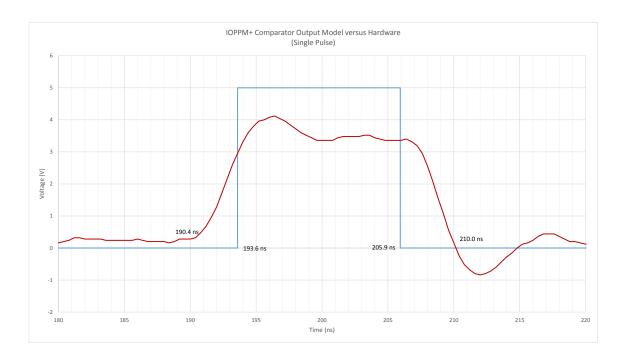

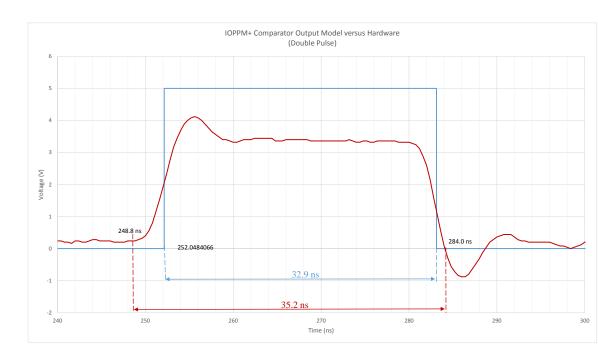

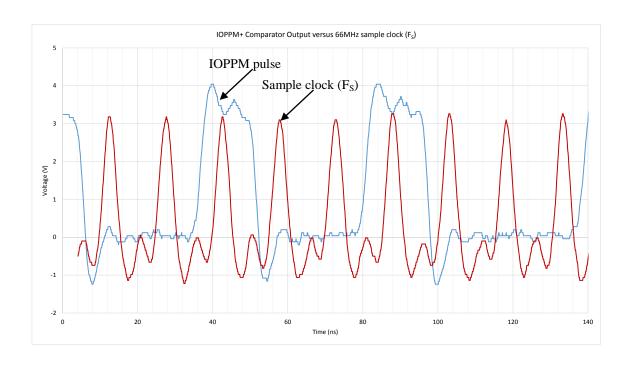

| 7.1.8      | Comparator Output (Test points I and J)              | 288 |

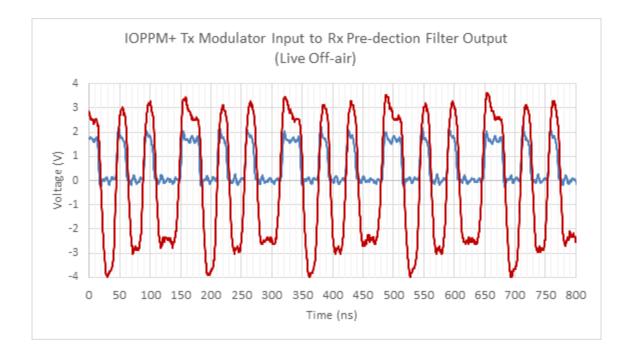

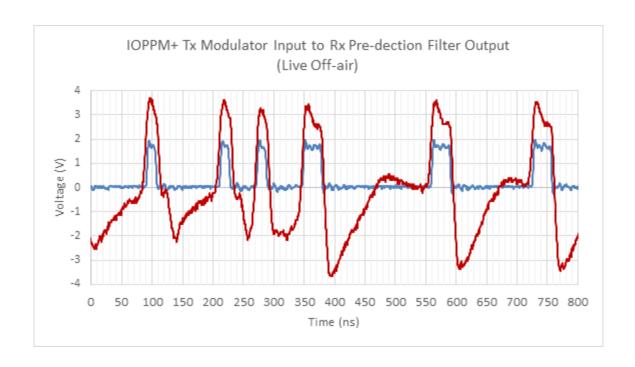

| 7.1.9      | DVB-T2 Transmission (Live Off-Air)                   | 293 |

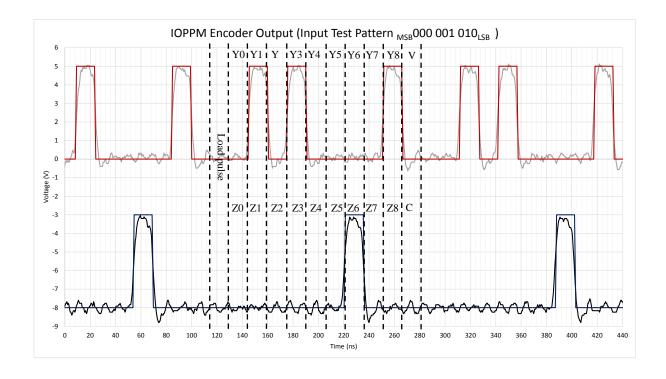

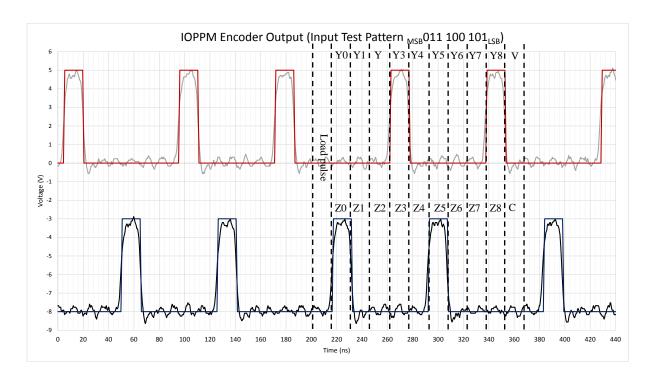

| 7.2 IO     | PPM Encoder and Decoder Verification                 | 295 |

| 7.3 Er     | nd-to-End System Verification                        | 305 |

| 7.3.1      | Reproduction and Errors                              | 307 |

| 7.3.2      | System Latency                                       | 308 |

| 7.3.3      | FSO Channel Signal Blocking and Recovery Time        | 308 |

| 7.4 Co     | onclusions                                           | 308 |

| 8 Discuss  | sion                                                 | 312 |

| 9 Conclu   | sions and Further Work                               | 317 |

| 9.1 Co     | onclusions                                           | 317 |

| 9.2 Fu     | rther Work                                           | 323 |

| 10 Refe    | rences                                               | 325 |

| Appendices |                                                      | 334 |

| Appendix   | x A MATLAB Simulation Code                           | 334 |

| A.1        | MATLAB code for LED intensity simulation             | 334 |

| Appendix   | x B IOPPM Encoder and Decoder Circuits               | 341 |

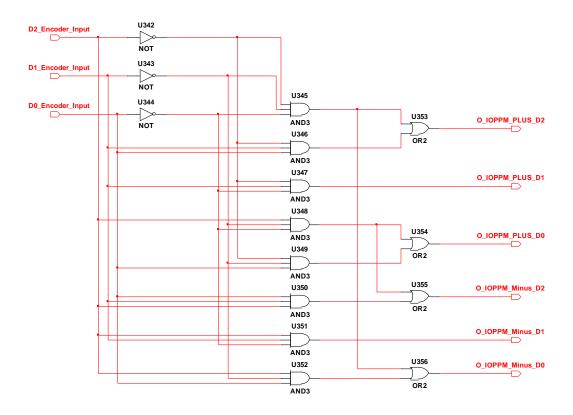

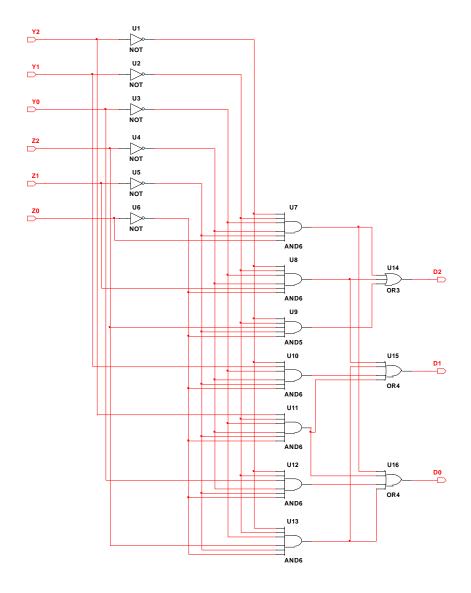

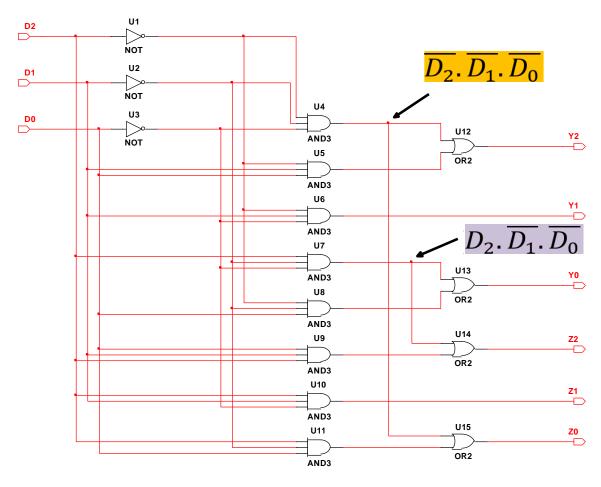

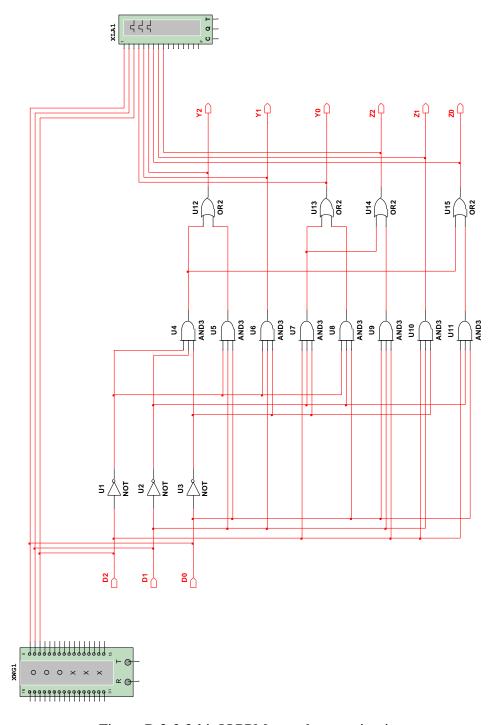

| B.1        | 3-bit IOPPM Encoder Derivation                       | 341 |

| B.2        | 3-bit Integrated IOPPM+ and IOPPM- Encoder Synthesis | 347 |

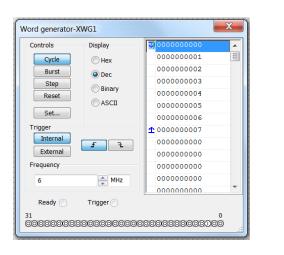

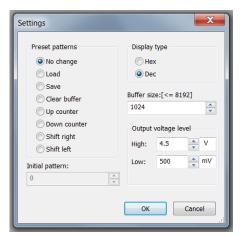

| B.3  | 3-t     | oit IOPPM Encoder Test Circuit and Test Data              | 348      |

|------|---------|-----------------------------------------------------------|----------|

| B.4  | l Mi    | PEG TS to IOPPM Encoding System                           | 352      |

| B.5  | 5 3-ł   | oit IOPPM Decoder Derivation                              | 353      |

| B.6  | 5 3-t   | oit IOPPM Decoder Synthesis                               | 361      |

| B.7  | 7 3-t   | oit IOPPM Decoder Test Circuit and Test Data              | 362      |

| B.8  | 3 Ml    | PEG TS to IOPPM Decoding System                           | 368      |

| B.9  | ) IO    | PPM Encoder and Decoder End-to-End Testing                | 369      |

| Appe | endix C | Silicon Labs Inc NDA and Reprint Permission Documents     | 371      |

| C.1  | Sil     | icon Labs Inc Non-Disclosure Agreement (N-14-)            | 371      |

| C.2  | 2 Sil   | icon Labs Inc Reprint Permission                          | 373      |

| Appe | endix D | Silicon Labs EVB                                          | 381      |

| D.1  | Ov.     | erview                                                    | 381      |

| Appe | endix E | Bush DH2636 DVB-T/T2 STB                                  | 386      |

| E.1  | Ov      | erview                                                    | 386      |

| E.2  | . Pro   | oduct Specification                                       | 390      |

| Appe | endix F | MPEG TS Source and Sink ICs                               | 391      |

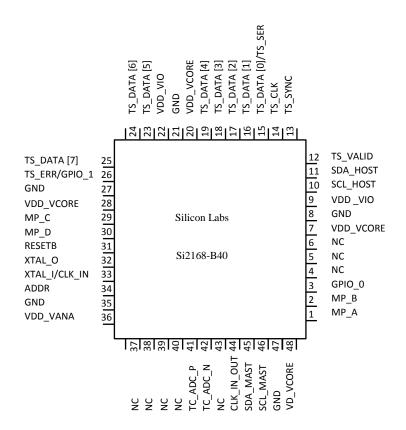

| F.1  | Sil     | icon Labs Si2168-B40 DVB-T2/T/C digital TV demodulator IC | pinout . |

|      | •••     |                                                           | 391      |

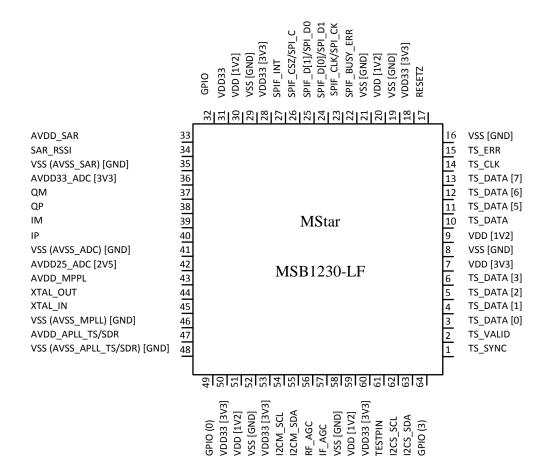

| F.2  | MS      | Star MSB1230-LF DVB-T2/T digital TV demodulator IC pinou  | t392     |

| Appe | endix G | MPEG TS Characterisation Test Setup                       | 393      |

| G.1  | Sil     | icon Labs Si2168 Test Setup                               | 393      |

| G.2      | MStar MSB1230 Test Setup                                      | 395 |

|----------|---------------------------------------------------------------|-----|

| Appendix | H Bypass Board Configuration                                  | 397 |

| H.1      | MSB1230 and MB J3 connector transport streams pin assignments | 397 |

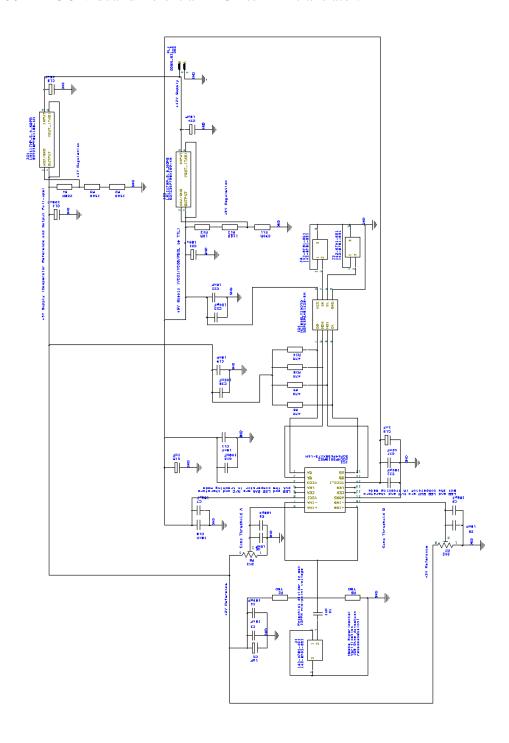

| H.2      | Bypass Board MPEG TS Switching Schematic                      | 398 |

| Appendix | I LED Characterisation Setup                                  | 399 |

| I.1      | Frequency Response and Bandwidth Test Setup                   | 399 |

| I.1      | Received Power Test Setup                                     | 401 |

| Appendix | J Multisim Circuits                                           | 402 |

| J.1      | 10-bit MPEG TS Buffer Register Circuit                        | 402 |

| J.2      | 10-bit PISO Circuit                                           | 403 |

| J.3      | 10-bit SIPO Circuit – Serial shift                            | 404 |

| J.4      | 10-bit SIPO Circuit – Parallel load                           | 405 |

| Appendix | K Altera Quartus II 66 MHz PLL Design                         | 406 |

| Appendix | L System Schematics, BOMs and Layouts                         | 412 |

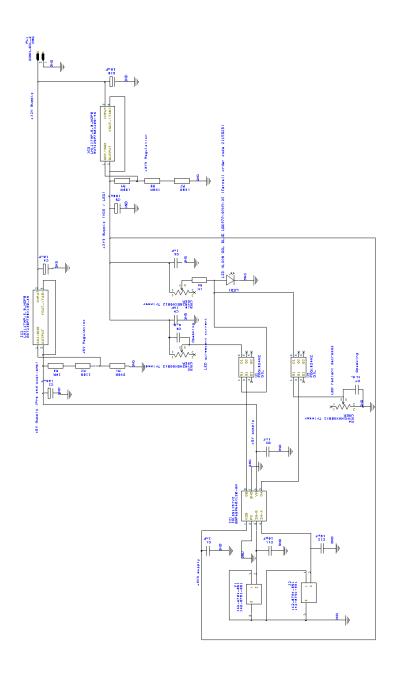

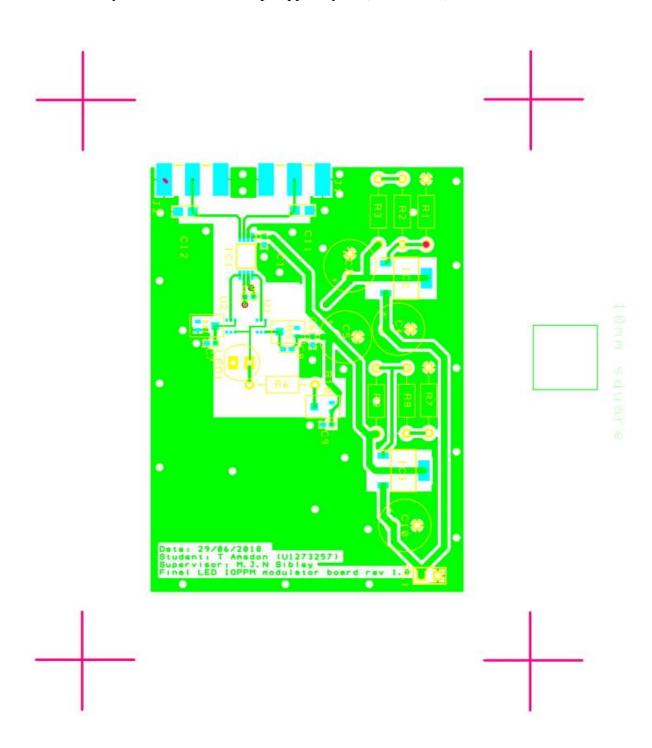

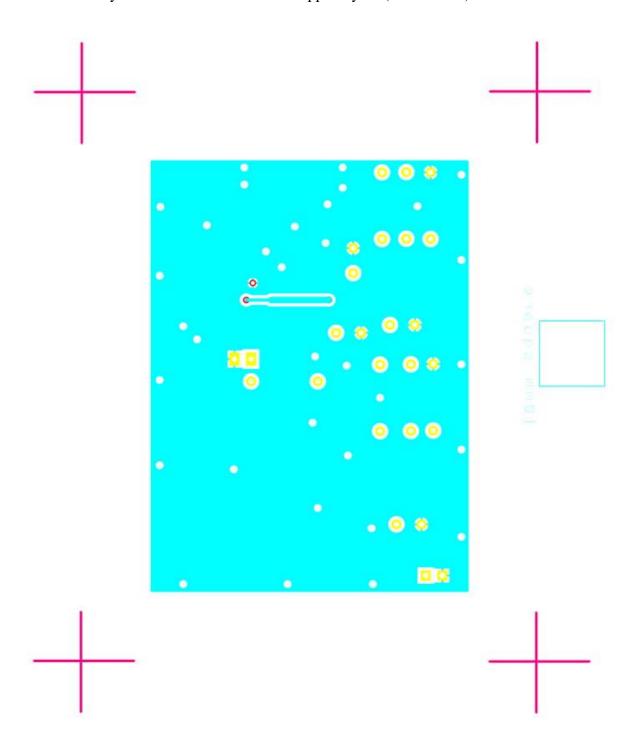

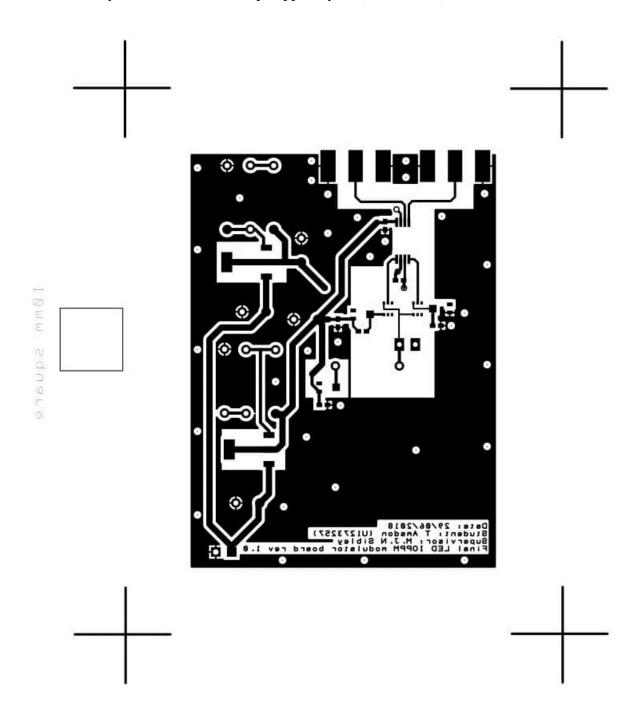

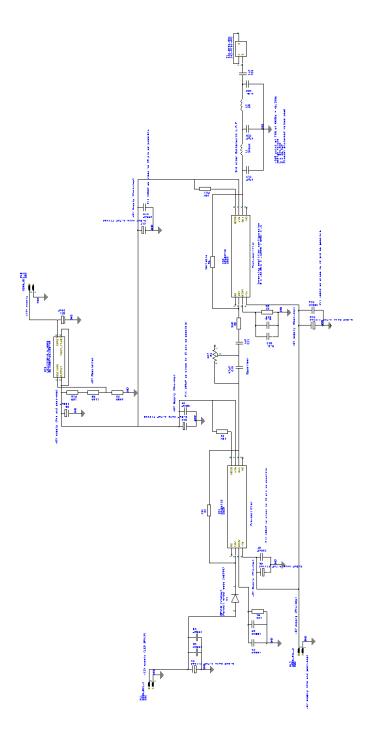

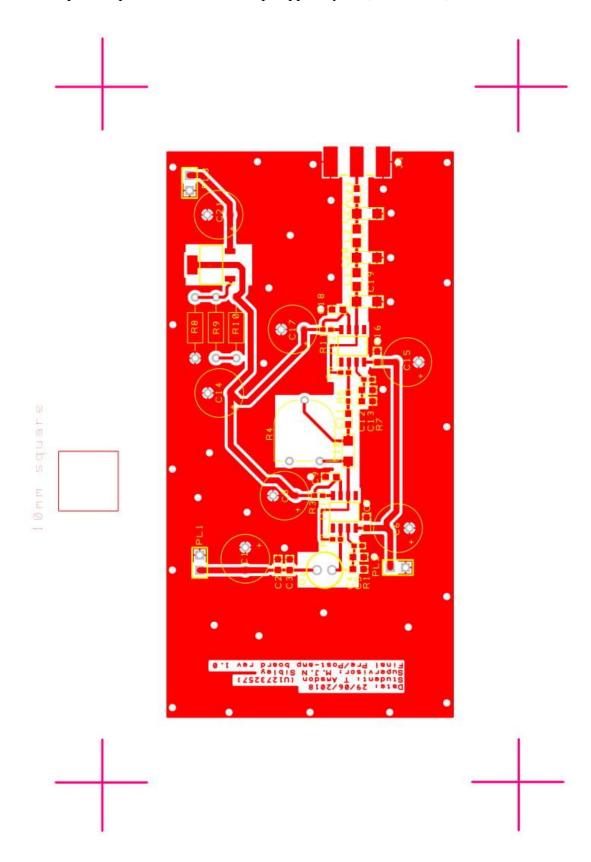

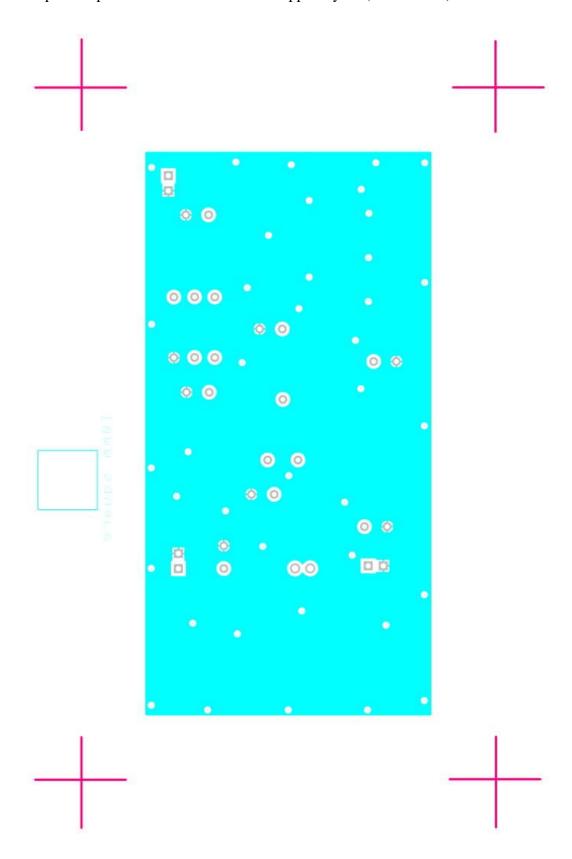

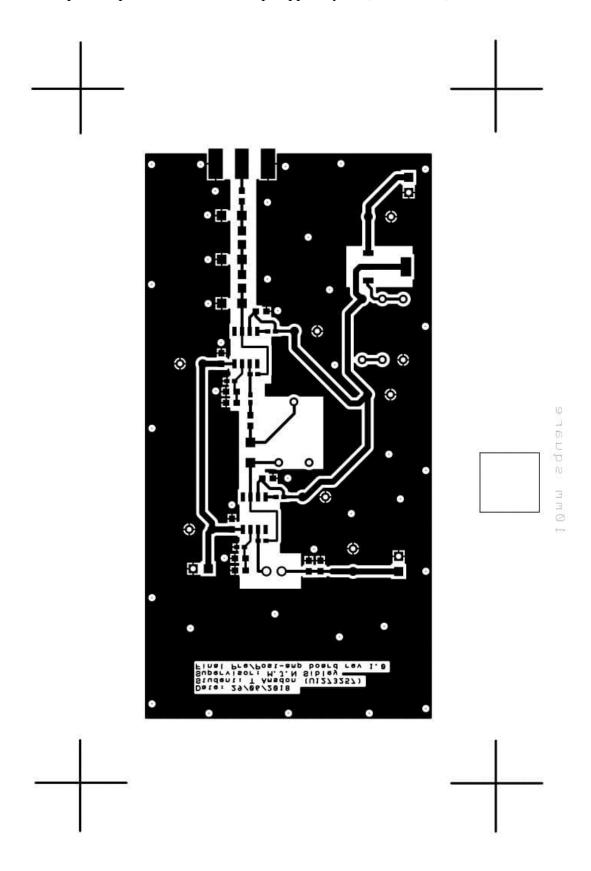

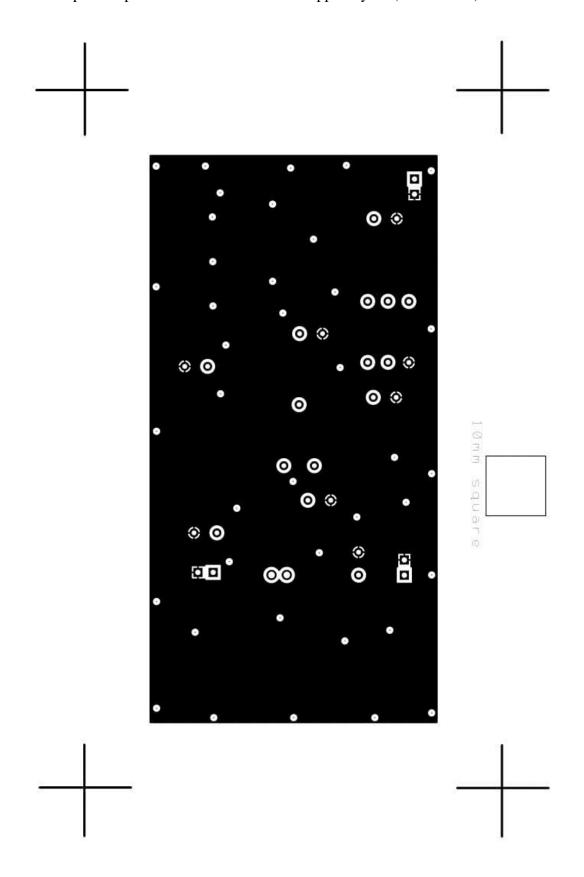

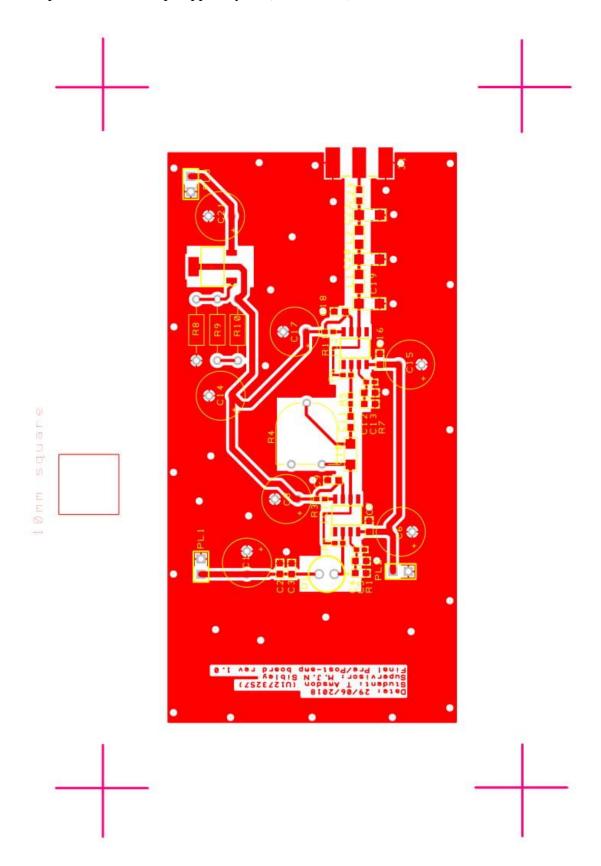

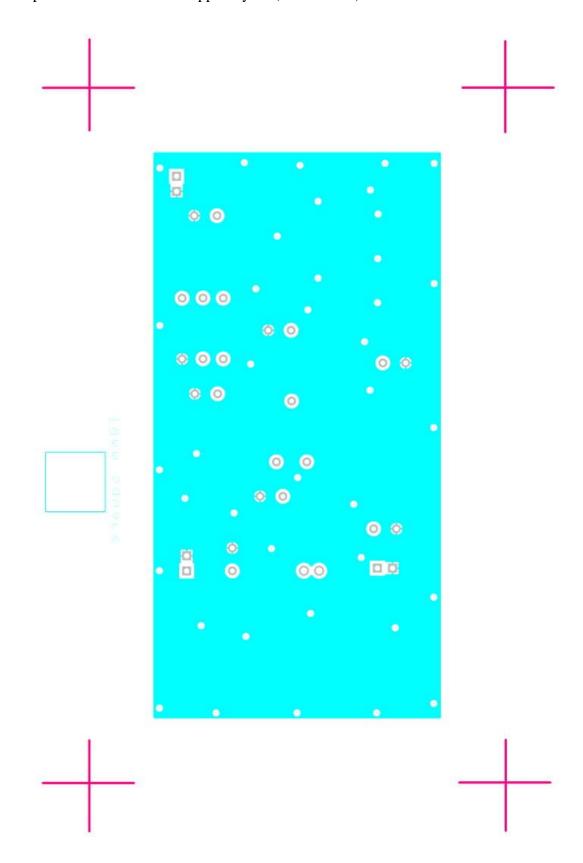

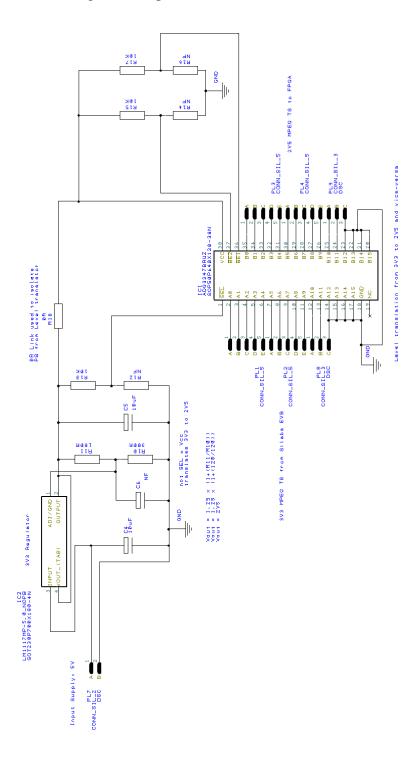

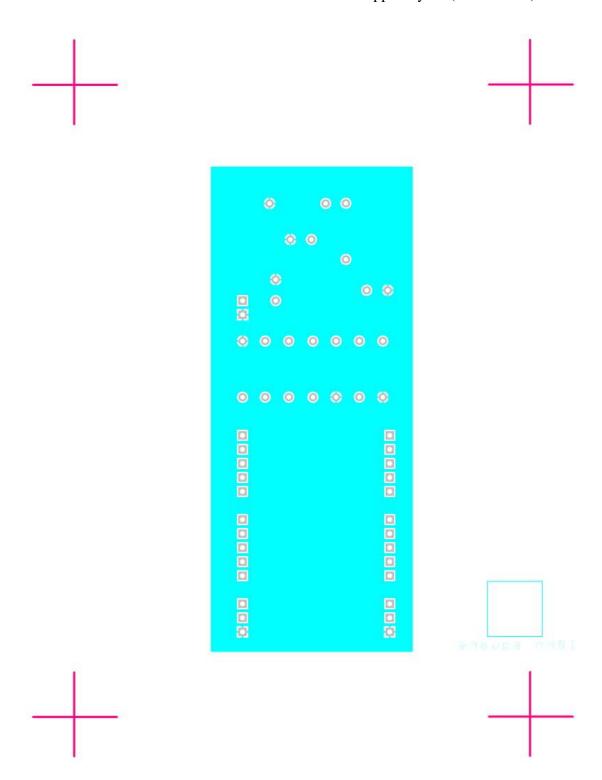

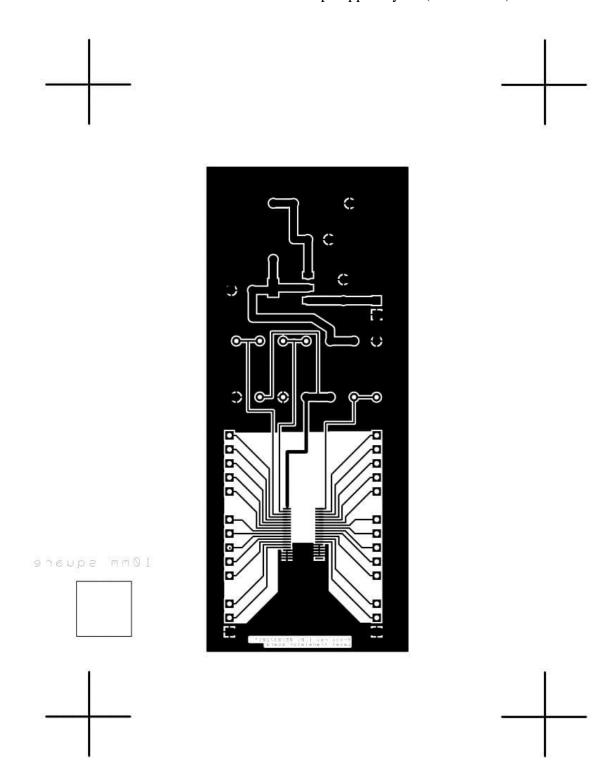

| L.1      | LED intensity modulator (Tx) circuit                          | 412 |

| L.2      | Pre and post-amplification circuit (Rx)                       | 418 |

| L.3      | Window Comparator circuit (Rx)                                | 424 |

| L.4      | Si2168-B40 to FPGA TTL level translator                       | 430 |

# **Table of Figures**

| Figure 1-1 VLC broadcast (MPEG TS) distribution system (author generated image)  | 2     |

|----------------------------------------------------------------------------------|-------|

| Figure 1-2 European: Samsung LE40A656 40" 1080p LCD HDTV                         | 4     |

| Figure 1-3 North America: Samsung LN-T5265F 52" 1080p LCD HDTV                   | 5     |

| Figure 1-4 Simplified DVB system architecture (author generated image)           | 10    |

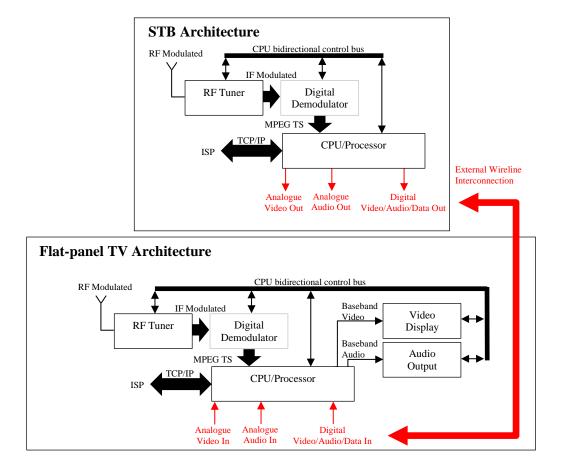

| Figure 1-5 Simplified block diagram of current DVB STB and TV architectures      | 13    |

| Figure 1-6 Conceptual block diagram of a broadcast (MPEG TS) and internet (TCP   | '/IP) |

| wireless distribution system (author generated image)                            | 15    |

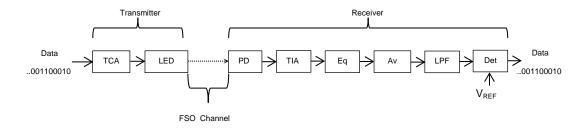

| Figure 1-7 Block diagram of a OWC system (author generated image)                | 20    |

| Figure 1-8 Gimbaled LED transmitter and target TV fitted with a PD (room side vi | iew)  |

| (author generated image)                                                         | 24    |

| Figure 1-9 Gimbaled LED transmitter and target TV fitted with a PD (room plan vi | ew)   |

| (author generated image)                                                         | 25    |

| Figure 1-10 Proof-of-concept block diagram of a VLC broadcast (MPEG              | TS)   |

| distribution system (author generated image)                                     | 26    |

| Figure 2-1 DVB transmitter (author generated image)                              | 32    |

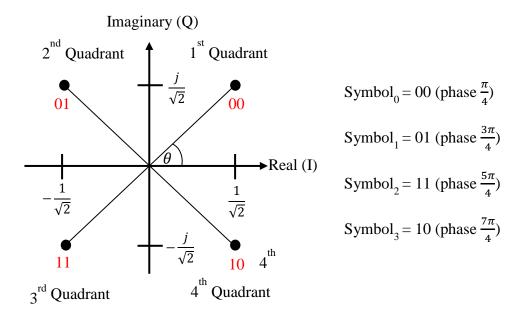

| Figure 2-2 QPSK constellation (author generated image)                           | 34    |

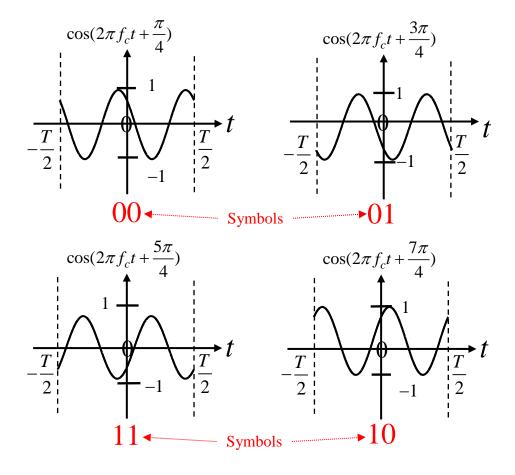

| Figure 2-3 Constellation points mapped to cosine (author generated image)        | 36    |

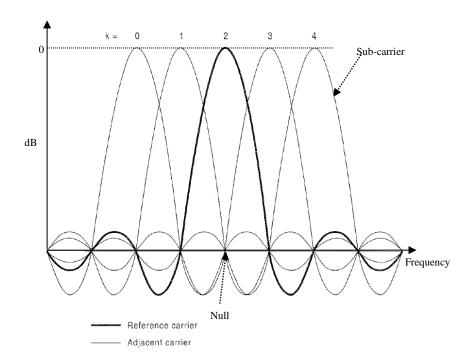

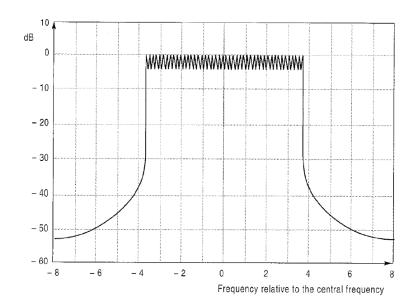

| Figure 2-4 COFDM sub-carriers (Benoit, 1997)                                     | 38    |

| Figure 2-5 DVB-T transmission spectrum (Benoit, 1997)                            | 39    |

| Figure 2-6 DVB MPEG encoding path (ISO, 2010)                                    | 40    |

| Figure 2-7 DVB multiplexing and headers (author generated image)                 | 42    |

| Figure 2-8 MPEG TS Packet (Fischer, 2010)                                        | 43    |

| Figure 2-9 DVB receiver (author generated image)                                 | 43    |

| Figure 2-10 DVB MPEG decoding path (author generated image)                          |

|--------------------------------------------------------------------------------------|

| Figure 2-11 DVB-T/T2 receiver MPEG TS (author generated image)48                     |

| Figure 2-12 MPEG TS parallel mode (CLK non-inverted)                                 |

| Figure 2-13 MPEG TS serial mode (CLK non-inverted)                                   |

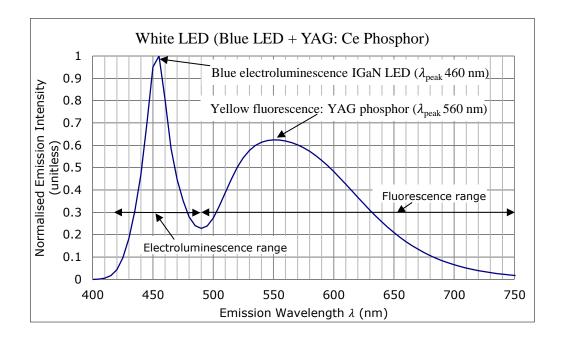

| Figure 2-14 Emission spectrum of an InGaN blue LED and YAG:Ce phosphor               |

| (Schubert, 2006)                                                                     |

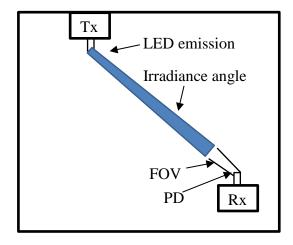

| Figure 2-15 Directed LOS transmission                                                |

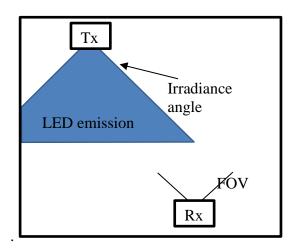

| Figure 2-16 Nondirected LOS transmission                                             |

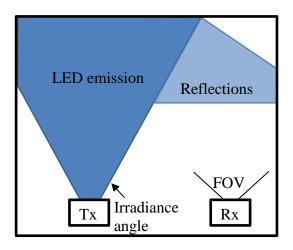

| Figure 2-17 Diffuse transmission                                                     |

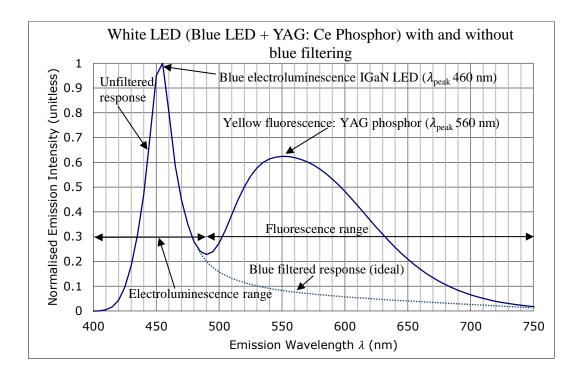

| Figure 2-18 Emission spectrum of an InGaN blue LED and YAG:Ce phosphor with and      |

| without blue filtering (Schubert, 2006)                                              |

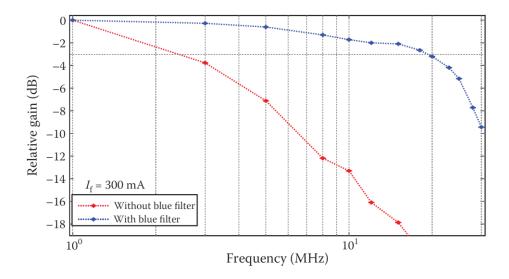

| Figure 2-19 White LEDs normalised frequency response with and without blue filtering |

| 67                                                                                   |

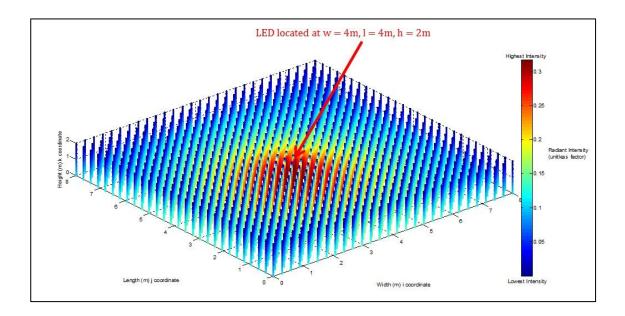

| Figure 2-20 Single LEDs Lambertian radiant intensity70                               |

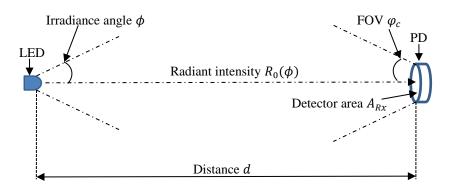

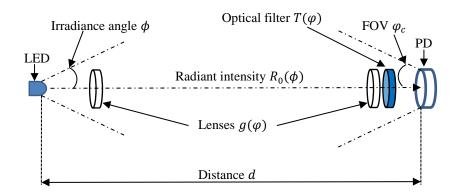

| Figure 2-21 Spatial components of directed LOS transmission71                        |

| Figure 2-22 Directed LOS transmission with concentrators and optical filter72        |

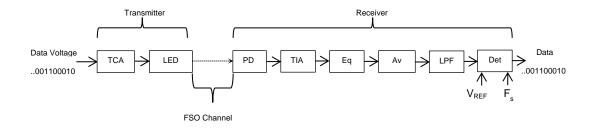

| Figure 2-23 Block diagram of a digital OWC system (author generated image)75         |

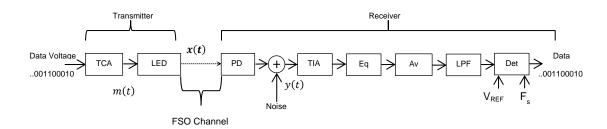

| Figure 2-24 Analogue signal processing blocks of a SISO OWC system (including noise  |

| source) (author generated image)                                                     |

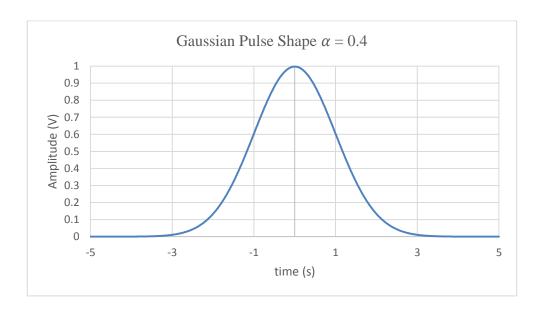

| Figure 2-25 Gaussian impulse response (author generated image)                       |

| Figure 2-26 Sinc pulse response (author generated image)                             |

| Figure 2-27 Rectangular pulse spectrum (author generated image)                      |

| Figure 2-28 On/off FET switch topologies (Z. e. Ghassemlooy et al., 2013)81          |

| Figure 2-29 LED electrical model (O'Brien et al., 2008)                              |

| Figure 2-30 Transimpedance amplifier circuit (Horowitz, 2015)                        |

| Figure 2-31 Passive equaliser (Minh et al., 2009)                                 | 89         |

|-----------------------------------------------------------------------------------|------------|

| Figure 2-32 Voltage amplifier circuit (Horowitz, 2015)                            | 90         |

| Figure 2-33 3 <sup>rd</sup> order Butterworth LPF                                 | 91         |

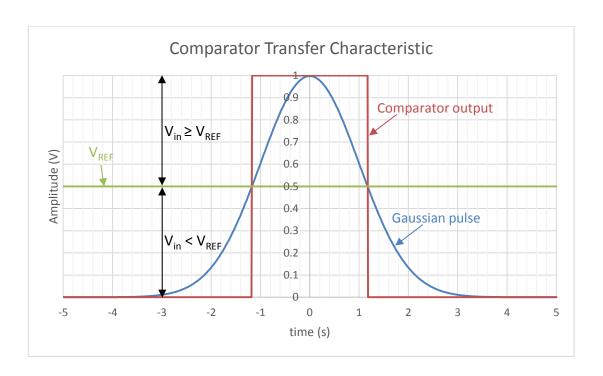

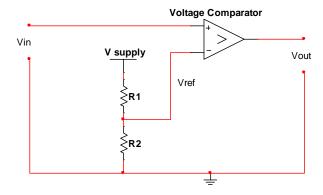

| Figure 2-34 Comparator transfer characteristic                                    | 92         |

| Figure 2-35 Non-inverting voltage comparator circuit (Horowitz, 2015)             | 92         |

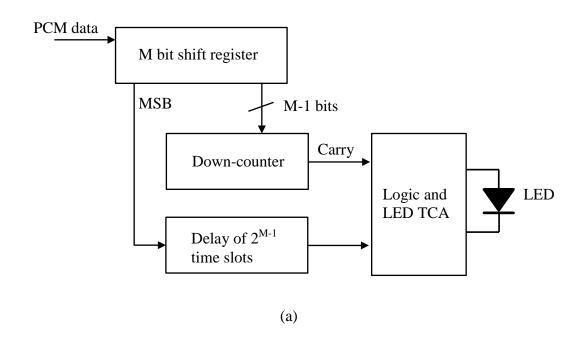

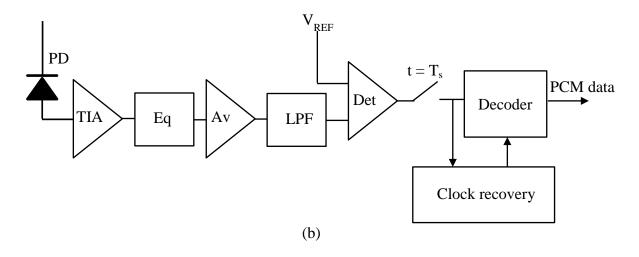

| Figure 2-36 Block diagram of an OPPM transmitter and receiver (M.J.N. Sib         | ley, 2010) |

|                                                                                   | 96         |

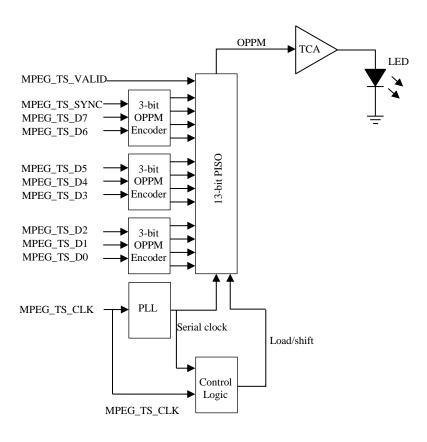

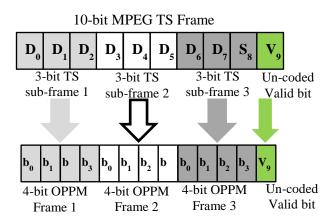

| Figure 2-37 OPPM MPEG TS encoder and transmitter                                  | 100        |

| Figure 2-38 10-bit MPEG TS to 4-bit sub-frame OPPM                                | 102        |

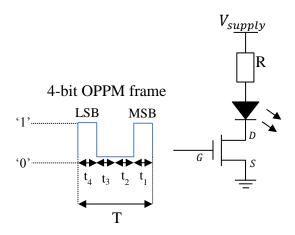

| Figure 2-39 OPPM LED driver                                                       | 103        |

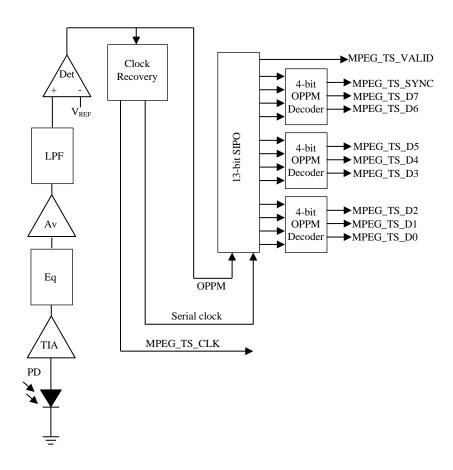

| Figure 2-40 OPPM MPEG TS receiver and decoder                                     | 103        |

| Figure 3-1 VLC MPEG TS encoder and decoder blocks (author generated image         | ge) 109    |

| Figure 3-2 IOPPM composite signal (author generated image)                        | 110        |

| Figure 3-3 IOPPM MPEG TS encoder/transmitter                                      | 117        |

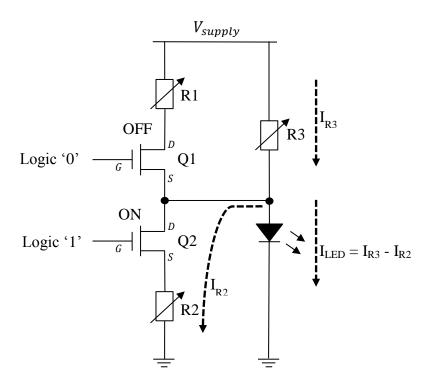

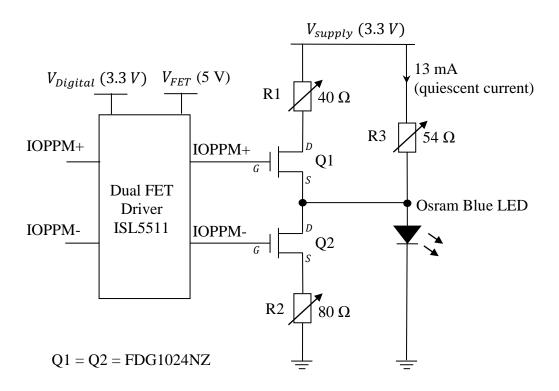

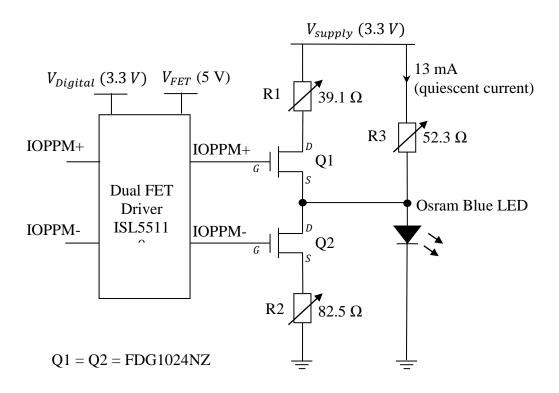

| Figure 3-4 IOPPM LED composite driver (increasing intensity)                      | 119        |

| Figure 3-5 IOPPM LED composite driver (decreasing intensity)                      | 119        |

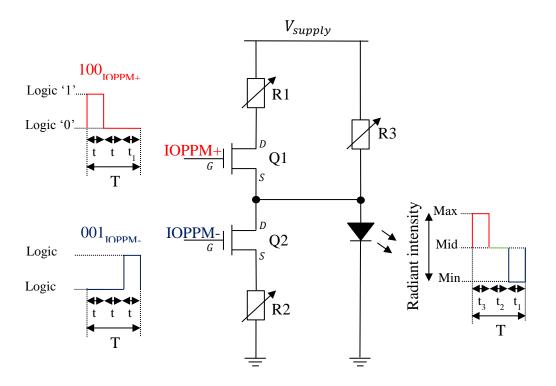

| Figure 3-6 IOPPM LED composite driver                                             | 120        |

| Figure 3-7 IOPPM MPEG TS receiver and decoder (single LED)                        | 122        |

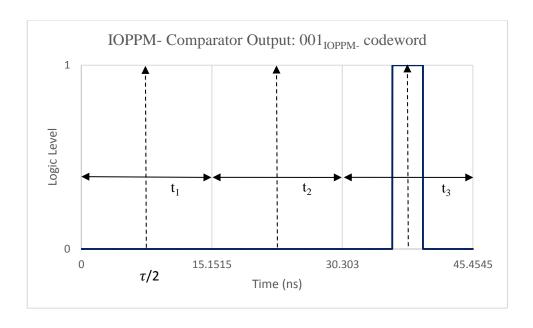

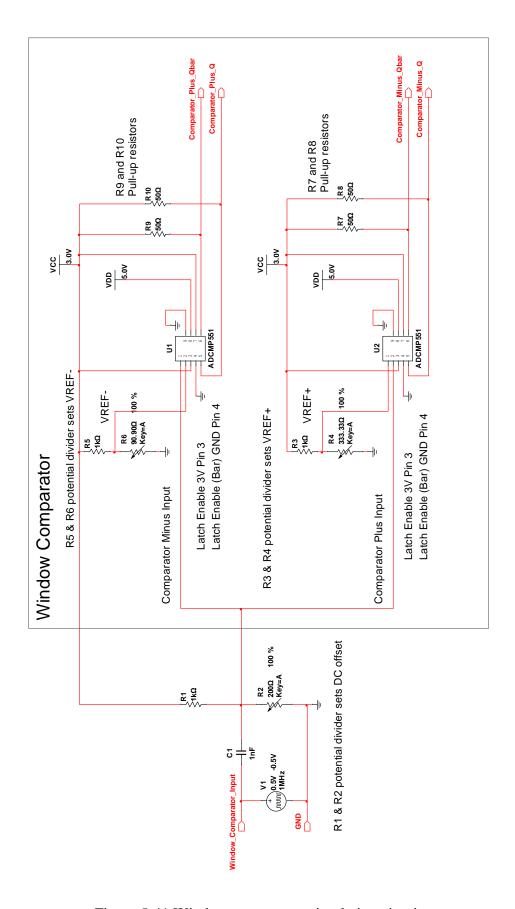

| Figure 3-8 Window voltage comparator                                              | 124        |

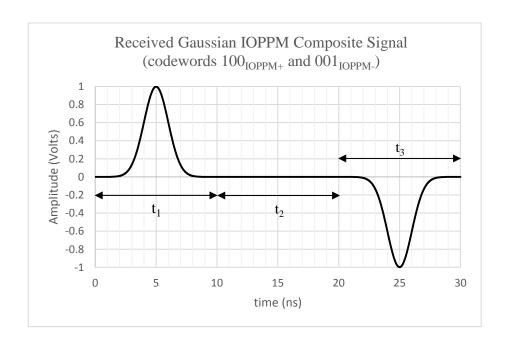

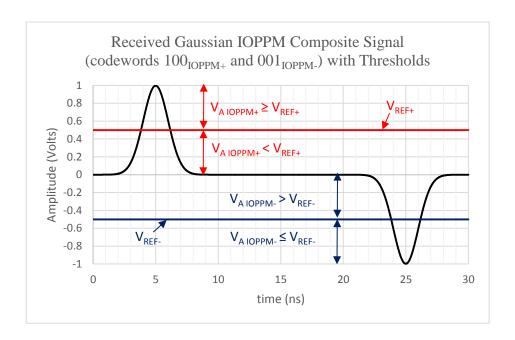

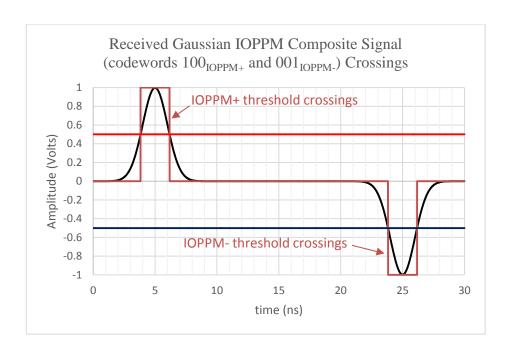

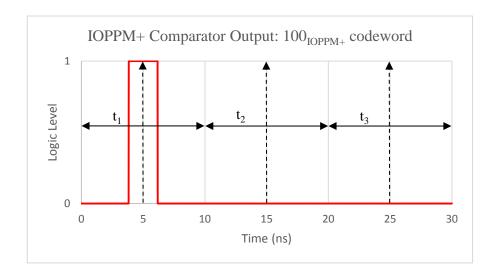

| Figure 3-9 IOPPM composite signal for codewords $100_{IOPPM+}$ and $001_{IOPPM-}$ | 125        |

| Figure 3-10 IOPPM composite signal detection thresholds                           | 126        |

| Figure 3-11 IOPPM composite signal threshold crossings                            | 127        |

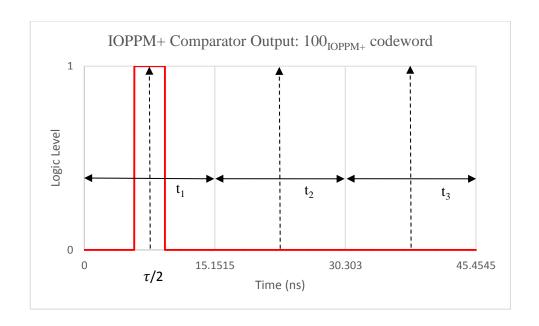

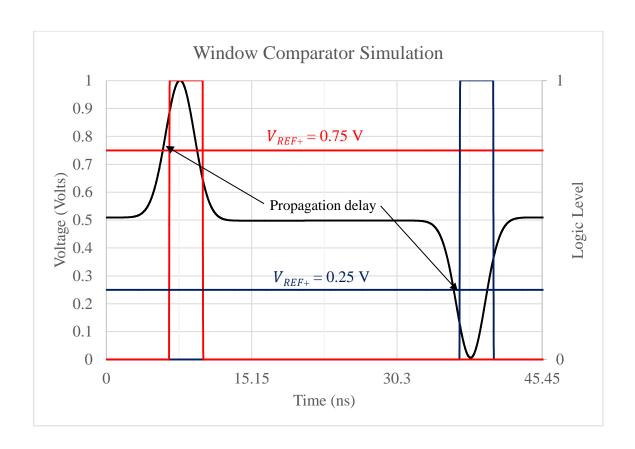

| Figure 3-12 IOPPM+ comparator digital output                                      | 128        |

| Figure 3-13 IOPPM- comparator digital output                                      | 128        |

| Figure 3-14 IOPPM MPEG TS encoder/transmitter (dual LEDs)                         | 130        |

| Figure 3-15 IOPPM LED driver (dual LED)                                          | 132     |

|----------------------------------------------------------------------------------|---------|

| Figure 3-16 IOPPM MPEG TS receiver and decoder (dual LED)                        | 133     |

| Figure 4-1 VLC MPEG TS source and sink devices (author generated image)          | 138     |

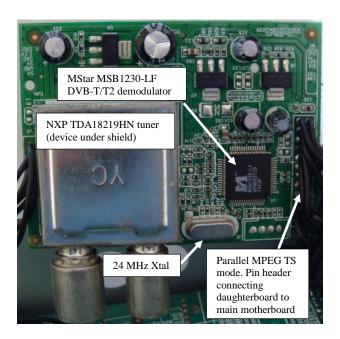

| Figure 4-2 Silicon Labs EVB core devices (author generated image)                | 139     |

| Figure 4-3 EVB MPEG TS clock (6.008 MHz, 50% duty cycle)                         | 142     |

| Figure 4-4 EVB MPEG TS synchronisation (author generated image)                  | 143     |

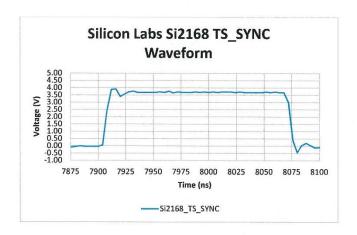

| Figure 4-5 EVB MPEG TS MPEG TS synchronisation (single pulse)                    | 144     |

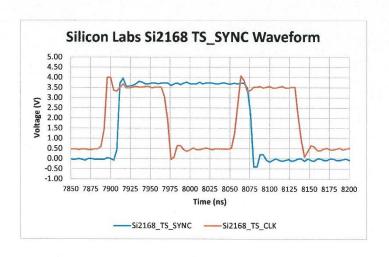

| Figure 4-6 EVB MPEG TS synchronisation (single pulse) and clock                  | 145     |

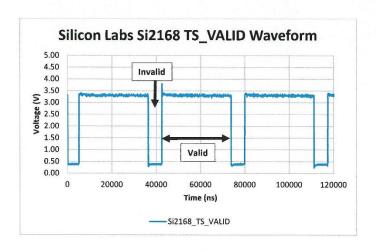

| Figure 4-7 EVB MPEG TS valid (author generated image)                            | 146     |

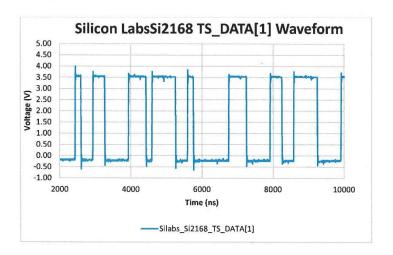

| Figure 4-8 EVB MPEG TS data (Data line D1) (author generated image)              | 147     |

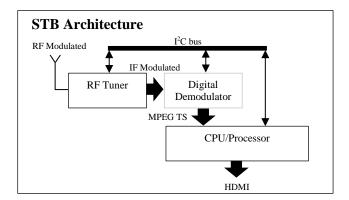

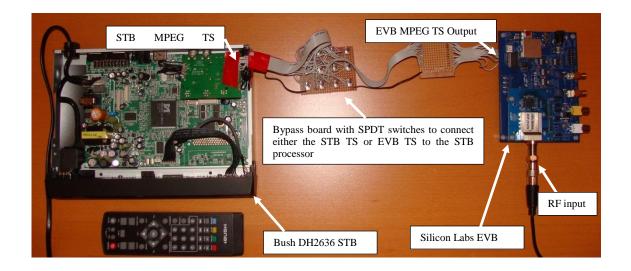

| Figure 4-9 Bush DH2636 STB core blocks (author generated image)                  | 149     |

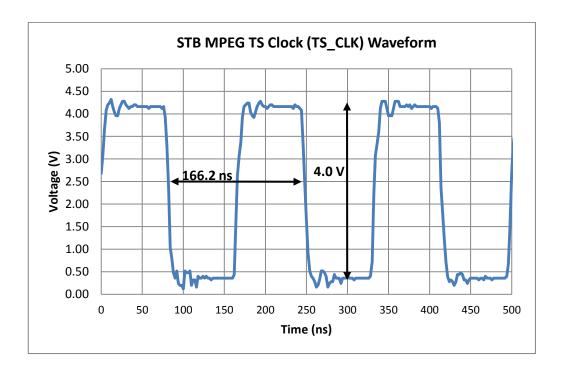

| Figure 4-10 STB MPEG TS clock (6.017 MHz, 50% duty cycle)                        | 151     |

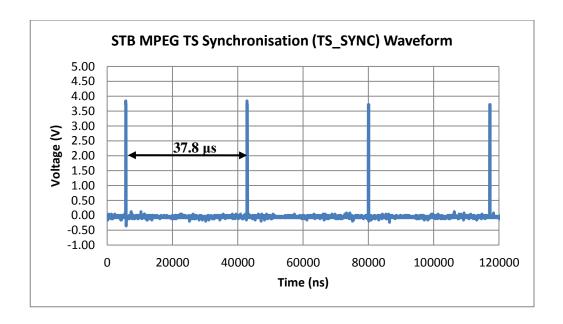

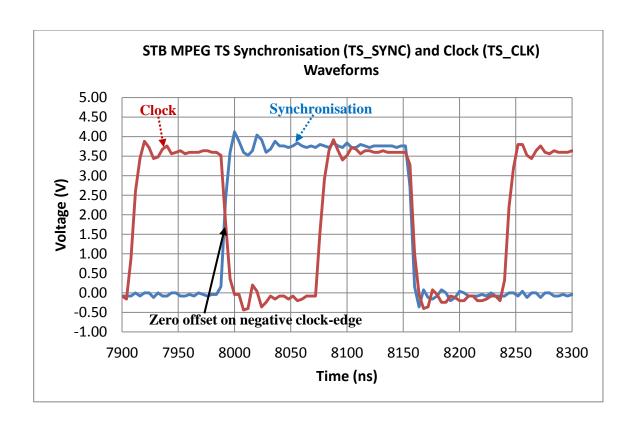

| Figure 4-11 STB MPEG TS synchronisation (author generated image)                 | 152     |

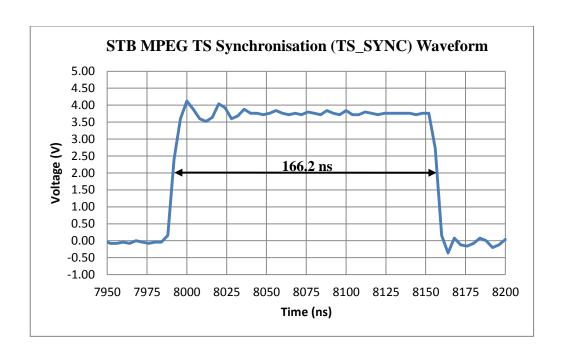

| Figure 4-12 STB MPEG TS synchronisation (single pulse) (author generated imag    | ge) 153 |

| Figure 4-13 STB MPEG TS synchronisation (single pulse) and clock                 | 154     |

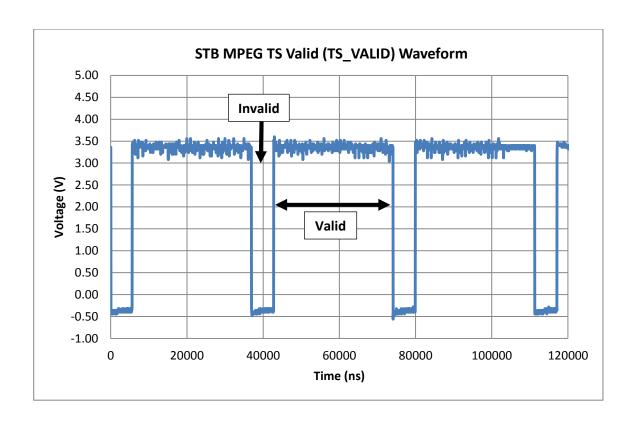

| Figure 4-14 STB MPEG TS valid (author generated image)                           | 155     |

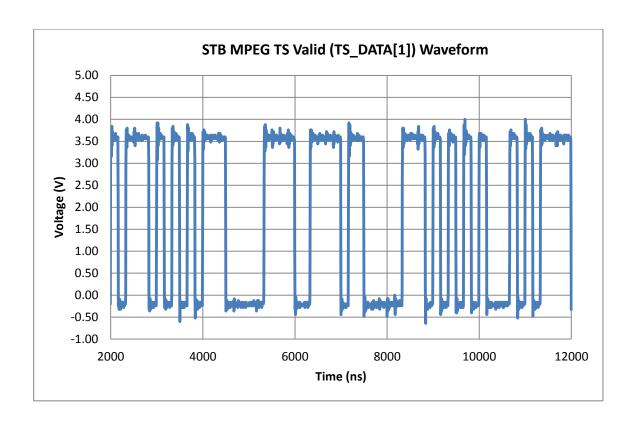

| Figure 4-15 STB MPEG TS DATA (Data line D1) (author generated image)             | 156     |

| Figure 4-16 Si2168 MPEG TS to MSD7853L physical test setup                       | 159     |

| Figure 4-17 Data source and sink end-to-end test configuration (author generated | image)  |

|                                                                                  | 160     |

| Figure 4-18 Osram White LED (author generated image)                             | 164     |

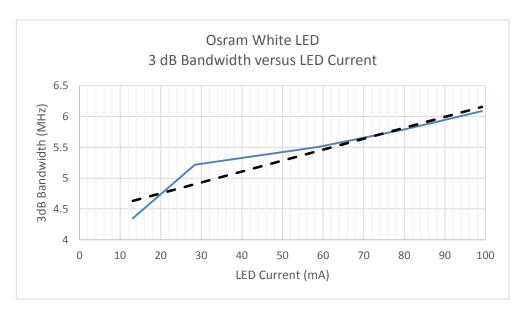

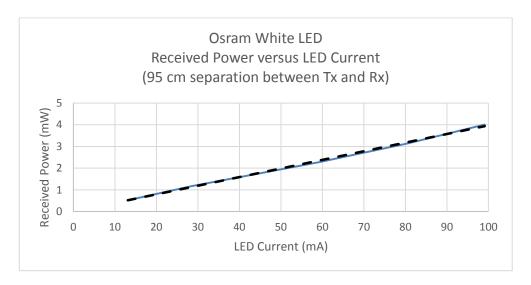

| Figure 4-19 White LED normalised frequency response (DC to 200 MHz)              | 165     |

| Figure 4-20 White LED normalised frequency response (DC to 10 MHz)               | 166     |

| Figure 4-21 White LED 3 dB bandwidth versus forward bias current                 | 166     |

| Figure 4-22 White LED received power versus forward bias current                 | 168     |

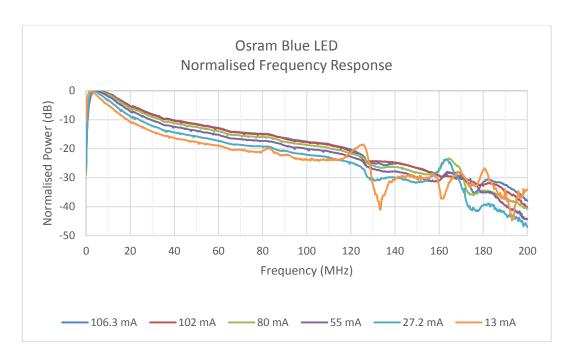

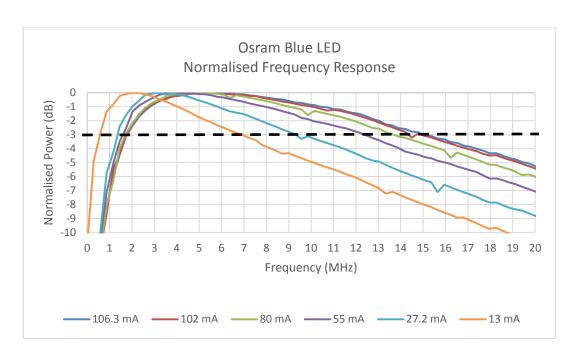

| Figure 4-23 Blue LED normalised frequency response (DC to 200 MHz)170                  |

|----------------------------------------------------------------------------------------|

| Figure 4-24 Blue LED normalised frequency response (DC to 20 MHz)171                   |

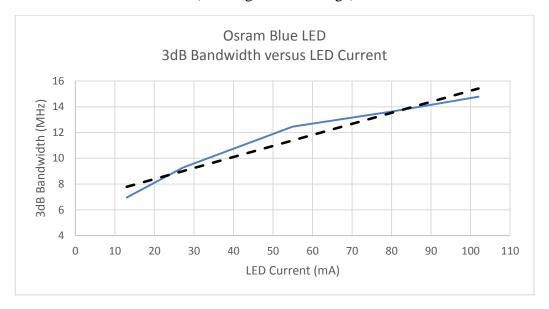

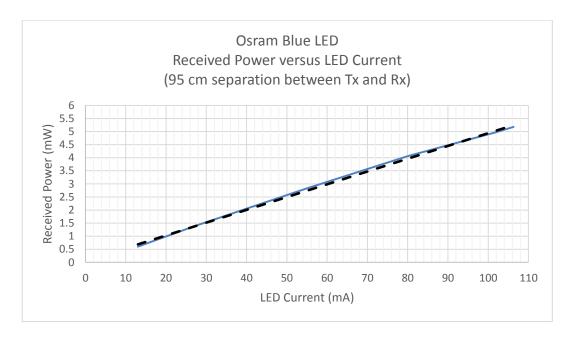

| Figure 4-25 Blue LED 3 dB bandwidth versus forward bias current                        |

| Figure 4-26 Blue LED received power versus forward bias current                        |

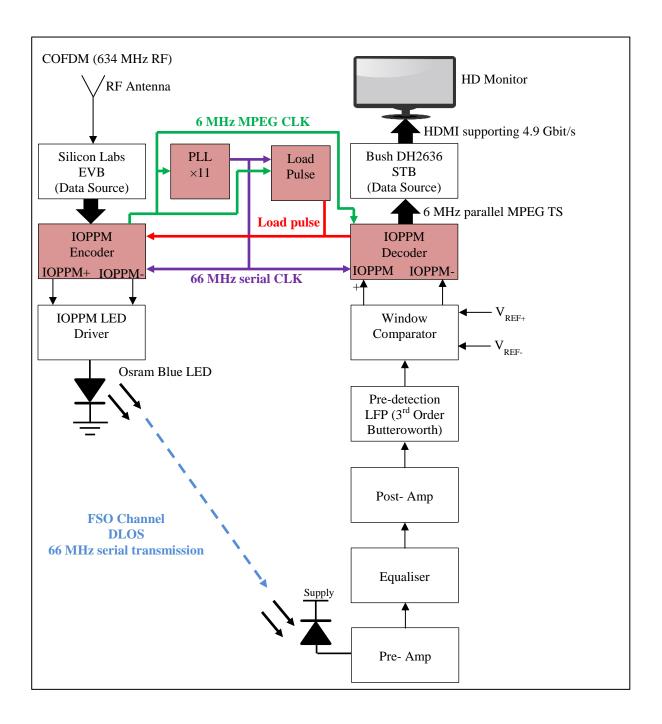

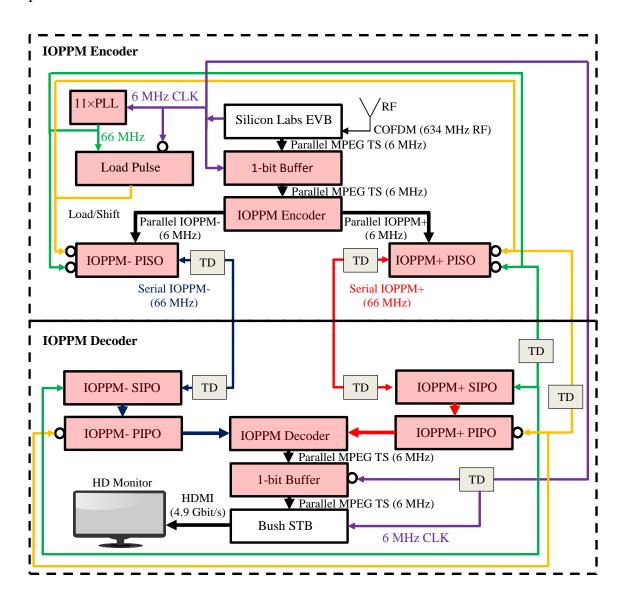

| Figure 5-1 Top-level block diagram of proof-of-concept system                          |

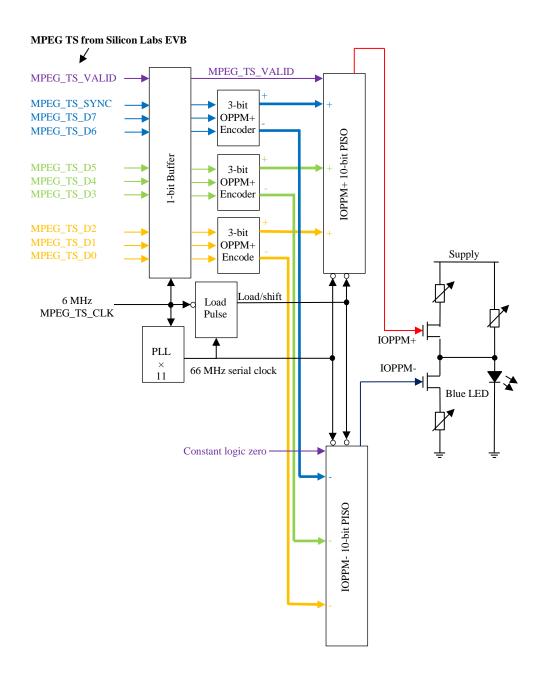

| Figure 5-2 Detailed IOPPM MPEG TS encoder/transmitter architecture (Single LED)        |

|                                                                                        |

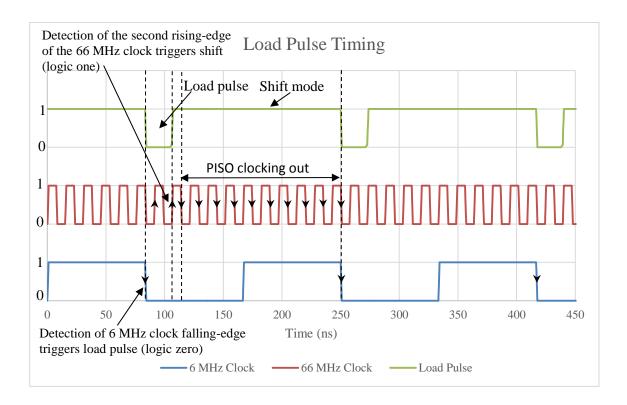

| Figure 5-3 PISO load pulse timing relative to the 6 MHz and 66 MHz clocks181           |

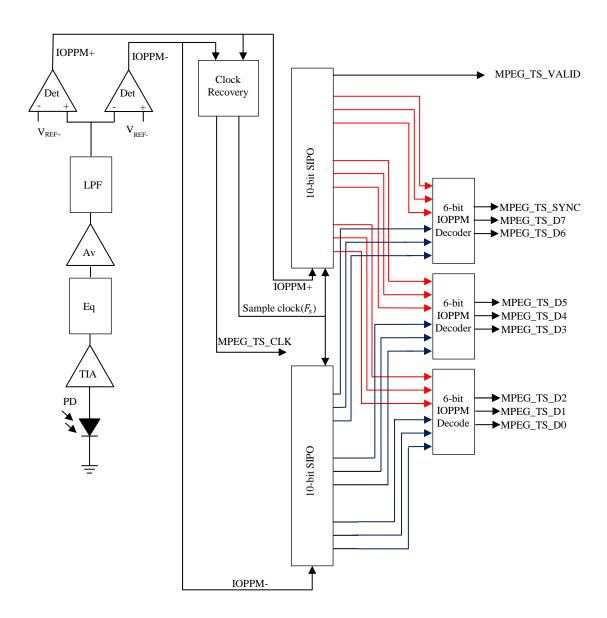

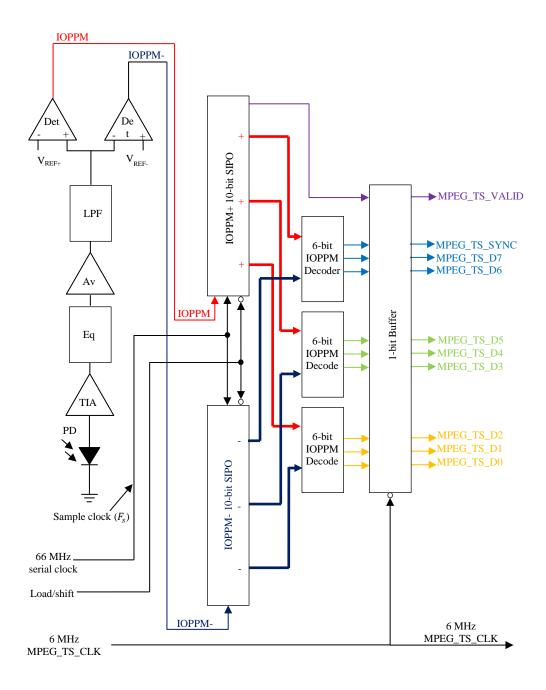

| Figure 5-4 Detailed IOPPM MPEG TS receiver/decoder architecture (Single LED) 182       |

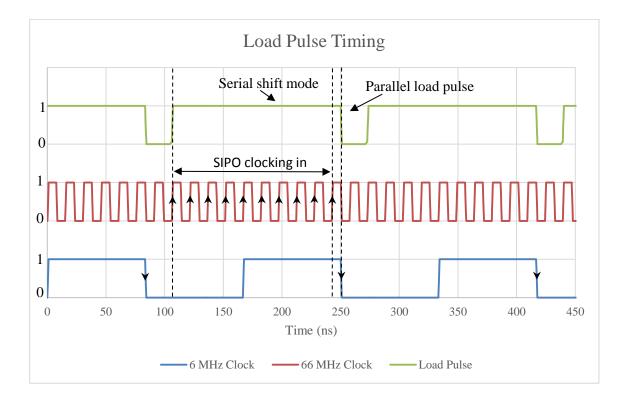

| Figure 5-5 SIPO parallel load pulse timing relative to the 6 MHz and 66 MHz clocks 184 |

| Figure 5-6 3-bit IOPPM encoder                                                         |

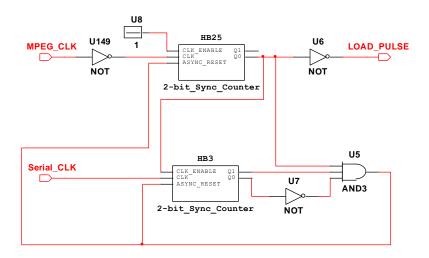

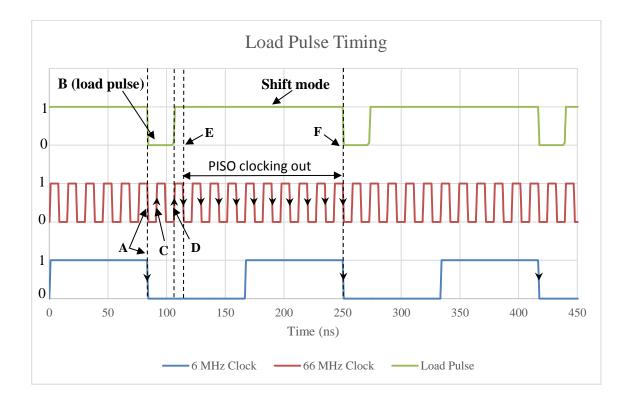

| Figure 5-7 Load pulse generator                                                        |

| Figure 5-8 PISO load pulse timing relative to the 6 MHz and 66 MHz clocks189           |

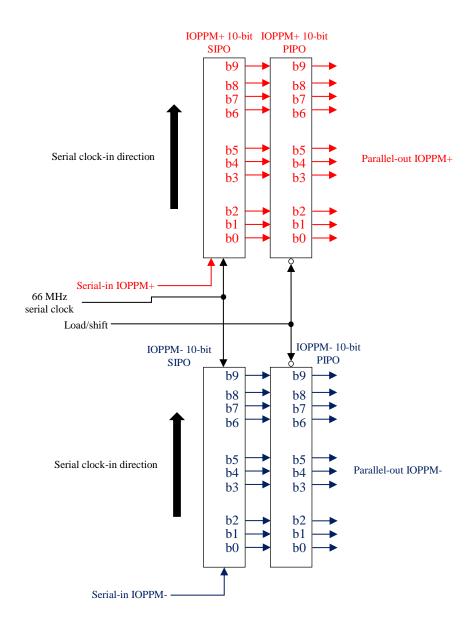

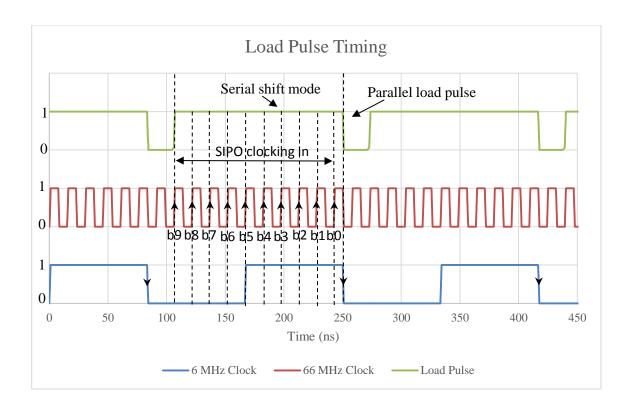

| Figure 5-9 SIPO and PIPO block diagram                                                 |

| Figure 5-10 SIPO/PIPO parallel load pulse timing relative to the 6 MHz and 66 MHz      |

| clocks                                                                                 |

| Figure 5-11 6-bit IOPPM decoder                                                        |

| Figure 5-12 IOPPM composite LED driver                                                 |

| Figure 5-13 IOPPM LED composite driver (codeword versus driver current)197             |

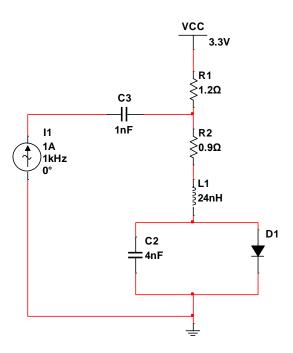

| Figure 5-14 Osram Blue LED model                                                       |

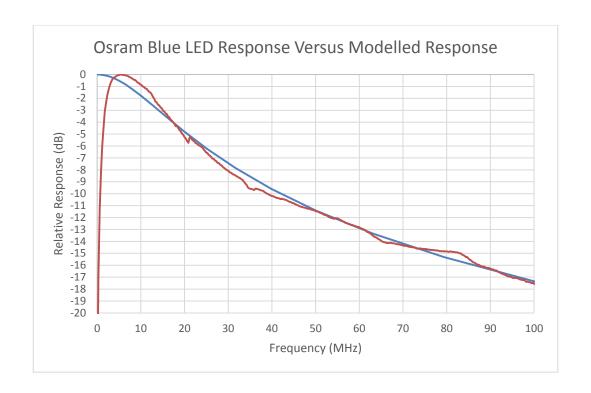

| Figure 5-15 Osram Blue LED measured response versus modelled response199               |

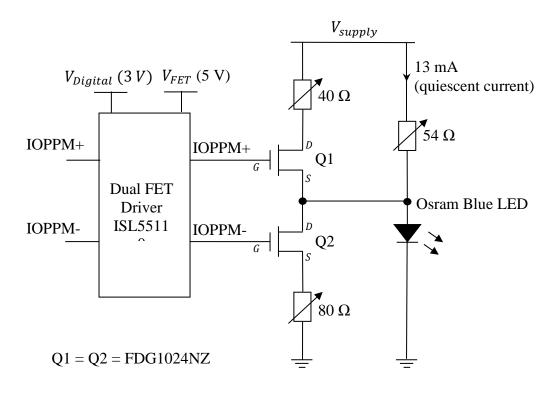

| Figure 5-16 IOPPM composite LED driver circuit and component values200                 |

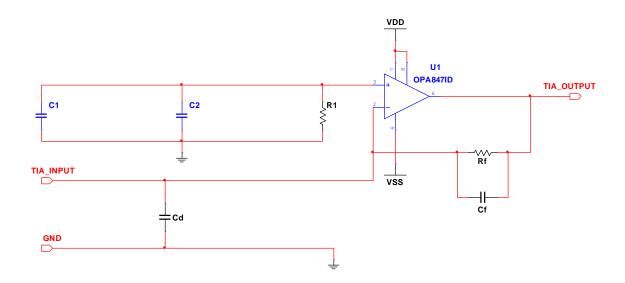

| Figure 5-17 TI OPA847 op-amp transimpedance amplifier                                  |

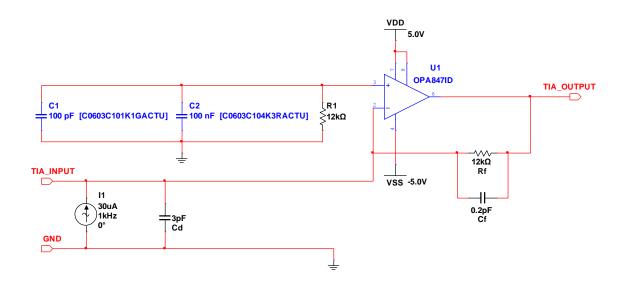

| Figure 5-18 TI OPA847 op-amp transimpedance amplifier circuit (component values)       |

| 203                                                                                    |

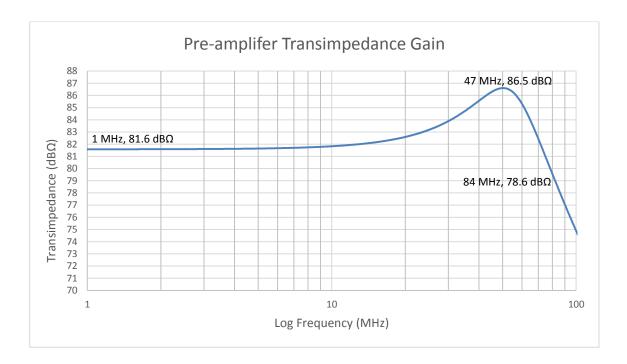

| Figure 5-19 TI OPA847 op-amp transimpedance amplifier gain response                                 |

|-----------------------------------------------------------------------------------------------------|

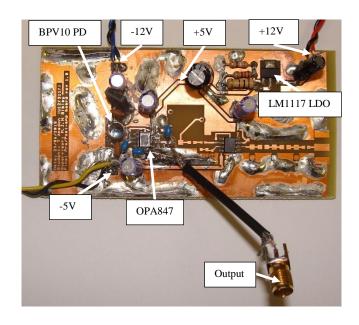

| Figure 5-20 BPV10 PIN PD and TI OPA847 pre-amplifier prototype                                      |

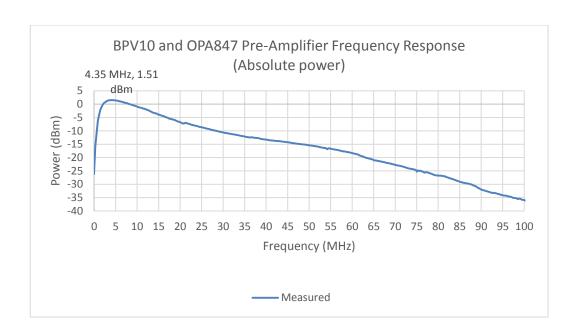

| Figure 5-21 BPV10 PIN PD and TI OPA847 op-amp frequency response206                                 |

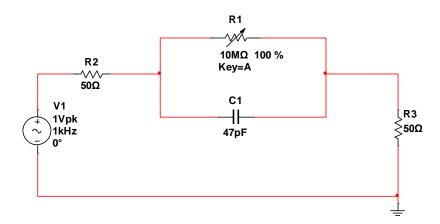

| Figure 5-22 2 <sup>nd</sup> order RC equaliser circuit                                              |

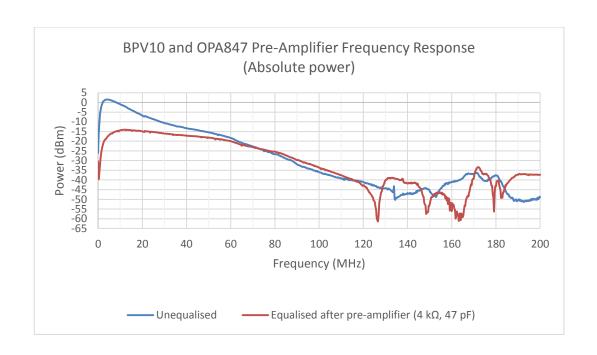

| Figure 5-23 BPV10 PIN PD and TI OPA847 op-amp frequency responses209                                |

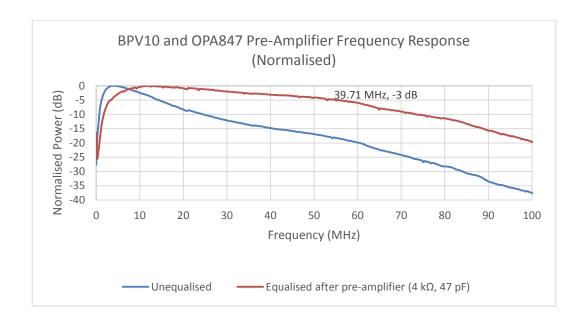

| Figure 5-24 BPV10 PIN PD and TI OPA847 op-amp normalised frequency responses                        |

|                                                                                                     |

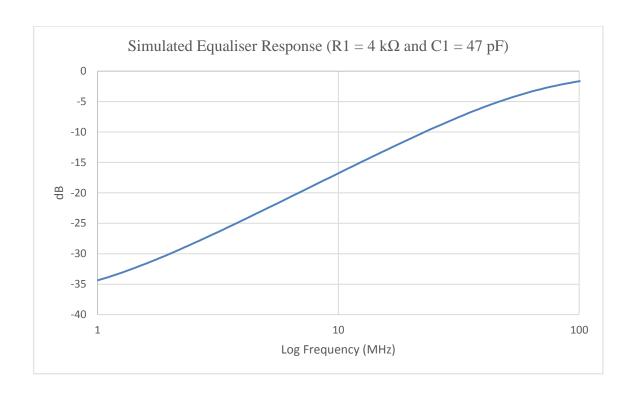

| Figure 5-25 Simulated frequency response of the 2 <sup>nd</sup> order equaliser (log frequency).210 |

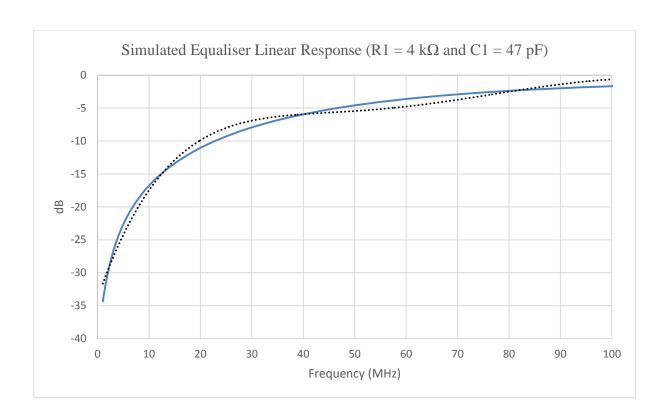

| Figure 5-26 Simulated frequency response of the 2 <sup>nd</sup> order equaliser (linear frequency)  |

|                                                                                                     |

| Figure 5-27 Unequalised PD and pre-amplifier (measured) and polynomial                              |

| approximated equaliser (simulated)                                                                  |

| Figure 5-28 Equalised PD and pre-amplifier (measured) and Equalised PD and pre-                     |

| amplifier (simulated)                                                                               |

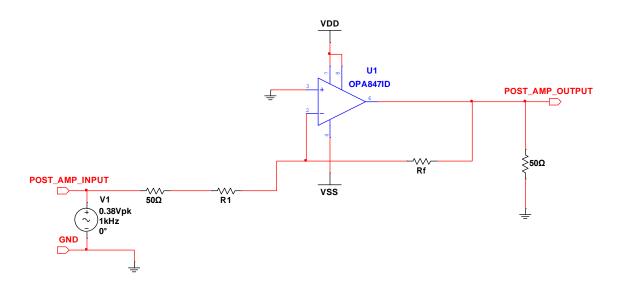

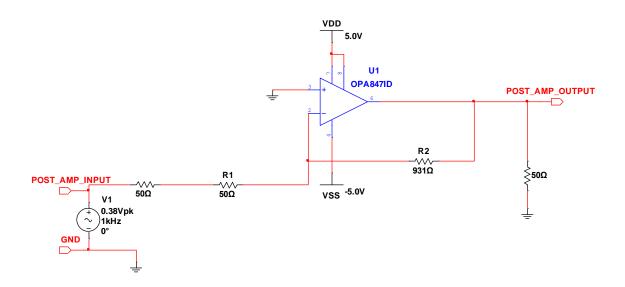

| Figure 5-29 Post-amplifier inverting voltage amplifier circuit                                      |

| Figure 5-30 Post-amplifier inverting voltage amplifier circuit (component values)215                |

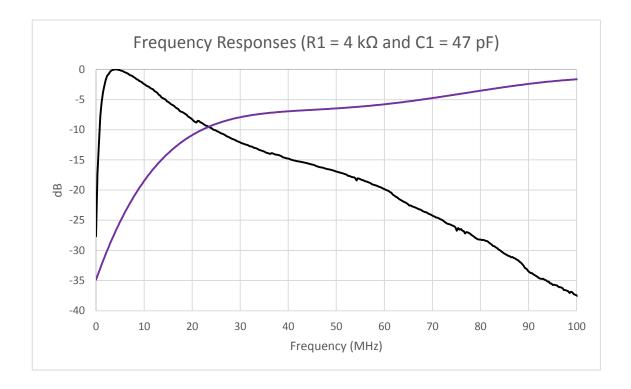

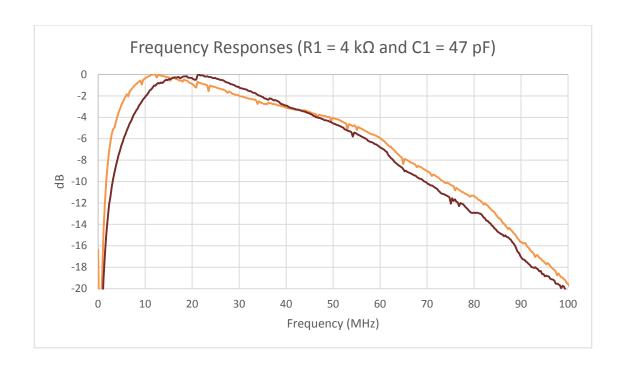

| Figure 5-31 Post-amplifier frequency response                                                       |

| Figure 5-32 2 <sup>nd</sup> order pre-detection LPF circuit                                         |

| Figure 5-33 2 <sup>nd</sup> order Butterworth LPF frequency response (passband)217                  |

| Figure 5-34 2 <sup>nd</sup> order Butterworth LPF frequency response (stopband)217                  |

| Figure 5-35 Window voltage comparator                                                               |

| Figure 5-36 IOPPM composite signal with 0.5 V DC offset                                             |

| Figure 5-37 IOPPM composite signal threshold crossings (1 Vpp, 0.5 V offset)221                     |

| Figure 5-38 IOPPM composite signal threshold crossings (1 Vpp, 0.5 V offset)222                     |

| Figure 5-39 IOPPM+ comparator digital output                                                        |

| Figure 5-40 IOPPM- comparator digital output                               | 223  |

|----------------------------------------------------------------------------|------|

| Figure 5-41 Window comparator simulation circuit                           | 224  |

| Figure 5-42 Window comparator simulation                                   | 225  |

| Figure 5-43 Differential PECL to single-ended TTL translator               | 226  |

| Figure 5-44 VLC Electrical System Model                                    | 228  |

| Figure 5-45 10 <sup>th</sup> order Butterworth LPF circuit                 | 229  |

| Figure 5-46 10 <sup>th</sup> order Butterworth LPF frequency response      | 230  |

| Figure 6-1 Final end-to-end system architecture                            | 235  |

| Figure 6-2 Quartus II hierarchical IOPPM encoder/decoder end-to-end system | m237 |

| Figure 6-3 66 MHz PLL block                                                | 238  |

| Figure 6-4 Time delay block                                                | 238  |

| Figure 6-5 single LCELL primitive                                          | 238  |

| Figure 6-6 Digital only end-to-end test configuration                      | 239  |

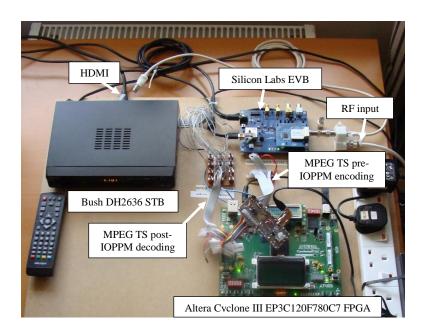

| Figure 6-7 Digital only end-to-end physical test configuration             | 240  |

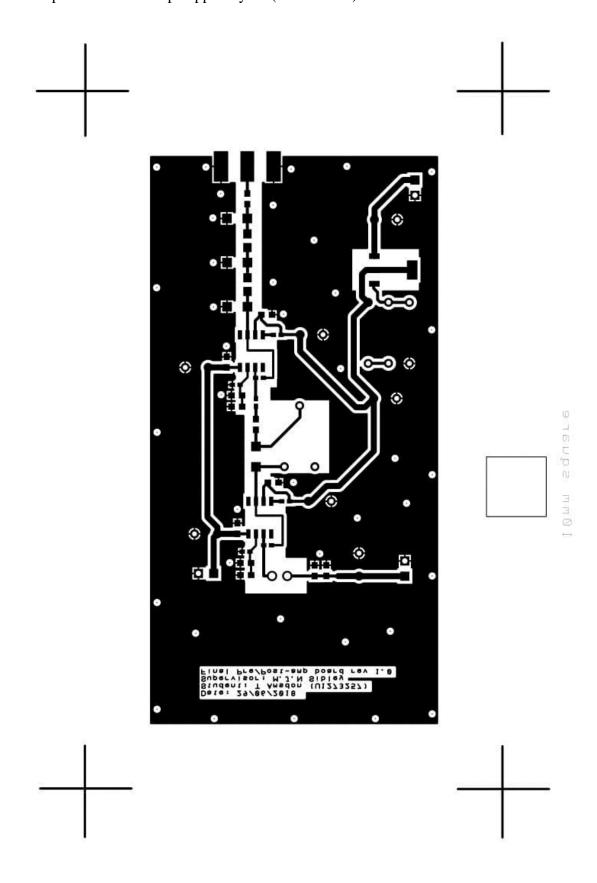

| Figure 6-8 Transmitter schematic                                           | 242  |

| Figure 6-9 Transmitter physical circuit                                    | 243  |

| Figure 6-10 Final transmitter schematic                                    | 245  |

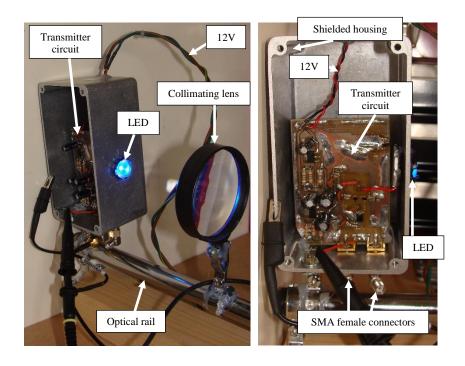

| Figure 6-11 Optical rail mounted transmitter module                        | 246  |

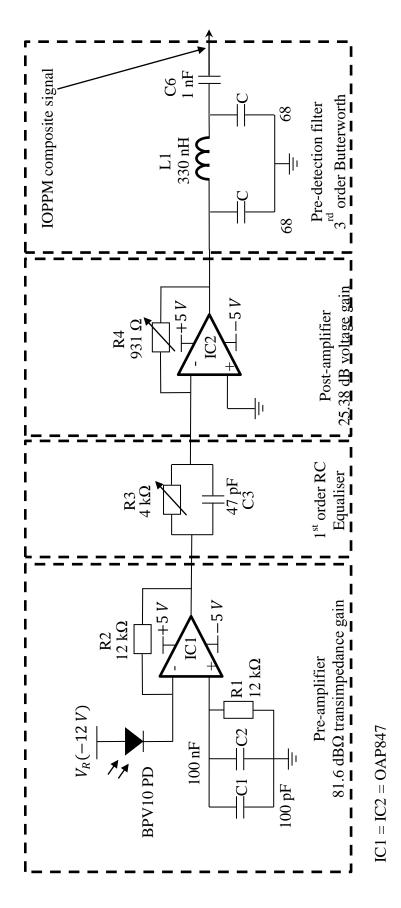

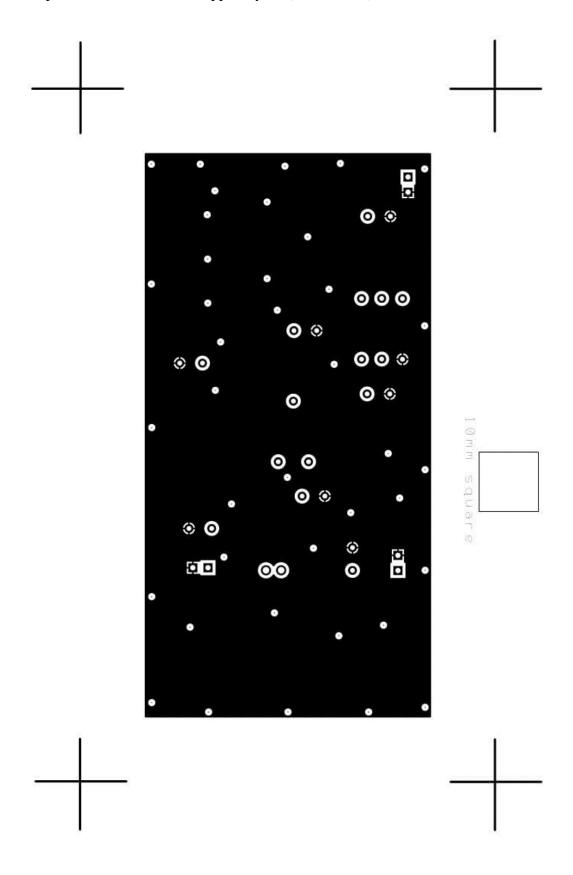

| Figure 6-12 Receiver schematic                                             | 247  |

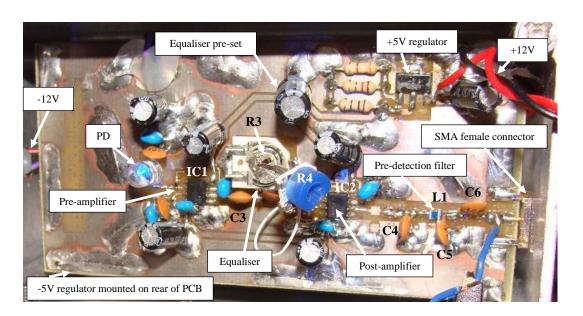

| Figure 6-13 Receiver physical circuit                                      | 248  |

| Figure 6-14 Optical rail mounted receiver module                           | 249  |

| Figure 6-15 Comparator schematic                                           | 250  |

| Figure 6-16 Comparator module                                              | 252  |

| Figure 6-17 Digital modules                                                | 254  |

| Figure 6-18 End-to-end VLC test system                                     | 257  |

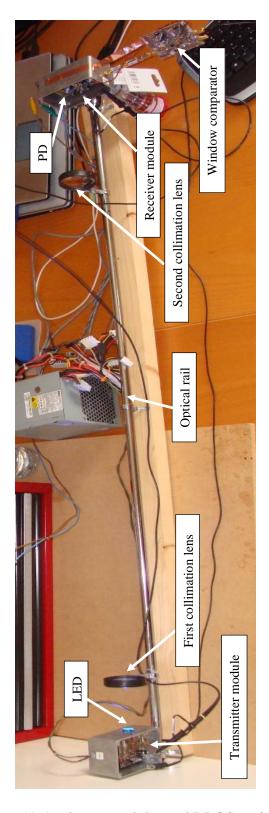

| Figure 6-19 Analogue modules and DLOS optical rail                       | 258 |

|--------------------------------------------------------------------------|-----|

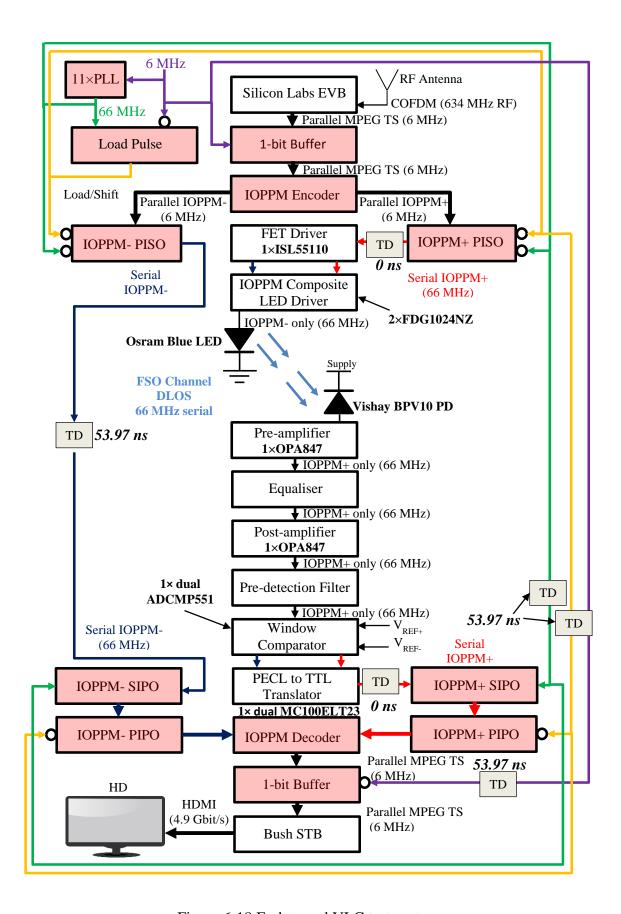

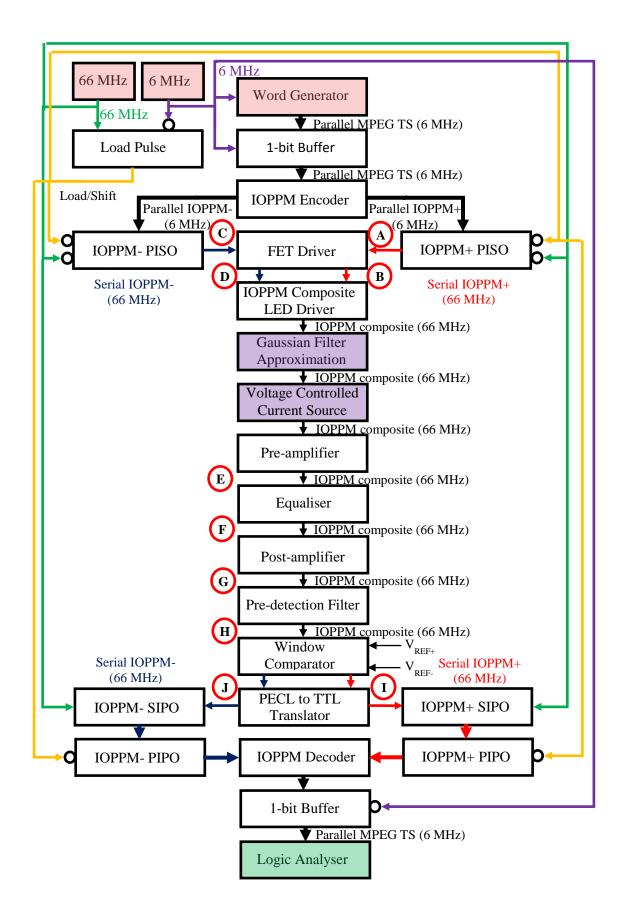

| Figure 7-1 VLC electrical model configuration and test points            | 263 |

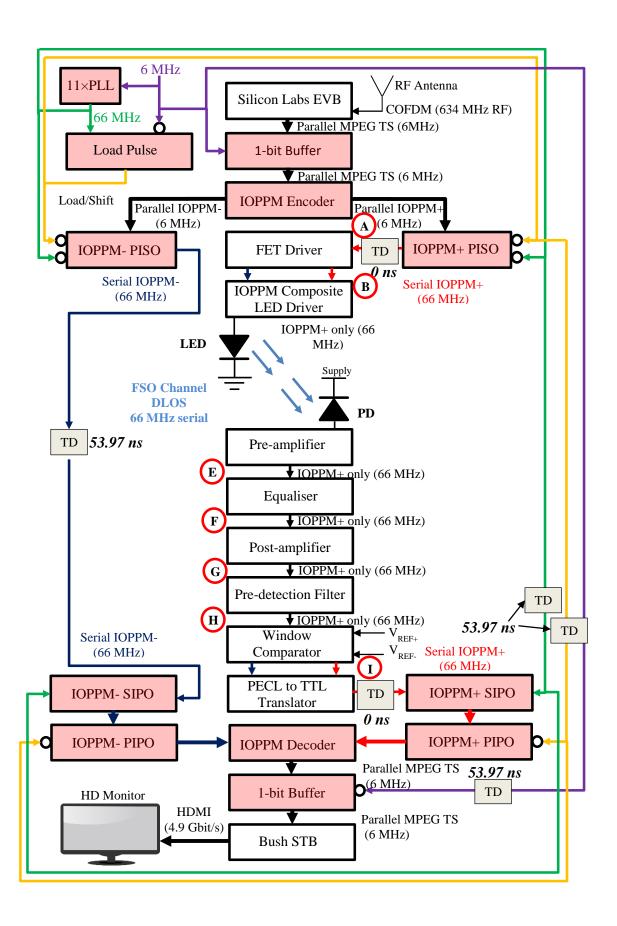

| Figure 7-2 VLC IOPPM+ optical transmission configuration and test points | 264 |

| Figure 7-3 VLC IOPPM+ optical transmission configuration and test points | 265 |

| Figure 7-4 IOPPM+ PISO output timing                                     | 267 |

| Figure 7-5 IOPPM+ PISO output timing (single pulse)                      | 268 |

| Figure 7-6 IOPPM+ PISO output timing (double pulse)                      | 269 |

| Figure 7-7 IOPPM+ PISO output FFT                                        | 271 |

| Figure 7-8 IOPPM+ PISO output FFT                                        | 271 |

| Figure 7-9 IOPPM+ FET driver output                                      | 273 |

| Figure 7-10 IOPPM+ pre-amplifier output                                  | 275 |

| Figure 7-11 IOPPM+ pre-amplifier output (single pulse)                   | 275 |

| Figure 7-12 IOPPM+ pre-amplifier output (double pulse)                   | 276 |

| Figure 7-13 IOPPM+ equaliser output                                      | 278 |

| Figure 7-14 IOPPM+ equaliser output (single pulse)                       | 280 |

| Figure 7-15 IOPPM+ equaliser output (double pulse)                       | 280 |

| Figure 7-16 IOPPM+ post-amplifier output                                 | 282 |

| Figure 7-17 Post-amplifier schematic                                     | 282 |

| Figure 7-18 IOPPM+ post-amplifier output (single pulse)                  | 283 |

| Figure 7-19 IOPPM+ post-amplifier output (double pulse)                  | 284 |

| Figure 7-20 IOPPM+ pre-detection filter output                           | 285 |

| Figure 7-21 IOPPM+ pre-detection filter output (single pulse)            | 286 |

| Figure 7-22 IOPPM+ pre-detection filter output (double pulse)            | 287 |

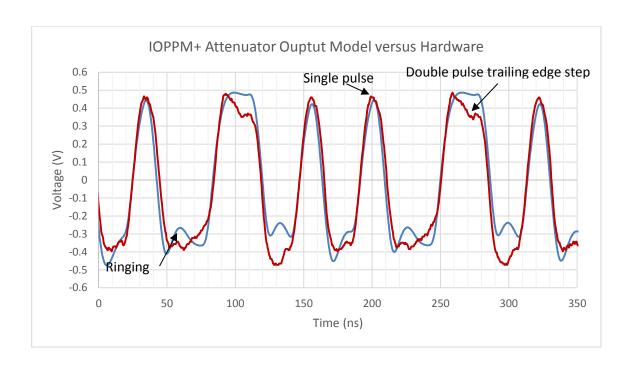

| Figure 7-23 IOPPM+ attenuator output                                     | 288 |

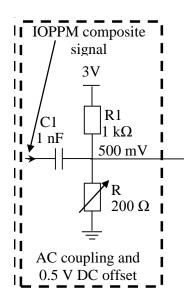

| Figure 7-24 Comparator DC offset circuit                                 | 289 |

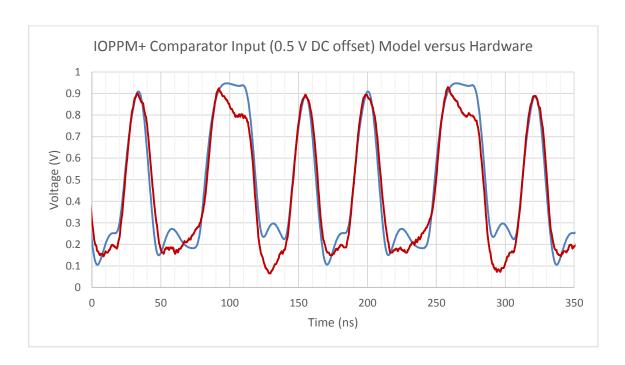

| Figure 7-25 IOPPM+ Comparator Input (measured at C1, R1 and C2 junction) | 289 |

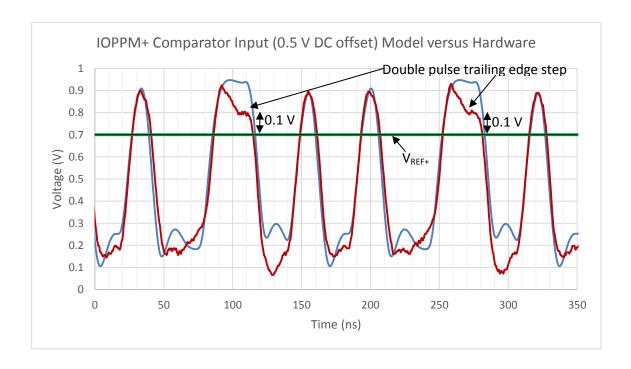

|--------------------------------------------------------------------------|-----|

| Figure 7-26 IOPPM+ Comparator Input (V <sub>REF+</sub> = 700 mV)         | 290 |

| Figure 7-27 IOPPM+ Comparator Output                                     | 292 |

| Figure 7-28 IOPPM+ comparator output (single bit)                        | 292 |

| Figure 7-29 IOPPM+ comparator output (double bit)                        | 293 |

| Figure 7-30 IOPPM+ Modulator module input and receiver module output     | 294 |

| Figure 7-31 IOPPM+ Modulator module input to receiver module output      | 295 |

| Figure 7-32 IOPPM encoder/transmitter                                    | 297 |

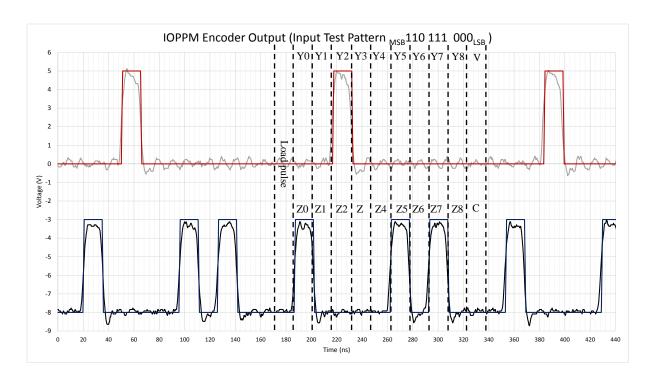

| Figure 7-33 Test pattern 1: IOPPM+ and IOPPM- serial output              | 300 |

| Figure 7-34 Test pattern 2: IOPPM+ and IOPPM- serial output              | 301 |

| Figure 7-35 Test pattern 3: IOPPM+ and IOPPM- serial output              | 302 |

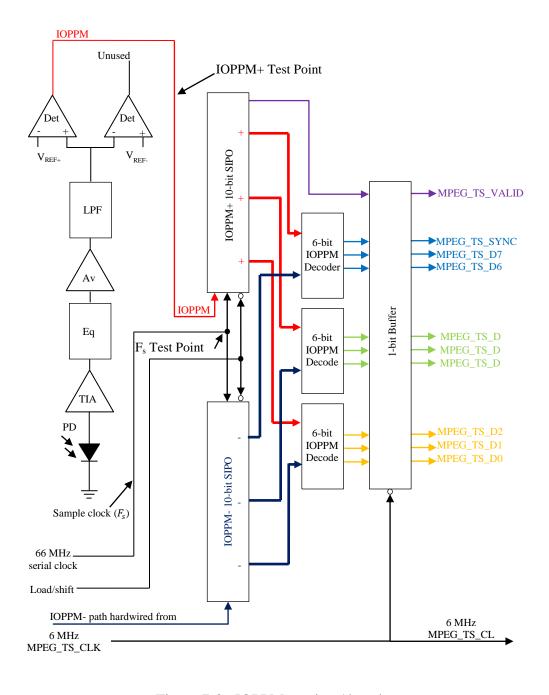

| Figure 7-36 IOPPM receiver/decoder                                       | 303 |

| Figure 7-37 Central decision detection                                   | 305 |

| Figure 7-38 VLC IOPPM+ optical transmission configuration                | 306 |

| Figure 8-1 Proof-of-concept VLC video distribution system                | 313 |

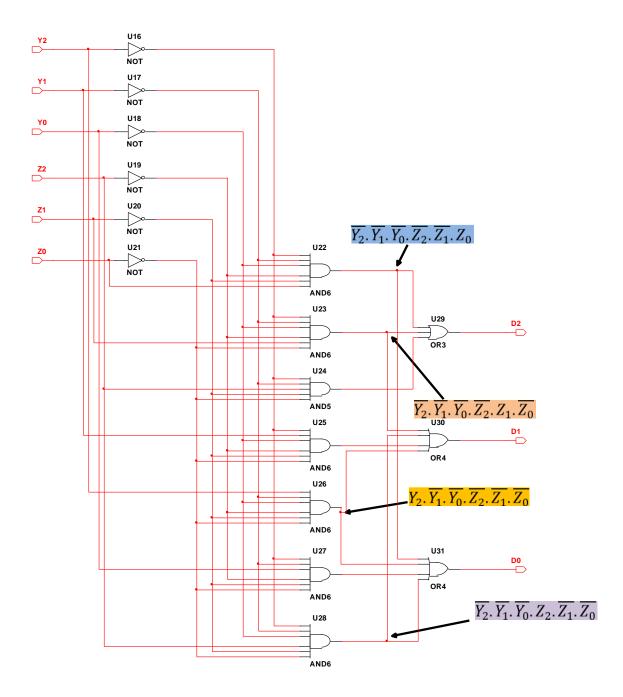

| Figure B.2-1 3-bit IOPPM encoder combinational logic circuit             | 347 |

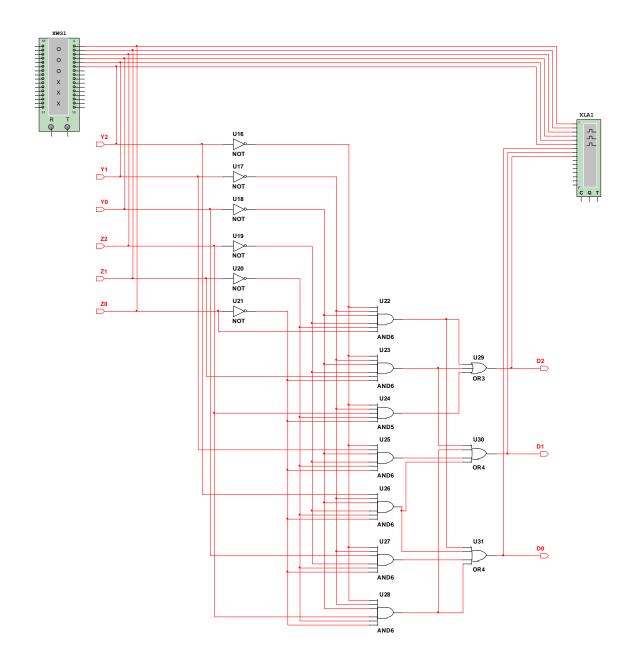

| Figure B.3-2 3-bit IOPPM encoder test circuit                            | 348 |

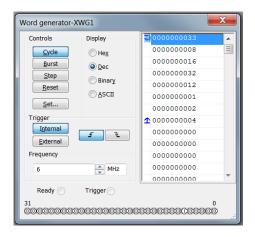

| Figure B.3-3 NI Multisim Word Generator IOPPM encoder test settings      | 349 |

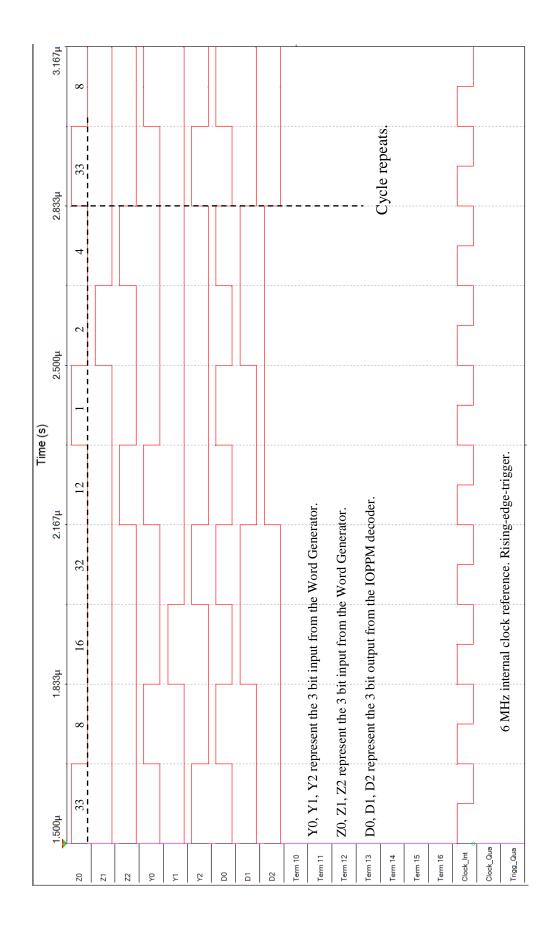

| Figure B.3-4 NI Multisim Logic Analyser IOPPM encoder test settings      | 349 |

| Figure B.3-5 IOPPM encoder test simulation timing traces                 | 351 |

| Figure B.4-6 9-bits of MPEG TS mapped to 3 × 3-bit IOPPM encoders        | 352 |

| Figure B.6-7 IOPPM decoder logic circuit                                 | 361 |

| Figure B.7-8 NI Multisim Word Generator IOPPM decoder test settings      | 362 |

| Figure B.7-9 IOPPM decoder test circuit                                  | 363 |

| Figure B.7-10 IOPPM decoder test simulation timing traces (valid inputs) | 365 |

| Figure B.7-11 IOPPM decoder test simulation timing traces (invalid inputs)367            |

|------------------------------------------------------------------------------------------|

| Figure B.8-12 $3 \times 6$ -bit to 3-bit IOPPM decoders to generate 9-bits of MPEG TS368 |

| Figure B.9-13 IOPPM encoder and decoder end-to-end test circuit                          |

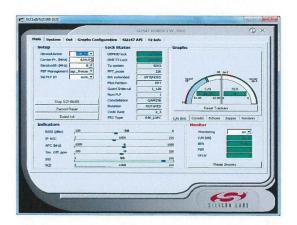

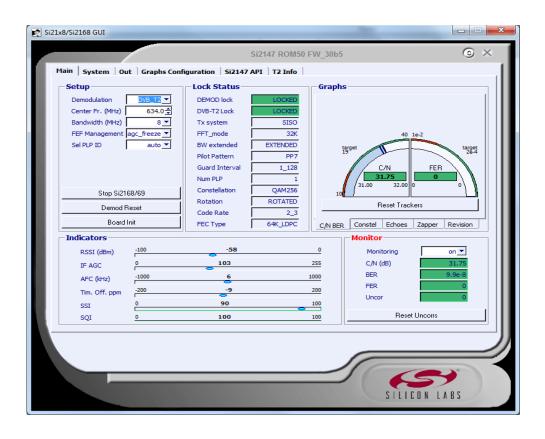

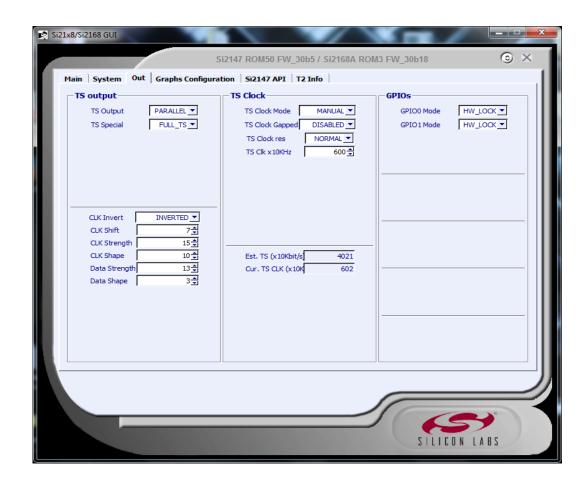

| Figure G.1-14 Silicon Labs Si2147/Si2168 software 'Main' tab settings (Silicon Labs      |

| Inc.)                                                                                    |

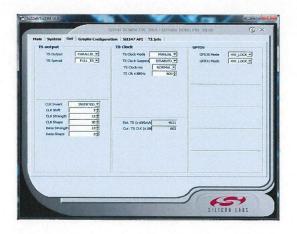

| Figure G.1-15 Silicon Labs Si2147/Si2168 software 'Out' tab settings (Silicon Labs       |

| Inc.)                                                                                    |

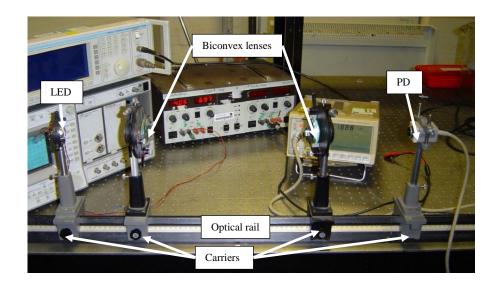

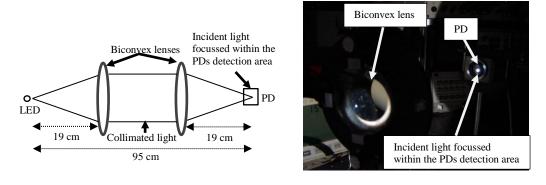

| Figure I.1-16 LED characterisation setup                                                 |

| Figure I.1-17 Collimating lenses arrangement (author generated image)400                 |

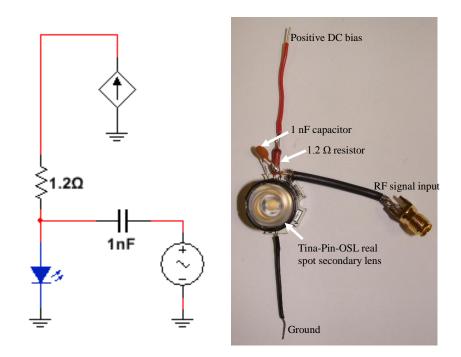

| Figure I.1-18 LED test circuit configuration (author generated image)400                 |

# Glossary

#### **Acronyms**

AC alternating current

ADC analogue-to-digital converter/conversion

AGC automatic gain control

AlGaAs aluminium gallium arsenide

AlGaInP aluminium gallium indium phosphide

AM amplitude modulation

ANSI American National Standards Institute

APD avalanche photodiode

ATSC Advanced Television Systems Committee

AVC Advanced Video Coding

BCH Bose-Chaudhuri-Hocquenghem

BER bit-error rate

xxvi

BOM bill-of-materials

BPF band-pass filter

CAS conditional access

CATV community access television or community antenna television

CC convolutional coding

Ce cerium

CENELEC European Committee for Electrotechnical Standardization

CFL compact fluorescent lighting

CFR Code of Federal Regulations

CMOS complementary metal-oxide semiconductor

CNR carrier-to-noise ratio

Codec compression/decompression

COFDM coded orthogonal frequency division multiplexing

CPE consumer premises equipment

CRT cathode-ray tube

CVBS composite video, blanking and synchronisation or composite

video baseband signal

CW continuous wave

DC direct current

DCO-OFDM direct-current-biased optical orthogonal frequency

division multiplexing

DD direct-detection

DLIF digital low intermediate frequency

DLOS directed line-of-sight

DMT discrete multi-tones

DSP digital signal processing

DSSS direct-sequence spread spectrum

xxvii

DTH direct-to-home satellite

DTMB Digital Terrestrial Multimedia Broadcast

DVB Digital Video Broadcasting

DVD digital versatile/video disc

DVR digital video recorder

EIRP equivalent isotropically radiated power

EPG electronic programme guide

ES elementary stream

ETSI European Telecommunications Standards Institute

EVB evaluation board

FCC Federal Communications Commission

FEC forward-error correction

FER frame-error rate

FET field-effect transistor

FOV field of view

FPGA field-programmable gate array

FSO free-space optical

FFT fast Fourier transform

GaAs gallium arsenide

GaAsP gallium arsenide phosphide

GaN gallium nitride

GBP gain bandwidth product

GUI graphical user interface

HD high-definition

HDMI high-definition multimedia interface

HDTV high-definition television

HEVC high efficiency video coding

I<sup>2</sup>C inter-integrated circuit

IC integrated circuit

IEC International Electrotechnical Commission

IF intermediate frequency

IM intensity modulation

InGaN indium gallium nitride

IOPPM inversion offset pulse position modulation

IP internet protocol

IPTV internet protocol television

IR infrared

IRC infrared communications

ISDB Integrated Services Digital Broadcasting

ISI inter-symbol interference

ITU International Telecommunications Union

LASER/laser light amplification by stimulated emission of radiation

LCD liquid crystal display

LDPC low-density parity-check

LED light-emitting diode

LFL linear fluorescent lighting

LNA low-noise amplifier

LO local oscillator

LOS line-of-sight

LPF low-pass filter

LSB least significant bit

LTI linear time-invariant

LVCMOS low-voltage CMOS

MIMO multiple-in-multiple-out

MIS metal-insulator-semiconductor

MPEG Moving Picture Experts Group

MSB most signification bit

NDA non-disclosure agreement

NLOS nondirected line-of-sight

NRZ non-return-to-zero

NTSC National Television System Committee

OEM original equipment manufacturer

OFDM orthogonal frequency division multiplexing

OLED organic light-emitting diode

OOK on-off keying

Op-amp operational amplifier

OPPM offset pulse position modulation

OWC optical wireless communications

PAL phase alternate line

PECL positive emitter-coupled logic

PMT programme map table

PbS lead sulphide

PCB printed circuit board

PCM pulse code modulation

PD photodiode/photodetector (interchangeable)

PES packetized elementary stream

PGA programmable gain amplifier

PID packet identifier

PIM pulse interval modulation

PIN positive-intrinsic-negative (as in PIN diode)

PISO parallel-in-serial-out

PLL phase-locked loop

PMT programme map table

PPM pulse position modulation

QAM quadrature amplitude modulation

QPSK quadrature phase-shift keying

RF radio frequency

RGB red, green and blue

RMS root mean square

RS Reed-Solomon

Rx receiver

SCART Syndicat des Constructeurs d'Appareils Radiorécepteurs et

Téléviseurs

SDTV standard-definition television

SECAM séquentiel couleur à mémoire

SiC silicon carbide

SISO serial-in-serial-out

SMD surface-mount device

SMPS switched-mode power supply

SNR signal-to-noise ratio

SSL solid-state lighting

STB set-top-box

TCA transconductance amplifier

TCP transmission control protocol

TIA transimpedance amplifier

xxxi

TOP take-over-point

TS transport stream

TTL transistor-transistor logic

TV television

Tx transmitter

UHDTV ultra-high-definition television

USB universal serial bus

VCR video cassette recorder

VGA video graphics array

VHDL VHSIC hardware description language

VHS video home system

VHSIC very high speed integrated circuit

VLC visible light communications

VLCC Visible Light Communications Consortium

YAG yttrium aluminium garnet (as in YAG phosphor)

#### **Notation**

**⊗** linear time-invariant convolution operator

$A_{Rx}$  PD active area

Av voltage gain

$C_{CM}$  common-mode capacitance

$C_D$  diode capacitance

$C_d$  LED depletion capacitance

$C_{DM}$  differential-mode capacitance

$C_f$  feedback capacitance

$C_s$  LED charge diffusion and storage capacitance

d distance between Tx and Rx

E photon energy (emitted by an LED)

$F_s$  sampling frequency

$f_c$  centre frequency

$f_{MIN SER CLK}$  minimum serial PISO clock frequency

$f_{TS CLK}$  frequency of the MPEG TS clock (at receiver demodulator)

$f'_{TS CLK}$  frequency primed is the actual MPEG TS clock (at transmission)

$g(\psi)$  concentrator optical gain (as a function of incident angle)

transconductance  $g_m$  $h_{LOS}(t)$ optical channel impulse response  $h_p(t)$ Gaussian pulse response  $H_{LOS}(0)$ DC gain for DLOS transmission  $H_p(\omega)$ modulating pulse frequency response Ι in-phase component  $I_D$ diode current FET drain-source current  $I_{DS}$  $I_F$ LED forward current  $I_p$ PD photocurrent  $I_S$ diode reverse saturation current imaginary number  $j = \sqrt{-1}$ j k number of nk encoder input bits order of the Lambertian emission mnumber of coder input bits/modulation order Μ number of nk encoder output bits or ideality factor for diodes nN number of bits n(t)additive noise

| $P_{er}$     | probability of erasure error                                    |

|--------------|-----------------------------------------------------------------|

| $P_f$        | probability of false alarm error                                |

| $P_{Rx}$     | optical power received at PD                                    |

| $P_{S}$      | probability of wrong slot error                                 |

| $P_{Tx}$     | optical power transmitted by LED                                |

| Q            | quadrature component                                            |

| r            | magnitude                                                       |

| R            | PD responsivity                                                 |

| $R_{DS\ ON}$ | FET drain-source resistance in the on state                     |

| $R_f$        | feedback resistor                                               |

| $R_0$        | Lambertian radiant intensity                                    |

| $S_i$        | time domain symbol (QPSK)                                       |

| t            | time variable                                                   |

| $t_d$        | decision time                                                   |

| Т            | period (representing one cycle) or temperature                  |

| $T(\varphi)$ | optical band-pass filter attenuation (as a function of incident |

| angle)       |                                                                 |

| $T_{offset}$ | time offset due to additional clock MPEG TS clock cycles        |

$T_S$  bit period or slot-time

$T_{TS\_DATA[n]}$  period of the MPEG TS data bit, bit number denoted by n

$T_{TS\_SYNC}$  period of the MPEG TS synchronisation pulse

$T_{TS\ VALID}$  period of the MPEG TS valid signal

$v_{ISI}$  any signal voltage present in a particular time slot

$v_{pk}$  peak signal voltage within the slot-time

$V_{AIOPPM+}$  composite positive IOPPM analogue pulse

$V_{A\ IOPPM-}$  composite negative IOPPM analogue pulse

$V_D$  diode voltage

$V_{D\ IOPPM+}$  window comparator positive IOPPM digital pulse output

$V_{D\ IOPPM-}$  window comparator negative IOPPM digital pulse output

$V_{DS}$  FET drain-source voltage

$V_F$  diode forward voltage

$V_{GS}$  FET gate-source voltage

$V_{in}$  input voltage

V<sub>output</sub> output voltage

$V_R$  diode reverse voltage

$V_{REF}$  comparator reference voltage

| $V_{REF+}$        | IOPPM positive threshold voltage                        |  |  |  |

|-------------------|---------------------------------------------------------|--|--|--|

| $V_{REF-}$        | IOPPM negative threshold voltage                        |  |  |  |

| m(t)              | modulating signal (data-carrying signal)                |  |  |  |

| $n_o$             | noise                                                   |  |  |  |

| x(t)              | optical intensity modulating signal                     |  |  |  |

| y(t)              | receiver photocurrent signal (including additive noise) |  |  |  |

| $Z_T$             | transimpedance                                          |  |  |  |

| α                 | Gaussian pulse peak height                              |  |  |  |

| $\eta_{qe}$       | quantum efficiency                                      |  |  |  |

| θ                 | angle in radians                                        |  |  |  |

| λ                 | wavelength                                              |  |  |  |

| τ                 | pulse period                                            |  |  |  |

| $	au_R$           | time (autocorrelation)                                  |  |  |  |

| Ø                 | irradiance angle                                        |  |  |  |

| $\emptyset_{1/2}$ | emission semi-angle/half-power/3 dB point               |  |  |  |

| ψ                 | incident angle (angle between Tx and Rx)                |  |  |  |

| $\psi_c$          | FOV angle                                               |  |  |  |

# **Constants**

| С | speed of light (approximately 299792458 $m  s^{-1}$ )                                                 |

|---|-------------------------------------------------------------------------------------------------------|

| h | Planck's constant (exactly $6.62607015 \times 10^{-34} J s$ )                                         |

| k | Boltzmann's constant $(\text{approximately } 1.38064852 \times 10^{23} \ m^2 \ kg \ s^{-2} \ K^{-1})$ |

| q | charge of an electron (approximately 1.60217662 $\times$ 10 <sup>-19</sup> $C$ )                      |

# 1 Introduction

# 1.1 Background

A proof-of-concept, unidirectional free-space visible light communication (VLC) system for distributing high-definition television (HDTV) content to wall-mounted TVs is presented. Specifically, the system is intended to distribute content received by Digital Video Broadcast (DVB) standard terrestrial set-top-box (STB) receivers.

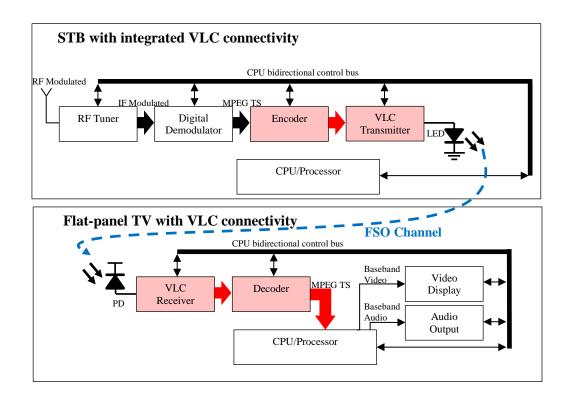

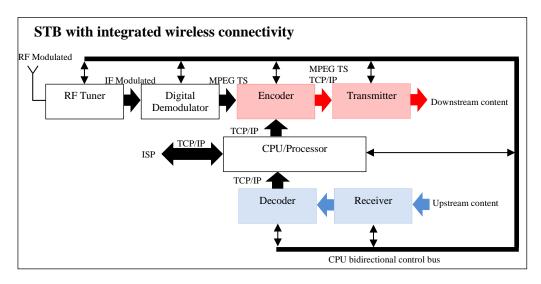

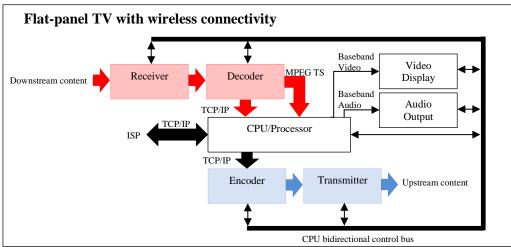

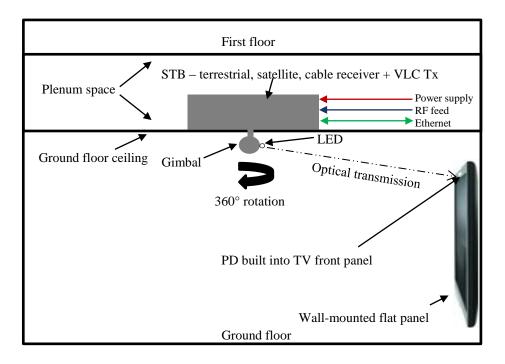

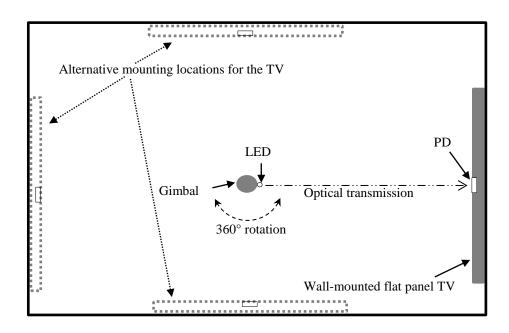

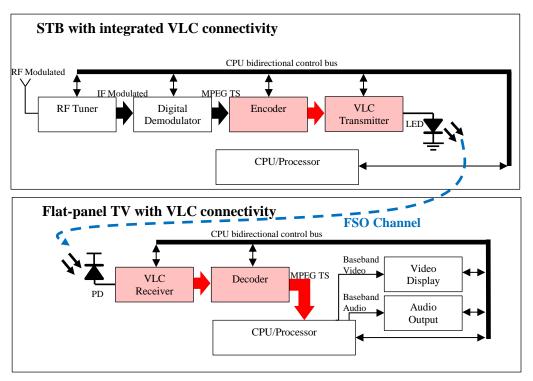

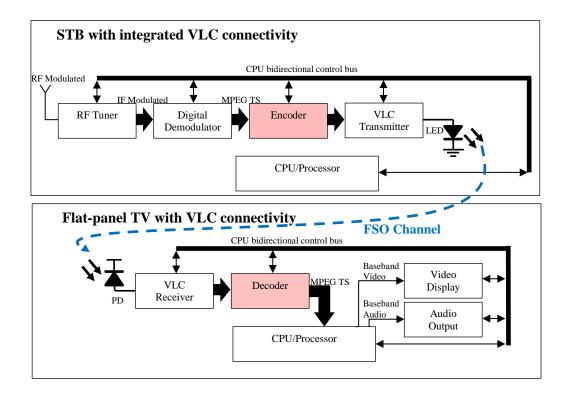

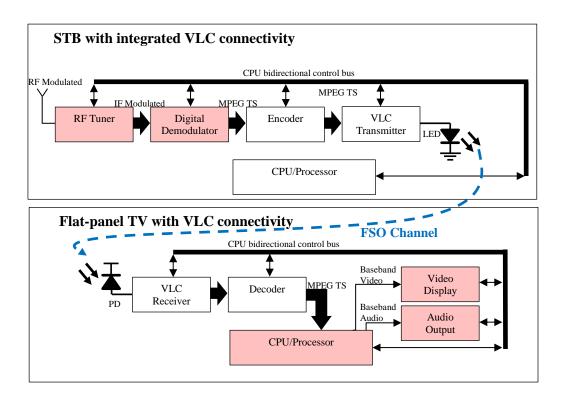

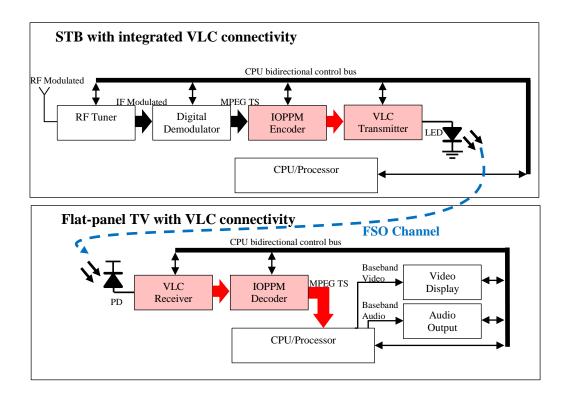

VLC based transmission techniques are offered as an alternative or a complementary solution to current radio frequency (RF) and power-line technologies for content distribution. This approach is also presented as a way for TV manufacturers to eliminate the need for region specific RF tuner and demodulator functions within a TV, replacing them with a simpler baseband optical receiver which interfaces directly with the Moving Picture Experts Group (MPEG) decoder. Using this approach the tuner and demodulator functions are relocated to a low-cost STB, which provides an integrated RF to VLC system external to the TV. This VLC enabled STB essentially receives and demodulates DVB content, and re-encodes it using a coding scheme suitable for free-space optical (FSO) transmission, and transmits to the TV over an optical channel exhibiting an inverse square attenuation characteristic and Gaussian impulse response. Figure 1-1 shows the conceptual block diagram of the system, with the key VLC blocks highlighted in pink.

Figure 1-1 VLC broadcast (MPEG TS) distribution system (author generated image)

This work also proves that all connector interfaces, except the mains power cable, can be eliminated from a digital TV to further reduce costs and complexity. The elimination of the interfaces also has the added benefit of making it easier to wall-mount a TV.

In this chapter, the concept of a VLC enabled content distribution system is defined. The evolution of TV interconnects from analogue to digital interfaces is introduced, and an explanation as to why TVs fitted with multiple interconnects pose wall-mounting challenges is given. Current trends in digital broadcasting are also discussed, highlighting the worldwide migration to all-digital based broadcast systems, with particular emphasis placed on the DVB standard. The current DVB compatible STB and TV architectures are summarised, and a new conceptual content distribution architecture is introduced. Wi-Fi and power-line technologies and the associated disadvantages are also presented, followed by an introduction to VLC systems suitability for content

distribution. A physical realisation of the conceptual VLC based system is also given. The chapter closes with a summary of the key aims and objectives of this work, highlighting the areas of originality.

### 1.1.1 TV Interconnects

The earliest electronic TVs received analogue broadcast video and audio content directly through an RF connector which was connected to a 75 Ω un-balanced coaxial feeder cable. The opposite end of the feeder was connected to either a set-top loop or roof-top Yagi array antenna capable of receiving off-air broadcasts from a line-of-sight (LOS) RF transmitter. Received signals were presented to a tuner and demodulator which selected the desired channel content and converted it to the required baseband video and audio signals needed for the respective reproduction (Zarach & Morris, 1979). This fundamental TV system architecture has remained largely the same throughout the decades, although TVs in the developed world now use a digital architecture, and receive only digital broadcasts (ITU, 2013). Furthermore, modern TVs are no longer limited to terrestrial reception, but can also receive cable and satellite broadcasts (ITU, 2013). All of these digital broadcasts use RF based transmissions techniques and channel specific modulation schemes, with a common baseband digital transport stream (TS) layer at the transmitter and receiver.

Early TVs did not have any baseband connectivity, but since the mass deployment of Betamax and video home system (VHS) video cassette recorders (VCR) in the 1980s, TVs evolved to support, not only RF connectivity, but direct wireline connectivity of baseband signals. These interconnects were used to support VCRs, games consoles and home computers, as well as, starting in the 1990s, digital STBs and digital video recorders (DVR) (O'Driscoll, 2000). The first analogue baseband phono connectors

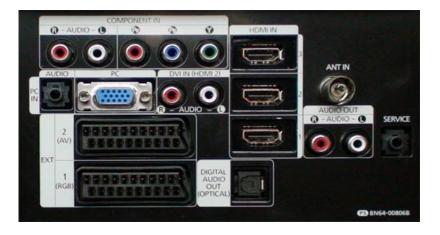

supported mono audio, and video in the form of the composite video, blanking and synchronisation (CVBS) signal used for phase alternate line (PAL) and SECAM (Séquentiel couleur avec mémoire) standards in Europe, and the NTSC (National Television System Committee) standard in North America (Jack, 2001). The analogue interconnects were expanded to included component video (P<sub>R</sub>, P<sub>B</sub>, Y), video graphics array (VGA), and S-video. In Europe the SCART (Syndicat des Constructeurs d'Appareils Radiorécepteurs et Téléviseurs) connector was developed to support analogue video, stereo audio and device-to-device signalling in a single interface. Stereo audio interfaces also evolved in the form phono and jack connectors. Digital interfaces appeared in the mid-1980s in the form of the audio optical fibre connector, and then in the 2000s, the high-definition multimedia interface (HDMI) connector appeared, capable of supporting digital video, audio and data (Whitaker, 1998). Ethernet interfaces have also been added to support internet connectivity, as well universal serial bus USB support for digital peripheral devices. Figure 1-2 and Figure 1-3 show the typical connectors found on the rear-panel of modern TVs in Europe and North America, respectively.

Figure 1-2 European: Samsung LE40A656 40" 1080p LCD HDTV

Figure 1-3 North America: Samsung LN-T5265F 52" 1080p LCD HDTV

### 1.1.2 Flat-panel TV Wall-mounting Challenges

Modern TVs use flat-panel screen technologies such as liquid-crystal display (LCD) and organic LED (OLED), which are lighter, less bulky, and have larger screen sizes than TVs built with cathode ray tubes (CRT). These advances have enabled consumers to wall-mount TVs, but challenges are introduced due to the TVs large number of connector interfaces. Firstly, a TV cannot operate without power, so a mains power cable input is essential and cannot be eliminated. Secondly, an RF input connector is required to enable the reception of terrestrial, cable and satellite broadcasts signals. Finally, a multitude of analogue and digital interconnects that have evolved since the 1980s are required to support connectivity to external peripheral devices. All these interfaces need cables that require channelling, either within the walls of the consumers premises i.e. chasing wall channels, or through the use of wall-mounted conduit; both of which are potentially expensive and inconvenient for the consumer. Furthermore, if the distance between the TV and the peripheral devices is a number of metres, the electrical performance of the baseband signals is degraded due to the long cable lengths. Specifically, increased cable length for baseband signals results in decreased signal-tonoise ratio (SNR) due to per unit length losses, and increased probability of ingress of interference signals, both of which can lead to degraded picture quality. In the case of analogue baseband systems these effects lead to increased noise (reduced signal-to-noise ratio SNR) or beat-patterns (spurious ingress) in the reproduced picture. In digital baseband systems these effects can lead to errors, resulting in macro-blocking, and in severe cases, complete loss of picture.

### 1.1.3 Digital TV Trends

In 2013, the International Telecommunications Union (ITU), which is a respected institution that has been collecting data on TV trends since the 1960s, published a detailed report about global TV trends (ITU, 2013). The report highlighted that TV, unlike radio and fixed telephony, had not seen any decline in penetration, and that 79% of worldwide households had at least one TV. It also stated that most of developed world, US, Europe, Russia, and Arab States, has access to TV services through digital based technologies. The report stated that 55% of the total worldwide households with a TV are able to receive digital broadcasts, and it also stated that the most rapidly growing digital TV deployments are occurring in developing countries in Asia and Africa.

As TV is still an extremely important mass communication system, able to reach large audiences, broadcasts for terrestrial, cable TV (CATV), direct-to-home satellite (DTH) are rapidly moving towards an all-digital based transmission system. Additionally, internet protocol TV (IPTV) is another method of accessing broadcast content.

Broadcast TV is still extremely important for mass communication and deployments are increasing, specifically using digital technologies. As the adoption of digital TV progresses, support for legacy analogue baseband connector interfaces will continue to diminish (ITU, 2013). Legacy peripheral devices such as VCRs, which are no longer in

mass production (Overly, 2016), will ultimately be replaced by modern digital based technologies.

Even digital baseband connector interfaces, used to support physical media such as digital versatile discs (DVD) and Blu-ray, will be eliminated, replaced by growing cloud-based storage and subscription based online streaming services, such as Netflix, Hulu and YouTube. Similarly, games consoles such as PlayStation and Xbox could be replaced by subscription based online gaming services.

### 1.1.4 All-Digital TV and DVB MPEG TS

In the future, it is likely that almost all baseband connector interfaces will be eliminated from the TV. Given this scenario, it is possible to envision a connector-less TV having only a mains power cable and some form of generic transceiver to enable internet access and reception of traditional RF based terrestrial, cable, and satellite broadcasts. It is also possible to envision a TV that is able to operate in any region of the world regardless of the broadcast standards used in that specific region – in effect, a region-less TV.

In order to take this concept further, it is necessary to consider the standards for broadcast content. Firstly, it is important to mention that TCP/IP is a worldwide standard protocol for internet communications, so worldwide interoperability already exists for TCP/IP connected devices (Kurose, Ross, & Paul, 2013). However, there is no such worldwide standardisation or interoperability for digital TV broadcasts (Jack, 2001). The TV tuner and digital demodulator functions are region-specific (ATSC, 2010; DVB, 2015; Song et al., 2007), meaning that different modulation and channel coding schemes are used around the world for digital TV broadcasts. TV manufacturers currently need to fit specific tuner and demodulator types for the region of the world where the TV operates. This is a non-optimal solution, as manufacturers need to design

and support a number of TV platforms with different receiver requirements. Ideally, manufacturers might prefer to produce a generic, region-less TV platform to enable cost savings in the design, compliance testing and manufacturing processes, as well as simplify in-the-field support.

To achieve a region-less TV architecture, it is impossible to immediately standardise worldwide digital TV broadcasts, as this would require expensive upgrades to both broadcast transmitter stations and consumer premises equipment (CPE). A better strategy is to eliminate the tuner and demodulator from TVs, and externalise these functions in a low-cost STB which is able to receive and retransmit digital broadcast content to the TV using a standardised TS bus and wireless connection. Also, by externalising the region-specific elements of the TV, future upgrades to the broadcast system only require replacement of the low-cost STB and not the high-cost TV.

Most households in the developed world use some type of STB to access digital broadcast services, increasingly through STBs that provide internet protocol TV (IPTV), as well as terrestrial, cable or satellite access. STBs already provide a viable and cost-optimised method for receiving digital content, so this further strengthens the argument for externalising the tuner and demodulator functions of the TV to a STB. By relocating the tuner and demodulator functions to a STB, standardised connectivity between the STB and TV can be achieved by identifying a common digital interface used across all digital broadcast TV systems. This common interface can effectively unify all broadcast standards through a single interface which can then be re-encoded for wireless distribution of content from the STB to the TV. This interface can also be used to provide internet and IPTV connectivity through the TCP/IP protocol.

The unification process begins by examining existing digital broadcast systems to identify common digital interfaces that can be used for STB to TV connectivity. Although there are a number of digital TV broadcast standards used around the world, for the sake of clarity, only the most prevalent digital broadcast standard, DVB, is discussed here.

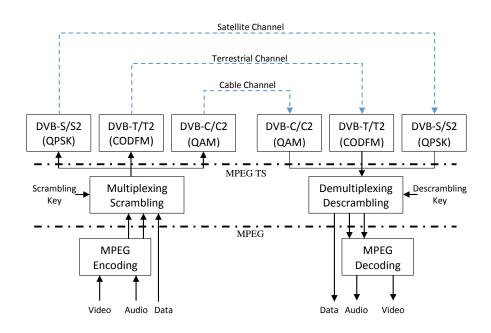

The DVB standard is subdivided by transmission type and provides for terrestrial broadcasts with DVB-T (SDTV) and DVB-T2 (HDTV), cable broadcasts with DVB-C (SDTV) and DVB-C2 (HDTV), and satellite broadcasts with DVB-S (SDTV) and DVB-S2 (HDTV). Most notably, the DVB-T standard is used extensively across Europe, Russia, Australasia, Africa, and certain parts of the Middle and Far-East. These standards specify all aspects of the broadcast system from transmission to reception, including source coding, channel coding and modulation schemes (NorDig, 2014).

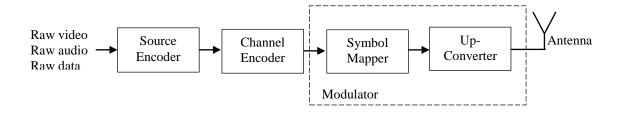

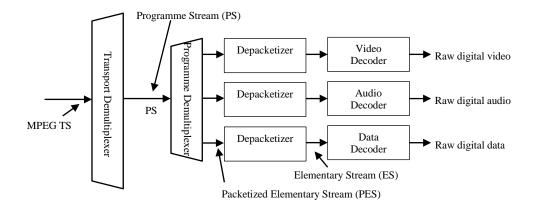

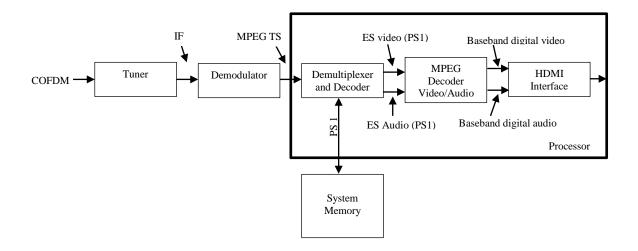

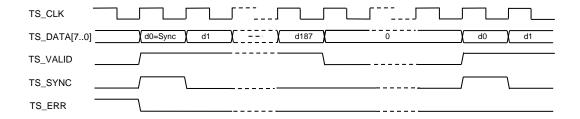

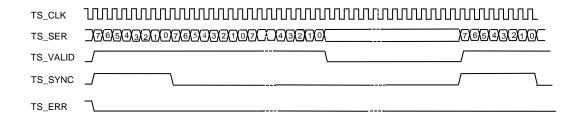

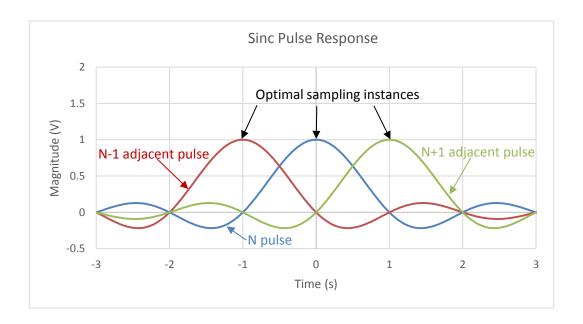

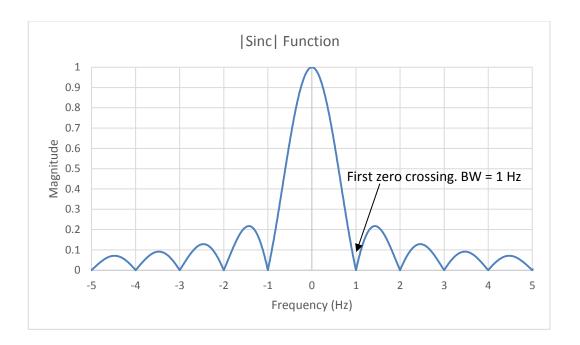

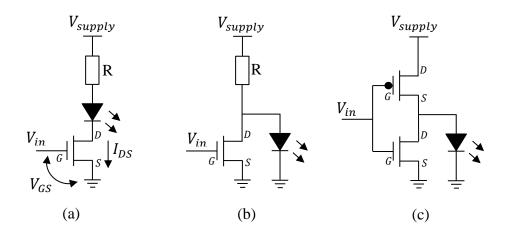

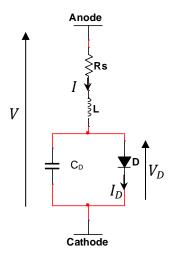

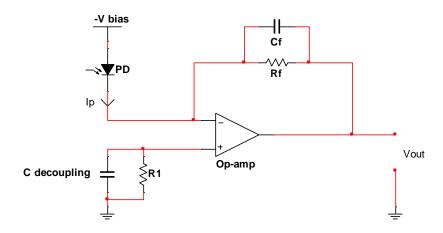

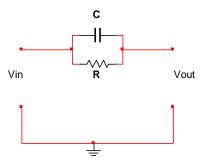

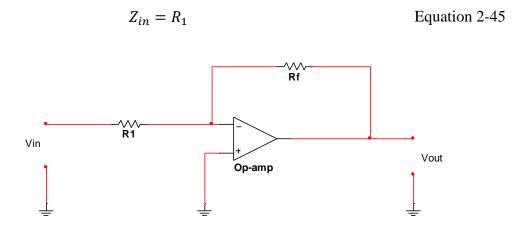

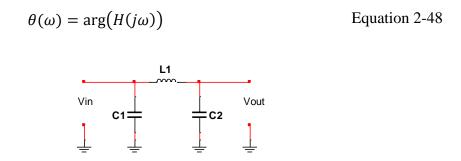

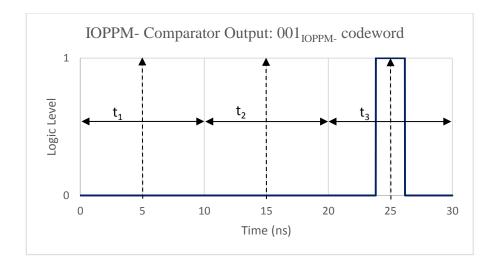

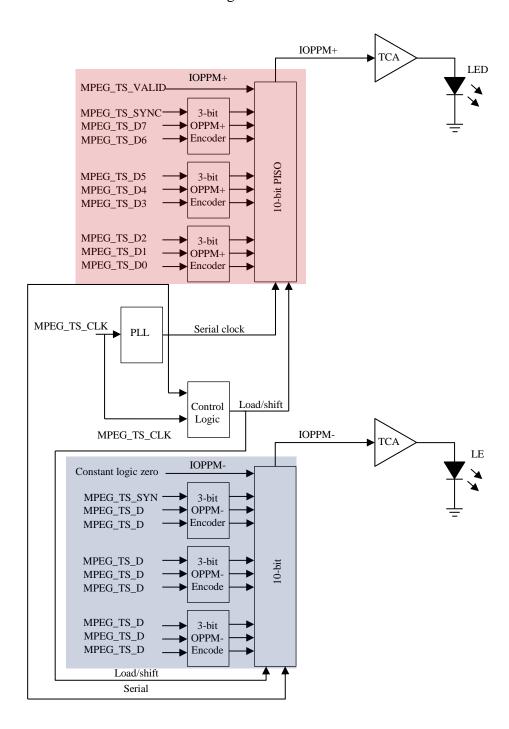

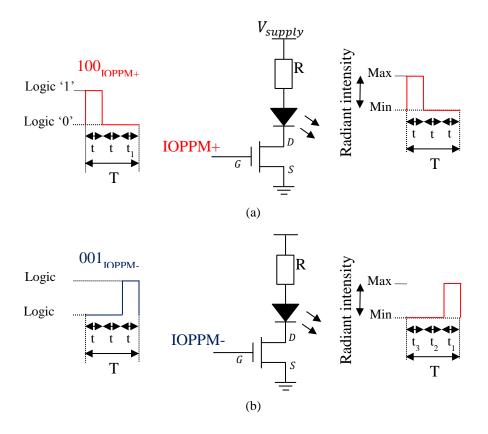

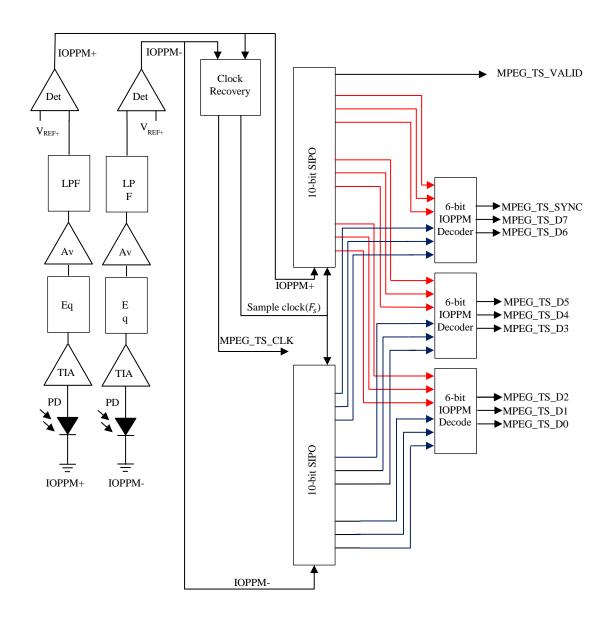

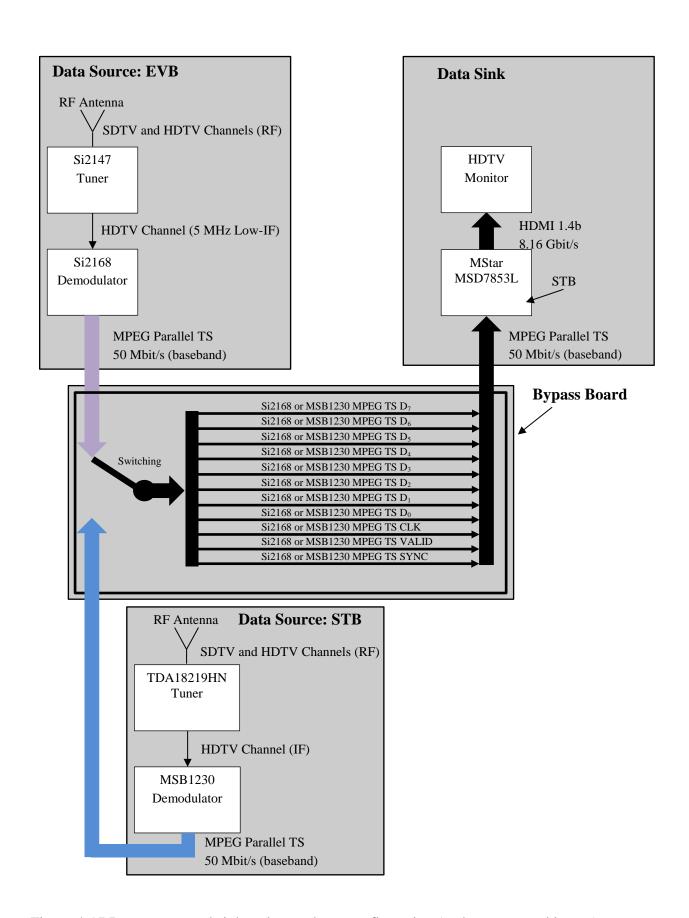

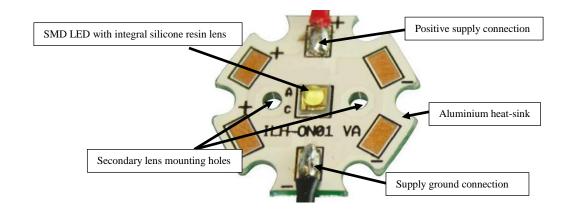

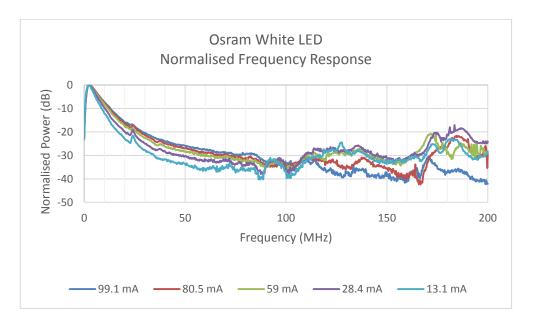

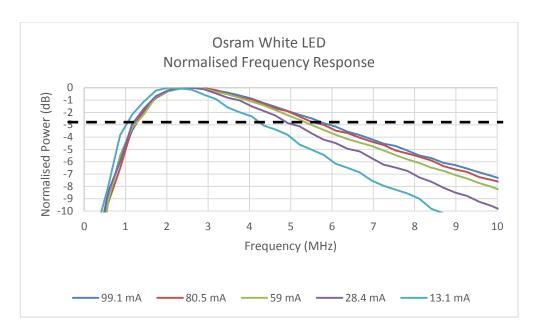

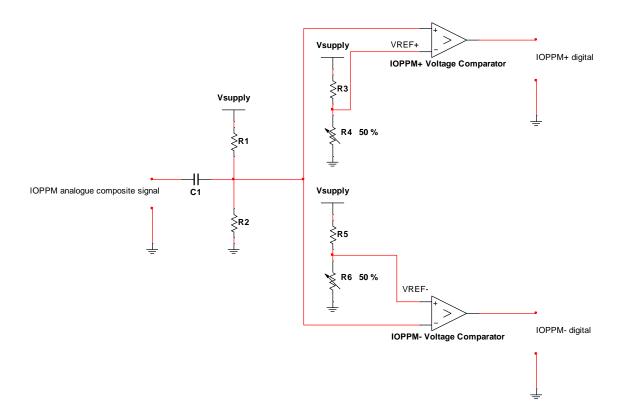

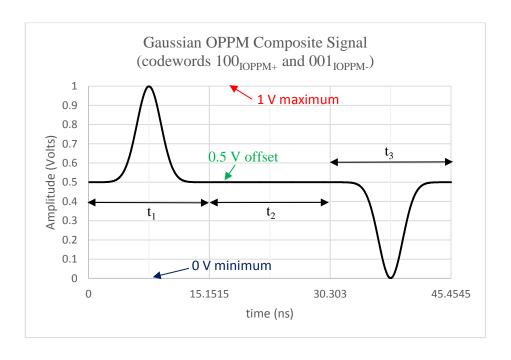

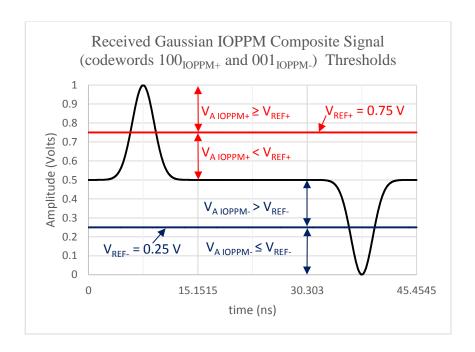

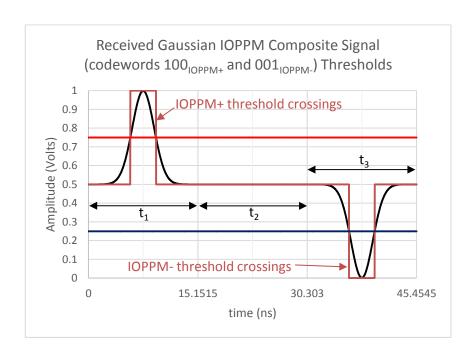

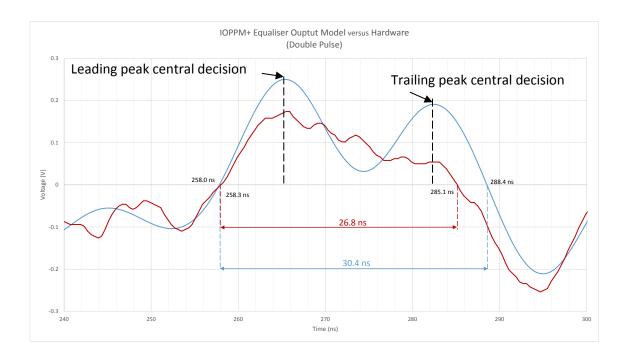

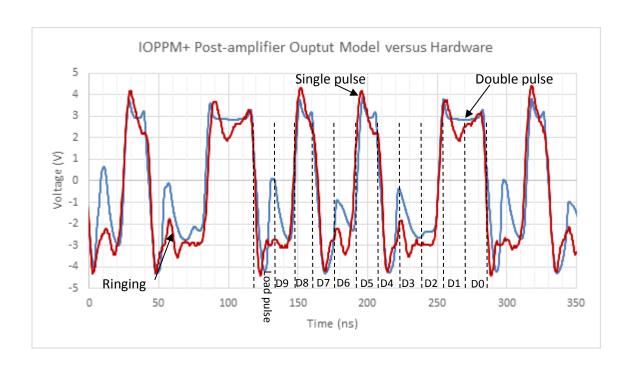

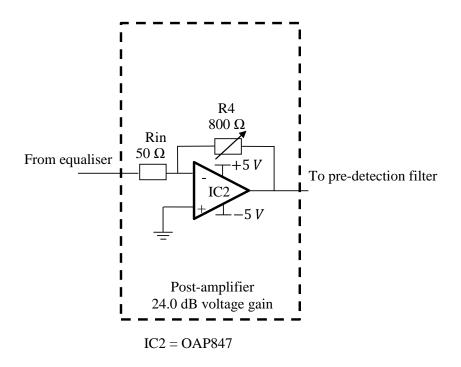

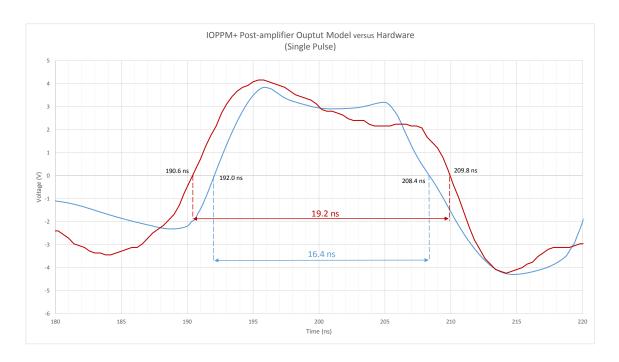

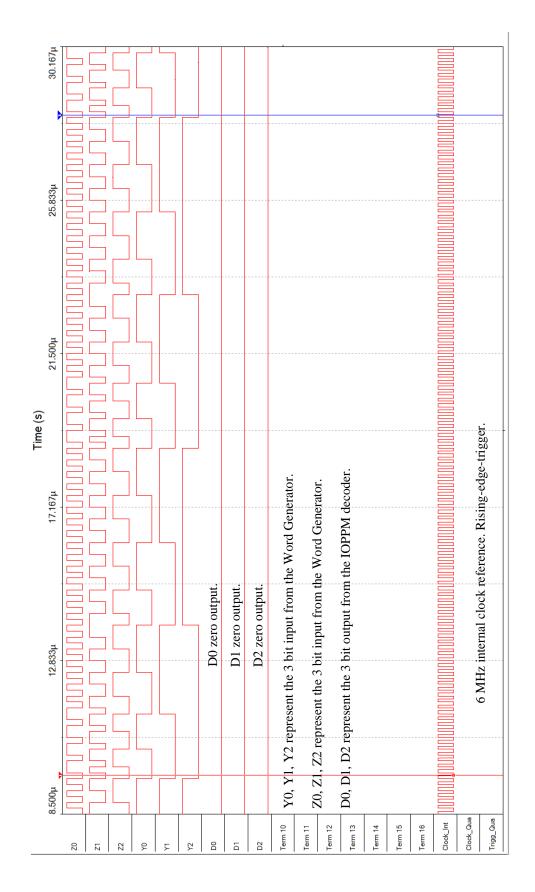

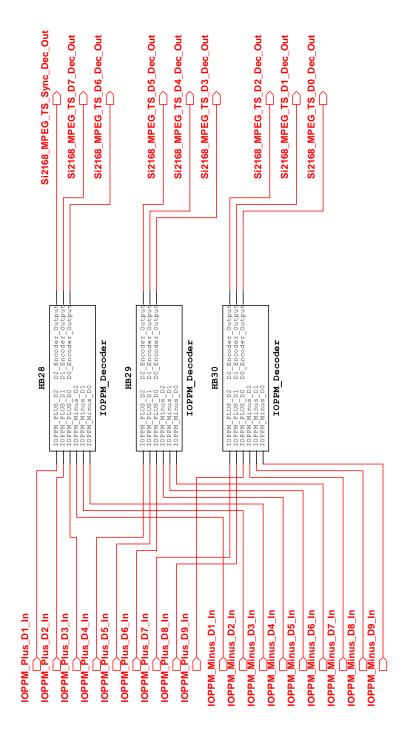

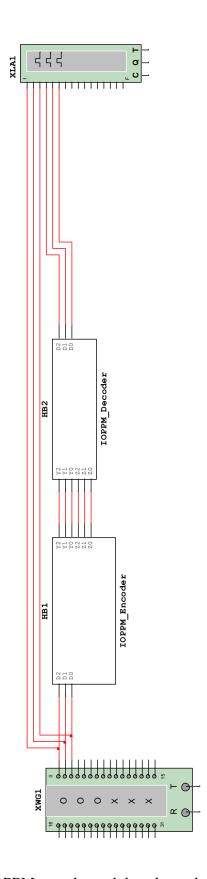

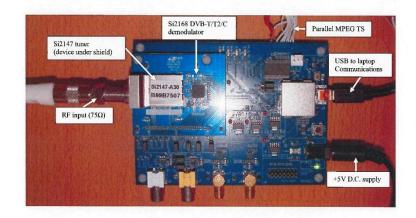

Figure 1-4 shows a simplified block diagram of the DVB system architecture for DVB-T/T2, DVB-S/S2 and DVB-C/C2. As illustrated in the diagram, the transmission type determines the modulation scheme used; terrestrial DVB-T/T2 uses coded orthogonal frequency division multiplexing (COFDM) modulation because of a resistance to signal multipath interference; satellite DVB-S/S2 uses quadrature phase-shift keying (QPSK) because of a high immunity to noise; and cable DVB-C/C2 uses quadrature amplitude modulation (QAM) because it is able to accommodate a significant number of bits-persymbol over well controlled, largely interference free, cable networks. Each modulation scheme uses a specific channel coding scheme, optimised for the channel type the broadcast content is transmitted over. The source coding, however, is common across all DVB standards (Bing, 2015). Currently MPEG-2 (H.262) is used for SDTV broadcasts and H.264, also referred to as MPEG-4 Part 10, Advanced Video Coding (MPEG-4