### 저작자표시-비영리-변경금지 2.0 대한민국

### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

### 공학박사학위논문

## Stretchable and Wearable Carbon Nanotube Electronics

신축성 있고 착용 가능한 탄소 나노튜브 기반 전자 기술

2020년 8월

서울대학교 대학원 협동과정 바이오엔지니어링전공 구 자 훈

## Stretchable and Wearable Carbon Nanotube Electronics

# A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUESTMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY IN ENGINEERING AT THE GRADUATE SCHOOL OF SEOUL NATIONAL UNIVERSITY

August 2020

By

Ja Hoon Koo

Supervisor

**Dae-Hyeong Kim**

### **Abstract**

### Stretchable and Wearable

### **Carbon Nanotube Electronics**

Ja Hoon Koo

Interdisciplinary Program for Bioengineering

The Graduate School

Seoul National University

Networks of carbon nanotubes (CNTs) are a promising candidate for use as a basic building block for next-generation soft electronics, owing to their superior mechanical and electrical properties, chemical stability, and low production cost. In particular, the CNTs, which are produced as a mixture of metallic and semiconducting CNTs via chemical vapor deposition, can be sorted according to their electronic types, which makes them useful for specific purposes: semiconducting CNTs can be employed as channel materials in transistor-based applications and metallic CNTs as electrodes. However, the development of CNT-based electronics for soft applications is still at its infant stage, mainly limited by the lack of solid technologies for

developing high-performance deformable devices whose electrical performances are comparable to those fabricated using conventional inorganic materials. In this regard, soft CNT electronics with high mechanical stability and electrical performances have been pursued.

First, wearable nonvolatile memory modules and logic gates were fabricated by employing networks of semiconducting CNTs as the channel materials, with strain-tolerant device designs for high mechanical stability. The fabricated devices exhibited low operation voltages, high device-to-device uniformity, on/off ratios, and on-current density, while maintaining its performance during ~30% stretching after being mounted on the human skin. In addition, various functional logic gates verified the fidelity of the reported technology, and successful fabrication of non-volatile memory modules with wearable features has been reported for the first time at the time of publication.

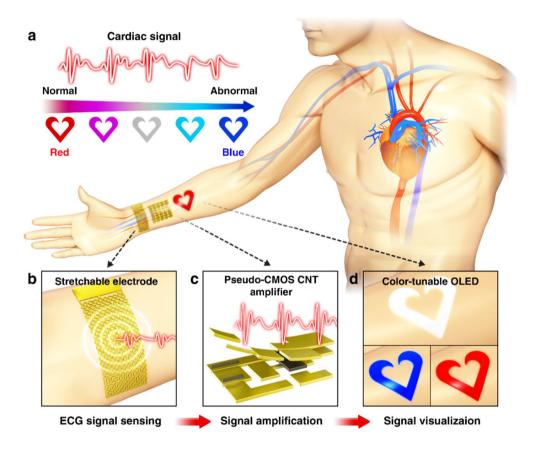

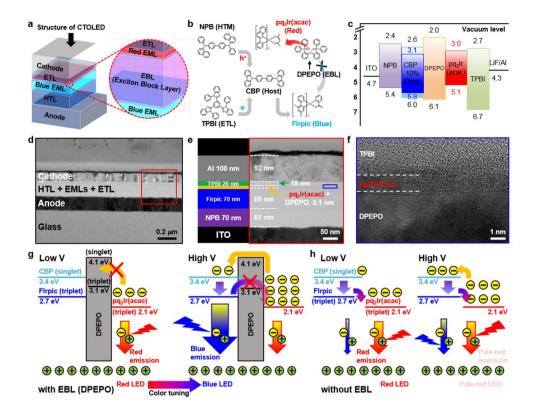

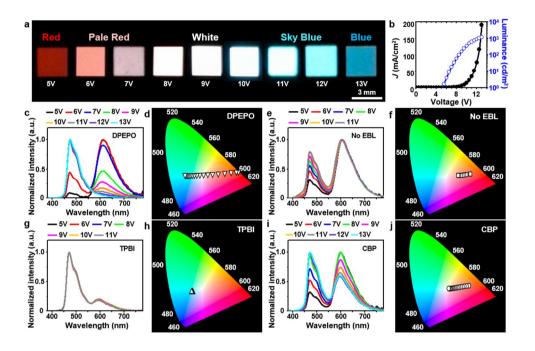

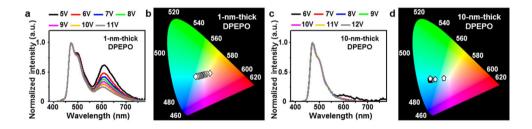

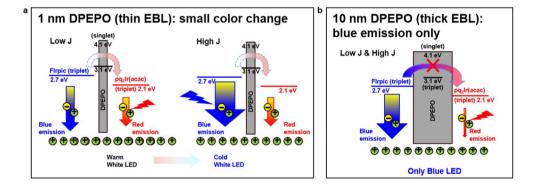

Second, the networks of semiconducting CNTs were used to fabricate signal amplifiers with a high gain of ~80, which were then used to amplify electrocardiogram (ECG) signals measured using a wearable sensor. At the same time, color-tunable organic light-emitting diodes (CTOLEDs) were developed based on ultra-thin charge blocking layer that controlled the flow of excitons during different voltage regimes. Together, they were integrated to construct a health monitoring platform whereby real-time ECG signals could be detected while simultaneously notifying its user of the ECG status via color changes of the wearable CTOLEDs.

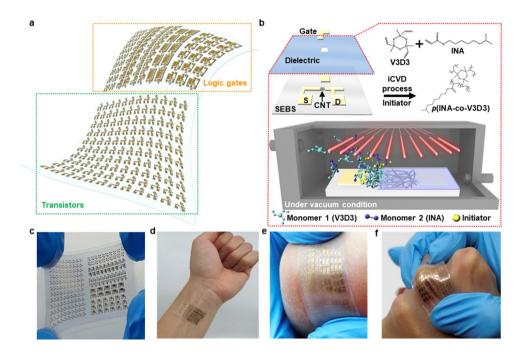

Third, intrinsically stretchable CNT transistors were developed, which was

enabled by the developments of thickness controllable, vacuum-deposited stretchable

dielectric layer and vacuum-deposited metal thin films. Previous works employed

strain-tolerant device designs which are based on the use of filamentary serpentine-

shaped interconnections, which severely sacrifice the device density. The developed

stretchable dielectric, compatible with the current vacuum-based microfabrication

technology, exhibited excellent insulating properties even for nanometer-range

thicknesses, thereby enabling significant electrical performance improvements such

as low operation voltage and high device uniformity/reproducibility, which has not

been realized in the most advanced intrinsically stretchable transistors of today.

Keywords: carbon nanotubes, flexible electronics, stretchable electronics,

wearable electronics, soft electronics

**Student number: 2014-31111**

iii

### **Contents**

| Abstract i                                                                  |

|-----------------------------------------------------------------------------|

| Contents····iv                                                              |

| List of Figures ······ vi                                                   |

| List of Tables X                                                            |

|                                                                             |

| Chapter 1. Introduction 1                                                   |

| 1.1 Discovery of CNTs and their benefits for soft electronic applications 1 |

| 1.2 Electrical sorting of CNTs····· 5                                       |

| 1.3 Deposition methods of solution-processed semiconducting CNTs······· 7   |

| 1.4 Conclusion                                                              |

| 1.5 References 24                                                           |

|                                                                             |

| Chapter 2. Stretchable Carbon Nanotube Charge-Trap Floating-Gate Memory     |

| and Logic Devices for Wearable Electronics                                  |

| 2.1 Introduction 32                                                         |

| 2.2 Experimental section 34                                                 |

| 2.3 Results and discussion 36                                               |

| 2.4 Conclusion 62                                                           |

| 2.5 References                                                              |

| Chapter 3. Wearable Electrocardiogram Monitor Using Carbon Nanotube |

|---------------------------------------------------------------------|

| Electronics and Color-Tunable Organic Light-Emitting Diodes 67      |

| 3.1 Introduction 67                                                 |

| 3.2 Experimental section 70                                         |

| 3.3 Results and discussion 73                                       |

| 3.4 Conclusion                                                      |

| 3.5 References 98                                                   |

|                                                                     |

| Chapter 4. Medium-Scale Electronic Skin Based on Carbon Nanotube    |

| Transistors with Vacuum-Deposited Stretchable Dielectric Film 102   |

| 4.1 Introduction 102                                                |

| 4.2 Experimental section 106                                        |

| 4.3 Result and discussion 111                                       |

| 4.4 Conclusion 135                                                  |

| 4.5 References 136                                                  |

### **List of Figures**

### Chapter 1

| Figure 1.1. First discovery of CNTs and development of their synthesis methods… 4                                               |

|---------------------------------------------------------------------------------------------------------------------------------|

| <b>Figure 1.2.</b> Sorting methods of semiconducting CNTs······ 6                                                               |

| Figure 1.3. Deposition methods of semiconducting CNTS and their application in                                                  |

| soft electronics 9                                                                                                              |

| Figure 1.4. Printing methods of semiconducting CNT thin films for active layer of                                               |

| transistors 13                                                                                                                  |

| Figure 1.5. Soaking methods for semiconducting CNT network deposition                                                           |

| Figure 1.6. Methods for aligned semiconducting CNT deposition 22                                                                |

|                                                                                                                                 |

| Chapter 2                                                                                                                       |

| Figure 2.1. Schematic illustration of the s-SWNT-based electronic devices as a                                                  |

| wearable array platform 40                                                                                                      |

| Figure 2.2. Schematic illustration of the fabrication process and exploded layer view                                           |

| of the wearable s-SWNT-based CTFM                                                                                               |

| Figure 2.3. Schematic illustration of the overall fabrication process in a large-scale                                          |

| view                                                                                                                            |

|                                                                                                                                 |

| <b>Figure 2.4.</b> Photographs of the wearable electronic platform on skin                                                      |

| Figure 2.4. Photographs of the wearable electronic platform on skin 43  Figure 2.5. Material and structural analysis of CTFM 44 |

| CTFM                                                                                                      |

|-----------------------------------------------------------------------------------------------------------|

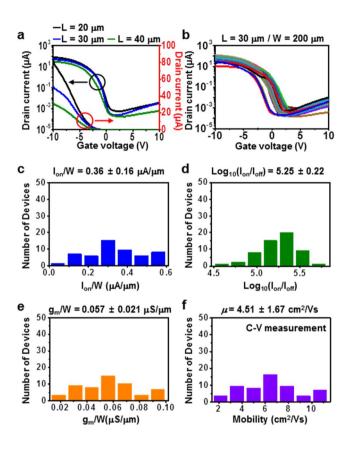

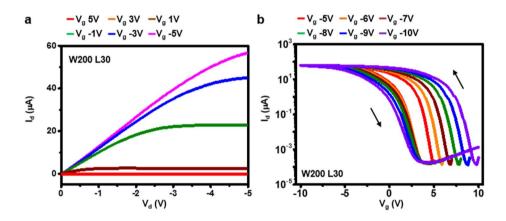

| <b>Figure 2.7.</b> Electrical characterization of transistors of CTFM 49                                  |

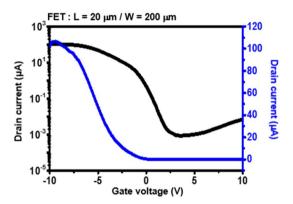

| <b>Figure 2.8.</b> Typical $I_d$ - $V_g$ curve of an s-SWNT field-effect transistor with $L=20~\mu m$     |

| and $W = 200 \mu$                                                                                         |

| Figure 2.9. $I_d$ - $V_d$ characteristics and $I_d$ - $V_g$ characteristics of CTFM under different $V_g$ |

| $(L = 30 \mu m)$                                                                                          |

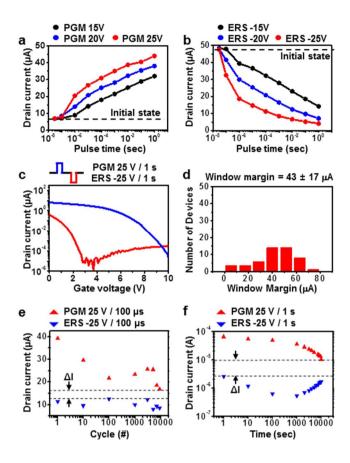

| <b>Figure 2.10.</b> Memory characteristics of CTFM 53                                                     |

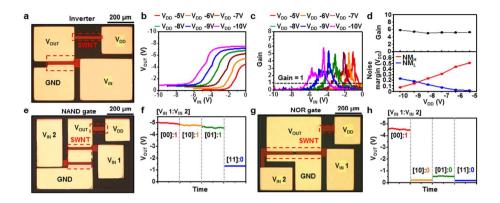

| Figure 2.11. Electrical characterization of the logic gates 55                                            |

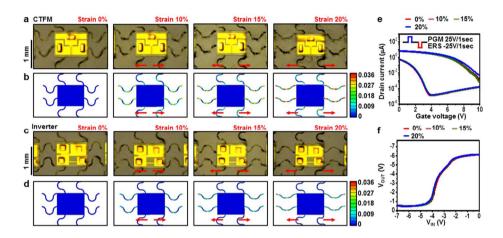

| Figure 2.12. Mechanical stability characterization of CTFM 59                                             |

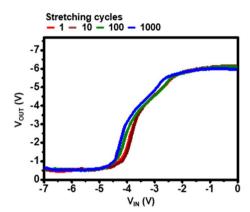

| Figure 2.13. VTCs of the inverter after cycled stretching tests. The number of                            |

| stretching cycles and applied strain are 1, 10, 100, and 1000 times and 20%,                              |

| respectively 60                                                                                           |

| Figure 2.14. Mechanical stability characterization of logic gates — 61                                    |

|                                                                                                           |

| Chapter 3                                                                                                 |

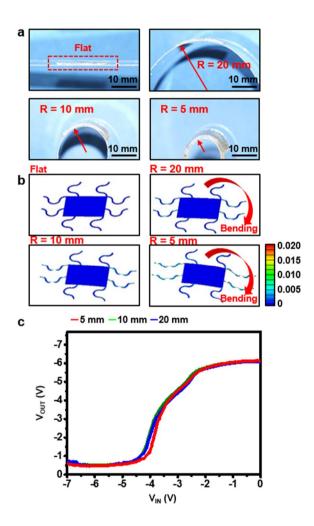

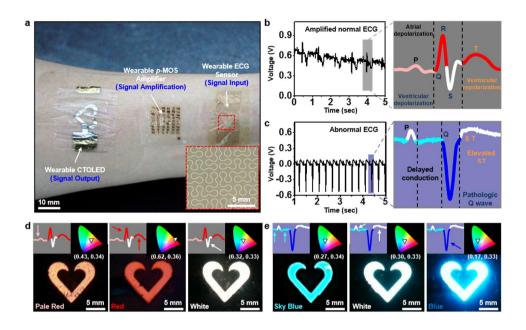

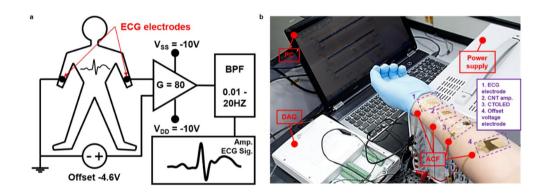

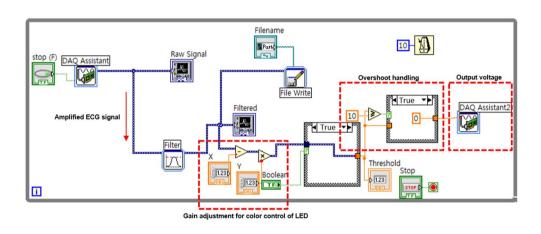

| Figure 3.1. Schematic illustration of the real-time wearable cardiac-monitoring                           |

| system 74                                                                                                 |

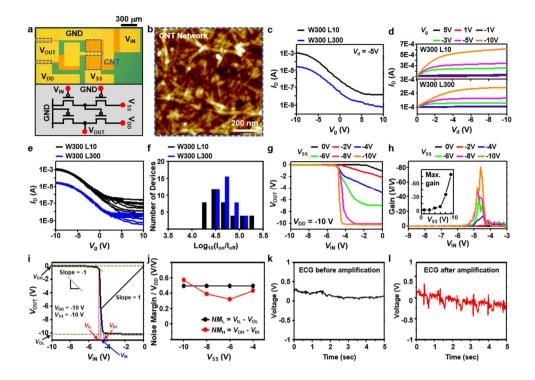

| Figure 3.2. Characterization of CNT signal amplifiers 77                                                  |

| Figure 3.3. Structural/material analysis of CTOLEDs and its working                                       |

| mechanism 83                                                                                              |

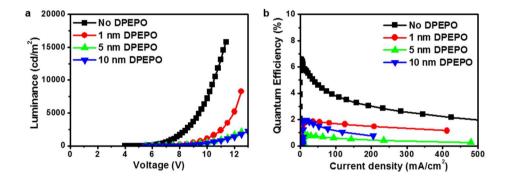

| Figure 3.4. J-V-L characteristics and EL spectra of the CTOLEDs with different EBL                        |

| thicknesses 84                                                                                            |

| Figure 3.5. EL spectra of the CTOLEDs with different EBL thicknesses and their    |

|-----------------------------------------------------------------------------------|

| corresponding CIE diagrams 85                                                     |

| Figure 3.6. Schematic illustration of the mechanism explaining the color tuning   |

| behavior of the OLED with different EBL thicknesses                               |

| Figure 3.7. Voltage-dependent luminance and quantum efficiency characteristics of |

| the fabricated CTOLED using EBLs with different thicknesses                       |

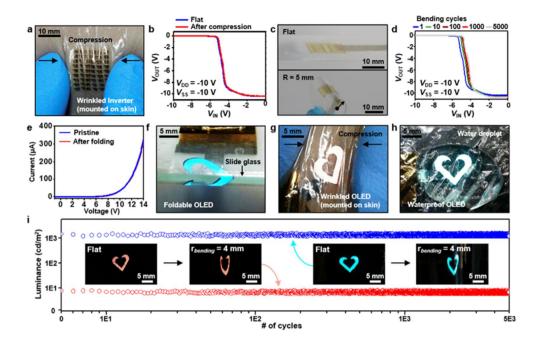

| Figure 3.8. Mechanical stability tests for CNT signal amplifiers and              |

| CTOLEDs90                                                                         |

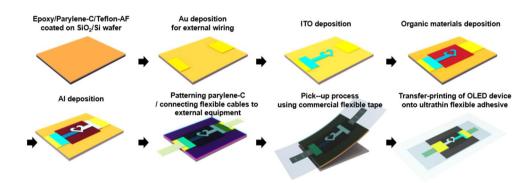

| Figure 3.9. Schematic illustration of the fabrication process of wearable         |

| CTOLEDs·····91                                                                    |

| Figure 3.10. Wearable health-monitoring system using CNT signal amplifiers and    |

| CTOLEDs······94                                                                   |

| Figure 3.11. ECG signal processing procedure and experimental setup 95            |

| Figure 3.12. A block diagram of LabVIEW-based software for controlling the color  |

| of the OLED according to the ECG amplitude change 96                              |

|                                                                                   |

| Chapter 4                                                                         |

| Figure 4.1. Intrinsically stretchable CNT electronic platform 113                 |

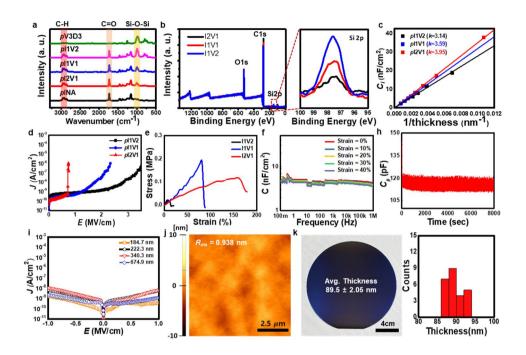

| Figure 4.2. Characterization of the stretchable dielectric film deposited using   |

| iCVD121                                                                           |

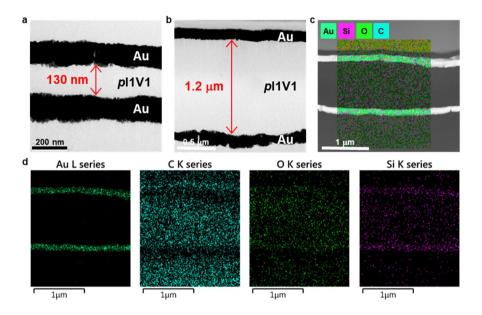

| Figure 4.3. Cross-sectional TEM image of MIM configuration employing the          |

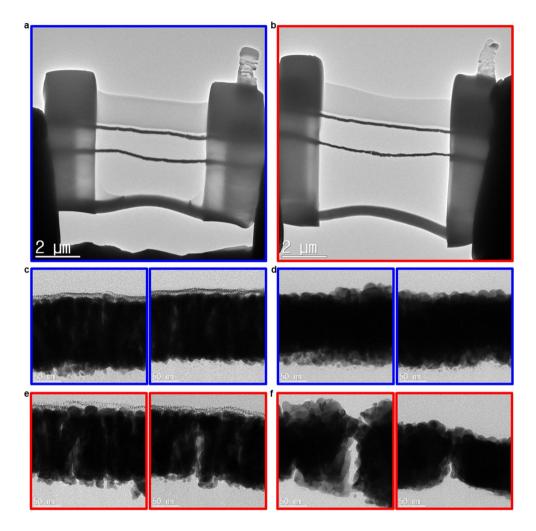

| stretchable dielectric film······ 122                                             |

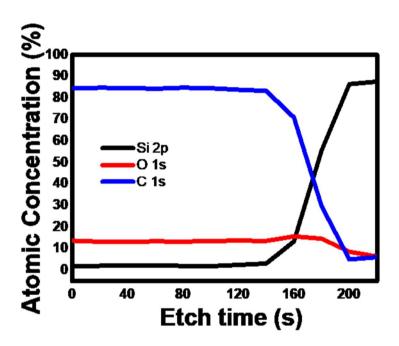

| <b>Figure 4.4.</b> Depth profile analysis of the deposited <i>p</i> I1V1 film······ 123       |

|-----------------------------------------------------------------------------------------------|

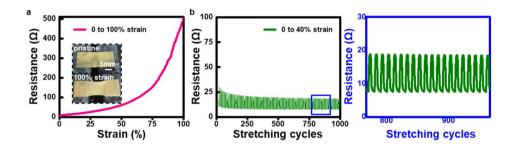

| <b>Figure 4.5.</b> Characterization of stretchable electrode 125                              |

| Figure 4.6. Cross-sectional TEM images of MIM samples before and after cyclic                 |

| stretching····· 126                                                                           |

| <b>Figure 4.7.</b> Photograph of the iCVD deposition on various substrates                    |

| Figure 4.8. Characterization of intrinsically stretchable CNT transistors and logic           |

| gates                                                                                         |

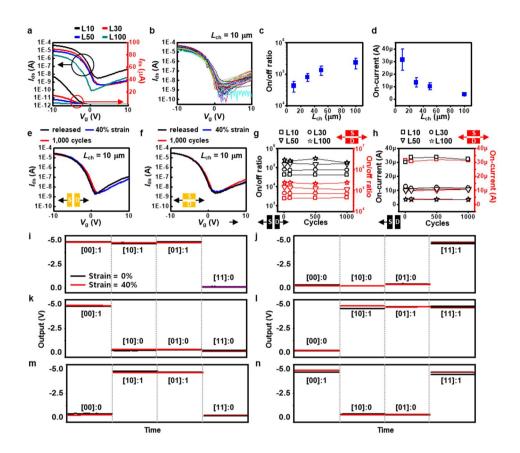

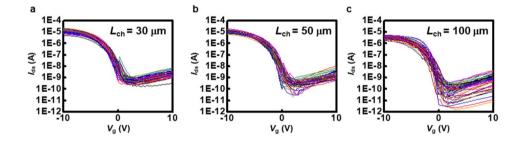

| Figure 4.9. Cumulative transfer curves of 150 transistors with varying channel                |

| lengths····· 131                                                                              |

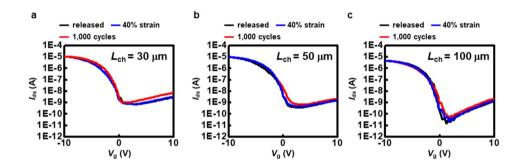

| Figure 4.10. Representative transfer curves of transistors with varying channel               |

| lengths, before stretching, after stretching at $40\%$ strain, and after stretching at $40\%$ |

| strain for 1,000 cycles······ 132                                                             |

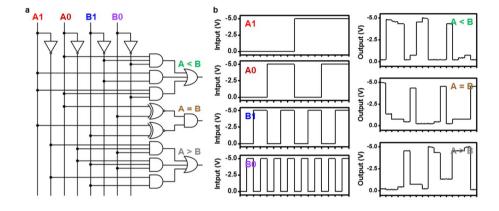

| Figure 4.11. Medium-level circuit demonstration of 2-bit magnitude                            |

| comparator 134                                                                                |

### **List of Tables**

### Chapter 1

| -                                                                                                |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| Table 1.1. Comparison of CNTs and other semiconducting materials for use as                      |  |  |  |  |  |  |  |  |

| channel material in soft electronics 3                                                           |  |  |  |  |  |  |  |  |

|                                                                                                  |  |  |  |  |  |  |  |  |

| Chapter 2                                                                                        |  |  |  |  |  |  |  |  |

| <b>Table 2.1.</b> High- and low-state noise margins of the inverter at different $V_{\rm DD}$ 56 |  |  |  |  |  |  |  |  |

|                                                                                                  |  |  |  |  |  |  |  |  |

| Chapter 4                                                                                        |  |  |  |  |  |  |  |  |

| Table 4.1. Flow rate of each monomer, deposition rate, and chemical                              |  |  |  |  |  |  |  |  |

| composition 110                                                                                  |  |  |  |  |  |  |  |  |

| <b>Table 4.2.</b> Mechanical properties of the copolymers from stretching tests 124              |  |  |  |  |  |  |  |  |

### **Chapter 1. Introduction**

### 1.1 Discovery of CNTs and their benefits for soft electronic applications

Recent efforts in the semiconductor material and device research have focused on the development of soft electronics with unusual form factors and functions, as they offer a wide variety of applications such as wearable and implantable biomedical devices, 1-3 electronic papers, 4-6 flexible and stretchable circuits, 7-9 and skin-inspired robotic systems with multiple sensing capabilities. 10-12 In often cases, a sustainable performance is required for these soft electronic devices during dynamic circumstances such as undergoing an extreme mechanical deformation. However, since most of the materials used in conventional planar electronic devices are not adequate due to their brittle and rigid nature, early stages of research focused on developing novel materials with excellent electrical and mechanical properties. A number of emerging materials have been reported including inorganic nanomaterials, 13-15 organics and small molecule materials, 16-18 metal oxides, 19-21 and two-dimensional (2D) nanomaterials. 22-24 Among the various materials, single-walled carbon nanotubes (CNTs) have stood out as an excellent and most adequate material choice owing to their high intrinsic carrier mobility, excellent mechanical stability, and good processability. 25-27 Table 1.1 shows a brief comparison on prospective materials for soft electronics, focusing on transistor properties, deformability, cost, processability, and stability.

CNTs are carbon-based cylindrical nanostructures with diameters generally in the range of a few nanometers and lengths in the range of few hundred nanometers, <sup>28-30</sup> and they can be categorized into single-walled nanotubes (SWNTs) and multi-walled nanotubes (MWNTs). While MWNTs are metallic, the electronic types (semiconducting or metallic) of SWNTs can be varied according to their chirality.<sup>31,32</sup> Ever since their first discovery in 1991,<sup>33</sup> the early stages of CNT research focused on their synthesis methods as depicted in Fig. 1.1. These methods include arc discharge, 34-36 laser ablation, 37,38 chemical vapor deposition (CVD), 39-41 and high-pressure carbon monoxide disproportionation (HiPCO). 42,43 As a result of intense research, significant progress have been achieved in terms of lowering the production cost, massive production with high selectivity of SWNTs, and control over the diameter, length, and morphology of the CNTs. However, the as-synthesized SWNTs cannot be directly applicable for use as channel material in transistor applications since the as-synthesized SWNTs comes in mixture of semiconducting and metallic types by nature. 44-46

\* Some contents of this chapter were published in *Nanotechnology* (2019, 30, 132001)

| Materials                    |                                                | Transistor Properties |                      |                                      | Deformability |                  |      |                             |           |

|------------------------------|------------------------------------------------|-----------------------|----------------------|--------------------------------------|---------------|------------------|------|-----------------------------|-----------|

|                              |                                                | On/off<br>ratio       | Mobility<br>(cm²/Vs) | On-<br>current<br>density<br>(µA/µm) | Flexible      | Stretch-<br>able | Cost | Solution-<br>Processability | Stability |

| CNT networks <sup>[25]</sup> |                                                | ~105                  | ~80                  | ~10                                  | 0             | 0                | Low  | 0                           | Excellent |

| Inorganic<br>nanomaterials   | Si NWs <sup>[13]</sup>                         | ~105                  | ~560                 | ~200                                 | 0             | ×                | High | 0                           | Excellent |

|                              | Si NMs <sup>[14]</sup>                         | ~105                  | ~490                 | NA                                   | 0             | ×                | High | ×                           | Excellent |

|                              | GaAS NWs <sup>[15]</sup>                       | ~105                  | NA                   | ~430                                 | 0             | ×                | High | 0                           | Excellent |

| Organics                     | DNTT <sup>[1]</sup>                            | ~107                  | ~1                   | ~0.12                                | 0             | Δ                | Low  | 0                           | Good      |

|                              | CONPHINE <sup>[2]</sup>                        | ~104                  | ~1                   | ~0.1                                 | 0             | 0                | Low  | 0                           | Good      |

|                              | Pentacene <sup>[16]</sup>                      | $\sim \! 10^6$        | ~2                   | ~1.6                                 | 0             | ×                | Low  | 0                           | Average   |

| Metal oxides                 | IZO <sup>[19]</sup>                            | ~108                  | ~10                  | ~0.1                                 | 0             | ×                | Low  | 0                           | Good      |

|                              | In <sub>2</sub> O <sub>3</sub> <sup>[20]</sup> | ~107                  | ~3                   | ~0.1                                 | 0             | ×                | Low  | 0                           | Good      |

|                              | a-IGZO <sup>[21]</sup>                         | ~103                  | ~10                  | ~0.1                                 | 0             | ×                | Low  | 0                           | Good      |

| 2D<br>nanomaterials          | MoS <sub>2</sub> <sup>[22]</sup>               | ~107                  | ~30                  | NA                                   | 0             | ×                | Low  | ×                           | Good      |

|                              | WSe <sub>2</sub> <sup>[23]</sup>               | ~106                  | ~250                 | NA                                   | 0             | ×                | Low  | ×                           | Average   |

|                              | Black<br>Phosporus <sup>[24]</sup>             | ~105                  | ~400                 | ~0.1                                 | 0             | ×                | Low  | ×                           | Poor      |

**Table 1.1.** Comparison of CNTs and other semiconducting materials for use as channel material in soft electronics.

1990 ~ 2000: First discovery of CNTs and development of their synthesis methods

Figure 1.1. First discovery of CNTs and development of their synthesis methods.

### 1.2 Electrical sorting of CNTs

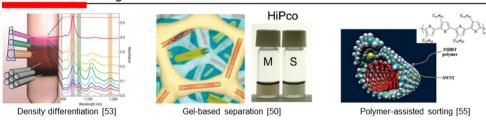

Extensive research efforts have been devoted to develop effective separation or sorting methods of as-synthesized SWNTs according to their electronic types (**Fig. 1.2**). In particular, various solution-based techniques have been developed that typically rely on the use of chirality-selective binding polymer dispersants and surfactants such as DNA-assisted sorting, <sup>47-49</sup> gel chromatography, <sup>50-52</sup> density gradient ultracentrifugation, <sup>53,54</sup> and conjugated polymer-assisted sorting. <sup>55,56</sup> These techniques have matured over the past decade such that it is not hard to purchase SWNT solutions with high purities of 99.999% in the market.

### 2000 ~ 2010: Sorting methods of s-CNTs

Figure 1.2. Sorting methods of semiconducting CNTs.

### 1.3 Deposition methods of solution-processed semiconducting CNTs

The deposition of semiconducting CNTs into a uniform thin film over a large area with optimized density is crucial in terms of minimizing the device-to-device performance variation and achieving high performances including high on/off ratios, carrier mobility, and current densities. Several deposition methods have been devised, such as soaking methods<sup>57-59</sup> and printing methods<sup>60-62</sup> for large-area deposition of random network semiconducting CNTs with excellent uniformity, and aligned deposition methods including Langmuir-Blodgett assembly,<sup>63,64</sup> solution shearing,<sup>65</sup> and AC-dielectrophoresis<sup>66-68</sup> for high electrical performances. Based on these techniques, the first generation of soft electronic devices based on SWNT thin film transistors are being reported, with novel applications including but not limit to user-interactive electronic skins (e-skins)<sup>69</sup> and stretchable/wearable circuits with multiple functionalities (Fig. 1.3).<sup>70,71</sup>

CNT field-effect transistors (FETs), the basic building blocks of soft CNT electronics, employ dense networks of semiconducting CNTs as the channel, which can reconfigure their percolation network with respect to the applied strain, thus maintaining their electrical performances during deformed states. Therefore, thin films of semiconducting CNT networks are highly desirable for soft electronics applications subject to extreme deformations. To form the networks, their deposition methods should be facile, reliable in terms of uniformity, and scalable to large area. In addition, the electrical performances of the CNT FETs such as carrier mobility, current on/off ratio, and on current density should be optimized.

CVD growth of CNTs is the most commonly used method to produce CNTs for electronic devices due to the superior electrical performances originating from relatively long nature of the synthesized CNTs and absence of bundles, which both reduce the number of tube-to-tube junctions that affect the resistance. However, they are not suitable for soft electronic applications, due to the following reasons: the thermal budget of the CVD-growth method is incompatible with most of the compliant substrates used in soft electronics and thus, the as-synthesized CNTs must be transferred from the original substrate. During such process, the CNTs are subject to damage, breakage, and consequent shortening, which results in the deterioration of the device performance. Furthermore, the elimination of the metallic CNTs after the transfer is troublesome, and their elimination often results in device-to-device performance variation as the metallic CNTs are randomly distributed inside the networks. One advantage for using solution-processed semiconducting CNTs is that post-treatment for elimination of metallic CNTs can be avoided. Furthermore, solution-processed semiconducting CNTs can be directly deposited in network forms on deformable substrates over a large area with relatively high uniformity.

# a 2010 ~ 2015: Deposition methods of solution-processed s-CNTs Solution shearing [65] b 2010 ~ present: Application of solution-processed s-CNTs in soft electronics User-interactive e-skin [69] Skin-mounted CNT circuit [70] CNT circuit for sweat monitoring [71]

**Figure 1.3.** (a) Deposition methods of semiconducting CNTS and (b) their application in soft electronics.

### 1.3.1 Printing methods for s-SWNT network deposition

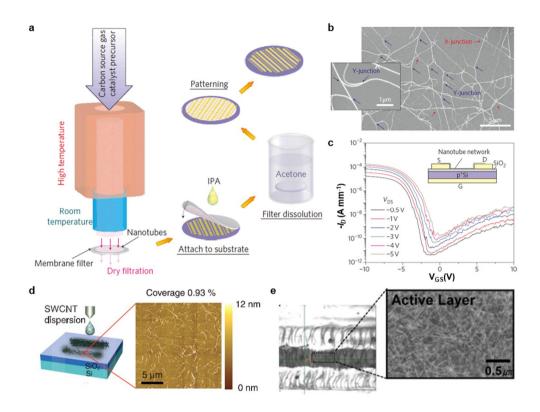

Printing methods such as dry transfer printing<sup>72-74</sup> or solution-based inkjet printing<sup>75-77</sup> are the most common methods to deposit various layers on deformable substrates. In 2011, Sun et al. reported the fabrication of high-performance FETs and integrated circuits on a flexible substrate using a customized dry transfer printing method of CVD-grown CNTs. 78 In specific, a simple gas-phase filtration method was used to directly collect the as-synthesized SWNTs on a membrane filter, which were then transferred from the filter to the target substrate. Figure 1.4a schematically illustrates such CNT synthesis and transfer processes, whereby the process is finalized by dissolving the filter in acetone, patterning the SWNT film by etching the outside region of the channel via O<sub>2</sub> plasma. Notably, the transferred CNT film consisted of individual and rather straight, long (~10 µm in length) nanotubes (Fig. 1.4b), which was a quite unique morphology when compared to those CNT networks prepared by other solution-based techniques. It can also be seen from the scanning electron microscope (SEM) image of Fig. 1.4b that the junctions formed by contacting nanotubes were mainly Y-type rather than X-type, which are known to have lower junction resistance than that of the X-junctions. The unique morphology of the transferred CNT film resulted in high performance of the FETs, with on/off ratios higher than  $10^6$  and effective device mobility of 35 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at a low  $V_{ds}$  of -0.5 V (Fig. 1.4c). However, the fabricated FETs suffered a severe loss in on/off ratios for those that contained metallic nanotubes within the transferred CNT film, thus leading to a low reliability in terms of device-to-device performance variation. For

such reasons, the direct transfer of CVD-grown CTs has not been considered a practical technique for soft electronic applications which require large-area uniformity.

Direct solution-based printing methods such as inkjet printing, on the other hand, can enable high-throughput and large-area fabrication of CNT FETs, with the possibility of avoiding additional photolithography or other expensive lithographic techniques. In this regard, several research groups have devoted extensive research efforts to investigate inkjet -printed SWNTs films for potential use in soft electronic applications. 79-81 Okimoto et al. successfully demonstrated that a relatively high on/off ratio of ~104 and a moderate carrier mobility of ~4 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> can be achieved in inkjet-printed CNT FETs by controlling the CNT density during inkjet printing (Fig. 1.4d). 77 In another research by Jung et al., the possibility of mass production of fully-printed flexible CNT devices have been demonstrated by combining roll-to-roll printing and inkjet printing methods.<sup>82</sup> The gate, dielectric layer, and source/drain electrodes were formed by roll-to-roll printing, followed by inkjet printing of CNT networks. Figure 1.4e shows an optical image of the source-channel-drain region, and the magnified view shows an SEM image of the inkjet-printed CNT networks. Except for a few variations in device performances which were mainly attributed to misalignment of the printed source/drain electrodes and thickness difference of the dielectric layers, the FETs exhibited negligible performance variation in terms of transfer and output curves. Using the scalable technique, the authors further reported the successful fabrication of various logic gates, ring oscillators, and radio frequency identification tags. In all, recent progresses in printing technology show promising results towards commercialization of CNT-based devices for soft electronic applications.

**Figure 1.4.** Printing methods of semiconducting CNT thin films for active layer of transistors. (a) Schematics of CNT growth, film collection by a filter, transfer, and patterning. (b) SEM image of transferred CNT film. (c) Transfer curve of a typical CNT FET with various applied drain voltages. (d) Schematic representation of CNT FET fabrication using inkjet printing and the corresponding atomic force microscope (AFM) image. (e) SEM image of the active layer of an all-printed CNT FET.

### 1.3.2 Soaking methods for semiconducting CNT network deposition

Soaking method refers to literal immersion of the target substrates into s-SWNT solutions for deposition of the CNT networks. It is the most common method adopted these days for fabrication of CNT FETs in soft electronic applications since it does not require the use of additional expensive tools or equipment such as printers, thereby potentially reducing the fabrication cost. Moreover, accurate control of the film density can be achieved by controlling the duration of immersion and concentration of the CNT solution. The CNTs deposited on unwanted regions of the substrate can then be easily removed by conventional photolithography processes and a brief expose to O<sub>2</sub> plasma. On these terms, the soaking methods have proven to be the most efficient tool for deposition of CNT films on deformable substrates using highly purified semiconducting CNT solutions.

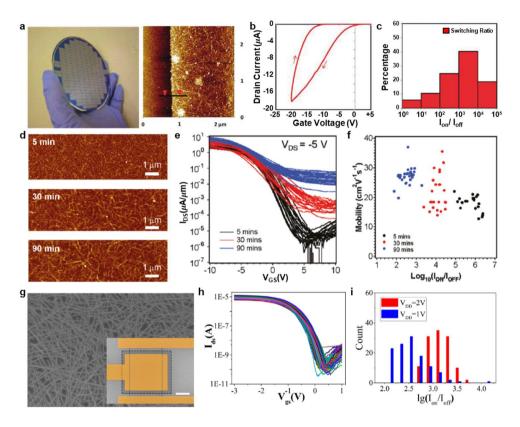

Early reports that adopted soaking methods used self-assembled monolayer (SAM) of aminosilane groups such as aminopropyltriethoxy silane (APTES) or aminopropyltrimethoxy silane (APTMS) to generate amine-terminated surface for deposition of CNTs films. 83-85 Due to the high affinity of CNTs to the amine-functionalized surfaces, large-area uniformity and controllable density could be achieved within considerably short soaking time. In 2012, Liyanage *et al.* demonstrated a wafer-scale fabrication of CNT FETs using APTMS as the SAM and soaking the wafer in a CNT solution (**Fig. 1.5a**). 86 To precisely control the uniformity and density of the deposited CNT film, a diluted solution was used with sufficient soaking time, which resulted in deposition of near-mono-layered networks of CNTs

with thickness of 2.3 nm (AFM image of **Fig. 1.5a**). Despite the excellent uniformity and density of the CNT networks, the electrical performances of the fabricated FETs exhibited rather low performances, requiring supply of high gate voltages to switch the devices (**Fig. 1.5b**) and moderate average on/off ratios of  $10^3 \sim 10^4$  (**Fig. 1.5c**). This is mainly ascribed to the shortening of the CNTs during the processes of sorting and diluting, and to the selection of materials for gate, dielectric, and source/drain.

Meanwhile, Takahashi et al. have reported a quick deposition of CNT film using poly-l-lysine as the SAM.<sup>87</sup> It can be seen from the AFM images in Fig. 1.5d that even for a short soaking time of 5 min, an abundance of SWNTs was deposited on the functionalized surface. The authors have systematically investigated the effect of soaking time on the electrical performances of SWNT-based FETs, where a tradeoff relationship between on-current density, carrier mobility, and on/off ratio was found with respect to the amount of soaking time (Figs. 1.5e and 1.5f). Longer soaking time resulted in denser networks of CNTs with multilayers, which consequently led to the loss of gate controllability on the CNTs and hence the FETs exhibited lower on/off ratios. On the contrary, since the amount of CNTs participating on current delivery significantly increased with longer soaking times, the on-current density as well as carrier mobility was found to be superior for the FETs with denser SWNT networks as their channel. The developed method proved to be highly efficient in terms of scalability and reliability, and in fact, several novel applications of CNTbased soft electronics have been further reported from the same research group in the following years.

More recently, CNT FETs with excellent electrical performances of low power consumption, high on/off ratios, large-scale performance uniformity, and low subthreshold voltage swing have been reported, which adopted the soaking method for deposition of CNT networks. Instead of using SAM to shorten the deposition time, sufficient soaking time of over 20 hours were allowed to ensure well-percolated networks of CNTs on 10 nm Y<sub>2</sub>O<sub>3</sub> dielectric (Fig. 1.5g). 88 FETs fabricated from such CNT network film exhibited excellent p-type transfer characteristics at low gate bias voltage of -3 to 1 V, with on/off ratios as high as  $\sim 10^5$  (Figs. 1.5h and 1.5i). The excellent uniformity and high performance of the developed FETs allowed for fabrication of medium-scale integrated circuits such as various logic gates, multiple stage ring oscillators, and 4-bit adders which comprises of 140 transistors. As such, the soaking method are deemed a promising method for future soft electronic applications, due to their high yield, large-scale processability, low cost, and no requirement on the thermal budget, although they can be time-consuming on some occasions. In addition, the resulting random network nature is highly tolerant of metallic nanotubes due to the averaging effect of massive CNTs, which is beneficial in that s-SWNT solutions with a 100% purity is nearly impossible to attain.

Figure 1.5. Soaking methods for semiconducting CNT network deposition. (a) Wafer-scale fabrication of CNT FETs using a soaking method, and an AFM image of a channel region. (b) Representative CNT FET transfer curve of. (c) Histogram of the on/off ratios of wafer-scale CNT FETs. (d) AFM images taken after different semiconducting CNT deposition times on poly-*l*-lysine-coated substrate using a soaking method. (e) Corresponding cumulative transfer characteristics and (f) on/off ratios and mobility measurements of CNT FETs. (g) SEM image of CNT networks deposited on a Y<sub>2</sub>O<sub>3</sub> dielectric after 20 h of soaking in s-SWNT solution. Electrical characterization of CNT FETs corresponding to (h) 120 transfer curves and (i) a histogram of the on/off ratios at different drain voltages.

### 1.3.3 Aligned CNT deposition methods

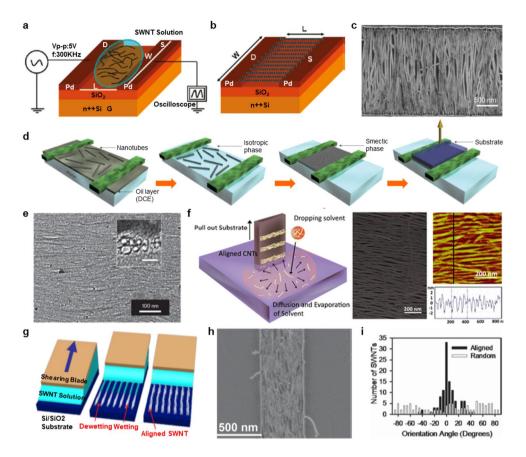

The deposition methods discussed in section 1.3.1 and 1.3.2 generally produces random networks of CNT films, and with recent advances in fabrication and design of FETs, they exhibit excellent electrical performances in terms of high on/off ratios and current carrying capacities. However, the carrier mobility of these devices, which are usually in the range of few tens of cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, can be substantially increased by adopting a different morphology of the deposited network. In fact, the critical limiting factor of carrier transport in CNT FETs is the number of tube-to-tube junctions within the CNT network, <sup>89-91</sup> which can be significantly reduced by aligning the nanotubes.

Among the various alignment techniques, one of the simplest is the acdielectrophoresis, where the CNTs inside a solution, placed in between two electrodes,

can be simply aligned by applying an ac-voltage to the electrodes (Figs. 1.6a and

1.6b). P2-94 Shekhar et al. reported that well-ordered arrays of nanotubes can be

generated, of which their density can be varied with respect to the concentration of

the CNT solution and the frequency of the applied ac-voltage. By optimization of

the control variables, maximum density of 30 CNTs/µm could be achieved (Fig. 1.6c).

Despite the simplicity and effectiveness of the alignment method, the acdielectrophoresis proved to be inadequate for fabrication of soft electronic devices

due to their nature of attracting and aligning metallic nanotubes, even with solutions

enriched with semiconducting CNTs. The FETs fabricated using the acdielectrophoresis method exhibited relatively low on/off ratios, and additional

methods were required to remove the unwanted metallic nanotubes, which consequently resulted in severe device-to-device performance in large-area applications.

In 2013, Cao et al. reported a scalable method for aligning CNTs based on Langmuir-Schaefer assembly.<sup>64</sup> Figure 4d schematically illustrates the process of the alignment technique, whereby an extremely high nanotube density of over 500 SWNTs/µm could be obtained (Fig. 1.6e). FETs fabricated using such dense networks of aligned CNTs exhibited unprecedented current carrying capacities of 120 µA/µm-1, but due to the existence of metallic nanotubes even with the use of 99% purity s-SWNT solutions, a low on/off ratio of  $\sim 10^3$  was reported. A year later, Joo et al. reported an evaporation-induced self-assembly method for aligning CNTs on the surface of a hydrophobic substrate. 95 Figure 1.6f depicts a brief schematic of the alignment method, where an organic solvent containing high-purity s-SWNTs is dropped on water, inducing diffusion of the organic solvent at the water-air interface to deposit aligned CNTs on a vertically-immersed hydrophobic substrate with packing densities of ~50 CNTs/μm (SEM image of Fig. 1.6f). Notably, the resulting FETs exhibited high on/off ratios of over 106, which is a direct result of using originally high-purity solution of 99.9% s-SWNTs and lesser chance to include metallic tubes within the aligned CNT films with comparably lower packing densities.

Park *et al.* investigated a solution shearing method, which was originally introduced to create densely packed single-crystalline structures of organic semiconductors with enhanced mobility, to produce well-ordered arrays of

semiconducting CNTs on alternating patterns of superhydrophobic and hydrophilic regions. Figure 1.6g illustrates a brief schematic of the shearing process for alignment of the CNTs and the resulting SEM image of the aligned CNTs is shown in Fig. 1.6h. The density of the nanotubes was approximately 150 ~ 200 CNTs/μm in the aligned region, with highly focused orientation angles below ± 15° (Fig. 1.6i). Comparative analysis on electrical performances of FETs based on aligned and random networked films of CNTs revealed a significant difference in on-current density and carrier mobility, where the FETs built from aligned CNTs exhibited current carrying capacity as high as 45 times higher and mobility 10 times higher than FETs of random network CNTs. It is worthwhile to mention that the high density of nanotubes compensated for on/off ratio of the FETs due to close proximity and multilayered nature of the CNTs, resulting in the reduction of electrostatic control of individual CNTs.

As verified from the reports on alignment methods of CNTs and their application as channel material in FETs, there are several limiting factors that can be a substantial obstacle for the use of aligned CNT films in soft electronic applications. First, many of the introduced methods are highly dependent on the purity of the s-SWNT solution, as even a single metallic nanotube can significantly deteriorate the electrical performances in terms of on/off ratio. Post treatments for elimination of metallic nanotubes are troublesome and they also affect the device-to-device performance uniformity, which is a critical issue in large-area applications. Second, the electrical performance boost of aligned CNT films is often limited to short-

channel devices, where the channel length is comparable to the length of the nanotubes. However, many of the FETs used in current soft electronic applications adopt larger dimensions than that of the nanotube length, focusing on the stability issues during deformed modes, not on reducing the device dimensions for increased packing density and higher speeds. These are some of the reasons why the random networks of CNTs based on soaking methods are mainly used in soft electronics these days, but there is no doubt that aligned CNT films will become needed in future applications that require higher carrier mobility such as in display applications.

Figure 1.6. Methods for aligned semiconducting CNT deposition. Schematics of (a) dielectrophoresis and (b) CNTs aligned as a result of dielectrophoresis. (c) SEM image of a typical dielectrophoresis assembly. (d) Schematic of aligned CNT deposition using the Langmuir–Schaeffer method. (e) TEM images of aligned CNT arrays transferred onto solid substrates, where the inset shows a high-resolution cross-sectional view. (f) Schematic of evaporation-induced self-assembly for aligned CNTs and SEM/AFM images showing the morphology of the deposited CNTs. (g) Schematic of the shearing method of aligned CNT deposition. (h) SEM image of the aligned CNTs in the hydrophilic region. (i) Histogram of the orientation angles of the shear-aligned CNTs.

### 1.4 Conclusion

As described throughout this chapter, CNTs are one of the most appealing candidate materials which are expected to dominate the soft electronics market, which undoubtedly will continue to grow. The biggest challenges faced by CNTs for soft electronic applications lies in the cost effective and scalable methods for sorting CNTs by electronic types, and in the processing and designed deposition of CNTs onto the mechanically compliant substrates. Careful considerations must be given to developing novel materials and processing technologies that allow fabrication of high-performance soft electronics based on semiconducting CNTs, such as novel stretchable dielectrics that support intimate interfacing with the CNTs for high carrier mobility and stretchable electrodes that support superior conducting properties during high levels of deformation with excellent mechanical stability.

With the aim of developing stretchable electronic devices based on semiconducting networks of CNTs, I have focused on developing robust technologies for forming semiconducting CNT networks on desired substrates without material dependencies, novel deposition of stretchable dielectric with low thermal budget, and fabrication technology for soft CNT devices with performance metrics comparable to those of inorganic-based devices on rigid substrates. In particular, I first developed stretchable CNT electronics based on unit devices of non-volatile memory, which were then used to develop stretchable integrated circuits in conjunction with wearable organic light-emitting devices for mobile health-monitoring, and finally medium-level stretchable CNT circuits for performing sophisticated functionalities.

#### 1.5 References

- Son, D. et al. Multifunctional wearable devices for diagnosis and therapy of movement disorders. Nat. Nanotechnol. 2014, 9, 397.

- 2. Xie, C. *et al.* Three-dimensional macroporous nanoelectronic networks as minimally invasive brain probes. *Nat. Mater.* **2015**, *14*, 1286.

- 3. Wang, S. *et al.* Skin electronics from scalable fabrication of an intrinsically stretchable transistor array. *Nature* **2018**, *555*, 83.

- 4. Chen, Y. *et al.* Flexible active-matrix electronic ink display. *Nature* **2003**, *423*, 136.

- Rogers, J. A. et al. Large-area rubber-stamped plastic sheets of electronics and microencapusulted electrophoretic inks. Proc. Natl. Acad. Sci. U. S. A. 2001, 98, 4835.

- 6. Heikenfeld, J. *et al.* A critical review of the present and future prospects for electronic paper. *J. Soc. Inf. Display* **2011**, *19*, 129.

- 7. Oh, J. Y. *et al.* Intrinsically stretchable and healable semiconducting polymer for organic transistors. *Nature* **2016**, *539*, 411, (2016).

- 8. Sekitani, T. *et al.* Organic nonvolatile memory transistors for flexible sensor arrays. *Science* **2009**, *326*, 1516.

- 9. Choi, C. *et al.* Human-eye-inspired soft optoelectronic device using high-density MoS2-graphene curved image sensor array. *Nat. Commun.* **2017**, *8*, 1664.

- 10. Takei, K. *et al.* Nanowire active-matrix circuitry for low-voltage macroscale artificial skin. *Nat. Mater.* **2010**, *9*, 821.

- 11. Cui, Y. *et al.* Electrical recording from hearts with flexible nanowire device arrays. *Nano Lett.* **2003**, *3*, 149.

- 12. Kim, Y. et al. A bioinspired flexible organic artificial afferent nerve. Science **2018**, 360, 998.

- 13. Viventi, J. *et al.* A conformal, bio-interfaced class of silicon electronics for mapping cardiac electrophysiology. *Sci. Transl. Med.* **2010**, *2*, 24ra22.

- 14. Miao, X. et al. Monolithic barrier-all-around high electron mobility transistor

- with planar GaAs nanowire channel. Nano Lett. 2013, 13, 2548.

- 15. Lee, J. *et al.* Ultra-wideband multi-Dye-sensitized upconverting nanoparticles for information security application. *Adv. Mater.* **2017**, *29*, 1603169.

- 16. Giri, G. *et al*. High-mobility, aligned crystalline domains of TIPS-pentacene with metastable polymorphs through lateral confinement of crystal growth. *Adv. Mater.* **2014**, *26*, 487.

- 17. Sheraw, C. D.*et al.* Organic thin-film transistor-driven polymer-dispersed liquid crystal displays on flexible polymeric substrates. *Appl. Phys. Lett.* **2002**, *80*, 1088.

- 18. Someya, T. *et al.* Conformable, flexible, large-area networks of pressure and thermal sensors with organic transistor active matrixes. *Proc. Natl. Acad. Sci. U. S. A.* **2005**, *102*, 12321.

- 19. Banger, K. K. *et al.* Low-temperature, high-performance solution-processed metal oxide thin-film transistors formed by a 'sol-gel on chip' process. *Nat. Mater.* **2011**, *10*, 45.

- 20. Kim, M.-G. *et al.* Low-temperature fabrication of high-performance metal oxide thin-film electronics via combustion processing. *Nat. Mater.* **2011**, *10*, 382.

- 21. Nomura, K. *et al.* Room-temperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors *Nature* **2004**, *432*, 488.

- 22. Chang, H.-Y. *et al.* High-performance, highly bendable MoS<sub>2</sub> transistors with high-k dielectrics for flexible low-power systems. *ACS Nano* **2013**, *7*, 5446.

- 23. Fang, H. *et al.* High-performance single layered WSe<sub>2</sub> p-FETs with chemically doped contacts. *Nano Lett.* **2012**, *12*, 3788.

- 24. Aji, A. S. et al. High mobility WS<sub>2</sub> transistors realized by multilayer graphene electrodes and application to high responsivity flexible photodetectors. Adv. Funct. Mater. 2017, 27, 1703448.

- Artukovic, E. et al. Transparent and flexible carbon nanotube transistors. Nano Lett. 2005, 4, 757.

- 26. Takenobu, T.; Takahashi, T. High-performance transparent flexible transistors using carbon nanotube films. *Appl. Phys. Lett.* **2006**, *88*, 033511.

- 27. Wang, C.; Zhang, J.; Ryu, K.; Badmaev, A.; Arco, L. G. D.; Zhou, C. Wafer-scale fabrication of separated carbon nanotube thin-film transistors for display applications. *Nano Lett.*, **2009**, *9*, 4285.

- 28. Cao, Q.; Rogers, J. A. Ultrathin films of single-walled carbon nanotubes for electronics and sensors: a review of fundamental and applied aspects. *Adv. Mater.* **2009**, *21*, 29.

- 29. Hu, L.; Hecht, D. S.; Gruner, G. Carbon nanotube thin films: fabrication, properties, and applications. *Chem. Rev.* **2010**, *110*, 5790.

- 30. Rouhi, N.; Jain, D.; Burke, P. J. High-performance semiconducting nanotube inks: Progress and prospects. *ACS Nano*, **2011**, *5*, 8471.

- 31. Strano, M. S. *et al.* Electronic structure control of single-walled carbon nanotube functionalization. *Science* **2003**, *301*, 1519.

- 32. O'Connell, M. J.; Eibergen, E. E.; Doorn, S. K. Chiral selectivity in the charge-transfer bleaching of single-walled carbon-nanotube spectra *Nat. Mater.* **2005**, *4*, 412.

- 33. Iijima, S. Helical microtubules of graphitic carbon. *Nature* **1991**, *354*, 56.

- 34. Iijima, S.; Ichihashi, T. Single-shell carbon nanotubes of 1-nm diameter. *Nature* **1993**, *363*, 603.

- 35. Gamaly, E. G.; Ebbesen, T. W. Mechanism of carbon nanotube formation in the arc discharge. *Phys. Rev. B* **1995**, *52*, 2083.

- 36. Shi, Z. *et al.* Mass-production of single-wall carbon nanotubes by arc discharge method. *Carbon* **1999**, *37*, 1449.

- 37. Yudasaka, M.; Komatsu, T.; Ichihashi, T.; Iijima, S. Single-wall carbon nanotube formation by laser ablation using double-targets of carbon and metal. *Chem. Phys. Lett.* **1997**, *278*, 102.

- 38. Scott, C. D.; Arepalli, S.; Nikolaev, P.; Smalley, R. E. Growth mechanisms for single-wall carbon nanotubes in a laser-ablation process. *Appl. Phys. A* **2001**, *72*, 573.

- 39. Kong, J.; Cassell, A. M.; Dai, H. Chemical vapor deposition of methane for

- single-walled carbon nanotubes. Chem. Phys. Lett. 1998, 292, 567.

- 40. Che, G.; Lakshmi, B. B.; Martin, C. R.; Fisher, E. R. Chemical vapor deposition based synthesis of carbon nanotubes and nanofibers using a template method. *Chem. Mater.* **1998**, *10*, 260.

- 41. Bower, C.; Zhou, O. Zhu, W.; Werder, D. J.; Jin, S. Nucleation and growth of carbon nanotubes by microwave plasma chemical vapor deposition. *Appl. Phys. Lett.* **2000**, *77*, 2767.

- 42. Bronikowski, M. J.; Willis, P. A.; Colbert, D. T.; Smith, K. A.; Smalley, R. E. Gas-phase production of carbon single-walled nanotubes from carbon monoxide via the HiPco process: A parametric study. *J. Vac. Sci. Technol. A* **2001**, *19*, 1800.

- 43. Chiang, I. W. *et al.* Purification and characterization of single-wall carbon nanotubes obtained from the gas-phase decomposition of CO. *J. Phys. Chem. B* **2001**, *105*, 8297.

- 44. Hur. S. H. *et al.* Printed thin-film transistors and complementary logic gates that use polymer-coated single-walled carbon nanotube networks. *J. Appl. Phys.* **2005**, *98*, 114302.

- 45. Cao, Q. *et al.* Medium-scale carbon nanotube thin-film integrated circuits on flexible plastic substrates. *Nature* **2008**, *454*, 495.

- 46. Kim, S.; Kim, S.; Park, J.; Ju, S.; Mohammadi, S. Fully transparent pixel circuits driven by random network carbon nanotube transistor circuitry. *ACS Nano* **2010**, *4*, 2994.

- 47. Ming, Z. *et al.* DNA-assisted dispersion and separation of carbon nanotubes. *Nat. Mater.* **2003**, *2*, 338.

- 48. Zheng, M.; Semke, E. D. Enrichment of single chirality carbon nanotubes. *J. Am. Chem. Soc.* **2007**, *129*, 6084.

- 49. Tu, X. M.; Manohar, S.; Jagota, A.; Zheng, M. DNA sequence motifs for structure-specific recognition and separation of carbon nanotubes. *Nature* **2009**, 460, 250.

- 50. Tanaka, T. et al. Simple and scalable gel-based separation of metallic and

- semiconducting carbon nanotubes. Nano Lett. 2009, 9, 1497.

- Liu, H.; Feng, Y.; Tanaka, T.; Urabe, Y.; Kataura, H. Diameter-selective metal/semiconductor separation of single-wall carbon nanotubes by agarose gel. *J. Phys. Chem. C* 2010, 114, 9270.

- 52. Liu, H.; Nishide, D. Tanaka, T.; Kautaura, H. Large-scale single-chirality separation of single-wall carbon nanotubes by simple gel chromatography. *Nat. Commun.* **2011**, *2*, 309.

- 53. Arnold, M. S.; Green, A. A.; Hulvat, J. F.; Stupp, S. I.; Hersam, M. C. Sorting carbon nanotubes by electronic structure using density differentiation. *Nat. Nanotechnol.* **2006**, *1*, 60.

- 54. Hersam, M. C. Progress towards monodisperse single-walled carbon nanotubes. *Nat. Nanotechnol.* **2008**, *3*, 387.

- 55. Nish, A.; Hwang, J. Y.; Doig, J.; Nicholas, R. J. Highly selective dispersion of single-walled carbon nanotubes using aromatic polymers. *Nat. Nanotechnol.* **2007**, *2*, 640.

- 56. Lee, H. W. *et al.* Selective dispersion of high purity semiconducting single-walled carbon nanotubes with regionegular poly(3-alkylthiophene)s. *Nat. Commun.* **2011**, *2*, 541.

- 57. Snow, E. S.; Campbell, P. M.; Ancona, M. G.; Novak, J. P. High-mobility carbon-nanotube thin-film transistors on a polymeric substrate. *Appl. Phys. Lett.* **2005**, *86*, 033105.

- 58. Wang, C. *et al.* Extremely bendable, high-performance integrated circuits using semiconducting carbon nanotube networks for digital, analog, and radio-frequency applications. *Nano Lett.* **2011**, *12*, 1527.

- 59. Zhang, J. *et al.* Separated carbon nanotube macroelectronics for active matrix organic light-emitting diode displays. *Nano Lett.* **2011**, *11*, 4852.

- 60. Jung, M. *et al.* All-printed and roll-to-roll-printable 13.56-MHz-operated 1-bit RF tag on plastic foils. *IEEE Trans. Electron Devices* **2010**, *57*, 571.

- 61. Cho, J. H. et al. Printable ion-gel gate dielectrics for low-voltage polymer thin-

- film transistors on plastic. Nat. Mater. 2008, 7, 900.

- 62. Ha, M. *et al.* Printed, sub-3V digital circuits on plastic from aqueous carbon nanotube inks. *ACS Nano* **2010**, *4*, 4388.

- 63. Li, X. *et al.* Langmuir-Blodgett assembly of densely aligned single-walled carbon nanotubes from bulk materials. *J. Am. Chem. Soc.* **2007**, *129*, 4890.

- 64. Cao, Q. *et al.* Arrays of single-walled carbon nanotubes with full surface coverage for high-performance electronics. *Nat. Nanotechnol.* **2013**, *8*, 180.

- 65. Park, S. *et al.* Large-area assembly of densely aligned single-walled carbon nanotubes using solution shearing and their application to field-effect transistors. *Adv. Mater.* **2015**, *27*, 2656.

- Krupke, R.; Henrich, F.; Kappes, M. M.; von Lohneysen, H. V. Surface conductance induced dielectrophoresis of semiconducting single-walled carbon nanotubes. *Nano Lett.* 2004, 4, 1395.

- 67. Monica, A. H.; Papadakis, S. J.; Osiander, R.; Paranjape, M. Wafer-level assembly of carbon nanotube networks using dielectrophoresis. *Nanotechnology* **2008**, *19*, 085303.

- 68. Shekhar, S.; Stokes, P.; Khondaker, S. I. Ultrahigh density alignment of carbon nanotube arrays by dielectrophoresis. *ACS Nano* **2011**, *5*, 1739.

- 69. Wang, C. *et al.* User-interactive electronic skin for instantaneous pressure visualization. *Nat. Mater.* **2013**, *12*, 899.

- Koo, J. H. *et al.* Wearable electrocardiogram monitor using carbon nanotube electronics and color-tunable organic light-emitting diodes. *ACS Nano* 2017, *11*, 10032.

- 71. Zhang, H. *et al.* High-performance carbon nanotube complementary electronics and integrated sensor systems on ultrathin plastic foil. *ACS Nano* **2018**, *12*, 2773.

- 72. Cao, Q. *et al.* Highly bendable, transparent thin-film transistors that use carbon-nanotube-based conductors and semiconductors with elastomeric dielectrics. *Adv. Mater.* **2006**, *18*, 304.

- 73. Kang, S. J. et al. Printed multilayer superstructures of aligned single-walled

- carbon nanotubes for electronic applications. Nano Lett. 2007, 7, 3343.

- Ryu, K. et al. CMOS-analogous wafer-scale nanotube-on-insulator approach for submicrometer devices and integrated circuits using aligned nanotubes. Nano Lett. 2008, 9, 189.

- 75. Li, J. *et al.* Ink-jet printed thin-film transistors with carbon nanotube channels shaped in long strips. *J. Appl. Phys.* **2011**, *109*, 084915.

- 76. Nobusa, Y. *et al.* Inkjet printing of single-walled carbon nanotube thin-film transistors patterned by surface modification. *Appl. Phys. Lett.* **2011**, *99*. 183106.

- 77. Okimoto, H. *et al.* Tunable carbon nanotube thin-film transistors produced exclusively via inkjet printing. *Adv. Mater.* **2010**, *22*, 3981.

- 78. Sun, D.-M. *et al.* Flexible high-performance carbon nanotube integrated circuits. *Nat. Nanotechnol.* **2011**, *6*, 156.

- 79. Okimoto, H. *et al.* Ink-jet printing of a single-walled carbon nanotube thin film transistor. *Jpn. J. Appl. Phys.*, **2009**, *48*, 06FF03.

- 80. Beecher, P. *et al.* Ink-jet printing of carbon nanotube thin film transistors. *J. Appl. Phys.* **2007**, *102*, 043710.

- 81. Takenobu, T. *et al.* Ink-jet printing of carbon nanotube thin-film transistors on flexible plastic substrates. *Appl. Phys. Express* **2009**, *2*, 025005.

- 82. Noh, J. *et al.* Integrable single walled carbon nanotube network based thin film transistors using roll-to-roll gravure and inkjet *Org. Electron.* **2011**, *12*, 2185.

- 83. Liu, J. *et al.* Controlled deposition of individual single-walled carbon nanotubes on chemically functionalized templates. *Chem. Phys. Lett.* **1999**, *303*, 125.

- 84. Choi, K. H. *et al.* Controlled deposition of carbon nanotubes on a patterned substrate. *Surf. Sci.* **2000**, *462*, 195.

- 85. Li, H. *et al.* Super-"amphiphobic" aligned carbon nanotube films. *Angew. Chem. Int. Edit.* **2001**, *40*, 1743.

- 86. Liyanage, L. S. *et al.* Wafer-scale fabrication and characterization of thin-film transistors with polythiophene-sorted semiconducting carbon nanotube networks. *ACS Nano* **2012**, *6*, 451.

- 87. Takahashi, T.; Takei, K.; Gillies, A. G.; Fearing, R. S.; Javey, A. Carbon nanotube active-matrix backplanes for conformal electronics and sensors. *Nano Lett.* **2011**, *11*, 5408.

- 88. Chen, B. *et al.* Highly uniform carbon nanotube field-effect transistors and medium scale integrated circuits. *Nano Lett.* **2016**, *16*, 5120.

- 89. Buldum, A.; Lu, J. P. Contact resistance between carbon nanotubes. *Phys. Rev. B: Condens. Matter Mater. Phys.* **2001**, *63*, 161403.

- Garrett, M. P.; Ivanov, I. N.; Gerhardt, R. A.; Puretzky, A. A.; Geohegan, D. B. Separation of junction and bundle resistance in single wall carbon nanotube percolation networks by impedance spectroscopy. *Appl. Phys. Lett.* 2010, 97, 163105.

- 91. Barman, S. N.; LeMieux, M. C.; Baek, J.; Rivera, R.; Bao, Z. Effects of dispersion conditions of single-walled carbon nanotubes on the electrical characteristics of thin film network transistors. *ACS Appl. Mater. Interfaces* **2010**, 2, 2672.

- 92. Stokes, P.; Silbar, E.; Zayas, Y. M.; Khondaker, S. I. Solution processed large area field effect transistors from dielectrophoreticly aligned arrays of carbon nanotubes. *Appl. Phys. Lett.* **2009**, *94*, 113104.

- 93. Krupke, R.; Linden, S.; Rapp, M.; Hennrich, F. Thin films of metallic carbon nanotubes prepared by dielectrophoresis. *Adv. Mater.* **2006**, *18*, 1468.

- 94. Rutherglen, C.; Jain, D.; Burke, P. rf resistance and inductance of massively parallel single walled carbon nanotubes: Direct, broadband measurements and near perfect 50Ω impedance matching. *Appl. Phys. Lett.* **2008**, *93*, 083119.

- 95. Joo, Y.; Brady, G. J.; Arnold, S.; Gopalan, P. Dose-controlled, floating evaporative self-assembly and alignment of semiconducting carbon nanotubes from organic solvents. *Langmuir* **2014**, *30*, 3460.

# Chapter 2. Stretchable Carbon Nanotube Charge-Trap Floating-Gate Memory and Logic Devices for Wearable Electronics

## 2.1 Introduction

Along with the increasing interests in wearable electronics, significant advancements have been achieved in technologies for flexible and stretchable devices, such as flexible displays, 1,2 skin-based electronics, 3-6 high-sensitivity deformable sensors, 7-11 wearable human-machine interfaces, 12-14 and compliant energy devices. 15-19 These unconventional electronic, optoelectronic, and energy devices are core components for next-generation wearable electronic systems. Although previous breakthroughs have dramatically advanced related technologies, current electronic devices still suffer from practical problems. One of the most significant concerns is the use of inorganic layers for the active channels and dielectric of conventional electronic devices which may incur mechanical cracks and/or breakdown in repetitive deformations and consequent accumulation of fatigues. The mechanical mismatch between human tissues and inorganic semiconductors aggravates this problem, particularly in skin-based wearable devices.

Extensive research has been conducted to dissipate the induced strain in the channel and active regions, such as ultrathin thickness design approaches, 20 neutral

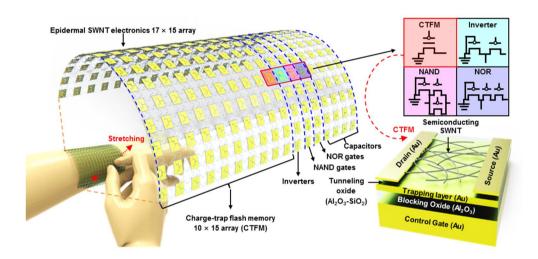

mechanical plane layouts. 21,22 and stretchable interconnections. 23-25 fundamental changes have been proposed to replace channel materials with soft ones, including graphene<sup>26-28</sup> and CNT. <sup>29-37</sup> Graphene may have issues in terms of the on/off ratio owing to its zero band gap, which is critical for digital circuits. Networks of semiconducting single-walled CNT (s-SWNT) are a promising candidate owing to their potential for high speed/performance electronics by the intrinsically high carrier mobility, 38-43 although challenges in terms of device structures/designs, material optimization, and fabrication/integration strategies exist. Therefore, efforts to develop stretchable/wearable types of memory modules and other electronic device components for advanced electronic circuits/systems are important. Here, we present materials and device design/fabrication strategies for an array (17 × 15) of s-SWNTbased stretchable electronic devices consisting of capacitors, charge-trap floatinggate memory (CTFM) units, and logic gates (inverters and NAND/NOR gates). Detailed material, electrical, and mechanical characterizations and theoretical analysis in mechanics provide useful insights in the design and development of s-SWNT-based wearable electronic systems.

<sup>\*</sup> The contents of this chapter were published in ACS Nano (2015, 9, 5585)

<sup>\*</sup> The contents of this chapter were also published in Ph. D. thesis of Donghee Son, "Non-volatile Memory Devices and Integrated Sensors for Multifunctional Stretchable and Bioresorbable Electronics

# 2.2 Experimental section

#### 2.2.1 Fabrication of s-SWNT-based wearable electronic devices

The detailed fabrication processes and materials used in the devices are described in 2.3 Results and discussion section, supplemented by Figs. 2.1, 2.2, and 2.3. Before the devices are transferred onto a human skin, the entire system is picked up from an SiO<sub>2</sub> temporary supporting substrate using water-soluble tape (3M, USA) and transferred onto a thin layer of polydimethylsiloxane ((PDMS), Dow Corning, USA). The water-soluble tape is dissolved using deionized (DI) water to release the devices, which are subsequently transfer-printed on the skin.

#### 2.2.2 Characterization of the device structures

The top-view images of the CTFMs, inverters, NAND/NOR gates, and capacitors are captured using an optical microscope (BX51 M, Olympus, USA). The density of the s-SWNT networks is examined using an atomic force microscope (Dimension Icon, Bruker, UK). The TEM images and the corresponding EDS data are taken using an electron microscope (JEM-2010, JEOL, Japan) operated at an acceleration voltage of 200 kV. For the cross-sectional analysis, the samples are cut using a focused ion beam (Quanta 3D FEG, FEI, USA) in the channel/trap region.

#### 2.2.3 Characterization of the electrical properties

The C-V measurements are conducted at a 100-kHz frequency at  $\pm 10~V$  using a parameter analyzer (B1500A, Agilent, USA) equipped with an LCR meter

and a probe station (MSTECH, Republic of Korea). The I-V curves are obtained using the same setup. The stretching tests are conducted using an automatic stretching stage that applies compressive and tensile strains in the x and y directions.

## 2.2.4 Finite element analysis (FEA) of the CTFMs and inverters

Finite element simulations are used to analyze the strain distribution of the CTFMs and inverters during the stretching (Figures 8b and d) and bending tests (Figure S6b). The CTFMs and inverters are modeled using four-node composite shell elements. The devices/substrates are modeled using eight-node solid elements. We assume perfect bonding (no-slip condition) between the devices and substrates. To simulate stretching, stretching boundary conditions are applied at the bottom surface of the substrate. To simulate bending, rotation boundary conditions corresponding to the given radius of curvature are applied at the bottom of the substrate. The isotropic linear elasticity represents the behavior of the materials of the flash memory devices and inverters. The Young's moduli of the CNT, Au, Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, and PI are 1 TPa, 77.2 GPa, 463 GPa, 73.1 GPa, and 2.5 GPa, respectively. The Poisson's ratios of CNT, Au, Al<sub>2</sub>O<sub>3</sub>, SiO<sub>2</sub>, and polyimide (PI) are 0.22, 0.42, 0.22, 0.17, and 0.34, respectively. The incompressible neo-Hookean model is used to represent the substrate:  $W = C_1(I_1 - 3)$  where W is the strain energy potential,  $I_1$  is the first invariant of the left Cauchy-Green tensor, and  $C_1$  (=3 kPa for the PDMS substrate) is a material parameter.

#### 2.3 Result and discussion

#### 2.3.1 Materials and device designs for the wearable CTFMs and logic gates

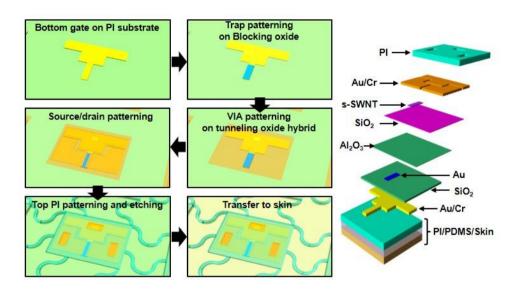

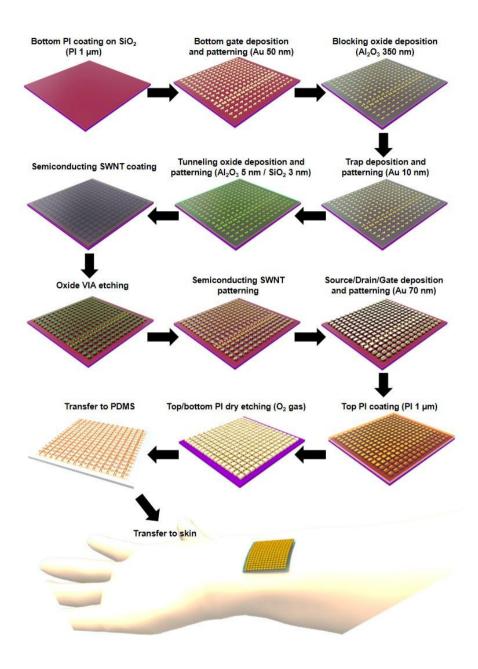

Figure 2.1 left depicts a schematic illustration of the wearable array of s-SWNT-based (99.9%-sorted s-SWNT, NanoIntegris Inc., USA) electronic devices composed of capacitors, CTFMs/transistors, and digital circuit components. The circuit diagrams (top) and layer information of the CTFM (bottom) are shown on the right. The ultrathin (< ~3 μm) and stretchable system design enables conformal integration of electronics onto the human skin. For mechanical robustness, the entire system is sandwiched between PI (Sigma Aldrich, USA; ~1 μm) ultrathin films. The detailed description of the fabrication processes and an exploded schematic illustration are shown in Fig. 2.2, and the corresponding large-scale view in Fig. 2.3. First, a PI layer (~1 µm) is spin-coated on a silicon oxide (SiO<sub>2</sub>) wafer, followed by the deposition of Cr/Au (~5 nm/~50 nm) back-gate electrodes using thermal evaporation. All electrodes and charge-trap layers are formed using photolithography and lift-off techniques. After the deposition of a blocking oxide (B<sub>ox</sub>) layer (~35-nmthick aluminum oxide (Al<sub>2</sub>O<sub>3</sub>)) by plasma enhanced atomic layer deposition (PEALD), ~10 nm of gold (Au) is deposited for the charge-trap layer of flash memories. Two consecutive layers of tunneling oxides (Al<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub>, ~5 nm/~3 nm) are deposited by PEALD (Al<sub>2</sub>O<sub>3</sub>) and e-beam evaporation (SiO<sub>2</sub>). Even though the use of organic dielectric layers would have been advantageous in terms of mechanical flexibility than the chosen inorganic dielectrics, Al<sub>2</sub>O<sub>3</sub> is used in this work due to its excellent thickness controllability and uniformity using PEALD, which in turn results

in high performance of the CTFM devices. The top surface of SiO<sub>2</sub> is functionalized to form an amine-terminated surface by immersing it into a poly-L-lysine solution (0.1 wt%, aqueous solution; Sigma Aldrich, USA) for 5 min. Then, random networks of SWNTs (whose average diameter and length are  $0.8 \sim 1.2$  nm and  $100 \sim 1,000$  nm, respectively) are deposited by dipping them into an s-SWNT solution (0.01 mg/mL, aqueous solution) for a few hours, followed by thorough rinsing using deionized (DI) water and isopropanol alcohol<sup>1</sup>. After annealing in a globe box at 200 °C for 1 h, isolation of the oxide layers and formation via connections follow. The fabrication of the other electronic devices uses similar procedures. But other devices, such as transistors in the logic circuits, do not contain the Au charge-trap layers and fabricated by using different patterns. The entire process is completed by depositing source/drain electrodes (Cr/Au, ~7 nm/70 nm), spin coating the top PI layer (~1 μm), and patterning the final serpentine/island layout by using photolithography and dry etching. Such design of island arrays connected with serpentine-shaped interconnects, with the assist of neutral mechanical plane designs, successfully protected the channel, dielectrics, and contacts during different bending and stretching modes.

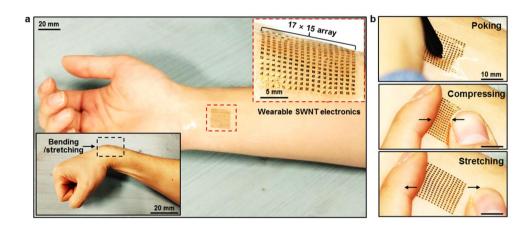

Figure 2.4a represents high-resolution camera images of wearable s-SWNT electronic devices, consisting of CTFMs/transistors ( $10 \times 15$  array), inverters ( $1 \times 15$  array), NAND/NOR gates ( $2 \times 15$  array), and capacitors ( $4 \times 15$  array). The inset at the bottom left (black box) shows the conformal lamination on the skin during bending deformations. The inset at the top right (red-dashed box) confirms the conformal contacts of the array through magnified observation. The use of ultrathin

PI films with serpentine structures, along with the van der Waals forces, successfully dissipates the induced strains during motions, and maintains intimate contacts. The detailed mechanical and electrical characterizations of these devices under reversible deformations with induced strains (~20%) are discussed later. Further deformations that can possibly occur during daily life activities are shown in **Fig. 2.4b.** The devices show no delamination and/or mechanical fractures during poking, compression, and stretching (top, middle, and bottom of the figure, respectively).

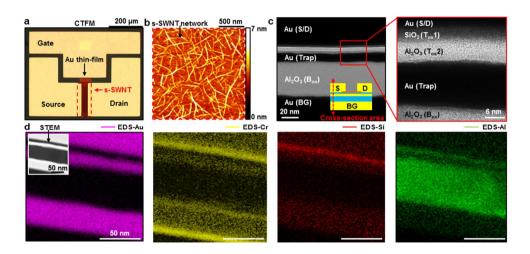

Figure 2.5a shows an optical microscope image (top view) of the CTFM with the s-SWNT channel and Au thin-film trap layer. The red-dashed box highlights the active area. The atomic force microscopy (AFM) image shows the magnified view of the s-SWNT networks in the channel (Figure 2.5b). It has been reported that random networks of SWNTs are well percolated if the density of the connected SWNTs exceeds a certain threshold.<sup>44</sup> This percolation threshold can be approximately quantified by using the number density (per unit area;  $\rho$ ), in which the average distance between SWNTs,  $1/\rho^{1/2}$ , equals to their average lengths, i.e.,  $\rho_{th}$  ~ 1/<SWNT length><sup>2</sup>. The estimated unit density of the s-SWNT networks is approximately  $30 \sim 40$  tubes/ $\mu$ m<sup>2</sup>: given the density, length, and device dimensions (channel lengths of 20, 30, and 40 µm), it can be concluded that the percolation of SWNTs is successfully formed to constitute an electrically conductive path between the source and drain electrodes. 45 Further improvements in the percolation of SWNT networks can be achieved by scaling down the channel length using industry facilities. To understand the structural compositions of the CTFMs, cross-sectional

transmission electron microscopy (TEM) and energy-dispersive X-ray spectroscopy (EDS) images are presented in **Figs. 2.5c** and **2.5d**, respectively. The magnified TEM image (**Fig. 2.5c**, right) shows the source/drain (Cr/Au) electrodes ( $\sim$ 7 nm/70 nm), hybrid tunneling oxides composed of  $\sim$ 3 nm SiO<sub>2</sub> (T<sub>ox</sub>1) and  $\sim$ 5 nm Al<sub>2</sub>O<sub>3</sub> (T<sub>ox</sub>2),  $\sim$ 10-nm Au thin-film trap, and  $\sim$ 35 nm B<sub>ox</sub>, from top to bottom. The TEM images of the CTFM show no visible cracks or voids. The elements in each layer are confirmed by EDS data (**Fig. 2.5d**).

**Figure 2.1.** Schematic illustration of the s-SWNT-based electronic devices as a wearable array platform, which consists of memory units, capacitors, and logic circuits (left). Simple circuitry schematics (CTFM, inverter, and NAND/NOR gates) are shown in the top right colored sections. The bottom right frame shows the cross-sectional layer information of the CTFM.

**Figure 2.2.** Schematic illustration of the fabrication process and exploded layer view of the wearable s-SWNT-based CTFM.

**Figure 2.3.** Schematic illustration of the overall fabrication process in a large-scale view.

**Figure 2.4.** (a) Optical camera image of the array of s-SWNT electronic devices (17 × 15) composed of CTFMs, inverters, NAND/NOR gates, and capacitors. Conformal contacts are well made with a human skin. The insets show a magnified image (top right) and bending/stretching deformations (bottom left). (b) Deformed wearable s-SWNT devices under poking (top), compression (middle), and stretching (bottom).

**Figure 2.5.** (a) Optical microscope image of a CTFM (top view). The red-dashed box indicates the active channel region composed of a random network of s-SWNTs. (b) AFM image of the 99.9%-sorted s-SWNTs layer showing high density of percolated s-SWNT networks. (c) (Left) Cross-sectional TEM image of the CTFM and (right) its magnified view. (d) EDS images showing the elements of each layer: Au, Cr, Si, and Al, from left to right, respectively.

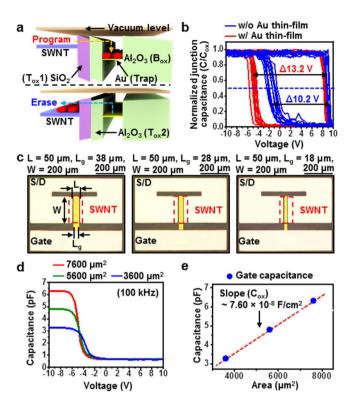

# 2.3.2 Mechanism of the CTFM and capacitance measurements