#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Ph.D. DISSERTATION

### Parallelism Management for Co-Located Parallel Applications

동시에 실행되는 병렬 처리 어플리케이션들을 위한 병렬성 관리

BY

Younghyun Cho

August 2020

DEPARTMENT OF ELECTRICAL ENGINEERING & COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

#### Ph.D. DISSERTATION

### Parallelism Management for Co-Located Parallel Applications

동시에 실행되는 병렬 처리 어플리케이션들을 위한 병렬성 관리

BY

Younghyun Cho

August 2020

DEPARTMENT OF ELECTRICAL ENGINEERING & COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

# Parallelism Management for Co-Located Parallel Applications

동시에 실행되는 병렬 처리 어플리케이션들을 위한 병렬성 관리

지도교수 Bernhard Egger 이 논문을 공학박사 학위논문으로 제출함 2020 년 4 월

> 서울대학교 대학원 전기 컴퓨터 공학부 조영현

Younghyun Cho의 공학박사 학위논문을 인준함 2020 년 6 월

| 위 위 | 원 장 | 이재진                  |

|-----|-----|----------------------|

| 부위  | 원장  | Bernhard Egger       |

| 위   | 원   | 염헌영                  |

| 위   | 원   | Lawrence Rauchwerger |

| 위   | 원   | David Isaac August   |

|     |     |                      |

#### Abstract

Running multiple parallel jobs on the same multicore machine is becoming more important to improve utilization of the given hardware resources. While co-location of parallel jobs is common practice, it still remains a challenge for current parallel runtime systems to efficiently execute multiple parallel applications simultaneously. Conventional parallelization runtimes such as OpenMP generate a fixed number of worker threads, typically as many as there are cores in the system, to utilize all physical core resources. On such runtime systems, applications may not achieve their peak performance when given full use of all physical core resources. Moreover, the OS kernel needs to manage all worker threads generated by all running parallel applications, and it may require huge management costs with an increasing number of co-located applications.

In this thesis, we focus on improving runtime performance for co-located parallel applications. To achieve this goal, the first idea of this work is to ensure spatial scheduling to execute multiple co-located parallel applications simultaneously. Spatial scheduling that provides distinct core resources for applications is considered a promising and scalable approach for executing co-located applications. Despite the growing importance of spatial scheduling, there are still two fundamental research issues with this approach. First, spatial scheduling requires a runtime support for parallel applications to run efficiently in spatial core allocation that can change at runtime. Second, the scheduler needs to assign the proper number of core resources to applications depending on the applications' performance characteristics for better runtime performance.

To this end, in this thesis, we present three novel runtime-level techniques to

efficiently execute co-located parallel applications with spatial scheduling. First,

we present a cooperative runtime technique that provides malleable parallel ex-

ecution for OpenMP parallel applications. The malleable execution means that

applications can dynamically adapt their degree of parallelism to the varying

core resource availability. It allows parallel applications to run efficiently at

changing core resource availability compared to conventional runtime systems

that do not adjust the degree of parallelism of the application.

Second, this thesis introduces an analytical performance model that can

estimate resource utilization and the performance of parallel programs in de-

pendence of the provided core resources. We observe that the performance of

parallel loops is typically limited by memory performance, and employ queue-

ing theory to model the memory performance. The queueing system-based ap-

proach allows us to estimate the performance by using closed-form equations

and hardware performance counters.

Third, we present a core allocation framework to manage core resources

between co-located parallel applications. With analytical modeling, we observe

that maximizing both CPU utilization and memory bandwidth usage can gen-

erally lead to better performance compared to conventional core allocation poli-

cies that maximize only CPU usage. The presented core allocation framework

optimizes utilization of multi-dimensional resources of CPU cores and memory

bandwidth on multi-socket multicore systems based on the cooperative parallel

runtime support and the analytical model.

Keywords: Runtime system, performance modeling, resource management

**Student Number**: 2013-20887

ii

### Contents

| $\mathbf{A}$ | Abstract    |        |                                                     |    |

|--------------|-------------|--------|-----------------------------------------------------|----|

| 1            | Intr        | oducti | ion                                                 | 1  |

|              | 1.1         | Motiv  | ation                                               | 1  |

|              | 1.2         | Backg  | round                                               | 5  |

|              |             | 1.2.1  | The OpenMP Runtime System                           | 5  |

|              |             | 1.2.2  | Target Multi-Socket Multicore Systems               | 7  |

|              | 1.3         | Contri | ibutions                                            | 8  |

|              |             | 1.3.1  | Cooperative Runtime Systems                         | 9  |

|              |             | 1.3.2  | Performance Modeling                                | 9  |

|              |             | 1.3.3  | Parallelism Management                              | 10 |

|              | 1.4         | Relate | ed Work                                             | 11 |

|              |             | 1.4.1  | Cooperative Runtime Systems                         | 11 |

|              |             | 1.4.2  | Performance Modeling                                | 12 |

|              |             | 1.4.3  | Parallelism Management                              | 14 |

|              | 1.5         | Organ  | nization of this Thesis                             | 15 |

| 2            | D           | • -    | Contint Colonialism with Communities Desertions Com |    |

| 2            | Dyr         | namic  | Spatial Scheduling with Cooperative Runtime Sys-    |    |

|              | $_{ m tem}$ | ıs     |                                                     | 17 |

|   | 2.1               | Overv                                                                         | iew                                                | 17                                           |

|---|-------------------|-------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------|

|   | 2.2               | Mallea                                                                        | able Workloads                                     | 19                                           |

|   | 2.3               | Coope                                                                         | erative OpenMP Runtime System                      | 21                                           |

|   |                   | 2.3.1                                                                         | Cooperative User-Level Tasking                     | 22                                           |

|   |                   | 2.3.2                                                                         | Cooperative Dynamic Loop Scheduling                | 27                                           |

|   | 2.4               | Exper                                                                         | imental Results                                    | 30                                           |

|   |                   | 2.4.1                                                                         | Standalone Application Performance                 | 30                                           |

|   |                   | 2.4.2                                                                         | Performance in Spatial Core Allocation             | 33                                           |

|   | 2.5               | Discus                                                                        | ssion                                              | 35                                           |

|   |                   | 2.5.1                                                                         | Contributions                                      | 35                                           |

|   |                   | 2.5.2                                                                         | Limitations and Future Work                        | 36                                           |

|   |                   | 2.5.3                                                                         | Summary                                            | 37                                           |

| 3 | Don               | formai                                                                        | nce Modeling of Parallel Loops using Queueing Sys- |                                              |

| 3 | ren               | ioi illai                                                                     | ice Modeling of Faraner Loops using Queueing Sys-  |                                              |

| 3 | tem               |                                                                               | ice windering of Faranei Loops using Queueing Sys- | 38                                           |

| 3 |                   | ıs                                                                            | iew                                                | <b>38</b>                                    |

| 3 | tem               | os<br>Overv                                                                   |                                                    |                                              |

| 3 | <b>tem</b> 3.1    | os<br>Overv                                                                   | iew                                                | 38                                           |

| 3 | <b>tem</b> 3.1    | os<br>Overv<br>Backg                                                          | iew                                                | 38<br>41                                     |

| ð | <b>tem</b> 3.1    | Overv<br>Backg<br>3.2.1                                                       | iew round                                          | 38<br>41<br>41                               |

| o | <b>tem</b> 3.1    | Overv<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3                                     | iew                                                | 38<br>41<br>41<br>43<br>46                   |

| o | tem<br>3.1<br>3.2 | Overv<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3                                     | iew                                                | 38<br>41<br>41<br>43<br>46<br>54             |

| J | tem<br>3.1<br>3.2 | Overv<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3<br>Queue                            | iew                                                | 38<br>41<br>41<br>43<br>46<br>54             |

| J | tem<br>3.1<br>3.2 | Overv<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3<br>Queue<br>3.3.1<br>3.3.2          | iew                                                | 38<br>41<br>41<br>43<br>46<br>54             |

| o | 3.1<br>3.2<br>3.3 | Overv<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3<br>Queue<br>3.3.1<br>3.3.2          | iew                                                | 38<br>41<br>41<br>43<br>46<br>54<br>54       |

| o | 3.1<br>3.2<br>3.3 | Overv<br>Backg<br>3.2.1<br>3.2.2<br>3.2.3<br>Queue<br>3.3.1<br>3.3.2<br>The S | iew                                                | 38<br>41<br>41<br>43<br>46<br>54<br>60<br>63 |

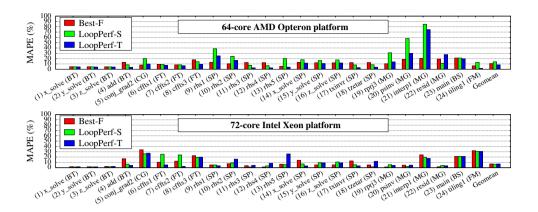

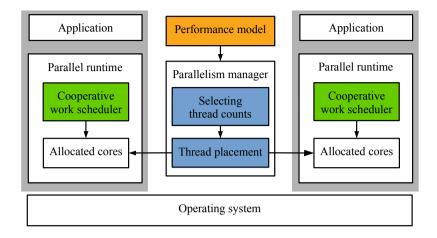

|   |     | 3.5.1   | 64-core AMD Opteron Platform                             | . 66  |

|---|-----|---------|----------------------------------------------------------|-------|

|   |     | 3.5.2   | 72-core Intel Xeon Platform                              | . 68  |

|   | 3.6 | Discus  | ssion                                                    | . 70  |

|   |     | 3.6.1   | Applicability of the Model                               | . 70  |

|   |     | 3.6.2   | Limitations of the Model                                 | . 72  |

|   |     | 3.6.3   | Summary                                                  | . 73  |

| 4 | Ma  | ximizi  | ng System Utilization via Parallelism Management         | 74    |

|   | 4.1 | Overv   | iew                                                      | . 74  |

|   | 4.2 | Backg   | ground                                                   | . 76  |

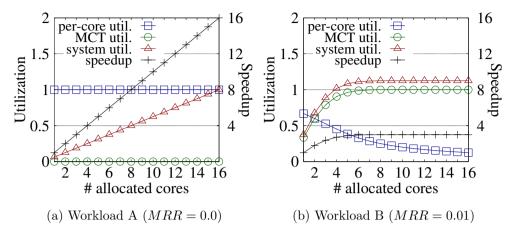

|   |     | 4.2.1   | Modeling Performance Metrics                             | . 76  |

|   |     | 4.2.2   | Our Resource Management Policy                           | . 79  |

|   | 4.3 | NuPo    | Co: Parallelism Management for Co-Located Parallel Loops | s 82  |

|   |     | 4.3.1   | Online Performance Model                                 | . 82  |

|   |     | 4.3.2   | Managing Parallelism                                     | . 86  |

|   | 4.4 | Evalu   | ation of NuPoCo                                          | . 90  |

|   |     | 4.4.1   | Evaluation Scenario 1                                    | . 90  |

|   |     | 4.4.2   | Evaluation Scenario 2                                    | . 98  |

|   | 4.5 | MOC     | A: An Evolutionary Approach to Core Allocation           | . 103 |

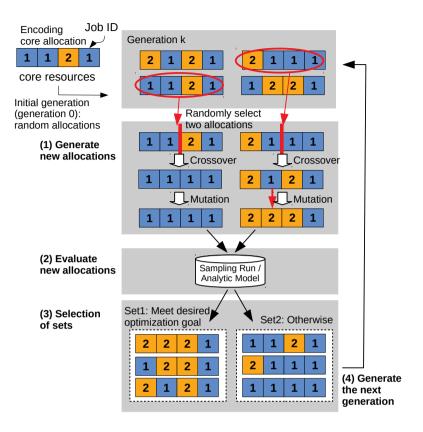

|   |     | 4.5.1   | Evolutionary Core Allocation                             | . 104 |

|   |     | 4.5.2   | Model-Based Allocation                                   | . 106 |

|   | 4.6 | Evalua  | ation of MOCA                                            | . 113 |

|   | 4.7 | Discus  | ssion                                                    | . 118 |

|   |     | 4.7.1   | Contributions and Limitations                            | . 118 |

|   |     | 4.7.2   | Summary                                                  | . 119 |

| 5 | Cor | nclusio | n and Future Work                                        | 120   |

|   | 5.1 | Concl   | usion                                                    | . 120 |

|              | 5.2   | Future  | e work                                                          | . 122 |

|--------------|-------|---------|-----------------------------------------------------------------|-------|

|              |       | 5.2.1   | Improving Multi-Objective Core Allocation                       | . 122 |

|              |       | 5.2.2   | Co-Scheduling of Parallel Jobs for HPC Systems                  | . 123 |

| $\mathbf{A}$ | Ada   | litiona | l Experiments for the Performance Model                         | 124   |

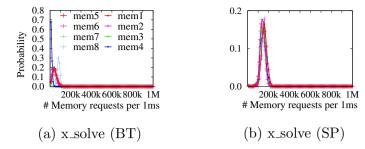

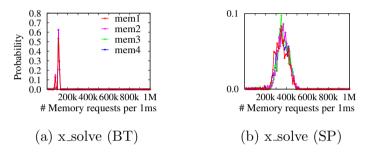

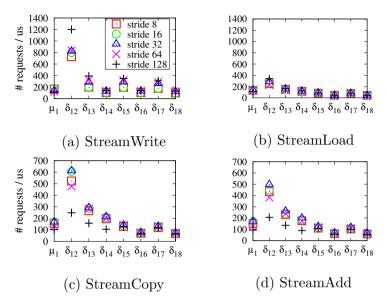

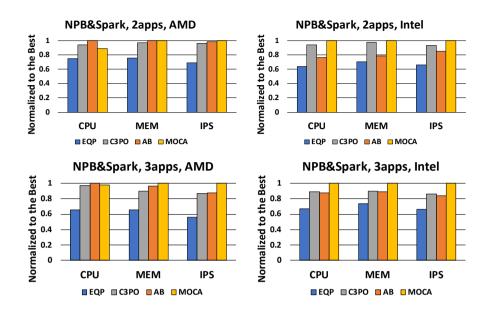

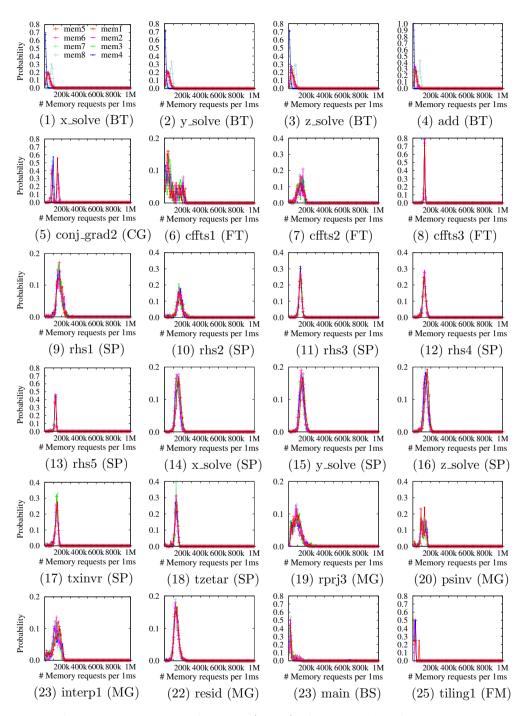

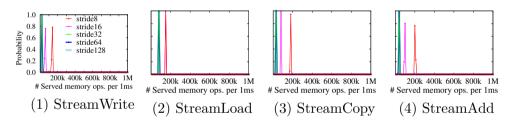

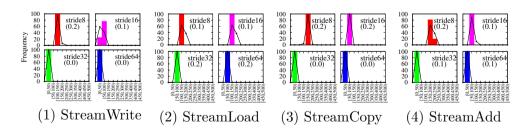

|              | A.1   | Memo    | ry Access Distribution and Poisson Distribution                 | . 124 |

|              |       | A.1.1   | Memory Access Distribution                                      | . 124 |

|              |       | A.1.2   | Kolmogorov Smirnov Test                                         | . 127 |

|              | A.2   | Additi  | onal Performance Modeling Results                               | . 134 |

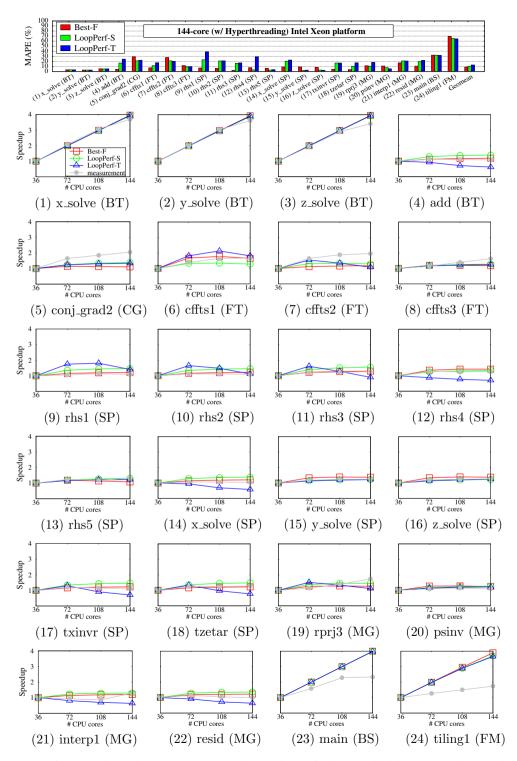

|              |       | A.2.1   | Results with Intel Hyperthreading                               | . 134 |

|              |       | A.2.2   | Results with Cooperative User-Level Tasking $\ \ldots \ \ldots$ | . 134 |

|              |       | A.2.3   | Results with Other Loop Schedulers                              | . 138 |

|              |       | A.2.4   | Results with Different Number of Memory Nodes                   | . 138 |

| В            | Oth   | er Res  | search Contributions of the Author                              | 141   |

|              | B.1   | Comp    | iler and Runtime Support for Integrated CPU-GPU System          | ıs141 |

|              | B.2   | Model   | ing NUMA Architectures with Stochastic Tool                     | . 143 |

|              | В.3   | Runtin  | me Environment for a Manycore Architecture                      | . 143 |

| 초            | 록     |         |                                                                 | 159   |

| A            | cknov | wledge  | ments                                                           | 161   |

## List of Figures

| 1.1 | Job scheduling in modern data centers                                        | 2  |

|-----|------------------------------------------------------------------------------|----|

| 1.2 | Execution model for parallel for loop                                        | 6  |

| 1.3 | SMP and multi-socket multicore systems                                       | 7  |

| 1.4 | Block diagram of target multi-socket multicore platforms $\ \ . \ \ . \ \ .$ | 8  |

|     |                                                                              |    |

| 2.1 | Spatial scheduling depending on the job flexibility                          | 20 |

| 2.2 | Execution model for OpenMP parallel sections                                 | 23 |

| 2.3 | Execution model for cooperative user-level tasking                           | 24 |

| 2.4 | Performance with different number of user-level tasks                        | 27 |

| 2.5 | Standalone application performance (OMP_parallel) $\ \ldots \ \ldots$        | 31 |

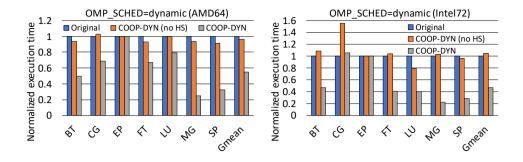

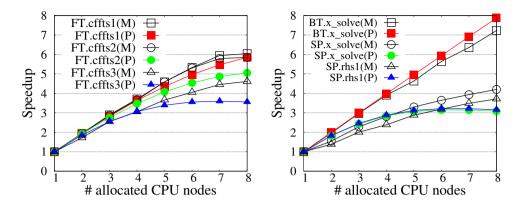

| 2.6 | Standalone application performance $(parallel\ for)$                         | 32 |

| 2.7 | Performance under COOP-ULT and COOP-DYN                                      | 32 |

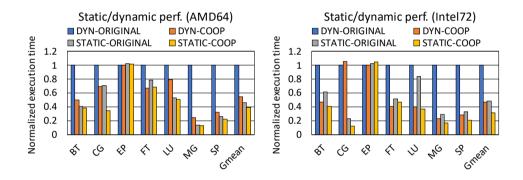

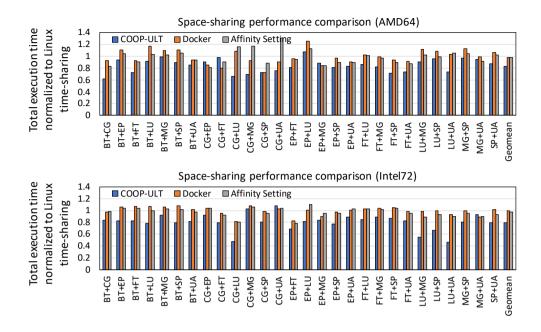

| 2.8 | Space-sharing performance comparison                                         | 33 |

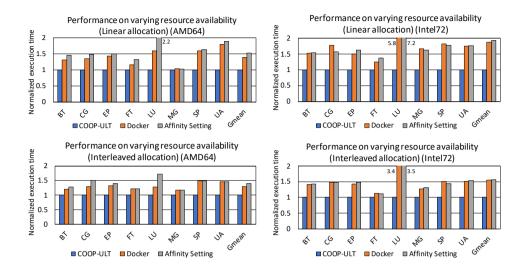

| 2.9 | Performance under varying resource availability                              | 34 |

|     |                                                                              |    |

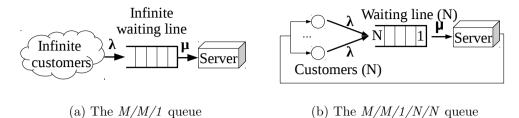

| 3.1 | Illustration of the $M/M/1$ and $M/M/1/N/N$ queueing systems .               | 42 |

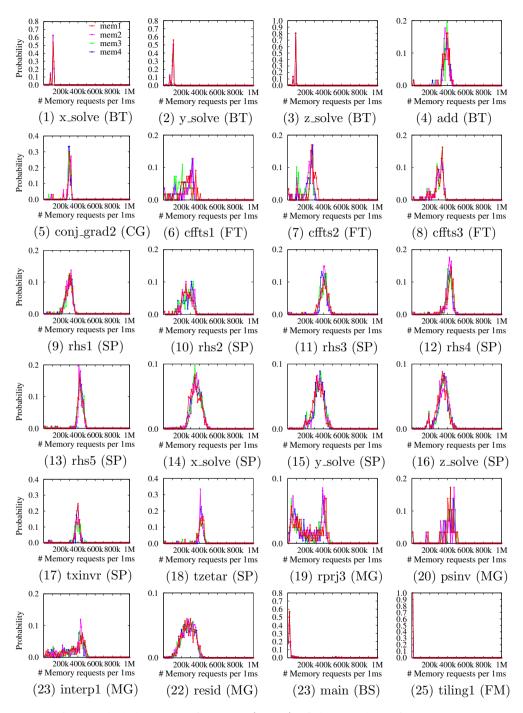

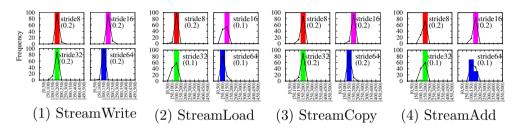

| 3.2 | PMF of the number of memory requests per time (AMD) $\ \ . \ \ . \ \ .$      | 47 |

| 3.3 | PMF of the number of memory requests per time (Intel)                        | 47 |

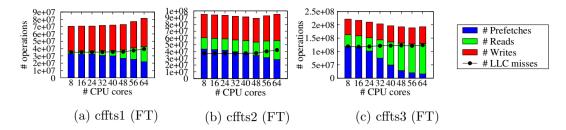

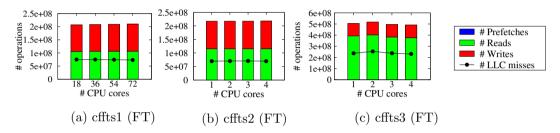

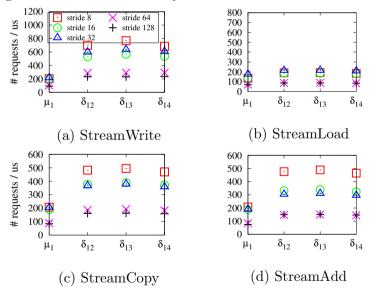

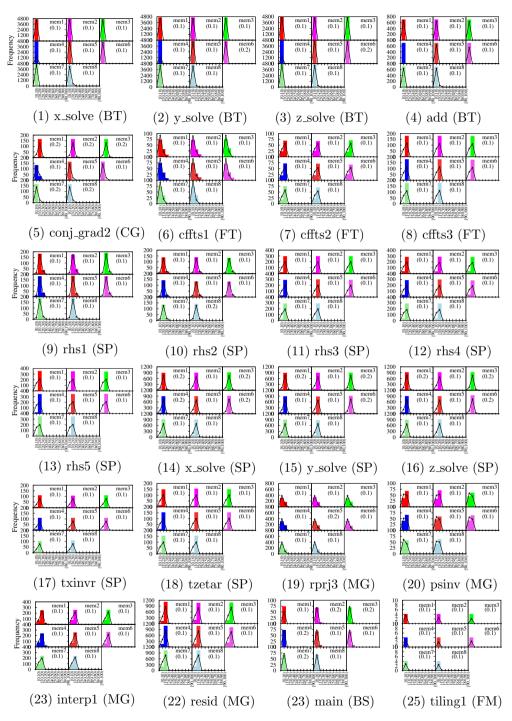

| 3.4 | Number of memory operations of parallel loops (AMD)                          | 48 |

| 3.5  | Number of memory operations of parallel loops (Intel)                      | 48  |

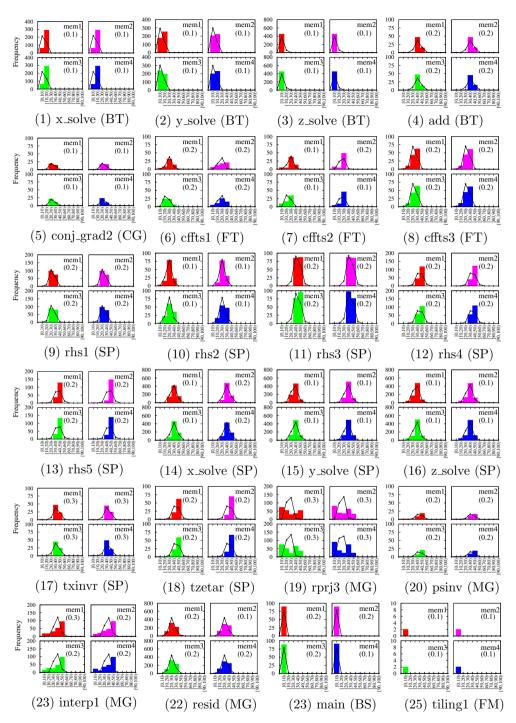

|------|----------------------------------------------------------------------------|-----|

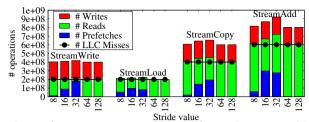

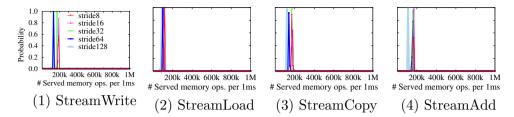

| 3.6  | Number of memory operations of synthetic workloads (AMD) $$                | 49  |

| 3.7  | Number of memory operations of synthetic workloads (Intel) $$              | 49  |

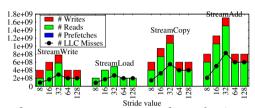

| 3.8  | Memory service rates for synthetic workloads (AMD)                         | 50  |

| 3.9  | Memory service rates for synthetic workloads (Intel) $\ \ldots \ \ldots$   | 50  |

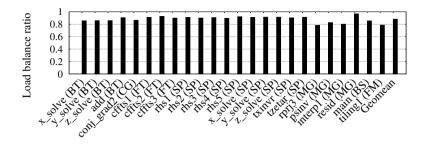

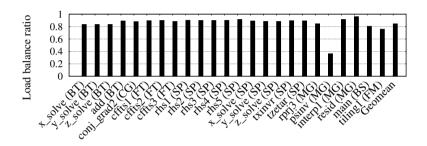

| 3.10 | Load balancing ratio of parallel loops                                     | 53  |

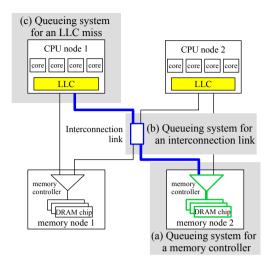

| 3.11 | A two-socket multicore system and data path                                | 54  |

| 3.12 | Hierarchical queueing systems                                              | 55  |

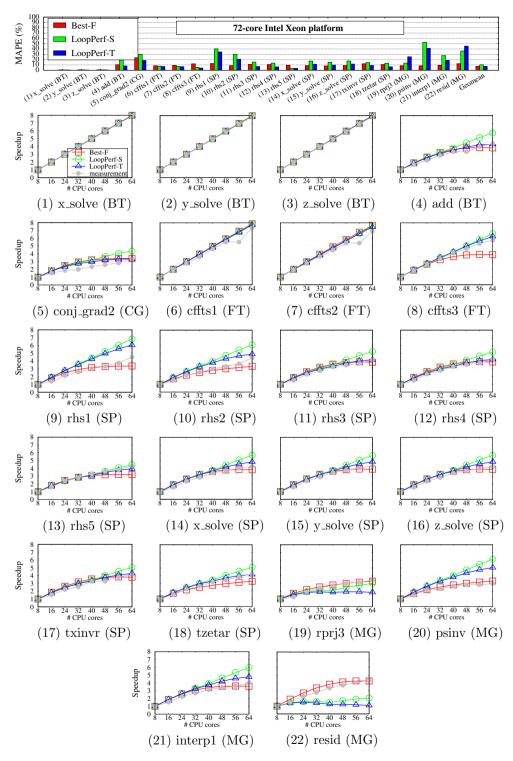

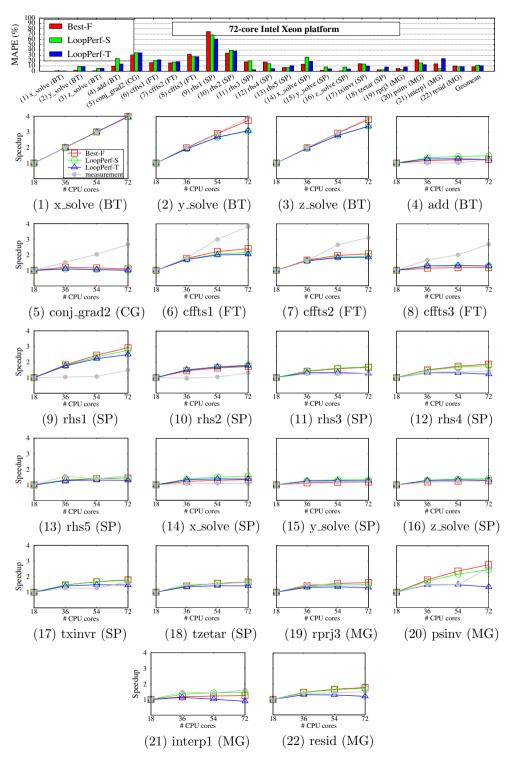

| 3.13 | MAPE of speedup prediction $\dots$                                         | 68  |

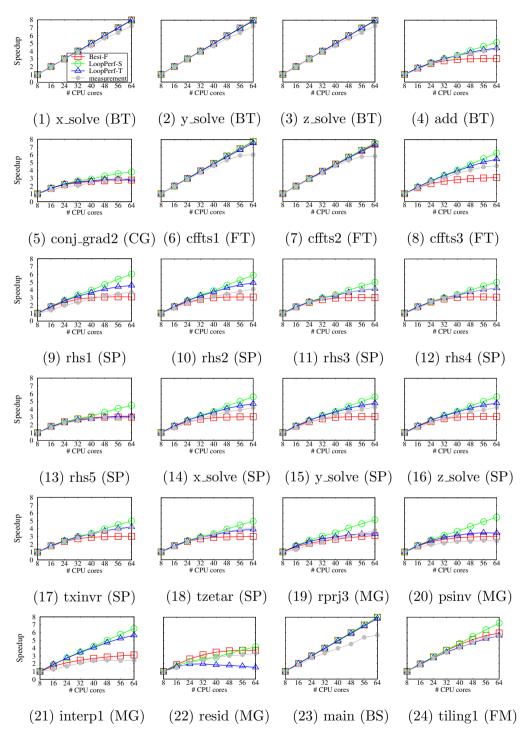

| 3.14 | Speedup prediction results (AMD) $\dots$                                   | 69  |

| 3.15 | Speedup prediction results (Intel)                                         | 71  |

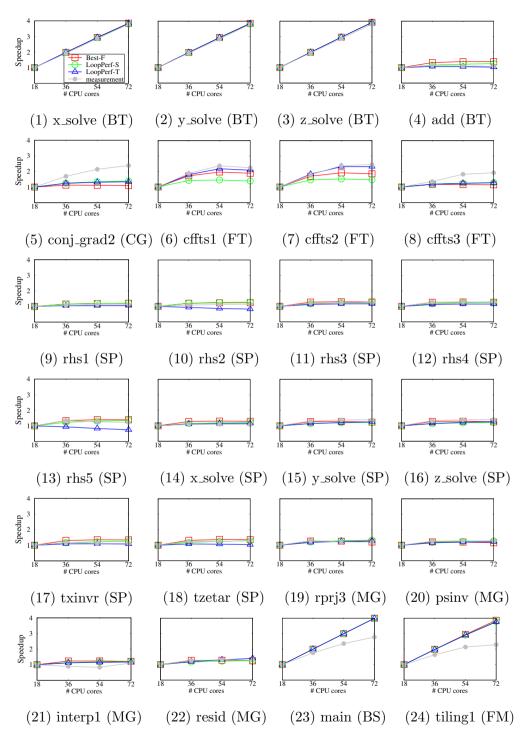

| 4.1  | The NuPoCo framework                                                       | 75  |

| 4.2  | Performance metrics                                                        | 79  |

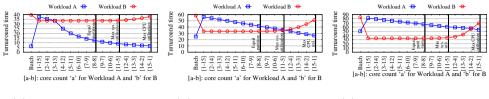

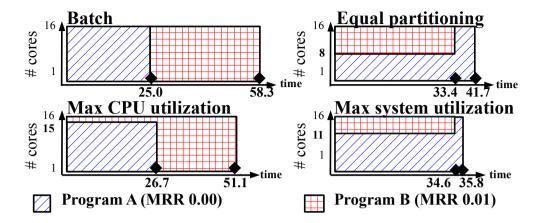

| 4.3  | Turnaround times of co-located workloads                                   | 80  |

| 4.4  | Performance of core allocation policies                                    | 81  |

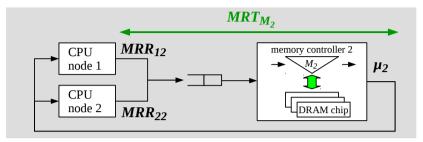

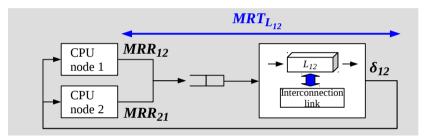

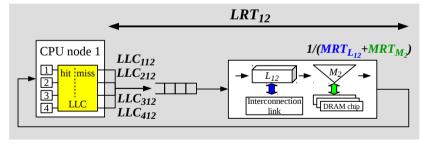

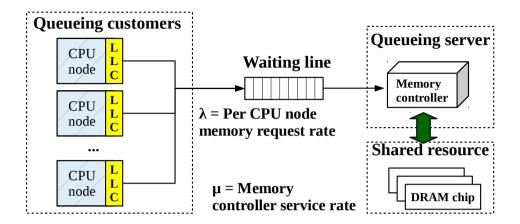

| 4.5  | Queueing system for individual memory controllers                          | 83  |

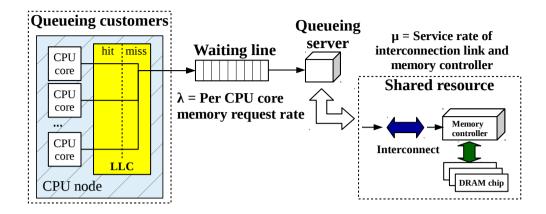

| 4.6  | Queueing system for CPU core utilization prediction                        | 84  |

| 4.7  | Speedup prediction validation                                              | 86  |

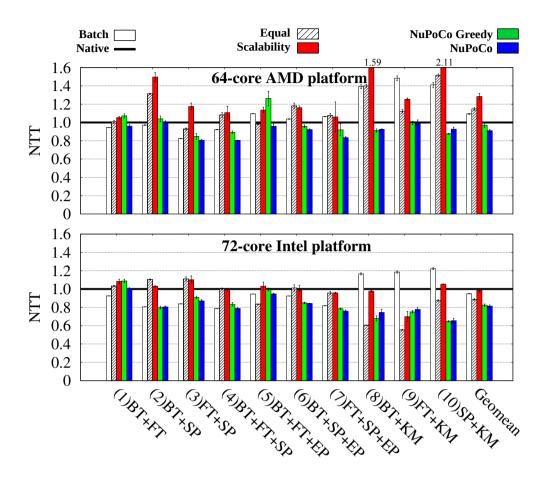

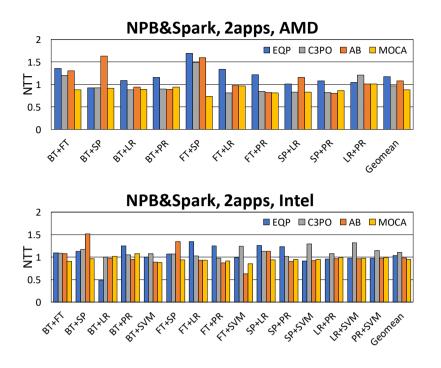

| 4.8  | Normalized turnaround time for co-located scenarios                        | 94  |

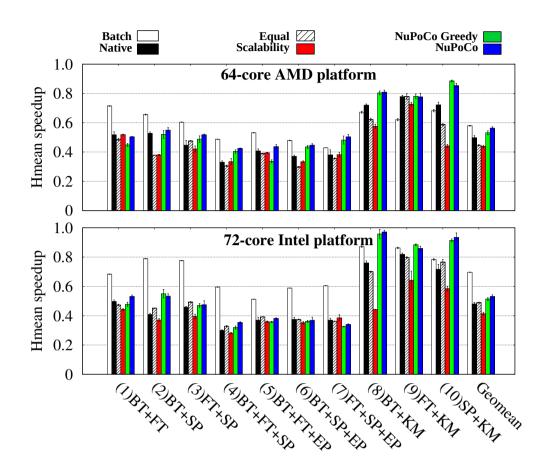

| 4.9  | Hmean of speedup for co-location scenarios $\dots \dots$ .                 | 96  |

| 4.10 | Trace visualization of a co-location scenario $\ \ldots \ \ldots \ \ldots$ | 98  |

| 4.11 | Normalized turnaround time for co-located scenarios                        | 102 |

| 4.12 | Overview of MOCA                                                           | 103 |

| 4.13 | Evolutionary core allocation                                               | 105 |

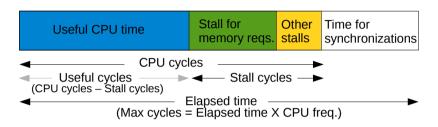

| 4.14 | CPU time breakdown and available measures                                  | 107 |

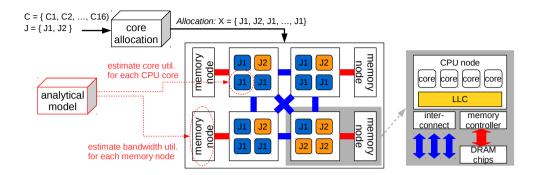

| 4.15 | Applying the analytical model                                              | 110 |

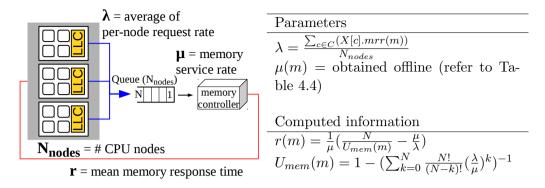

| 4.16 | Queueing system for an individual memory node                                                                                                                         |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

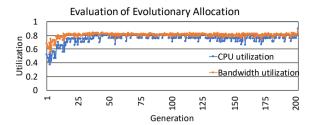

| 4.17 | An evolutionary process with the analytical model $\dots \dots \dots$ |

| 4.18 | Mixes of two applications (NPB and Spark)                                                                                                                             |

| 4.19 | Mixes of three applications (NPB and Spark) $\ \ldots \ \ldots \ \ldots \ 116$                                                                                        |

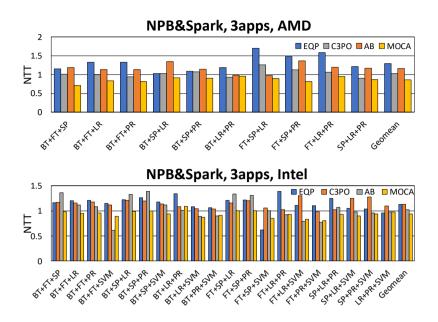

| 4.20 | Resource usage and IPS comparison for the co-location scenarios $117$                                                                                                 |

| A.1  | PMF of the number of memory requests per time (AMD) $\dots 125$                                                                                                       |

| A.2  | PMF of the number of memory requests per time (Intel) 126 $$                                                                                                          |

| A.3  | Histogram of the number of memory requests per time (AMD) $$ . 128                                                                                                    |

| A.4  | Histogram of the number of memory requests per time (Intel) $129$                                                                                                     |

| A.5  | PDF of the number of served memory operations for synthetic                                                                                                           |

|      | workloads (AMD) $\dots \dots \dots$                                   |

| A.6  | Histogram of the number of served memory operations for syn-                                                                                                          |

|      | thetic workloads (AMD)                                                                                                                                                |

| A.7  | PDF of the number of served memory operations for synthetic                                                                                                           |

|      | workloads (Intel)                                                                                                                                                     |

| A.8  | Histogram of the number of served memory operations for syn-                                                                                                          |

|      | thetic workloads (Intel) $\dots \dots \dots$                          |

| A.9  | Speedup prediction results on Intel with Hyperthreading 135                                                                                                           |

| A.10 | Speedup prediction results (AMD)                                                                                                                                      |

| A.11 | Speedup prediction results (Intel)                                                                                                                                    |

### List of Tables

| 3.1 | Selected parallel loops                                             |

|-----|---------------------------------------------------------------------|

| 3.2 | Input parameters of the queueing systems                            |

| 3.3 | Modeled performance information                                     |

|     |                                                                     |

| 4.1 | Target applications                                                 |

| 4.2 | Co-location scenarios                                               |

| 4.3 | Profiled application information                                    |

| 4.4 | Hardware-dependent parameters                                       |

| 4.5 | Target applications and their performance characteristics 114       |

|     |                                                                     |

| A.1 | Two-sample Kolmogorov-Smirnov test (AMD)                            |

| A.2 | Two-sample Kolmogorov-Smirnov test (Intel)                          |

| A.3 | Two-sample Kolmogorov-Smirnov test for synthetic workloads $133$    |

| A.4 | Scalability prediction accuracy for different work schedulers $139$ |

| A.5 | Prediction accuracy for varying memory configurations 140           |

### Chapter 1

### Introduction

#### 1.1 Motivation

Modern shared-memory multiprocessor systems are typically multi-socket multicore systems that consist of dozens of processor cores with an increasing number of CPU sockets and memory nodes to provide sufficient computation power and memory bandwidth. Today's parallel applications, however, are typically able to achieve only a fraction of the peak performance on such complex computer systems [58, 88]. Memory-intensive applications often cannot achieve the best performance when given full use of all available core resources because of the limited memory bandwidth and the non-uniform memory access (NUMA) property of multi-socket systems, while computation-intensive applications may under-utilize the memory system.

In modern data centers and high-performance computing (HPC) systems, running multiple parallel jobs on the same multicore machine is becoming more important to efficiently utilize the given hardware resources [41, 11, 93, 33].

Figure 1.1 Job scheduling in modern data centers.

For example, as shown in Figure 1.1, data centers typically use a cluster-level scheduler that decides which parallel jobs will be co-located on the same multicore node [25, 26, 48, 10, 93]. Co-location of parallel jobs may improve resource utilization if the co-located workloads have different resource requirements, e.g. CPU-intensive and memory-intensive workloads. Then, the runtime system manages multicore resources for the co-located workloads to meet the given optimization goal (e.g. reducing execution time). On the other hand, many parallel workloads are able to run on a varying number of core resources using either compiler/runtime support [53, 71, 40] or Linux's resource isolation API such as sched\_setaffinity and cgroup (as used in Docker [27]). In this context, allocating the proper number of core resources for co-located applications to optimize application performance and/or platform throughput has been an important topic of research in the compiler and runtime community [65, 72, 76, 75, 21, 81, 29, 28, 59, 91, 15]

While co-location of parallel jobs is already common practice, it still remains a challenge for current runtime systems to efficiently execute multiple parallel applications on modern multicore systems. Conventional parallelization runtime systems such as OpenMP [9] and Intel TBB [73] assume that each parallel application can utilize all existing hardware resources and thus generate threads, typically as many as there are cores in the given system, to utilize

all physical core resources. On such conventional runtimes, however, multiple parallel applications do not run efficiently. First, applications may not achieve their peak performance when given full use of all available core resources. Moreover, the execution model is not scalable for an increasingly large number of core resources because the OS kernel needs to manage all (kernel-level) threads generated by all running parallel applications. In this context, the runtime and OS community has pointed out that spatial scheduling is a scalable design for (future) multicore systems [5, 57, 90]. To overcome the scalability issue, the spatial scheduling approach provides distinct core resources to the co-located applications, and then the applications adapt their execution to the allocated core resources.

The spatial scheduling approach has two fundamental research issues. First, applications ideally should have malleability which is the ability to dynamically adjust the degree of parallelism (DoP) to adapt to the changes to the allocated core resources. Without malleability, applications can suffer from a significant slowdown when allocated core resources change due to the thread migration overhead and unbalanced numbers of threads among allocated core resources. Although the parallel computing research community has presented several runtime techniques to achieve malleable parallel execution, these existing techniques require special compiler/runtime [71, 72] that limits their applicability or use a simplistic task/work scheduling which can incur a significant scheduling overhead for a large number of core resources [40]. Second, the spatial scheduling approach needs to decide the proper number (and location) of core resources between co-located applications depending on the given scheduler's policy. Many existing core allocation techniques are predominantly CPU- or speedup-centric, meaning that they assign more core resources to CPU-intensive applications or highly-scalable applications [76, 75, 21, 81, 91], by leveraging runtime heuristics or application speedup information. Although optimizing CPU usage has long been a common strategy for many resource management problems, the approach ignores the fact that multiple resources such as CPU and memory bandwidth are consumed simultaneously. Optimizing only CPU usage can lead to under-utilized memory systems resulting in an inefficient tail execution once all the computation-intensive applications have been finished.

In this thesis, we focus on improving the runtime performance (the execution time) of co-located parallel applications on multi-socket multicore systems thereby reducing the operating cost of HPC and data centers. To achieve this goal, the first idea of this work is to ensure spatial scheduling for executing colocated parallel applications. The first research goal is to provide efficient malleable parallel execution in spatial core allocation for shared-memory parallel applications with minimal changes to the current runtime system. In particular, we focus on providing malleable execution for OpenMP workloads which are widely used in many HPC and data center workloads. Based on the malleable parallel runtime support, the next research goals focus on performance modeling of parallel programs and parallelism management for co-located parallel applications. While performance modeling has long been an important research issue, existing modeling techniques for core resource management rely on additional efforts before applications are executed such as offline training [65] or machine learning [36, 29]. Ideally, the performance modeling and parallelism management should be done online and within a reasonable overhead. Therefore, we focus on an analytical solution that can efficiently estimate the performance of parallel programs and can also be applied to runtime systems while providing useful insights for the resource manager to develop an appropriate scheduling policy. Finally, based on the malleable runtime and the analytical performance model, we aim to provide a parallelism management framework that determines

the core allocation for co-located parallel applications and improve the overall system throughput.

#### 1.2 Background

To better understand the research issues of this thesis, this section provides background information about the OpenMP runtime system. We also provide the information about our target multi-socket multicore systems that are used for evaluation throughout this thesis.

#### 1.2.1 The OpenMP Runtime System

In this thesis, we mainly consider OpenMP parallel applications. OpenMP is the de-facto standard for shared-memory parallel processing in HPC and is also widely used for many data center and big-data workloads.

OpenMP's parallelism is based on the fork-join execution model [9]. Applications consist of multiple parallel fork-join sections that may consist of one or more parallel loops. Parallel loops annotated with the parallel for pragma are the basic mechanism to initiate parallelism in OpenMP applications, and different parallel loops exhibit different resource requirements and performance characteristics. To consider applications' changing performance characteristics, in this thesis, we focus on optimizing the execution of co-located parallel applications in the level of parallel loop.

In an OpenMP parallel loop, the outermost loop iterations represent the smallest parallel unit of work. OpenMP supports three loop scheduling methods: static, dynamic, and guided. Programmers can select a scheduling discipline by annotating the specific method to the parallel for pragma. Static scheduling, selected by schedule(static), divides and assigns the loop itera-

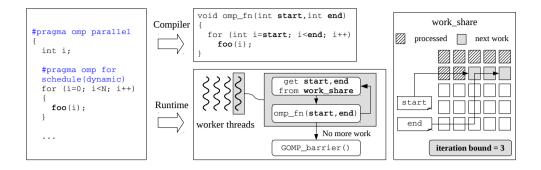

Figure 1.2 Execution model for parallel for loop.

tions of a parallel loop equally to the worker threads. This policy benefits from a small dispatch overhead but may suffer from load imbalance. With dynamic scheduling, selected by schedule(dynamic), loop iterations are assigned to the worker threads at runtime; this process is illustrated by Figure 1.2 for the GNU OpenMP (GOMP) runtime system [34]. Each thread repeatedly fetches and executes a fixed number of loop iterations from the global shared  $work\_share$  data structure until there is no more work. Guided scheduling, annotated by schedule(guided), operates similar to dynamic scheduling but dynamically adjusts the number of loop iterations assigned to a thread. Li's guided scheduling [54], for example, assigns  $\lceil items/2N \rceil$  loop iterations where items represents the number of remaining loop iterations and N stands for the number of worker threads.

An important observation of the OpenMP loop scheduling is that, in principle, the work of a parallel loop can be divided into multiple chunks of work which can be scheduled dynamically. While the default OpenMP loop schedulers use a fixed number of worker threads and do not support malleable execution, we exploit the inherent malleability in OpenMP parallel loops and provide malleable execution through a runtime-level support presented in Chapter 2.

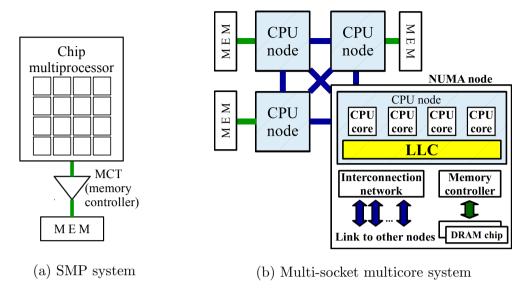

Figure 1.3 SMP and multi-socket multicore systems.

#### 1.2.2 Target Multi-Socket Multicore Systems

The runtime techniques discussed in this thesis assume multi-socket multicore systems that contain multiple CPU sockets and memory nodes. Such multi-socket multicore systems are becoming more common in HPC and even data centers to provide more computational power and memory bandwidth. Figure 1.3 provides a simplified view of symmetric multiprocessing (SMP) and multi-socket multicore systems. Unlike an SMP system that comprises multiple cores and one memory, multi-socket systems contain a number of memory controllers to increase the memory bandwidth in the presence of a large number of cores. In such systems, one node consists of a CPU node, itself composed of a group of CPU cores, and its attached memory node. The individual nodes are connected by an interconnection network such as AMD's HyperTransport [74] or Intel's QPI (Quick Path Interconnect) [68]. These architectures exhibit Non-Uniform Memory Accesses (NUMA) characteristics because of the varying ac-

Figure 1.4 Block diagram of the target multi-socket multicore platforms.

cess latencies of the cores to the different memory controllers.

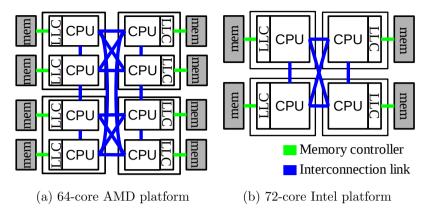

Our work has been evaluated on two commodity multi-socket platforms, a 64-core AMD Opteron and a 72-core Intel Xeon system. The AMD platform, shown in Figure 1.4 (a), comprises a total of eight CPU nodes in four physical processor packages (AMD Opteron 6380 [1]) and 128 GB of memory. The AMD Opteron processors run at 2.5GHz. Each CPU node contains eight computing cores that share a last-level cache (LLC) of 12 MB. The processor nodes are connected by AMD's Hyper Transport [74] with a maximum hop distance of two. The Intel system, shown in Figure 1.4 (b), has four Intel Xeon E7-8870 v3 [42] processors (2.1GHz) each consisting of 18 cores sharing a 45 MB LLC. The system is equipped with 512 GB of memory (some experiments used 756 GB of memory (e.g. Section 4.4) before we changed the DRAM chips). Each processor represents a CPU node, the four nodes are connected with Intel's QPI [68].

#### 1.3 Contributions

In this thesis, we propose novel runtime-level techniques for the aforementioned goals for executing co-located parallel applications.

#### 1.3.1 Cooperative Runtime Systems

The first research contribution of this thesis is a runtime-level technique that provides malleable parallel execution for OpenMP applications under dynamic spatial scheduling. We call a runtime system using this technique a cooperative runtime system. The cooperative runtime technique has been implemented into the GNU OpenMP runtime [34] and allows OpenMP programs to dynamically adjust the DoP with a low overhead. OpenMP applications typically have multiple parallel code sections (e.g. parallel for loops) that may exhibit different performance characteristics. Therefore, applications should be able to adjust the DoP for each parallel loop to fully exploit the benefits of spatial core allocation. The cooperative runtime system provides this ability without any modifications to the application code or the compiler. To dynamically change the DoP of a parallel loop, i.e. number of active threads, the technique splits the workload into multiple chunks of work and dynamically schedules the chunks on the provided core resources. In Chapter 2, we show the benefits of malleable execution using the cooperative runtime system when executing OpenMP applications in dynamic spatial core allocation compared to the traditional OpenMP runtime that does not adjust the DoP at runtime. Some parts of this runtime technique have been discussed in our previous paper at The International Conference on Parallel Architectures and Compilation Techniques (PACT) 2018 [15] and also presented at The Workshop of Programmability and Architectures for Heterogeneous Multicores (Multiprog) 2017 [18].

#### 1.3.2 Performance Modeling

The second contribution of this thesis is an analytical performance model for estimating resource utilization and the performance of parallel loops on sharedmemory multi-socket multi-core systems in dependence of the provided core resources. The approach employs queueing theory to model memory accesses in multicore systems; the queueing model allows us to compute useful performance information such as memory response time and bandwidth utilization by using closed-form equations. Based on the key insight that scalability of OpenMP parallel loops is typically limited by memory performance, a hierarchically constructed M/M/1/N/N queue system is used to analytically compute the response time at the different congestion points in the memory system of modern NUMA architectures. After automatically tuning the model to a specific architecture by executing a number of micro-benchmarks, the required parameter values are obtained at runtime from hardware performance counters present in modern commodity AMD and Intel processors. In Chapter 3, evaluated with 24 OpenMP parallel loops, we validate the accuracy of the presented queueing system by comparing the measured and modeled speedup curves. This work has led to several publications in parallel computing venues such as PACT 2016 [17] and TPDS 2020 [19]. In PACT 2016 [17], we presented an earlier version of the analytical model. A more sophisticated version has been presented in TPDS 2020 [19].

#### 1.3.3 Parallelism Management

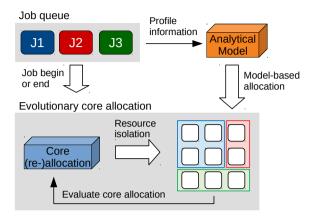

Employing the cooperative runtime system and the analytical model, we finally present a parallelism management and core allocation framework called NuPoCo (NUMA performance optimizations for co-located parallel applications). From the cooperative runtime support, for an OpenMP application, the framework keeps track of changing parallel loops and manages parallelism for each of the co-located parallel loops.

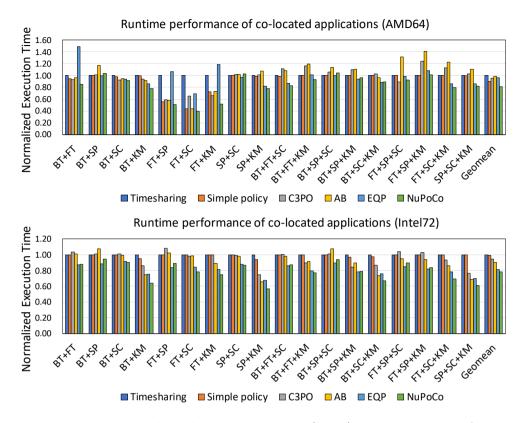

NuPoCo maximizes the overall system utilization by considering the uti-

lization of both CPU cores and memory bandwidth to determine the proper number of cores for each of the co-located parallel loops. NuPoCo leverages the analytical model to compute CPU and memory bandwidth utilization and then determines the degree of parallelism based on a greedy allocation algorithm to maximize the sum of CPU utilization and memory bandwidth utilization. Our evaluation shows that NuPoCo improves the average system throughput (i.e. reduction of execution time) on commodity AMD and Intel multi-socket systems in the order of 10 to 20% over conventional execution models using standard Linux time-sharing. This parallelism management framework has been presented in PACT18 [15].

#### 1.4 Related Work

#### 1.4.1 Cooperative Runtime Systems

To enable spatial scheduling on a Linux-based system, the most simple approach is using system calls such as sched\_setaffinity or Linux's cgroup for CPU affinity masking. For example, in SBMP [76] and C3PO [75], an application's worker threads are pinned to the assigned cores without changing the degree of parallelism of the application. Hence, applications still use a fixed number of kernel-level threads and the approach cannot avoid thread interference on the same cores and suffers from a load imbalance due to thread migration and unbalanced numbers of threads among cores.

To dynamically adjust the DoP (i.e. the number of kernel-level threads) of parallel programs, runtime systems often use supports from the application runtime. The OpenMP runtime system [34] already provide a similar feature. For example, OpenMP's *OMP\_parallel* code regions can run with any number of threads (if not defined by the application programmer) that can be selected

when entering the parallel region. Several runtime systems [21, 36, 28] assign a varying number of threads for such parallel regions. Once created, however, the number of worker threads within a parallel section remains constant and the benefit is limited compared to fully malleable execution.

To provide malleability, several compilers [53, 71, 72] generate flexible code. The basic idea is to divide the total work into composable chunks of work and schedule them onto provided core resources. Varuna's [81] virtual tasks (VTask) decouple software from hardware threads and require no compiler support. The VTask technique splits the parallel work by intercepting creation of Pthreads and manages them using a work pool. However, these approaches require special compiler and runtime system which limits the applicability and makes it difficult to exploit advanced runtime optimizations provided by the existing runtime system such as OpenMP.

Callisto [40] uses a scheduler activation technique in the OpenMP runtime to provide malleable execution for OpenMP parallel programs. Callisto is similar to our work as our approach also achieves workload malleability by leveraging dynamic loop scheduling logic in the OpenMP runtime system. However, our approach has merits that we perform dynamic granularity control and can preserve data locality optimizations on NUMA multi-core systems through hierarchical scheduling. Chapter 2 discusses the merit of our work scheduling.

#### 1.4.2 Performance Modeling

Several performance modeling techniques have been presented for multi-socket systems. Pandia [35] predicts the performance of parallel applications for different thread counts and placements. The performance prediction is based on six different profiling runs to obtain the performance features. NuCore [88] is an analytical model to predict the optimal core allocation for multi-threaded applica-

tions. NuCore finds the core allocation that maximizes the memory bandwidth usage at minimum core count. Integer programming is used to solve the model. A detailed DRAM performance model, DraMon [89], is employed to predict the memory performance in NuCore. DraMon requires a number of parameters that need to be obtained from expert knowledge or architecture data sheets. On the other hand, the presented method in this thesis requires a small number of input parameters that can be obtained from hardware performance counters at runtime. In addition, the queueing systems analytically compute the performance of each memory controller and interconnection link separately using closed-form expressions; such information can be used for various optimizations.

Applying queueing models to model multiprocessor architectures has been discussed in the literature. Jonkers [47, 46] has presented conceptual queueing models for multiprocessor architectures consisting of multiple memory controllers and an interconnection network. However, these works do not provide an evaluation on real hardware platforms. Tudor et al. [85, 84] applied an M/M/1 queueing system to evaluate memory contention in an SMP system with Uniform Memory Access (UMA) times. In contrast to our work, they do not apply a queueing system for the interconnection links in NUMA machines; instead, they used regression to evaluate the performance on a different number of CPU nodes. Moreover, the M/M/1 model assumes an infinite number of queueing customers, however, multiprocessor systems contain a finite number of cores.

In our preliminary work [17], we have presented a speedup prediction model using M/M/1/N/N queueing systems. In current model, we extended the previous work in a number of ways. First, the model now provides an experimental study showing that parallel loops act like queueing customers. Second, the previous work uses simpler queueing systems assuming a fully-connected interconnection network and does not take into account memory performance variations

with hardware optimizations. The presented technique in this thesis provides more accurate prediction results than the maximum bound of accuracy when using fixed memory service rates, as shown by our evaluation in Chapter 3.

#### 1.4.3 Parallelism Management

To determine the proper thread or core count between co-located parallel applications, SBMP [76], SCAF [21], and Varuna [81] execute a parallel program in several configurations at runtime and perform a regression analysis to estimate the performance scalability. Then, they determine the thread count according to a policy. For example, SCAF [21] selects the thread count that maximizes the speedup of all running applications. Parcae [72], C3PO [75], and Aurora [60] perform hill-climbing to reach an optimal thread count. For example, Parcae [72] initially reserves an equal number of cores to all running parallel applications. ACTOR [22] adjusts thread count for power and performance optimizations based on a prediction model that requires hardware performance counters. Emani et al. [29, 28] and ADAPT [52] apply machine learning models to compute the number of threads assigned to applications. These approaches, however, do not provide information about the memory performance on modern multi-socket systems. We focus on maximizing overall system utilization of all CPU cores and memory bandwidth with an analytical solution.

Thread placement is known to strongly affect performance on multi-socket systems [92, 24]. While previous parallelism managers do not consider thread placement or uses simplistic linear partitioning [76, 75], we consider the architecture's NUMA properties to determine a good placement of threads to cores. A number of thread and data placement techniques have been presented for multi-threaded applications on multi-socket systems [92, 62, 24, 82]. LIRA [20] performs heuristics to determine thread placement of co-located applications

on NUMA CPU nodes. Threads are placed in order to minimize resource contention while preserving an efficient data placement. Unlike these approaches, we focus on assigning the proper number of threads between co-located parallel applications at runtime.

Recently, the co-scheduling approach, i.e. co-locating multiple parallel jobs on the same multicore node, is gaining importance in the HPC domain. Breitbart et al. [12, 10] perform co-scheduling of multiple applications on multi-core nodes. To maximize system throughput their scheduler detects an application's main memory bandwidth utilization at runtime and co-locate applications that may benefit from co-scheduling on the same nodes using migrations. However, they do not adjust the number of threads for parallel applications; parallelism management has a large potential to improve single node performance as shown by our previous researches [15].

In data centers, workloads usually use a workload abstraction such as Hadoop and Spark and are managed by several tools such as virtualization and Linux's control groups. Similar to HPC schedulers, data center schedulers also require applications' resource requirements and user runtime estimates. Mesos [41] is a data center operating system that considers workload's varying resource requirements. There are several scheduling techniques to consider heterogeneous clusters [86] and to reduce the burden of user runtime estimates [70].

#### 1.5 Organization of this Thesis

The remainder of this thesis is organized as follows. Chapter 2 introduces the cooperative runtime system that achieves efficient dynamic spatial scheduling for simultaneously running parallel programs. Chapter 3 presents the analytical performance model for estimating resource utilization and the scalability of

parallel programs. Then, our parallelism and core management techniques that leverages the runtime support from Chapter 2 and Chapter 3 are presented. Chapter 4 presents NuPoCo, the parallelism management framework to manage parallelism of parallel loops for co-located parallel applications. We finally conclude this thesis in Chapter 5.

### Chapter 2

### Dynamic Spatial Scheduling with Cooperative Runtime Systems

#### 2.1 Overview

As more and more core resources are integrated into a single shared-memory multicore system, spatial scheduling that provides distinct core resources to running parallel applications (i.e. space-sharing) is regarded as a promising approach for efficiently executing multiple co-located parallel applications [87, 76, 29, 21, 28]. A key challenge of spatial scheduling is providing an efficient runtime environment for parallel applications to execute efficiently in spatial core allocation that can dynamically vary at runtime (i.e. dynamic spatial scheduling). For example, spatial schedulers may assign a new core allocation once a new parallel job begins or ends. Moreover, applications have multiple phases (e.g. different parallel loops) that may have different performance characteristics. Spatial schedulers thus need to determine a new allocation to consider applications' different phases. In this context, parallel programs ideally should

have malleability meaning that programs need to be able to dynamically adjust the degree of parallelism (DoP) in accordance with the provided core resources.

Conventional parallelization runtimes such as OpenMP [9], Intel TBB [73], Cilk [8], and OpenCL [49], however, do not support such a malleable execution. These runtime systems generate a fixed number of worker threads using kernel-level threading such as Pthreads, typically as many cores as there are in the given multicore system, to utilize all physical core resources. Consequently, parallel applications may suffer from a significant slowdown when allocated core resources dynamically change due to the thread migration overhead and unbalanced numbers of worker threads among allocated core resources. In this context, the parallel computing research community has presented several runtime techniques to achieve malleable parallel execution. The basic idea is to divide the total work into a certain number of chunks of work and dynamically schedule them onto the available core resources at runtime. Existing runtime techniques, however, require their special compiler/runtime framework [71, 72] that limits their applicability or remain rooms for performance improvement in terms of their simplistic task/work scheduling [40] which can suffer from a scheduling overhead for a large number of cores.

In this chapter, we present a cooperative runtime technique to provide malleable parallel execution for OpenMP applications. We implemented this runtime support in the GNU OpenMP runtime system (provided by gcc-9) [34]. With the cooperative OpenMP runtime system, OpenMP parallel programs can dynamically adjust the DoP, i.e., the number of active worker threads, for varying core allocation. The cooperative OpenMP runtime system consists of two key runtime techniques called cooperative user-level tasking and cooperative dynamic loop scheduling that provide malleability at the level of parallel loop. To be able to dynamically adjust the DoP of a parallel loop, the coopera-

tive runtime system splits the parallel loop's iteration space into multiple tasks (with user-level tasks) and dynamically schedule them onto the available core resources. To reduce the overhead from dynamic scheduling, the work scheduler uses hierarchical scheduling where the tasks are partitioned into multiple regions and scheduled by distributed schedulers. We have evaluated the cooperative runtime system for eight NPB applications [4] on a 64-core AMD Opteron and a 72-core Intel Xeon system. The evaluation shows that the cooperative OpenMP runtime system can execute OpenMP applications more efficiently in spatial core allocation, with 20–30% shorter execution time on average, compared to the conventional spatial scheduling that does not adjust the DoP of the application.

As a summary, the following research contributions are discussed in this chapter.

- A runtime-level support, called a cooperative runtime system, to enable malleable parallel execution for OpenMP applications without any modifications to the application code or the compiler.

- An efficient user-level tasking and dynamic scheduling technique to achieve both malleability and high performance for OpenMP parallel loops.

- An evaluation of the cooperative runtime system that shows the benefits

of malleable parallel execution in spatial scheduling.

#### 2.2 Malleable Workloads

In this section, we show the benefit of achieving malleability in spatial scheduling. Conventional spatial schedulers in the HPC domain have assumed rigid jobs that run only with a specific number of processors and inform the scheduler that how much time the job will run (called user runtime estimates) [32].

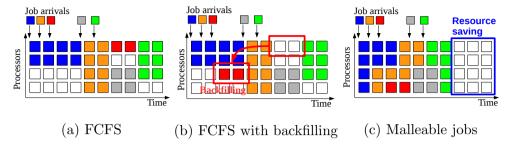

Figure 2.1 Spatial scheduling depending on the job flexibility.

However, such an approach suffers from resource fragmentation. For example, in First-Come First-Served (FCFS) scheduling shown in Figure 2.1 (a), processors that cannot meet the requirements of the next job need to remain idle until additional processors have become available. Backfilling is a technique that allows jobs to execute earlier as long as the jobs do not delay the start of other jobs, as shown in Figure 2.1 (b). Backfilling schedulers can reduce resource fragmentation of FCFS scheduling and have been adopted in real HPC centers in the past two decades [56, 66]. In practice, however, backfilling scheduling still suffers from resource fragmentation depending on the job resource requirements. In addition, user runtime estimates are typically much longer than the actual job runtime and result in resource underutilization. In this context, scheduling malleable jobs is gaining importance [40, 6] to achieve maximal performance. Malleable jobs are able to execute with any number of threads and can change during the job runtime. Thanks to the flexibility, as shown in Figure 2.1 (c), malleable jobs can theoretically provide higher resource utilization and shorter job response times [6].

As we discussed in Section 1.2.1, the default OpenMP runtime system does not support malleable execution because the runtime system generates a fixed number of worker threads. To execute such parallel applications in spatial core allocation that changes dynamically, on Linux-based systems, the most simple approach [76, 75, 91] is using system calls such as sched\_setaffinity or Linux's cgroup to allow the application's threads to execute on the provided core resources. On such runtime systems, applications can suffer from a significant slowdown when allocated core resources change due to the thread migration overhead and unbalanced numbers of threads among allocated core resources. To execute parallel applications efficiently in spatial scheduling, therefore, applications ideally should have malleability to dynamically adjust the DoP to adapt to the changes to the allocated core resources. Such malleable execution then allows only one active thread to execute on each core resource.

# 2.3 Cooperative OpenMP Runtime System

As discussed in Section 1.2.1, an OpenMP application consist of one or more parallel each exhibiting different performance characteristics. The presented cooperative runtime technique provides the ability for each parallel loop to adjust the DoP at runtime. The technique exploits inherent malleability in the OpenMP programming model, and allows for a malleable execution without requiring any modifications to the application code.

The cooperative OpenMP runtime system enables malleable parallel execution for OpenMP parallel loops based on two key scheduling techniques called cooperative user-level tasking (COOP-ULT) and cooperative dynamic loop scheduling (COOP-DYN). In OpenMP, parallel loops annotated with the parallel for pragma are the basic mechanism to initiate parallelism in OpenMP applications. For an OpenMP parallel loop, the outermost loop iterations represent the smallest parallel unit of work which are scheduled by the OpenMP runtime system. COOP-ULT and COOP-DYN are orthogonal techniques which provide malleability for different types of OpenMP parallel loops. While COOP-

ULT enables malleable execution for OpenMP parallel regions (OMP\_parallel) that may incorporate multiple parallel loops with static scheduling, COOP-DYN enables malleable execution for parallel loops annotated with dynamic loop scheduling (e.g. schedule(dynamic)). These two techniques consider common parallel programming patterns in OpenMP and can provide malleability for existing OpenMP applications in well-known benchmarks such as NPB3.4 [4], Parsec [7], and Rodinia [14]. We present the details of these techniques in the following sections.

#### 2.3.1 Cooperative User-Level Tasking

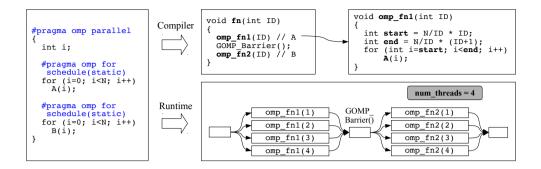

To understand the COOP-ULT technique, we first discuss the type of OpenMP parallel code that can be executed under the COOP-ULT technique. Figure 2.2 shows an example OpenMP fork-join parallel code that can be executed with COOP-ULT and illustrates how the default (GNU) OpenMP runtime system executes the code. In the figure, the loops annotated with "# pragma omp for" are executed in parallel, and there is an implicit barrier between the two parallel loops executing functions A and B. Then, the compiler generates code fn on the right side. The code contains two functions omp\_fn1 and omp\_fn2 that execute parallel for loops for A and B. The code also contains a barrier function, shown by GOMP\_Barrier, between these two functions omp\_fn1 and omp\_fn2. For a barrier, all worker threads need to stop until all other threads reach the barrier point.

The OpenMP runtime system then executes the code fn using multiple threads. For example, in the figure, four threads are executed in parallel. The amount of work (i.e. the number of loop iterations) between the worker threads is equally partitioned given the static partitioning method.

The OpenMP programming model provides several ways to select the num-

Figure 2.2 Execution model for OpenMP parallel sections.

ber of worker threads. First, the programmer can annotate the number of worker threads using the num\_threads clause. If not defined by the num\_threads clause, thread count can basically be any number. The OpenMP runtime [34], by default, generates threads as many as system's core resources to utilize all physical cores. Users can also use environment variable OMP\_NUM\_THREADS to use a specific number of worker threads.

#### **Achieving Malleability**

An important observation of the OpenMP runtime model is that the thread count can be any number if not specified by the programmer. Therefore, if we create more worker threads, each thread will execute a smaller amount of work. We use this property to achieve malleable execution.

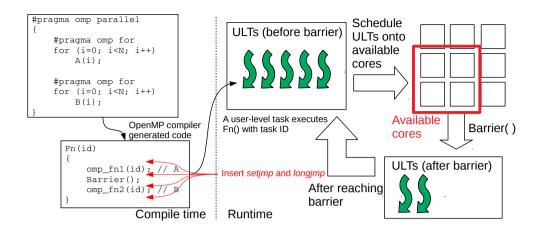

Figure 2.3 illustrates the basic idea of the cooperative runtime technique. To be able to change the number of threads dynamically, the key idea of cooperative user-level tasking is to (1) generate many number (larger than the number of physical cores) of threads (2) then dynamically execute them on the allocated core resources. Thanks to this dynamic scheduling, cooperative user-level tasking can allow only one worker thread to execute on a active core

Figure 2.3 Execution model for cooperative user-level tasking.

resource and thus can reduce interference caused by unbalanced numbers of threads on allocated cores. However, by default, the OpenMP runtime system uses kernel-level threads (Pthreads) for each thread object. Managing a large number of kernel-level threads requires a huge management cost and incurs a high runtime overhead due to frequent sleep and wakeup operations. Also, the default OpenMP runtime system prevents from creating a large number of kernel-level threads (e.g. more than a thousand) due to its high management cost.

To reduce this runtime overhead, we use user-level tasks (ULTs) instead of kernel-level threading. Cooperative user-level tasking first creates a many number of user-level tasks that execute the parallel code. (We currently create  $\#cores \times 20$  ULTs; we will discuss why in the following section.) Each physical core executes only one kernel-level thread that dynamically fetches ULTs at runtime. Since switching ULTs does not require an access to the Linux kernel, this approach can minimize the threading overhead while achieving malleability. There are a number of OpenMP runtime systems such as Callisto [40] and

Bolt/Argobots [79, 45] that exploit user-level threading. Compared to other user-level theading techniques used in these previous works that typically use a timer interrupt to get into the scheduler routine, we use simpler ULT scheduling (called zero-interrupt ULT scheduling) as we do not need to switch tasks before completing a task or reaching a barrier. We implemented this by inserting setjmp and longjmp API that saves and restores the minimal execution status of the executing code. Our technique requires small modifications to the OpenMP runtime system. In addition, in contrast Callisto and Bolt/Argobots, our ULT scheduling considers the NUMA property in multi-socket systems and also aims to reduce the dynamic scheduling overhead. In the below, we present a NUMA-aware and efficient ULT scheduling method called hierarchical scheduling.

#### **Hierarchical Scheduling**

Furthermore, to preserve data locality optimizations of applications in NUMA systems and to minimize ULT scheduling overhead, we apply hierarchical scheduling (HS) where we partition the ULTs into multiple regions and performs distributed scheduling. The dynamic scheduling overhead becomes more and more critical with an increasing number of core resources. To reduce the overhead from scheduling contention, the hierarchical scheduling partitions the ULTs into multiple regions based on the CPU nodes. Each CPU node has its ULT region and schedules ULTs from the local region. Load balancing is also achieved through work stealing from the local queues of other CPU nodes. Then, a local work queue distributes ULTs to the threads in that node. The regions are equally partitioned according to OpenMP's static scheduling policy. Such a partitioning can be effective when neighboring work items exhibit high locality and preserve manual optimizations for static scheduling with a technique such as [63].

#### **Balancing Malleability and Performance**

The COOP-ULT technique executes parallel loops with a given number of ULTs. If we create more ULTs, the workload has more flexibility to adapt to the changing core allocation (because each ULT executes a smaller amount of work) but may suffer from a runtime overhead to schedule a large number of tasks. It is therefore important to create a proper number of ULTs to achieve both malleability and high performance.

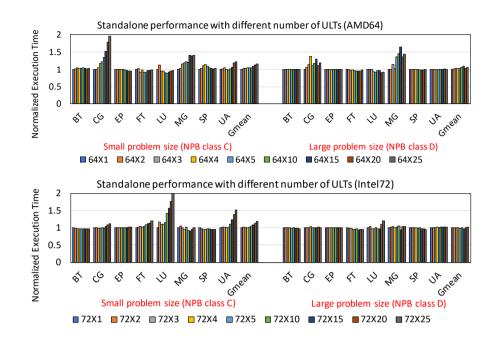

Figure 2.4 shows the runtime performance (execution time) of NPB3.4 OpenMP Fortran applications [4] that are executed under the COOP-ULT technique with different numbers of ULTs. For the experiments, we used two multisocket multicore platforms, the 64-core AMD (Opteron 6380 [1]) and the 72-core Intel (Xeon E7 8870 v3 [42]) system described in Section 1.2.2. In the figure, the first option creates as many ULTs as there are physical cores in the system; this leads to no malleability, but no scheduling overhead. The other options show the performance when increasing the number of ULTs. The results show that several applications such as CG and MG in AMD and LU in Intel suffer from a low performance when we create many ULTs due to the scheduling overhead. The overhead from scheduling ULTs becomes more prominent if the execution time of a ULT is small compared to the scheduling overhead. For example, in the case of LU in Intel, parallel loops execute significantly faster in Intel compared to our AMD platform, and the scheduling overhead became prominent. On the other hand, applications typically have significantly less performance degradation if we have a larger problem size (class D) because the scheduling overhead is less prominent compared to the execution time of each ULT.

Based on this experiment, to balance the mall eability and performance, the COOP-ULT technique currently creates  $\#cores \times 20$  ULTs. Although it

Figure 2.4 Application performance with different number of user-level tasks.

may still suffer from scheduling overhead for applications with a small problem size, applications are able to change their DoP with enough flexibility, and the scheduling overhead is generally negligible for applications with a sufficient problem size. Selecting the optimal number of ULTs (depending on the application) can improve the performance and flexibility, and is left as future work.

# 2.3.2 Cooperative Dynamic Loop Scheduling

As discussed in Section 1.2.1, OpenMP supports three loop scheduling methods: static, dynamic, and guided. These scheduling policies, by default, are not able to change the degree of parallelism at runtime. Static and guided scheduling are not malleable at all because they assign a comparatively large amount of work in the first assignment. Parallel loops with dynamic scheduling, on the other hand, may be adequate to achieve malleable execution by modifying the

## Algorithm 1 Cooperative worker threads

```

1: while there is more work do

2:

if own core is not available then

3:

go to sleep

for each thread \in worker\_threads do

4:

5:

if thread's core is available then

wake up thread

6:

work\_chunk \leftarrow qet\_work\_chunk(chunk\_size)

7:

if work_chunk received then

8:

9:

work\_chunk \rightarrow execute()

if id == 0 and elapsed\_time < epoch then

10:

chunk\_size \leftarrow (chunk\_size \times 2)

11:

```

loop scheduler. For example, the loop scheduler can dynamically assign the chunk of work onto the provided core resources. However, the dynamic scheduler can suffer from a significant dispatch overhead depending on the allocation granularity. In this section, we present the COOP-DYN technique that achieves malleable execution for OpenMP parallel loops with dynamic scheduling while optimizing the scheduling performance.

#### Achieving Malleability

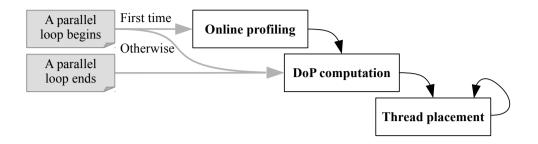

We have implemented dynamic spatial scheduling into the GNU OpenMP runtime [34] by modifying the dynamic loop scheduling method in the OpenMP loop scheduler. To provide malleability while minimizing overhead and maximizing load balance, we use an adaptive dynamic scheduling technique as explained in Algorithm 1. A parallelism manager can keep track of the execution of OpenMP applications by intercepting calls that initiate or terminate parallel loops. The results of the core allocation are then communicated to the OpenMP parallel runtimes through shared memory. The runtimes dynamically change the DoP of cooperative parallel loops by adjusting the number of worker threads and pinning them to the assigned cores.

In the cooperative loop scheduling, before requesting new work, each thread checks the availability of its core. If the core is no longer available, the thread goes to sleep (lines 2–3). Active worker threads review the current core allocation and wake up threads whose core has become available (lines 5–6). Each thread acquires a chunk of work by calling the  $get\_work\_chunk$  function on line 7. To decrease the dispatch overhead, the master thread (id 0) dynamically adjusts the work chunk size based on the elapsed execution time of a work chunk (lines 12–13). The details of the work chunk size control are explained in the following section "Balancing Malleability and Performance".

#### **Hierarchical Scheduling**

Similar to the cooperative user-level tasking, here cooperative loop scheduling also support hierarchical scheduling for NUMA systems. The idea is basically the same with the cooperative user-level tasking. Instead of scheduling ULTs, here we partition the loop items into multiple regions for each CPU node and a local scheduler schedules items for cores in the same CPU node. Load balancing is also achieved through work stealing among CPU nodes.

#### Balancing Malleability and Performance

To provide malleability while minimizing overhead and maximizing load balance, we use an adaptive dynamic scheduler as illustrated in Algorithm 1. If the processing time of a work chunk is smaller than the global scheduling period of the space-sharing scheduler, we increase the chunk size. To provide sufficient opportunities for load balancing, the maximum chunk size is set to  $\lceil W/2N \rceil$  where W represents the remaining iterations, N the number of available cores in the system. This is similar to the guided loop scheduling algorithm for multi-core systems [54].

The OpenMP runtime implements a work sharing approach in which each worker thread shares the data structure containing information about the processed and still unprocessed loop iterations. We designate one worker thread as the delegate thread that is allowed to change the work chunk size.

# 2.4 Experimental Results

In this section, we evaluate the cooperative runtime system on the 64-core AMD Opteron and the 72-core Intel Xeon system (Section 1.2.2).

## 2.4.1 Standalone Application Performance

The cooperative runtime system provides malleability by leveraging dynamic loop scheduling and user-level tasking. A concern is whether, despite its flexibility, the performance of the cooperative runtime system is on par with the existing schedulers. Here, we show that the cooperative runtime system can provide comparable performance to the default execution mode for standalone application execution while providing the ability to dynamically change the number of threads.

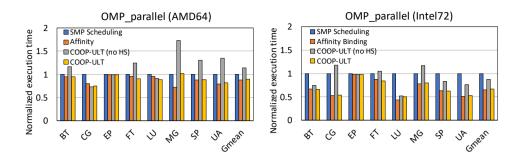

Figure 2.5 shows the turnaround times of standalone applications in NPB3.4 [4] OpenMP fortran applications executed with COOP-ULT compared to the default mode (SMP Scheduling and Affinity Binding). All these applications in this scenario use an input data size of class D [4]. In SMP Scheduling and Affinity Binding, applications generate worker threads with the number of system cores.

Figure 2.5 Standalone applications performance (OMP\_parallel).

In SMP Scheduling, the generated threads are managed by Linux's default SMP scheduling (threads can execute on any core resource). In the Affinity Binding mode, on the other hand, each thread is bound to each core by managing their CPU affinity (only one thread can execute on each core). For these applications, cooperative user-level tasking performance is comparable to the default mode. Comparing COOP-ULT and COOP-ULT (no HS), we observe that single global ULT scheduling without hierarchical scheduling (COOP-ULT (no HS)) incurs high scheduling overhead. The presented cooperative user-level tasking combines the best of both worlds by respecting data locality, yet being able to react to workload imbalance while also supporting malleable parallelism.

In Figure 2.6, we modify the NPB applications to use dynamic loop scheduling (by annotating "schedule(dynamic)" pragma) for all parallel loops in the application. The cooperative dynamic loop scheduling can also provide malleable execution for dynamic loops. In this scenario, we also observe that cooperative loop scheduling can even improve the single application performance a lot. For example, COOP-DYN (no HS) improves performance by managing the work chunk size dynamically. Since the original dynamic loop scheduler assigins

Figure 2.6 Standalone application performance (parallel for).

Figure 2.7 Performance under COOP-ULT and COOP-DYN.

works with a basic granularity of 1, it often incurs a high scheduling overhead for a large number of cores. In addition, the hierarchical scheduling and work stealing in COOP-DYN can further improve the performance.

Here, we compare the overall performance of static (cooperative user-level tasking) and dynamic versions (cooperative loop scheduling). Cooperative user-level tasking is beneficial than cooperative dynamic loop scheduling. The performance under loop scheduling generally depends on the application. While in our experiments we observe that static implementation provides overall higher

Figure 2.8 Space-sharing performance comparison with different tools.

performance compared to when using dynamic loop scheduling. Some applications such as EP and FT has benefit of dynamic loop scheduling. Because we mainly consider high-performance kernels and the workloads exhibit rather regular patterns. However, with cooperative runtimes we can also improve the performance of dynamic loops while providing flexibly to change the number of threads.

#### 2.4.2 Performance in Spatial Core Allocation

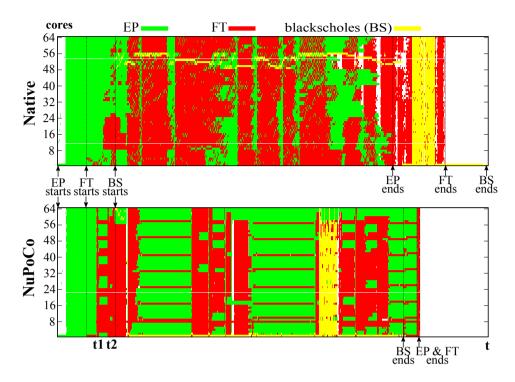

We claim that, in spatial core allocation, COOP-ULT provides better performance than existing performance isolation tools that are not able to manage the number of threads dynamically. In Figure 2.8, we evaluate the performance (the total execution time) of two co-located parallel applications with spatial core

Figure 2.9 Performance under varying resource availability.

allocation using different resource isolation techniques. We evaluate the runtime performance under different resource isolation options, COOP-ULT, Docker and Affinity Setting. COOP-ULT represents our cooperative user-level tasking technique, and Docker uses its resource isolation based on Linux cgroup. To minimize other performance effect from using specific resource manager Docker, we have also implemented our specific tool based on a kernel module to manage CPU affinity for application's threads (Affinity Setting). For an application, the kernel module assigns CPU affinity for the application's spawned threads. All the worker threads of the application can be assigned to any core resource among the allocated core resources. The Linux SMP scheduler manages the threads on the given allocated core resources. We first evaluate the two application mixes performance with spatial core allocation (each application uses the same number of core resources; cores are allocated in an interleaved way).