#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Ph.D. Dissertation

# Hardware Friendly Neural Network Architecture and Accelerator Design for Efficient Inference

효율적인 추론을 위한 하드웨어 친화적 신경망 구조 및 가속기 설계

August 2020

Department of Electrical and Computer Engineering

College of Engineering

Seoul National University

Joonsang Yu

## Hardware Friendly Neural Network Architecture and Accelerator Design for Efficient Inference

효율적인 추론을 위한 하드웨어 친화적 신경망 구조 및 가속기 설계

> 지도교수 이 혁 재 이 논문을 공학박사 학위논문으로 제출함 2020년 7월

> > 서울대학교 대학원 전기 정보 공학부 유 준 상

유준상의 공학박사 학위 논문을 인준함 2020년 7월

| 위  | 원 장: | 김태환 | (인)     |

|----|------|-----|---------|

| 부위 | 원장:  | 이혁재 | (인)     |

| 위  | 원:   | 유승주 | <br>(인) |

| 위  | 원:   | 류수정 | <br>(인) |

| 위  | 원:   | 이진호 | <br>(인) |

## **Abstract**

Joonsang Yu

Dept. of Electrical and Computer Engineering

The Graduate School

Seoul National University

Deep learning is the most promising machine learning algorithm, and it is already used in real life. Actually, the latest smartphone use a neural network for better photograph and voice recognition. However, as the performance of the neural network improved, the hardware cost dramatically increases. Until the past few years, many researches focus on only a single side such as hardware or software, so its actual cost is hardly improved. Therefore, hardware and software co-optimization is needed to achieve further improvement. For this reason, this dissertation proposes the efficient inference system considering the hardware accelerator to the network architecture design.

The first part of the dissertation is a deep neural network accelerator with stochastic computing. The main goal is the efficient stochastic computing hardware design for a convolutional neural network. It includes stochastic ReLU and optimized max function, which are key components in the convolutional neural network. To avoid the range limitation problem of stochastic numbers and increase the signal-to-noise ratio, we perform weight normalization and upscaling. In addition, to reduce the overhead of binary-to-stochastic conversion, we propose a scheme for sharing stochastic number generators among the neurons in the convolutional neural network.

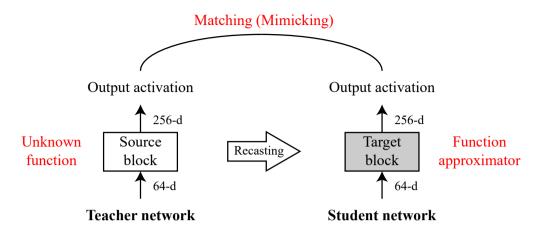

The second part of the dissertation is a neural architecture transformation. The network recasting is proposed, and it enables the network architecture transformation. The primary goal of this method is to accelerate the inference process through the

transformation, but there can be many other practical applications. The method is based

on block-wise recasting; it recasts each source block in a pre-trained teacher network

to a target block in a student network. For the recasting, a target block is trained such

that its output activation approximates that of the source block. Such a block-by-block

recasting in a sequential manner transforms the network architecture while preserving

accuracy. This method can be used to transform an arbitrary teacher network type to

an arbitrary student network type. It can even generate a mixed-architecture network

that consists of two or more types of block. The network recasting can generate a

network with fewer parameters and/or activations, which reduce the inference time

significantly. Naturally, it can be used for network compression by recasting a trained

network into a smaller network of the same type.

The third part of the dissertation is a fine-grained neural architecture search. In-

heritedNAS is the fine-grained architecture search method, and it uses the coarse-

grained architecture that is found from the cell-based architecture search. Basically,

fine-grained architecture has a very large search space, so it is hard to find directly. A

stage independent search is proposed, and this method divides the entire network to

several stages and trains each stage independently. To break the dependency between

each stage, a two-point matching distillation method is also proposed. And then, oper-

ation pruning is applied to remove the unimportant operation. The block-wise pruning

method is used to remove the operations rather than the node-wise pruning. In addi-

tion, a hardware-aware latency penalty is proposed, and it covers not only FLOPs but

also memory access.

keywords: Stochastic Computing, Deep Neural Network Accelerator,

Network Compression, Network Transformation, Neural Architecture Search

**student number**: 2015-20950

ii

# **Contents**

| A١ | ostrac  | t e e e e e e e e e e e e e e e e e e e   | Ĭ   |

|----|---------|-------------------------------------------|-----|

| C  | onten   | ts ·                                      | iii |

| Li | st of l | Figures                                   | vi  |

| Li | st of T | <b>Tables</b>                             | xi  |

| 1  | Intr    | oduction                                  | 1   |

|    | 1.1     | DNN Accelerator with Stochastic Computing | 2   |

|    | 1.2     | Neural Architecture Transformation        | 4   |

|    | 1.3     | Fine-Grained Neural Architecture Search   | 6   |

| 2  | Bac     | kground                                   | 8   |

|    | 2.1     | Stochastic Computing                      | 8   |

|    | 2.2     | Neural Network                            | 10  |

|    |         | 2.2.1 Network Compression                 | 10  |

|    |         | 2.2.2 Neural Network Accelerator          | 13  |

|    | 2.3     | Knowledge Distillation                    | 17  |

|    | 2.4     | Neural Architecture Search                | 19  |

| 3  | DNI     | N Accelerator with Stochastic Computing   | 23  |

|    | 3.1     | Motivation                                | 23  |

|   |     | 3.1.1   | Multiplication Error on Stochastic Computing  | 23 |

|---|-----|---------|-----------------------------------------------|----|

|   |     | 3.1.2   | DNN with Stochastic Computing                 | 24 |

|   | 3.2 | Unipo   | lar SC Hardware for CNN                       | 25 |

|   |     | 3.2.1   | Overall Hardware Design                       | 25 |

|   |     | 3.2.2   | Stochastic ReLU function                      | 27 |

|   |     | 3.2.3   | Stochastic Max function                       | 30 |

|   |     | 3.2.4   | Efficient Average Function                    | 36 |

|   | 3.3 | Weigh   | t Modulation for SC Hardware                  | 38 |

|   |     | 3.3.1   | Weight Normalization for SC                   | 38 |

|   |     | 3.3.2   | Weight Upscaling for Output Layer             | 43 |

|   | 3.4 | Early l | Decision Termination                          | 44 |

|   | 3.5 | Stocha  | astic Number Generator Sharing                | 49 |

|   | 3.6 | Experi  | iments                                        | 53 |

|   |     | 3.6.1   | Accuracy of CNN using Unipolar SC             | 53 |

|   |     | 3.6.2   | Synthesis Result                              | 57 |

|   | 3.7 | Summ    | ary                                           | 58 |

| 4 | Neu | ral Arc | hitecture Transformation                      | 59 |

|   | 4.1 | Motiva  | ation                                         | 59 |

|   | 4.2 | Netwo   | ork Recasting                                 | 61 |

|   |     | 4.2.1   | Recasting from DenseNet to ResNet and ConvNet | 63 |

|   |     | 4.2.2   | Recasting from ResNet to ConvNet              | 63 |

|   |     | 4.2.3   | Compression                                   | 63 |

|   |     | 4.2.4   | Block Training                                | 65 |

|   |     | 4.2.5   | Sequential Recasting and Fine-tuning          | 67 |

|   | 4.3 | Experi  | iments                                        | 69 |

|   |     | 4.3.1   | Visualization of Filter Reduction             | 70 |

|   |     | 4.3.2   | CIFAR                                         | 71 |

|   |     | 4.3.3   | ILSVRC2012                                    | 73 |

| Ał | strac | stract (In Korean) 113 |                                         |    |  |

|----|-------|------------------------|-----------------------------------------|----|--|

| 6  | Con   | clusion                |                                         | 93 |  |

|    | 5.5   | Summ                   | ary                                     | 92 |  |

|    |       | 5.4.2                  | Penalty Analysis                        | 90 |  |

|    |       | 5.4.1                  | Fine-Grained Architecture Search        | 88 |  |

|    | 5.4   | Experi                 | ments                                   | 87 |  |

|    | 5.3   | Hardw                  | vare-aware Penalty Design               | 85 |  |

|    |       | 5.2.3                  | Entire Search Procedure                 | 83 |  |

|    |       | 5.2.2                  | Operation Pruning                       | 82 |  |

|    |       | 5.2.1                  | Stage Independent Search                | 79 |  |

|    | 5.2   | Inherit                | redNAS                                  | 79 |  |

|    |       | 5.1.2                  | Hardware-Aware Optimization             | 78 |  |

|    |       | 5.1.1                  | Search Space Reduction Versus Diversity | 77 |  |

|    | 5.1   | Motiva                 | ation                                   | 77 |  |

| 5  | Fine  | -Graine                | ed Neural Architecture Search           | 77 |  |

|    | 4.4   | Summ                   | ary                                     | 76 |  |

# **List of Figures**

| 2.1 | Stochastic computing multipliers. (a) Stochastic multiplication in unipo-  |    |

|-----|----------------------------------------------------------------------------|----|

|     | lar encoding with range [0, 1]. (b) Stochastic multiplication in bipolar   |    |

|     | encoding with range $[-1, 1]$                                              | 9  |

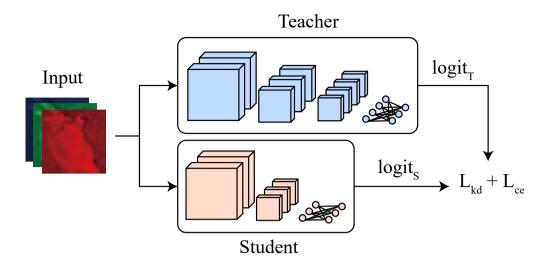

| 2.2 | Simplified knowledge distillation method                                   | 17 |

| 2.3 | Example of gradient-based neural architecture search and continuous        |    |

|     | relaxation                                                                 | 21 |

| 3.1 | Mean absolute errors for multiplications of two 10-bit streams in stochas- |    |

|     | tic computing. (a) Unipolar encoding (AND gate error). (b) Bipolar         |    |

|     | encoding (XNOR gate error)                                                 | 24 |

| 3.2 | Convolutional neural network based on stochastic computing. (a) A          |    |

|     | simplified convolutional neural network consisting of convolutional,       |    |

|     | pooling, and fully connected layers. (b) Structure of a stochastic com-    |    |

|     | puting neuron, which can be used for both convolutional and fully-         |    |

|     | connected layers. (c) Max pooling hardware structure                       | 26 |

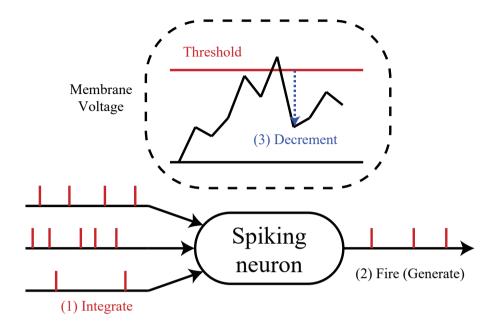

| 3.3 | Simplified integrated-and-fire (IF) neuron in spiking neural networks.     | 28 |

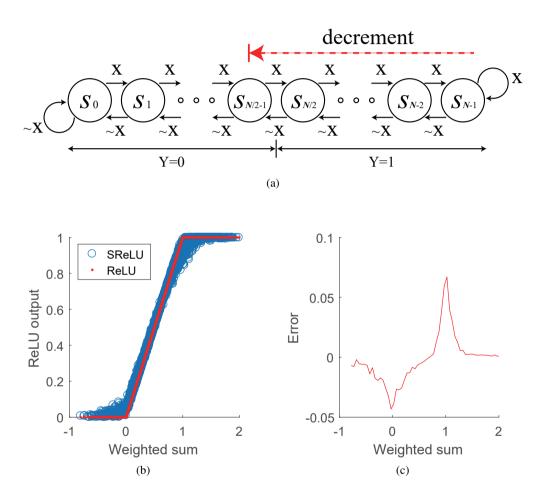

| 3.4 | Stochastic ReLU function based on finite state machine. (a) State dia-     |    |

|     | gram of SReLU. (b) Results of SReLU and saturated ReLU for $3,000$         |    |

|     | random inputs.(c) Mean error of SReLU to approximate saturated ReLU.       | 29 |

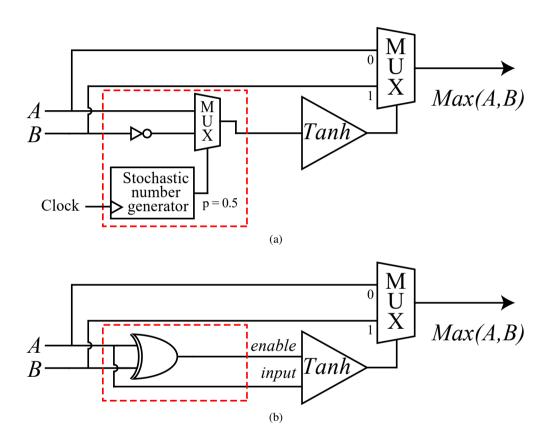

| 3.5 | Stochastic max function. (a) The conventional stochastic max func-         |    |

|     | tion. (b) Our proposed stochastic max function (SMax)                      | 32 |

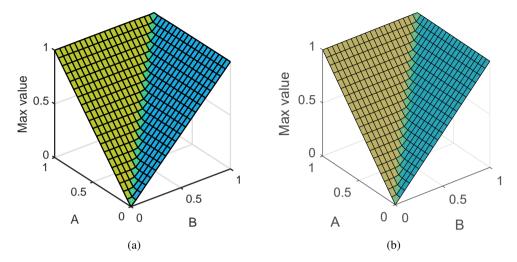

| 3.6  | Results of the stochastic max functions for 1,000 random bitstream            |    |

|------|-------------------------------------------------------------------------------|----|

|      | pairs. (a) The conventional stochastic max function. (b) Our proposed         |    |

|      | stochastic max function (SMax)                                                | 33 |

| 3.7  | Error of stochastic max functions. (a) The previous work. (b) Our pro-        |    |

|      | posed max function                                                            | 34 |

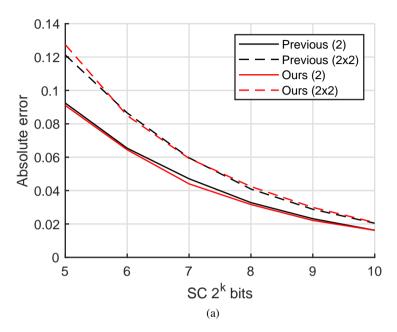

| 3.8  | Mean absolute errors of 2-input max operation and $2 \times 2$ max pooling    |    |

|      | hardware. X-axis means the length of input/output bitstreams                  | 35 |

| 3.9  | The scaled adder hardware                                                     | 36 |

| 3.10 | $2 \times 2$ stochastic average function. (a) The conventional stochastic av- |    |

|      | erage pooling function (scaled adder). (b) Our proposed stochastic av-        |    |

|      | erage function (SAvg).                                                        | 37 |

| 3.11 | Mean absolute errors of 2-input average operation and $2\times 2$ average     |    |

|      | pooling hardware. X-axis means the length of input/output bitstreams.         | 39 |

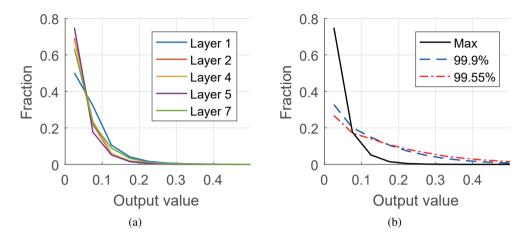

| 3.12 | Distribution of activations (output values) for each layer. The number        |    |

|      | of activations is normalized to the number of neurons in each layer,          |    |

|      | and zero activations are not counted. (a) Comparison of distributions         |    |

|      | for each layer when max normalization is applied. (b) Comparison of           |    |

|      | different normalization schemes                                               | 42 |

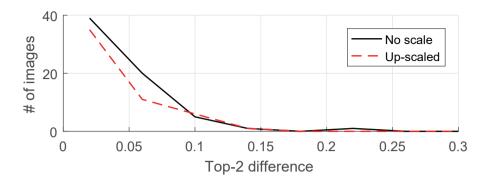

| 3.13 | Distribution of top-2 differences for misclassified images                    | 44 |

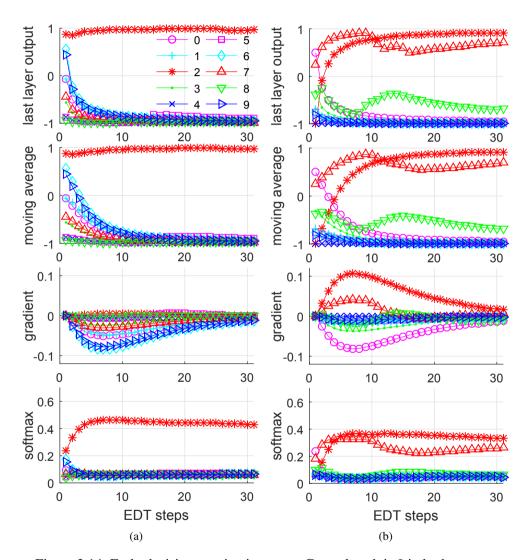

| 3.14 | Early decision termination steps. Ground truth is 2 in both cases             | 45 |

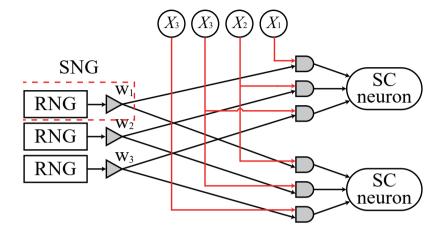

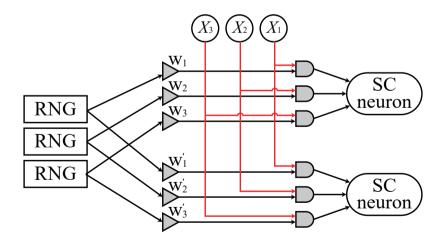

| 3.15 | Simplified sharing of a random number generator among the different           |    |

|      | stochastic number generators                                                  | 49 |

| 3.16 | Stochastic number generator sharing method for the convolutional layer.       | 51 |

| 3.17 | Stochastic number generator sharing method for the fully-connected            |    |

|      | layer                                                                         | 51 |

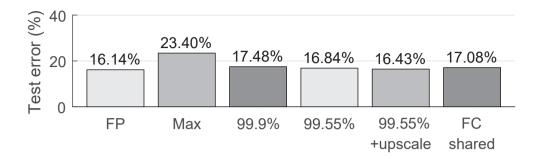

| 3.18 | Test error for CIFAR-10 dataset. The test error of floating-point is         |    |

|------|------------------------------------------------------------------------------|----|

|      | 16.14%. In SC, test error is minimized when both 99.55% normal-              |    |

|      | ization and weight upscaling are used, and its test error is $16.43\%$ . In  |    |

|      | addition, test error becomes 17.08% when RNG sharing is applied to           |    |

|      | fully-connected layer                                                        | 54 |

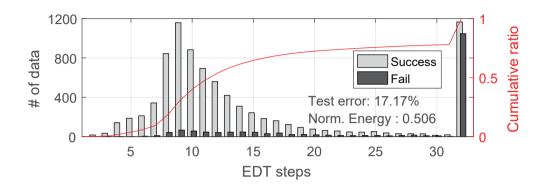

| 3.19 | Early decision termination result on CIFAR-10 dataset. More than half        |    |

|      | of the test data can be classified with lower than $2^9$ -bit precision, but |    |

|      | $20\%$ of the data still require $2^{10}$ -bit precision                     | 55 |

| 3.20 | Early decision termination result on MNIST dataset. Almost test data         |    |

|      | can be correctly classified with $2^6$ -bit precision                        | 55 |

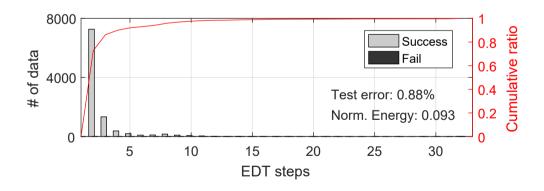

| 3.21 | Synthesis result of conventional bipolar neuron and proposed unipolar        |    |

|      | neuron. (a) Area comparison of bipolar and unipolar neuron. LFSR is          |    |

|      | used to calculate area in all neuron. (b) Energy consumption of each         |    |

|      | neuron. All circuit execute $2^{10}$ (=1024)-bits                            | 57 |

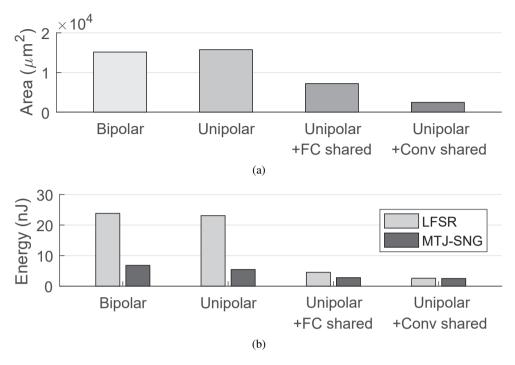

| 4.1  | ResNet and DenseNet Top-1 validation errors for different numbers            |    |

|      | of multiplications (left) and inference times (right). To measure the        |    |

|      | inference time, single NVIDIA Titan X (Pascal) is used and batch size        |    |

|      | is set to 16. DenseNet has much fewer multiplications than ResNet,           |    |

|      | but its inference time is much longer                                        | 60 |

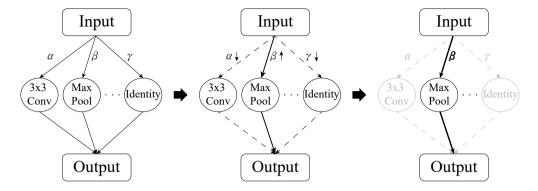

| 4.2  | Basic concept of the network recasting. The target block of the student      |    |

|      | network is trained by mimicking the source block of the teacher network.     | 61 |

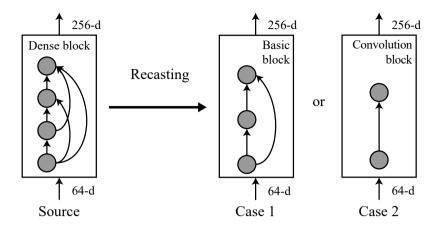

| 4.3  | Block recasting of a dense block into a basic block (Case 1) and a           |    |

|      | convolution block (Case 2). The basic block has shorter inference time       |    |

|      | than the dense block because it has much smaller activation load. The        |    |

|      | convolution block is even faster than the basic block, but its capacity      |    |

|      | is much smaller and so it can cause accuracy loss                            | 62 |

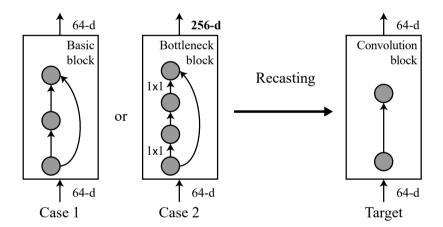

| 4.4 | Block recasting of a residual block—basic block (Case 1) and bottle-                      |    |

|-----|-------------------------------------------------------------------------------------------|----|

|     | neck (Case 2)— into a convolution block. The recasting of the basic                       |    |

|     | block keeps the same number of input and output channels. However,                        |    |

|     | since the bottleneck block uses a smaller number of channels for the                      |    |

|     | feature extraction, we recast it into a convolution block that has the                    |    |

|     | same number of input and output channels as the original $3\times3$ con-                  |    |

|     | volution                                                                                  | 2  |

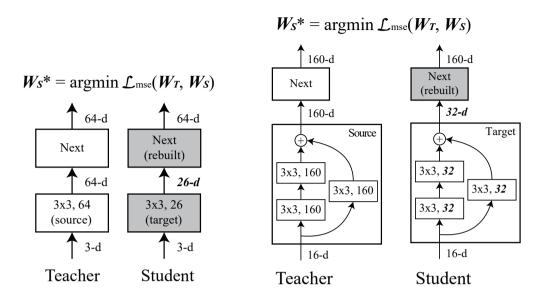

| 4.5 | Examples of the VGG-16 and WRN-28-10 compression. Both exam-                              |    |

|     | ple shows recasting of the first layer in each network                                    | 4  |

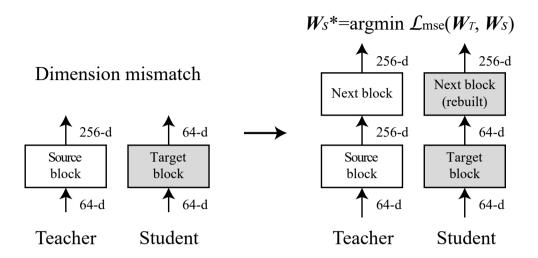

| 4.6 | Dimension mismatch and proposed block training method. The dimen-                         |    |

|     | sion mismatch happens when the source block is recast into a smaller                      |    |

|     | target block. The next block is used to match the dimension of output                     |    |

|     | activation. After rebuilding the next block, both blocks are trained by                   |    |

|     | minimizing $\mathcal{L}_{mse}(W_T, W_S)$                                                  | 6  |

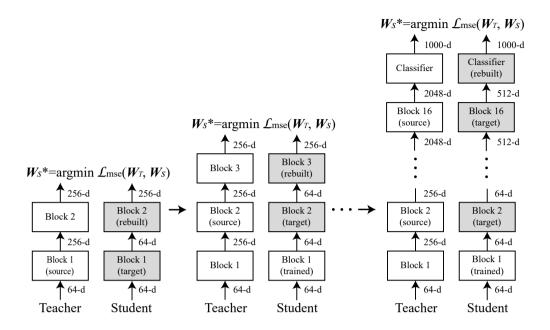

| 4.7 | Example of sequential recasting for ResNet-50. All blocks are recast in                   |    |

|     | this example. In each step, the target block and the next block (shaded                   |    |

|     | blocks) are initialized randomly and trained by minimizing $\mathcal{L}_{mse}(W_T,W_S)$ . | 68 |

| 4.8 | Example of the mixed-architecture network. It has both residual and                       |    |

|     | dense block                                                                               | 8  |

| 4.9 | Visualization of filters in the first layer of AlexNet (left) and a student               |    |

|     | network (right) Redundant filters are removed after network recasting 7                   | 0  |

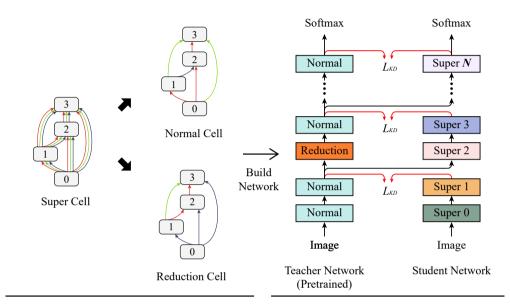

| 5.1 | The overall process of InheritedNAS. First, coarse-grain architecture          |    |

|-----|--------------------------------------------------------------------------------|----|

|     | is searched. After then the fine-grain architecture is searched with pre-      |    |

|     | trained coarse-grain architecture. To reduce the search space, we di-          |    |

|     | vide and train the network using the knowledge distillation, and the           |    |

|     | teacher network gives layer-wise/stage-wise hints to the student net-          |    |

|     | work for the fine-grain architecture search. Each super cell has its own       |    |

|     | architecture parameters, so each block has intrinsic architectures after       |    |

|     | search                                                                         | 80 |

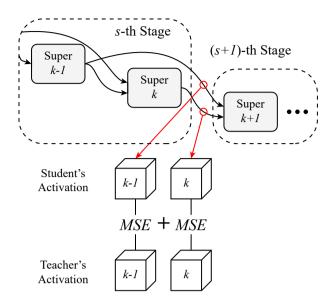

| 5.2 | The two-point matching distillation. This method can break the de-             |    |

|     | pendency from $s$ -th to $(s+1)$ -th stage, so each stage can be trained       |    |

|     | independently                                                                  | 81 |

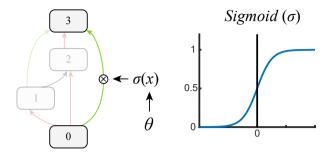

| 5.3 | Forward propagation for the connectivity parameters $\theta$ . The probabil-   |    |

|     | ity of connection is calculated with the sigmoid function, and it works        |    |

|     | as the scaling factor of each operation                                        | 83 |

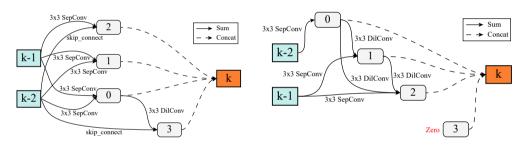

| 5.4 | Comparison of searched architecture. ( <i>left</i> ) The normal cell of DARTS. |    |

|     | (right) The first block of our searched network (OS1)                          | 80 |

# **List of Tables**

| 3.1 | Accuracy and gate count comparison for max function                     | 35 |

|-----|-------------------------------------------------------------------------|----|

| 3.2 | Accuracy and gate count comparison for average pooling                  | 39 |

| 3.3 | Average signal-to-noise ratio for different normalizations              | 42 |

| 3.4 | Comparison with previous works in terms of configuration and test error | 56 |

| 4.1 | Candidates for the network recasting                                    | 66 |

| 4.2 | Error rates (%) of architecture transform results on CIFAR datasets     |    |

|     | (B/M: billion/million)                                                  | 72 |

| 4.3 | Error rates (%) of compression results on CIFAR datasets (B/M: bil-     |    |

|     | lion/million)                                                           | 73 |

| 4.4 | Error rate (%) of network recasting results on ILSVRC2012 (B/M:         |    |

|     | billion/million, I/B: image/batch)                                      | 74 |

| 4.5 | Comparison of error rate (%) with previous works on ILSVRC2012          |    |

|     | (B/M: billion/million)                                                  | 75 |

| 5.1 | Experimental results of InheritedNAS                                    | 89 |

| 5.2 | Architecture search results through the hardware penalties              | 90 |

| 5.3 | Latency on the CPU and GPU                                              | 91 |

## Chapter 1

## Introduction

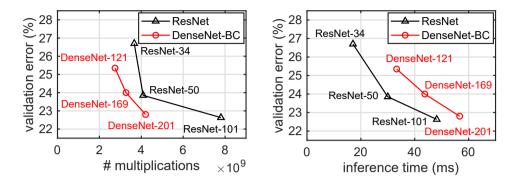

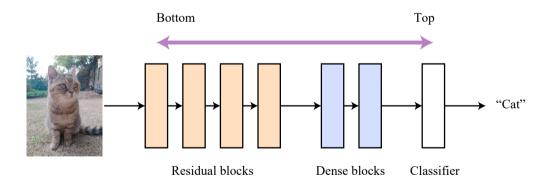

Nowadays, we live in the ear of big data, and almost global companies use them for technological advancements and people's convenience. Deep learning (DL) is considered the most popular and promising machine learning (ML) algorithm, and it is also the most famous big data application. In recent image classification challenges, a convolutional neural network (CNN), which is a kind of deep neural network (DNN) architecture, is widely used and achieves the highest classification accuracy. Several CNN architectures have been introduced to achieve even higher accuracy [1, 2, 3, 4, 5, 6], and the networks become deeper and deeper to take the exponential advantage of depth [7]. To train a deep network, He et al. [4] proposed the residual network (ResNet), which consists of the summation of identity mapping and output of convolutional layers. It helps to propagate gradients from the top layer to bottom layer, so it can alleviate the vanishing gradient problem. In addition, ResNet shows top-5 accuracy (probability of having the right answer in the top-5 predictions) higher than 95%, and top-1 accuracy higher than 80% [4], exceeding the capability of a human.

To achieve state-of-the-art accuracy, many network architectures and training methods are proposed, but it causes the inefficiency on inference. Deeper network architectures help to achieve higher accuracy, but those require a huge amount of computation.

A DNN consists of an enormous number of multiply-and-accumulate (MAC) oper-

ations for matrix-vector multiplication, which is very inefficient on the conventional hardware. In addition, several previous works show that DNN has tremendous redundancy, and it can be removed easily [8]. So, it is important to achieve the speed up and energy consumption by removing the redundancy. Moreover, hardware aware network architecture design is required for further optimization.

## 1.1 DNN Accelerator with Stochastic Computing

To reduce the computational cost while maintaining a reasonable level of accuracy, various kinds of methods have been introduced. For example, the fixed-point hardware is widely used [9] because it is much cheaper than floating-point hardware. Note, however, that fixed-point number representation has a much narrower dynamic range than the floating-point counterpart, and thus the hardware should be designed carefully to avoid overflow or underflow. Alternatively, analog computing can be adopted to perform the MAC operations at a cost lower than that of conventional digital hardware [10]. A memristor crossbar is an example of analog matrix-vector multiplications, which has been shown to have a huge improvement in terms of performance and energy consumption over digital implementations.

Approximate computing is another way of reducing computational cost by sacrificing accuracy. The concept fits well with DNNs, since sacrificing a certain level of accuracy for the internal computations of a DNN does not necessarily degrade its prediction quality. Stochastic computing (SC) can be considered as approximate computing; it has several advantages over conventional fixed-point computation and analog computation. First, compared with fixed-point, SC multiplier has a smaller hardware footprint, lower power consumption, and lower latency. Thanks to those characteristics, more neurons can be integrated into the same area compared to the conventional fixed-point hardware. Secondly, SC requires a smaller number of conversions than analog. DNNs using analog MAC hardware typically require digital-to-analog con-

version and analog-to-digital conversion much more pervasively, i.e., before and after every MAC layer. The conversion overhead of SC, on the other hand, can be confined to primary inputs (binary-to-stochastic), weight parameters (binary-to-stochastic), and primary outputs (stochastic-to-binary) [11]. In addition, SC allows dynamic change of precision without any hardware modification [12]. This characteristic of SC can be exploited to considerably reduce the latency of SC DNN at no increase in hardware cost [11].

There have been several attempts to design efficient SC hardware for DNNs, targeting fully-connected networks [11] as well as CNN [13, 14, 15, 16, 17]. However, the previous SC DNN designs have two main problems. First, they do not scale well in terms of recognition accuracy beyond the MNIST dataset. The MNIST consists of simple high-contrast gray-scale handwritten digit images. Actually, each pixel has an 8-bit value, but 80.9% of the pixels have value 0, and 7.4% of the pixels have value 250 or larger. On the other hand, general object recognition datasets such as CIFAR-10 and ImageNet have three channels with many mid-range pixels making it really difficult to classify them, which is why there is no reported result yet on those datasets in the previous SC DNN papers. Second, they incur large overhead due to the conversion of fixed-point data and weights into stochastic bitstreams, which significantly reduces energy- and area-efficiency of SC DNNs.

In the first part of the dissertation (Section 3), we address the three central problems of SC DNNs by proposing the following set of novel techniques. First, we propose to use unipolar encoding for SC DNN designs, which can help reduce random errors of SC and make SC DNN more accurate. We also propose a set of unipolar SC-based hardware modules, such as SReLU and Smax, which are SC versions of ReLU and max, respectively. Second, we propose data-driven weight normalization and weight upscaling tailored for SC DNNs. Thirdly, to minimize the conversion overhead associated with SC, we propose a novel SNG (stochastic number generator) sharing scheme.

Through our experiments, we show that our SC DNN achieves significantly im-

proved recognition accuracy and efficiency compared with the state-of-the-art result. In terms of recognition accuracy, our optimized version achieves 16.43% test error on CIFAR-10, which is very close to the floating-point test error. In terms of efficiency, we show that, with the proposed SNG sharing scheme, a fully-connected neuron and a convolutional neuron need only 47.5% and 16.2% area, respectively, compared with the conventional SC neuron without sharing. In addition, our experiments show that the energy efficiency of the fully-connected and convolutional neurons can be made  $5.3\times$  and  $9.2\times$  higher, respectively, by using the proposed sharing scheme.

#### 1.2 Neural Architecture Transformation

As mentioned before, deeper network architectures help to achieve higher accuracy, but those have a huge amount of parameters and computation redundancies. In conventional neural network training, L1 or L2 (weight decay) regularization is used to improve the generalization performance. Both methods decrease the weight values, so weights become close to zero. For this reason, most weight values are located in the near-zero area, and those hardly affect the final prediction. Actually, many filters cannot extract the meaningful features [18], so those can be removed. To obtain an efficient network, the network compression method is introduced by removing the redundancies of the trained network. The weight and filter pruning methods are introduced to remove redundant filter [8, 19], and they remove the weight or filter whose absolute value is smaller than the given threshold value. The pruning can reduce the network size effectively, so other pruning approaches are proposed for further reduction.

On the other hand, there are architectural approaches that are designing the computation efficient network. Szegedy et al. [2] propose the inception module, and it supports several filter size of convolution.  $3 \times 3$  and  $5 \times 5$  require many multiplications, so they introduce the  $1 \times 1$  convolution to reduce the number of multiplications.  $1 \times 1$  convolution is used before the main convolution, and it reduces the number of

activation channels. By using  $1 \times 1$  convolution, we can reduce not only the number of multiplications but also the number of weight parameters. For this reason, recent networks use  $1 \times 1$  convolutions [4, 6].

However, in many cases, both pruning and  $1 \times 1$  convolution cannot reduce the inference time effectively. First, the pruning method can reduce the model size effectively, but its actual speedup is much smaller than the compression ratio. Weight pruning method can remove unimportant parameters, but the filter becomes sparse matrix after pruning. The sparse matrix is hard to accelerate on conventional hardware such as CPU and GPU. Second,  $1 \times 1$  convolution causes more memory access, so it increases the actual inference time. Memory access already occupies the most of inference time, but  $1 \times 1$  convolution causes the growth of the memory access. Actually, even if the number of multiplication and parameters is small enough, the network can take a much longer time for the inference.

In the second part of the dissertation (Section 4), we focus on the inference time reduction rather than parameter and multiplication reduction. To reduce the inference time, we propose the *network recasting* method by transforming the network architecture for a smaller activation load. We transform the network architecture through the block-wise recasting of source blocks into target blocks. The recasting is done by training the target block to mimic the output activation of the source block, so the accuracy can be preserved after recasting. We can obtain a *mixed-architecture network* by recasting parts of the trained network. By the mixed-architecture network, we mean a network having multiple types of the block that can exploit the advantages of individual block types within a single network. In addition, we can use the network recasting method for network compression by recasting each block to a smaller one of the same type. We have achieved up to  $3.2\times$  actual speedup with 0.22% top-5 accuracy loss on ILSVRC2012 dataset by the DenseNet-121 recasting.

#### 1.3 Fine-Grained Neural Architecture Search

Recently, neural architecture search (NAS) is proposed to design network architecture automatically. NAS is one of the automated machine learning (AutoML) research, and it finds the neural network architecture with the neural network. Zope et al. [20] propose the first modern NAS algorithm, and it can find architecture using the deep reinforcement learning (RL). The overall process is similar to the design space exploration, but the deep RL can reduce the search space effectively. The evolutionary algorithm also can reduce the search space, so it is also combined with NAS algorithm [21]. However, those method requires a huge amount of time because every network architecture has to be trained during the search process. To reduce the search time, Liu et al. [22] propose the gradient-based NAS approach. Gradient-based NAS is finding the network architecture with conventional cross-entropy loss. This method trains network only one time, so it can reduce search time dramatically.

For the convergence, many NAS algorithms restrict the search space. Cell-based architecture search finds cell architecture and reuses them over the entire network. It has a much smaller search space compared with the whole architecture search, so it is much easier. However, a cell-based approach reduces the diversity of each cell, so it can reduce the optimization chance. According to the position in the network, each layer has a different characteristics. For example, the bottom layers have large input and output activation, and the top layers have large parameters. By adopting the proper structure, parameter, and memory overhead can be relaxed. ProxylessNAS [23] and FBNet [24] allow the layer-wise search space by using the simpler cell structure for the convergence.

In the last part of the dissertation (Section 5), we proposed *InheritedNAS*, the fine-grained architecture search method. The proposed method gives diversity for each block, so the network can achieve a higher accuracy or more efficient inference. To obtain the fine-grained architecture, we propose *the stage independent architecture search*, which can reduce the complexity of search space preserving the block diver-

sities. In addition, we also proposed *the operation pruning*, which is the operation removing method. This method estimates the importance of each operation and prunes the less important operations. The operation pruning optimizes each block and helps to achieve a more efficient network. On the other hand, we also proposed *the mixed penalty* that consists of FLOPs and memory access for hardware-aware architecture search. This penalty also keeps the block diversity and helps to find hardware friendly block designs.

## Chapter 2

## **Background**

## 2.1 Stochastic Computing

The stochastic computing (SC) is the digital hardware design scheme, and it is based on the probability theorem. SC uses the bitstream to express the number, and it is called the stochastic number. The bitstream consists of only 0 and 1, and the probability of emerging 1 means the actual value of a stochastic number. Only one bit (0 or 1) can be observed in every cycle, and the bits emerge during the several cycles. For example, nine 1s and one 0s are observed during ten cycles, the value of this stochastic number becomes 9/10 in the binary system. If every bit is 1 or 0 in a bitstream, this value becomes 1 or 0 in the binary system. Therefore stochastic number has a range limitation form 0 to 1, and it is also the same as the probability. By generating the 1s with probability p, it means that stochastic number has p value in the binary system. Basically, an additional sign bit is required for the negative value because there is no negative probability. Therefore, the number of bit lines becomes twice due to the additional sign bit. However, the additional bit line is can be saved when 0 bit is regarded as -1. For the same example, the value becomes (9-1)/10 when there are nine 1s and one 0. In this case, the lower limit of the stochastic number becomes -1. Therefore, the value of stochastic number and its range limitation is changed according to

$$\begin{array}{c} 1,1,1,1,0,1,1,1,1 \ (9/10) \\ 0,0,1,0,0,0,0,1,0,0 \ (2/10) \\ \hline \\ 1,1,1,1,1,0,1,1,1,1 \ (8/10) \\ \hline \\ 0,0,1,0,0,0,0,1,0,0 \ (-6/10) \\ \hline \\ \end{array}$$

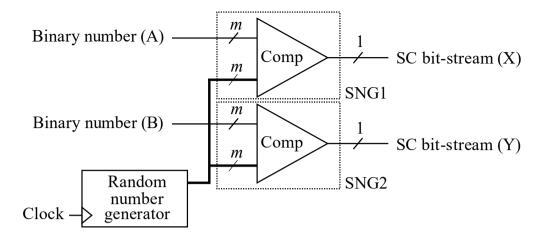

Figure 2.1: Stochastic computing multipliers. (a) Stochastic multiplication in unipolar encoding with range [0, 1]. (b) Stochastic multiplication in bipolar encoding with range [-1, 1].

the meaning of 0 bit. The former case is called as *the unipolar encoding*, and the latter case is *the bipolar encoding*.

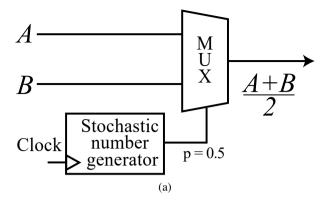

SC has a very small hardware footprint compared with the binary system. For example, multipliers can be implemented with only one gate in SC. Figure 2.1 shows the multiplier of SC for the unipolar and bipolar encoding. In unipolar encoding, single AND gate work as the multiplier. The value of the upper bitstream is 9/10, so 1 is generated with a probability 0.9, and 1 is also generated with a probability 0.2 in the lower bitstream. So, the probability that both bitstreams have 1 bit is  $0.9 \times 0.2$ , and this is the same with AND gate operation. The XNOR gate is used for the multiplication in the bipolar encoding. Likewise, the scaled addition and subtraction are implemented with only one multiplexer, so those also have a very small hardware footprint. Thanks to this characteristic, SC is used in the signal processing hardware [25, 26, 27, 28, 29]. The edge detection logic can be implemented using only two XOR gates and one MUX [25], and gamma-correction logic also consists of one OR gate and one DFF [26].

Another advantage of SC is that the computation precision can be changed without any hardware modifications. The precision of the stochastic number and computation logics is directly related to bitstream length. So, the precision of the given number can be adjusted by changing the bitstream length. When the bitstream length is reduced to  $2^{n-1}$ , its precision is also reduced to n-1-bit. In addition, the precision of arithmetic

logics depends on the precision of given input bitstreams, so the bitstream length has to be changed to adjust the precision of the entire hardware. Thanks to this characteristic, the concept of the progressive precision is introduced [25]. The quality (or prediction accuracy) of processing result is improved according to the computation cycles. The decision time is can be reduced when simple data (or operation) is given. For example, in the edge-detection, the sharp edges can be found easily, so the computation cycles of sharp edges can be reduced effectively.

#### 2.2 Neural Network

The neural network is a kind of machine learning algorithm. The artificial neural network (ANN) mimics the behaviors of the neuron [30], and it was widely used for the regression problem because ANN can approximate any kind of function [31]. After introducing the backpropagation [32], the deep neural network (DNN) can be trained. As the depth of the neural network increases, the DNN achieves much higher prediction accuracy for the classification problem. These days, the DNN shows the state-of-the-art result for the many artificial intelligence areas compared with other machine learning algorithms. However, the computation cost and inference time also increase according to the network depth. To solve this problem, there is a lot of researches in both software and hardware aspects.

#### 2.2.1 Network Compression

For the software approach, the network compression method is proposed to reduce the DNN model size and its inference time. The network depth and width dramatically increases to improve the prediction accuracy, but the actual improvement is much smaller than the network expansion. Therefore, many researchers have been focusing on the redundancy of the trained network. To reduce the network size, the weight pruning, and quantization methods are introduced [33, 34, 8]. Moreover, the matrix decompo-

sition method also used to reduce the parameter by using a low-rank approximation technique [35]. Nowadays, many researches focus on the network pruning and the quantization method and reduce the model size preserving the accuracy of the trained network.

#### **Pruning**

To reduce the search space or running time, the pruning method had been widely used in the various research areas. Han et al. [8] propose a weight pruning method, which removes useless weight connections. It is the first approach introducing the pruning method to neural network research. The basic concept of the first weight pruning is that the near-zero weight can be removed with any significant accuracy loss. After pruning, the removed weights are never used. To give the degree of freedom, the other works reuse the pruned weights. Guo et al. [36] introduce the pruning mask, which decides the pruning candidates. The mask is determined in every pruning epoch, and the pruned weight can be revived. Han et al. [37] also propose a re-initialization method, and it means that the pruning weights are revived with random initial values. This re-initialized weight can improve the prediction accuracy after the fine-tuning. Furthermore, the filter-wise pruning methods are also proposed [19, 38, 39, 40, 41]. In previous observation, several filters do not extract the meaningful features [18], and it can be removed with the group lasso regularization [42, 43]. Some previous approaches for the filter pruning are similar to the weight pruning method [19, 44]. The average percentage of zeros (APoZ) and the sum of absolute value are used to estimate the importance of each filer, and filters are pruned iteratively according to the estimated importance. Luo et al. [39] propose an activation-based pruning method, where pruning candidates are determined by the squared error of activations. They assume that small activation is not important for classification because it barely affects higher-level feature extraction. In recent work, Lin et al. [40] use reinforcement learning (RL) to prune filters according to the input data. This work introduces runtime neural pruning that removes the filters using deep Q-network for each input data in runtime. Basically, these filter pruning methods achieve faster inference on a GPU, but still have limitations in compression; the methods for estimating the importance of filters should be designed manually with prior knowledge, and nonetheless, those methods cannot find redundant filters effectively due to a great deal of complexity.

#### **Ouantization**

Another network compression approach is the quantization, and it can be used for the weight as well as activation value. The neural network does not require high computation precision, because it generates the decision probability [45]. The differences between the first and the second probable class are commonly large enough for the correct classification. In other words, those input data can be classified with lower precision when the computation error is smaller than the difference. By reducing the computation precision, the network size also can be reduced because it depends on the total memory of the weight values. Moreover, the computation cost also can be reduced according to the computation precision. For this reason, lots of the network quantization methods are proposed for efficient inference. The homogeneous quantization method is firstly proposed and it shows high compression results with reasonable accuracy loss [46]. The stochastic rounding method is proposed to use a much lower computation precision [47]. Han et al. [48] propose the weight sharing based quantization method, which can be used to achieve much higher compression ratio by using Huffman encoding. The layer-wise quantization methods are introduced for further improvement and those researches reveal that the input and output layer requires high precision but other layers can be quantized much lower precision [49, 50]. To reduce the model size extremely, the ternary weight and binary weight quantization methods are proposed [34, 51, 52]. Recently, many researches use the additional loss function to alleviate the accuracy loss in the quantization process. The explicit loss-error-aware Quantization (ELQ) is proposed to ternarize or binarize the weight value with much smaller accuracy loss [53]. The ELQ considers both the weight approximation error and its impact on the cross-entropy loss, so it can help to preserve the prediction accuracy. The learnable quantization method is also introduced [54], and the new quantization parameters are included in the training process. Furthermore, the automated quantization method is also proposed [55]. By using the deep reinforcement learning algorithm (the actor-critic model proposed by [56]), the quantization levels are determined.

#### 2.2.2 Neural Network Accelerator

DNN consists for a huge amount of multiplications and accumulations (MACs). For example, the number of multiplication is 4.09 billion in ResNet-50 model [4]. There is a tremendous amount of computation, so it spend a very long time in conventional computer architecture. However, the multiplication and accumulation emerge regularly, and its computation pattern is fixed when the network is chosen. For this reason, it can be accelerated easily by increasing the parallel computation, so many DNN accelerators are introduced. In addition, the network compression methods can help to achieve much faster inference, so the compression-aware accelerator design is very important.

#### **Conventional Binary System**

First of all, the DianNao [57] is designed to increases the utilization of the processing elements (PE) by using a tiling approach, and it achieves much higher speed-up compared with the conventional GPU architecture. And, the Eyeriss propose the spatial architectures that based on the CNN row stationary dataflow [58]. The systolic array is used to improve the efficiency of the convolution/fully-connected operation for the data center [59]. For further improvement, the network compression methods are considered to design the accelerator. The weight pruning can remove the connections of neurons, but it makes the sparse matrix so it is hard to be accelerated in conventional GPU architecture. However, it is easy to implement skipping operation for the zero

weights, so DNN accelerator can achieve further speed-up and energy-saving [60]. Most of the activation values also become zero due to the ReLU activation function that is widely used in modern neural network architecture. Another previous work propose both zero weight and activation skipping hardware, and they also solve the load imbalance problem caused by lots of zero values [61]. DNN accelerators also exploit quantized weight and activation values. Basically, a huge amount of area and energy consumption can be reduced by using the fixed-point rather than floating-point hardware [57]. The mixed-precision hardwares are proposed to use the advantages of the layer-wise quantization. The bit-serial hardware is proposed to support varying the bit precision [62]. The bit-flexible hardware also is proposed, and it used the bunch of 2-bit arithmetic operations to supporting the power-of-2 bitwidth operations [63]. By combining the quantization with sparsity, the DNN accelerator shows a much powerful result compared with conventional computer architecture [64]. In recent works, the prediction method is also used for further improvement. The SnaPEA architecture used the reordering and sampling method to predict the pre-activation values [65]. They calculate the partial sum of the convolution, and they skip the remaining operation when the temporal partial sum becomes smaller than zero. The ComPEND architecture also focuses on zero value prediction, but they change the two's complement operation [66]. The two's complement value consists of the large negative value and smaller positive values to express the negative. They invert this composition, and they calculate positive first, and then stop operation when the partial sum drops below zero. The convolution is used in the spatial domain, so it has local similarity. By using this characteristic, several works focus on the value prediction and its hardware for spatial domain [67].

#### **Analog System**

To implement a lower precision accelerator, an analog circuit can help to reduce area and energy consumption. The ISAAC proposes the memristor crossbar array architecture for the multiply-accumulate (MAC) operation [10]. For the MAC operation, digital-to-analog conversion and analog-to-digital conversion are required, but it has a huge amount of area and energy consumption overhead. They solve those problems by using the flipped form of the weight values, and it reduces ADC size effectively. The Prime architecture uses ReRAM crossbar array similar to ISAAC, but it chooses processing-in-memory (PIM) architecture for its implementation [68]. The PipeLayer proposes the highly parallel design according to the parallelism granularity and weight duplication by exploiting the inter-layer parallelism [69].

#### **Stochastic Computing System**

Approximate computing is another way of reducing computational cost by sacrificing accuracy. The concept fits well with DNN, since sacrificing a certain level of accuracy for the internal computations of a DNN does not necessarily degrade its prediction quality. SC can be considered as approximate computing; it has several advantages over conventional fixed-point computation and analog computation. First, compared with fixed-point, SC multiplier has a smaller hardware footprint, lower power consumption, and lower latency. Thanks to those characteristics, more neurons can be integrated into the same area compared to the conventional fixed-point hardware. Secondly, SC requires a smaller number of conversions than analog. DNN using analog MAC hardware typically requires digital-to-analog conversion and analog-to-digital conversion much more pervasively, i.e., before and after every MAC layer. In addition, SC allows dynamic change of precision without any hardware modification [12]. For those reasons, many previous works attempt to implement the SC DNN accelerator.

SC logics for the neural computation is proposed [70], and ANN is implemented with proposed logics [71]. However, only a single layer ANN model can be implemented, and SC cannot be used for the modern DNN model. SC has computation error and it is amplified pass through the many layers in DNN, so it cannot classify any given data. In addition, SC logics proposed in previous work [70] only support

only a single-input case. To solve those problems, the weight scaling method and new stochastic hyperbolic tangent are proposed [11], and it is the first full SC hardware for the modern DNN. In addition, they also use the progressive precision characteristic of SC and propose the early decision termination method to considerably reduce the latency of SC DNN at no increase in hardware cost. The DSCNN architecture supports SC-CNN, and they propose the improved version of single input stochastic hyperbolic tangent function [13]. After then, many CNN architectures with full SC logics are proposed. The SC-DCNN propose the optimized SC MAX pooling logic and reorganize the structure of convolutional neuron by switching the activation function and pooling operation [14]. To achieve a more efficient SC-DNN accelerator, li et al. [15] investigate the relationship and accuracy result for the MUX based inner product, parallel counter-based inner product, and order of activation function and pooling operation. The new version of SC tanh logic and SC ReLU function logics are proposed and those hardwares can improve the energy efficiency [16].

On the other hand, partial SC hardwares are also proposed. For the partial SC hardware, the binary-to-stochastic and stochastic-to-binary conversion is needed similar to the analog DNN accelerator. The SC-MAC hardware is proposed to solve conversion overhead, and it also improves the multiplication accuracy by reducing the effect of stochastic error [72]. They use the thermal coding for one stochastic number so it only requires down counter for the multiplication. And it shows similar accuracy with conventional SC multiplication because the randomness of other value is still guaranteed. The dynamic precision scaling technique is also proposed to change the precision in runtime [73]. The other work proposes the differential Multiply-and-Accumulate (DMAC) logics, and it helps to achieve the much higher speed-up compared with the previous SC-MAC hardware [74].

Figure 2.2: Simplified knowledge distillation method.

## 2.3 Knowledge Distillation

To train a smaller network with higher accuracy, mimic learning and knowledge distillation (KD) are introduced [75, 76]. These methods train a smaller network called *student network* using logits of a large network called *teacher network*. The teacher network was trained by minimizing cross-entropy loss that is widely used in conventional neural network training, and then the student network is trained by following the logits of the teacher network. The logits of the teacher network is considered as the soft target values, so it is much easier to follow the logit values rather than the original labels as shown in Figure 2.2. To follow the behavior of teacher network, Ba and Caruana [75] trains a student network by minimizing L2 loss between logits of student and teacher networks. Hinton at al. [76] uses logits of the teacher network to generate the soft target, and train the student network by minimizing cross-entropy loss with the soft target. Both works achieve a higher accuracy than conventional training method by using the proposed method, and Hinton at al. [76] also obtains the network that has the accuracy of the ensemble model. It is hard to train a deep student network due to the vanishing-gradient problem, so several KD methods have been proposed

to train a deep student network [77, 78]. Romero at al. [77] propose the hint training method that trains the student network with a convolutional regressor. They use a thinner and deeper student network, and train half of the student network by following the teacher network. Due to the dimension of the feature map is not matched, they use convolutional regressor and then train student network. After then, they also use the KD method for training of the entire network. Their method shows the higher accuracy compared with the original KD method, and they also show reasonable training result for the deeper network without any shortcut path. Luo et al. [78] also propose the method to train the deeper network. They also use a feature map of a hidden layer, but they use an additional path from the hidden layer to the output layer for gradient propagation. It also shows a better result compared with the conventional backpropagation method.

Recently, the KD method is widely used for the various areas; network compression, quantization, and network transformation. For the network compression, the activation matching method is widely used [79, 80]. The activation matching is a kind of hint training, but they never use the convolutional regressor. Zagoruyko et al. [79] introduce the attention transfer method to reduce the number of residual blocks while conserving the accuracy. The attention map is the channel-wise accumulation result in the feature map, and it shows the effective points in forward propagation. By following the attention map of the teacher network, the student network also can follow the behavior of the teacher network. They show the layer reduction of ResNet [4], and it shows a much better result compared with conventional training. Yim et al. [80] also propose the residual block reduction method using the relationship between input and output activations. Rather than the attention map, they propose the flow of the solution process (FSP), and this concept mimics the teaching method of a real-world teacher. In the real-world, the teacher does not give the solution, but they show the process to reach the solution. Similar to the real-world teacher, they give the relationship of input and output feature map to the student network. By mimicking the FSP, the student network can be trained well. For the quantization, KD can also be applied easily [81, 82, 83]. Mishra et al. [81] use the low precision network as the student network, and it mimics the behavior of the teacher network similar to the original KD method. They show several kinds of quantization methods with KD, and the fine-tuning method achieves the best result. The fine-tuning method use a fully trained teacher and student network and then apply quantization. To restore the accuracy, the student network is fine-tuned by minimizing KD loss. Polino et al. [82] propose the differentiable quantization method, and it optimizes the location of quantization points. They define the differentiable quantization function, the quantization precision can be determined through the standard SGD. Their quantization process consists of the differentiable quantization and quantized distillation. After the quantization, they also use the KD method to recover the accuracy loss. For the network transformation, several previous works show the noticeable results [84, 85, 86]. Furlane et al. [84] firstly show the possibility of KD between different network architecture. They show the ResNet training result using logits of DenseNet, and it shows a better result compared with conventional backpropagation. Heo et al. [85] also show that KD can be applied between different network architecture. Li et al. [86] use the KD for the neural architecture search (NAS) application.

### 2.4 Neural Architecture Search

The neural architecture search (NAS) is the method to find better neural network architecture using the neural network itself. It is one of the automated machine learning research areas (AutoML), and Zoph and Le [20] propose the first NAS method. They propose the controller network using RNN, and it is trained to find network architecture. The controller generates the architecture hyperparameters such as filter size, stride, the number of output channels, the number of layers, etc. The network is built with the generated architecture hyperparameters, and it is trained to estimate valida-

tion accuracy. The validation accuracy is used to calculate the reward value to train the controller network, so it works as the environment in reinforcement learning. The controller is trained to increase the reward, and finally it can find the reasonable network architecture and shows good validation accuracy. To find better network architecture, the concept of a cell structure is proposed [87, 88]. The cell is the building block of network, and the network consists of several cells. This concept is already widely used for the network architecture design. For example, DenseNet [6] consists of the dense block and ResNet [4] also consists of residual or bottleneck block. Thanks to the concept of cell structure, the search space is dramatically reduced. They only find two kinds of cell; normal cell and reduction cell [87]. Training of the controller becomes much easier than previous work because the search space is much smaller.

The evolutionary algorithm is used to find neural network topology [89]. They firstly use the evolutionary algorithm for the network search, and it only covers the simple multi-layer perceptron. Liu et al. [90] propose an architecture search algorithm with the evolutionary algorithm for modern CNN architecture. They combine the evolutionary algorithm with the cell structure, and they only use a single cell as the network building block. To reduce the feature map size, they use the separable convolution with stride 2 that is proposed in [91]. Real et al. [21] combined evolutionary algorithm with the cell structure, and find normal and reduction cell. They find the network that has higher accuracy and lower computation cost compared with RL based architecture search. Elsken et al. [92] propose multi-objective architecture search for evolutionary architecture search, it covers accuracy, inference time, and the number of parameters.

One-shot architecture search is one of the neural architecture searches, which train all operations and select proper operation after training [93, 94, 95, 96, 22]. Basically, a one-shot search reuses the trained weight parameter for final prediction. The differentiable architecture search is one of the one-shot architecture searches, which is found network architecture by training itself. Liu et al. [22] propose the concept of gradient-

Figure 2.3: Example of gradient-based neural architecture search and continuous relaxation.

based architecture search (DARTS), and it can reduce the network search time dramatically. Previous RL-based and evolutionary search requires a huge amount of time to train each candidate network. However, gradient-based architecture searches train weight parameters, and it also search network architecture concurrently. Due to the network architecture is discrete, it is hard to train the network architecture with conventional training loss. To solve this problem, DARTS propose continuous relaxation for the operation selection. They replace the discrete selection with softmax function, and train architecture parameter to find proper architecture as shown in Figure 2.3. A gradient-based search takes a few GPU days to find network architecture, and it is much faster than previous RL-based search. For this reason, the gradient-based search is widely used in recent work. To improve the performance and efficiency of DARTS, several methods are proposed. ProxylessNAS reduces the memory consumption by using binarization method, so it can support a large-scale tasks (e.g. ImageNet) [23]. DARTS has to compute all operations for the training, so its memory consumption is proportionate to the number of operations. Actually, DARTS uses 8 operations for each edge, so its memory consumption is about 8 times compared with the standard network. Due to this characteristic, DARTS cannot find large-scale network directly. To solve this problem, ProxylessNAS select operation according to the probability, and then train architecture parameters with the binarization method [97]. In forward propagation, the operation is binarized, and the selected operation is only calculated. In backward propagation, the gradient is calculated the same as conventional backpropagation, and architecture parameters are updated for selected operation as well as non-selected operation. ProxylessNAS also propose the latency penalty, and it can help to find a faster network for the given hardware. They measured the latency of each block for the given hardware (GPU and mobile CPU), and use those measured value for the latency penalty. FBNet [24] and FBNetV2 [98] use similar approaches, but FBNetV2 also support spatial and channel dimension search. The previous gradientbased search uses pre-defined spatial and channel dimensions, and those are regarded as the trainable parameters in FBNetV2. They propose a channel masking method to determine channel dimension dynamically, and resolution subsampling is used for the spatial dimension. They use several masks that have different size, and one mask is selected according to the gradient descent similar to gradient-based operation selection. Recently, several works focus on the latency constraint in the network architecture search. ProxylessNAS and FBNet show the latency estimation method using the linear combination of every block. However, this method cannot estimate the latency of complex network architecture such as DARTS. For this reason, Xu et al. [99] propose the latency prediction model (LPM), and it can predict the latency of the determined network using architecture configuration. By using LPM, latency becomes a differentiable term, so it can be applied for the latency penalty.

# **Chapter 3**

# **DNN Accelerator with Stochastic Computing**

### 3.1 Motivation

## 3.1.1 Multiplication Error on Stochastic Computing

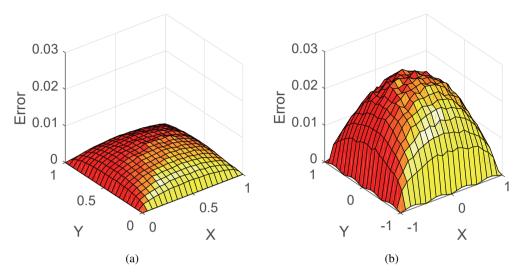

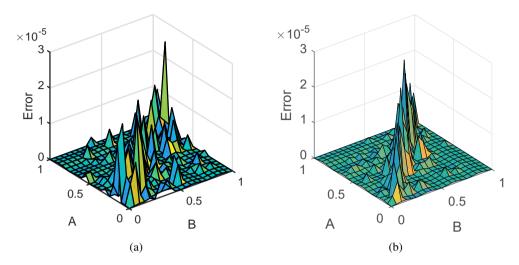

In stochastic computing, a multiplier can be implemented with a single AND gate for unipolar encoding and a single XNOR gate for bipolar encoding as we mentioned Section 2.1. The two input stochastic bitstreams are multiplied by a multiplier (AND or XNOR gate), generating outputs cycle by cycle (one bit at a cycle), which is similar to bit-serial logic. The multiplication results are close to the accurate ones but may have some stochastic errors. Figure 3.1 shows the multiplication errors for the two encodings; each point represents the absolute error averaged over 1,000 multiplication results. The error is maximized when both input values are 0.5 in unipolar encoding, while it is maximized when they are 0 in bipolar. In both cases, the maximum error occurs at the center, but the mean absolute error of the bipolar case is 3.76 times higher than that of the unipolar case.

Figure 3.1: Mean absolute errors for multiplications of two 10-bit streams in stochastic computing. (a) Unipolar encoding (AND gate error). (b) Bipolar encoding (XNOR gate error).

## 3.1.2 DNN with Stochastic Computing

Sigmoid, hyperbolic tangent, and ReLU are commonly used activation functions in DNNs, but ReLU is most popular because it suffers less from the gradient vanishing problem during the backward propagation in a training phase [100], and so deeper networks can be better trained.

When using ReLU in SC hardware, unipolar encoding can be a better choice, because ReLU generates many zero activations (during the forward propagation, ReLU generates 0 at the output when the input is negative). Actually, more than 50% activation values are 0 when ReLU is used [61], so zero values have to be multiplied with weights in the next layer. In bipolar encoding, zero multiplication error is the biggest, and zero value also maximizes switching activity in the hardware. However, zero multiplication is accurate in unipolar encoding, and there is no switching activity. Therefore, unipolar encoding is well-matched with ReLU, and better than bipolar encoding in terms of computation accuracy and energy consumption.

For those problems, unipolar encoding can be a better choice than bipolar encoding. By using unipolar encoding, we can compute near-zero values with a much smaller stochastic error. In addition, we can use unipolar encoding without additional sign bit due to the ReLU function. ReLU function removes all negative values, so every activation value becomes positive. Thanks to this characteristic, we can save a bit-line and improve computation accuracy at the same time. For those reasons, we choose the unipolar encoding for the SC DNN designs, and it is well-matched with DNN.

## 3.2 Unipolar SC Hardware for CNN

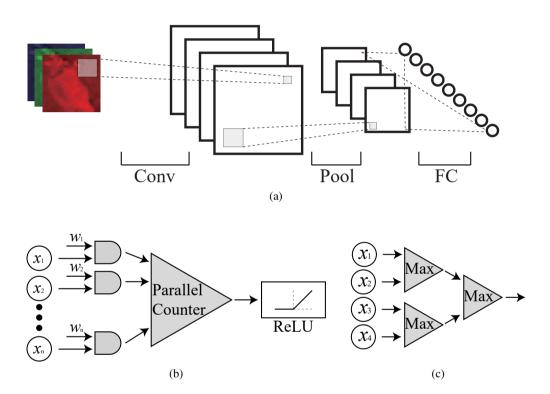

### 3.2.1 Overall Hardware Design

A CNN consists of three major layers: convolutional layer, pooling layer, and fully-connected (FC) layer. The feature maps of an input image are extracted by the convolutional layer. After that, the pooling layer reduces the size of each feature map, which is directly related to the amount of computation. And then, the FC layer classifies the input image with the resulting feature maps. Figure 3.2(a) illustrates a simplified network and the order of the three basic layers. The layers can be stacked to make a stacked network (deep neural network), which is widely used these days to classify more complex images and to improve the classification accuracy. For example, LeNet-5 [32] is a famous network for MNIST dataset; it consists of two convolutional layers, two pooling layers, and two FC layers.

The convolutional layer and the FC layer are two main layers where most of the computations take place. Each of the layers typically contains many neurons and each neuron basically performs MAC operations regardless of the layer types. Actually, we can implement the FC layer with the convolutional layer when its filters cover all pixels of input feature map. Thus the two layers can be implemented with neurons of the same structure. Figure 3.2(b) shows the SC hardware structure of such a neuron. The neuron consists of AND gates for multiplications, a parallel counter for accumulation,

Figure 3.2: Convolutional neural network based on stochastic computing. (a) A simplified convolutional neural network consisting of convolutional, pooling, and fully connected layers. (b) Structure of a stochastic computing neuron, which can be used for both convolutional and fully-connected layers. (c) Max pooling hardware structure.

and a stochastic ReLU module for activation. Stochastic bitstreams coming from the previous layer are multiplied with weight bitstreams using the AND gates. The input bitstreams are always positive or 0 because of ReLU, but the weight values can be negative; thus, the sign of a multiplication result will be the same as the sign of the weight. Therefore, for the multiplication result, we can make the AND gate calculate only the magnitude in unipolar encoding and then take the sign of the weight. For the accumulation of the multiplication results, we use two small adder trees per neuron, one for the group of negative multiplication results and the other for that of positive ones. Because the sign of a multiplication result depends only on the weight fixed by the training, the grouping of the multiplication results is also fixed and the implementation can be easy and efficient. Each adder tree for accumulation is implemented by a parallel counter. In every cycle, the counters count the number of ones in the multiplication results to generate negative and positive sums. The two sums are added together to obtain the final accumulation result for the corresponding cycle. Finally, the output activation bitstream is generated by the stochastic ReLU (SReLU) function. SReLU generates positive unipolar streams from the accumulated values (refer to Section 3.2.2 for the details). Figure 3.2(c) illustrates the max pooling layer consisting of several stochastic max (Smax) functions. In this paper, we mainly use the  $2 \times 2$  max pooling to implement networks for CIFAR-10 and MNIST datasets because  $2 \times 2$  is a popular size for a max pooling layer (refer to Section 3.2.3 for the details). For the efficient average pooling, we also proposed designing method and we will cover its detail in Section 3.2.4.

#### 3.2.2 Stochastic ReLU function

The basic concept of SReLU is inspired by the integrate-and-fire (IF) neuron in spiking neural networks (SNN) [101]. Figure 3.3 illustrates the behaviors of integrate-and-fire neuron. The IF neuron integrates all input spikes into its own membrane voltage, and increase or decrease the membrane voltage according to the synaptic weight values. If

Figure 3.3: Simplified integrated-and-fire (IF) neuron in spiking neural networks.

the resulting membrane voltage becomes larger than a preset threshold, an output spike is generated, and the membrane voltage is decreased by the threshold value. Otherwise, the membrane voltage remains the same. SReLU is an FSM (finite state machine) that mimics the three key operations of the IF neuron: integration, output generation, and decrement. The integration of the input spikes coming from the parallel counter is implemented as a transition to a higher state in SReLU. Differ from the IF neuron, SReLU just integrates accumulated value with its state (membrane voltage) because the weighted sum is covered by AND gates and parallel counter. If the resulting state is higher than the threshold after the integration, the output bit becomes 1, and a transition is made to a lower state to mimic decrement of the membrane voltage. Otherwise, the output bit becomes 0 and no state transition occurs.

Figure 3.4(a) illustrates the state diagram of SReLU. Each state works as the corresponding membrane voltage. Among the N states, the (N/2-1)-th state represents 0 volt, and the lower states and the upper states represent negative values and positive

Figure 3.4: Stochastic ReLU function based on finite state machine. (a) State diagram of SReLU. (b) Results of SReLU and saturated ReLU for 3,000 random inputs.(c) Mean error of SReLU to approximate saturated ReLU.

values, respectively. The number of states is determined based on the number of input bitstreams so that the FSM can cover the dynamic range of the incoming accumulation result. According to our experience, it is sufficient to set the number of states to twice the number of input bitstreams. For the sake of efficient implementation, we set the number of states to power of two.

We set the threshold for output spike generation to half of the highest state value. Then the decision to fire a spike depends only on the MSB of the state value. Thus, in every cycle, the SReLU module first checks the MSB of its own state value. If it is 1, the module lowers the state by the threshold value. Then the input value (accumulation result) is added to the state. Note that the output is always the same as the MSB of the state value and thus no additional hardware is needed.

Figure 3.4(b) shows the comparison between SReLU and conventional ReLU with saturation, and Figure 3.4(c) shows mean error of SReLU function. 3,000 random bitstreams are used to calculate the outputs and the mean errors. The maximum value of SC bitstream is 1 because of range limitation, so the SReLU output cannot express numbers larger than 1. For this reason, as shown in Figure 3.4(b), the output is saturated to 1 when the weighted sum is larger than 1. However, the error due to saturation is not really an issue since the problem can be alleviated by applying normalization, which will be explained in Section 3.3. The accuracy of negative and linear regions is more important than that of the saturation region, but as shown in Figure 3.4(c), the errors are much smaller in those regions.

#### 3.2.3 Stochastic Max function

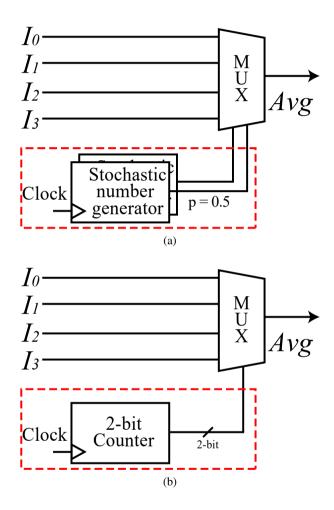

Figure 3.5(a) illustrates the stochastic max function was proposed in [29]. The basic concept of the previous max function is that A increases and B decreases the state of the hyperbolic tangent. This is the reason why B is inverted. And then, A or B is randomly selected with the even probability. It means that we can compare two values by computing average value. If A is larger than B, the state become higher than middle

point. Conversely, the state become lower than middle point when B is larger than A. The stochastic number generators (SNGs) is used to implement those behavior, but it occupies most of its area. For example, an SNG based on a linear feedback shift register (LFSR), which is the most popular digital random number generator, requires 54 gates (NAND-2 equivalent) occupying about 48% of the max function area. We propose an optimized stochastic max (Smax) function shown in Figure 3.5(b) to reduce the SNG overhead. The basic concept of Smax is updating only the difference of the two input SC bitstreams. The difference can be easily calculated with a single XOR gate. In Figure 3.5(b), for example, if A and B are different, the Tanh module (implemented as an FSM) is enabled to update its own state. The input from A to Tanh works as a bipolar-encoded number, so 1 increases the state and 0 decreases it. Thus, if A is larger, Tanh tends to stay on the high state side; if B is larger, it tends to stay on the low state side. The Mux in Figure 3.5(b) selects A when Tanh is at a state higher than half of the highest state. When the enable value is 0 (i.e., A and B are the same), Tanh does not update its state.

Figure 3.5: Stochastic max function. (a) The conventional stochastic max function. (b) Our proposed stochastic max function (SMax).

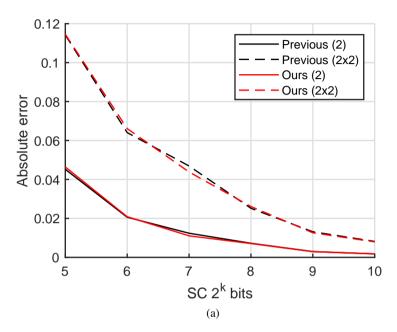

Figure 3.6: Results of the stochastic max functions for 1,000 random bitstream pairs. (a) The conventional stochastic max function. (b) Our proposed stochastic max function (SMax).

Figure 3.6 shows the max function results for both previous work and our proposed hardware. To check the functionality of each logic, we generated 1,000 random bitstream pairs for each point. The proposed hardware do not have any random selection logic, but its result is very similar to the previous work in every point. In addition, Figure 3.7 shows the computation errors of each hardware. Figure 3.6(a) shows mean absolute errors for the previous stochastic hardware. The result of the previous hardware shows irregular errors for every points. This phenomenon is caused by the random selection operation. If the larger value is selected more than the smaller value, error can decreases. However, the max operation error can also increases when the smaller value is selected more. For this reason, the error of the previous hardware depends on the randomly generated selection bitstream. The proposed hardware does not have random selection, so its accuracy only depends on the input bitstreams. Figure 3.6(b) shows the computation errors of the proposed hardware. Compared with the previous work, the proposed hardware shows the smaller errors for the every point. Moreover, the proposed hardware shows more regular error patterns. Thanks to this characteristic,

Figure 3.7: Error of stochastic max functions. (a) The previous work. (b) Our proposed max function.

we can handle the computation errors more easily.