#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

## Ph.D. Dissertation of Engineering

Approximate Computing for Aging Compensation and Energy-efficient Neural Network 근사 컴퓨팅을 이용한 회로 노화 보상과 에너지 효율적인 신경망 구현

August 2020

Graduate School of Seoul National University

Department of Electrical and Computer Engineering

Heesu Kim

# Approximate Computing for Aging Compensation and Energy-efficient Neural Network

지도교수 이 혁 재

이 논문을 공학박사 학위논문으로 제출함 2020년 7월

> 서울대학교 대학원 전기·정보공학부 김희수

김희수의 공학박사 학위논문을 인준함 2020년 7월

| 위  | <sup>원</sup> 장 | 김태환 | (인) |

|----|----------------|-----|-----|

| 부위 | 원장             | 이혁재 | (인) |

| 위  | 원              | 유승주 | (인) |

| 위  | 원              | 류수정 | (인) |

| 위  | 원              | 이진호 | (인) |

#### Abstract

Heesu Kim

Department of Electrical and Computer Engineering

College of Engineering

Seoul National University

Approximate computing reduces the cost (energy and/or latency) of computations by relaxing the correctness (i.e., precision) of computations up to the level, which is dependent on types of applications. Moreover, it can be realized in various hierarchies of computing system design from circuit level to application level.

This dissertation presents the methodologies applying approximate computing across such hierarchies; compensating aging-induced delay in logic circuit by dynamic computation approximation (Chapter 1), designing energy-efficient neural network by combining low-power and low-latency approximate neuron models (Chapter 2), and co-designing in-memory gradient descent module with neural processing unit so as to address a memory bottleneck incurred by memory I/O for high-precision data (Chapter 3).

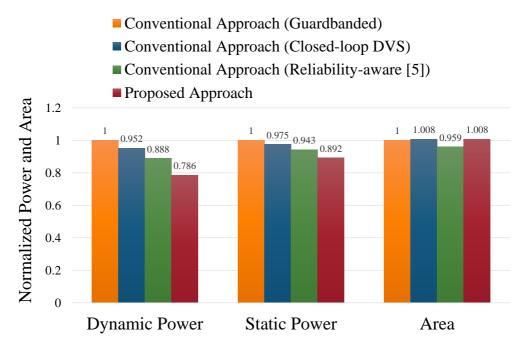

The first chapter of this dissertation presents a novel design methodology to turn the timing violation caused by aging into computation approximation error without the reliability guardband or increasing the supply voltage. It can be realized by accurately monitoring the critical path delay at run-time. The proposal is evaluated at two levels: RTL component level and system level. The experimental results at the RTL component level show a significant improvement in terms of (normalized) mean squared error caused by the

timing violation and, at the system level, show that the proposed approach successfully transforms the aging-induced timing violation errors into much less harmful computation approximation errors, therefore it recovers image quality up to perceptually acceptable levels. It reduces the dynamic and static power consumption by 21.45% and 10.78%, respectively, with 0.8% area overhead compared to the conventional approach.

The second chapter of this dissertation presents an energy-efficient neural network consisting of alternative neuron models; Stochastic-Computing (SC) and Spiking (SP) neuron models. SC has been adopted in various fields to improve the power efficiency of systems by performing arithmetic computations stochastically, which approximates binary computation in conventional computing systems. Moreover, a recent work showed that deep neural network (DNN) can be implemented in the manner of stochastic computing and it greatly reduces power consumption. However, Stochastic DNN (SC-DNN) suffers from problem of high latency as it processes only a bit per cycle. To address such problem, it is proposed to adopt Spiking DNN (SP-DNN) as an input interface for SC-DNN since SP effectively processes more bits per cycle than SC-DNN. Moreover, this chapter resolves the encoding mismatch problem, between two different neuron models, without hardware cost by compensating the encoding mismatch with synapse weight calibration. A resultant hybrid DNN (SPSC-DNN) consists of SP-DNN as bottom layers and SC-DNN as top layers. Exploiting the reduced latency from SP-DNN and low-power consumption from SC-DNN, the proposed SPSC-DNN achieves improved energyefficiency with lower error-rate compared to SC-DNN and SP-DNN in same network configuration.

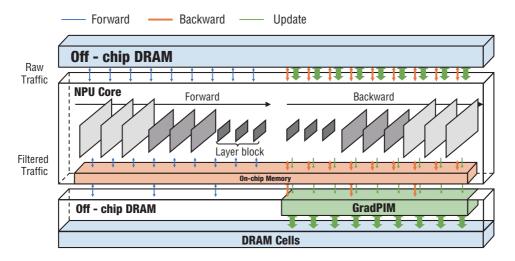

The third chapter of this dissertation proposes GradPim architecture,

which accelerates the parameter updates by in-memory processing which is co-

designed with 8-bit floating-point training in Neural Processing Unit (NPU)

for deep neural networks. By keeping the high precision processing algorithms

in memory, such as the parameter update incorporating high-precision weights

in its computation, the GradPim architecture can achieve high computational

efficiency using 8-bit floating point in NPU and also gain power efficiency by

eliminating massive high-precision data transfers between NPU and off-chip

memory. A simple extension of DDR4 SDRAM utilizing bank-group paral-

lelism makes the operation designs in processing-in-memory (PIM) module

efficient in terms of hardware cost and performance. The experimental results

show that the proposed architecture can improve the performance of the pa-

rameter update phase in the training by up to 40% and greatly reduce the

memory bandwidth requirement while posing only a minimal amount of over-

head to the protocol and the DRAM area.

Keywords: approximate computing, circuit aging, stochastic computing, spik-

ing neural network, in-memory, mixed-precision, neural processing unit

**Student Number**: 2015-20917

iii

# Contents

| Abstra  | act     |                                                    | i   |

|---------|---------|----------------------------------------------------|-----|

| List of | Figur   | es                                                 | vii |

| List of | Table   | $\mathbf{s}$                                       | x   |

| Chapt   | er 1: [ | Dynamic Computation Approximation for Aging        |     |

|         | C       | Compensation                                       | 1   |

| 1.1     | Introd  | luction                                            | 1   |

|         | 1.1.1   | Chip Reliability                                   | 1   |

|         | 1.1.2   | Reliability Guardband                              | 2   |

|         | 1.1.3   | Approximate Computing in Logic Circuits            | 2   |

|         | 1.1.4   | Computation approximation for Aging Compensation . | 3   |

|         | 1.1.5   | Motivational Case Study                            | 4   |

| 1.2     | Previo  | ous Work                                           | 5   |

|         | 1.2.1   | Aging-induced Delay                                | 5   |

|         | 1.2.2   | Delay-Configurable Circuits                        | 6   |

| 1.3     | Propo   | osed System                                        | 8   |

|         | 1.3.1   | Overview of the Proposed System                    | 8   |

|         | 1.3.2   | Proposed Adder                                     | 9   |

|         | 1.3.3   | Proposed Multiplier                                | 11  |

|         | 1.3.4   | Proposed Monitoring Circuit                        | 16  |

|         | 1.3.5   | Aging Compensation Scheme                          | 19  |

| 1.4   | Design         | n Methodology                                                | 20        |

|-------|----------------|--------------------------------------------------------------|-----------|

| 1.5   | 1.5 Evaluation |                                                              | 24        |

|       | 1.5.1          | Experimental setup                                           | 24        |

|       | 1.5.2          | RTL component level – Adder/Multiplier $\dots$               | 27        |

|       | 1.5.3          | RTL component level – Monitoring circuit                     | 30        |

|       | 1.5.4          | System level                                                 | 31        |

| 1.6   | Summ           | nary                                                         | 38        |

| Chapt | er 2: E        | Energy-Efficient Neural Network by Combining Ap-             |           |

|       | p              | roximate Neuron Models                                       | 40        |

| 2.1   | Introd         | luction                                                      | 40        |

|       | 2.1.1          | Deep Neural Network (DNN)                                    | 40        |

|       | 2.1.2          | Low-power designs for DNN                                    | 41        |

|       | 2.1.3          | Stochastic-Computing Deep Neural Network                     | 41        |

|       | 2.1.4          | Spiking Deep Neural Network                                  | 43        |

| 2.2   | Hybri          | d of Stochastic and Spiking DNNs                             | 44        |

|       | 2.2.1          | Stochastic-Computing vs Spiking Deep Neural Network          | 44        |

|       | 2.2.2          | Combining Spiking Layers and Stochastic Layers $\ .\ .\ .$ . | 46        |

|       | 2.2.3          | Encoding Mismatch                                            | 47        |

| 2.3   | Evalu          | ation                                                        | 49        |

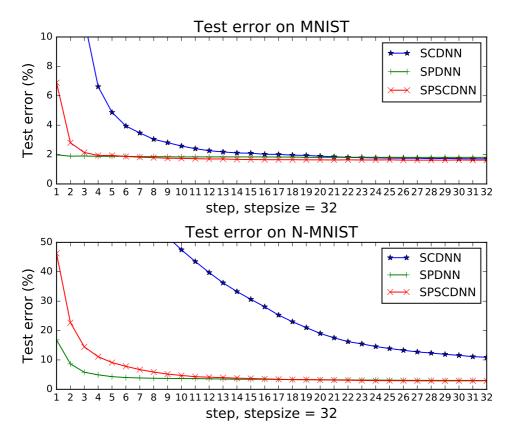

|       | 2.3.1          | Latency and Test Error                                       | 49        |

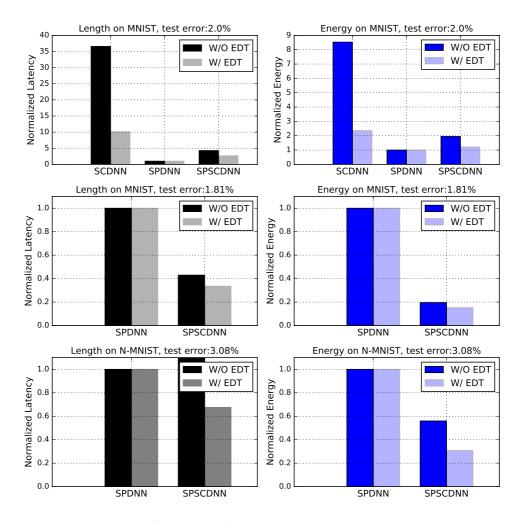

|       | 2.3.2          | Energy Efficiency                                            | 51        |

| 2.4   | Summ           | nary                                                         | 54        |

| Chapt | er 3: C        | GradPIM: In-memory Gradient Descent in Mixed-                |           |

|       | F              | Precision DNN Training                                       | <b>55</b> |

| 3.1   | Introd         | luction                                                      | 55        |

|       | 3.1.1          | Neural Processing Unit                                       | 55        |

|       | 3.1.2          | Mixed-precision Training                                     | 56        |

|       | 3.1.3          | Mixed-precision Training with In-memory Gradient De-         |           |

|       |                | scent                                                        | 57        |

|         | 3.1.4                            | DNN Parameter Update Algorithms                     | 59  |

|---------|----------------------------------|-----------------------------------------------------|-----|

|         | 3.1.5                            | Modern DRAM Architecture                            | 61  |

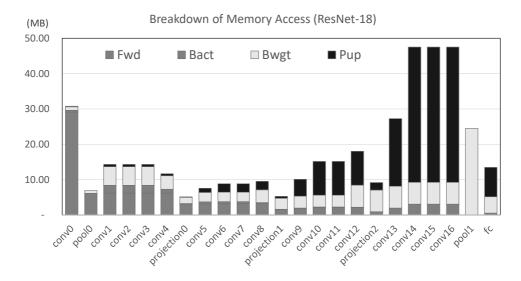

|         | 3.1.6                            | Motivation                                          | 63  |

| 3.2     | Previo                           | ous Work                                            | 65  |

|         | 3.2.1                            | Processing-In-Memory                                | 65  |

|         | 3.2.2                            | Co-design Neural Processing Unit and Processing-In- |     |

|         |                                  | Memory                                              | 66  |

|         | 3.2.3                            | Low-precision Computation in NPU                    | 67  |

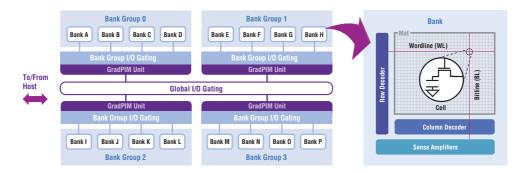

| 3.3     | $\operatorname{Grad} \mathbf{F}$ | PIM                                                 | 68  |

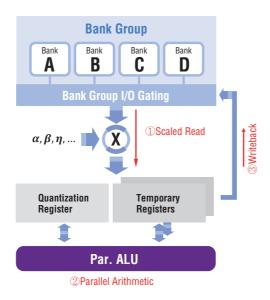

|         | 3.3.1                            | GradPIM Architecture                                | 68  |

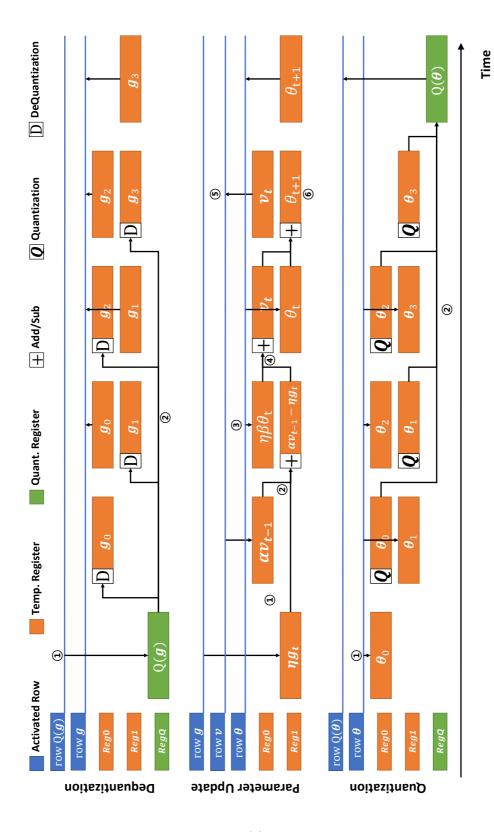

|         | 3.3.2                            | GradPIM Operations                                  | 69  |

|         | 3.3.3                            | Timing Considerations                               | 70  |

|         | 3.3.4                            | Update Phase Procedure                              | 73  |

|         | 3.3.5                            | Commanding GradPIM                                  | 75  |

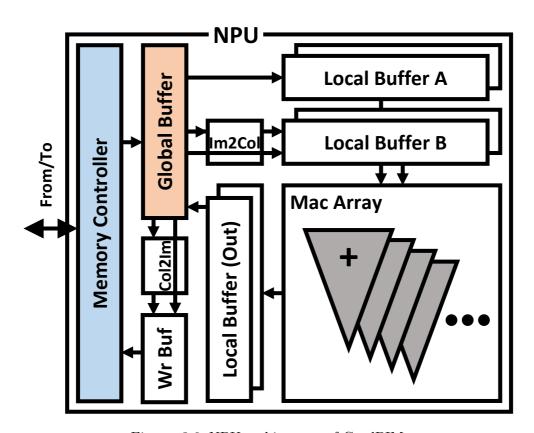

| 3.4     | NPU                              | Co-design with GradPIM                              | 76  |

|         | 3.4.1                            | NPU Architecture                                    | 76  |

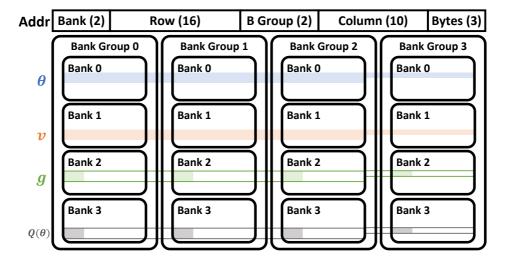

|         | 3.4.2                            | Data Placement                                      | 79  |

| 3.5     | Evalua                           | ation                                               | 82  |

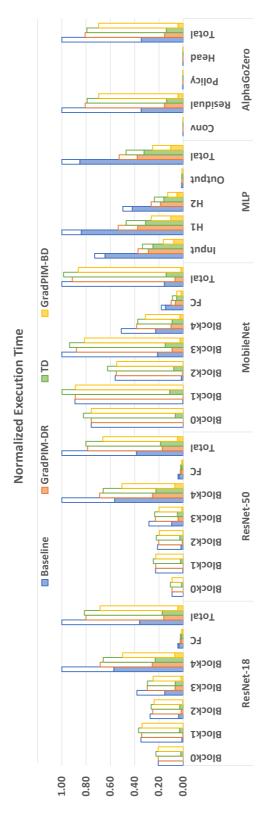

|         | 3.5.1                            | Evaluation Methodology                              | 82  |

|         | 3.5.2                            | Experimental Results                                | 83  |

|         | 3.5.3                            | Sensitivity Analysis                                | 88  |

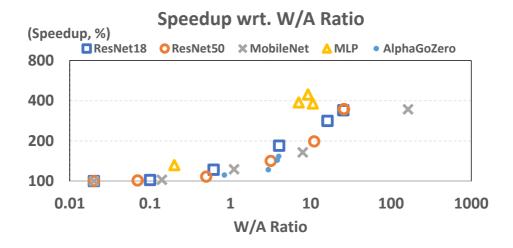

|         | 3.5.4                            | Layer Characterizations                             | 90  |

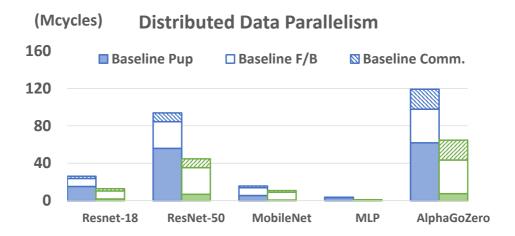

|         | 3.5.5                            | Distributed Data Parallelism                        | 90  |

| 3.6     | Summ                             | nary                                                | 92  |

|         | 3.6.1                            | Discussion                                          | 92  |

| Bibliog | graphy                           |                                                     | 113 |

| 요약      |                                  |                                                     | 114 |

# List of Figures

| 1.1 | Impact of the aging-induced delay on an image processing ap-     |    |

|-----|------------------------------------------------------------------|----|

|     | plication                                                        | 4  |

| 1.2 | Simplified block diagram of the proposed system                  | 8  |

| 1.3 | Proposed adders (a) masking type (b) cutting type                | 10 |

| 1.4 | 4-bit (a) conventional and (b) proposed CSA array multiplier.    |    |

|     | Dashed arrows present critical paths and those in (b) present    |    |

|     | them before and after the truncation of multiplicand operand.    |    |

|     | The red-colored operands are position-changed operands (par-     |    |

|     | tial products) in the proposed multiplier. The bottom of (b)     |    |

|     | shows detailed changes of the critical paths                     | 12 |

| 1.5 | Structure of the proposed monitoring circuits; (a) generic and   |    |

|     | (b) dedicated. Delay elements used in each monitoring circuit    |    |

|     | are presented at bottom of each. Note that cells for generating  |    |

|     | partial products and switch logic are omitted for clarity        | 15 |

| 1.6 | Aging compensation scheme with approximation                     | 19 |

| 1.7 | Design methodology of the proposed system                        | 20 |

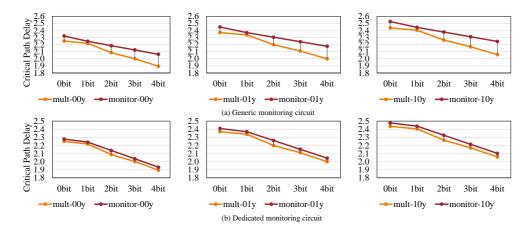

| 1.8 | Critical path delays of the proposed multiplier and two types of |    |

|     | monitoring circuits: (a) generic and (b) dedicated. The shorter  |    |

|     | distance between the critical path delays means the lower delay  |    |

|     | mismatch and the better monitoring performance                   | 29 |

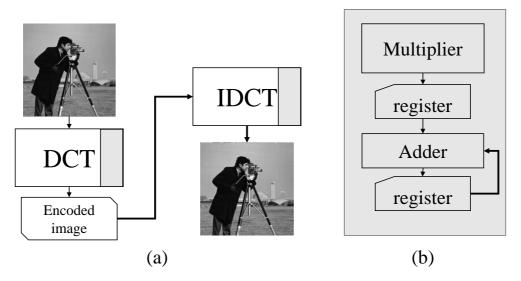

| 1.9 | (a) DCT/IDCT codec blocks and (b) matrix multiplication unit     |    |

|     | in DCT and IDCT blocks                                           | 31 |

| 1.10 | Evaluation of aging compensation of proposed adder with ap-                  |    |

|------|------------------------------------------------------------------------------|----|

|      | proximation in image processing application. The value under                 |    |

|      | the images are PSNR                                                          | 32 |

| 1.11 | Evaluation of aging compensation of proposed multiplier (and                 |    |

|      | proposed adder) with approximation in image processing appli-                |    |

|      | cation. The value under the images are PSNR. $\ \ldots \ \ldots \ \ldots$    | 33 |

| 1.12 | Power and area comparison of DCT/IDCT codec block for con-                   |    |

|      | ventional and proposed approaches. The proposed approach in-                 |    |

|      | cludes the proposed adder and multiplier                                     | 36 |

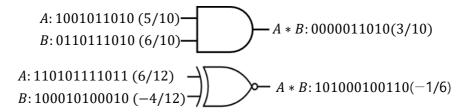

| 2.1  | Example of stochastic number and their multiplication. AND                   |    |

|      | and XNOR gates are used for unipolar and bipolar encoding,                   |    |

|      | respectively                                                                 | 42 |

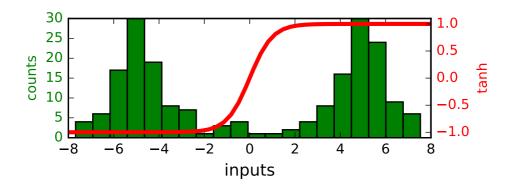

| 2.2  | The histogram shows the distribution of input values to the                  |    |

|      | activation function in the first layer of SC-DNN for a test image.           |    |

|      | The activation function of $tanh$ is drawn on top of the histogram           |    |

|      | to show that most of the inputs exist in the saturation regions              |    |

|      | of the function                                                              | 45 |

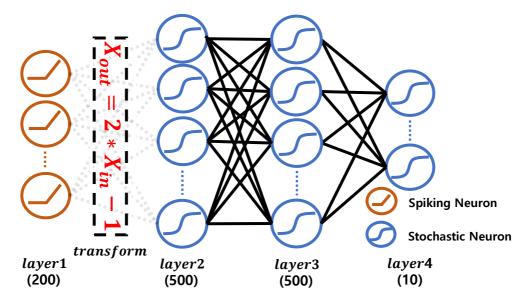

| 2.3  | Topology of SPSC-DNN. The transform layer is placed to emu-                  |    |

|      | late encoding mismatch between the spiking neuron and stochas-               |    |

|      | tic neuron in training phase. SC-DNN and SP-DNN also have                    |    |

|      | the same topology, except for different type of neuron. Each                 |    |

|      | layer has 200-500-500-10 neurons, respectively. $\ \ldots \ \ldots \ \ldots$ | 48 |

| 2.4  | X-axis values are in number of steps; each step corresponds to $32$          |    |

|      | bits in the input bitstream (thus the total length of a bitstream            |    |

|      | is $32 \times 32 = 1024$ bits)                                               | 50 |

| 2.5  | Latency (i.e., length) and energy consumption in SC-DNN, SP-            |    |

|------|-------------------------------------------------------------------------|----|

|      | DNN, and SPSC-DNN for different dataset and target test er-             |    |

|      | ror. The effect of EDT is also evaluated. Since SC-DNN cannot           |    |

|      | reach the target test error for $1.81\%$ on MNIST and $3.08\%$ on       |    |

|      | N-MNIST, it is not included in the graphs on the second and             |    |

|      | third rows.                                                             | 53 |

| 3.1  | Mixed-precision training with GradPIM                                   | 58 |

| 3.2  | Modern DDR4 SDRAM internal architecture                                 | 61 |

| 3.3  | Breakdown of the memory access of ResNet-18 layers with mixed $$        |    |

|      | precision training                                                      | 64 |

| 3.4  | DRAM internal architecture of GradPIM unit                              | 68 |

| 3.5  | Example procedure for quantization/dequantization and mo-               |    |

|      | mentum SGD algorithm with GradPIM                                       | 72 |

| 3.6  | NPU architecture of GradPIM                                             | 77 |

| 3.7  | Address mapping and data placement scheme for $\operatorname{GradPIM}.$ | 80 |

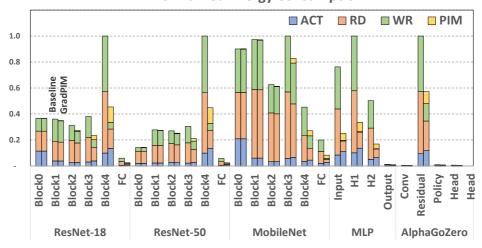

| 3.8  | Normalized execution time of each layer on various networks             |    |

|      | using GradPIM. The filled parts of the bars represent parameter         |    |

|      | update phase, and the empty parts of the bars represent the             |    |

|      | forward/backward phase                                                  | 84 |

| 3.9  | Energy consumption of various networks using GradPIM                    | 86 |

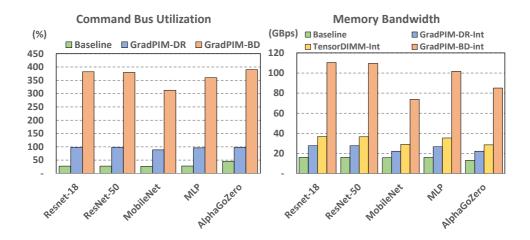

| 3.10 | Command bus utilization (left) and the external/internal mem-           |    |

|      | ory bandwidth consumption using GradPIM (right)                         | 87 |

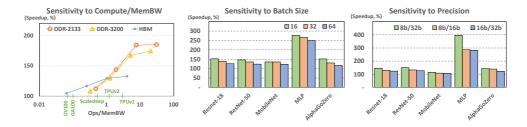

| 3.11 | Sensitivity to compute-bandwidth ratio (left), minibatch size           |    |

|      | (mid), and minibatch size (right)                                       | 88 |

| 3.12 | Layer characterizations                                                 | 90 |

| 3 13 | Projections to distributed training                                     | 91 |

## List of Tables

| 1.1 | Comparison of 32-bit Ripple Carry Adder and Proposed Adder     | 26 |  |  |  |

|-----|----------------------------------------------------------------|----|--|--|--|

| 1.2 | 1.2 Comparison of 16-bit Carry Save Adder Array Multiplier and |    |  |  |  |

|     | Proposed Multiplier                                            | 28 |  |  |  |

| 2.1 | Power (mW) Measured on Stochastic and Spiking Neuron of        |    |  |  |  |

|     | Each Layer Where The Number of Inputs of The Neurons in        |    |  |  |  |

|     | The 1st, 2nd, 3rd, and 4th Layers is 784, 200, 500, and 500,   |    |  |  |  |

|     | Respectively                                                   | 53 |  |  |  |

| 3.1 | Truth Table for GradPIM Commands                               | 75 |  |  |  |

| 3.2 | NPU Synthesis Results                                          | 82 |  |  |  |

| 3.3 | DRAM parameters                                                | 83 |  |  |  |

| 3.4 | GradPIM Layout Results                                         | 85 |  |  |  |

## Chapter 1

# Dynamic Computation Approximation for Aging Compensation

#### 1.1 Introduction

#### 1.1.1 Chip Reliability

Recently the chip reliability problem is getting much worse as the process technology scales down. Among others, BTI (Bias Temperature Instability) is a key reliability problem that degrades the chip performance by increasing the threshold voltage and decreasing the drain current [1]. This incurs chip slowdown, and after all, generates timing violation errors. In addition, metal-oxide thin-film transistors suffer fast aging and thus much larger timing variations in low supply voltage systems. Therefore, aging is a more serious problem in low power systems such as Internet-of-Things (IoT) or biomedical devices.

#### 1.1.2 Reliability Guardband

The conventional approach to compensating for this aging-induced timing violation error is assigning a reliability guardband to supply voltage [2]. However, there are many problems in applying this approach to low power design. First of all, it is a too pessimistic approach since it should assign a relatively large guardband that can compensate for the chip slowdown after many years (say 10 years) of aging. This approach wastes extra power/area that is unnecessary during the first 10-years. Second, it is very difficult to determine an accurate guardband at design-time because the chip slowdown by aging depends on operating conditions including supply voltage, temperature, and application scenario. That is, the guardband should be determined by considering the worst-case operating conditions; it is very risky to determine the guardband by considering the statistical or balance conditions because it cannot ensure the normal chip operation in the worst-case conditions. Third, increasing the supply voltage to secure the guardband makes the aging accelerate.

#### 1.1.3 Approximate Computing in Logic Circuits

Instead of increasing supply voltage and/or using faster (but larger) circuit as in the conventional approach while maintaining the computation accuracy, adopting the concept of approximate computing can be a more efficient solution in applications such as image/video processing, where the output quality is less sensitive to small errors. Under the assumption that the quality degradation by the approximation is not large, approximate computing can effectively increase performance and/or reduce power consumption. Therefore, simplified or approximate arithmetic (logic) circuits (adders, multipliers) are widely used to generate acceptable quality results in signal processing applications,

especially in image/video processing applications [3, 4, 5, 6].

#### 1.1.4 Computation approximation for Aging Compensation

In this chapter, an approach that enables the system to adapt to aging dynamically is presented. Thus, it does not need to add the pessimistic reliability guardband at design-time. Instead, it monitors the aging-induced delay at run-time and compensate for the increased delay by curtailing the critical path in a way of minimizing the accuracy loss due to the computation approximation. Therefore, it is essential to measure the chip slowdown due to aging and compensate for it adequately at run-time. For the implementation, the chip performance is measured periodically [7] using on-chip monitor since the aging is a very slow process. Ideally, this approach does not need to add any reliability guardbands. Practically, however, a small guardband should be secured to compensate the delay mismatch between the monitoring circuit and the actual critical path delay of the target block. The approach also requires reconfigurable circuits that can adjust the level of approximation. A design methodology is presented to implement reconfigurable adder and multiplier that replace conventional adder and multiplier. Since they are the fundamental arithmetic building blocks for more complex arithmetic circuits, arithmetic circuits consisting of them also can be implemented following such design methodology. Note that all aging-induced delays in the system cannot be compensated by computation approximation. For example, timing errors in control logic cannot be translated to computation error. For those kinds of logic, it should be handled by other means such as employing reliable margin, transistor upsizing, or other forms of redundancy.

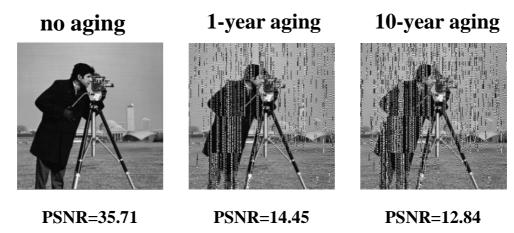

Figure 1.1: Impact of the aging-induced delay on an image processing application.

#### 1.1.5 Motivational Case Study

The main issue in this case study is whether or not a reliability guardband is essentially required in every circuit design. Conventionally, even in error-tolerant circuits, the guardband is indispensably required to gain reasonable outputs. To demonstrate this, the proposed approach that compensates aging-induced delay dynamically is applied to a image processing system that performs Discrete Cosine Transform (DCT) and Inverse Discrete Cosine Transform (IDCT). Detailed setup is described in subsection 1.5.1.

To simulate aging effect of circuits, a degradation-aware library (standard cell libraries), which has been recently proposed and made publicly available [5] is used. The library is compatible with existing EDA tool flows like Synopsys and hence one can directly use them to perform static timing analysis of a circuit netlist without requiring any modifications. In practice, the library contains the delay information of standard cells under the effect (i.e., BTI) that aging has on the electrical characteristics of nMOS and pMOS transistors (e.g., threshold voltage and carrier mobility). Note that even though the

degradation-aware library [5] only models BTI, the proposed approach is agnostic to any type of transistor aging (i.e., BTI or HCI) since it just measures aging-induced delay, then compensates the increased delay, regardless of its source. In practice, both of BTI and HCI can be modeled jointly during the cell library characterization [8]. In this work, I focus on the worst-case aging estimation provided by [5] in which a continuous DC stress is assumed (i.e., 100% duty cycle) in order to ensure reliability for the entire projected lifetime (10 years). Therefore, the recovery mechanism of BTI that depends on the running workload is not considered to provide upper boundary of aging.

As shown in Figure 1.1, removing the guardband in the circuit design results in a significant quality drop on an image when the circuit first encodes the image and then decodes it. In such a chain of circuits, errors are increasingly accumulated. The errors first occur in the encoder and then they are propagated to the decoder which leads to a larger impact on the quality of the final output image. As process technology advances, this problem becomes worse and worse because the aging-induced delay by BTI and HCI (Hot Carrier Injection) increases [9].

#### 1.2 Previous Work

#### 1.2.1 Aging-induced Delay

Many approaches have been studied to avoid aging-induced timing violation errors. The conventional approach to compensate for the errors is assigning an additional reliability guardband to supply voltage (or to slack of the critical path) [2]. However, it is too pessimistic and it is very difficult to determine an accurate guardband at design-time. In [5], the circuits are optimized

against aging through logic synthesis with degradation-aware cell libraries. It enables the optimization process to select cells with most suitable input slew and output load capacitance for each set of operating conditions, considering aging effects. The work in [10] quantifies the impact of aging-induced errors and approximation errors on quality loss when the guardband is removed. It replaces the guardband with an equivalent reduction of precision in approximate computing applications. The aging effects are characterized and applied at design-time. However, such design-time approaches naturally result in an over-design. A more aggressive optimization can be done by run-time measurement of the chip slowdown due to aging and compensation. There is a technique for variation-resilient design that allow timing violation errors and manage the design reliability dynamically [11]. For measuring the chip slowdown, many on-chip aging monitors are presented [12, 13, 14, 15]. However, all these approaches raise the operation voltage to suppress the errors for accurate computing.

#### 1.2.2 Delay-Configurable Circuits

Approximate computing [4] is a concept to trade-off computation accuracy for speed (i.e., delay) or energy, thus it can be exploited to alleviate timing violation errors including those incurred by the aging-induced delay [10]. Especially, approximate arithmetic circuits such as adders and multipliers have been widely studied. The approximate circuits can be divided into two categories: statically configurable and dynamically configurable circuits. The statically configurable circuits [16, 17, 18, 19, 20] have been proposed, and they have configuration parameters which enables the trade-off between the computation precision and the low energy consumption by adjusting approximation

level. Some works [18, 19] extensively explore design space for finding an optimal point on the trade-off curve. [18] proposes an approximate adder having fine-grain configuration parameters, providing high flexibility in design space and the trade-off curve. [19] separates the higher significant bits and the lower significant bits, and processes them differently using some design alternatives, which they proposed to avoid errors in the higher significant bits, for better quality-energy trade-off. However, none of these approaches handle run-time effects such as the aging-induced delay since they need re-design or re-synthesis at design-time to change the configuration.

On the other hand, dynamically configurable circuits [21, 22, 23, 24, 25, 26] can be configured to various approximation levels at run-time without re-synthesis, thus being able to handle the run-time effects. The accuracy-configurable adder proposed in [21] changes the accuracy of results by selecting the operation mode at run-time. It basically outputs approximate results by cutting propagation path, and if needed, it corrects the errors for accurate results with multiple overlapping sub-adders. The gracefully-degrading adder in [22] is comprised of fixed structured multiple sub-adder units with selectable length for carry prediction bits, so it can satisfy a computation quality requirement varying at run-time. [25, 26] propose dynamically configurable multipliers that decrease power consumption by disabling switching activities of inactive sections resulting from the reduced input bit-width determined at run-time.

Although those circuits are configurable at run-time, they do not consider timing violation errors incurred by run-time effects, but primarily configure the approximate circuit to achieve energy reductions with acceptable accuracy degradation. Several prior work have specifically targeted timing ef-

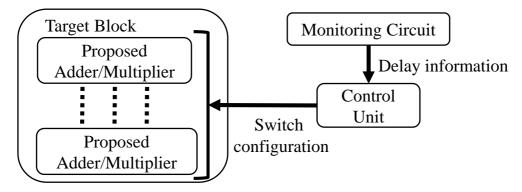

Figure 1.2: Simplified block diagram of the proposed system.

fects [6, 23, 24]. The dynamic voltage accuracy scaling approach proposed in [23, 24] achieves dynamic voltage overscaling by bit-width reduction under timing constraints. [6] proposes quality and delay configurable circuits to replace the temperature guardband at run-time. Neither of these approaches target aging, however.

This work is the first to directly measure and compensate for the aging-induced delay of basic arithmetic circuits such as adders and multipliers at run-time. The proposed approximate circuits truncate its least significant bits (LSBs) to reduce the critical path delay using the measured delay information at run-time with only a couple of gates overhead.

### 1.3 Proposed System

#### 1.3.1 Overview of the Proposed System

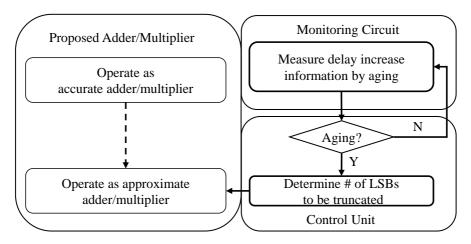

Figure 1.2 is the simplified block diagram of the proposed system. It comprises the monitoring circuit, control unit, and the target block. The target block implements a signal processing application such as an image/video codec. it is considered to use the proposed adder/multiplier in the target block. The mon-

itoring circuit outputs the delay information of the adders/multipliers in the target block under the current operating condition. Then, the control unit can reduce the critical path delay of the adders/multipliers by truncating LSBs according to the measured aging-induced delay information. It is performed using the switches of the adders/multipliers to cut-off their carry propagation paths. The overhead of the control unit is not too large because it just translates the 5-bit output of the monitoring circuit into the 4-bit configuration input in a way of counting. As mentioned in the previous section, the proposed adder/multipliers basically operates as an accurate circuit, but becomes an approximate one if some aging is detected by the monitoring circuit. Detailed explanations of each component in Figure 1.2 are given in the following subsections.

#### 1.3.2 Proposed Adder

The proposed adder structure is based on ripple carry adder, which is the most cost/power-efficient adder among conventional adders. It shows the lowest power consumption and the best power-delay product metric, compared to other conventional accurate adders [16]. So, it has been widely chosen for the low power design. However, in a conventional ripple carry adder, errors in the most significant part (called MSP errors) are generated when the carry signal cannot be propagated to the MSP positions during one clock period due to the aging-induced delay. Such MSP errors are much more critical than errors in the least significant part (called LSP errors), especially when the sign bit in the 2's complement representation is involved in the errors.

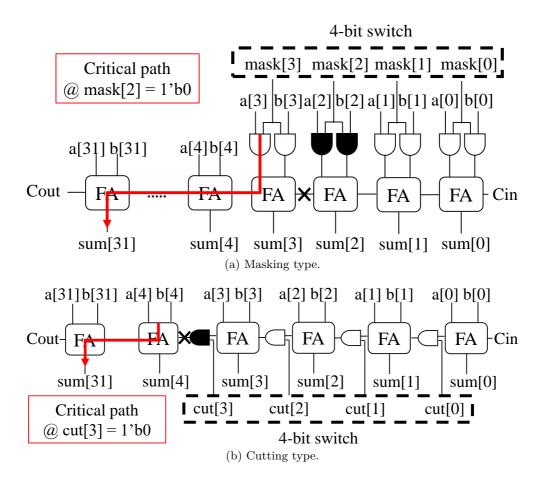

To resolve this problem, two types of adders—masking and cutting— are proposed to prevent MSP errors. Figure 1.3 shows the structure of the two

Figure 1.3: Proposed adders (a) masking type (b) cutting type .

proposed adders. The difference from the conventional adder is that the proposed adders have a 4-bit switch to cut-off the carry propagation path. These circuits reduce the critical path delay according to the configuration input value from the control unit. The masking type adder truncates some LSBs of the adder input to cut-off the carry propagation path, while the cutting type adder directly blocks the carry propagation from some LSBs. (those two types of gating are named to "truncation" afterwards.) For example, in case of masking type adder, when setting the configuration input to "mask[3:0] = 4'b1011", the carry-out (CO) of the third full adder (FA) is always zero. Then the critical path becomes shorter; the new critical path is from a[3] to sum[31] (red arrow in Figure 1.3a). Also, in case of cutting type adder, when setting the configuration input to "cut[3:0] = 4'b0111", the carry out of the fourth FA is always gated not to propagate it into the next (fifth) FA. They are configured dynamically at run-time, only when the aging-induced delay is detected by the monitoring circuit. The blocking of carry propagation in these examples may generate many LSP errors instead of a few critical MSP errors.

In Figure 1.3, we can see only the 4-bit switch to cut-off the carry propagation path. However, the optimal number of bits depends on the maximum amounts of the delay increase due to aging, which in turn depends on operating conditions and process technology. Detailed explanations determining it are given in Section 1.4.

#### 1.3.3 Proposed Multiplier

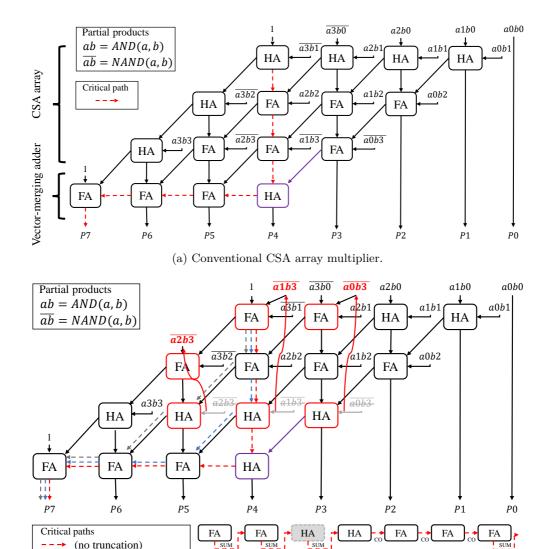

The proposed multiplier structure is based on Baugh-Wooley multiplier [27] which supports unsigned and signed parallel multiplication and I call it Carry-Save-Adder (CSA) array multiplier (see Figure 1.4a) in this chapter because

(b) Proposed CSA array multiplier.

FA FA

HA

HA

FA

FΑ

FΑ

(a0 = 0, 1-bit trunc.)

(a1, a0 = 0, 2-bit trunc.)

Figure 1.4: 4-bit (a) conventional and (b) proposed CSA array multiplier. Dashed arrows present critical paths and those in (b) present them before and after the truncation of multiplicand operand. The red-colored operands are position-changed operands (partial products) in the proposed multiplier. The bottom of (b) shows detailed changes of the critical paths.

the main part of the multiplier is a CSA array, which has array structure with full adders (FAs) and half adders (HAs). The CSA array performs the partial product additions propagating values from the upper rows to bottom rows through diagonal arrows (carry-out) and vertical arrows (sum). The other part of the multiplier is the vector-merging adder, which performs the carry propagations to transform the outputs of the CSA array into a binary form. I consider this to be a representative multiplier, since the CSA array multiplier is a base structure of many parallel and power-delay optimized multipliers including [28] and [29], which employ [30] and/or Wallace-tree algorithm [31] along with the CSA array multiplier structure.

In order to cut the critical path by truncating the LSBs, two types of truncation, masking and cutting, can be considered as for the adder. However, masking is selected for the proposed multiplier, because there are many wires in between rows of CSA array making delay paths rather complex, thus requiring many AND cells to cut them if cutting type is chosen.

When applying the masking truncation, truncation happens in either multiplicand (ai's in Figure 1.4) or multiplier operand (bi's in Figure 1.4). If truncation occurs in the LSBs of multiplier operand, it eliminates value propagation delay in the CSA array by forcing the outputs (carry-out and sum) of the corresponding FAs/HAs to be fixed since the truncation fixes the inputs of the FAs/HAs to either "0" or "1". For example, if 2 bits of LSBs of multiplier operand (b0 = 0, b1 = 0) is truncated as in Figure 1.4a, all outputs (carry-out and sum) of the FAs/HAs of the first row in the CSA array are fixed to either "0" or "1" depending on their inputs fixed for b0 or b1. Thus, the delay path through the first row is not on the critical path now. In the same way, as the number of truncated bits increases, the critical path delay decreases.

On the other hand, if the LSBs of a multiplicand operand is truncated, the partial products including sign bits (a3 or b3) in the conventional CSA array multiplier (Figure 1.4a) hinders the critical path reduction. For example, if a0 is truncated to be "0", then a0b3 is always "1", and thus the purple arrow in Figure 1.4a can be either "0" or "1" according to the input of vertical arrow (the input of diagonal arrow is always "0" due to a0 = 0). Therefore, the critical path delay is not affected by the truncation. If fixing the value of the purple arrow to "0" happens, the critical path delay can be shortened since the carry-out of the purple HA is fixed to "0". To achieve this, I change the position of operand-bits from a lower row to higher rows as represented by solid red-arrows and red operand-bits in Figure 1.4b, and exchange the FA and HA cells according to the position changes. Note that these changes do not alter the computation results. Now, if 1-bit in LSP is truncated (a0 = 0), the purple arrow is fixed to "0". Hence the critical path is changed to the bluedashed arrows from the red-dashed arrows as depicted in Figure 1.4b. For 2bit truncation (a0 = 0, a1 = 0), the critical path becomes gray-dashed arrows. Note also that this position changes of operands do not cost any overhead, since the number of FAs and HAs is unchanged.

I choose to truncate multiplicand operand, because it can reduce the critical path delay starting from 1-bit truncation. On the other hand, if I choose to truncate multiplier operand, the minimum number of LSBs that can reduce the critical path delay is 2 bits since 1-bit truncation cannot fix the outputs of every FA/HA on the first row. Therefore, truncating the multiplicand operand shows better efficiency in terms of the trade-off between reduction of critical path delay and errors of computation approximation. It also enables to handle the initial stage of aging with 1-bit truncation.

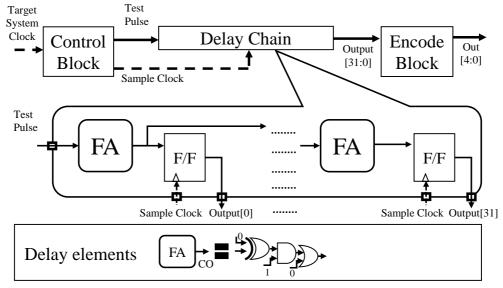

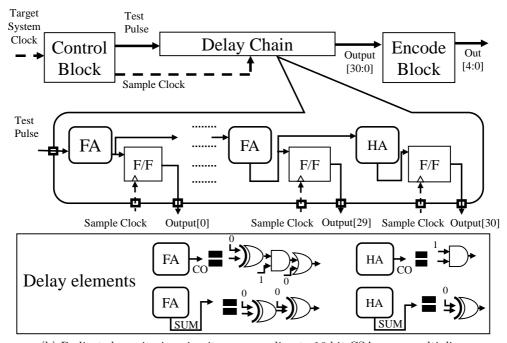

(a) Generic monitoring circuit corresponding to 32-bit ripple carry adder.

(b) Dedicated monitoring circuit corresponding to 16-bit CSA array multiplier.

Figure 1.5: Structure of the proposed monitoring circuits; (a) generic and (b) dedicated. Delay elements used in each monitoring circuit are presented at bottom of each. Note that cells for generating partial products and switch logic are omitted for clarity.

#### 1.3.4 Proposed Monitoring Circuit

The monitoring circuit is a key component to determine the quality and effectiveness of the proposed system. More accurate aging-induced delay measurement makes the quality degrade more gracefully with approximation. On the other hand, the inaccurate measurement might bring excessive quality degradation from LSP errors or still incur MSP errors, in spite of using the run-time monitoring system. The dynamic approach gives better quality results than static approach under the assumption that the sensor/monitor gives accurate delay information.

Monitoring circuits is designed to be used for the proposed adder/multiplier based on the state-of-the-art monitoring circuit [7]. Figure 1.5 shows the detailed structure of the monitoring circuits designed for the 32-bit adder and the 16-bit multiplier. Both of them consist of three main blocks: delay chain, control block, and encode block. Delay chain is an array of delay elements, each of which represents an element of the critical path of the target circuits.

The monitoring circuit proposed in [7] is a generic monitoring circuit which uses unit delay elements to measure increased delay. It computes the ratio of the number of delay elements which are not reachable in a clock cycle over the total number of the delay elements. Therefore, it is applicable to any target circuits including the ones proposed here. However, the resolution of delay adjustment can be a problem. In [7], while they control the continuous value (i.e. supply voltage) to adjust the circuit delay, it handles a discrete value, which is the number of truncation bits in target circuits. Therefore, the delay elements should be designed to be aligned with the unit of truncation. This type of monitoring circuit is called as dedicated monitoring circuit. The other parts of the dedicated monitoring circuit except for the comprising delay

elements are equal to the generic monitoring circuit.

The monitoring circuits operate as follows. First, the control block generates a test pulse and sample clock signals by using the target system clock. While the test pulse signal propagates through the delay chain, the sample clock samples it to see how many delay elements are propagated through within one clock period. Then the outputs of the flip-flops (a string of 1's followed by a string of 0's) are encoded to 5-bit delay output information. For example (Figure 1.5a), at the initial year (0-year without the guardband), the output [31:0] is always 32'hffff\_ffff. However, if the input pulse signal cannot propagate through the whole delay chain within one clock period due to the aging-induced delay, it becomes 32'h7fff\_ffff, 32'h3fff\_ffff, 32'h1fff\_ffff or 32'h0fff\_ffff as the amount of delay increases. Based on this output information from the monitoring circuit, the control unit can truncate the LSBs of the target circuit according to the amount of propagation path beyond a clock cycle. Note that some input bits of the delay elements (FAs/HAs) are fixed to either "0" or "1" in order to make them bypass the test pulse.

In the case of the proposed adder, it consists of "FA-CO (FA carry-out)" propagation path only in their critical path, so if FA-CO is chosen as a unit delay element for the monitoring circuit, the dedicated monitoring circuit has a structure of the generic monitoring circuit. Practically, two-input NAND, NOR, XOR cells comprises a delay element and a flip-flop (F/F) is appended to each of the delay element as depicted in Figure 1.5a. As a result, the whole delay chain has completely the same cell composition as the critical path of the proposed adder (i.e., ripple carry adder). That is why the monitoring circuit can measure the aging-induced delay of the adder accurately. The number of delay elements depends on the number of adder bits. In case of the proposed

multiplier, as shown in Figure 1.4, the critical path of CSA array multipliers contains four types of propagation paths that exist in FAs and HAs. They are "FA-SUM" path consisting of two XOR cells, "FA-CO" path consisting of an XOR, an AND, and an OR cells, "HA-SUM" path consisting of one XOR cell, and "HA-CO" path consisting of one AND cell as depicted in Figure 1.5b. Therefore, four types of delay elements corresponding to each propagation path are designed, then they constitute a delay chain by connecting themselves in the reverse order of LSBs truncation. For example, as shown in the bottom right of Figure 1.4b, after the 1-bit truncation, the critical path is shortened as the amount of "HA-SUM" delay (upper shaded delay path) and after the 2-bit truncation, the critical path is further shortened as the amount of "FA-SUM" (bottom shaded delay path). Therefore, "HA-SUM" delay element is placed in the end of the delay chain and a "FA-SUM" delay element in front of the "HA-SUM" delay element as shown in Figure 1.5b. Unlike the adder where the generic and the dedicated monitors have the same structure, the generic and the dedicated monitor of the multiplier have different structures, their performance will be compared in subsection 1.5.3. The number of delay elements on the delay chain depends on multipliers number of operand-bits.

Note that in the delay chains, the delay elements for generating partial products (an AND or a NAND) and switch logic (an AND) are omitted. However, they can be considered by placing equivalent delay elements in the delay chain or using a small guardband.

The monitoring circuit is required to have switching activity similar to that of the target circuits for having closely correlated aging characteristics. However, checking whether aging-induced delay incurs timing violation, involving fetching output values of delay elements into flip-flops, is not required to be

Figure 1.6: Aging compensation scheme with approximation.

performed at all times, because aging is a very slow process with alternating phases of stress and recovery. Also, the delay measured by the monitoring circuit should be calibrated to get pure aging-induced delay independent to the process, voltage, and temperature variations that are also measured by own monitors [32].

#### 1.3.5 Aging Compensation Scheme

Figure 1.6 illustrates the proposed aging compensation scheme using computation approximation. At 0-year (no aging), the proposed adder/multiplier of target block operate as accurate adder/multiplier. At the same time, the monitoring circuit periodically gives the delay information to the control unit. If an aging-induced timing violation error is detected, the control unit determines the number of LSBs to be truncated by the amount of delay increase due to aging. Then the proposed adder/multiplier operate as approximate ones by truncating some LSBs. When the delay by aging further increases, the control unit conpart1/figures the adder/multiplier to truncate more LSBs. This scheme is automatically operated at run-time.

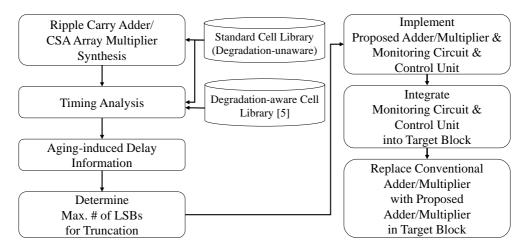

Figure 1.7: Design methodology of the proposed system.

## 1.4 Design Methodology

In order to apply the proposed scheme, it is required to implement the proposed adder/multiplier and monitoring circuit for a given design specification and process technology. The design methodology of the proposed system is shown in Figure 1.7. The flow chart on the left-hand side shows the *design analysis steps* for the proposed system implementation, and the flow chart on the right-hand side shows the *design integration steps* to integrate the proposed circuits into the target block design. It is very easy to plug the proposed methodology into a conventional design flow.

In the design analysis steps, a ripple carry adder and a CSA array multiplier are synthesized as the reference adder/multiplier structure with general standard (degradation-unaware) cell library, which does not consider any aging effects. With static timing analysis, the aging-induced delay is measured by comparing the critical path delay before and after the aging. The critical path delay after aging is analyzed with degradation-aware library [5] as mentioned in subsection 1.1.5. Note that even though the design methodology

requires to develop a degradation-aware library for each technology, it is a one-time effort for each technology and not application-specific. Therefore, it can be reused for any design in the same technology. In addition, during the cell library creation several corners and several operating conditions are typically considered. Therefore, having an extra corner that describes the library behavior after aging would not lead to a significant increase in complexity.

Based on the measured aging-induced delay, the maximum number of LSBs to be truncated for aging compensation can be determined during the expected lifetime. Just one simulation run is enough to determine the maximum number of LSBs (MaxBits) to be truncated during the expected lifetime (10 years) of the target circuit since if a few more bits are added on the simulated MaxBits, it can sufficiently cover the whole range of the truncation. That is because MaxBits is the upper bound of the coarse-grain (bit-wise) truncation and a few more bits (2-3 bits) on the switch logic cost only a few more gates, such as ANDs and NANDs. It is noteworthy that the reference circuits do not have a switch logic, and thus the reference designs have shorter critical path delay than the proposed circuits. However, it also can be sufficiently covered by MaxBits since the switch logic has only a gate cell delay.

Next, in the design integration steps, the monitoring circuit, control unit, and the proposed adder/multiplier are implemented according to the specification determined in the previous steps. Then, the monitoring circuit and the control unit are integrated into the target block. Finally, the conventional adder/multiplier is replaced with the proposed adder/multiplier in the target block.

There are some important guidelines to correlate the delay characteristics between the delay chain of the monitoring circuit and the critical path of the proposed adder/multiplier. As the cell delay is mainly affected by process, voltage, and temperature (PVT), it is very important to make the PVT conditions of the monitoring circuit same as that of the adder/multiplier in the target block. This PVT matching directly relates to the accuracy improvement of the proposed system. The guidelines are; First, the monitoring circuit should share the same supply voltage rail with the adder/multiplier in the target block to correlate them closely in terms of delay characteristics and aging process, both of which are voltage dependent. Second, the monitoring circuit should be placed closely to the target block because the delay variation due to on-chip process variation is too large to be ignored in an advanced process technology and the temperature inside one chip can vary over a range of tens of degrees at the worst-case when either of monitoring circuit or target circuit is located at the hotspot region whereas the other is located at the cool (idle) region. These guidelines are mandatory for better delay correlations between the monitoring circuit and the adder/multiplier in the target block, and thus they should be followed carefully when integrating the monitoring circuit into a chip.

In practice, even when following the guidelines, any remaining PVT mismatches between the monitoring circuit and the adder/multiplier in the target block need to be compensated by employing a small guardband. The PVT mismatches can in general result in mismatches in the calibration for the pure aging-induced delay mentioned in subsection 1.3.4 as well as aging degree of the monitor and target circuits. For the case of temperature, which has the largest effect on delays, assuming a worst-case temperature difference of 2 °C between the monitor and target circuits results in a maximum 1.8% difference in delays [6] and a negligible difference in aging degree over 10 years [33] that

have to be covered by a guardband. In addition, the switching activity differences, when the monitor circuit is shared across the target circuits, also have to be covered by a guardband.

There are several approaches to estimate and bound such margins and guardbands. To estimate PVT mismatches and guardbands, the result of standard intra-chip PVT variation analysis, which is supported by Process Design Kits (PDKs) with analysis tools and statistical information for varying PVT conditions of the underlying technology, can be utilized. The PDKs and statistical information are provided by foundry companies. Given PVT mismatches, degradation-aware cell libraries characterized for different PVT operating points can be used to analyze both the direct delay impact and the indirect impact on aging and aging-induced delays under different PVT conditions of monitor and target circuit. The designer can apply the estimated guardband by adding the worst-case difference in six or three sigma values obtained from the analysis and/or the statistical data. Note that one does not need to analyze all pairs of target and monitoring circuits in a chip. Estimating mismatches and guardbands can be done conservatively to determine the worst-case scenario over a chip (if necessary, a domain). Finally, to further contain mismatches and required guardbands, one can implement the sensor (i.e., monitor) using standard cells that are the most susceptible to aging. In such a case, the reading and predictions from the sensor will be conservative.

From the hardware overhead point of view, this aging compensation system does not generate a large area overhead. Compared to the conventional ripple carry adder and CSA array multiplier, the overhead of the proposed adder/multiplier can be ignored because a couple of AND and NAND cells are added to cut-off the carry propagation path. The monitoring circuit and

the control unit are very simple logics. In addition, this system does not require voltage scaling when the delay increases, because it compensates for the aging-induced delay increase by computation approximation. So, it does not incur additional power consumption due to the voltage scaling for the assignment of the reliability guardband.

For the logic that cannot be compensated by computation approximation (e.g., control logic), the designer can use the degradation-aware cell library to synthesize them for aging compensation [5]. This ensure that the synthesized netlist consistently does not violate timing constraints even at the maximum age that the cell library is characterized for. Since the cell library provides worst-case delay information incurred by aging effects, the synthesis tool will generate a circuit that will meet constraints under such maximum-age delays. Besides, conventional types of aging compensation schemes also can be also used (e.g., up-sizing the transistors and increasing supply voltage).

#### 1.5 Evaluation

#### 1.5.1 Experimental setup

Two experiments are conducted to evaluate the proposed system and scheme. First, two types (masking and cutting) of 32-bit proposed adder and one type (masking) of 16-bit multiplier are implemented and they are evaluated with randomly generated inputs. The 100K random inputs are generated with normal distributions using \$dist\_normal() functions in Verilog since the random inputs with normal distribution have similar characteristics with the actual input extracted from an image encoder/decoder block [5]. Mean and standard deviation values in [34] are used for this test input generation. Next, the

proposed system and scheme with real application environment is evaluated. The experiment with DCT and IDCT circuits, which encode and decode input images that are widely used for image codec applications, is performed. The output port of DCT is directly connected to the input port of IDCT to encode and then decode the input image file and see the impact of aging-induced delay on the image quality. The two different monitoring circuits for adders and multipliers are used to measure the aging-induced delay. Note that the monitoring circuits can be shared by operators (adder/multiplier) of the same kind in the same block while the granularity of blocks varies from design to design.

Synopsys Design Compiler (N-2017.09-SP4) is employed with compile\_ultra option to synthesize the RTL codes of the proposed adder/multiplier with the degradation-aware cell libraries, based on the 45nm Nangate process technology [5]. To prevent the re-arrangement of the gate-level structure by Design Compiler, the bottom-up synthesis methodology (i.e., Hierarchical design) is used: Firstly, adder and multiplier are synthesized with the same clock period longer than the point that incurs the structure re-arrangement. Then, a target block (i.e., MAC unit) synthesized by integrating the synthesized adder and multiplier with the target clock period (2.65ns), while applying set\_dont\_touch option on the adder and multiplier not to re-arrange the synthesized netlist.

Synopsys Prime Time (J-2014.06-SP3) is employed for the static timing analysis and power estimation of the synthesized netlist under aging. the timing information is analyzed while changing the configuration of the 4-bit switch with the "set\_case\_analysis" command. Gate-level simulation is performed with Mentor ModelSim, in order to analyze the MSE, NMSE and error rate

Table 1.1: Comparison of 32-bit Ripple Carry Adder and Proposed Adder

| 32-bit Ripple Carry Adder   |                                 |               |          |         |          |          |        |  |  |

|-----------------------------|---------------------------------|---------------|----------|---------|----------|----------|--------|--|--|

| Aging Time                  | year 0                          | year 0 year 1 |          |         | year 10  |          |        |  |  |

| Dynamic + Static Power (uW) | 53.86                           | 53.70         |          |         | 54.43    |          |        |  |  |

| Area                        | 153.22                          |               |          |         |          |          |        |  |  |

| Critical Path Delay (ns)    | 1.966                           | 2.065         |          |         | 2.129    |          |        |  |  |

| Error Rate                  | 0.00%                           | 1.54%         |          |         | 2.89%    |          |        |  |  |

| MSE                         | 0.00                            | 4.85E+16      |          |         | 8.18E+16 |          |        |  |  |

| NMSE                        | 0.00                            | 0.00 1.85E+07 |          |         | 2.11E+07 |          |        |  |  |

|                             | 32-bit Proposed Adder - Masking |               |          |         |          |          |        |  |  |

| Aging Time                  | year 0                          | 0 year 1      |          |         | year 10  |          |        |  |  |

| # of Truncated LSBs         | -                               | 0             | 1        | 2       | 0        | 2        | 4      |  |  |

| Dynamic + Static Power (uW) | 56.21                           | 56.03         | 55.16    | 53.78   | 56.62    | 54.39    | 51.47  |  |  |

| Area                        | 161.73                          |               |          |         |          |          |        |  |  |

| Critical Path Delay (ns)    | 1.993                           | 2.108         | 2.044    | 1.980   | 2.172    | 2.040    | 1.865  |  |  |

| Error Rate                  | 0.00                            | 1.54%         | 75.18%   | 75.13%  | 2.89%    | 75.53%   | 74.87% |  |  |

| MSE                         | 0.00                            | 4.85E+16      | 3.85E+16 | 5.98    | 8.18E+16 | 7.68E+16 | 95.67  |  |  |

| NMSE                        | 0.00                            | 1.85E+07      | 1.39E+07 | 0.21    | 2.11E+07 | 2.17E+07 | 0.84   |  |  |

|                             | 32-bit Proposed Adder - Cutting |               |          |         |          |          |        |  |  |

| Aging Time                  | year 0                          | year 1        |          | year 10 |          |          |        |  |  |

| # of Truncated LSBs         | -                               | 0             | 1        | 2       | 0        | 2        | 4      |  |  |

| Dynamic + Static Power (uW) | 54.71                           | 54.54         | 53.13    | 52.14   | 55.27    | 52.86    | 51.01  |  |  |

| Area                        | 157.47                          |               |          |         |          |          |        |  |  |

| Critical Path Delay (ns)    | 2.032                           | 2.134         | 2.053    | 1.972   | 2.198    | 2.033    | 1.865  |  |  |

| Error Rate                  | 0.00%                           | 1.53%         | 50.55%   | 49.93%  | 3.02%    | 51.18%   | 49.87% |  |  |

| MSE                         | 0.00                            | 4.71E+16      | 5.20E+16 | 7.99    | 8.31E+16 | 1.14E+17 | 127.67 |  |  |

| NMSE                        | 0.00                            | 1.79E+07      | 1.99E+07 | 0.21    | 2.09E+07 | 3.51E+07 | 0.89   |  |  |

by aging-induced delay. Standard delay file (.sdf) is used to consider the aging-induced delay for the gate-level simulation.

the  $256 \times 256$  representative images from "video trace library" [35] are used as the input images. The Peak Signal-to-Noise Ratio (PSNR) metric is used for the evaluation of image quality. In the following subsection, image quality changes at year 0 and year 10 with/without the proposed compensation scheme will be presented. These results are generated by gate-level simulation with the degradation-aware cell libraries [5].

#### 1.5.2 RTL component level – Adder/Multiplier

The two types (masking and cutting) of the proposed 32-bit adders and one type (masking) of the proposed 16-bit multiplier, which can be configured to truncate four bits in LSBs at maximum, are implemented. The maximum number of truncated bits in LSBs is so decided because the delay increase by 10-year aging (about 8%) can be sufficiently compensated by 4-bit truncation for the adder and 3-bit truncation for the multiplier. In terms of the accuracy at the component level, the aforementioned error metrics (MSE, NMSE and error rate) are used.

Table 1.1 shows the comparison of power, area, and critical path delay between the conventional 32-bit ripple carry adder and the two types of the proposed adders. The conventional ripple carry adder generates aging-induced timing violation errors when the reliability guardband is not included. The error rate increases up to 1.54% (year 1) and 2.89% (year 10) and MSP errors incur high MSE and NMSE, which is due to the critical path delay increase by about 5.03% (year 1) and 8.29% (year 10). More than half of the aging-induced delay occurs within the first year, which is about 60% of the total delay increase by aging during the expected lifetime.

The critical path delay decreases by configuring the switch to cut-off the carry propagation path. At year 1, the critical path delay of 2-bit truncation is smaller than that of no truncation at year 0. It means that the 1-year's aging-induced delay can be compensated by the 2-bit truncation, and it eliminates the MSP errors. On the other hand, 1-bit truncation at year 1 cannot eliminate MSP errors perfectly, so it still shows high error values (i.e., MSE and NMSE). At 10-year, however, it is required to truncate four bits, because 2-bit truncation is not enough to recover the critical path delay. When the delay

Table 1.2: Comparison of 16-bit Carry Save Adder Array Multiplier and Proposed Multiplier

| 16-bit CSA Array Multiplier          |         |          |          |        |          |          |        |  |

|--------------------------------------|---------|----------|----------|--------|----------|----------|--------|--|

| Aging Time                           | year 0  | year 1   |          |        | year 10  |          |        |  |

| Dynamic + Static Power (uW)          | 661.90  | 659.40   |          |        | 657      |          |        |  |

| Area                                 | 1409.53 |          |          |        |          |          |        |  |

| Critical Path Delay (ns)             | 2.223   | 2.342    |          |        | 2.407    |          |        |  |

| Error Rate                           | 0.00%   | 4.35%    |          |        | 8.97%    |          |        |  |

| MSE                                  | 0.00    | 1.35E+17 |          |        | 2.12E+17 |          |        |  |

| NMSE                                 | 0.00    | 7.63E+15 |          |        | 8.10E+15 |          |        |  |

| 16-bit Proposed Multiplier - Masking |         |          |          |        |          |          |        |  |

| Aging Time                           | year 0  | year 1   |          |        | year 10  |          |        |  |

| # of Truncated LSBs                  |         | 0        | 1        | 2      | 0        | 2        | 3      |  |

| Dynamic + Static Power (uW)          | 665.30  | 662.80   | 645.20   | 621.90 | 660.40   | 619.90   | 596.20 |  |

| Area                                 | 1414.32 |          |          |        |          |          |        |  |

| Critical Path Delay (ns)             | 2.250   | 2.370    | 2.338    | 2.200  | 2.435    | 2.264    | 2.169  |  |

| Error Rate                           | 0.00%   | 5.72%    | 47.45%   | 70.00% | 10.55%   | 70.14%   | 81.68% |  |

| MSE                                  | 0.00    | 1.86E+17 | 5.84E+16 | 126.41 | 2.44E+17 | 2.19E+16 | 632.06 |  |

| NMSE                                 | 0.00    | 7.46E+15 | 1.77E+15 | 0.83   | 1.10E+16 | 1.79E+14 | 4.12   |  |

is compensated, the error values decrease significantly even though the error rate (rate of inaccurate sum) increases. Note that this error rate mostly comes from the LSP errors, so the error values are not large. This experimental results demonstrate that the proposed adders compensate for the aging-induced delay with computation approximation gracefully.

Table 1.2 shows that the same analysis can be done on the proposed multiplier. Without any truncation, after 1-year and 10-year aging, it shows very high error values due to the timing violation. The increased delay ratios are 5.35% (year 1) and 8.28% (year 10) which are close to that of the adder. However, the multiplier has a higher error rate than the adder; 1.53% vs 5.72% (year 1) and 3.02% vs 10.55% (year 10). It means that the multiplier produces more timing violations than the adder in both of year 1 and year 10. By truncating LSBs, the same benefits as in the adder can be achieved. After 1-year aging, the multiplier effectively recovers their functionality by truncating two bits with acceptable approximation error, 0.83 in NMSE. That is because the

Figure 1.8: Critical path delays of the proposed multiplier and two types of monitoring circuits: (a) generic and (b) dedicated. The shorter distance between the critical path delays means the lower delay mismatch and the better monitoring performance.

critical path delay becomes shorter than the delay of no truncation at year 0. After 10-year aging, however, the multiplier needs one more bit (i.e., three bits in total) to be truncated for acceptable error compensation.

Static power is always reduced due to aging since the aging increases the threshold voltage of transistors. However, dynamic power depends on the circuit design and application, and thus it can increase or decrease by aging [36]. In the experiment, the total power of the adders slightly decreases at year 1 but increases at year 10. However, for the multipliers, total power consistently decreases as aging proceeds. In case of the proposed adder/multiplier, a couple of additional AND or NAND cells are inserted for the switch logic. Due to these small overheads, the delay, area, and power consumption increase a little bit compared to the reference circuit. However, as more LSBs get truncated, the power consumption gradually decreases since the cut-off paths stop switching after the truncation.

#### 1.5.3 RTL component level – Monitoring circuit

the two types of monitoring circuit are introduced in subsection 1.3.4. One is the generic monitoring circuit which contains homogeneous delay elements. The other is the dedicated monitoring circuit which contains target-dependent heterogeneous delay elements. Because the adder contains homogeneous delay components (FA-CO) on its critical path, its delay can be accurately measured by a generic monitoring circuit. On the other hand, because the multiplier contains heterogeneous delay components (FA-CO, FA-SUM, HA-CO, and HA-SUM) on its critical path, it is inefficient to use a generic monitoring circuit to measure the its delay. To demonstrate this, critical path delay of the proposed multiplier is measured with the two types of monitoring circuit.

The requirement of feasible monitoring circuit is that its delay should be longer than that of the target circuit at every aging stages and for any number of truncated bits. That requires the monitoring circuit to have some amount of margin. However, if monitoring circuits have an excessive margin than is necessary, it can cause unnecessary truncation in the target circuit. To make matters worse, the excessive margin may impose slow circuit. Therefore, tight margin is essential for better monitoring circuits.

Figure 1.8 shows the critical path delays of the multiplier and the two types of monitoring circuits while increasing the number of truncated bits at year 0, year 1, and year 10 of aging using the degradation aware library [5]. Figure 1.8a is for the generic monitoring circuit, and Figure 1.8b is for the dedicated monitoring circuit. If comparing the two graphs, we can notice that the differences of the critical path delays between the multiplier and the monitoring circuit are bigger for the case of the generic monitoring circuit in Figure 1.8a.

The generic monitoring circuit has a line with a constant negative slope

Figure 1.9: (a) DCT/IDCT codec blocks and (b) matrix multiplication unit in DCT and IDCT blocks.

as it contains homogeneous delay elements. To meet the monitoring circuit requirement described above, in Figure 1.8a, the line of monitoring circuit should be placed above the line of the multiplier when 1-bit is truncated. As a result, it imposes excessive margin for the other number of truncated bits.

On the other hand, in case of the dedicated monitoring circuit, as shown in Figure 1.8b, the delay curve of the dedicated monitoring circuit follows that of the multiplier very closely on every number of truncated bits and aging years while keeping the requirement described above. As a result, it requires less margin than that of the generic monitoring circuit.

#### 1.5.4 System level

To evaluate the proposed system and scheme at the system level, DCT/IDCT codec blocks (See Figure 1.9) which encode and then decode the images from "video trace library" [35] are used. With this experiment, the feasibility of the proposed system in a real image processing application are shown. In

#### 1-year aging no compensation 2-bit truncation no compensation 2-bit truncation 35.49dB 14.45dB 13.47dB 35.60dB Cameraman **Foreman** no compensation 2-bit truncation no compensation 2-bit truncation 13.04dB 41.85dB 14.32dB 45.60dB Carphone Salesman 10-year aging no compensation 4-bit truncation no compensation 4-bit truncation 12.84dB SS.... Cameraman Cantion 4-bit truncation 37.18dB 11.12dB Foreman no compensation 4-bit truncation no compensation 12.16dB 11.36dB 42.06dB 45.73dB Carphone Salesman

Figure 1.10: Evaluation of aging compensation of proposed adder with approximation in image processing application. The value under the images are PSNR.

#### 1-year aging no compensation 2-bit truncation no compensation 2-bit truncation 13.00dB Cameraman **Foreman** no compensation 2-bit truncation no compensation 2-bit truncation 13.19dB 41.08dB 12.30dB 42.26dB Carphone Salesman 10-year aging no compensation **3-bit truncation** no compensation **3-bit truncation** 9.99dB 9.96dB 36.62dB 25.85dB **Foreman** Cameraman no compensation no compensation **3-bit truncation** 3-bit truncation 10.18dB 35.76dB 9.80dB 35.45dB Carphone Salesman

Figure 1.11: Evaluation of aging compensation of proposed multiplier (and proposed adder) with approximation in image processing application. The value under the images are PSNR.

the matrix multiplication unit of the blocks, each of a multiplier and an adder occupies a pipeline stage. different monitoring circuits to each of the adder and the multiplier are integrated. Experiments for the adder and the multiplier are performed independently, then a experiment for the combination of the two, which is a MAC unit, is performed.

Figure 1.10 shows the experimental results for the adder. Note that in this experiment, a delay-optimized multiplier (having high power consumption) instead of the proposed multiplier employ is utilized so that the adder is on the critical path. As shown in the figure, the four images show similar degradation due to the aging. For example, PSNR of "Cameramen" is degraded down to 14.45dB after 1-year aging and 12.84dB after 10-year aging, respectively. It means that without the proposed scheme the reliability guardband is essentially required even in error-tolerant applications, such as image processing, which do not immediately fails by timing violation at the cost of quality degradation. The fact that most of the aging occurs within the initial 1 year of the expected lifetime is also confirmed as observed in the RTL component level analysis.

In the proposed system, the aging-induced delay can be compensated for with computation approximation. For example, in case of 1-year aging, PSNR of "Cameramen" is recovered to 35.49dB by 2-bit truncation as shown in Figure 1.10. In case of 10-year aging, more bits should be truncated in order to recover the image quality. As shown in the figure, 4-bit truncation can recover PSNR of "Cameramen" to 35.55dB. These results indicate that the proposed system can dynamically compensate for the aging-induced delay with computation approximation at run-time, based on the delay information from the monitoring circuit (e.g. 2-bit truncation after 1-year aging and 4-bit truncation

after 10-year aging).

Next, a experiment for the 16-bit proposed multiplier is performed. Figure 1.10 shows the experimental results for the multiplier on the four images. Without compensation, multiplier's degradation in PSNR is more severe than that of the adder at equal aging stages, because the rate of timing violations in the multiplier is higher as mentioned in subsection 1.5.2. The compensation recovers PSNR up to acceptable levels by the computation approximation at both 1-year and 10-year aging stages, except for the 3-bit truncation for the "Cameraman" at 10-year aging, whose glitches are caused by the LSP errors of truncation. The reason why these glitches appear only in the case of the multiplier and not in the case of the adder, is that the truncation of the multiplier is directly applied to input images since the multiplications are performed earlier than the additions as shown in Figure 1.9b. The input images are represented as 8-bit integers, therefore truncation of 3 bits out of 8 bits may incur large approximation errors. On the other hand, truncation of the adder is performed on the results of the multiplier which have less significance in their LSBs.