**Ph.D. Dissertation**

### A Study on low damage etching and gate dielectrics for E-mode AlGaN/GaN-on-Si FETs

AlGaN/GaN 전력소자의 특성 향상을 위한 식각과 절연막에 관한 연구

August 2020

Graduate School of Electrical and Computer Engineering

**Seoul National University**

**Il-Hwan Hwang**

## Abstract

The Si technology for power devices have already approached its theoretical limitations due to its physical and material properties, despite the considerable efforts such as super junction MOSFET, trench gate, and insulated gate bipolar transistors. To overcome these limitations, many kinds of compound materials such as GaN, GaAs, SiC, Diamond and InP which have larger breakdown voltage and high electron velocity than Si also have been studied as future power devices. GaN has been considered as a breakthrough in power applications due to its high critical electric field, high saturation velocity and high electron mobility compared to Si, GaAs, and SiC. Especially, AlGaN/GaN heterostructure field-effect transistors (HFETs) have been considered as promising candidates for high power and high voltage applications.

However, these AlGaN/GaN heterostructure field-effect transistors with the 2DEG are naturally normally-on, which makes the devices difficult to deplete the channel at zero gate bias. Among the various methods for normally-off operation of GaN devices, gate-recess method is a promising method because it can be easier to implement than other approaches and ensure normally-off operation. However, charge trapping at the interface between gate dielectric and (Al)GaN and in the gate dielectric is a big issue for recessed gate MIS-HEMTs. This problem leads to degradation of channel mobility, on-resistance and on-current of the devices. Especially, V<sub>th</sub> hysteresis after a positive gate voltage sweep and V<sub>th</sub> shift under a gate bias stress are important reliability challenges in gate recessed MIS-HEMTs.

The scope of this work is mainly oriented to achieve high quality

interface at dielectric/(Al)GaN MIS by studying low damage etching methods and the ALD process of various dielectric layers.

In the etching study, various etching methods for normally-off operation have been studied. Also, etching damage was evaluated by various methods such as atomic force microscopy (AFM), photoluminescence (PL) measurements, X-ray photoelectron spectroscopy (XPS) measurements and electrical properties of the recessed schottky devices. Among the etching methods, the ALE shows the smoothest etched surface, the highest PL intensity and N/(Al+Ga) ratio of the etched AlGaN surface and the lowest leakage current of the gate recessed schottky devices. It is suggested that the ALE is a promising etching technique for normally-off gate recessed AlGaN/GaN MIS-FETs.

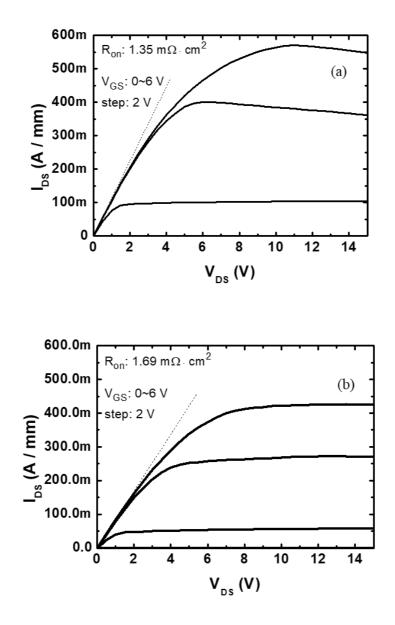

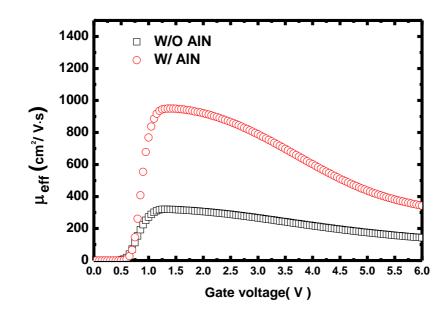

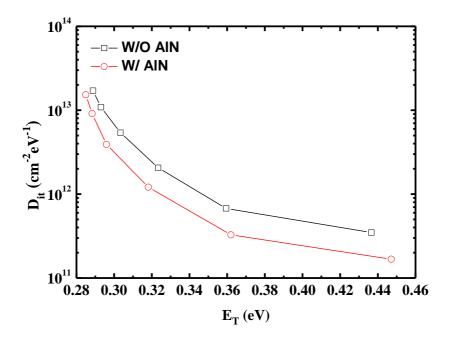

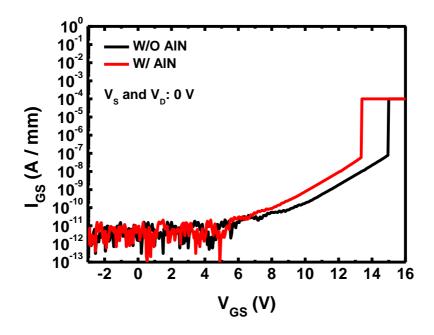

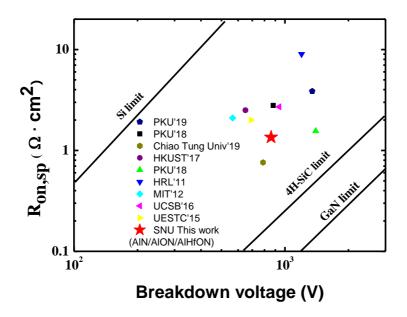

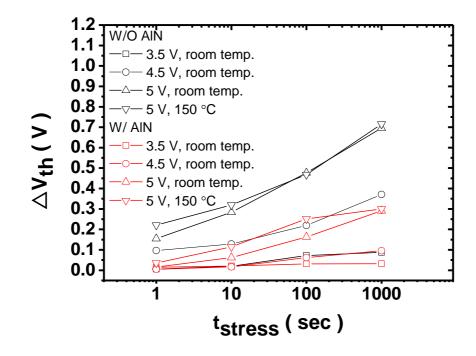

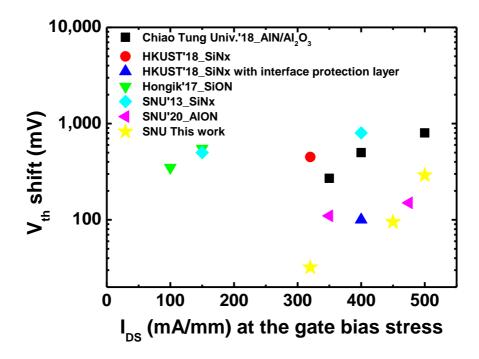

In the study of dielectrics, excellent electrical characteristics and small threshold voltage drift under positive gate bias stress are achieved by employing the SiON interfacial layer. However, considerable threshold voltage drift is observed under the higher positive gate bias stress even at the devices using the SiON interfacial layer. For further improvement of interface and reliability of devices, we develop and optimize an ALD AlN as an interfacial layer to avoid the formation of poor-quality oxide at the dielectric/(Al)GaN interface. We also develop an ALD AlHfON as a bulk layer, which have a high dielectric constant and low leakage current and high breakdown field characteristics. Devices with AlN/AlON/AlHfON layer. The extracted static R<sub>on</sub> values of devices with AlN/AlON/AlHfON and AlON/AlHfON are 1.35 and 1.69 m $\Omega \cdot cm^2$ , respectively. Besides, the effective mobility, D<sub>it</sub> and threshold voltage instability characteristics are all improved by employing the ALD AlN.

In conclusion, for high performance and improvement of reliability of normally-off AlGaN/GaN MIS-FETs, this thesis presents an etching technique for low damage etching and high-quality gate dielectric layer and suggests that the ALE and ALD AlN/AlON/AlHfON gate dielectric are very promising for the future normally-off AlGaN/GaN MIS-FETs

Keyword : Gallium nitride (GaN), Metal-insulator-semiconductor (MIS), Reliability, Aluminum nitride (AlN), Atomic layer etching (ALE), Aluminum hafnium oxynitride (AlHfON)

**Student Number : 2014-21616**

# **Table of Contents**

| List of Tables                                                 |

|----------------------------------------------------------------|

| List of Figures                                                |

| Chapter 1. Introduction 1                                      |

| 1.1. Backgrounds 1                                             |

| 1.2. Normally-off Operation in AlGaN/GaN HFETs 3               |

| 1.3. Issues and Feasible Strategies in AlGaN/GaN MIS-          |

| HFETs11                                                        |

| 1.4. Research Aims 15                                          |

| 1.5. References                                                |

| Chapter 2. Development and Evaluation of Low Damage            |

| Etching processes                                              |

| 2.1. Introduction                                              |

| 2.2. Various Evaluation Methods of Etching Damage 24           |

| 2.3. Low-Damage Dry Etching Methods                            |

| 2.3.1. Inductively Coupled Plasma-Reactive Ion                 |

| Etching Using BCl <sub>3</sub> /Cl <sub>2</sub> Gas Mixture 29 |

| 2.3.2. Digital Etching Using Plasma Asher and HCl              |

|                                                                |

| 2.3.3. Atomic Layer Etching Using Inductively                  |

| Coupled Plasma-Reactive Ion Etching System (ICP-               |

| RIE)                                                           |

| 2.4. Conclusion                                  | 75       |

|--------------------------------------------------|----------|

| 2.5. References                                  | 76       |

| Chapter 3. SiON/HfON Gate Dielectric Layer by Al | LD for   |

| AlGaN/GaN MIS-FETs                               | 80       |

| 3.1. Introduction                                | 80       |

| 3.2. ALD Processes for SiON and HfON             | 83       |

| 3.3. Electrical Characteristics of ALD SiON, HfC | )N and   |

| SiON/HfON Dual Layer on n-GaN                    | 87       |

| 3.4. Device Characteristics of Normally-off AlGa | N/GaN    |

| MIS-FETs with SiON/HfON Dual Layer               | 95       |

| 3.5. Conclusion                                  | 113      |

| 3.6. References                                  | 114      |

| Chapter 4. High Quality AlN/AlON/AlHfON Gate Die | electric |

| Layer by ALD for AlGaN/GaN MIS-FETs              | 120      |

| 4.1. Introduction                                | 120      |

| 4.2. Development of ALD AlN/AlON/AlHfON          | J Gate   |

| Stack                                            | 122      |

| 4.2.1. Process Optimization for ALD AlN          | 122      |

| 4.2.2. ALD AlN as an Interfacial Layer           | 144      |

| 4.2.3. Thickness Optimization of AlN/            | 'AlON/   |

| AlHfON Layer                                     | 149      |

| 4.2.4. ALD AlHfON Optimization                   | 159      |

| 4.2.5. Material Characteristics of AlN/AlON/     |          |

| AlHfON Layer167                                                 |

|-----------------------------------------------------------------|

| 4.3. Device Characteristics of Normally-off AlGaN/GaN           |

| MIS-FETs with AlN/AlON/AlHfON Layer 171                         |

| 4.4. Conclusion                                                 |

| 4.5. References                                                 |

| Chapter 5. Concluding Remarks 188                               |

| Appendix 190                                                    |

| A. N <sub>2</sub> Plasma Treatment Before Dielectric Deposition |

|                                                                 |

| B. Tri-gate Normally-on/off AlGaN/GaN MIS-FETs 200              |

| C. AlGaN/GaN Diode with MIS-gated Hybrid Anode and              |

| Edge termination                                                |

| Abstract in Korean                                              |

| Research Achievements                                           |

# **List of Tables**

| Table 1.1 Characteristics of various semiconductor materials2                |

|------------------------------------------------------------------------------|

| Table 1.2 Advantages and disadvantages of the various methods for            |

| normally-off GaN HEMT9                                                       |

| Table 2.1 Surface composition of GaN during different processing steps       |

| estimated from the XPS data27                                                |

| Table 2.2 The XPS results of the etched AlGaN surfaces by the $BCl_3\!/Cl_2$ |

| based dry etching and the digital etching using asher and HCl                |

|                                                                              |

| Table 2.3 The XPS results of the etched AlGaN surfaces by the digital        |

| etching using asher and HCl and the atomic layer etching using               |

| ICP etcher69                                                                 |

| Table 2.4 Ideality factors and barrier heights determined from I-V           |

| characteristics of the fabricated diodes on n-GaN73                          |

| Table 3.1 Comparison of PVD, CVD and ALD85                                   |

| Table 4.1 Atomic percentages of Al, N, C and O for the ALD AlN143            |

| Table 4.2 Description of studied AlN/AlON/AlHfON layers149                   |

| Table 4.3 Description of studied AlN/AlON/AlHfON layers154                   |

| Table 4.4 Description of studied AlON, AlHfON and HfO2 layers160             |

| Table 4.5 Atomic percentages of Hf, Al, N, C and O for the ALD AlHfON        |

| layer                                                                        |

# **List of Figures**

| Figure 1.1 Theoretical limits for Si, SiC and GaN2                         |

|----------------------------------------------------------------------------|

| Figure 1.2 Schematic drawing of the crystal structure of wurtzite Ga-face  |

| and N-face GaN3                                                            |

| Figure 1.3 Polarization induced sheet charge density and directions of the |

| spontaneous and piezoelectric polarization in Ga- and N-face               |

| strained and relaxed AlGaN/GaN heterostructures5                           |

| Figure 1.4 Charge distribution profile of an AlGaN/GaN heterostructure $6$ |

| Figure 1.5 Band diagram of an AlGaN/GaN heterostructure                    |

| Figure 1.6 Methods for normally-off AlGaN/GaN FETs; (a) recessed gate,     |

| (b) Fluorine treatment, (c) cascode configuration, (d) p-GaN               |

| gate                                                                       |

| Figure 1.7 Band diagram of the dielectric/AlGaN/GaN MIS structure          |

| under various gate biases12                                                |

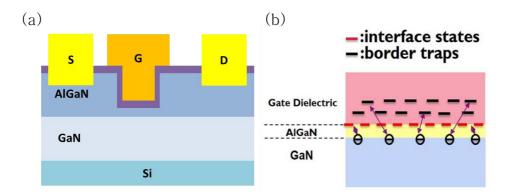

| Figure 1.8 (a) Schematic cross-sectional view of gate recessed MIS-        |

| HEMTs, (b) schematic of interface states and border traps in               |

| recessed AlGaN/GaN MIS-HEMTs13                                             |

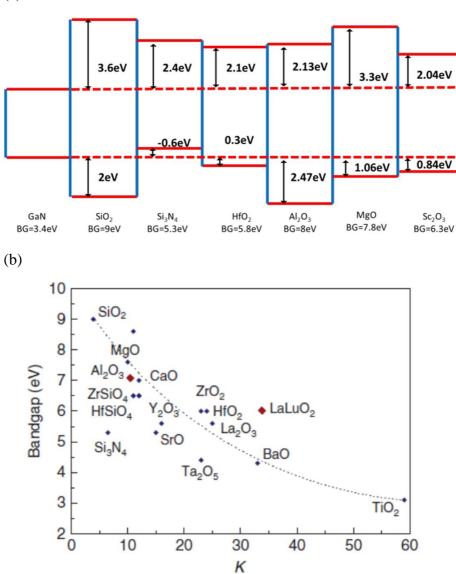

| Figure 1.9 (a) Conduction and valence band offsets for various dielectric  |

| on GaN, (b) dielectric constant vs bandgap for various                     |

| dielectric layers14                                                        |

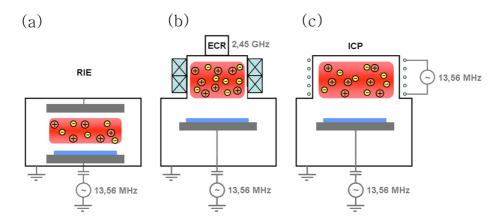

| Figure 2.1 Various dry etching methods (a) reactive ion etching (RIE), (b) |

| electron-cyclotron-resonance reactive ion etching, (c)                     |

| inductively coupled plasma reactive ion etching (ICP-RIE)                  |

|                                                                            |

|                                                                            |

Figure 2.2 AFM images of GaN surfaces (a) After BCl<sub>3</sub>/Cl<sub>2</sub> plasma dry

etching (b) After BCl<sub>3</sub>/Cl<sub>2</sub> plasma dry etching in ICP system... Figure 2.3 I-V characteristics of Schottky diodes fabricated on both the Figure 2.4 Schematic illustration of electron transport through the interface of metal with ICP -etched GaN: (a) forward bias condition and Figure 2.5 Photoluminescence spectra at 20 K of an unetched GaN sample Figure 2.8 Self bias and etch rate as functions of (a) RF bias power and (b) Figure 2.9 AFM images as functions of RF bias power (a) 4 W, (b) 6 W Figure 2.10 The process of digital etching. (a) plasma oxidation and (b) Figure 2.11 The image of microwave plasma asher which is used for plasma oxidation......35 Figure 2.12 XPS spectra of O1s from the AlGaN surfaces which are treated with HCl at room temperature and HCl at 80 °C, respectively Figure 2.13 The etch rate per cycle for a fixed dipping time of 5 minutes in HCl at 80 °C, varying oxygen plasma time and plasma power

Figure 2.14 The etch rate per cycle for a fixed oxygen plasma time of 3 minutes, varying dipping time in HCl at 80 °C and plasma

Figure 2.15 The etch rate per cycle for a fixed oxygen plasma time of 3 minutes and varying dipping time in HCl at room temperature Figure 2.16 Fabrication process for the gate recessed schottky devices ...41 Figure 2.17 The gate-recess processes for the gate recessed schottky Figure 2.18 The schematic cross section and dimensions of the fabricated Figure 2.19 I-V characteristics of the fabricated gate recessed Schottky devices. (a) drain current and (b) gate current......44 Figure 2.21 Atomic force microscopy (AFM) images of a 3um x 3um area. (a) before etching, (b) after  $\sim 5$  nm etching by the BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching using ICP etcher and (c) ~5 nm etching by the digital etching using asher and HCl......47 Figure 2.22 N/(Al+Ga) ratios of the etched samples by the BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching and the digital etching using asher and HCl......49 Figure 2.23 Schematic illustration of one cycle of ALE. (a) O<sub>2</sub> plasma, (b) purge, (c) BCl<sub>3</sub> plasma and (d) purge ......51

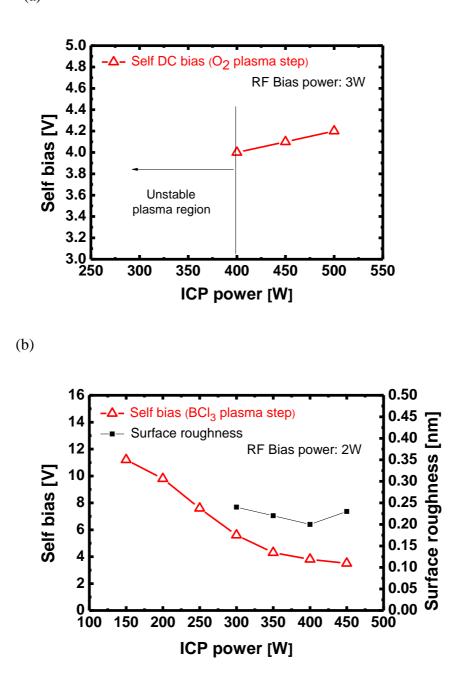

- Figure 2.25 The DC self-biases for varying ICP power and the fixed bias power. (a) O<sub>2</sub> plasma step and (b) BCl<sub>3</sub> plasma step ......55

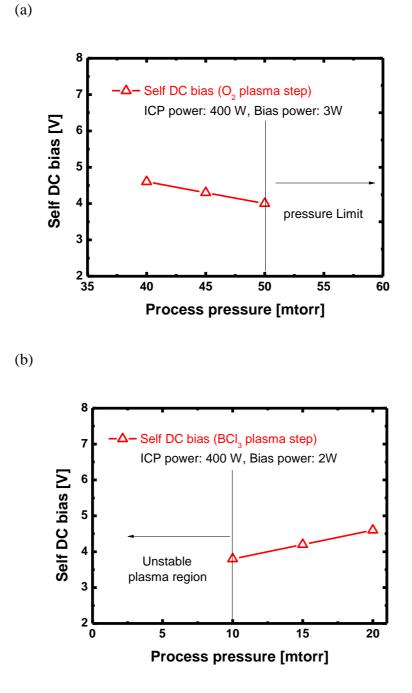

- Figure 2.26 The DC self-biases for varying pressure and the fixed bias and ICP power. (a) O<sub>2</sub> plasma step and (b) BCl<sub>3</sub> plasma step ......57

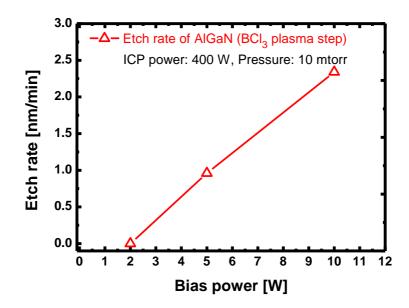

| Figure 2.27 Etch rates for varying bias power and the fixed ICP power of                          |

|---------------------------------------------------------------------------------------------------|

| 400W with BCl <sub>3</sub> plasma58                                                               |

| Figure 2.28 Etch rates for varying O <sub>2</sub> plasma time and each different BCl <sub>3</sub> |

| plasma time per cycle60                                                                           |

| Figure 2.29 Etch rates for varying BCl <sub>3</sub> plasma time and each different O <sub>2</sub> |

| plasma time per cycle60                                                                           |

| Figure 2.30 The ALE linearity between the etch depth and the number of                            |

| cycles61                                                                                          |

| Figure 2.31 The gate-recess processes for the gate recessed Schottky                              |

| devices63                                                                                         |

| Figure 2.32 The schematic cross section and dimensions of the fabricated                          |

| devices                                                                                           |

| Figure 2.33 I-V characteristics of the fabricated gate recessed Schottky                          |

| devices. (a) drain current and (b) gate current                                                   |

| Figure 2.34 PL characteristics for the samples                                                    |

| Figure 2.35 Atomic force microscopy (AFM) images of a 3um x 3um area.                             |

| (a) before etching, (b) after ~5 nm etching by the digital                                        |

| etching using asher and HCl and (c) ~5 nm etching by the                                          |

| ALE                                                                                               |

| Figure 2.36 N/(Al+Ga) ratios of the etched samples by the digital etching                         |

| using asher and HCl and the ALE using ICP etcher70                                                |

| Figure 2.37 Cross-section of the fabricated diodes on n-GaN71                                     |

| Figure 2.38 I-V curves of the fabricated diodes on n-GaN. (a) forward I-V                         |

| characteristics (linear scale), (b) forward I-V characteristics                                   |

| (log scale) and (c) reverse I-V characteristics (log scale)73                                     |

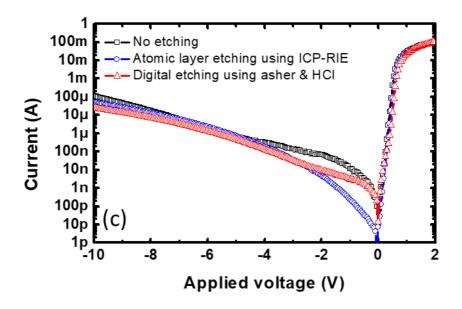

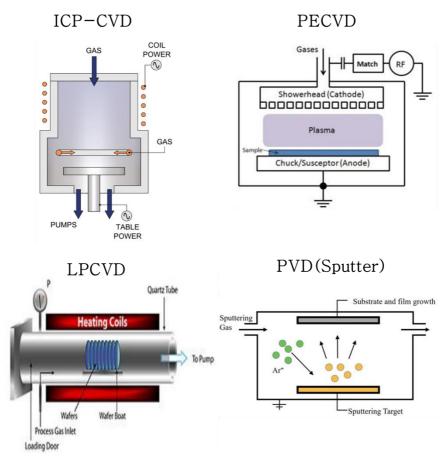

| Figure 3.1 Various deposition processes for gate dielectrics                                      |

| Figure 3.2 Configuration of the PEALD system in ISRC                                              |

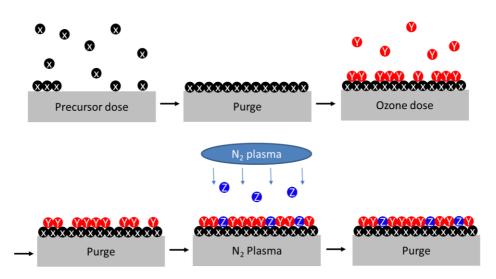

| Figure 3.3 Schematic of one deposition cycle of ALD SiON and HfON86        |

|----------------------------------------------------------------------------|

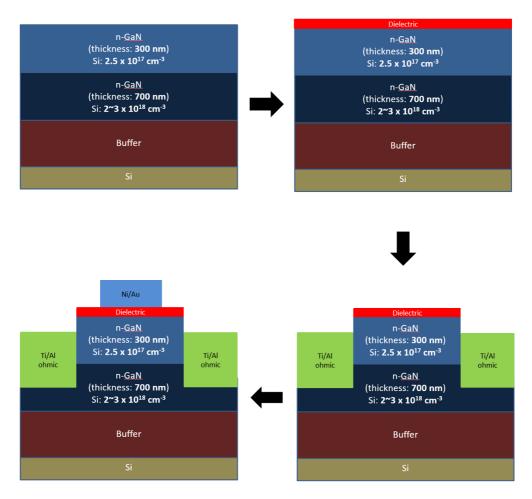

| Figure 3.4 Process flow of circular MIS capacitors                         |

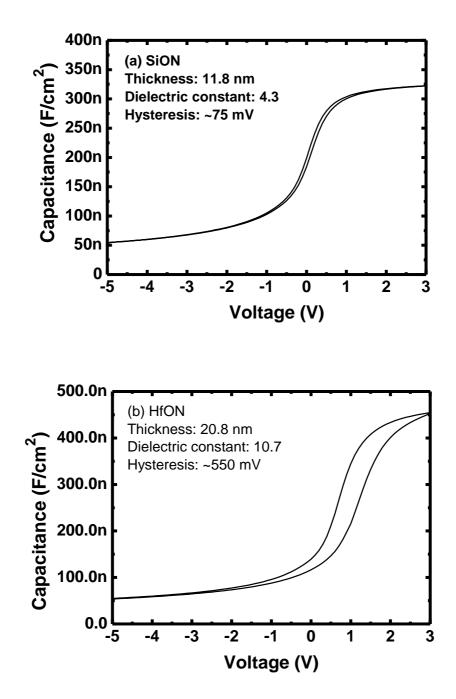

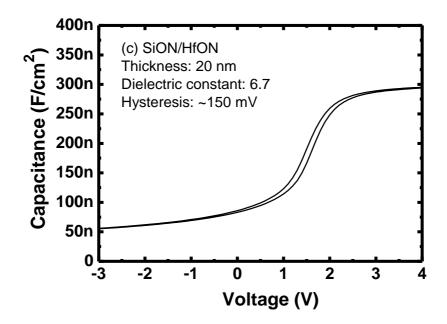

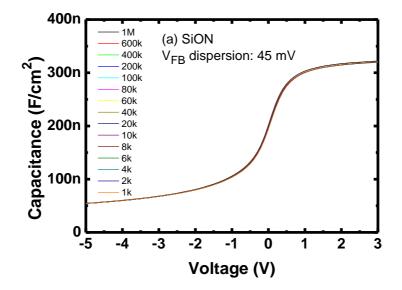

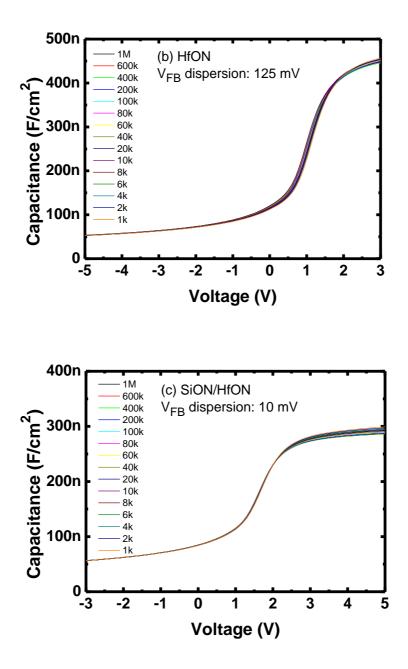

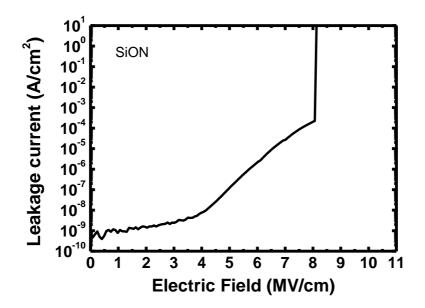

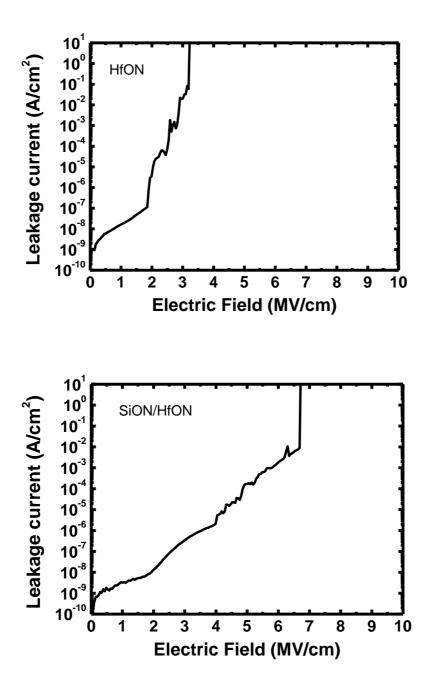

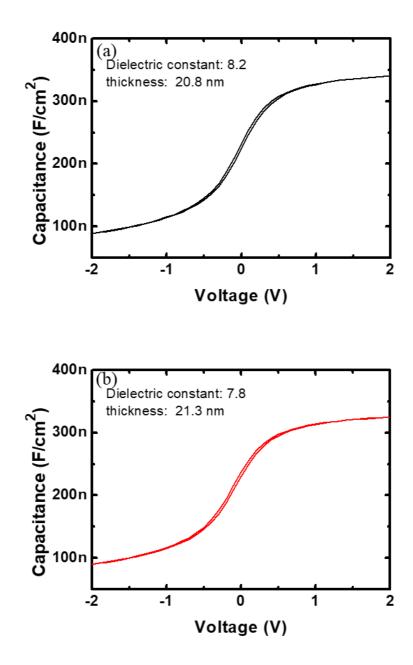

| Figure 3.5 C-V curves of (a) 11.8 nm SiON, (b) 20.8 nm HfON and (c) 5      |

| nm SiON/15 nm HfON on n-GaN at 1MHz90                                      |

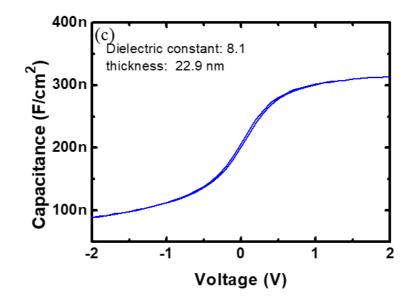

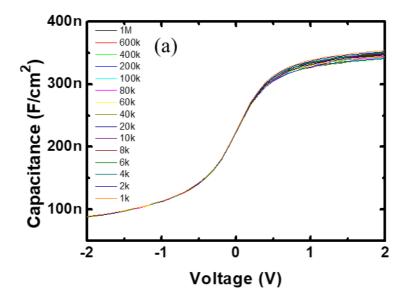

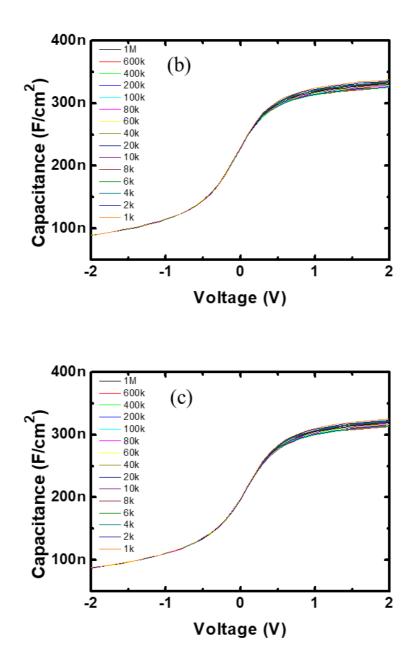

| Figure 3.6 C-V curves with multi frequency range from 1 MHz to 1 KHz       |

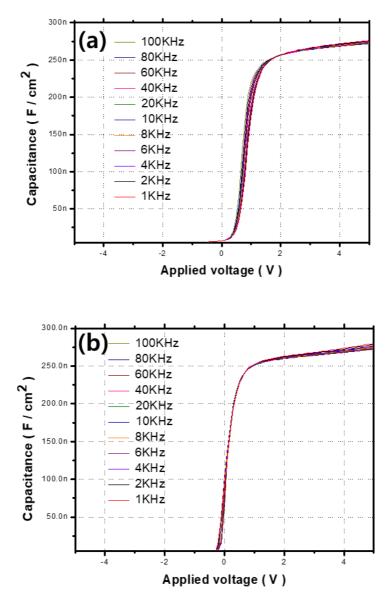

| of (a) SiON, (b) HfON and (c) SiON/HfON on n-GaN92                         |

| Figure 3.7 J-E curves of the fabricated dielectric on n-GaN capacitors94   |

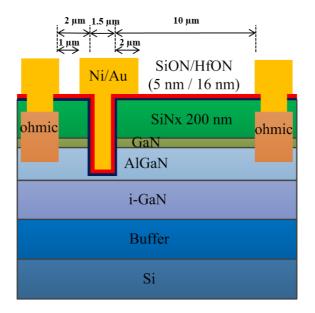

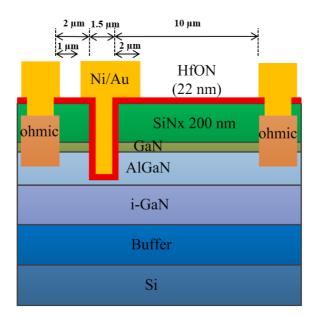

| Figure 3.8 Cross-sectional views of gate recessed AlGaN/GaN MIS-FETs       |

| with 5 nm SiON/16 nm HfON and with 22 nm HfON96                            |

| Figure 3.9 Schematic of the process flow of the gate recessed MIS-FETs     |

|                                                                            |

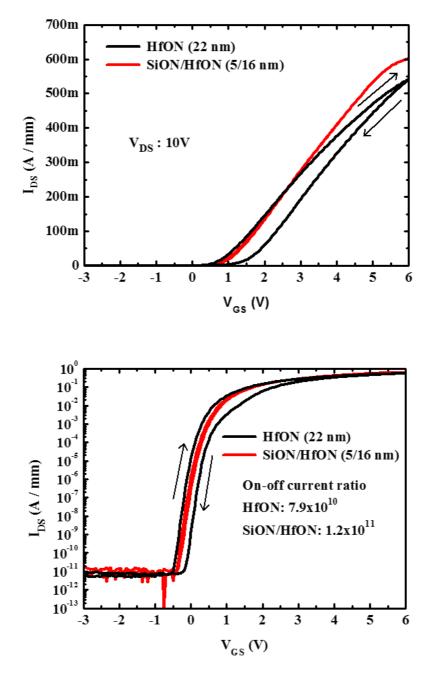

| Figure 3.10 Transfer characteristics of gate recessed AlGaN/GaN MIS-       |

| FETs with 22 nm HfON and with 5 nm SiON/16 nm HfON                         |

|                                                                            |

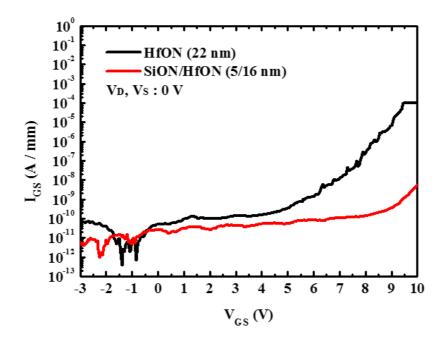

| Figure 3.11 Gate leakage current characteristics of gate recessed          |

| AlGaN/GaN MIS-FETs with 22 nm HfON and with 5 nm                           |

| SiON/16 nm HfON102                                                         |

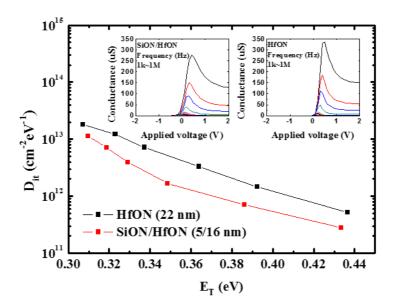

| Figure 3.12 Interface trap density extracted using the conductance method. |

| The measured conductances were shown in the insets103                      |

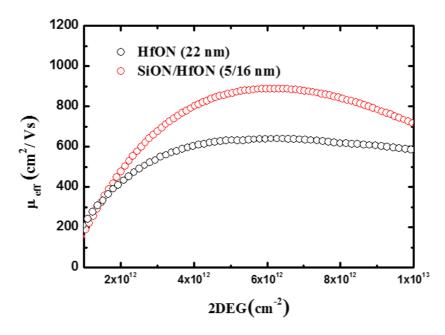

| Figure 3.13 Effective mobility in the normally-off GaN channel of a FAT-   |

| FET with a gate length of 100 $\mu$ m with 22 nm HfON and with             |

| 5 nm SiON/16 nm HfON104                                                    |

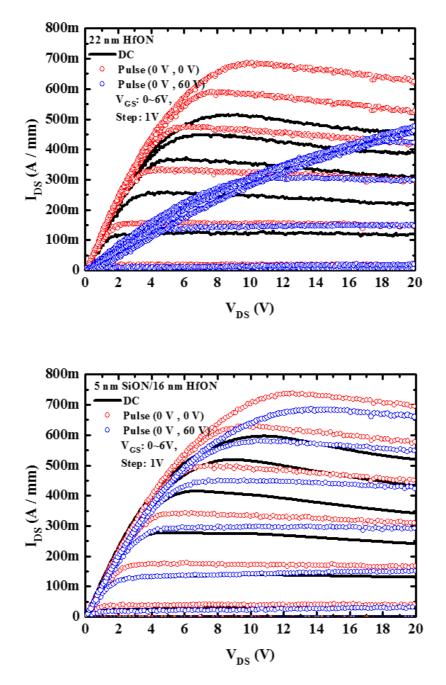

| Figure 3.14 Pulsed I-V characteristics of gate recessed AlGaN/GaN MIS-     |

| FETs with 22 nm HfON and with 5 nm SiON/16 nm HfON                         |

|                                                                            |

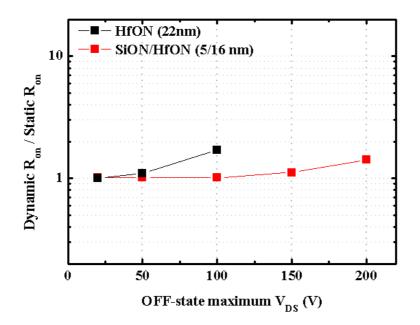

| Figure 3.15 Dynamic on-resistance characteristics of gate recessed         |

|                                                                            |

AlGaN/GaN MIS-FETs with 22 nm HfON and with 5 nm

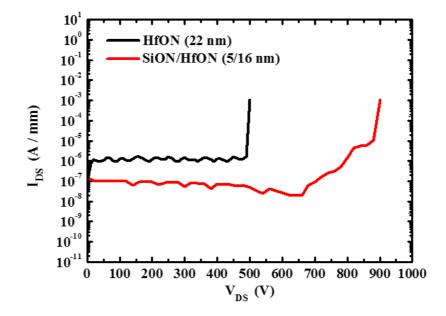

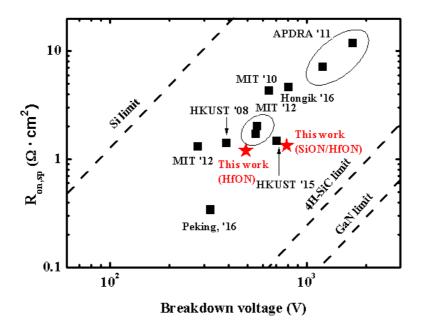

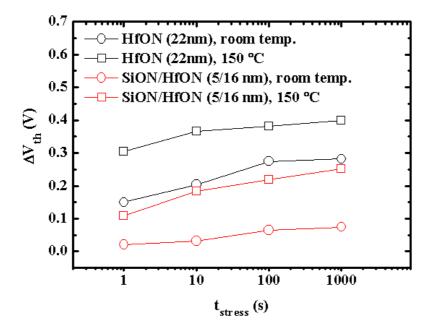

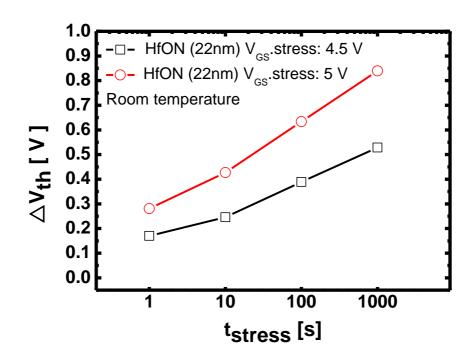

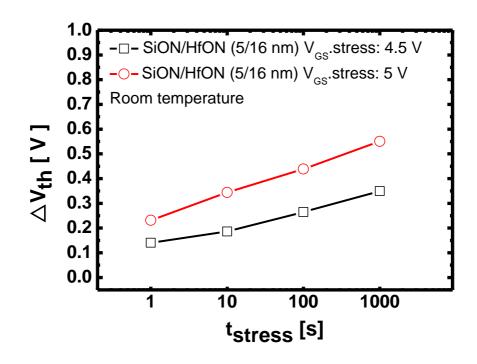

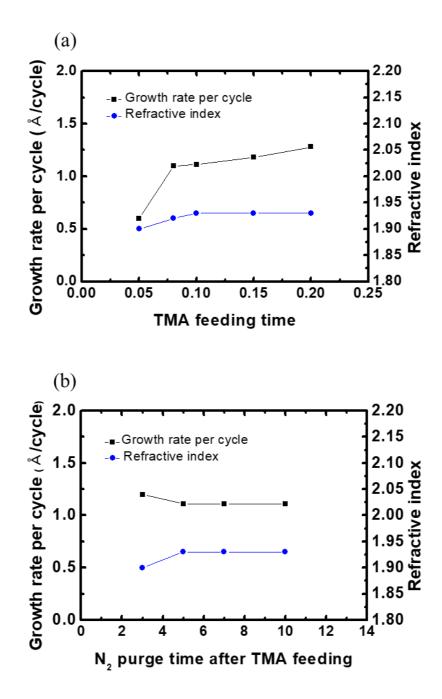

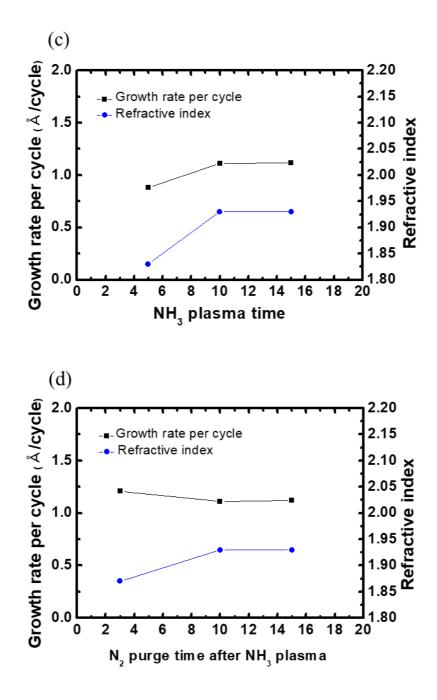

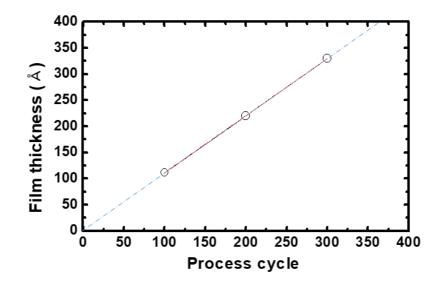

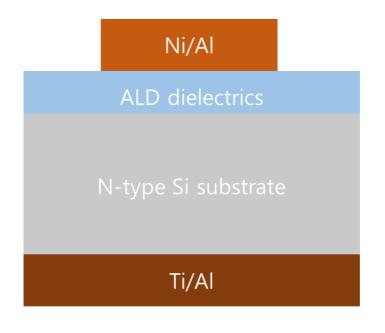

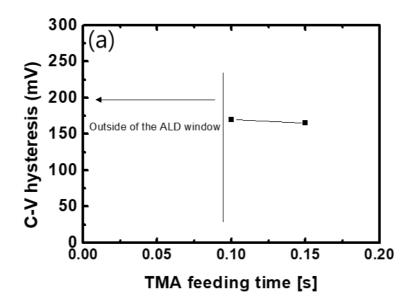

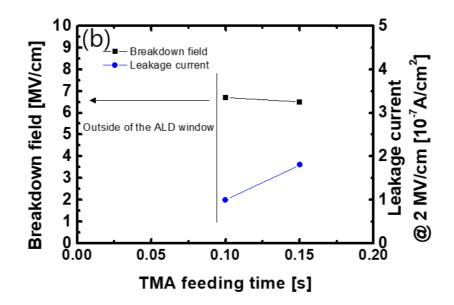

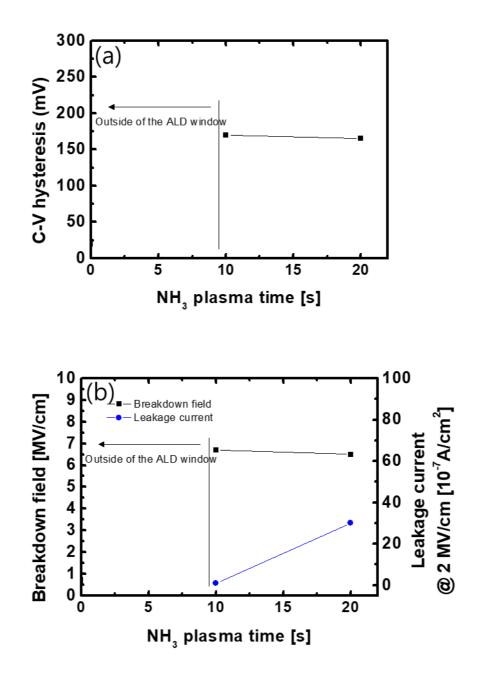

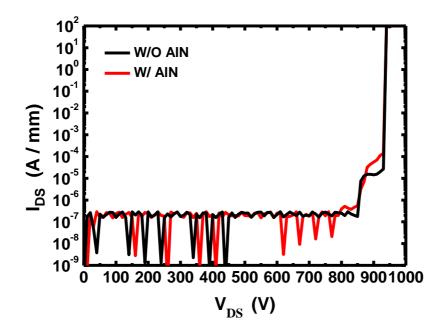

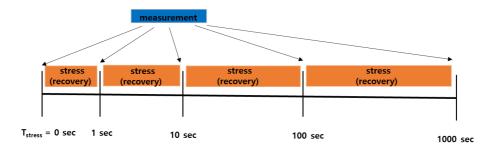

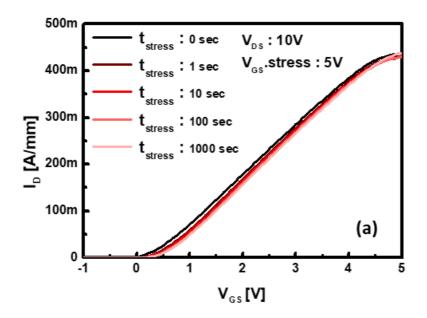

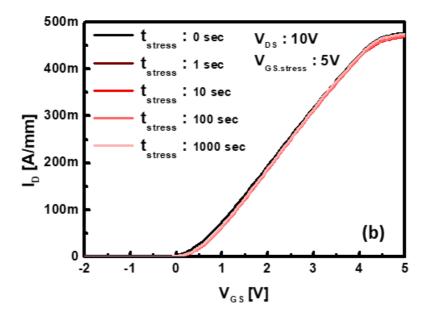

SiON/16 nm HfON......107 Figure 3.16 Off-state I-V characteristics at  $V_{GS} = 0$  V for gate recessed AlGaN/GaN MIS-FETs with 22 nm HfON and with 5 nm Figure 3.17 Benchmark of breakdown voltage and specific Ron for gate re-Figure 3.18 Threshold voltage instability of gate recessed AlGaN/GaN MIS-FETs with 22 nm HfON and with 5 nm SiON/16 nm HfON under positive gate bias of 3.5 V and various stress time Figure 3.19 Threshold voltage instability of gate recessed AlGaN/GaN MIS-FETs with 22 nm HfON and with 5 nm SiON/16 nm HfON under positive gate biases of 4.5 and 5 V and various Figure 4.2 ALD window of ALD AlN. (a) TMA feeding time, (b) N<sub>2</sub> purge time after TMA feeding, (c)  $NH_3$  plasma time and (d)  $N_2$ purge time after NH<sub>3</sub> plasma ......125 Figure 4.3 AlN film thickness vs number of ALD cycles ......126 Figure 4.4 Process flow of Si MIS-capacitors......127 Figure 4.5 Electrical characteristics of AlN as a function of TMA feeding time. (a) C-V hysteresis vs TMA feeding time and (b) breakdown field and leakage current at 2 MV/cm of AlN vs Figure 4.6 Electrical characteristics of AlN as a function of NH<sub>3</sub> plasma time. (a) C-V hysteresis vs NH<sub>3</sub> plasma time and (b)

breakdown field and leakage current at 2 MV/cm of AlN vs

| NH3 plasma time130                                                          |

|-----------------------------------------------------------------------------|

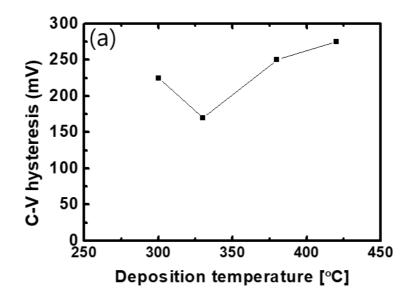

| Figure 4.7 Electrical characteristics of AlN as a function of deposition    |

| temperature. (a) C-V hysteresis vs deposition temperature and               |

| (b) breakdown field and leakage current at 2 MV/cm of AlN                   |

| vs deposition temperature132                                                |

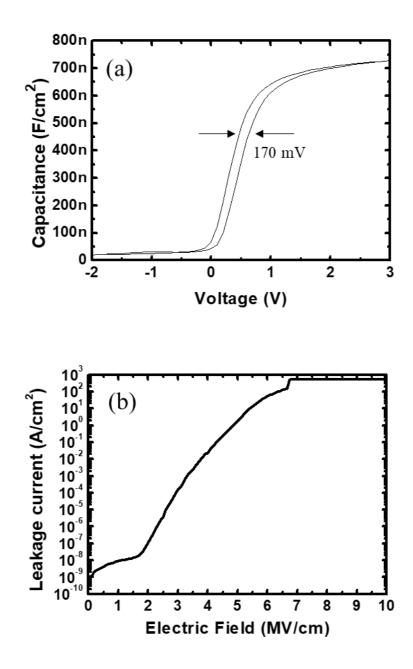

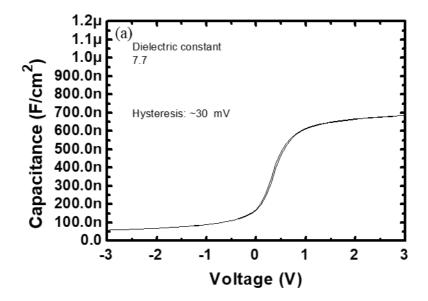

| Figure 4.8 Electrical characteristics of the optimized AlN on Si. (a) C-V   |

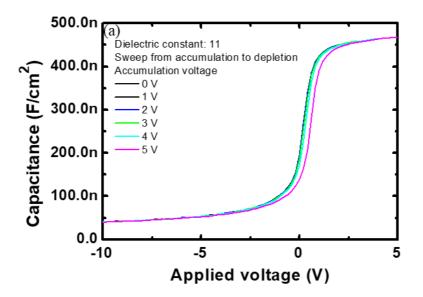

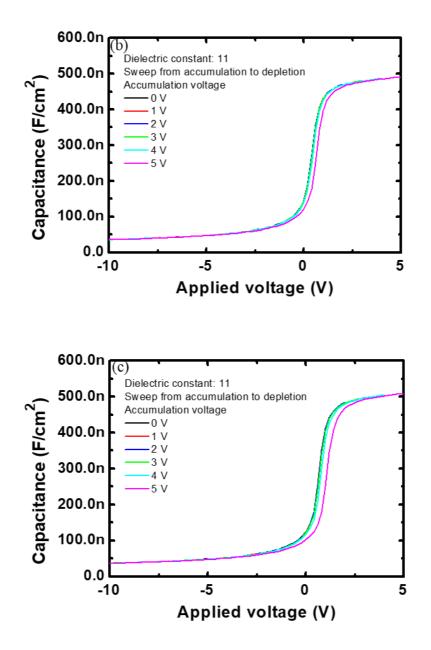

| characteristics and (b) J-V characteristics                                 |

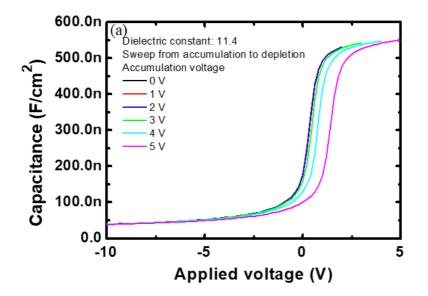

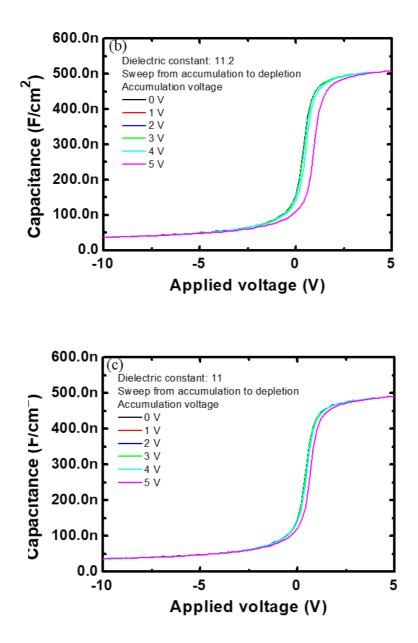

| Figure 4.9 C-V characteristics of the ALD AlN on n-GaN capacitors. $NH_3$   |

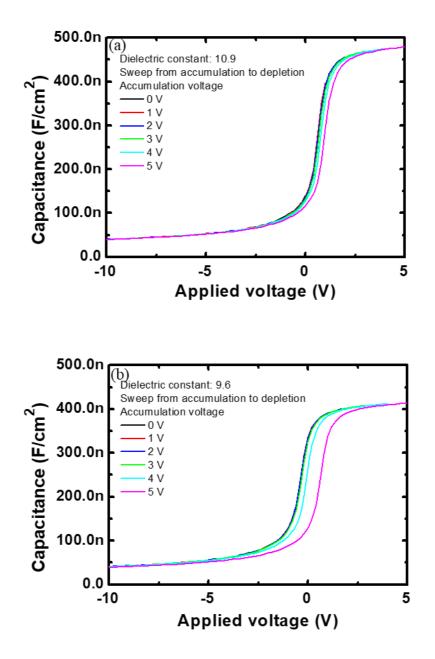

| plasma power (a) 100 W, (b) 50 W and (c) 30 W136                            |

| Figure 4.10 C-V characteristics of the ALD AlN on n-GaN capacitors with     |

| various frequencies varying from 1k to 1MHz. (a) 100 W, (b)                 |

| 50 W and (c) 30 W137                                                        |

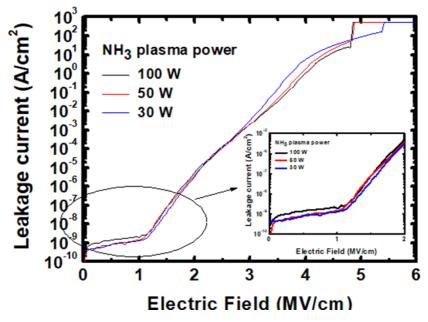

| Figure 4.11 J-V characteristics of the ALD AlN on n-GaN capacitors with     |

| various NH <sub>3</sub> plasma powers138                                    |

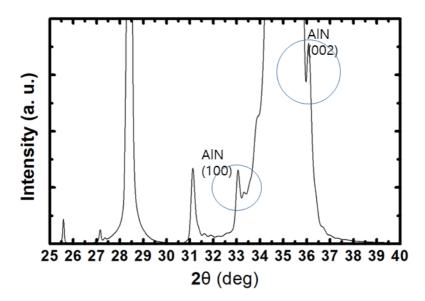

| Figure 4.12 XRD result for the ALD AlN of 100 nm on n-GaN139                |

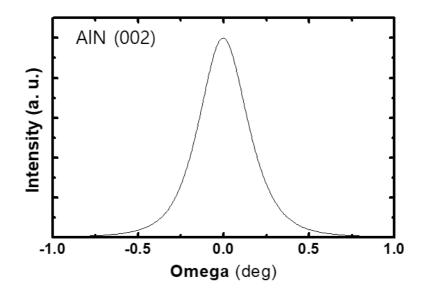

| Figure 4.13 Rocking curve of AlN (002) plane of the ALD AlN140              |

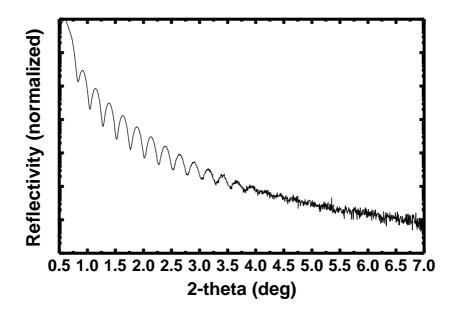

| Figure 4.14 XRR measurement of the ALD AlN of ~ 30 nm on n-GaN              |

|                                                                             |

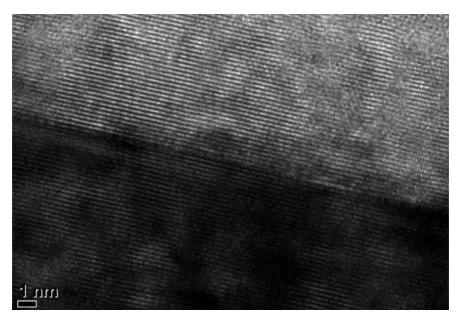

| Figure 4.15 Cross-sectional TEM image of the AlN/n-GaN interface 142        |

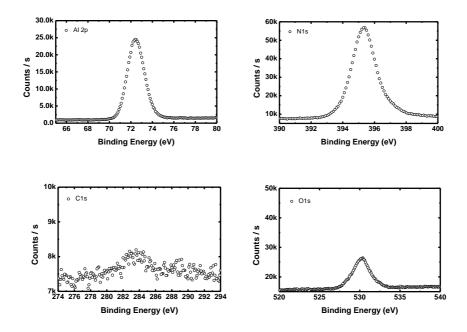

| Figure 4.16 XPS spectra of Al 2p, N 1s, C 1s and O 1s of the AlN143         |

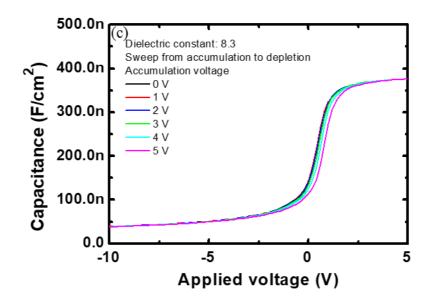

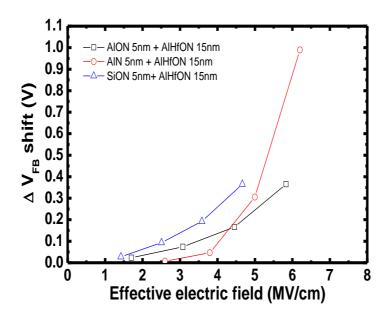

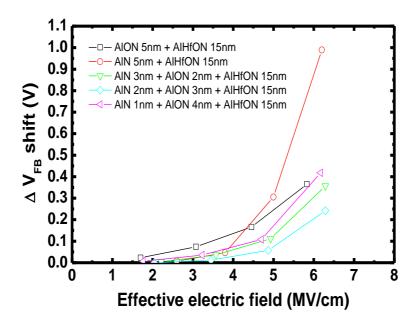

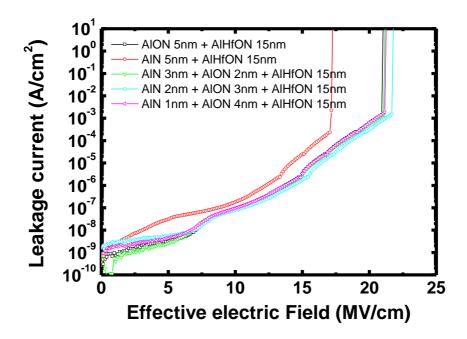

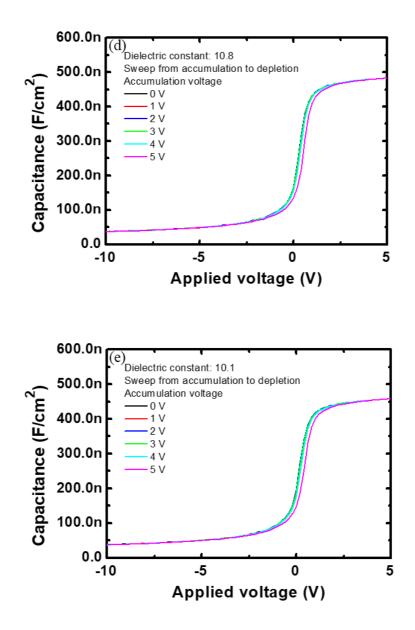

| Figure 4.17 C-V characteristics of the GaN MIS capacitors with              |

| accumulation voltages ranging from 0 to 5 V. (a) AlON 5                     |

| nm/AlHfON 15 nm, (b) AlN 5 nm/AlHfON 15 nm and (c)                          |

| SiON 5 nm/AlHfON 15 nm146                                                   |

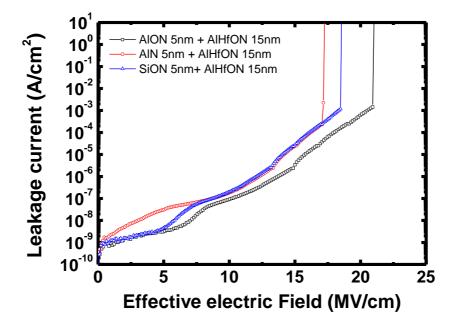

| Figure 4.18 $V_{FB}$ shift as a function of effective electric field in the |

| fabricated GaN MIS capacitors147                                            |

|                                                                             |

Figure 4.19 J- $E_{eff}$  characteristics of the fabricated GaN MIS capacitors 148

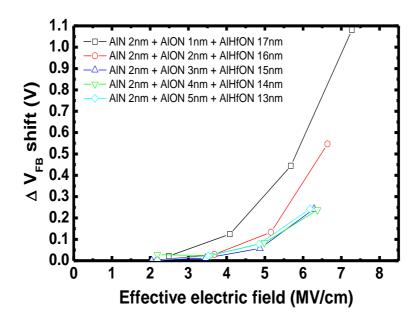

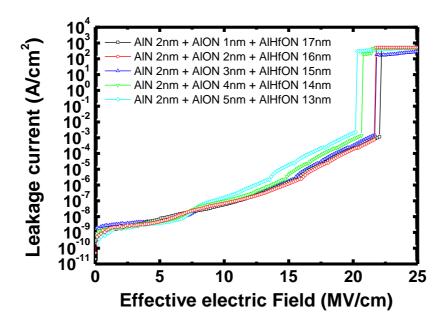

- Figure 4.22 J-E<sub>eff</sub> characteristics of the fabricated GaN MIS capacitors ......

100

- Figure 4.25 J-E<sub>eff</sub> characteristics of the fabricated GaN MIS capacitors 158

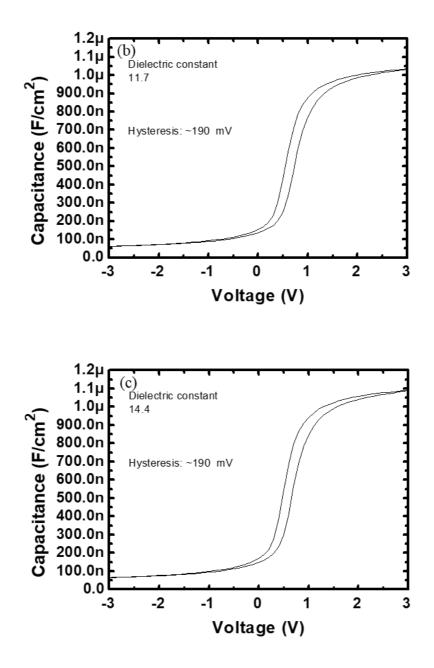

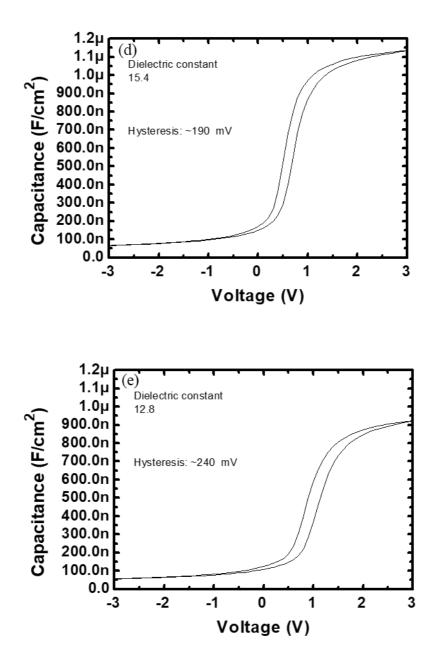

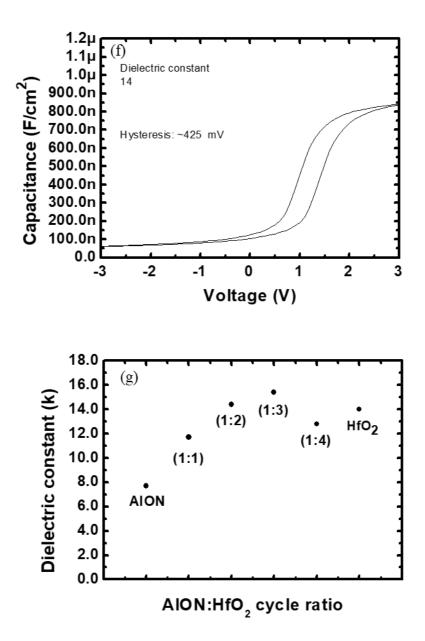

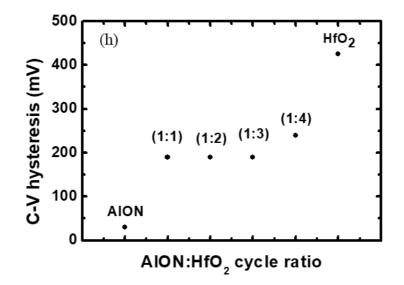

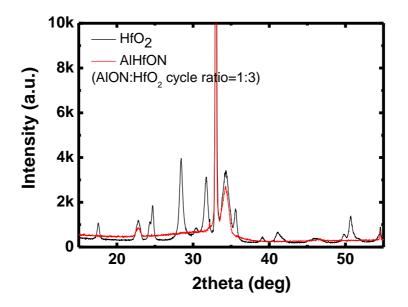

- Figure 4.26 C-V characteristics of (a) AlON, AlHfON with AlON : HfO<sub>2</sub> cycle ratio of (b) 1:1, (c) 1:2, (d) 1:3, (e) 1:4 and (f) HfO<sub>2</sub> and (g) the dielectric constants and (h) the amount of C-V

- hysteresis of the dielectric layers......164

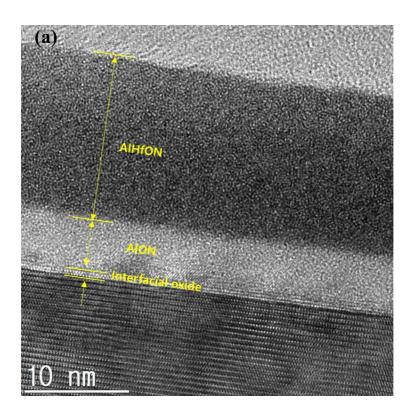

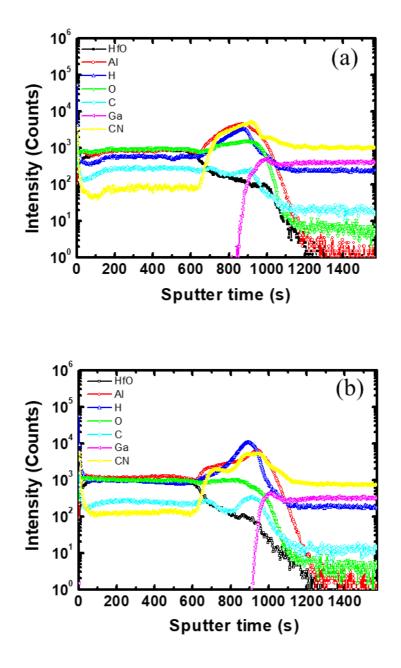

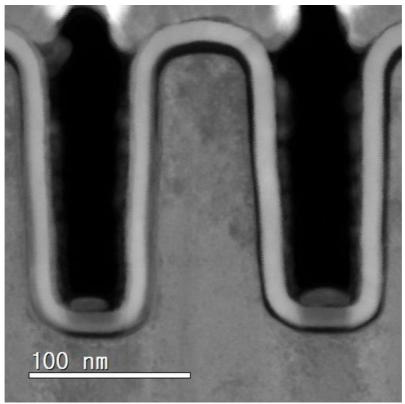

- Figure 4.29 TEM images of (a) AlON/AlHfON and (b)

- Figure 4.35 Gate leakage characteristics of the fabricated devices with AlN/AlON/AlHfON and AlON/AlHfON......177

- Figure 4.36 Off-state I-V characteristics of the fabricated devices with AlN/AlON/AlHfON and AlON/AlHfON at  $V_{GS} = 0$  V......178

## **Chapter 1. Introduction**

#### 1.1. Background

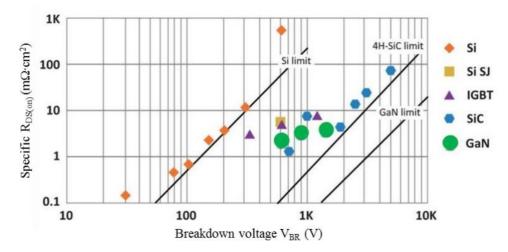

The silicon technology has been the main stream in the semiconductor industry for many decades because of its several advantages such as fundamentally good electrical properties and low-cost compared to other materials [1-3]. the Si-based devices also have been developed in power applications such as mobile, electric vehicles and home appliances. However, as shown in Fig. 1.1, the Si technology for power devices have already approached its theoretical limitations due to its physical and material properties, despite the considerable efforts such as super junction MOSFET, trench gate, and insulated gate bipolar transistors [4-6]. To overcome these limitations, many kinds of compound materials such as GaN, GaAs, SiC, Diamond and InP which have larger breakdown voltage and high electron velocity than Si also have been studied as future power devices [7-11]. Table 1.1 lists characteristics of various semiconductor materials. Among them, GaN has been considered as a breakthrough in power applications due to its high critical electric field, high saturation velocity and high electron mobility compared to Si, GaAs, and SiC [12].

Fig. 1.1 Theoretical limits for Si, SiC and GaN [13].

|                                                  | Si   | GaAs | 4H-SiC | GaN                     | Diamond | InP  |

|--------------------------------------------------|------|------|--------|-------------------------|---------|------|

| Bandgap (eV)                                     | 1.1  | 1.42 | 3.26   | 3.39                    | 5.45    | 1.34 |

| Electron<br>mobility<br>(cm²/V · s)              | 1350 | 8500 | 700    | 900(Bulk)<br>2000(2DEG) | 1900    | 5400 |

| Saturation<br>velocity<br>(10 <sup>7</sup> cm/s) | 1.0  | 1.0  | 2.0    | 2.5                     | 2.7     | 2.4  |

| Critical field<br>(MV/cm)                        | 0.3  | 0.4  | 3.0    | 3.3                     | 5.6     | 0.6  |

| Thermal<br>conductivity<br>(W/cm · K)            | 1.5  | 0.43 | 3.7    | 1.3                     | 20      | 0.7  |

Table 1.1 Characteristics of various semiconductor materials

## **1.2. Normally-off Operation in AlGaN** /GaN HFETs

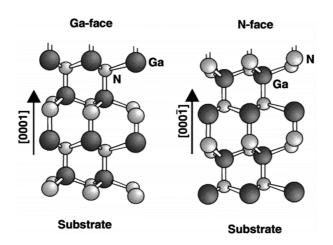

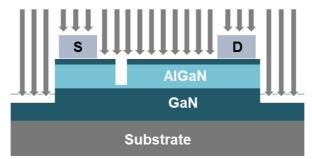

AlGaN/GaN heterostructure field-effect transistors (HFETs) have been considered as promising candidates for high power and high voltage applications. Two-dimensional electron gases (2DEGs) in AlGaN/GaN heterostructure can be achieved without intentionally doping, which contribute to the excellent performance of AlGaN/GaN based HFETs. The most common growth direction of GaN is normal to the [0001] basal plane, where the atoms are arranged in bilayers. These bilayers consist of two closely spaced hexagonal layers, One with cations and the other with anions. The basal surface should be either Ga- or N-faced as shown in Fig. 1.2 [14].

**Fig. 1.2** Schematic drawing of the crystal structure of wurtzite Ga-face and N-face GaN [14].

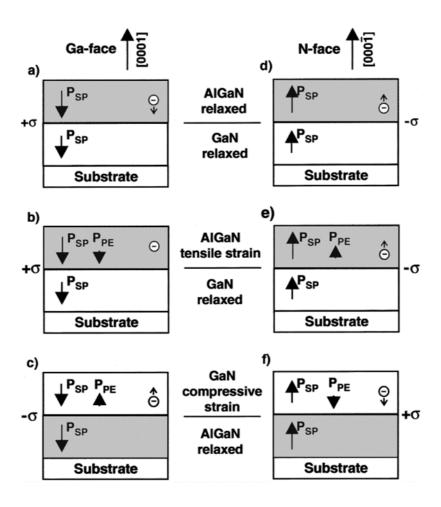

The large electron sheet densities and high mobilities of 2DEGs have been correlated to the spontaneous and piezoelectric polarization. Without external electric fields, the total polarization P of AlGaN or GaN is the sum of the spontaneous polarization and piezoelectric polarization. Each polarization can be defined by

$$\mathbf{P}_{SP} = P_{SP}\mathbf{z}$$

,  $\mathbf{P}_{PE} = 2\frac{a-a_0}{a_0}\left(e_{31} - e_{33}\frac{C_{13}}{C_{33}}\right)$ .

$\alpha$ : the lattice constant of the strained layer  $\alpha_0$ : the length of the hexagonal edge  $e_{31}, e_{33}$ : the the piezoelectric coefficients  $C_{13}, C_{33}$ : elastic constants [15, 16]

The spontaneous polarization can cause electric fields up to 3MV/cm in III-N crystals, and strain from AlGaN/GaN grown pseudomorphically cause an additional piezoelectric field of about 2 MV/cm [17].

**Fig. 1.3** Polarization induced sheet charge density and directions of the spontaneous and piezoelectric polarization in Ga- and N-face strained and relaxed AlGaN/GaN heterostructures [14].

The negative sign of the spontaneous polarization is reported for GaN and the negative piezoelectric polarization and the positive piezoelectric polarization are formed for tensile strained AlGaN and compressive strained AlGaN, respectively. As a result, parallel piezoelectric and spontaneous polarization are formed at tensile strain and antiparallel piezoelectric and

spontaneous polarization exist at compressive strain as shown in Fig. 1.3.

Fig. 1.4 Charge distribution profile of an AlGaN/GaN heterostructure [17]

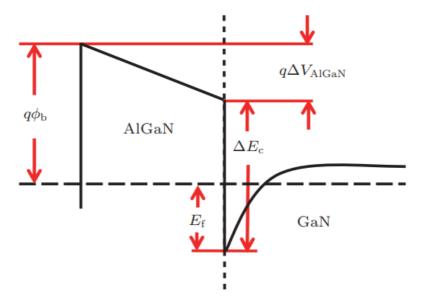

Fig. 1.5 Band diagram of an AlGaN/GaN heterostructure[17]

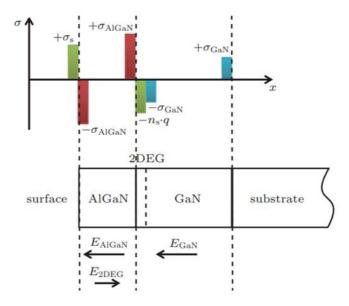

In the case of pseudomorphic AlGaN/GaN heterostructures with Gaface polarity and parallel piezoelectric and spontaneous polarization formed at tensile strain, the profile of the charge distributional of an AlGaN/GaN heterostructure can be depicted in Fig. 1.4.  $\sigma_{AlGaN}$  and  $\sigma_{GaN}$  are the polarization charges induced by AlGaN and GaN respectively, and  $\sigma_s$  is the ionized surface charge. The sheet density of 2DEG can be defined as

$$n_{\rm s} = rac{\sigma_{

m AlGaN}}{q} - rac{arepsilon}{q^2 d} (q\phi_{

m b} + E_{

m f} - \Delta E_{

m c}).$$

Where  $\varphi_b$ ,  $E_f$  and  $\Delta E_c$  are the surface barrier height, the Fermi level position with respect to the GaN conduction-band edge at the AlGaN/GaN interface, and the conduction band discontinuity between GaN and AlGaN, respectively, as seen in Fig. 1.5 [17]. The sheet density of 2DEG can be increased by increasing the Al-content of the AlGaN barrier and the AlGaN barrier thickness on GaN [14, 18].

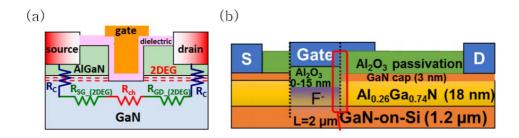

The 2DEG in AlGaN/GaN heterostructures enables GaN devices to operate in high frequency applications due to the high electron mobility and high saturation electron velocity of the 2DEG. However, these devices with the 2DEG are naturally normally-on, which makes the devices difficult to deplete the channel at zero gate bias. For power applications, normally-off devices offer desirable fail-safe operation conditions and simple circuit and system architecture because normally-off operation allow the elimination of negative-polarity power supply [19, 20]. For normally-off operation of GaN devices, several methods have been reported; recessed gate [19], fluorine treatment [21], cascode configuration [22] and the p-GaN gate [23] as shown in Fig. 1.6.

**Fig. 1.6** Methods for normally-off AlGaN/GaN FETs; (a) recessed gate [22], (b) Fluorine treatment [24], (c) cascode configuration [22], (d) p-GaN gate [22].

| Method                   | Advantages                                                                           | Disadvantages                                                                                                                        |  |

|--------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| Recessed gate            | . gate • Large forward<br>breakdown • Electron tra<br>dielectric/(.<br>• Etching dar |                                                                                                                                      |  |

| Fluorine<br>treatment    | • High current density                                                               | <ul><li>Thermal instability</li><li>Fluorine ion damage</li></ul>                                                                    |  |

| Cascode<br>configuration | • Stable V <sub>th</sub> > 0 of the<br>Si MOSFET                                     | <ul> <li>Package complexity</li> <li>Parasitic inductance</li> <li>High temperature<br/>operation limit by si<br/>devices</li> </ul> |  |

| P-GaN gate               | <ul> <li>Low resistance<br/>under the gate</li> <li>No dielectric issues</li> </ul>  | <ul> <li>Limited positive<br/>gate voltage swing</li> <li>P-GaN etching<br/>issue</li> </ul>                                         |  |

**Table. 1.2** Advantages and disadvantages of the various methods fornormally-off GaN HEMT.

The recessed gate approach can easily deplete the 2DEG channel by reducing the barrier layer thickness under the gate which can be realized by ICP dry etching [25]. However, low damage etching and high-quality dielectric/(Al)GaN interface are required for the high channel mobility and reliability of the devices. The fluorine treatment introducing negatively charge fluorine ions under the gate also depletes the channel by raising the potential of the AlGaN barrier. As a result, normally-off operation can be realized, but this approach has drawbacks in view of temperature stability and dispersion behavior as the charged ions might introduce deep traps [21, 26]. P-GaN gate on the AlGaN/GaN is the one of promising approaches for normally-off operation. The big advantage of this approach is that there are no dielectric issues. However, the limited positive gate voltage swing and the P-GaN etching issue are disadvantages of this approach [22]. With the cascode configuration, normally-off operation also can be obtained like in a Si MOSFET. This approach has some drawbacks such as the package complexity and parasitic inductances that affect the switching performance of the devices [27]. More details on methods for normally-off operation can be found in Table 1.2.

# 1.3. Issues and Feasible Strategies in AlGaN/GaN MIS-HFETs

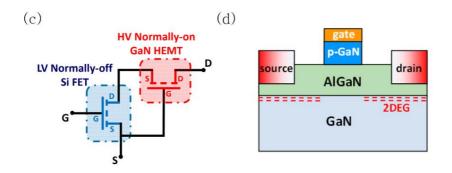

Among the various methods for normally-off operation of GaN devices, the recessed gate is a promising method because it can be easier to implement than other approaches and ensure normally-off operation. However, as discussed in the former section, charge trapping at the interface between gate dielectric and (Al)GaN and in the gate dielectric is a big issue for recessed gate MIS-HEMTs [28]. This problem leads to degradation of channel mobility, on-resistance and on-current of the devices. Especially, Vth hysteresis after a positive gate voltage sweep and V<sub>th</sub> shift under a gate bias stress are important reliability challenges in gate recessed MIS-HEMTs [29]. Therefore, it is important to understand the basic mechanism of V<sub>th</sub> shift of the devices. If gate bias is applied to the devices which is large enough for the electrons in the 2DEG to spill over to the dielectric/(Al)GaN interface, the interface traps are quickly filled with electrons and become negatively charged. Also, Bulk traps which is very close to the interface can be filled with electrons and negatively charged. When gate bias returns to zero, the filled traps above Fermi level start to detrap. Although the traps with short time constant release electrons quickly, the traps with long time constant remain filled for a long time, resulting in the V<sub>th</sub> shift of the devices as shown in Fig. 1.7 [30].

Fig. 1.7 Band diagram of the dielectric/AlGaN/GaN MIS structure under various gate biases [30]

Fig. 1.8 (a) Schematic cross-sectional view of gate recessed MIS-HEMTs,(b) schematic of interface states and border traps in recessed AlGaN/GaNMIS-HEMTs [29]

in order to minimize the V<sub>th</sub> shift, a gate recess etching with low plasma induced damage and a high-quality gate dielectric are needed for low interface states and border traps in the gate recessed MIS-FETs as shown in Fig. 1.8. In gate recess etching, some methods have been developed for smooth and high-quality interface between the gate dielectric and etched (Al)GaN surface such as slow etch rate of (Al)GaN recipes [31], digital etching using thermal oxidation or oxygen plasma [32, 33] and TMAH wet etching [34]. Also, many studies for reducing the high interface and bulk traps in the gate dielectric have been done using various gate dielectric layers such as SiNx, Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub> and SiO2 of which various properties such as conduction and valence band offsets of dielectrics on GaN, dielectric constant and bandgap of dielectrics as shown in Fig. 1.9.

**Fig. 1.9** (a) Conduction and valence band offsets for various dielectric on GaN [35], (b) dielectric constant vs bandgap for various dielectric layers [36]

#### 1.4. Research Aims

In this research, process development and characterization of normallyoff AlGaN/GaN MIS-FETs are carried out for high power and voltage applications. The final goal of this work is to achieve high quality dielectric/(Al)GaN interface of normally-off AlGaN/GaN MIS-FETs. The detailed outline of this dissertation is described below.

In chapter 2, various etching methods for normally-off operation have been studied. Also, etching damage was evaluated by various methods such as atomic force microscopy (AFM), photoluminescence (PL) measurements, X-ray photoelectron spectroscopy (XPS) measurements and electrical properties of the recessed schottky devices. It was suggested that ALE can break through the limitations of the digital etching and continuous etching processes and enables more precise etching depth control. Also the smoothest etched surface, the highest PL intensity and N/(Al+Ga) ratio of the etched AlGaN surface and the lowest leakage current of the gate recessed schottky devices were obtained by using the ALE.

In chapter 3, normally-off AlGaN/GaN MIS-HEMTs with atomic layer deposited 5 nm SiON/16 nm HfON and with atomic layer deposited 22 nm HfON gate insulator were demonstrated. The devices using SiON also exhibited excellent pulsed I-V and dynamic on-resistance characteristics. In addition, small threshold voltage drift under positive gate bias stress was achieved due to the SiON interfacial layer.

In chapter 4, ALD AlN as an interfacial layer was developed and optimized to avoid the formation of poor-quality oxide at the dielectric/(Al)GaN interface. Also, ALD AlHfON as a bulk layer which had

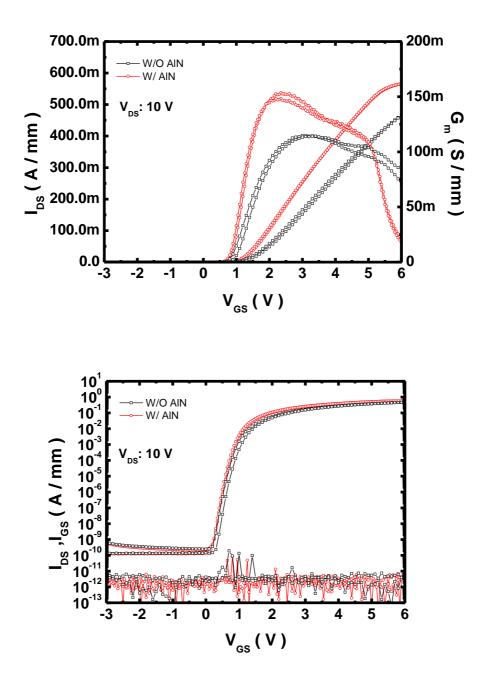

a high dielectric constant and low leakage current and high breakdown field characteristics was developed. Finally, Normally-off AlGaN/GaN MIS-FETs with 2 nm AlN/3 nm AlON/15 nm AlHfON layer were fabricated. The devices with AlN/AlON/AlHfON layer showed smaller I-V hysteresis of  $\sim$ 10 mV and high drain current density of  $\sim$ 566 mA/mm. the effective mobility, D<sub>it</sub> and threshold voltage instability characteristics were all improved by employing the ALD AlN.

#### **1.5. References**

- [1] S. Natarajan, M. Agostinelli, S. Akbar, M. Bost, A. Bowonder, V. Chikarmane, S. Chouksey, A. Dasgupta, K. Fischer, Q. Fu, T. Ghani, M. Giles, S. Govindaraju, R. Grover, W. Han, D. Hanken, E. Haralson, M. Haran, M. Heckscher, R. Heussner, P. Jain, R. James, R. Jhaveri, I. Jin, H. Kam, E. Karl, C. Kenyon, M. Liu, Y. Luo, R. Mehandru, S. Morarka, L. Neiberg, P. Packan, A. Paliwal, C. Parker, P. Patel, R. Patel, C. Pelto, L. Pipes, P. Plekhanov, M. Prince, S. Rajamani, J. Sandford, B. Sell, S. Sivakumar, P. Smith, B. Song, K. Tone, T. Troeger, J. Wiedemer, M. Yang, and K. Zhang, "A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size," *Tech. Dig. Int. Electron Devices Meet. IEDM*, vol. 2015–February, no. February, p. 3.7.1-3.7.3, 2015.

- [2] S. E. Thompson and S. Parthasarathy, "Moore's law: the future of Si microelectronics," *Mater. Today*, vol. 9, no. 6, pp. 20–25, 2006.

- [3] F. S. Corporation, "CMOS, the Ideal Logic Family," p. 10, 1983.

- [4] A. Kanale and B. J. Baliga, "Enhancing Short Circuit Capability of 1.2-kV Si IGBT Using a Gate-Source Shorted Si Depletion Mode MOSFET in Series with the Emitter," *IEEE Trans. Power Electron.*, vol. 35, no. 6, pp. 6350–6361, 2020.

- [5] R. S. Saxena and M. J. Kumar, "A new strained-silicon channel trench-gate power MOSFET: Design and analysis," *IEEE Trans. Electron Devices*, vol. 55, no. 11, pp. 3299–3304, 2008.

- [6] F. D. Bauer, "The super junction bipolar transistor: A new silicon power device concept for ultra low loss switching applications at medium to high voltages," *Solid. State. Electron.*, vol. 48, no. 5, pp. 705–714, 2004.

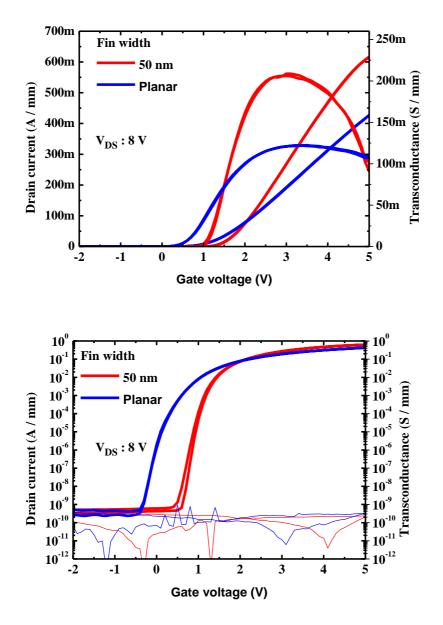

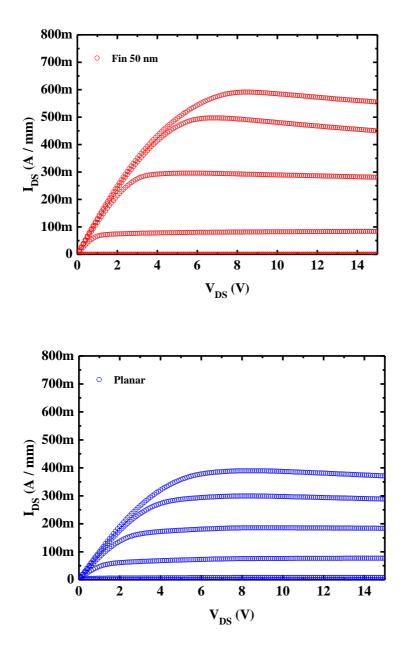

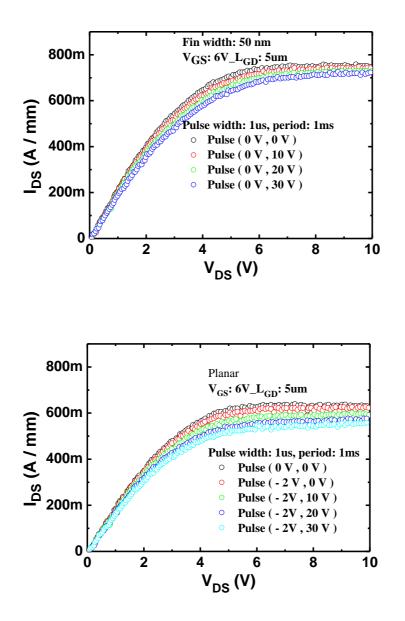

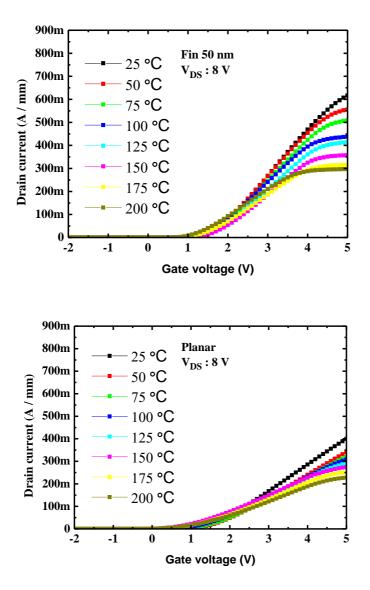

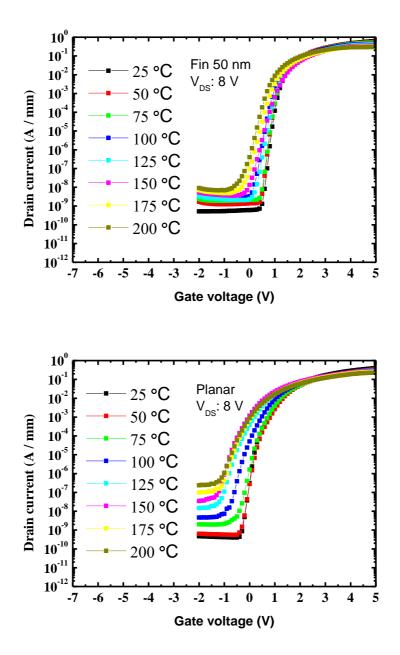

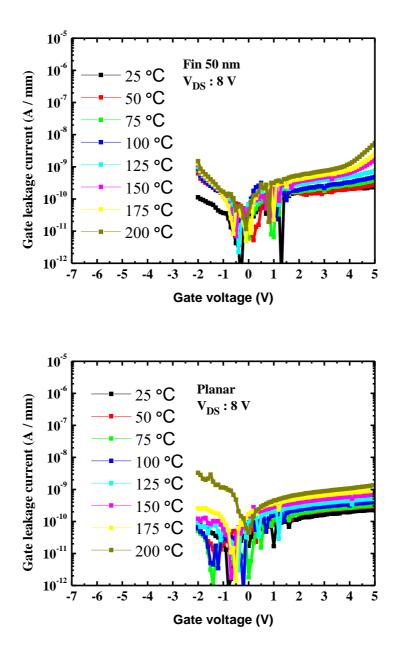

- [7] C. Wu, J. Chen, P. Han, M. Lee, K. Yang, H. Wang, P. Chang, Q. H. Luc, Y. Lin, C. Dee, A. A. Hamzah, E. Y. Chang, and A. A. Gan, "Normally-Off Tri-Gate GaN MIS-HEMTs with Power Device

Applications," *IEEE Trans. Electron Devices*, vol. 66, no. 8, pp. 3441–3446, 2019.

- [8] T. P. Chow, I. Omura, M. Higashiwaki, H. Kawarada, and V. Pala, "Smart power devices and ICs using GaAs and wide and extreme bandgap semiconductors," *IEEE Trans. Electron Devices*, vol. 64, no. 3, pp. 856–873, 2017.

- [9] H. Umezawa, M. Nagase, Y. Kato, and S. I. Shikata, "High temperature application of diamond power device," *Diam. Relat. Mater.*, vol. 24, pp. 201–205, 2012.

- [10] C. Nguyen and M. Micovic, "The state-of-the-art of GaAs and InP power devices and amplifiers," *IEEE Trans. Electron Devices*, vol. 48, no. 3, pp. 472–478, 2001.

- [11] M. Ostling, R. Ghandi, and C. M. Zetterling, "SiC power devices -Present status, applications and future perspective," *Proc. Int. Symp. Power Semicond. Devices ICs*, pp. 10–15, 2011.

- [12] S. Chowdhury, Z. Stum, Z. Da Li, K. Ueno, and T. P. Chow, "Comparison of 600V Si, SiC and GaN power devices," *Mater. Sci. Forum*, vol. 778–780, no. October 2015, pp. 971–974, 2014.

- [13] X. Liu, E. M. C. Analysis, G. Based, and P. Module, "Methodology for EMC Analysis in a GaN Based Power Module To cite this version : HAL Id : tel-01739626 Methodology for EMC Analysis in a GaN Based Power Module Méthodologie d ' Analyse de la CEM dans un Module de Puissance à Composants GaN," 2018.

- [14] O. Ambacher, J. Smart, J. R. Shealy, N. G. Weimann, K. Chu, M. Murphy, W. J. Schaff, L. F. Eastman, R. Dimitrov, L. Wittmer, M. Stutzmann, W. Rieger, and J. Hilsenbeck, "Two-dimensional electron gases induced by spontaneous and piezoelectric polarization charges in N- And Ga-face AIGaN/GaN heterostructures," *J. Appl. Phys.*, vol. 85, no. 6, pp. 3222–3233, 1999.

- [15] A. F. Wright, "Elastic properties of zinc-blende and wurtzite AIN, GaN, and InN," *J. Appl. Phys.*, vol. 82, no. 6, pp. 2833–2839, 1997.

- [16] O. Ambacher, B. Foutz, J. Smart, J. R. Shealy, N. G. Weimann, K. Chu, M. Murphy, A. J. Sierakowski, W. J. Schaff, L. F. Eastman, R. Dimitrov, A. Mitchell, and M. Stutzmann, "Two dimensional electron

gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures," *J. Appl. Phys.*, vol. 87, no. 1, pp. 334–344, 2000.

- [17] X. G. He, D. G. Zhao, and D. S. Jiang, "Formation of twodimensional electron gas at AlGaN/GaN heterostructure and the derivation of its sheet density expression," *Chinese Phys. B*, vol. 24, no. 6, 2015.

- [18] X. G. He, D. G. Zhao, and D. S. Jiang, "Formation of twodimensional electron gas at AlGaN/GaN heterostructure and the derivation of its sheet density expression," *Chinese Phys. B*, vol. 24, no. 6, 2015.

- [19] K. J. Chen and C. Zhou, "Enhancement-mode AlGaN/GaN HEMT and MIS-HEMT technology," *Phys. Status Solidi Appl. Mater. Sci.*, vol. 208, no. 2, pp. 434–438, 2011.

- [20] M. Su, C. Chen, and S. Rajan, "Prospects for the application of GaN power devices in hybrid electric vehicle drive systems," *Semicond. Sci. Technol.*, vol. 28, no. 7, 2013.

- [21] Y. Cai, Y. Zhou, K. M. Lau, and K. J. Chen, "Control of threshold voltage of AlGaN/GaN HEMTs by fluoride-based plasma treatment: From depletion mode to enhancement mode," *IEEE Trans. Electron Devices*, vol. 53, no. 9, pp. 2207–2214, 2006.

- [22] F. Roccaforte, G.Greco, R. Fiorenza and F. Iucolano, "An overview of normally-off GaN-based high electron mobility transistors, Materials, 12. 10, 2019.

- [23] I. Hwang, J. Kim, H. S. Choi, H. Choi, J. Lee, K. Y. Kim, J. B. Park, J. C. Lee, J. Ha, J. Oh, J. Shin, and U. I. Chung, "P-GaN Gate HEMTs with tungsten gate metal for high threshold voltage and low gate current," *IEEE Electron Device Lett.*, vol. 34, no. 2, pp. 202–204, 2013.

- [24] X. Sun, Y. Zhang, K. S. C. T. Palacios, and T. P. Ma, "Impacts of Fluorine-treatment on E-mode AlGaN / GaN MOS-HEMTs," no. V, pp. 438–441, 2014.

- [25] S. Huang, Q. Jiang, K. Wei, G. Liu, J. Zhang, X. Wang, Y. Zheng, B. Sun, C. Zhao, H. Liu, Z. Jin, X. Liu, H. Wang, S. Liu, Y. Lu, C. Liu,

S. Yang, Z. Tang, J. Zhang, Y. Hao, and K. J. Chen, "High-temperature low-damage gate recess technique and ozone-assisted ALD-grown Al2O3 gate dielectric for high-performance normally-off GaN MIS-HEMTs," *Tech. Dig. - Int. Electron Devices Meet. IEDM*, vol. 2015–February, no. February, p. 17.4.1-17.4.4, 2015.

- [26] A. Lorenz, J. Derluyn, J. Das, K. Cheng, S. Degroote, F. Medjdoub, M. Germain, and G. Borghs, "Influence of thermal anneal steps on the current collapse of fluorine treated enhancement mode SiN/AlGaN/GaN HEMTs," *Phys. Status Solidi Curr. Top. Solid State Phys.*, vol. 6, no. SUPPL. 2, pp. 996–998, 2009.

- [27] Z. Liu, X. Huang, F. C. Lee, and Q. Li, "Package parasitic inductance extraction and simulation model development for the high-voltage cascode GaN HEMT," *IEEE Trans. Power Electron.*, vol. 29, no. 4, pp. 1977–1985, 2014.

- [28] T. L. Wu, J. Franco, D. Marcon, B. De Jaeger, B. Bakeroot, X. Kang, S. Stoffels, M. Van Hove, G. Groeseneken, and S. Decoutere, "Positive bias temperature instability evaluation in fully recessed gate GaN MIS-FETs," *IEEE Int. Reliab. Phys. Symp. Proc.*, vol. 2016– September, no. 5, p. 4A21-4A26, 2016.

- [29] T. L. Wu, D. Marcon, B. Bakeroot, B. De Jaeger, H. C. Lin, J. Franco, S. Stoffels, M. Van Hove, R. Roelofs, G. Groeseneken, and S. Decoutere, "Correlation of interface states/border traps and threshold voltage shift on AlGaN/GaN metal-insulator-semiconductor highelectron-mobility transistors," *Appl. Phys. Lett.*, vol. 107, no. 9, pp. 2–6, 2015.

- [30] Y. Lu, S. Yang, Q. Jiang, Z. Tang, B. Li, and K. J. Chen, "Characterization of VT-instability in enhancement-mode Al2O3-AlGaN/GaN MIS-HEMTs," *Phys. Status Solidi Curr. Top. Solid State Phys.*, vol. 10, no. 11, pp. 1397–1400, 2013.

- [31] G. Algan, G. Hemt, W. Wang, Y. Li, C. Lin, Y. Chan, S. Member, G. Chen, and J. Chyi, "Low Damage, Cl 2 -Based Gate Recess Etching for," vol. 25, no. 2, pp. 52–54, 2004.

- [32] S. Lin, M. Wang, F. Sang, M. Tao, C. P. Wen, B. Xie, M. Yu, J. Wang,Y. Hao, W. Wu, J. Xu, K. Cheng, and B. Shen, "A GaN HEMT

structure allowing self-terminated, plasma-free etching for highuniformity, high-mobility enhancement-mode devices," *IEEE Electron Device Lett.*, vol. 37, no. 4, pp. 377–380, 2016.

- [33] S. D. Burnham, K. Boutros, P. Hashimoto, C. Butler, D. W. S. Wong, M. Hu, and M. Micovic, "Gate-recessed normally-off GaN-on-Si HEMT using a new O2- BCl3 digital etching technique," *Phys. Status Solidi Curr. Top. Solid State Phys.*, vol. 7, no. 7–8, pp. 2010–2012, 2010.

- [34] D. H. Son, Y. W. Jo, C. H. Won, J. H. Lee, J. H. Seo, S. H. Lee, J. W. Lim, J. H. Kim, I. M. Kang, S. Cristoloveanu, and J. H. Lee, "Normally-off AlGaN/GaN-based MOS-HEMT with self-terminating TMAH wet recess etching," *Solid. State. Electron.*, vol. 141, no. November 2017, pp. 7–12, 2018.

- [35] R. D. Long and P. C. McIntyre, "Surface preparation and deposited gate oxides for gallium nitride based metal oxide semiconductor devices," *Materials (Basel).*, vol. 5, no. 7, pp. 1297–1335, 2012.

- [36] R. D. Clark, "Emerging applications for high K materials in VLSI technology," *Materials (Basel).*, vol. 7, no. 4, pp. 2913–2944, 2014.

## Chapter 2. Development and Evaluation of Low Damage Etching Processes

#### **2.1. Introduction**

As mentioned in the former section, the gate recess is a promising technique for normally-off operation because it is easier to implement than other approaches and ensure normally-off operation. Due to the high chemical inertness of GaN, many dry etching techniques and plasma chemistries have been used for etching of GaN based materials using reactive ion etching (RIE) [1,2], electron-cyclotron-resonance reactive ion etching [3,4] and inductively coupled plasma reactive ion etching (ICP-RIE) [5-7] as shown in Fig. 2.1. However, plasma induced damage in the gate recess process using such dry etching methods can generates trapping centers on the etched surface and forms a nonstoichiometric surface due to preferential loss of nitrogen [8-10], decreasing the electron mobility and increasing the leakage current of the fabricated devices [8, 11].

**Fig. 2.1** Various dry etching methods (a) reactive ion etching (RIE), (b) electron-cyclotron-resonance reactive ion etching, (c) inductively coupled plasma reactive ion etching (ICP-RIE) [12]

For low etching damage, many research groups have studied various etching methods and resulted in great achievements [13-15]. However, efforts to reduce the etching damage are still needed for improving the electrical performance and reliability of the devices.

# 2.2. Various Evaluation Methods of Etching Damage

Dry etching is widely used for AlGaN/GaN HFETs due to the limitation of wet chemical etching of (Al)GaN. However, plasma induced damage in the dry etching process can affects the electrical properties of the devices such as channel mobility, leakage current, on-current and  $V_{th}$  instability due to formation of traps on the etched surface [16-17]. Therefore, to improve the device performance, it is necessary to clarify the influence and remove etching damage.

Etching damage can be evaluated by various methods such as atomic force microscopy (AFM), photoluminescence (PL) measurements, X-ray photoelectron spectroscopy (XPS) measurements and electrical properties of the recessed schottky devices. Generally, plasma induced damage create nitrogen vacancies of shallow donor levels, resulting in a nonstoichiometric surface [18]. some research groups have used AFM to quantify the surface morphology as root-mean-square (rms) roughness as shown in Fig. 2.2 because rough etch morphology often indicates a nonstoichiometric surface [1, 19].

RMS roughness: 0.68 nm

**Fig. 2.2** AFM images of GaN surfaces (a) After BCl<sub>3</sub>/Cl<sub>2</sub> plasma dry etching (b) After BCl<sub>3</sub>/Cl<sub>2</sub> plasma dry etching in ICP system [16]

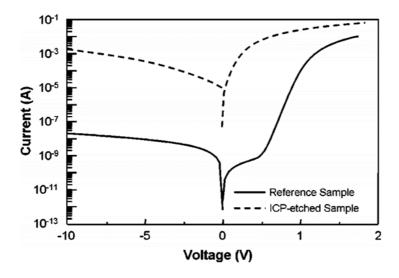

Also, etching damage can be investigated by observing the electrical properties of recessed schottky devices [8, 16]. As shown in Fig. 2.3.

**Fig. 2.3** I-V characteristics of Schottky diodes fabricated on both the reference and ICP-etched surfaces [8]

The leakage current of Schottky devices by the dry etching can be explained by tunneling of electrons via plasma induced traps because the traps provide a conducting path with lower energy barrier [8]. Tunneling of electrons through the plasma induced traps is shown in Fig. 2.4.

**Fig. 2.4** Schematic illustration of electron transport through the interface of metal with ICP -etched GaN: (a) forward bias condition and (b) reverse bias condition [8]

Another method for evaluation of etching damage is to investigate atomic concentration ratio of N/Ga at the etched surface. Physical sputtering of dry etching process removes N atoms preferentially compared to Ga atoms [20]. X-ray photoelectron spectroscopy (XPS) surface analysis can be performed to investigate the surface composition as shown in table 2.1.

|            | As grown<br><i>n-</i> GaN | Dry etched <i>n</i> -GaN<br>(ICP: 500 W,<br>rf chuck: 250 W,<br>and 33% $Cl_2$<br>in $Cl_2/BCl_3$ ) | Etched <i>n</i> -GaN subjected<br>to HF treatment and RTA<br>in $N_2$ ambient at 900 °C |

|------------|---------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Ga (%)     | 28.5±0.2                  | $23.3 \pm 0.2$                                                                                      | $28.1 \pm 0.2$                                                                          |

| N (%)      | $17.2 \pm 0.2$            | $11.1 \pm 0.2$                                                                                      | $16.3 \pm 0.2$                                                                          |

| C (%)      | $38.5 \pm 0.2$            | $34.8 \pm 0.2$                                                                                      | $20.8 \pm 0.2$                                                                          |

| O (%)      | $15.6 \pm 0.2$            | $30.6 \pm 0.2$                                                                                      | $24.6 \pm 0.2$                                                                          |

| Ga/N ratio | $1.6 \pm 0.1$             | $2.1 \pm 0.1$                                                                                       | $1.7 \pm 0.1$                                                                           |

Table 2.1 Surface composition of GaN during different processing steps

estimated from the XPS data [10]

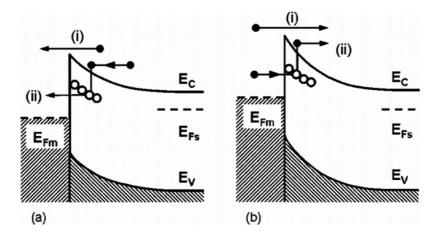

Additionally, photoluminescence (PL) studies can be used for evaluation of etching damage because plasma induced damage from dry etching process introduce non-radiative centres. photoluminescence intensity is very sensitive to surface recombination [20]. Many research groups have used photoluminescence measurement to evaluate etching damage [20-23] as shown in Fig. 2.5.

**Fig. 2.5** Photoluminescence spectra at 20 K of an unetched GaN sample and samples subject to various plasma exposures [20]

#### 2.3. Low-Damage Dry Etching Methods

## 2.3.1. Inductively Coupled Plasma– Reactive Ion Etching Using BCl3/Cl2 gas mixture

Dry etching was done using a inductively coupled plasma -Reactive Ion Etching system. It is capable of accommodating 6-inch wafer and can control source and bias power of 13.56 MHz independently. The process chamber was evacuated using a turbo pump and has a helium backside cooling system. The ICP-RIE etcher used in the following experiments is shown in Fig. 2.6.

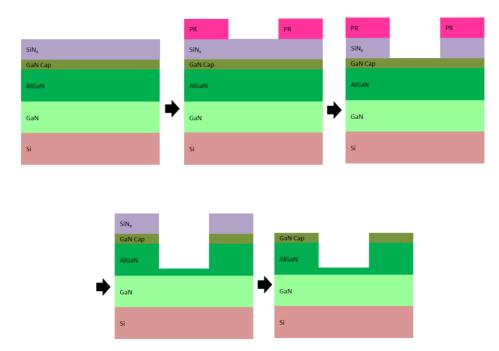

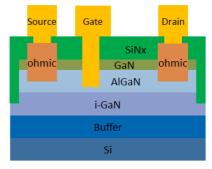

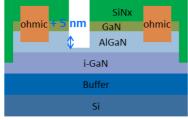

To estimate the etch rate in each etching condition, AlGaN/GaN on Si epi-wafers were used. The epi structure consists of a Si substrate, a carbondoped GaN buffer layer, UID GaN channel layer and an AlGaN barrier layer with a GaN cap layer. The samples for estimation of etch rate were prepared as follow: SiN<sub>x</sub> layer of 60 nm was deposited on the epi-wafers as a hard mask and patterned using optical lithography and reactive ion etching (RIE) etching using SF<sub>6</sub> gas as shown in Fig. 2.7. After dry etching, the SiN<sub>x</sub> mask layer was removed using the dilute hydrofluoric acid (DHF). The etched depth of the samples was measured by atomic force microscopy (AFM).

- Source power: 13.56 MHz

- Bias power: 13.56 MHz

- Controllable DC bias

- Helium backside cooling system

- Automatic loadlock

### Fig. 2.6 Configuration of the ICP-RIE system in ISRC

Fig. 2.7 Process flow for estimation of etch rate.

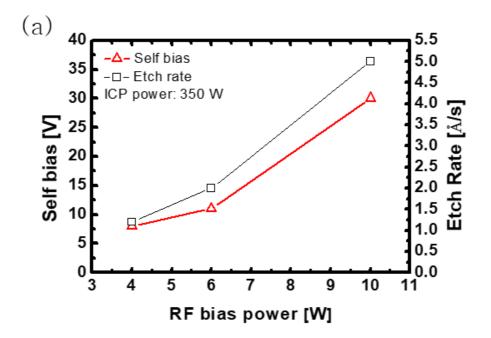

To optimize the etching condition of (Al)GaN, BCl<sub>3</sub>/Cl<sub>2</sub> gas mixture was used. The temperature of chuck which samples is placed on was maintained at 5°C with a chiller system. ICP power and RF bias power are controlled independently at 13.56MHz. It is important to reduce the DC self-bias because it increases ion bombardment energy that can result in plasma induced damage [24-27]. The DC self-bias is strong function of RF bias power and the decreasing trend of DC self-bias was shown as the ICP power increases. It is mainly due to the enhanced ion density at higher ICP power [28]. Detailed results of etching according to the ICP power and RF bias power is well described in Fig. 2.8.

**Fig. 2.8** Self bias and etch rate as functions of (a) RF bias power and (b) ICP power

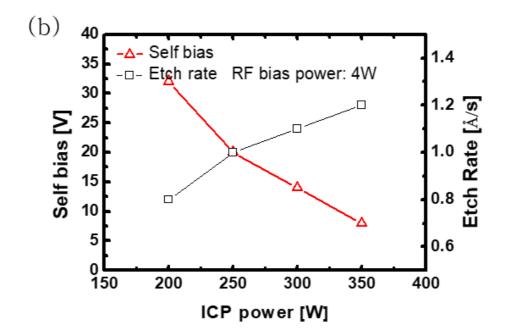

The surface morphology of etching conditions as a function of RF bias power is shown in Fig. 2.9. It is seen that RMS roughness increases with the increasing the RF bias power. It is suggested that the low DC self-bias resulted in the low physical bombardment effect, leading to the smooth surface morphology of the etched surface [29]. The smallest RMS value of 0.28 nm is obtained at the RF bias power of 4 W and the ICP power of 350 W. The lower RF bias power and higher ICP power were not considered due to unstable etch rate and reflected power in those conditions.

**Fig. 2.9** AFM images as functions of RF bias power (a) 4 W, (b) 6 W and (c) 10 W (ICP power: 350 W)

## 2.3.2. Digital Etching Using Plasma Asher and HCl

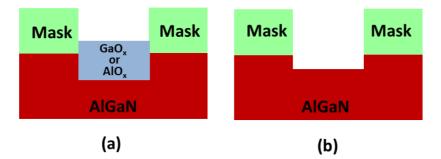

As discussed in the former section, the conventional dry etching using the  $BCl_3/Cl_2$  gas mixture has a possibility of damage to the etched surface and limitation to reduce etching damage. Recently, the digital etching consisting of plasma oxidation and wet etching of the oxide has been studied for low etching damage [14, 30] as shown in Fig 2.10.

O<sub>2</sub> plasma oxidation Removal of the oxide using HCl

**Fig. 2.10** The process of digital etching. (a) plasma oxidation and (b) removal of the oxide using HCl

The digital etching technique can reduce etching damage of the etched surface and easily control the recess depth. Conventionally, plasma oxidation in digital etching has been performed using the reactive ion etch (RIE) or inductively coupled plasma etch (ICP). However, as shown in Fig. 2.11, we used microwave plasma asher for plasma oxidation because microwave-excited plasma is characterized high density and low plasma induced damage [31].

- Manufacturer: Plasma-finish

- Model: V15G

- Rated power output: 300 W

- Frequency: 2.45 GHz

Fig. 2.11 The image of microwave plasma asher which is used for plasma oxidation

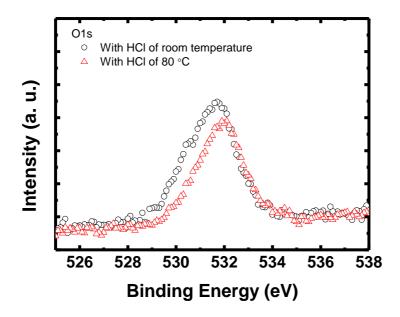

Also, After plasma oxidation of AlGaN samples, HCl:H<sub>2</sub>O (1:3) at 80 °C was used for the removal of oxide because high temperature HCl was more effective in removing the oxide than room temperature HCl. As shown in Fig. 2.12, the lower O1s peak intensity was observed from the AlGaN surface treated with HCl at 80 °C than that treated with HCl at room temperature.

**Fig. 2.12** XPS spectra of O1s from the AlGaN surfaces which are treated with HCl at room temperature and HCl at 80 °C, respectively for 5 minutes after plasma oxidation

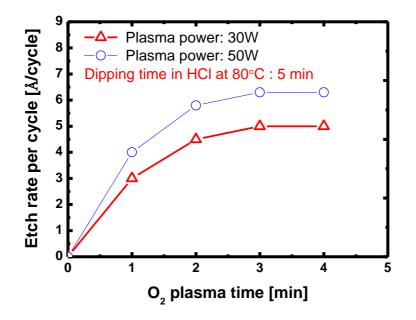

To study the effect of the  $O_2$  plasma time,  $O_2$  plasma oxidation of various times were carried out at a fixed dipping time in HCl. As shown in Fig. 2.13, the etch rate per cycle increased with  $O_2$  plasma time up to 3 minutes. Above 3 minutes, the etch rate per cycle remained constant.

**Fig. 2.13** The etch rate per cycle for a fixed dipping time of 5 minutes in HCl at 80 °C, varying oxygen plasma time and plasma power

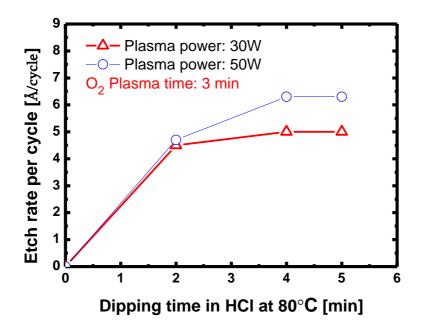

The etch rate per cycle for a fixed plasma oxidation time of 3 minutes and varying dipping time in HCl at 80 °C was evaluated. The etch per cycle increased by increasing the dipping time in HCl and remained constant at 4 minutes as shown in Fig. 2.14.

**Fig. 2.14** The etch rate per cycle for a fixed oxygen plasma time of 3 minutes, varying dipping time in HCl at 80 °C and plasma power

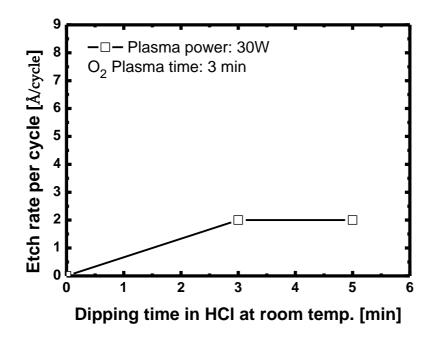

The etch rate per cycle for a fixed plasma oxidation time of 3 minutes and varying dipping time in HCl at room temperature was also evaluated to study the temperature effect of HCl. The etch per cycle increased by increasing the dipping time in HCl and remained constant at 3 minutes as shown in Fig. 2.15. However, the etch rate per cycle was lower than that in HCl at 80 °C which shows high temperature HCl was more effective in removing the oxide than room temperature HCl.

**Fig. 2.15** The etch rate per cycle for a fixed oxygen plasma time of 3 minutes and varying dipping time in HCl at room temperature

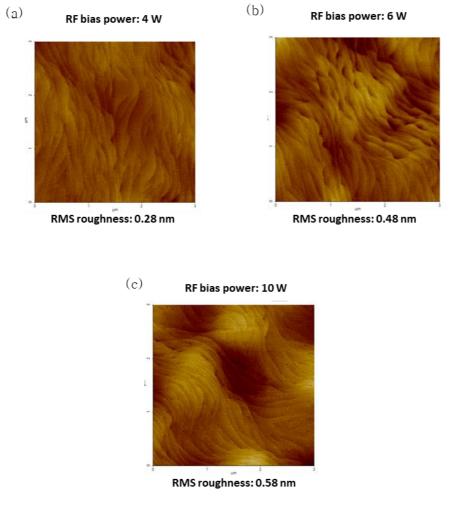

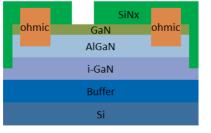

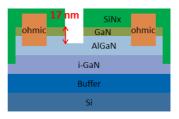

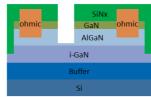

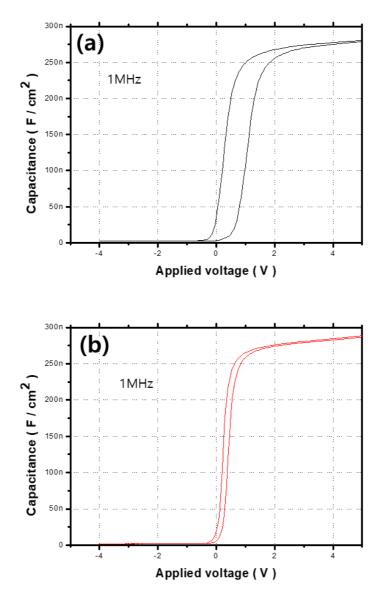

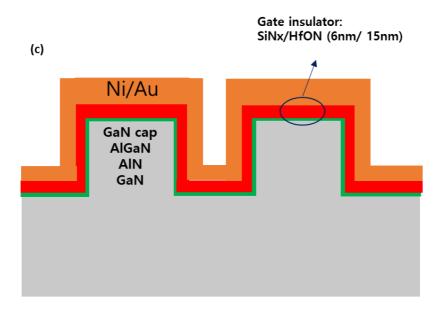

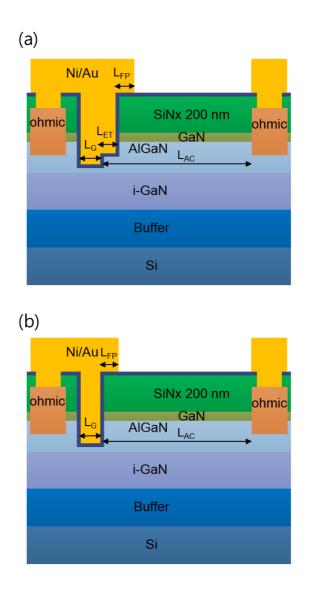

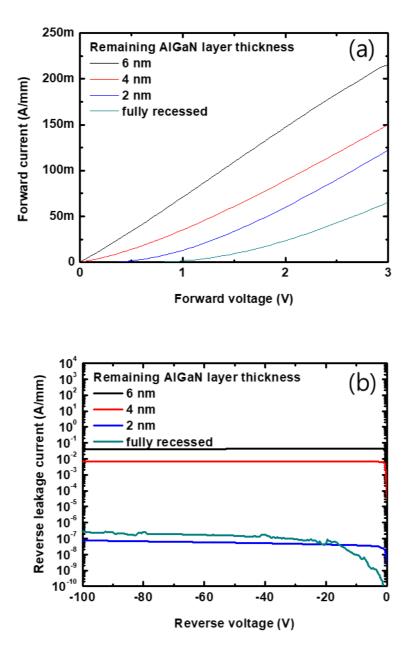

To evaluate etching damage of the digital etching using asher and HCl, gate recessed schottky devices are fabricated. We used a epi-wafer grown by metal-organic chemical vapor deposition consisting of a 10nm SiN<sub>x</sub> in-situ capping layer, a 3.8nm GaN capping layer, a 22.1nm undoped AlGaN barrier layer, a 490nm GaN channel layer, a 4450nm GaN buffer and a Si (111) substrate. The device fabrication was begun by solvent cleaning. The ohmic contacts were formed with partially recessed using BCl<sub>3</sub>/Cl<sub>2</sub> plasma, Ti/Al/Ni/Au metallization and rapid thermal annealing at 830 °C in N<sub>2</sub> ambient. The contact resistance was 0.7  $\Omega$ ·mm, which was measured using the transmission line method (TLM) with contact spacings of 2, 4, 6, 8 and 12 um. After MESA isolation using BCl<sub>3</sub>/Cl<sub>2</sub> based inductively coupled

plasma reactive ion etch (ICP-RIE), the surface cleaning was carried out using a buffered oxide etch solution (BOE, HF :  $NH_4F = 1 : 30$ ) for 1 minute and N<sub>2</sub> plasma treatment for 2 minutes with a microwave plasma system, followed by deposition of SiN<sub>x</sub> film as a passivation layer. The gate-recess regions were patterned and SiN<sub>x</sub> opening was performed with SF<sub>6</sub> based reactive ion etching (RIE) at 20 W. After gate-recess and pad opening process, Ni/Au (40 nm/ 250 nm) gate metal was deposited with e-gun evaporation. Detailed fabrication process for the gate recessed schottky devices was described in Fig. 2.16.

| SiNx<br>GaN<br>AlGaN |

|----------------------|

| i-GaN                |

| Buffer               |

| Si                   |

1. Surface cleaning

| ohmic | SiNx<br>GaN<br>AlGaN | ohmic |

|-------|----------------------|-------|

|       | i-GaN                |       |

|       | Buffer               |       |

|       | Si                   |       |

3. Mesa isolation

| ohmic | SiNx<br>GaN<br>AlGaN | ohmic |

|-------|----------------------|-------|

|       | i-GaN                |       |

|       | Buffer               |       |

|       | Si                   |       |

2. Ohmic process

|       | SiN    | İx    |

|-------|--------|-------|

| ohmic | GaN    | ohmic |

|       | AlGaN  |       |

| •     | i-GaN  |       |

|       | Buffer |       |

|       | Si     |       |

4. Passivation

5. SiNx open

7. SiNx open

6. Gate recess

8. Gate metallization (Ni/Au)

Fig. 2.16 Fabrication process for the gate recessed schottky devices

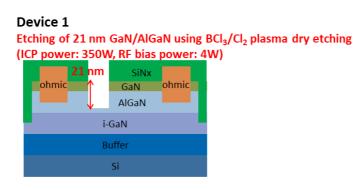

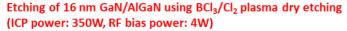

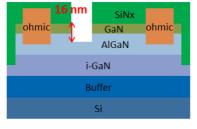

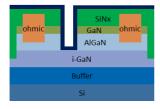

The gate-recess was performed using two methods. The first method was only  $BCl_3/Cl_2$  based dry etching, while the second method was a combination of  $BCl_3/Cl_2$  based dry etching and digital etching using asher and HCl as shown in Fig. 2.17.

#### Device 2

Additional etching of 5 nm AlGaN using the digital etching using asher and HCl (Microwave plasma power: 30W)

Fig. 2.17 The gate-recess processes for the gate recessed schottky devices

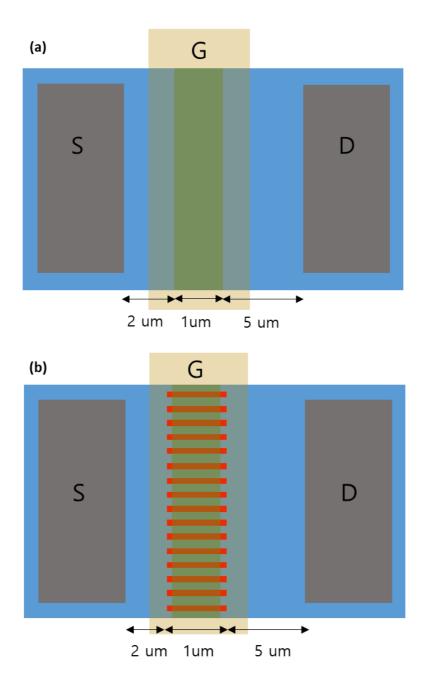

The gate length, source to gate distance, gate to drain distance and gate width of the fabricated devices were 2, 2, 15 and 100 um, respectively as shown in Fig. 2.18.

Fig. 2.18 The schematic cross section and dimensions of the fabricated devices

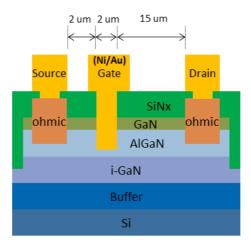

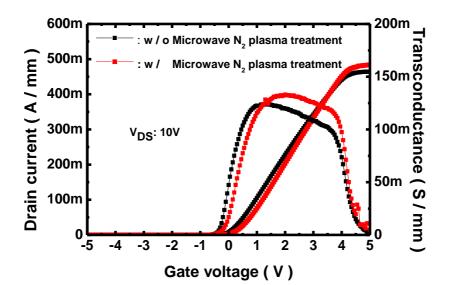

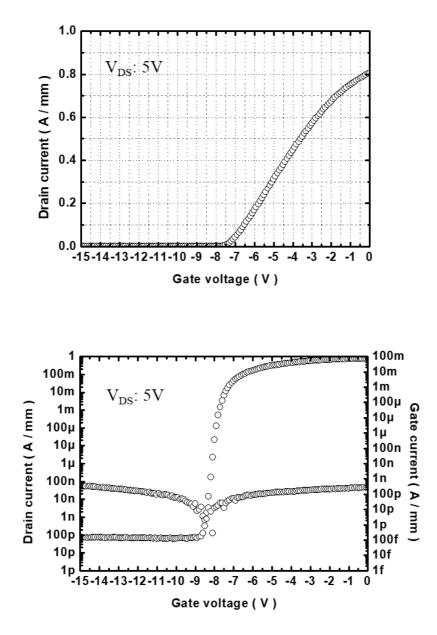

Fig. 2.19 shows I-V characteristics of the gate recessed Schottky devices for the only BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching and the combination of BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching and digital etching using asher and HCl. The reverse leakage current of the device with digital etching using asher and HCl was lower than that using only BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching, showing low etching damage of the device using the digital etching.

**Fig. 2.19** I-V characteristics of the fabricated gate recessed Schottky devices. (a) drain current and (b) gate current

We also investigated the photoluminescence characteristics of three GaN samples. one sample was etched by the  $BCl_3/Cl_2$  based dry etching, another sample was etched by the digital etching using asher and HCl and the other sample was kept unetched as a control sample. The etching depth was ~5 nm for samples. For the photoluminescence experiments, we used a 266 nm laser source with a power of  $2W/cm^2$ . Fig. 2.20 shows the PL spectra of the three samples.

Fig. 2.20 PL characteristics for the samples.

The sample etched by the digital etching using asher and HCl showed the higher band edge peak compared to the sample etched by the BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching. This suggests that the digital etching produces less plasma-induced damage on the GaN surface than the BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching.

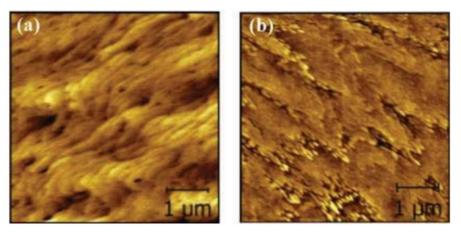

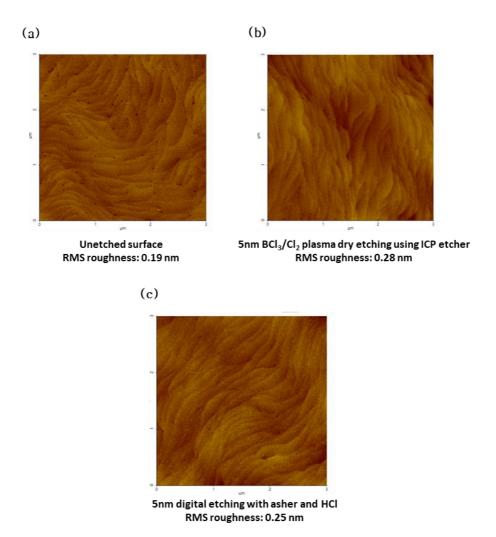

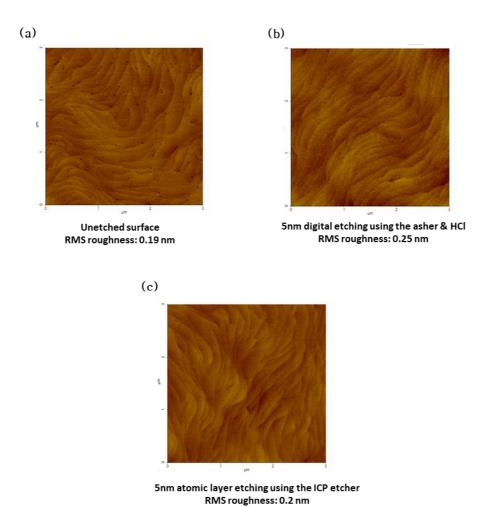

Fig. 2.21 shows atomic force microscopy (AFM) images of a 3 um x

3um area of GaN and AlGaN surface (a) before etching (GaN) (b) after ~5 nm etching by the BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching (AlGaN surface) and (c) ~5 nm etching by the digital etching using asher and HCl (AlGaN surface). The used epi structure consists of a Si substrate, a carbon-doped GaN buffer layer, UID GaN channel layer and an AlGaN barrier layer with a GaN cap layer. The root mean square (RMS) surface roughnesses of the surface unetched, the surface etched by the BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching and the surface etched by the digital etching were 0.19, 0.28 and 0.25 nm respectively. This result indicates the low plasma-induced damage characteristics of the digital etching.

**Fig. 2.21** Atomic force microscopy (AFM) images of a 3um x 3um area. (a) before etching, (b) after ~5 nm etching by the  $BCl_3/Cl_2$  based dry etching using ICP etcher and (c) ~5 nm etching by the digital etching using asher and HCl

We also performed X-ray photoelectron spectroscopy (XPS) measurements on the etched samples as an evaluation method of etching damage. An epi-wafer consisting of a Si substrate, a carbon-doped GaN buffer layer, UID GaN channel layer and an AlGaN barrier layer with a GaN cap layer was used for XPS analysis. one sample was etched by the BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching and the other sample was etched by the digital etching. The etched depth of samples was ~5 nm. The XPS results of the etched AlGaN surfaces are shown in Table 2.2.

|        | BCl <sub>3</sub> /Cl <sub>2</sub> based<br>dry etching | Digital etching using<br>asher & HCl |

|--------|--------------------------------------------------------|--------------------------------------|

| Al (%) | 9.6                                                    | 8.6                                  |

| Ga (%) | 28.7                                                   | 25.8                                 |

| N (%)  | 29.9                                                   | 28.2                                 |

| 0 (%)  | 5.4                                                    | 8                                    |

| C (%)  | 26.4                                                   | 29.4                                 |

**Table 2.2** The XPS results of the etched AlGaN surfaces by the  $BCl_3/Cl_2$  based dry etching and the digital etching using asher and HCl

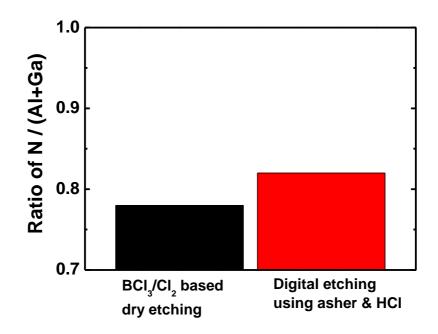

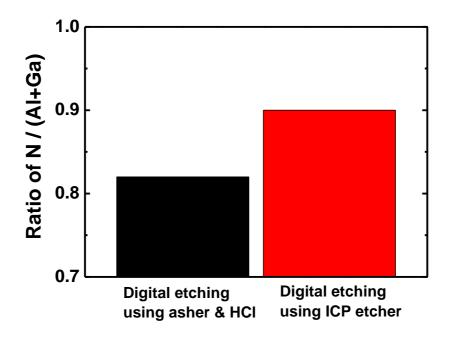

Fig. 2.22 also show the N/(Al+Ga) ratios for the two samples. We found that the etched sample by the digital etching using asher and HCl had N/(Al+Ga) ratio of 0.82, while the etched sample by the BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching had less nitrogen on the AlGaN surface (N/(Al+Ga)=0.78). High N/(Al+Ga) ratio of the sample etched by the digital etching indicates that the digital etching technique has less physical sputtering component and lower etching damage characteristics compared to the BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching

Fig. 2.22 N/(Al+Ga) ratios of the etched samples by the  $BCl_3/Cl_2$  based dry etching and the digital etching using asher and HCl

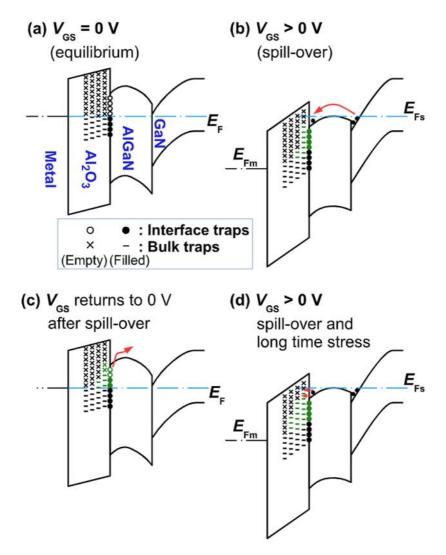

## 2.3.3. Atomic Layer Etching Using Inductively Coupled Plasma – Reactive Ion Etching System

The digital etching process using  $O_2$  plasma asher for oxidation of AlGaN and HC1 : H<sub>2</sub>O solution for removal of the formed oxide layer has been presented, but it is labor-consuming and take much process time due to the low etch rate (~0.5 nm/cycle) compared to other etching processes. The recent studies on atomic layer etching (ALE) have demonstrated that Atomic layer etching using  $O_2$  and BCl<sub>3</sub> gases could reduce etching damage and improve the surface roughness [32-34]. Also, ALE can break through the limitations of continuous etching processes and enables more precise etching depth control. However, It is important to have a self-limiting characteristics in ALE resulting in the good linearity between the etching depth and the number of cycles. Also Efforts to reduce the dc self-bias in ALE are needed for low etching damage.

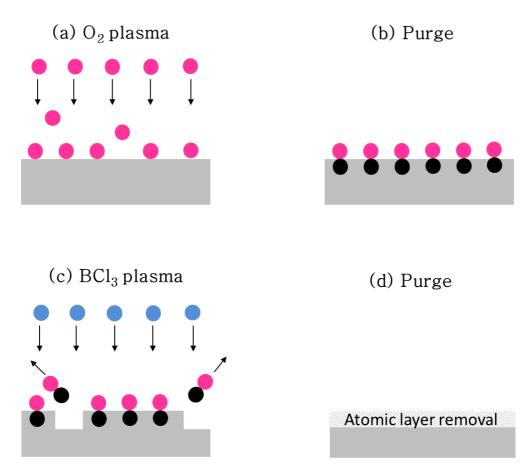

We studied a ALE using the ICP-RIE system and O<sub>2</sub> and BCl<sub>3</sub> gases for AlGaN etching. The ALE is composed of four steps as shown in Fig. 2.23.

**Fig. 2.23** Schematic illustration of one cycle of ALE. (a)  $O_2$  plasma, (b) purge, (c) BCl<sub>3</sub> plasma and (d) purge.

The AlGaN was oxidized with O<sub>2</sub> plasma and a purge step was carried out to remove residual gases and radicals in the chamber. Then, the oxidized layer was removed with BCl<sub>3</sub> plasma and a purge step was carried out.

The ALE process was performed in the ICP-RIE system, operating at a 13.56MHz RF bias power and a separate 13.56MHz RF ICP power. The temperature of the chuck was room temperature and the chamber pressure of the  $O_2$  plasma step and the  $O_2$  flow rate were 50mtorr and 50sccm respectively. the chamber pressure of the BCl<sub>3</sub> plasma step and the BCl<sub>3</sub> flow rate were 10mtorr and 10sccm respectively.

To estimate the etch rate of the ALE, AlGaN/GaN on Si epi-wafers consisting of a Si substrate, a carbon-doped GaN buffer layer, UID GaN channel layer and an AlGaN barrier layer with a GaN cap layer were used. Also, a  $SiN_x$  was used as a mask layer. After the ALE, the  $SiN_x$  mask layer was removed using the dilute hydrofluoric acid (DHF). The etched depth of the samples was measured by atomic force microscopy (AFM).

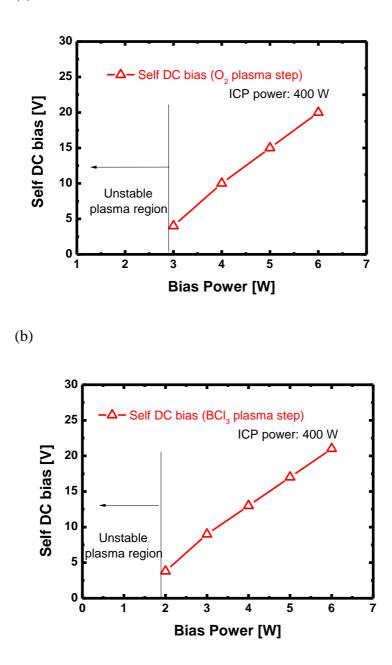

To study the effect of the bias power on the DC self-bias, for varying bias power and a fixed ICP power of 400W, the DC self-biases were investigated. The results are shown in Fig. 2.24

**Fig. 2.24** The DC self-biases for varying bias power and a fixed ICP power of 400W. (a) O<sub>2</sub> plasma step and (b) BCl<sub>3</sub> plasma step

The DC self-bias increased with an increase of the bias power. We chose the bias power of 3W in the  $O_2$  plasma step and the bias power of 2W at the BCl<sub>3</sub> plasma step for the ALE process because each plasma step was unstable at lower bias powers. As shown in Fig. 2.25, the effect of the ICP power on the DC self-bias was also investigated for varying ICP power and a fixed bias power. The DC self-bias decreased with an increase of the ICP power at the both plasma steps. This decreasing trend of the DC self-bias is mainly due to the enhanced ion density at higher ICP power [28]. We chose the ICP power of 400W at both plasma steps for the ALE process.

**Fig. 2.25** The DC self-biases for varying ICP power and the fixed bias power. (a)  $O_2$  plasma step and (b) BCl<sub>3</sub> plasma step

The effect of the pressure at the both plasma steps was studied at the fixed ICP power of 400W and the fixed bias power of 3W ( $O_2$  plasma step) or 2W (BCl<sub>3</sub> plasma step) as shown in Fig. 2.26. The DC self-bias decreased with an increase of the pressure at the  $O_2$  plasma step. However, the DC self-bias increased with an increase of the pressure at the BCl<sub>3</sub> plasma step. For the low DC self-bias, the pressure of 50mtorr and 10mtorr were chosen for the  $O_2$  plasma step and the BCl<sub>3</sub> plasma step, respectively.

**Fig. 2.26** The DC self-biases for varying pressure and the fixed bias and ICP power. (a) O<sub>2</sub> plasma step and (b) BCl<sub>3</sub> plasma step

As mentioned above, It is important to have a self-limiting characteristics in ALE, resulting in the good linearity between the etching depth and the number of cycles. For varying bias power and the fixed ICP power of 400W with BCl<sub>3</sub> plasma, etch rates are investigated as shown in Fig. 2.27. The AlGaN layer is not etched at the bias power of 2W and the etch rates increased with the increase of the bias power. It indicates that our ALE technique is a self-limiting etch process at the bias power of 2W with BCl<sub>3</sub> plasma.

**Fig. 2.27** Etch rates for varying bias power and the fixed ICP power of 400W with BCl<sub>3</sub> plasma

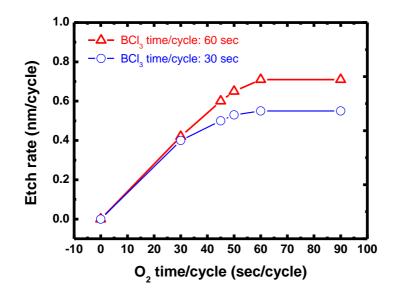

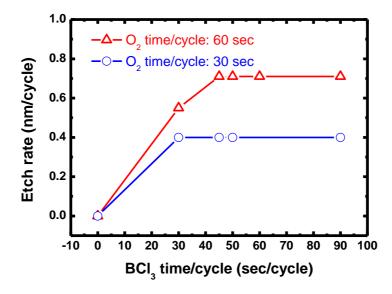

Fig. 2.28 shows that the etch rate per cycle for varying  $O_2$  plasma time per cycle and each different BCl<sub>3</sub> plasma time per cycle. The etch rate increased with  $O_2$  plasma time per cycle up to 60 sec. Above 60 sec of  $O_2$ plasma time per cycle, the etch rate per cycle remained fairly constant at the both BCl<sub>3</sub> plasma times. The etch rate per cycle at the BCl<sub>3</sub> plasma time of 60sec was higher than that at BCl<sub>3</sub> plasma time of 30sec. Fig. 2.29 shows that the etch rate per cycle for varying BCl<sub>3</sub> plasma time per cycle and each different  $O_2$  plasma time per cycle. The etch rate increased with BCl<sub>3</sub> plasma time per cycle up to 45 sec at the  $O_2$  plasma time per cycle. Above 45sec of BCl<sub>3</sub> plasma time per cycle, the etch rate per cycle became saturated. The etch rate per cycle at the  $O_2$  plasma time of 60sec was higher than that at the  $O_2$  plasma time of 30sec.

Fig. 2.28 Etch rates for varying  $O_2$  plasma time and each different  $BCl_3$  plasma time per cycle

Fig. 2.29 Etch rates for varying  $BCl_3$  plasma time and each different  $O_2$  plasma time per cycle

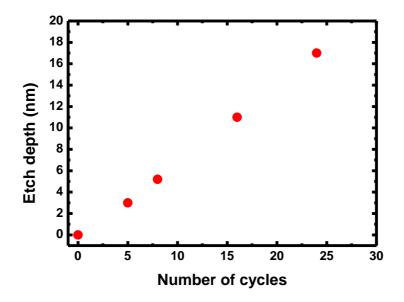

The linearity of the ALE was investigated as shown in Fig. 2.30. the result showed a good linearity between the etched depth versus the number of cycles, indicating that the ALE technique had good controllability in terms of the etch depth.

Fig. 2.30 The ALE linearity between the etch depth and the number of cycles

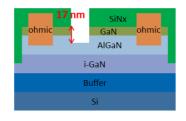

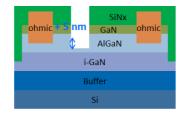

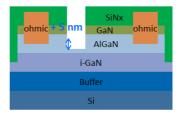

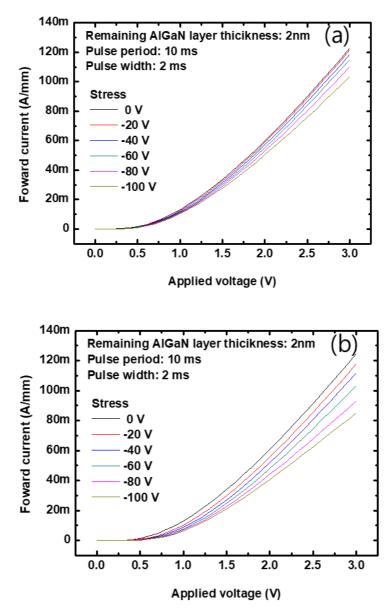

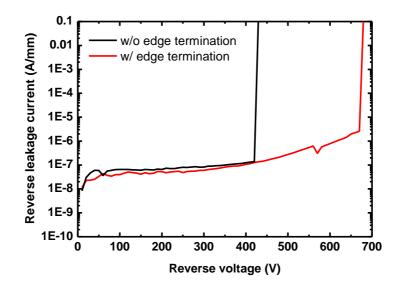

To evaluate etching damage of the ALE, gate recessed schottky devices are fabricated. We used an epi-wafer grown by metal-organic chemical vapor deposition consisting of a 9.9nm SiN<sub>x</sub> in-situ capping layer, a 3.7nm GaN capping layer, a 22nm undoped AlGaN barrier layer, a 490nm GaN channel layer, a 4450nm GaN buffer and a Si (111) substrate. Because the epi-wafer had a different epi-structure with that used in the previous section 2.3.2, we fabricated gate recessed schottky devices using the digital etching with asher and HCl again as the reference devices. The fabrication process for the gate recessed Schottky devices was same to the process in the section 2.3.2. The gate-recess was performed using two methods. The first method was a combination of BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching and digital etching using asher and HCl, while the second method was a combination of BCl<sub>3</sub>/Cl<sub>2</sub> based dry etching and ALE. Details of the gate-recess for the gate recessed Schottky devices are shown in Fig. 2.31.

### Device 1

Etching of 17 nm GaN/AlGaN using BCl<sub>3</sub>/Cl<sub>2</sub> plasma dry etching

Additional etching of 5 nm AlGaN using digital etching using asher & HCl

#### Device 2 Etching of 17 nm GaN/AlGaN using BCl<sub>3</sub>/Cl<sub>2</sub> plasma dry etching

Additional etching of 5 nm AlGaN using ALE

Fig. 2.31 The gate-recess processes for the gate recessed Schottky devices

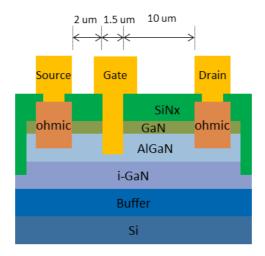

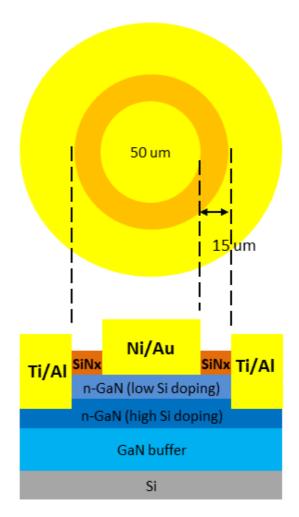

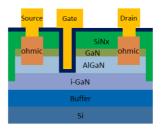

The gate length, source to gate distance, gate to drain distance and gate width of the fabricated devices were 1.5, 2, 10 and 100 um, respectively as shown in Fig. 2.32.

Fig. 2.32 The schematic cross section and dimensions of the fabricated devices

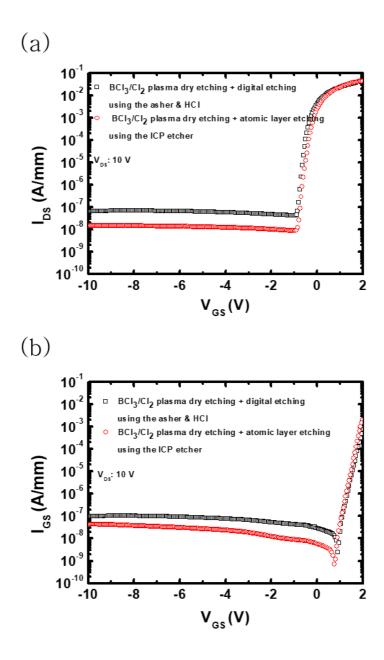

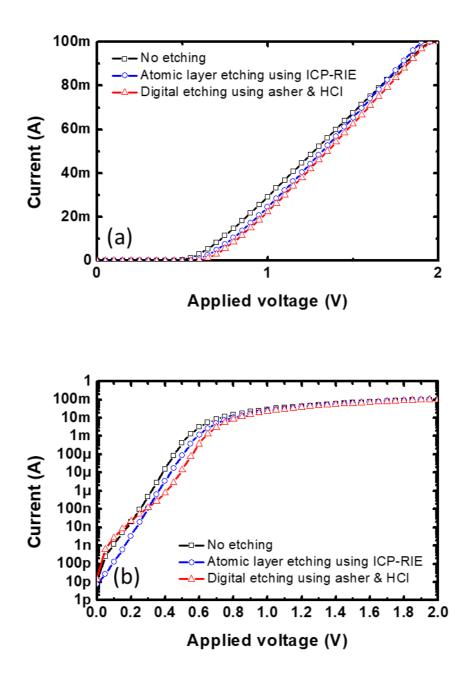

I-V characteristics of the fabricated gate recessed Schottky devices is shown in Fig. 2.33. The reverse leakage current of the device using ALE was lower by one order than that using the digital etching with asher and HCl. It can be explained by reduction of electrons tunneling via plasma induced traps because the traps provide a conducting path with lower energy barrier. It also suggests that lower etching damage can be achieved by the ALE than the digital etching with asher and HCl.

**Fig. 2.33** I-V characteristics of the fabricated gate recessed Schottky devices. (a) drain current and (b) gate current

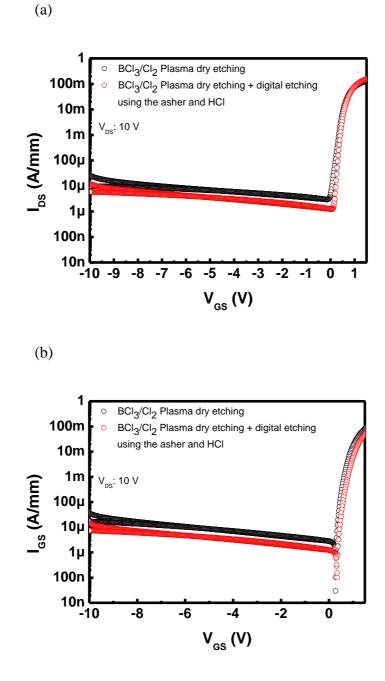

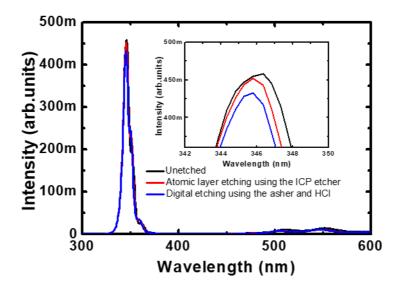

Photoluminescence characteristics of GaN samples were investigated. A sample was etched by the ALE and the etching depth was ~5 nm. A GaN sample which was etch by the digital etching using asher and HCl and an unetched control GaN sample were also plotted for comparison. For the photoluminescence experiments, we used a 266 nm laser source with a power of 2W/cm<sup>2</sup>. Fig. 2.34 shows the PL spectra of the three samples.

Fig. 2.34 PL characteristics for the samples.

The sample etched by the ALE showed the higher band edge peak compared to the sample etched by the digital etching using asher and HCl. This result indicates that the ALE produces less plasma-induced damage on the GaN surface than the digital etching using asher and HCl. Also, PL intensity of the GaN sample etched by the ALE was almost comparable to that of the unetched control sample.

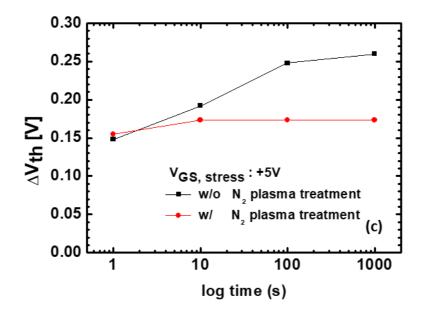

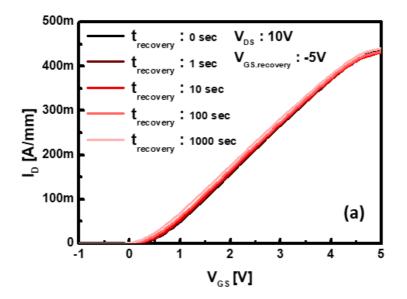

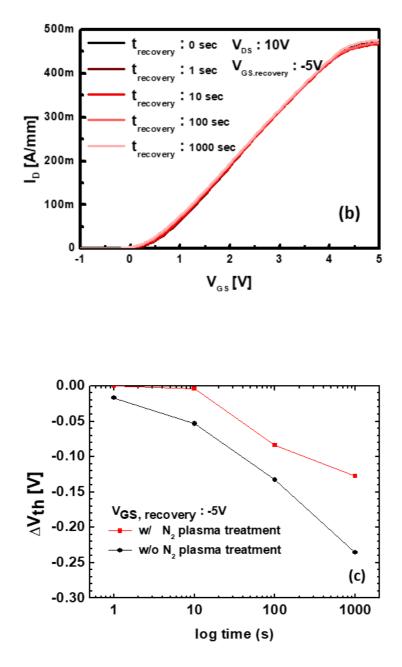

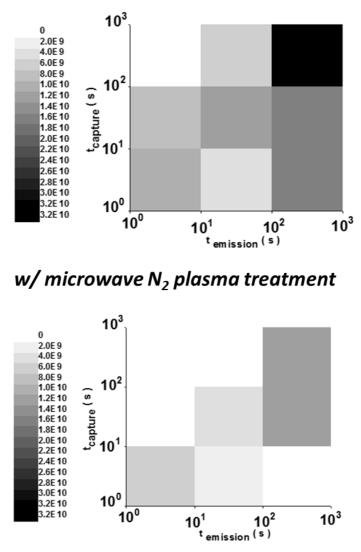

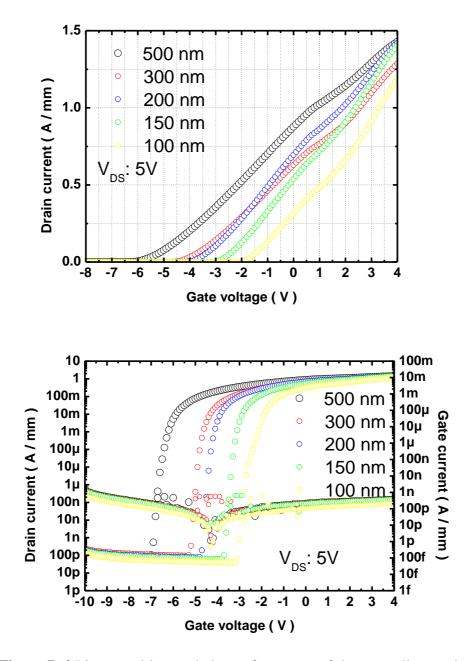

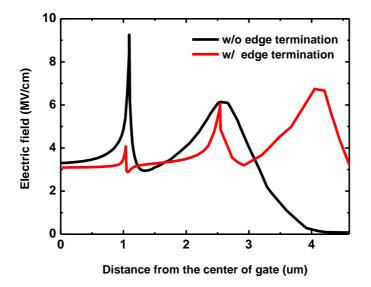

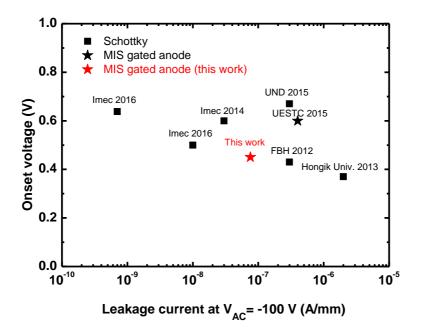

The surface morphology of the AlGaN samples and the control sample