#### 저작자표시-비영리-변경금지 2.0 대한민국

## 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

#### Ph.D. DISSERTATION

# Code Transformation Techniques to Enforce Security Policies for Memory Safety

메모리 보호를 위한 보안 정책을 시행하기 위한 코드 변환 기술

BY

JANGSEOP SHIN

FEBRUARY 2020

DEPARTMENT OF ELECTRICAL ENGINEERING AND

COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

### Ph.D. DISSERTATION

# Code Transformation Techniques to Enforce Security Policies for Memory Safety

메모리 보호를 위한 보안 정책을 시행하기 위한 코드 변환 기술

BY

JANGSEOP SHIN

FEBRUARY 2020

DEPARTMENT OF ELECTRICAL ENGINEERING AND

COMPUTER SCIENCE

COLLEGE OF ENGINEERING

SEOUL NATIONAL UNIVERSITY

# Code Transformation Techniques to Enforce Security Policies for Memory Safety

메모리 보호를 위한 보안 정책을 시행하기 위한 코드 변환 기술

> 지도교수 백 윤 흥 이 논문을 공학박사 학위논문으로 제출함

> > 2020년 2월

서울대학교 대학원 전기 컴퓨터 공학부 신 장 섭

신장섭의 공학박사 학위 논문을 인준함 2020년 2월

| 위 원         | 장: | 문수묵 | (인) |

|-------------|----|-----|-----|

| 부위원         | 장: | 백윤흥 | (인) |

| 위           | 원: | 이재욱 | (인) |

| 위<br>위<br>위 | 원: | 이병영 | (인) |

| 위           | 원: | 조영필 | (인) |

**Abstract**

Computer memory is a critical component in computer systems that needs to be

protected to ensure the security of computer systems. It contains security sensitive data

that should not be disclosed to adversaries. Also, it contains the important data for op-

erating the system that should not be manipulated by the attackers. Thus, many secu-

rity solutions focus on protecting memory so that sensitive data cannot be leaked out

of the computer system or on preventing illegal access to computer data. In this thesis,

I will present various code transformation techniques for enforcing security policies

for memory protection. First, I will present a code transformation technique to track

implicit data flows so that security sensitive data cannot leak through implicit data

flow channels (i.e., conditional branches). Then I will present a compiler technique to

instrument C/C++ program to mitigate use-after-free errors, which is a type of vul-

nerability that allow illegal access to stale memory location. Finally, I will present a

code transformation technique for low-end embedded devices to enable execute-only

memory, which is a strong security policy to protect secrets and harden the computing

device against code reuse attacks.

주요어: Computer Security, Memory protection, Code transformation

학 번: 2013-20813

i

# **Contents**

| A۱ | bstrac  | et            |                                                                | i    |

|----|---------|---------------|----------------------------------------------------------------|------|

| C  | onten   | ts            |                                                                | ii   |

| Li | st of ' | <b>Fables</b> |                                                                | vi   |

| Li | st of l | Figures       |                                                                | viii |

| 1  | Intr    | oductio       | n                                                              | 1    |

| 2  | Bac     | kgroun        | d                                                              | 4    |

| 3  | ΑH      | ardwar        | e-based Technique for Efficient Implicit Information Flow Trac | ck-  |

|    | ing     |               |                                                                | 8    |

|    | 3.1     | Introd        | uction                                                         | 8    |

|    | 3.2     | Relate        | d Work                                                         | 10   |

|    | 3.3     | Our A         | pproach for Implicit Flow Tracking                             | 12   |

|    |         | 3.3.1         | Implicit Flow Tracking Scheme with Program Counter Tag         | 12   |

|    |         | 3.3.2         | $t_{PC}$ Management Technique                                  | 15   |

|    |         | 3.3.3         | Compensation for the Untaken Path                              | 20   |

|    | 3.4     | Archit        | ecture Design of IFTU                                          | 22   |

|    |         | 3.4.1         | Overall System                                                 | 22   |

|   |       | 3.4.2 Tag Computing Core                                             | 24 |

|---|-------|----------------------------------------------------------------------|----|

|   | 3.5   | Performance and Area Analysis                                        | 26 |

|   | 3.6   | Security Analysis                                                    | 28 |

|   | 3.7   | Summary                                                              | 30 |

| 4 | CRC   | Count: Pointer Invalidation with Reference Counting to Mitigate Use- |    |

|   | after | -free in Legacy C/C++                                                | 31 |

|   | 4.1   | Introduction                                                         | 31 |

|   | 4.2   | Related Work                                                         | 36 |

|   | 4.3   | Threat Model                                                         | 40 |

|   | 4.4   | Implicit Pointer Invalidation                                        | 40 |

|   |       | 4.4.1 Invalidation with Reference Counting                           | 40 |

|   |       | 4.4.2 Reference Counting in C/C++                                    | 42 |

|   | 4.5   | Design                                                               | 44 |

|   |       | 4.5.1 Overview                                                       | 45 |

|   |       | 4.5.2 Pointer Footprinting                                           | 46 |

|   |       | 4.5.3 Delayed Object Free                                            | 50 |

|   | 4.6   | Implementation                                                       | 53 |

|   | 4.7   | Evaluation                                                           | 56 |

|   |       | 4.7.1 Statistics                                                     | 56 |

|   |       | 4.7.2 Performance Overhead                                           | 58 |

|   |       | 4.7.3 Memory Overhead                                                | 62 |

|   | 4.8   | Security Analysis                                                    | 67 |

|   |       | 4.8.1 Attack Prevention                                              | 68 |

|   |       | 4.8.2 Security considerations                                        | 69 |

|   | 4.9   | Limitations                                                          | 69 |

|   | 4.10  | Summary                                                              | 71 |

|   |       |                                                                      |    |

| 5  | uXC    | M: Eff    | icient eXecute-Only Memory on ARM Cortex-M               | 73  |

|----|--------|-----------|----------------------------------------------------------|-----|

|    | 5.1    | Introdu   | uction                                                   | 73  |

|    | 5.2    | Backg     | round                                                    | 78  |

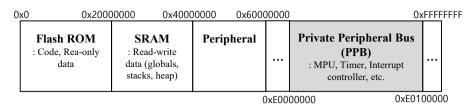

|    |        | 5.2.1     | ARMv7-M Address Map and the Private Peripheral Bus (PPB) | 78  |

|    |        | 5.2.2     | Memory Protection Unit (MPU)                             | 79  |

|    |        | 5.2.3     | Unprivileged Loads/Stores                                | 80  |

|    |        | 5.2.4     | Exception Entry and Return                               | 80  |

|    | 5.3    | Threat    | Model and Assumptions                                    | 81  |

|    | 5.4    | Appro     | ach and Challenges                                       | 82  |

|    | 5.5    | uXOM      | 1                                                        | 85  |

|    |        | 5.5.1     | Basic Design                                             | 85  |

|    |        | 5.5.2     | Solving the Challenges                                   | 89  |

|    |        | 5.5.3     | Optimizations                                            | 98  |

|    |        | 5.5.4     | Security Analysis                                        | 99  |

|    | 5.6    | Evalua    | ntion                                                    | 100 |

|    |        | 5.6.1     | Runtime Overhead                                         | 103 |

|    |        | 5.6.2     | Code Size Overhead                                       | 106 |

|    |        | 5.6.3     | Energy Overhead                                          | 107 |

|    |        | 5.6.4     | Security and Usability                                   | 107 |

|    |        | 5.6.5     | Use Cases                                                | 108 |

|    | 5.7    | Discus    | ssion                                                    | 110 |

|    | 5.8    | Relate    | d Work                                                   | 111 |

|    | 5.9    | Summ      | ary                                                      | 113 |

| 6  | Con    | clusion   | and Future Work                                          | 114 |

|    | 6.1    | Future    | Work                                                     | 115 |

| Αl | ostrac | et (In Ko | orean)                                                   | 132 |

Acknowlegement 133

# **List of Tables**

| 3.1 | Synthesis Result                                                                           | 27 |

|-----|--------------------------------------------------------------------------------------------|----|

| 4.1 | The list of runtime library functions of CRCount                                           | 47 |

| 4.2 | Statistics for the SPEC CPU2006 benchmarks. # tot alloc. de-                               |    |

|     | notes the total number of object allocations. # ptr stores by                              |    |

|     | inst. denotes the number of tracked pointer stores by the store in-                        |    |

|     | structions, while # ptr stores by memcpy denotes the num-                                  |    |

|     | ber of pointer stores by memcpy. max mem. shows the maximum                                |    |

|     | amount of memory occupied by the objects that are allocated but not                        |    |

|     | freed. max undeleted shows the maximum amount of memory oc-                                |    |

|     | cupied by the undeleted objects. max undel. / max mem. shows                               |    |

|     | the ratio between max mem and max undeleted. leaks shows                                   |    |

|     | the memory leak caused by an error in the pointer footprinting. The                        |    |

|     | last column shows the number of pointers tracked down by DangSan.                          | 57 |

| 4.3 | Real world vulnerabilities tested with CRCount. The Original col-                          |    |

|     | umn shows the behavior of the original program when run with the                           |    |

|     | exploit input. We disabled the ${\tt Zend}$ allocator in ${\tt PHP}$ to test the exploits. | 65 |

| 5.1 | Basic instruction conversion (only shown for load word instruction) .                      | 86 |

| 5.2 | 2 Verification details by the type of unconverted memory instructions.       |     |  |

|-----|------------------------------------------------------------------------------|-----|--|

|     | $Target_{address}$ denotes the memory address accessed by load/store in-     |     |  |

|     | structions and $Target_{value}$ denotes the value to be written by the store |     |  |

|     | instructions                                                                 | 90  |  |

| 5.3 | Statistics for instruction conversion and sp check instrumentation           | 104 |  |

# **List of Figures**

| 2.1  | Typical attack process starting from a memory vulnerability           | 5  |

|------|-----------------------------------------------------------------------|----|

| 3.1  | An example code with implicit flow                                    | 13 |

| 3.2  | Example of tag propagation rules                                      | 14 |

| 3.3  | An example code with implicit flow through the untaken path           | 15 |

| 3.4  | $t_{PC}$ setting and clearing example                                 | 16 |

| 3.5  | Solving push/pop imbalance                                            | 18 |

| 3.6  | Incorrect push/pop insertion for a loop                               | 19 |

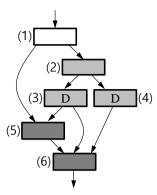

| 3.7  | Example CFG for tag compensation                                      | 21 |

| 3.8  | Overall system design                                                 | 23 |

| 3.9  | Tag computing core architecture design                                | 24 |

| 3.10 | Performance Comparison                                                | 28 |

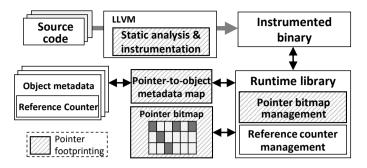

| 4.1  | Overview of CRCount                                                   | 45 |

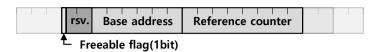

| 4.2  | Layout of per-object metadata. rsv. field is reserved for C++ support |    |

|      | (§4.6) and garbage collection (§4.7)                                  | 48 |

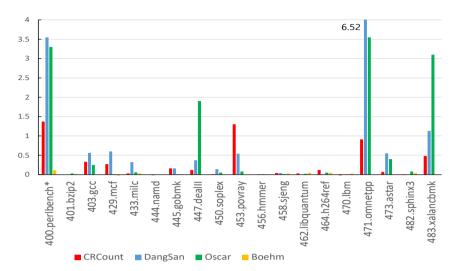

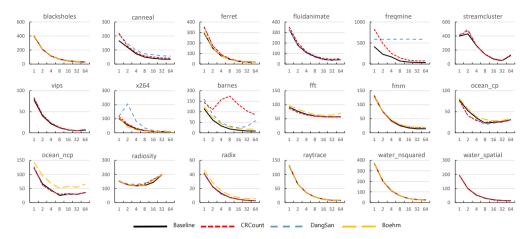

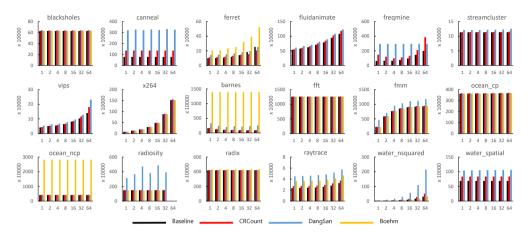

| 4.3  | Performance overhead on SPEC CPU2006. We use the reported num-        |    |

|      | bers in the original papers for perlbench of DangSan, which fails     |    |

|      | to run, and all the benchmarks of Oscar. For Boehm GC, we were able   |    |

|      | to run only C benchmarks excluding gcc                                | 60 |

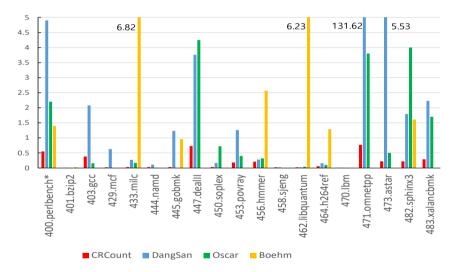

| 4.4 | Memory overhead on SPEC CPU2006. Some numbers are those that           |    |

|-----|------------------------------------------------------------------------|----|

|     | have been reported in the original paper as in Figure 4.3              | 60 |

| 4.5 | Comparison of the execution time on PARSEC. We could not get the       |    |

|     | correct result for freqmine for DangSan because we could not en-       |    |

|     | able OpenMP with DangSan, which is required to run freqmine in         |    |

|     | the multithreaded mode. The results for Boehm GC is only included      |    |

|     | for the subset of the C benchmarks that we could run                   | 61 |

| 4.6 | Memory overhead on PARSEC                                              | 62 |

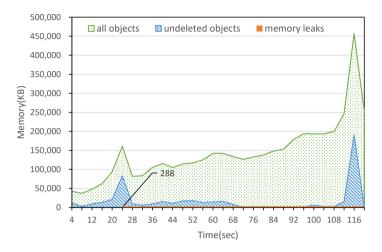

| 4.7 | Changes in memory usage during the execution of gcc with 200.i         |    |

|     | input file. all objects denotes the total amount of memory allo-       |    |

|     | cated for heap-allocated objects and the undeleted objects. undeleted  |    |

|     | objects and memory leaks indicate the amount of the memory             |    |

|     | occupied by undeleted objects and memory leaks, respectively           | 66 |

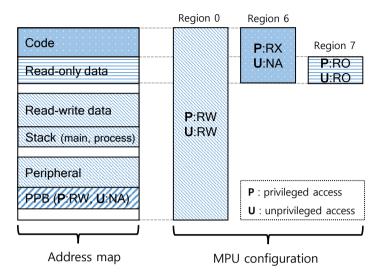

| 5.1 | System address map for ARMv7-M [47]                                    | 78 |

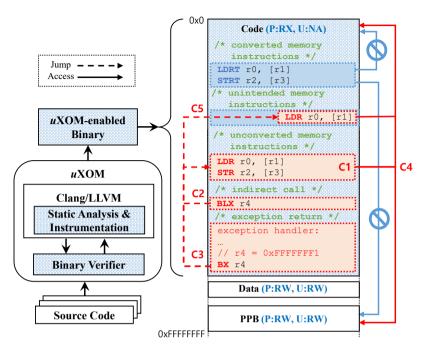

| 5.2 | uXOM approach                                                          | 83 |

| 5.3 | uXOM-specific memory permission. Unlabeled regions (white-colored      |    |

|     | regions) in the address map indicate the unused regions where the      |    |

|     | memory access generates data abort. The PPB region has a default       |    |

|     | memory permission (P:RW, U:NA) regardless of the MPU configuration.    | 88 |

| 5.4 | An unconverted store before and after applying the atomic verification |    |

|     | technique. In the update_register functions r0 and r1 are used to pass |    |

|     | arguments that will be used as unconverted store's base register and   |    |

|     | source register, respectively.                                         | 92 |

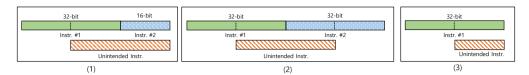

| 5.5 | The generation of an unintended instruction by an unaligned execution  |    |

|     | of a 32-bit instruction                                                | 94 |

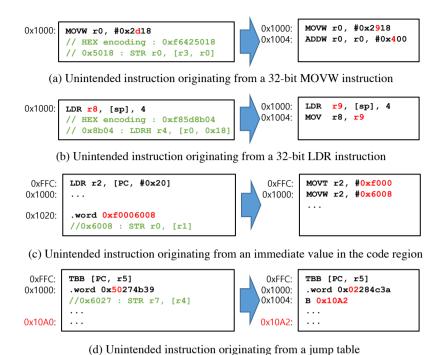

| 5.6 | Examples of unintended instructions and code transformations to re-    |    |

|     | move them.                                                             | 96 |

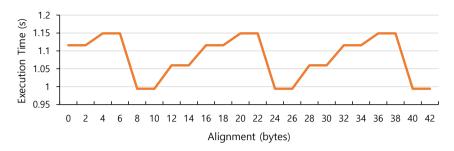

| 5.7  | .7 Execution time of bitcount according to the different alignments of |     |  |

|------|------------------------------------------------------------------------|-----|--|

|      | the code region                                                        | 101 |  |

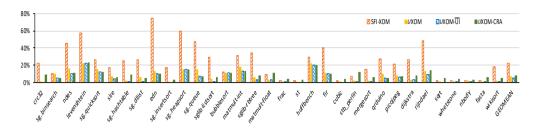

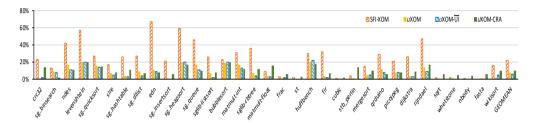

| 5.8  | Runtime overhead on BEEBs benchmark suite                              | 102 |  |

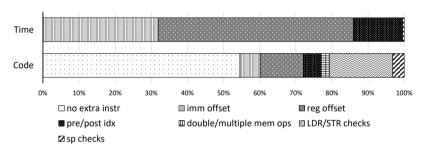

| 5.9  | Performance overhead breakdown for the different components of $uXOM$  | 1-  |  |

|      | $\overline{\text{UI}}$ transformation                                  | 104 |  |

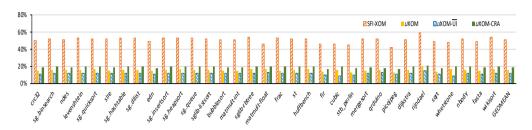

| 5.10 | Code size overhead on BEEBs benchmark suite                            | 105 |  |

| 5 11 | Energy overhead on BEERs benchmark suite                               | 105 |  |

# Chapter 1

## Introduction

Computing devices are ubiquitous in modern human life. We rely on computer systems to handle various jobs for us. As the computer systems become more involved in our everyday life and business, more security sensitive data are processed by the computer systems, which makes it important that these data are protected from unauthorized entity. Also, protecting the integrity of the computer system is important, since attackers can manipulate the operation of computer systems to do harm to us.

In the field of computer security, one of the most critical component is the computer memory. It is the very component that contains security sensitive data. It also contains data for the control of the system—Attackers can control the operation of the system by corrupting computer memory. Therefore, many security solutions focus on the protection of memory. The security solutions differ depending on the given security goal. The security goal can be just to protect secret data from unauthorized users (i.e., to enforce confidentiality), or to prevent data corruption by unauthorized users (i.e., to enforce integrity of the data). There can be different approaches to achieve these goals. Since memory corruption is usually the result of software vulnerabilities, some solutions seek to detect or mitigate the errors resulting from the vulnerabilities. Some solutions manage and enforce access permission for different memory regions so that

there can be some restriction in accessing the memory even if the vulnerabilities are exploited.

In this thesis, I present various code transformation techniques to enforce security policies for memory protection. The advantage of code transformation techniques is that it can be deployed very easily, since it does not require silicon changes and it can be directly applied on existing systems. The code transformation is done by the compiler automatically, so manual intervention is not required. Thus, it is less errorprone and can be efficiently applied.

In Chapter 3, I will present a code transformation technique for efficient implicit information flow tracking. Dynamic information flow tracking (DIFT) is a promising technique for tracking the data inside a computer system. If we mark a security sensitive data, DIFT system will track propagation of the data through registers and memory during program runtime. However, the value of the secret can leak through implicit flows such as conditional branches. If the secret value is used as a condition for branch statements, the attacker can infer the value via the control flow that is taken as the result of the conditional statement. I will show how the proposed technique can help track these kind of implicit flow efficiently.

In Chapter 4, I will present a code transformation technique to efficiently mitigate use-after-free errors. Use-after-free errors are one of the common software vulnerabilities that allow illegal access to already deallocated heap memory. There have been many researches that tackle this problem but all of them suffer from high performance or memory overhead. In this chapter, I present how our technique can mitigate use-after-free error efficiently by automatically tracking reference counts for the heap objects in legacy C/C++ programs.

In Chapter 5, I will present a technique to enforce execute-only memory (XOM) for ARM Cortex-M processors, which is a popular processor for low-end embedded devices. XOM is a promising technique to hide sensitive data or software intellectual

properties. It can also effectively hide randomized code layout from attackers, thus providing protection against code-reuse attacks. Current high-end processors from both Intel and ARM support XOM feature in their CPUs. However, low-end embedded processors currently do not support XOM feature natively. In this chapter, I will show how we transform the code in ARM Cortex-M processor using special instructions to effectively enable XOM without causing too much performance/memory overhead.

# Chapter 2

# **Background**

In this chapter, I will introduce typical attack process that starts from memory corruption vulnerabilities. Then I will explain how researches defend against attacks by blocking the certain point of attack process. I will also explain the importance of the role of compiler in defending against these type of attacks.

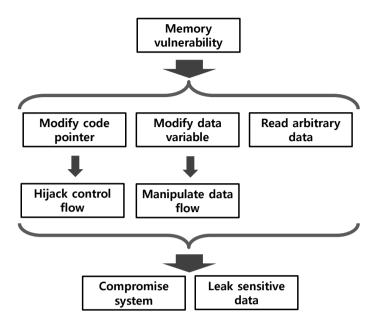

Figure 2.1 shows how the attacker typically compromise system security starting from the memory corruption vulnerability. The attacker can modify code pointer such as return address or function pointer to hijack control flow of the program. The attacker can alternatively modify data pointer or data variable to manipulate data flow of a program. For example, there can be a variable denoting the authentication status of a user. Attacker can modify the variable by exploiting a memory corruption vulnerability thereby bypassing proper authentication process. Data flow is manipulated in this case, since originally the authentication variable should be toggled inside the authentication function, but the attacker modifies the authentication variable in the abnormal position of the program where the memory corruption occurs. Sometimes the purpose of the attacker can just be using the memory corruption to read illegitimate memory address to leak sensitive data as in the case of Heartbleed vulnerability [1].

Many researches focus on breaking particular point of this chain of attack process.

Figure 2.1: Typical attack process starting from a memory vulnerability.

Numerous work have been done to eliminate the source of the memory corruption problem by finding vulnerabilities in the program or developing ways to detect/prevent memory error once triggered by the attacker at runtime. The memory error can be roughly divided as spatial error such as buffer overflow and temporal errors such as use-after-free vulnerabilities. Some work statically analyze the program [39, 112] or dynamically feeding random inputs into the program and trigger crashes [22, 84, 96] to find new vulnerabilities. However, these approach cannot find all the vulnerabilities in the program. Therefore, other researches focus on detecting/preventing errors at runtime. These works typically instrument the program to keep track of data structures and insert checks or invalidate pointers so that illegitimate memory access can be captured [31, 57, 103].

Next line of work focus on isolating the security sensitive data or controlling the access of the attackers to illegitimate memory address so that the attackers cannot modify code pointers or data variables illegally or read memory region which is not

allowed. Code pointer integrity [54] isolates code pointers in a safe region so that attackers cannot temper with code pointers using memory vulnerabilities. WIT [3] assigns a color to the object (by coloring the shadow memory area that corresponds to the object) and assigns the same color to the memory access instructions that can legitimately access the memory object. Before any memory access, the colors are compared to detect possible attack attempt that exploits memory vulnerabilities to access arbitrary data.

Another way to break the attack chain is to tackle the next step in the attack process. When the attacker uses the memory vulnerability to modify illegal data value, she needs to know to which value she wants to convert the data in order to complete her attack. For example, to launch successful code reuse attack, she needs to know the address of the code gadgets that she wants to use for her attack sequence. Various code layout randomization defenses have been developed to prevent the attackers from learning the address of the code gadgets [12, 29, 33]. Data randomization techniques [13, 15, 21] have been proposed to randomize data representation in memory so that attacker cannot know how to change the data value in memory.

Finally, some techniques try to defend against the final goal of the attacker. To compromise a computing system from user space applications, attackers usually have to utilize system calls to do anything meaningful such as launching a shell, reading a file, etc. Therefore, a bunch of work focus on monitoring system calls to detect signs of attack [35, 105]. For another line of work, the sole purpose of the defense is to prevent leakage of sensitive data through the output channels such as standard output and public network/files. Dynamic information flow tracking (DIFT) [97] is a popular approach for solving this problem. It marks the sensitive data and tracks data flow through the program.

Implementation wise, most of the above mentioned solutions require some form of program transformation. Binary level solution is possible and there are plenty of researches that work on binaries [104, 107, 116]. Binary level solutions have an advantage that the program source code is not required so it can be readily applied to a given binary. However, they are often limited in implementing more advanced security mechanism without involving high performance overhead and they often require extra information such as symbols and relocation [107]. On the other hand, compilers can perform more precise analysis using the given source code, enabling sophisticated security solutions with much lower overhead.

This thesis introduces my work on compiler based security solutions for preventing attacks on computer memory. Chapter 3 introduces a hardware and compiler technique to prevent leakage of sensitive data through implicit information flows. The compiler mainly analyzes program control flow graph and instruments special hardware instructions at the right place for guiding hardware to maintain the program counter tag for tracking data propagation through implicit control flows. Chapter 4 presents a compiler based technique to prevent attacks utilizing use-after-free vulnerabilities. The compiler mainly analyzes the type information in the program intermediate representation and inserts runtime library calls into necessary places to maintain reference counts for controlling memory free operation. Chapter 5 presents a compiler technique to enable execute-only memory on ARM Cortex-M based microprocessors. In this work, the main job of the compiler is to transform certain instructions into special hardware instructions. It also generates verification code and analyzes and inserts check code to sandbox the stack pointer.

# Chapter 3

# A Hardware-based Technique for Efficient Implicit Information Flow Tracking

#### 3.1 Introduction

In recent years, computer security has been severely threatened by various malicious attacks that intend to leak sensitive information [72]. The general goal of these attacks is to transfer the critical data from sensitive sources (e.g., SIM card, password list) to output channels like network connections so that the attackers can acquire the sensitive information in the system. To achieve the goal, the malicious program or the victim program being exploited by attackers first accesses the critical data and then copies them from the source to the destination at each instruction execution. When they are finally delivered to the output channel, the attacker can leak the sensitive information out of the system.

One of the most widely used solutions against this type of attacks is *Dynamic in- formation flow tracking* (DIFT) [72]. Generally, DIFT sets up rules to taint internal data of interest and keeps track of their taintness throughout the system. At runtime, whenever an instruction is executed, the taintness of sources is propagated to the destinations, to track the information flow associated with the data transfers (data copying

and transformations). An alarm will be triggered as soon as any of the tainted data is involved in potentially illegal activities, such as being included in a data stream on the output channels. In several previous studies [26, 30, 72, 81, 117], it was demonstrated that DIFT is an effective way to detect the attacks which attempt to leak the sensitive information with explicit data transfers.

However, there have been some advanced attacks that can bypass the explicit DIFT approaches by acquiring certain sensitive information only through the execution control flow analysis of a victim program without data transfers. In practice, when a data value affects a conditional branch result, execution flow is altered and it affects other data. Then the affecting value can often be inferred merely by examining the values of the affected ones. In this case, we can see that although there is no *explicit* data copy or transfer, the affecting data value is in effect transferred to other data values via the *implicit flow* along the execution control path. In the previous studies [50, 56], they presented empirical evidence that the attackers can leak the sensitive information by exploiting the implicit flow. Thus, in order to deal with such advanced attacks, a DIFT solution should track the taintness of the sensitive data tags not only through the explicit information flow associated with data copy and transfer operations, but also through the implicit flow associated with conditional branch operations.

For the tracking of implicit flow, several software solutions have been proposed [50, 114]. In these works, they analyze the program code and find the control flow that might be related to the implicit information flow at runtime. Then, they augment the original application with the additional code to keep track of the implicit flow as well as the explicit flow. In spite of their effectiveness, the main drawback of these solutions is that they incur too much runtime overhead, since it takes up to 20 instructions to emulate a single tag propagation operation per instruction.

To reduce the performance overhead for implicit flow tracking, RIFLE [101] resorts to a hardware technique. Although they have shown an impressive improvement

on the overall DIFT computation, their experiment also reveals that they still suffer from the non-negligible performance overhead for implicit flow tracking. This is primarily because their hardware has been designed originally for the information tracking with explicit data transfers. Therefore, to utilize their hardware for implicit flow tracking, they had to convert the implicit flow problem to the equivalent explicit one. For this reason, they instrumented their binary code to transform all implicit information flow operations across conditional branches into explicit data copy operations. According to their experiments, the performance degrades by a factor of two in the worst case, mainly due to the instrumented instructions.

Motivated by previous work, we have developed a dedicated hardware unit to efficiently tackle the implicit flow tracking problem. In this paper, we introduce our hardware engine for implicit flow tracking, called the *implicit flow tracking unit* (IFTU), and the implicit flow tracking scheme designed to work on IFTU. We have built IFTU as an external hardware module attached to the host processor via the system interconnect. To evaluate its effectiveness, we have implemented our solution on an FPGA board. In our experiments, we show that our proposed approach with IFTU successfully tracks the implicit information flow on the system with negligible performance overhead, while the additional logic required for the implicit flow tracking is also small.

#### 3.2 Related Work

There has been much prior work that focuses on explicit information flow tracking [26, 30, 58, 72, 81, 97, 117]. Software approaches in [72, 81] suggest the use of a binary instrumentation technique, which mainly inserts additional instructions to the target code to keep track of the tainted data at runtime. During the program execution, the taintness of data is propagated according to the data dependency, and any misuse of data (e.g. information leak) is detected by their proposed solutions. Other works in-

troduced in [26,30,97] suggest the use of specialized hardware logic for DIFT mainly to reduce the performance overhead caused by the DIFT computation. In [26,97], for instance, they augmented the host processor internals directly, including register files and caches. In [30,58], they proposed a decoupled DIFT hardware that can be attached to the outside the host. These previous approaches, implemented either in software or hardware, show their effectiveness in the tracking of explicit flows. However, a critical limitation they have is that they do not consider the implicit flows, which can result in the *under-tainting problem* where the values that should be tainted are not tainted [50].

To resolve the under-tainting problem, several software solutions for implicit flow tracking have been proposed. In [36], the authors use dynamic analysis to keep track of the flow of sensitive information processed by the web browser application. To handle the implicit flows, their taint engine examines all conditional branch instructions that are encountered during execution. If such an instruction has at least one tainted operand, the taint engine identifies all instructions whose execution is conditionally dependent on the direction of the branch and then it taints the results of those instructions. In [50], another software solution, called DTA++, is proposed. To achieve efficiency in the tracking, instead of examining all conditional branches, DTA++ focuses only on the implicit flows within certain code patterns (i.e., the information-preserving transformations), based on the observation that under-tainting usually occurs at just a few locations. With the proposed tracking strategy, DTA++ can achieve effectiveness and efficiency in implicit flow tracking. Nevertheless, the main drawback of these software approaches is that they still suffer from performance degradation mainly due to the additional code instrumented with the binary translation. For example, although DTA++ only applies the tracking technique to certain cases, the performance overhead is around 1.5X even with the parallel execution of the binary translation.

For this reason, several hardware techniques [100, 101] have been proposed to enhance the tracking performance. RIFLE [101] is a hybrid approach that uses compiler-

assisted binary rewriting to change the program to turn implicit information flows due to condition flags into explicit tag assignments. However, as discussed, the main problem of RIFLE is that it relies on the hardware architecture designed for the explicit flow tracking and thus requires code transformation to convert implicit flows to explicit ones. Since too many additional instructions are added to the original program binary to utilize the hardware, the efficiency is severely degraded and the performance overhead reaches up to 1.5X in the worst case (when the data cache of the system is duplicated to store the tags). On the other hand, in our approach, we propose a hardware engine specialized for implicit flow tracking and thus can overcome the limitation of RIFLE. GLIFT [100] and Leases [99] are interesting hardware solutions that track information flow at the gate level to build a system with strong noninterference properties which can be used to eliminate all forms of information leak, including those from timing and storage channels. While this is a potentially promising approach, all the hardware has to be re-designed from the gates up, requiring unproven new hardware design methodologies and tools. On the other hand, our IFTU can be connected to the commodity processor with an external interface, not requiring the redesign of the off-the-shelf processor architecture, since it is designed as an external module.

## 3.3 Our Approach for Implicit Flow Tracking

We now discuss our approach for efficient implicit flow tracking, inspired by [25] and improved. After briefly explaining the tracking scheme implemented in our work, we will describe our code analysis and transformation technique whose purpose is to enable the scheme to work correctly in real programs.

## 3.3.1 Implicit Flow Tracking Scheme with Program Counter Tag

The code snippet in Figure 3.1 shows a simple example of implicit information flow in a program. In this example, the value of x can be changed to either 0 or 1 according

to the branch result that is affected by the signedness of variable s. Clearly, there is a flow of information between the two variables since the value of s affects the value of x; however, it is not the result of direct data transfers, but rather the result of the branch outcome affected by setting the condition flag through the comparison.

```

x := 2

if s <= 0 then x := 0 else x := 1

```

Figure 3.1: An example code with implicit flow

To handle these implicit flows correctly, language-based static techniques [85] use a tracking scheme that introduces the program counter tag (denoted as  $t_{PC}$ ), which indicates whether the control flow path is affected by tainted data or not. In this scheme, for every conditional branch, the taintness of data that is used for the condition checking is propagated to  $t_{PC}$ . Then, for the instructions after the branch, the value of  $t_{PC}$  is propagated to the tags of their destinations to indicate that the values are affected by the branch result. Now, assume that the example described in Figure 3.1 is tracked with this scheme. In this example, the variable s is used for the condition checking of the branch. Thus, if the variable s contains the sensitive information and its tag is tainted,  $t_{PC}$  is also set to 1, to indicate that the branch result is affected by the sensitive information. Then, by propagating the value of  $t_{PC}$  to the tag for variable s when it is set, the implicit flow along the branch can be tracked.

In our approach, to handle the implicit flow as well as the explicit ones, we combine the tracking scheme introduced above with the conventional DIFT technique that tracks the data flow [72]. To denote tagging, every location for storing data such as registers and memory is augmented with a tag bit. Then, the tags are propagated during the program execution, based on a set of tag propagation rules that are specified for each basic operation type such as arithmetic, logical, or conditional branch.

Figure 3.2 shows an example code at the assembly level and the associated tag propagation operations. Basically, the tag propagation rules applied in our approach are based on the data dependency, as in the previous works [72, 81]. For example,

when the ldr instruction at line 1 is executed, the tags of sources (%i0 register and the memory location pointed by the register value) are propagated to the tag for register %q2. In addition to the basic rules, we add new rules to track the implicit flow along the control path. In principle, a conditional branch has its condition code, such as equal, not equal or less than. When the branch is executed, the processor checks the condition code register (CCR) which generally consists of several condition bits (e.g., N,Z,V,C in SPARC machines), and determines the control path based on the value of CCR. That is, the result of a conditional branch is affected by the value of CCR. In practice, CCR is configured by an arithmetic instruction like sub, or a specialized comparison instruction like cmp, as in the code at line 3. For this reason, in our solution, when CCR is set by these instructions, the tags of their sources are propagated to  $t_{CCR}$ , which is the tag for CCR (see the right column of line 3). Then, when a conditional branch is executed later, the value of  $t_{CCR}$  is propagated to  $t_{PC}$  (see line 4). (If an unconditional branch is executed, such tag propagation is not performed since the branch is not affected by CCR (see line 6).) Thus,  $t_{PC}$  can indicate whether the control path is affected by tainted data or not. Since the value of  $t_{PC}$  is propagated to the destination tags (marked in boldface at the right column) at each ordinary instruction execution, we can track the implicit flow along the control dependency.

|   |     | Original Code                | Tag Propagation                                                       |

|---|-----|------------------------------|-----------------------------------------------------------------------|

| 1 |     | ldr [%i0], %g2               | $tag[\%g2] = tag[\%i0] \text{ or } tag[mem[\%i0]] \text{ or } t_{nc}$ |

| 2 |     | sub %g2, %g3, %g1            | $tag[\%g1] = tag[\%g2] \text{ or } tag[\%g3] \text{ or } t_{pc}$      |

| 3 |     | cmp %g1, #0                  | $tag[\%ccr] = tag[\%g1]$ or $t_{pc}$                                  |

| 4 |     | be L1 // branch equal        | $tag[\%pc] = \mathbf{t_{ccr}}  \mathbf{or}  \mathbf{t_{pc}}$          |

| 5 |     | mov #2, %g2                  | $tag[\%g2] = \mathbf{t_{pc}}$                                         |

| 6 |     | b L2 // unconditional branch | none                                                                  |

| 7 | L1: | mov '1', %g2                 | $tag[\%g2] = \mathbf{t_{pc}}$                                         |

| 8 | L2: | add %g5, %g2, %g3            | $tag[\%g3] = tag[\%g5] \text{ or } tag[\%g2] \text{ or } t_{pc}$      |

Figure 3.2: Example of tag propagation rules

In spite of its effectiveness, there is a challenge in correctly tracking implicit flow

with the propagation rules introduced above. In principle, the taintness of  $t_{PC}$  set for a conditional branch should be propagated only to the instructions whose execution is conditionally dependent on the result of the branch according to the definition of implicit flow. Otherwise, the taintness of  $t_{PC}$  would be propagated to the tag for the data that is not affected by the branch or the tag that should be tainted would not be tainted. Thus, it is necessary to analyze the code in order to determine the exact scope of every conditional branch, which is a set of instructions that are affected by the branch result. In section 3.3.2, we will discuss a code analysis technique to identify the scopes of conditional branches and the management scheme for correctly clearing  $t_{PC}$  based on the analysis.

```

x := 2

if s \le 0 then x := 0

```

Figure 3.3: An example code with implicit flow through the untaken path

Also, from the tag propagation rules in Figure 3.2, once  $t_{PC}$  is tainted, all the instructions executed after that will be affected, because their execution is decided by a tagged condition. However, information flow can also exist between the condition of a branch and the instructions that are not executed. For example, in Figure 3.3, if the condition for the if statement is true, then x will be tainted according to the propagation rules. However, if the condition is false, x will not be tainted even though the value of x can leak the information about the branch condition. This example shows that only propagating tags according to the executed instructions is not enough, and there is the necessity for tag compensation of the untaken path. In section 3.3.3, we will describe the tag compensation scheme.

## 3.3.2 $t_{PC}$ Management Technique

In principle, the result of a conditional branch determines the control path which in turn determines the instructions executed by the processor. For example, in the control

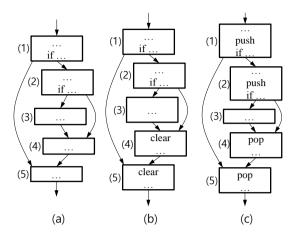

Figure 3.4:  $t_{PC}$  setting and clearing example

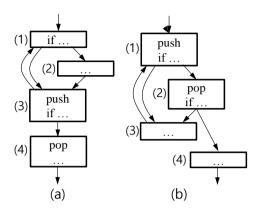

flow graph (CFG) shown in Figure 3.4(a), the execution of block (2) is determined depending on the result of the conditional branch in block (1). However, at a certain point in a program, the control path is no longer affected by the conditional branch. In general, the influence of a conditional branch ends at the *immediate post-dominator* of the branch. In our example, block (5) is the immediate post-dominator of block (1) because all paths from block (1) to the exit must pass block (5). Thus, the value of  $t_{PC}$  set at a conditional branch should be cleared upon the entrance of the immediate post-dominator (5) of the branch in (1) (Figure 3.4(b)).

However, this scheme does not work if the code has multiply-nested branches. For instance, we have a doubly-nested branch in block (2). According to the above scheme,  $t_{PC}$  set in block (1) would be cleared in block (4) although it should have remained set until block (5). In order to remedy this, a new  $t_{PC}$  stack is introduced that is used to save and restore the value of  $t_{PC}$  at each nested branch level. Basically, we save the current  $t_{PC}$  value by pushing it onto the stack just before a conditional branch, and later when we need to clear  $t_{PC}$ , we simply overwrite the current value in  $t_{PC}$  with the value popped from the stack (Figure 3.4(c)).

In Algorithm 1, we illustrate our algorithm that finds and marks the places in the

```

Algorithm 1: Algorithm for inserting push/pop and compensation code

Input: Control flow graph of a function

Output: Control flow graph with push/pop operations and compensation tag

set operations inserted for correct implicit flow tracking

1 foreach loop l do

Insert push at the end of the preheader of l;

Insert pop at the start of the (common) immediate post-dominator of

exiting block(s) of l;

4 end

5 foreach conditional branch block t do

Find t's immediate post-dominator block p;

if t is inside a loop and p is outside then continue;

7

if t is inside a loop and p does not dominate blocks with loop back edge

8

then continue:

Insert push before conditional branch in t;

9

Insert pop at the beginning of p;

10

R = \text{set of basic blocks that is reachable from } t \text{ before reaching } p;

11

foreach block b in R \cup \{p\} do

12

foreach predecessor block pred of b do

13

if pred is not in R \cup \{t, p\} then

14

Insert push between pred and b;

15

end

16

end

17

end

18

foreach live-in register r of p do

19

D = \text{set of basic blocks in } R \text{ that defines } r;

20

R_D = set of basic blocks in R that are reachable from basic blocks in

21

D before reaching p \cup \{p\};

G = \text{set of basic blocks in } R that are guaranteed to pass at least one

22

basic block in D before reaching p;

foreach edge e connecting a block in R - R_D - G with a block in R_D -

23

G do

Insert tag compensation for r;

24

end

25

end

26

27 end

28

```

code where such push/pop operations should be performed. Basically, as explained above, a push operation is inserted before a conditional branch and a pop operation is inserted at the immediate post-dominator of a conditional branch (see lines 9-10). However, real application codes have some exceptional cases that need a more complex algorithm such as ours.

Figure 3.5: Solving push/pop imbalance

In Figure 3.5(a), we can see one of these exceptional cases that should be handled in our algorithm. In the figure, push/pop operations are marked according to the naive algorithm. Now suppose that the control flow takes the path (1)-(3)-(4) at runtime. If so, a push operation will be performed at block (1) and two pop operations will be processed at block (4). This obviously causes an error in the stack management because more entries are popped from the stack than are pushed onto the stack. In general, this problem arises when there is a path that reaches a pop operation inserted for some other conditional branch without passing that conditional branch.

To avoid this problem, for a conditional branch block t and its immediate post-dominator p, we first define a set R consisting of the basic blocks that are reachable from t before reaching p. Then, among the paths that reach p, let P be a path  $(p_1)$ -...- $(p_{r-1})$ - $(p_r)$ -...-(p) that does not pass t, where  $p_r$  is the first basic block in the path that is in R. Then, we insert a new basic block that contains a dummy push operation, between  $p_{r-1}$  and  $p_r$ . (For the example in Figure 3.5(a), such a new block is inserted between blocks (1) and (3) as shown in Figure 3.5(b).) In this way, we can make sure

that the number of push and pop operations are equal along any path. This process corresponds to lines 12-18 of Algorithm 1.

Figure 3.6: Incorrect push/pop insertion for a loop

When the host code includes a loop (e.g., (1), (2), and (3) in Fig 3.6), we must handle a few other exceptional cases. If the immediate post-dominator of a conditional branch block is out of the loop, the push operation marked before the conditional branch is repeatedly executed while the corresponding pop operation is not performed during the loop iteration. In Figure 3.6(a), the immediate post dominator of the conditional branch block (3) is out of the loop, so the push operation may be performed many times while the pop operation will only be executed once in (4). Also, even if the immediate post dominator is in the loop, there can be push/pop imbalances if the block(s) with the backward edge of the loop is not dominated by the immediate post dominator. For example, in Figure 3.6(b), the immediate post dominator of the conditional branch block (1) is block (2). However, there is a path from block (1) that leads to the block with the loop back-edge (block (3)) without crossing block (2). Therefore, the push operation may be performed more than the corresponding pop operation. To handle these exceptional cases, we insert a push operation in the preheader for the loop so that the push is performed only once upon the entrance of the loop, and insert a pop operation in the (common) immediate post dominator of the loop-exiting block(s) of the loop. We rely on this push-pop pair to handle all the conditional branch blocks that correspond to the above exceptional case. Note that push operations do not affect the  $t_{PC}$  value so moving the push operation in front of the loop does not change the correctness of the result. This process is described at lines 1-4 and 7-8 in Algorithm 1.

#### 3.3.3 Compensation for the Untaken Path

To compensate for the untaken path, we analyze the code to find out which register tag needs to be set in which location. There can also be implicit flow through the memory location, but our implementation does not compensate for the memory locations since memory addresses could be determined in the runtime which means that we will have to actually execute the path to determine which memory tag to apply compensation. This could possibly introduce false negatives, but the chances are relatively low since it will also be hard for the attacker to reason about the implicit flow through the memory locations.

Among the registers, we only need to consider the ones that are live-in to the immediate post dominator of the conditional branch block. Registers that are not live at the entry point of the post dominator are not used after the immediate post dominator and cannot be used for the propagation of data. The register tag for the live-in register is set at runtime if there is at least one instruction defining the register on the execution path between the conditional branch and its immediate post dominator. Thus, an implicit flow through an untaken branch will occur if there is an instruction defining the register through some execution path but not all execution paths.

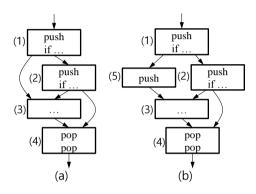

Based on this idea, we find the minimum number of program points where the tag compensation is needed for each register. We first define three sets of basic blocks as described in lines 20-22 in Algorithm 1. In Figure 3.7, we show these sets of basic blocks where block (1) is the conditional branch block currently concerned with. Blocks which define the register are marked with D. Lightly shaded blocks are the

**Figure 3.7:** Example CFG for tag compensation

blocks which pass at least one basic block which defines the register. Darker blocks are the ones that are reachable from blocks defining the register. After determining these sets of blocks, we start from the conditional branch block (block (1)) and traverse the CFG in depth-first manner. If we encounter a lightly shaded block, we do not need to set the register tag since there will be at least one register definition along that path. If we encounter a dark shaded block, we put the register tag set operation on the edge between the current block (block (1)) and the dark block (block (5)). In this way, we can make sure that the register tag is set for all execution path between the conditional branch block and its immediate post dominator. The entire process corresponds to lines 19-26 in Algorithm 1.

We implemented the code analysis and transformation technique described in Algorithm 1 on the LLVM compiler framework. Our transformation tool inserts the pop and push operations in the host code, which are implemented as special instructions whose encodings are not used by the ISA of the host processor architecture. Thus, at runtime, the host processor regards such marked operations as nop operation. Our IFTU processes these operations to manage the  $t_{PC}$  stack. For the register tag compensation, we used a dummy add instruction that adds 0 to the target register and sets the register to that value. It does not change the semantic meaning of the original program, but it can set the register tag if the PC tag is set at that time.

## 3.4 Architecture Design of IFTU

In this section, we will discuss the hardware architecture of our solution. After introducing an architectural overview of our solution, we will discuss the detailed structure of IFTU.

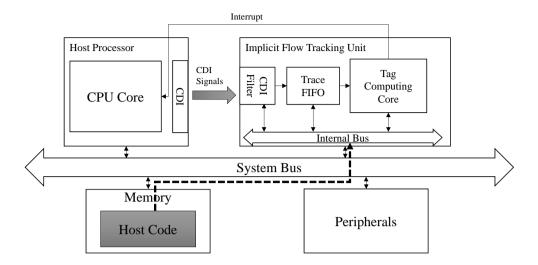

#### 3.4.1 Overall System

Figure 3.8 shows the overall system design for our solution, which mainly consists of the host processor and IFTU. In our implementation, as introduced in Section 1, we design our IFTU as an external hardware module and integrate it with the host processor through the system bus, instead of embedding the dedicated hardware logic internally in the host processor [25]. The main advantage achievable from this design strategy is that our proposed solution can be easily adopted by existing commercial platforms such as application processor (AP) SoC platforms for smartphones. Generally in these platforms, the host processors are typically the commodity processors that are quite difficult to modify the internals without tremendous cost and labor from the vendors. Thus, our solution would be adoptable in these platforms as it does not require such modification.

However, such design strategy raises a challenge. As discussed in Section 3, in order to track the information flow of a program, the taintness of tags should be propagated during the program execution according to the propagation rules. Since the rules are dependent on the instruction type and operands, it is necessary for IFTU to know about the instructions executed by the host. For this reason, our IFTU reads the host program code in main memory and extracts the propagation rules as shown in Figure 3.8. Nevertheless, the problem is that, from only the host code, IFTU cannot obtain some essential information required for the correct flow tracking, which is only resolved during code execution. In particular, such information includes (1) an execution path of the original program and (2) memory addresses of load/store instructions.

Figure 3.8: Overall system design

Without this information, our IFTU cannot perform the tag operations correctly, while following the execution of the host program.

To resolve the problem, in our solution, we utilize the core debug interface (CDI) in the host processor, as was done in the hardware-based solution introduced in [58]. CDI is an interface placed in recent commodity processors, whose main role is to provide the external debug modules with the processor's internal status information required for debug/trace, without affecting the performance of the host. Based on the specification of CDI in commercial processors and the prior works that utilize CDI [7, 58,59,109], in our prototype, we assume that CDI provides a set of signals as follows: instruction address, current context ID (or process ID), data address/value of memory access instructions, branch type/source address/target address, exception and privilege mode information. Since the set of signals includes the necessary runtime information for flow tracking, our IFTU can follow the execution of the host and perform the tag operations correctly.

As shown in Figure 3.8, IFTU consists of three components: the *CDI filter*, the *trace FIFO* and the *tag computing core* (TCC). Although the CDI in the host processor pro-

vides plenty of signals, our IFTU needs only a subset of those signals. The role of the CDI filter is to filter out unnecessary signals and leave the ones that are necessary for the tracking: the current process ID (PID), the address of memory data accessed by a load/store and the target address of a branch. (The current PID is necessary to recognize the active process running on the host. If the monitored program goes into sleep mode, the main controller informs the trace FIFO to ignore the traces from the CDI filter.) IFTU consumes the traces containing such information to obtain necessary information and store them in the trace FIFO in order at runtime.

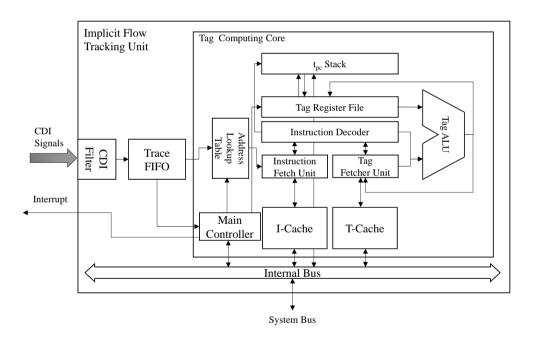

## 3.4.2 Tag Computing Core

Figure 3.9: Tag computing core architecture design

Figure 3.9 shows the microarchitecture of TCC, whose main role is to manage all tags and perform the tag operations. The overall operation of IFTU is controlled by the *main controller* in TCC. It contains several configuration registers and the host processor can control the functions of IFTU by setting the registers, such as the tag

initialization that marks the location of tainted data. To track the flow of information, we augment the tags to the processor registers and memory locations, as in other previous approaches [72,97]. The tags for registers are stored to a special register file in TCC called the *tag register file* (TRF). Each entry of TRF represents the 1-bit tag for the corresponding processor register. We also add two register tags  $t_{PC}$  and  $t_{CCR}$  to the basic structure of TRF, which are used only for the implicit flow tracking. For the memory tags, we reserve a special region called the *tag space* in the main memory. Each bit of the tag space represents the tag for a memory word (32-bit). The *T-cache* is employed in our TCC design to reduce the access latency of tag fetching.

The branch target addresses transferred from CDI are consumed by TCC in order to follow the execution path of the host program. However, since the addresses stored in the trace FIFO are virtual addresses, they cannot be used directly for fetching the host code from main memory. To resolve this problem, TCC includes the *address lookup table* (ALT) where an entry of ALT is comprised of the process ID and the virtual-to-physical address mapping information [58]. At runtime, the host OS kernel updates the entries whenever a code page is allocated on the host, and by using the information the *instruction fetcher unit* reads the host code from the memory with the translated physical addresses. To reduce the access latency required for the instruction fetch, we employ the *I-cache* in TCC as done in previous work [58].

After the host code is fetched, it is delivered to the *instruction decoder* which extracts the propagation rules from the opcode and operands of the instruction. TCC accesses TRF to fetch the tag values if the rule requires register tags. If the operand is the memory address for a load/store, TCC firstly accesses the trace FIFO to acquire the exact address. (Since all load/store instructions generate the CDI signals for the access addresses and the trace containing such information is stored in the trace FIFO in order, it is guaranteed that TCC can obtain the address for the memory instruction.) Then, TCC loads the memory tag corresponding to the address from the T-cache. If

a miss occurs, the *tag fetcher unit* accesses the tag space to handle the miss. Finally, once all the tags are prepared, the *tag ALU* performs the tag propagation with the tags and the resulting values are written to TRF or the T-cache.

To support the management scheme for  $t_{PC}$  introduced in Section 3, TCC includes the hardware for the  $t_{PC}$  stack as shown in Figure 3.9. As discussed, in the instrumented host code, the push/pop operations for the  $t_{PC}$  stack are included. When the instruction decoder encounters such operations, TCC takes the corresponding actions: for push operations, TCC reads the value of  $t_{PC}$  from TRF and pushes it to the stack. For pop operations, the top entry of the stack is popped and overwrites the  $t_{PC}$ . As our current hardware stack implementation has 32 entries, the stack will overflow if the nested level of branches exceeds 32. To cope with this case, we reserve a memory region for the entries to be stored to if the stack is full. Then the tag value for PC is saved or restored from the memory region.

## 3.5 Performance and Area Analysis

To evaluate our approach, we have built a full-system prototype on an FPGA board. In this prototype, we used SPARC V8 processor as the host processor which has separate 4KB instruction/data caches. The AMBA2 AHB compliant bus is used to interconnect the host processor with our IFTU and Linux 2.6 is used as the host OS kernel. IFTU is implemented as described in Section 4 and it includes 4KB I-cache/512B T-cache. Based on the parameters, we synthesized our prototype on to a Xilinx Virtex5 FPGA board. Table 3.1 presents the design statistics of our implemented hardware. Our experiment shows that our IFTU incurs a hardware resource overhead of 28.18% for LUTs, and the memory requirement is increased by about 4.5 KB (mainly due to the caches) when compared to the baseline system that includes the host core. It is noteworthy that the amount of logic required to perform the implicit flow tracking is very small. In our approach, the two tag registers (i.e.,  $t_{PC}$ ,  $t_{CCR}$ ) and the  $t_{PC}$  stack are the

components installed for the implicit flow tracking. In our experiment, the hardware resources for these components are estimated to be about only 5.7% of the overall IFTU. This clearly shows that our approach can be implemented with a small amount of additional logic on top of the DIFT hardware for the explicit flow tracking.

| Category | Component                                                         | LUTs   |

|----------|-------------------------------------------------------------------|--------|

|          | Host Processor Core                                               | 4876   |

| Baseline | Bus components and Memory Controller                              | 844    |

| System   | Peripherals (TIMER, UART, Interrupt Controller and etc.)          | 963    |

|          | Total Baseline System                                             | 6683   |

|          | Components for CDI (CDI Filter, Trace FIFO, Address Lookup Table) | 826    |

|          | Main Controller and Bus Interface                                 | 330    |

|          | Instruction Cache                                                 | 293    |

|          | Tag Cache                                                         | 180    |

| IFTU     | Instruction/Tag Fetcher Unit                                      | 97     |

| IFIU     | Instruction Decoder                                               | 35     |

|          | Tag ALU                                                           | 109    |

|          | t <sub>pc</sub> Stack                                             | 13     |

|          | Total IFTU                                                        | 1883   |

|          | % IFTU over Baseline System                                       | 28.18% |

**Table 3.1:** Synthesis Result

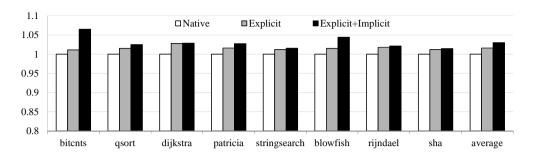

To measure the performance overhead of our approach, we chose eight applications from the *mibench* benchmark suite and executed them on three systems each with different configurations. The first configuration is *Native*, which stands for a system that performs the original application without information flow tracking. In the *Explicit* configuration, our IFTU performs only the explicit flow tracking and therefore the host code is not instrumented. Finally, in *Explicit+Implicit*, IFTU performs the tracking scheme proposed in this paper.

Figure 3.10 shows the execution times for the three configurations normalized to that of *Native*. The results show that the *Explicit* incurs about 1.6% performance overhead although the host code is not instrumented in this configuration. The performance loss is mainly due to the resource competition between the host processor and our IFTU. Since both modules are connected to the same system bus and share

Figure 3.10: Performance Comparison

the same main memory, the bus transactions of IFTU for accessing the main memory slightly degrades the host performance. *Explicit+Implicit*, which stands for our proposed approach, shows an average performance overhead of about 3%. This shows that the overhead caused by our code instrumentation is negligible. Overall, the performance of our approach is much greater than that of the previous hardware approach, RIFLE [101].

We also measured the code size increase due to the code instrumentation. For the given benchmarks, the code size is increased by 0.3% on average. This shows that the code size overhead of our approach is also negligible.

# 3.6 Security Analysis

To evaluate the accuracy of our taint propagation methods, we used a program that has explicit and implicit information flow. We chose a  $\pi$  computing program that calculates the digits of  $\pi$  and uses the sprintf library function to put the ASCII representation of  $\pi$  in the specified buffer. While not strictly a security-related program, we found it adequate for evaluating our implicit flow tracking methods. The program is shown in Listing 1. The program calculates the 1002 digits of  $\pi$ , refining the value at each iteration. The final value will be transformed into the ASCII form by the sprintf call. To transform the sprintf library function to track implicit flow, we have copied the corresponding functions from dietlibc. We have slightly modified the core of the

**Listing 1:**  $\pi$  computing program

sprintf function so that it involves implicit flow when translating decimal digits to the ASCII form.

In the program, if the memory location for the array a is tagged at the start, the correct explicit and implicit information flow tracking scheme should tag the part of the buffer array where the ASCII characters are written. We ran our information tracking hardware after tagging array a, and examined the tagged memory locations after the program is finished. A total of 593 words were tagged, of which 337 were for array a and 250 for buffer. 6 other locations were additionally tagged. We have analyzed the execution trace to find out why those 6 locations were tagged and why there is one missing tag for the buffer array. Since there are 1002 digits of  $\pi$ , 251 words should have been tagged in the buffer array. We found out that all 6 additionally tagged locations are for temporary data in the stack frame that is destroyed when the sprintf function is returned. Those temporary data contained the  $\pi$  digit, its ASCII representation, or the length of the character written for the  $\pi$  digit. Thus, we do not need to regard them as false positives. For the buffer array, we found that the tag corresponding to the last word of the character string has been reset at the end because the sprintf function has put a null value at the end of the character string. Since there is a 1-bit tag for each 4-byte word, the tag corresponding to the last word was reset even though there were two tainted bytes.

The analysis of the results shows that our implicit information flow tracking scheme effectively catches the implicit information flow without significant false positive rates.

Although the sprintf function is quite complicated, our  $t_{PC}$  stack maintenance technique clears the  $t_{PC}$  at the right time so that the tainted tags do not spread throughout memory locations. Although there can also be false positives and false negatives introduced by the granularity of the memory tag, we can expect its impact to be small since character data is usually grouped together.

# 3.7 Summary

This paper presented IFTU, our external hardware engine for implicit (and explicit) flow tracking. To keep track of the implicit flows in a program, we employed a tracking scheme which utilizes a  $t_{PC}$  register and stack together with the code analysis and instrumentation technique that help us correctly manage the value of  $t_{PC}$ . To perform this task efficiently, we have installed within IFTU hardware logic specialized for the task, such as the  $t_{PC}$  stack. We have connected IFTU with the host processor via CDI to acquire the runtime information necessary for tracking, while minimizing the host performance degradation. Our experiments on an FPGA prototype showed that our IFTU can perform both the explicit and implicit flow tracking with only about 3% performance loss. In addition, the synthesis result revealed that the hardware resources required for efficient implicit flow tracking are only about 5.7% of the overall resources for IFTU.

# **Chapter 4**

CRCount: Pointer Invalidation with Reference Counting to Mitigate Use-after-free in Legacy C/C++

## 4.1 Introduction

*Use-after-free* (UAF) errors refer to unlawful dereferences of *dangling pointers*, which are the pointers that still point to a freed and thus stale object. UAF errors constitute a serious threat to software security because they are considered significantly difficult to identify by compilers and manual analyses. This difficulty is attributed to the fact that the temporal distances between arbitrary pointer operations, such as setting a pointer to the address of the object, freeing the object, and dereferencing the pointer, can be very long and hence very difficult to analyze accurately in reality. This difficulty has led attackers to leverage UAF errors as a primary source for exploitation in their attempts [65,110,115] to access or corrupt arbitrary memory locations in a victim process.

In the past decade, mitigation against UAF errors has been approached by many researchers from various directions. In one group of studies [66, 67, 69, 87, 89], researchers attempted to detect the UAF error when a pointer is dereferenced to access its referred object (or *referent*). Their goal is to validate the access to the object by

carrying out a sequence of operations to check whether the referent is stale. To support this *access validation* mechanism, each time an object is allocated, they label the object with a unique *attribute* that identifies the allocation. Later, when a pointer is dereferenced, they examine the attribute of its referent to check whether or not the access is made by a dangling pointer whose referent no longer holds the original valid allocation in memory.

Although mitigation techniques based on access validation are claimed to be extensive and complete, they tend to incur an excessively high performance overhead. This high overhead is attributed to the fact that the attribute checks must be executed exhaustively for every memory access, thereby considerably increasing the total execution time. More recently in a different group of studies, as a new direction of UAF defense research to reduce this performance overhead, some researchers have proposed an approach based on *pointer invalidation* [57, 103, 115]. Their mitigation approach against UAF errors is to deter the violations preemptively by getting rid of the dangling pointers at the outset. As a pointer becomes dangling when its referents get freed, this approach in principle can succeed by invalidating all the related pointers when an object is freed such that an exception is triggered when one of the invalidated pointers is dereferenced afterwards. However in practice, for this approach to be successful, we need to address the problem of accurately tracking down every change, such as the creation, copy, or destruction of pointers, and hence, of identifying pointers and their referents located anywhere on the execution path. Unfortunately, this *pointer* tracking problem in general is prohibitively difficult and expensive to solve with high accuracy because the pointers may be copied into a number of different data structures during program execution.

For precise pointer tracking, DANGNULL [57] uses dynamic range analysis to monitor the pointer arithmetic operations that alter the reference relationships between the pointers and the memory objects. Unfortunately, DANGNULL suffers from a high

performance overhead. A majority of this overhead is attributed to the design element that requires the system to immediately update the metadata for the objects when there is a change in the reference relationships. To alleviate this performance overhead, DangSan [103] takes a different approach wherein the total cost for updating the reference relationships is reduced by discarding the transitional changes intermittently produced in a sequence of pointer arithmetic operations. More specifically, in this approach, when any of the existing reference relationships is changed by pointer arithmetic, this change is not reflected immediately in the relationships (thus saving CPU cycles); instead, the change is merely stored in a history table as a record for future reference. The actual reference relationships are checked later when the object is freed. Experiments on DangSan have proven the effectiveness of this approach by showing that it achieved a considerably lower performance overhead than DANGNULL. However, the experiments also show that the history table can become unbearably large when benchmark programs use pointers intensively. For example, the memory overhead of omnetpp benchmark was more than a hundred times the original memory consumption. As UAF errors are more likely to be prevalent in programs with a heavy use of pointers, such an immense memory overhead might be a significant obstacle for a broad application of this approach.

From the observations on previous work, we found that such a high overhead, either performance-wise or space-wise, of the existing pointer invalidation techniques is basically caused by the approach that when an object is freed, these techniques promptly locate and explicitly invalidate all the pointers referring to the object. This *explicit pointer invalidation* approach seems to be intuitive as it mitigates UAF errors by eradicating the root cause (i.e. dangling pointers), but it is usually very costly as it demands expensive algorithms or a large amount of space to maintain the up-to-date list of pointer locations linking to each object at all times during program execution. DANGNULL spends many CPU cycles to manage binary trees as the data structures

to store pointer locations. Every time there is a change in one of the locations, the trees are traversed and modified accordingly, consuming a considerable amount of the execution time. Even worse, the total performance overhead increases in proportion to the numbers of pointers and referents, which can increase considerably for programs, such as omnetpp, that perform frequent arithmetic operations on a myriad of pointers.