Ph.D. DISSERTATION

# Design Methodology for Cost Effective Clock and Power Gating

비용 효율적인 클럭 및 파워 게이팅 설계 방법론

BY

GYOUNGHWAN HYUN

FEBRUARY 2020

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING COLLEGE OF ENGINEERING SEOUL NATIONAL UNIVERSITY Ph.D. DISSERTATION

# Design Methodology for Cost Effective Clock and Power Gating

비용 효율적인 클럭 및 파워 게이팅 설계 방법론

BY

GYOUNGHWAN HYUN

FEBRUARY 2020

DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING COLLEGE OF ENGINEERING SEOUL NATIONAL UNIVERSITY

### Design Methodology for Cost Effective Clock and Power Gating

비용 효율적인 클럭 및 파워 게이팅 설계 방법론

지도교수 김 태 환

이 논문을 공학박사 학위논문으로 제출함

2019년 12월

서울대학교 대학원

전기정보공학부

현경환

현경환의 공학박사 학위 논문을 인준함

2020년 1월

| 위 원 장:               |  |

|----------------------|--|

| 부위원장:                |  |

| 위 원:                 |  |

| 위 원:                 |  |

| 위 원:<br>위 원:<br>위 원: |  |

### Abstract

Low power design is of great importance in modern system-on-chips (SoCs). This dissertation studies on low power design methodologies for saving dynamic and static power consumption. Precisely, we unveil two novel techniques of cost effective low power design.

Firstly, we propose a novel clock gating method for reducing the dynamic power consumption. Flip-flop's input data toggling based clock gating is one of the most commonly used clock gating methods, in which one critical and inherent limitation is the sharp increase of gating logic as more flip-flops are involved in gating. In this dissertation, we propose a new clock gating method to overcome this limitation. Specifically, (1) we analyze the resources of gating logic in the input data toggling based clock gating, from which an ineffectiveness in resource utilization is observed and we propose a new clock gating technique called *flip-flop state driven clock gating* which completely eliminates the essential and expensive component of XOR gates for detecting input toggling of flip-flops; (2) we provide the supporting logic circuitry of our proposed XOR-free clock gating, confirming its safe applicability through a comprehensive timing analysis; (3) we propose, based on the flip-flops' state profile, a clock gating methodology that seamlessly combines our flip-flop state based clock gating with the toggling based clock gating. Through experiments with benchmark circuits, it is confirmed that our clock gating method is very effective in reducing power, which otherwise the toggling based clock gating shall miss the power saving opportunity, while meeting all timing constraints.

Secondly, for reducing the static power consumption, we solve two critical limitations of the conventional approaches to the allocation of state retention storage for power gated circuits. Those are (1) the *long wakeup delay* caused by the senseless use of multi-bit retention flip-flops (MBRFFs) and (2) the inability to optimize retention flip-flops for the flip-flops with mux-feedback loop. It should be noted that the conventional approaches have regarded the long wakeup delay as an inevitable consequence of maximizing the reduction of total storage size for state retention while they have treated the flip-flops with mux-feedback loop (called self-loop flip-flop) as nonoptimizable component, but practically, the self-loop flip-flops synthesized from hardware description language (HDL) code are not far from a small amount and thus, can in no way be negligible. More precisely, for solving (1), we show that the use of MBRFFs with up to two bits, consequently, constraining the wakeup delay to no more than two clock cycles, is enough to maintain the high reduction of total retention storage and for solving (2), we devise a 2-phase retention control mechanism for a pair of flipflops, one of which has self-loop, by which just a single retention bit can be used to restore state of the two flip-flops, and propose an independent set based algorithm for maximally extracting the non-conflict pairs from circuits. Through experiments with benchmark circuits, it is shown that our proposed method is very effective against reducing the state retention storage and the power consumption compared with the existing best MBRFF allocation while the wakeup delay is strictly limited to two clock cycles.

**Keywords**: Low power, Clock gating, Power gating, State retention, Retention flip-flop **Student number**: 2016-30222

# Contents

| Al                                                      | ostrac  | et      |                                                | i   |

|---------------------------------------------------------|---------|---------|------------------------------------------------|-----|

| Co                                                      | onten   | ts      |                                                | iii |

| Li                                                      | st of [ | Fables  |                                                | v   |

| Li                                                      | st of l | Figures |                                                | vii |

| 1                                                       | INT     | RODU    | CTION                                          | 1   |

|                                                         | 1.1     | Clock   | Gating                                         | 1   |

|                                                         | 1.2     | Power   | Gating and State Retention                     | 3   |

|                                                         | 1.3     | Multi-  | bit Retention Registers                        | 4   |

|                                                         | 1.4     | Contri  | butions of This Dissertation                   | 6   |

| 2 FLIP-FLOP STATE DRIVEN CLOCK GATING: CONCEPT, DESIGN, |         |         | ,                                              |     |

|                                                         | ANI     | O MET   | HODOLOGY                                       | 9   |

|                                                         | 2.1     | Motiva  | ations                                         | 9   |

|                                                         |         | 2.1.1   | Toggling based Clock Gating                    | 9   |

|                                                         |         | 2.1.2   | Area and Power by Clock Gating                 | 10  |

|                                                         | 2.2     | The Pr  | roposed Clock Gating                           | 13  |

|                                                         |         | 2.2.1   | Concept of Flip-flop State Driven Clock Gating | 13  |

|                                                         |         | 2.2.2   | Design of Gating Logic Circuitry               | 17  |

|                                                         |         | 2.2.3   | Integrated Clock Gating Methodology            | 22  |

|    |                        | 2.2.4    | Cost Formulation                                               | 23  |

|----|------------------------|----------|----------------------------------------------------------------|-----|

|    | 2.3                    | Experin  | ments                                                          | 25  |

|    |                        | 2.3.1    | Experimental Setup                                             | 25  |

|    |                        | 2.3.2    | Experimental Results                                           | 26  |

| 3  | ALG                    | GORITH   | IM AND DESIGN OPTIMIZATION OF ALLOCATING MUL                   | ЛI- |

|    | BIT                    | RETEN    | TION FLIP-FLOPS FOR POWER GATED CIRCUITS                       | 32  |

|    | 3.1                    | Motiva   | tions                                                          | 32  |

|    |                        | 3.1.1    | Flip-flops with Mux-feedback Loop                              | 32  |

|    |                        | 3.1.2    | Impact of Wakeup Delay                                         | 37  |

|    | 3.2                    | The Pro  | oposed Allocation Algorithm                                    | 39  |

|    | 3.3                    | Design   | of Multi-Bit Retention Flip-Flop and Multi-Bit Extension       | 48  |

|    |                        | 3.3.1    | Multi-Bit Retention Flip-Flop                                  | 48  |

|    |                        | 3.3.2    | Multi-Bit Flip-Flop Extension                                  | 52  |

|    | 3.4                    | Experin  | ments                                                          | 54  |

|    |                        | 3.4.1    | Experimental Setup                                             | 54  |

|    |                        | 3.4.2    | Experimental Results                                           | 57  |

| 4  | CON                    | ICLUSI   | IONS                                                           | 65  |

|    | 4.1                    | Flip-flo | op State Driven Clock Gating: Concept, Design, and Methodology | 65  |

|    | 4.2                    | Algorit  | hm and Design Optimization of Allocating Multi-bit Retention   |     |

|    |                        | Flip-flo | ops for Power Gated Circuits                                   | 66  |

| Ab | Abstract (In Korean) 7 |          |                                                                | 71  |

|    |                        |          |                                                                |     |

# **List of Tables**

| 2.1 | Benchmark circuit information                                                                                        |

|-----|----------------------------------------------------------------------------------------------------------------------|

| 2.2 | Comparison of the clock gating ratio, the number of clock gating cells                                               |

|     | (i.e., ICGs), the clock tree power $P_{clk}$ , the flip-flop power $P_{ff}$ , the                                    |

|     | combination logic power $P_{combi}$ including the power by clock gat-                                                |

|     | ing logic, the total power $P_{total}$ produced (1) by the conventional idle                                         |

|     | logic driven clock gating (Logic-driven CG), produced (2) by Logic-                                                  |

|     | driven CG followed by the conventional toggling driven clock gating                                                  |

|     | (Toggling-driven CG), and produced (3) by Logic-driven CG fol-                                                       |

|     | lowed by our state driven clock gating (State-driven CG), finally ap-                                                |

|     | plying Toggling-driven CG.                                                                                           |

|     | $^{\dagger}$ Excluding the power consumed by the internal clock inverters in the flip-flops. $^{\ddagger}$ Including |

|     | the power consumed by the internal clock inverters in the flip-flops                                                 |

| 2.3 | Comparison of total area and cell area used (1) by the conventional                                                  |

|     | idle logic driven clock gating (Logic-driven CG), used (2) by Logic-                                                 |

|     | driven CG followed by the conventional toggling driven clock gating                                                  |

|     | (Toggling-driven CG), and used (3) by Logic-driven CG followed                                                       |

|     | by our state driven clock gating (State-driven CG), finally applying                                                 |

|     | Toggling-driven CG.    30                                                                                            |

| 3.1 | Proportion of self-loop FFs in IWLS benchmark circuits                                                               |

| 3.2 | State retention and restoration for the three types of retention flip-flop.      |    |

|-----|----------------------------------------------------------------------------------|----|

|     | (The notations in parentheses represent the values in the retention stor-        |    |

|     | age of the corresponding SBRFFs/MBRFF and cycle times.)                          | 40 |

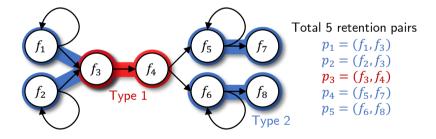

| 3.3 | State restoration of flip-flops in a retention pair $p(f_i, f_j)$ where $f_i$ is |    |

|     | minimally allocated by a 1st-phase SBRFF. The state of $f_i$ at the sec-         |    |

|     | ond cycle will be set by one of the blue solid and red dotted arrows if          |    |

|     | $f_i$ is a self-loop FF (i.e., type 2 retention pair) and otherwise (i.e., type  |    |

|     | 1 retention pair) will be set only by the blue arrow                             | 42 |

| 3.4 | Benchmark circuit information                                                    | 57 |

| 3.5 | Comparison of the previous non-uniform MBRFF approaches ([18])                   |    |

|     | with flow options 1 and 2, and our proposed approach                             | 58 |

| 3.6 | Comparison of active power and sleep power consumption used by                   |    |

|     | SBRFF (conventional single bit retention flip-flop allocation for sin-           |    |

|     | gle bit flip-flops), SBR-MBFF (conventional single bit retention flip-           |    |

|     | flop allocation for multi-bit flip-flops), MBRFF (our multi-bit reten-           |    |

|     | tion flip-flop allocation for single-bit flip-flops), and MBR-MBFF (our          |    |

|     | multi-bit retention flip-flop allocation for multi-bit flip-flops)               | 60 |

| 3.7 | Comparison of total area and cell area used by SBRFF (conventional               |    |

|     | single bit retention flip-flop allocation for single bit flip-flops), SBR-       |    |

|     | MBFF (conventional single bit retention flip-flop allocation for multi-          |    |

|     | bit flip-flops), MBRFF (our multi-bit retention flip-flop allocation for         |    |

|     | single-bit flip-flops), and MBR-MBFF (our multi-bit retention flip-flop          |    |

|     | allocation for multi-bit flip-flops).                                            | 62 |

| 3.8 | Multi-bit information of the MBR-MBFF based designs.                             | 63 |

# **List of Figures**

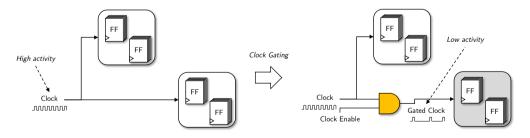

| 1.1 | Clock gating.                                                                         | 1  |

|-----|---------------------------------------------------------------------------------------|----|

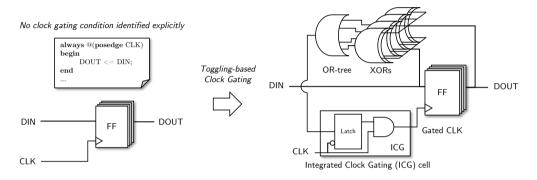

| 1.2 | Toggling-based clock gating.                                                          | 2  |

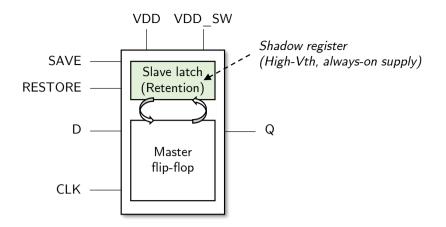

| 1.3 | Structure of a single-bit retention flip-flop. A slave latch for retention is         |    |

|     | designed with high-Vt transistors and powered by an always-on power                   |    |

|     | supply (VDD).                                                                         | 4  |

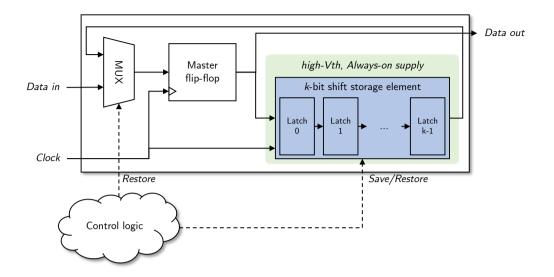

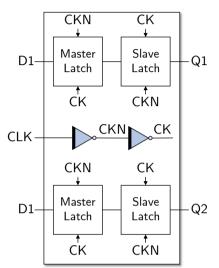

| 1.4 | Structure of a multi-bit retention flip-flop (MBRFF). The <i>k</i> -bit ( $k \ge 1$ ) |    |

|     | shift storage element is used to store prior $k$ consecutive states of the            |    |

|     | <i>regular flip-flop</i> just before entering the sleep mode                          | 5  |

| 2.1 | (a) Block-level structure of the input data toggling based clock gat-                 |    |

|     | ing [8], in which the logic blocks added for clock gating are marked                  |    |

|     | with yellow color. (b) The changes of area including XORs (i.e., FFs                  |    |

|     | + XORs + OR-tree + ICG) and excluding XORs (i.e., FFs + OR-tree                       |    |

|     | + ICG) as the flip-flop grouping size $k$ changes. (c) The changes of                 |    |

|     | power consumption including (i.e., FFs + XORs + OR-tree + ICG)                        |    |

|     | and excluding XORs (i.e., FFs + OR-tree + ICG) as the grouping size                   |    |

|     | changes                                                                               | 11 |

| 2.2 | Flip-flop distribution with respect to the state-1 probability measured               |    |

|     | by simulation for a set of IWLS benchmark circuits                                    | 14 |

| 2.3 | (a) State-0/1 waveforms of flip-flops $f_1, f_2, \ldots, f_5$ in which $f_1, f_2$                  |    |

|-----|----------------------------------------------------------------------------------------------------|----|

|     | and $f_3$ are stuck at state-0 most of time while $f_4$ and $f_5$ are stuck at                     |    |

|     | state-1 most of time. (b) State-0 waveforms and ratios in Definition 2                             |    |

|     | of $\{f_1, f_2\}$ and $\{f_1, f_3\}$ derived from (a). (c) State-1 waveform and                    |    |

|     | ratio in Definition 3 of $\{f_4, f_5\}$ derived from (a).                                          | 15 |

| 2.4 | Circuitry of the proposed state driven clock gating. (a) Block-level                               |    |

|     | structure, in which the logic blocks added for clock gating are marked                             |    |

|     | with yellow color. (b) Clock Disable (CD) block including OR-tree                                  |    |

|     | to assert the clock enable for flip-flops that have a high probability of                          |    |

|     | state-0. (c) Clock Disable (CD) block including AND-tree to assert the                             |    |

|     | clock enable for flip-flops that have a high probability of state-1                                | 18 |

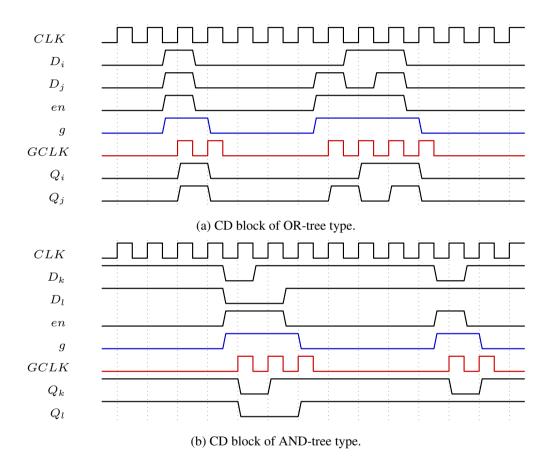

| 2.5 | Timing waveforms of the signals on (a) CD block of OR-tree type in                                 |    |

|     | Fig. 2.4(b) and (b) CD block of AND-tree type in Fig. 2.4.                                         | 20 |

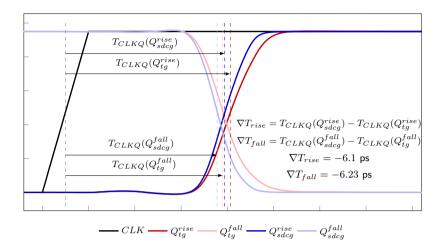

| 2.6 | Timing waveforms by HSPICE simulation for the clock-to-Q delay                                     |    |

|     | $(T_{CLKQ})$ on a flip-flip in the toggling driven clock gating $(Q_{tg}: \text{red})$             |    |

|     | curves) and a flip-flop in our state driven driven clock gating ( $Q_{sdcg}$ :                     |    |

|     | blue curves)                                                                                       | 21 |

| 2.7 | Timing waveforms by HSPICE simulation for the delay of CD blocks                                   |    |

|     | in the toggling driven clock gating (red curves) and our state driven                              |    |

|     | clock gating (blue curves). The flip-flop group size is $k = 2, 4, \ldots, 16$ .                   | 21 |

| 2.8 | Example of generating a flip-flop group $S_i$ for clock gating. The input                          |    |

|     | flip-flop set $\mathcal{F}$ is $\{f_1, f_2, f_3, f_4, f_5\}$ and $f_1$ is picked as a seed in Step |    |

|     | 2.2                                                                                                | 24 |

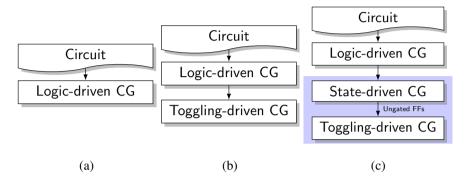

| 2.9 | $Tested \ clock \ gating \ flows. \ (a) \ Logic-driven \ CG \ only. \ (b) \ Logic-driven$          |    |

|     | CG followed by Toggling-driven CG. (c) Logic-driven CG followed                                    |    |

|     | by our State-driven CG and finally Toggling-driven CG. $\ldots$ .                                  | 26 |

|     |                                                                                                    |    |

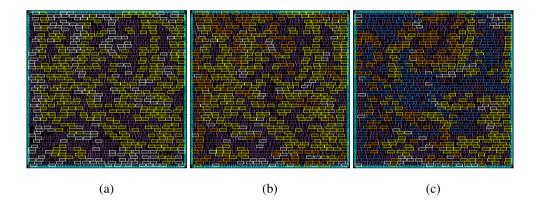

| 2.10 | Layouts for WB_DMA. The colored rectangles represent flip-flops: un-               |    |

|------|------------------------------------------------------------------------------------|----|

|      | gated (white), gated by Logic-driven CG (yellow), gated by Toggling-               |    |

|      | driven CG (orange), gated by our State-driven CG (blue). (a) Lay-                  |    |

|      | out produced by Logic-driven CG. (b) Layout produced by Toggling-                  |    |

|      | driven CG. (c) Layout produced by our State-driven CG                              | 31 |

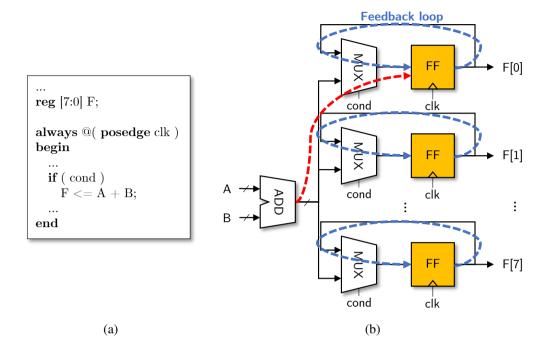

| 3.1  | Synthesis of flip-flops with mux-feedback loop. (a) a Verilog HDL                  |    |

|      | code (b) a synthesized structure for the code in (a). $\ldots$                     | 33 |

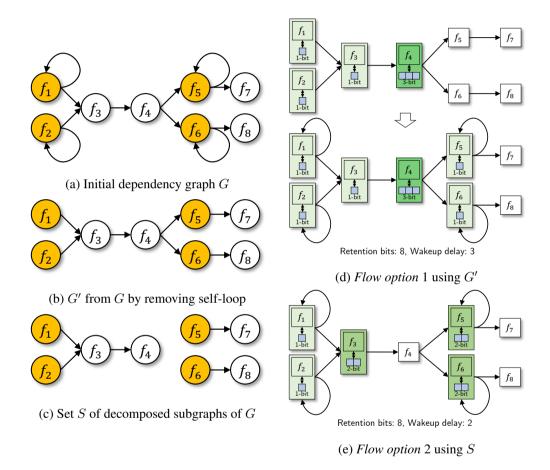

| 3.2  | Two flow options used by the conventional approaches of allocating                 |    |

|      | retention flip-flops to circuits with self-loop FFs                                | 35 |

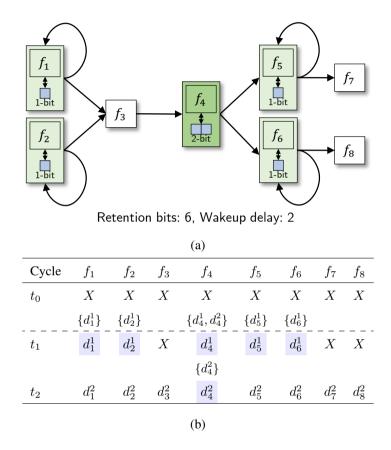

| 3.3  | (a) A better allocation of retention bits over that in Fig. 3.2. (b) The           |    |

|      | state restoration of the wakeup sequence for the retention bit allocation          |    |

|      | in (a). ( $\{\cdots\}$ indicates the state(s), to be used when waking up, stored   |    |

|      | in the retention bit(s) and $d_i^j$ indicates the state of flip-flop $f_i$ at time |    |

|      | $t_j, j = 1, 2.$ )                                                                 | 36 |

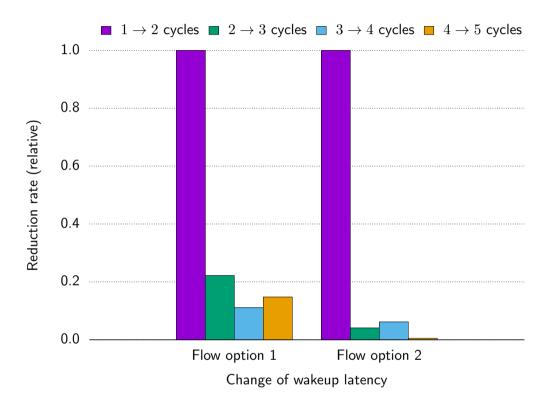

| 3.4  | Average changes of the reduction rate of the total size of retention               |    |

|      | storage by Flow options 1 and 2 using [18] as the wakeup latency                   |    |

|      | changes for IWLS benchmark circuits in Table 3.1                                   | 38 |

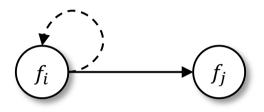

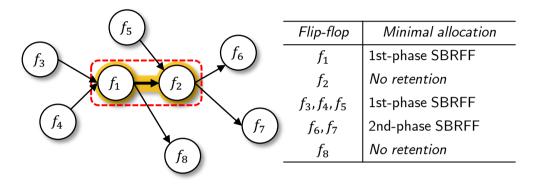

| 3.5  | Retention pair $p(f_i, f_j)$                                                       | 41 |

| 3.6  | Retention pairs of type 1 (in red color) and type 2 (in blue color) in a           |    |

|      | flip-flop dependency graph $G$                                                     | 41 |

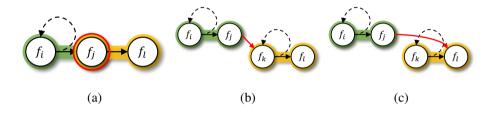

| 3.7  | Conditions of conflict between retention pairs. (a) Condition $1$ (b)              |    |

|      | Condition 2 (c) Condition 3.                                                       | 43 |

| 3.8  | Minimally required retention bits for the flip-flops in a retention pair           |    |

|      | $p(f_1, f_2)$ and its driving and driven flip-flops                                | 44 |

| 3.9  | Two retention pairs that cause conflicts due to each of <i>conditions 1</i> ,      |    |

|      | 2, and 3, and the minimally required retention bits for the green pair             |    |

|      | when the yellow pair is allocated by the minimally required retention              |    |

|      | bits                                                                               | 45 |

| 3.10 | Tie-breaking based on the cost formulation in $Eq.(3.1)$                 | 47 |

|------|--------------------------------------------------------------------------|----|

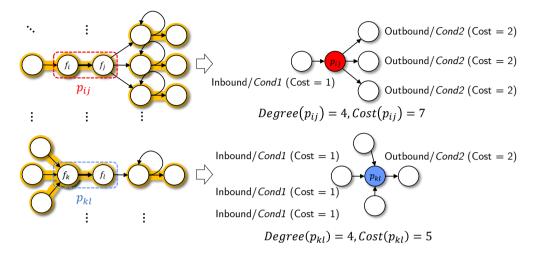

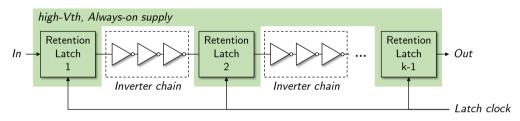

| 3.11 | Conceptual schematic of the pulsed latch array of the $k$ -bit retention |    |

|      | register in [14]. High-Vt transistors powered by an always-on power      |    |

|      | supply are used for the retention latches (in green color)               | 48 |

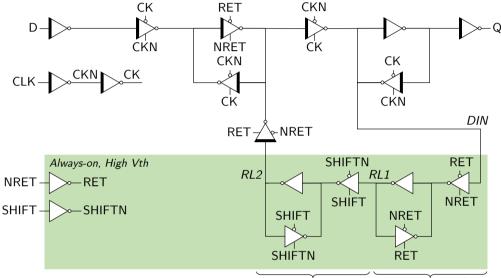

| 3.12 | Schematic of our 2-bit MBRFF. The always-on supply region in green       |    |

|      | color consists of two retention latches and two input inverters for con- |    |

|      | trol pins <i>NRET</i> and <i>SHIFT</i>                                   | 49 |

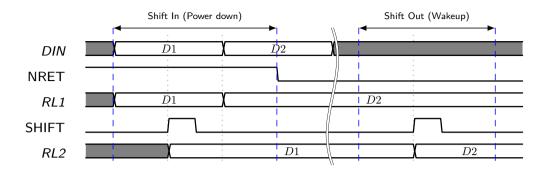

| 3.13 | Waveforms of the 2-bit shift register using two control signals          | 50 |

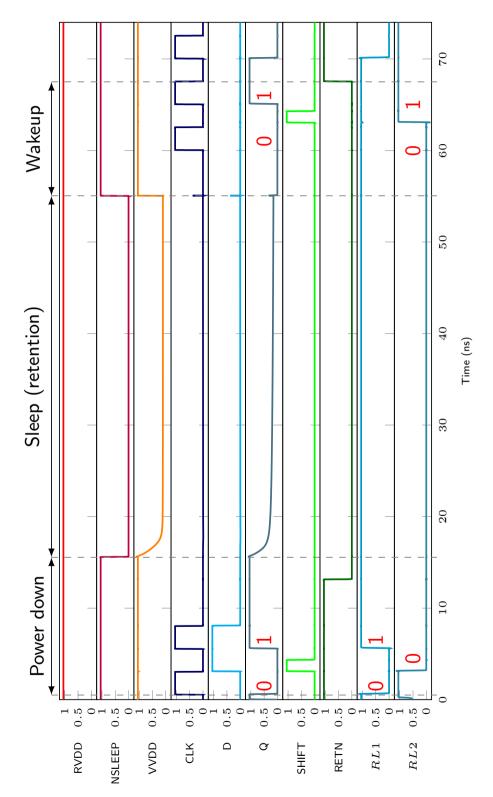

| 3.14 | Spice simulation waveforms of a 2-bit MBRFF                              | 51 |

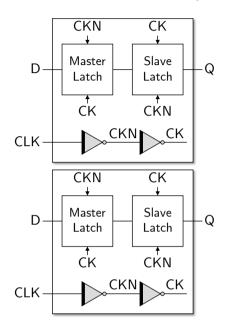

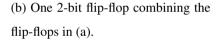

| 3.15 | Comparison of the internal structures of the 1-bit master-slave based    |    |

|      | flip-flop and the 2-bit master-slave flip-flop                           | 52 |

| 3.16 | Schematic of a 2-bit/2-bit MBR-MBFF. The cells in light blue color       |    |

|      | are shared between two master flip-flops $FF1$ and $FF2$                 | 53 |

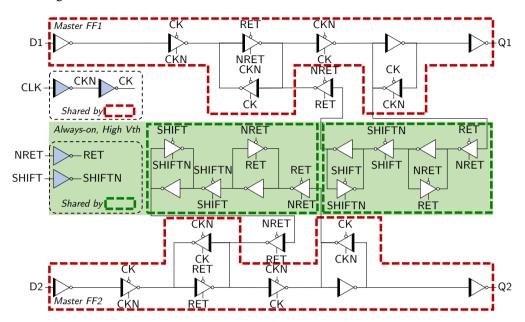

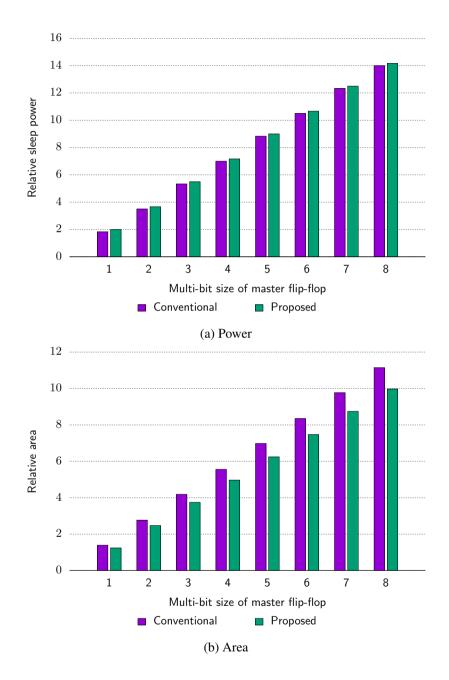

| 3.17 | Comparison of power and area of a MBR-MBFF between the conven-           |    |

|      | tional design and the proposed design. The size of the retention storage |    |

|      | is 2-bit.                                                                | 55 |

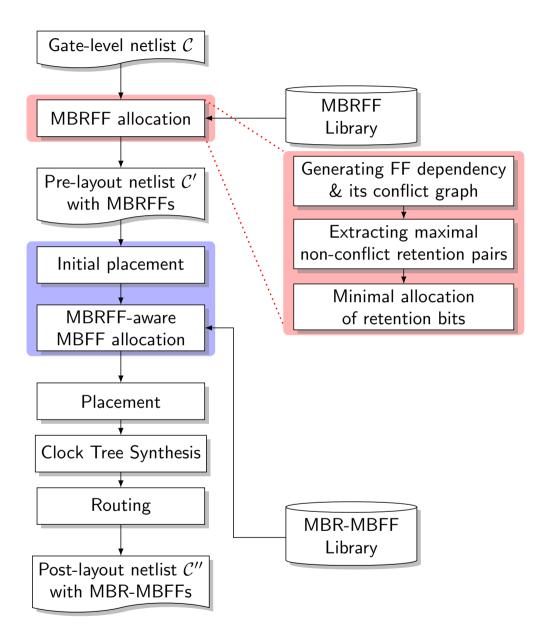

| 3.18 | Design flow of the proposed MBR-MBFF approach                            | 56 |

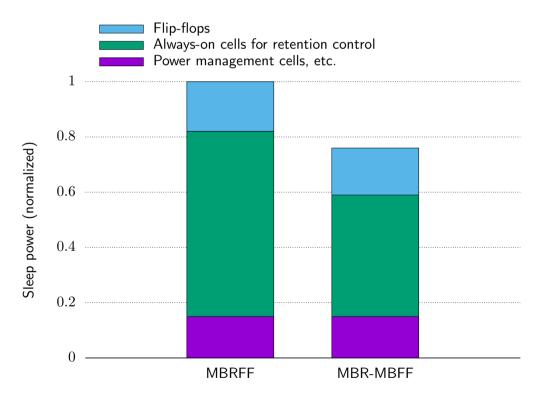

| 3.19 | Sleep power breakdown of our MBRFF approach without MBFF ex-             |    |

|      | tension (MBRFF) and MBRFF approach with MBFF extension (MBR-             |    |

|      | MBFF)                                                                    | 63 |

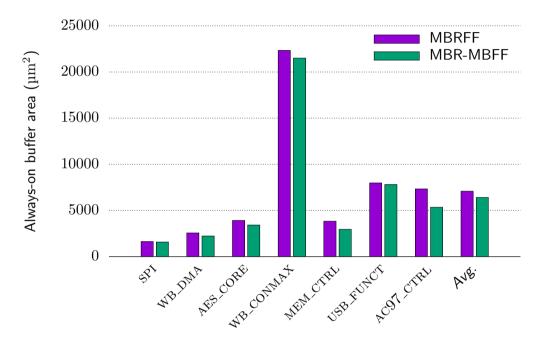

| 3.20 | Comparison of always-on cell area of our MBRFF approach without          |    |

|      | MBFF extension (MBRFF) and MBRFF approach with MBFF exten-               |    |

|      | sion (MBR-MBFF).                                                         | 64 |

### **Chapter 1**

### **INTRODUCTION**

### 1.1 Clock Gating

In synchronous digital system, a large portion of dynamic power is consumed by the clock signal, taking over 40% of total power consumption in the entire systems [1, 2]. As a vehicle to reduce the dynamic power consumption, a technique by gating clock signals has been known to be one of the most powerful techniques. As shown in Fig. 1.1, *Clock gating* saves dynamic power by shutting off a subtree of clock network during idle state of the driven logic blocks or by disabling the clock signals to a group or groups of flip-flops during their untoggling states.

Figure 1.1: Clock gating.

For the situation where designers have a prior knowledge of or can explicitly or implicitly extract simple logic conditions for some blocks in a circuit that can be safely in an idle state, the idle state based clock gating can be applied to the part of clock network that drives the blocks. Note that the clock enable/disable logic conditions are generally extracted in the system or RTL design stage since the inter-dependency of the execution among the logic sub-blocks is easily identifiable in those stages. However, for the case where it is not easy or apparent to identify simple logic for clock gating or there is no subcircuit block of reasonable size for clock gating, the toggling based clocking gating can be the best alternative as shown in Fig. 1.2.

Figure 1.2: Toggling-based clock gating.

One important consideration in applying the toggling based gating is that since the toggling based clock gating is a flip-flop level fine-grained gating, the sharp increase of the supplemental logic required for detecting input toggling/untoggling of every flip-flop for clock gating as well as generating enabling/disabling clock signal is a big power burden on the circuits. Even so, there are many design cases available, to which the application of toggling based clock gating [3], for instance, being reported for some controller design that its idle based gating to RTL blocks reduces the power dissipation by  $23\sim27\%$  while its toggling based gating to flip-flops reduces the power more than double [4].

The traditional toggling based clock gating can be implemented at various design levels, from architecture-level to cell-level (e.g., [5, 6, 7, 8]). The main focuses of most of the existing methods of the clock gating are aggressively selecting candidate flipflops for clock gating and grouping the flip-flops for gating to (partially) share gating logic at the expense of degradation of power saving (e.g., [9, 10]).

#### **1.2** Power Gating and State Retention

As the semiconductor process technology shrinks, the impact of leakage power on power consumption has been significantly increased and it has been extremely important to reduce leakage power in modern SoCs. Power gating has been widely used and has become one of the most popular design techniques to reduce the leakage power consumption, thus to extend the battery lifetime in industrial products [11]. However when the circuit goes the sleep mode by power gating, the state of flip-flops may be lost. Therefore, a proper state restoration scheme is required to backup the state when the circuit wakes up [12].

One commonly adopted restoration methodology is replacing each regular flip-flop with a unique retention flip-flop that is able to perform the additional role of retaining a prior state during the sleep mode [13]. While there are several variants on the implementation of retention flip-flop, it is basically composed of two components: one is a master flip-flop and the other is a slave latch. The master is designed with low-Vt transistors for fast switching during the active mode while the slave retains the prior state (i.e., 0 or 1) of the master flip-flop during the sleep mode and is designed with high-Vt transistors to save leakage power during the sleep mode as shown in Fig. 1.3. According to [14], applying this single-bit retention flip-flops (SBRFFs) causes in general 20% area overhead over the regular flip-flops. Therefore, it is quite important to minimize the total storage size of retention flip-flops (equivalently, the total number of bits to be used to retain circuit state during the sleep mode) to be deployed.

To reduce total storage size of retention flip-flops, the selective state retention power gating (SSRPG) techniques have been proposed [15, 16]. This techniques are basically based on the assumption that relatively small essential flip-flops are required

Figure 1.3: Structure of a single-bit retention flip-flop. A slave latch for retention is designed with high-Vt transistors and powered by an always-on power supply (VDD).

to restore the state of entire flip-flops of the designs. However, these approaches are based on an exhaustive simulation or a formal analysis and require a knowledge of operations of the design, which are impractical in general.

#### **1.3 Multi-bit Retention Registers**

On the other hand, Chen *et al.* [14, 17] proposed to use multi-bit retention flip-flops (MBRFFs) whose internal structure is shown in Fig. 1.4.

While an SBRFF has a single-bit storage element for retaining a single-bit state, an MBRFF has a k-bit ( $k \ge 1$ ) shift storage element for retaining k-bit states of the regular (master) flip-flop. Before a circuit enters the sleep mode, consecutive prior states of the master flip-flop are stored in the k-bit storage element sequentially and then the states stored are retained during the sleep mode. When the circuit wakes up, the stored state data will be shifted out to the master flip-flop for k consecutive cycles, propagating them to the neighboring flip-flops through the connected combinational logic. Chen *et al.* [14, 17] attempted to solve the problem of allocating k-bit *uniform* MBRFFs with the objective of minimizing the number of flip-flops to be replaced with

Figure 1.4: Structure of a multi-bit retention flip-flop (MBRFF). The *k*-bit ( $k \ge 1$ ) shift storage element is used to store prior k consecutive states of the regular flip-flop just before entering the sleep mode.

*k*-bit retention flip-flops. They showed that even though the transition latency between sleep and active modes takes k - 1 more cycles over the case of applying SBRFFs, the use of MBRFFs considerably decreases total storage size of the retention registers used in power gating, thereby further reducing the power consumption. Based on the MBRFF technique, recently Fan *et al.* [18] proposed an integer linear programming (ILP) based incremental greedy method that is able to allocate *non-uniform* MBRFFs of various sizes of retention storage under the constraint of maximum wake-up latency bound. The objective function to be minimized in each iteration of the method is the amount of storage size required for retaining the state of flip-flops in the ready list. However, both uniform and non-uniform MBRFF replacement techniques have two critical limitations. Those are (1) the *long wakeup delay* caused by the senseless use of MBRFFs and (2) the inability to optimize retention flip-flops for the *flip-flops with mux-feedback loop*. Note that the prior approaches have regarded the long wakeup delay as an inevitable consequence of maximizing the reduction of total storage size for

state retention while they have treated the flip-flops with self-loop as nonoptimizable component, but the flip-flops with self-loop synthesized from HDL code are prevalent in practice and thus, can in no way be negligible.

#### **1.4** Contributions of This Dissertation

In this dissertation, Chapter 2 and Chapter 3 present novel low power techniques for reducing dynamic power consumption and static power consumption respectively.<sup>1</sup>

In Chapter 2, we propose a new clock gating technique by addressing (1) how the supplemental (non-sharing) logic for toggling based clock gating can be elegantly reduced or completely eliminated while maximally reaping the benefit of power saving by the clock gating and (2) how the input toggling based clock gating flow is seam-lessly integrated into our clock gating flow to maximally exploit the synergy effect on power saving.

The contributions of this work are summarized as:

- 1. We analyze the resources of gating logic in input data toggling based clock gating, from which we observe an ineffectiveness in resource utilization and propose a new clock gating technique called *flip-flop state driven clock gating*, which completely eliminates the essential component of XOR gates for detecting input toggling of flip-flops.

- 2. We provide the *XOR-free gating logic circuitry supporting our flip-flop state driven clock gating*, confirming its safe applicability through a comprehensive timing analysis.

- 3. We propose, based on the flip-flops' state profile, a *clock gating methodology* that seamlessly integrates our flip-flop state driven clock gating with the application flow of the conventional toggling driven clock gating.

<sup>&</sup>lt;sup>1</sup>Preliminary versions of this work were presented in [19] and [20]

4. A set of experiments with benchmark circuits is performed to assess how much our new clock gating methodology is effective in saving power without timing violation.<sup>2</sup> In summary, ours is able to achieve on average 7.59% more power saving over the input data toggling based clock gating.

In Chapter 3, we propose a new allocation algorithm of multi-bit retention registers for power gated circuits to overcome the limitations of conventional approaches: (1) the long wakeup delay; (2) the inability to optimize the flip-flops with mux-feedback loop. Precisely, for solving (1), we show that the use of MBRFFs with up to two bits, consequently, constraining the wakeup delay to no more than two clock cycles, is enough to maintain the high reduction of total retention storage and for solving (2), we devise a 2-phase retention control mechanism for a pair of flip-flops, one of which has self-loop, by which just a single retention bit can be used to restore state of the two flip-flops, and propose an independent set based algorithm for maximally extracting the non-conflict pairs from circuits.

The contributions of this work are summarized as:

- 1. Unlike the conventional approaches, which have tried to reduce the retention storage at the expense of (long) wakeup delay, we develop an effective algorithm for *MBRFF allocation that is specialized to the wakeup delay constrained to two clock cycles*.

- 2. While the conventional approaches have invariably taken into no consideration of the retention storage optimization for the flip-flops with self-loop together with their neighbor flip-flops, we propose *a 2-phase retention control scheme, so that just a single retention bit can be used* to restore state of a flip-flop with self-loop and one of its neighbors.

<sup>&</sup>lt;sup>2</sup>Our proposed clock gating in this work is carried out after the completion of cell placement, from which the location information of the flip-flops is available. However, if the wire delay perturbation is not a serious concern, our clock gating is also applicable to the logic synthesis stage.

- 3. Based on the proposed control scheme, we formulate the retention storage reduction problem into an *independent set based problem and we develop an effective heuristic* that maximally extracts non-conflict pairs of flip-flops from circuits.

- 4. We propose a new design of a multi-bit retention flip-flop and its multi-bit flipflop extension to reduce the area and power overhead of multi-bit retention flipflops and control paths for state retention powered by an always-on power supply.

- 5. Experimental data are provided to show how much our proposed approach reduces the total retention storage size for practical designs while the wakeup delay is constrained to up to two cycles. In short, our approach is able to use the retention storage by 9.8% less on average over that used by the state-of-the-art MBRFF method.

The rest of the paper is organized as follows. Chapter 2 describes the concept, design, and methodology of our flip-flop state driven clock gating. Then, Chapter 3 describes a new allocation algorithm and design of multi-bit retention flip-flops for power gated circuits. Finally, Chapter 4 presents the conclusions of this dissertation.

### Chapter 2

## FLIP-FLOP STATE DRIVEN CLOCK GATING: CON-CEPT, DESIGN, AND METHODOLOGY

#### 2.1 Motivations

#### 2.1.1 Toggling based Clock Gating

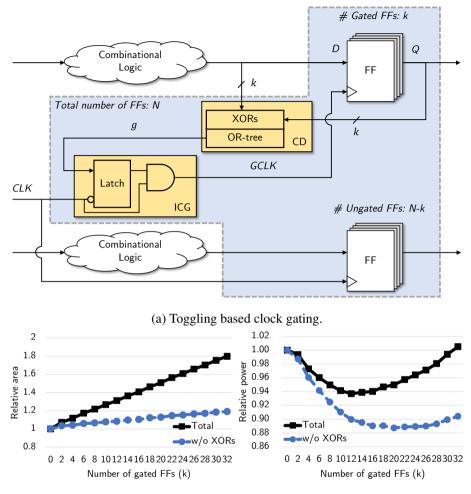

Flip-flop's input data toggling based clock gating shuts off the clock signal to a flip-flop when the state of the flip-flop is not subject to change at the next clock cycle. A block-level circuit structure supporting the clock gating for a group of k flip-flops ( $R = \{f_1, f_2, ..., f_k\}$ ) is shown in Fig. 2.1(a) [8], in which the newly added logic blocks (i.e., *Clock Disable* (CD) and *Integrated Clock Gating* (ICG) [21]) to the original circuit are marked with yellow color.

The logic operations of CD and ICG are:

• CD (= XORs + OR-tree): Boolean equation for CD can be expressed as:

$$g = (D_1 \oplus Q_1) + (D_2 \oplus Q_2) + \dots + (D_k \oplus Q_k)$$

(2.1)

Thus, the implementation requires k 2-input XOR gates, one for each flip-flop, and an OR-tree consisting of k-1 2-input OR gates. The equation indicates that if g is 1, there is at least one flip-flop in R that will change its state at the next clock cycle. Thus, the condition of disabling clock signal to *all* k flip-flops i n R at the next clock cycle is  $\bar{g}$ .

• ICG (= Latch + AND): It receives the logic value of *g* from CD and decides if the clock signal is to be disabled or not while synchronizing it to the rising edge of *CLK*.

The effectiveness of the toggling based clock gating on reducing power closely relies on the number of occurrences of the clock cycles at which g is false (i.e., all flip-flops simultaneously untoggling).

One strong evidence of the usefulness of the toggling based clock gating can be found in [3], which measured statistical toggling data of more than 22,000 flip-flops in a DSP core and found that on average 95% of clock signals to the flip-flops in a clock cycle was untoggled. On the other side, this evidence has cast a strong doubt towards us on *"is it really necessary to allocate an expensive 2-input XOR for every flip-flop in toggling driven clock gating?"* for the circuits with such extremely biased toggling distribution. That is, there is an important factor that has not been carefully addressed by the existing works on the toggling based clock gating. Precisely, the resulting clock gating logic components (XORs and OR-tree in CD and a latch in ICG) incur area overhead, which causes nontrivial impact on power. The following subsection describes in-depth analyses of the gating overhead.

#### 2.1.2 Area and Power by Clock Gating

We performed power analysis using Synopsys *PrimeTime-PX* to the blocks enclosed by the dotted line in Fig. 2.1(a), varying the flip-flop group size k = 0, 2, 4, ..., 32 for clock gating, assuming that the circuit has a total of 32 (= N) flip-flops, and each flipflop toggles independently with toggling probability of 0.05. The curves in Figs. 2.1(b) and 2.1(c) show the changes of the area and the power consumption of the blocks

(b) Gating area including flip-flops w/ and (c) Power consumption w/ and w/o XOR w/o XOR gates. gates.

Figure 2.1: (a) Block-level structure of the input data toggling based clock gating [8], in which the logic blocks added for clock gating are marked with yellow color. (b) The changes of area including XORs (i.e., FFs + XORs + OR-tree + ICG) and excluding XORs (i.e., FFs + OR-tree + ICG) as the flip-flop grouping size k changes. (c) The changes of power consumption including (i.e., FFs + XORs + OR-tree + ICG) and excluding XORs (i.e., FFs + OR-tree + ICG) as the grouping size changes.

enclosed by the dotted line in Fig. 2.1(a) as the grouping size k of flip-flops varies.

**Observation 1**: The total quantity, Area(CG), of area overhead incurred by clock gating for a group of k flip-flops is:

$$Area(CG) = k \cdot Area(XOR) + (k-1) \cdot Area(OR) + Area(ICG)$$

(2.2)

$$Area(CG + FFs) = \begin{cases} N \cdot Area(FF) + Area(CG) & \text{if } k > 0\\ N \cdot Area(FF) & \text{if } k = 0 \end{cases}$$

(2.3)

The black curve in Fig. 2.1(b) shows the changes of the value of Area(CG+FFs)in terms of the cell size as the value of k changes while the blue curve in Fig. 2.1(b) shows the changes of the value of  $Area(CG+FFs) - k \cdot Area(XOR)$ . The big gap between the two curves in Fig. 2.1(b) indicates that XORs occupy a significant portion of Area(CG+FFs) as k increases.

**Observation 2**: The numbers on the black power curve in Fig. 2.1(c) are obtained by summing the power consumption of (1) the clock gating logic (i.e., XORs, OR-tree, and ICG), (2) the *k* flip-flops selected for clock gating, and (3) the remaining 32-*k* flip-flops. (The details of the calculation of their power consumption will be described in Sec. 3.10.) The power curve indicates that the power consumption gradually decreases as *k* increases, and then grows back. It means that the total *power saving heavily depends on the value of group size k*, which in turn closely relies on the joint toggling probabilities among the grouped flip-flops.

On the other hand, the blue curve in Fig. 2.1(c) indicates the changes of power consumption by (1), (2) and, (3) excluding that by XORs. The comparison of the two curves implies that *XORs occupy a considerable portion of power consumption*. (Note that if XORs were all removed, clearly the timing of clock gating would also be shorten by the amount of 2-input XOR delay, though it's a small constant saving.)

Based on the observations, our strategy targets two directions: (i) investigating a new clock gating technique that does not need the expensive XORs required for detecting input toggling while maximally reaping the benefit of toggling driven clock gating (Sec. 2.2) and (ii) seamlessly integrating our clock gating flow into the existing flow of toggling driven clock gating (Sec. 2.2.3).

#### 2.2 The Proposed Clock Gating

#### 2.2.1 Concept of Flip-flop State Driven Clock Gating

Our idea of an XOR-free clock gating is based on the following observation.

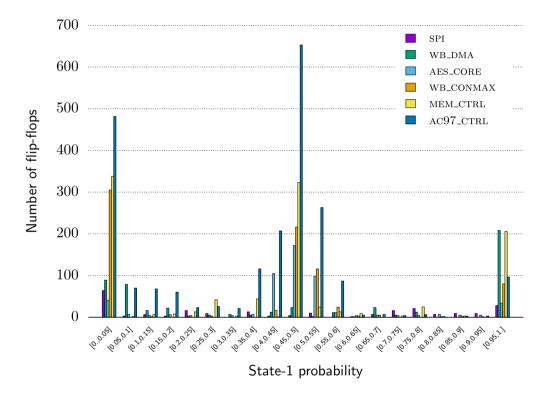

**Observation 3**: We performed circuit simulation as does in observations 1 and 2 to a set of IWLS benchmark circuits [22] for a sufficiently long period of time and measured the probability of each flip-flop being state-1. Fig. 2.2 shows the flip-flop distribution with respect to the state-1 probability. For example, the length of the bars on the x-coordinate  $[p_x, p_x+0.05]$  represents the number of flip-flops whose probability of being state-1 is in between  $p_x$  and  $p_x+0.05$ . The shape of flip-flop distribution in Fig. 2.2 clearly indicates that a large portion (> 39%) of the flip-flops in circuits tends to be stuck at state-0 or state-1 most of the simulation time, which means the input toggling on those flip-flops rarely happens. Thus, the role (i.e., detecting toggling) of XORs is actually not fully utilized on those flip-flops, although the flip-flops shall in fact very likely be selected for toggling driven clock gating.

Observation 3 motivates us to elaborate the toggling based clock gating by devising a new strategy of clock gating.

**Definition 1. (State driven clock gating)** For a flip-flop which is classified as stuck at state-0 (state-1) most of time, disable the clock signal to the flip-flop when the coming input at the next clock cycle is 0 (1).

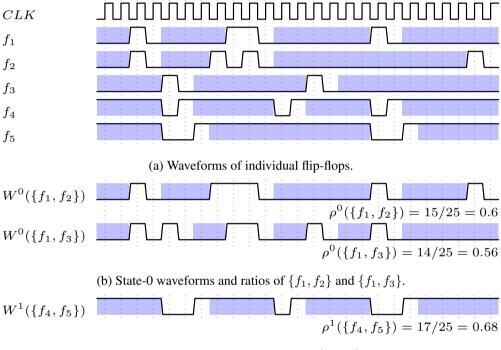

For a flip-flop which is classified as unstuck at state-0 or state-1 most of time, we will apply the toggling driven clock gating to the flip-flop. (The selection of flip-flops for applying state driven clock gating and the integration into the toggling based clock gating will be described in Sec. 2.2.3.) For example, Fig. 2.3(a) shows the state waveforms of flip-flops  $f_1, f_2, \ldots, f_5$ . Flip-flops  $f_1, f_2$ , and  $f_3$  are classified as stuck at

Figure 2.2: Flip-flop distribution with respect to the state-1 probability measured by simulation for a set of IWLS benchmark circuits.

(c) State-1 waveform and ratio of  $\{f_4, f_5\}$ .

Figure 2.3: (a) State-0/1 waveforms of flip-flops  $f_1, f_2, \ldots, f_5$ . in which  $f_1, f_2$  and  $f_3$  are stuck at state-0 most of time while  $f_4$  and  $f_5$  are stuck at state-1 most of time. (b) State-0 waveforms and ratios in Definition 2 of  $\{f_1, f_2\}$  and  $\{f_1, f_3\}$  derived from (a). (c) State-1 waveform and ratio in Definition 3 of  $\{f_4, f_5\}$  derived from (a).

state-0 and  $f_4$  and  $f_5$  as state-1, in which the blue intervals are the time on which our state driven clock gating safely disables the clock signal. Thus, as long as  $f_1$ ,  $f_2$ , and  $f_3$  ( $f_4$  and  $f_5$ ) are in state-0 (state-1), their clock signal can be disabled with no help of XOR. However, since applying clock gating to the flip-flops individually will still increase the gating overhead, because of no sharing of ICG, a careful grouping of flip-flops for clock gating is essential.

**Definition 2.**  $(W^0(S,t), \rho^0(S))$  Let w(f,t) be the state value on the simulation waveform of flip-flop f at simulation time  $t, 0 \le t \le T_{max}$ . Then, for a set S of flip-flops and simulation waveforms of the flip-flops in  $S, W^0(S,t)$  called **state-0 waveform of** S is defined to a waveform which satisfies, for every t in  $[0, t_{max}]$ ,

- 1.  $W^0(S,t) = 0$ , if  $w(f_i,t) = 0$ , for all  $f_i \in S$ .

- 2.  $W^0(S,t) = 1$ , otherwise.

Then,  $\rho^0(S)$  called state-0 ratio is defined to the portion of the simulation times at which  $W(S,t) = 0, 0 \le t \le T_{max}$ .

For example, Fig. 2.3(b) shows the generation of state-0 waveforms of  $S1 = \{f_1, f_2\}$ and  $S2 = \{f_1, f_3\}$  from the waveforms of  $f_1$ ,  $f_2$ , and  $f_3$  in Fig. 2.3(a), and the values of  $\rho^0(\cdot)$ . The blue bars in Fig. 2.3(b) indicate the clock cycle times at which the clock signals to the flip-flops in S1 and S2 are disabled if our state driven clock gating were applied to flip-flop groupings S1 and S2. Thus, for the two grouping  $S_1$  and  $S_2$  of flipflops, containing the same number of flip-flops, since  $S_1$  has the higher  $\rho^0(\cdot)$  value than that of  $S_2$ , selecting grouping S1 rather than S2 is a better choice for applying our state driven clock gating.

**Definition 3.**  $(W^1(S,t), \rho^1(S)) W^1(S,t)$  called state-1 waveform of S is defined to be a waveform that satisfies, for every t in  $[0, t_{max}]$ ,

- 1.  $W^1(S,t) = 1$ , if  $w(f_i,t) = 1$ , for all  $f_i \in S$ .

- 2.  $W^1(S, t) = 0$ , otherwise.

Then,  $\rho^1(S)$  called state-1 ratio is defined to the portion of the simulation times at which  $W^1(S,t) = I$ .

For example, Fig. 2.3(c) shows the generation of state-1 waveform for  $S3 = \{f_4, f_5\}$ from the waveforms of  $f_4$ , and  $f_5$  in Fig. 2.3(a), and the value of  $\rho^1(S3)$ . Note that the generation of  $W^0(S)$  and  $W^1(S)$  can be performed incrementally as S gradually increases, thus, the time complexity is bounded by  $O(|S| \cdot T_{max})$ .

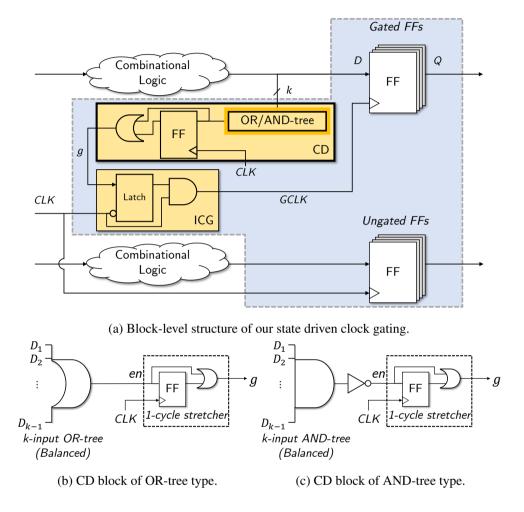

#### 2.2.2 Design of Gating Logic Circuitry

Fig. 2.4(a) shows the block-level structure of our proposed state driven gating and Figs. 2.4(b) and (c) show the internal structure of *two types* (i.e., OR-tree type or AND-tree type) of *Clock Disable* (CD) block. Compared with the structure of toggling driven clock gating shown in Fig. 2.1, ours *never include the most expensive XORs* in CD, one for every gated flip-flop in toggling driven clock gating. The supporting new or updated logic circuitry is the followings:

- 1. Unlike the toggling driven clock gating which consistently allocates an OR-tree for a group of flip-flops, ours allocates an *AND-tree*, shown in Fig. 2.4(c), for a flip-flop group that has a high probability of state-1 while allocating an *OR-tree*, shown in Fig. 2.4(b), for a flip-flop group that has a high probability of state-0.

- Our clock gating includes a *signal stretcher*<sup>1</sup> composed of *a flip-flop* and *an 2-input OR* gate, for each group of flip-flops as shown in Figs. 2.4(b) and (c).

- 3. An inverter is needed in the AND-tree type CD block before the signal stretcher because it is assumed that the clock enable signal (*en*) is active high.

<sup>&</sup>lt;sup>1</sup>Note that just one *distinct signal stretcher* is required *for every group* of gated flip-flops in the state driven clock gating while *one distinct XOR* is required *for every gated flip-flop* in the toggling driven clock gating.

Figure 2.4: Circuitry of the proposed state driven clock gating. (a) Block-level structure, in which the logic blocks added for clock gating are marked with yellow color. (b) Clock Disable (CD) block including OR-tree to assert the clock enable for flip-flops that have a high probability of state-0. (c) Clock Disable (CD) block including ANDtree to assert the clock enable for flip-flops that have a high probability of state-1. The role of *signal stretcher* to expand clock enable signal *en* from CD block and guarantee one more clock toggling at the next cycle after *en* is de-asserted. For example, in the case where a group of flip-flops has a high probability of state-0, the OR-tree type is used and *en* is asserted to high when at least one of the input data (D) is changed to state-1 and the clock is enabled. When every value of the input data (D) goes to state-0, *en* is de-asserted but one more clock toggling *is required to capture the last state transition* from state-1 to state-0.

Fig. 2.5 demonstrates the timing waveforms of the signals on CD blocks in Figs. 2.4(b) and (c), in which the enable signal for ICG (g) is stretched by one cycle compared with en and the gated clock (GCLK) is toggling during consecutive cycles during g is asserted.

We performed HSPICE simulation to extract the actual timing delay on the gated flip-flops and CD blocks in Fig. 2.1 and Fig. 2.4. Fig. 2.6 compares the timing waveforms for the clock-to-Q ( $T_{CLKQ}$ ) on a gated flip-flop in the toggling driven clock gating and a gated flip-flop in the proposed state driven clock gating. Compared with the toggling driven clock gating which has an XOR gate on the output of the flipflop ( $Q_{tg}$ , the red curves in Fig. 2.6), the clock-to-Q delay ( $Q_{sdcg}$ , the blue curves in Fig. 2.6) of the flip-flop in the state driven clock gating is decreased by 6.1 ps for rise transition and 6.23 ps for fall transition. Contrary to the conventional toggling based gating, the proposed clock gating requires no additional output load on the output of the gated flip-flop, thereby not increasing the clock-to-Q delay in comparison with a regular ungated flip-flop.

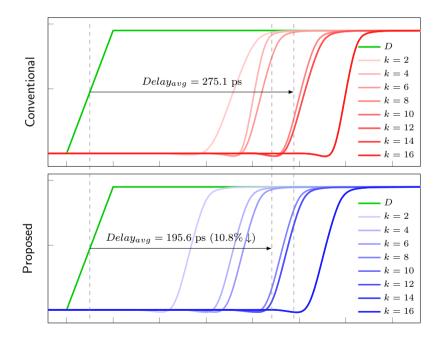

The delay of CD block varies depending on the flip-flop grouping size k. Fig. 2.7 shows the timing waveforms of the outputs of CD block in Fig. 2.1 and Fig. 2.4 varying k = 2, 4, ..., 16. For the simulation, we used 2- ,3-, and 4-input OR gates and 2-, 3- input XOR gates which are available in the cell library. In comparison with the delay of CD block (red curves) in the toggling based gating, the delay (blue curves) in the state driven clock gating is reduced by  $8.11\% \sim 29.79\%$ .

Figure 2.5: Timing waveforms of the signals on (a) CD block of OR-tree type in Fig. 2.4(b) and (b) CD block of AND-tree type in Fig. 2.4.

Figure 2.6: Timing waveforms by HSPICE simulation for the clock-to-Q delay  $(T_{CLKQ})$  on a flip-flip in the toggling driven clock gating  $(Q_{tg}: \text{ red curves})$  and a flip-flop in our state driven driven clock gating  $(Q_{sdcq}: \text{ blue curves})$ .

Figure 2.7: Timing waveforms by HSPICE simulation for the delay of CD blocks in the toggling driven clock gating (red curves) and our state driven clock gating (blue curves). The flip-flop group size is k = 2, 4, ..., 16.

The timing analyses shown in Fig. 2.6 and Fig. 2.7 clearly ensure that the application of our state drive clock gating is more safe in terms of timing as well as more economical in terms of area/power over the toggling driven clock gating.

#### 2.2.3 Integrated Clock Gating Methodology

Our clock gating methodology applies the proposed state driven clock gating to two disjoint subsets of flip-flops which have a high probability of state-0 or state-1, followed by applying the conventional toggling driven clock gating to the rest of flip-flops. Precisely, we carry out the clock gating methodology to an input circuit C in the following three steps.

• Step 1: For the circuit C, the flip-flop set  $\mathcal{F}$  in C with the placement information, and simulation waveform  $w(f_i, t)$  and its  $W^0(\cdot)$ ,  $W^1(\cdot)$ ,  $\rho^0(\cdot)$ ,  $\rho^1(\cdot)$  for every  $f_i \in \mathcal{F}$ ,

- 1.1 Set  $\mathcal{F}^0 = \{f_i | \rho^0(\{f_i\}) > p_{HIGH}\}.^2$

- 1.2 Set  $\mathcal{F}^1 = \{f_i | \rho^1(\{f_i\}) > p_{HIGH}\}.$

- 1.3 Apply Step 2 to  $\mathcal{F}^0$ .

- 1.4 Apply Step 2 to  $\mathcal{F}^1$ .

- 1.5 Apply Step 3 to  $\mathcal{F}$  ( $\mathcal{F}^0 \cup \mathcal{F}^1$ ).

• Step 2 (*State driven clock gating*): For an input flip-flop set  $\mathcal{F}$ ,  $D_{max}$  (in terms of Manhattan distance), and cost  $\nabla P(S, f_i)$  which represents the amount of power consumption to be saved additionally by the inclusion of flip-flop  $f_i$  to flip-flop group S of clock gating. (The details on the cost formulation will be described in Sec. 3.10.)

2.2 If  $\mathcal{F}$  is empty, return. Otherwise, pick a seed,  $f_s$ , which has the largest number of flip-flops in  $\mathcal{F}$  within  $D_{max}$ .

<sup>2.1</sup> Set i = 1.

$<sup>^{2}</sup>p_{HIGH}$  is a user controlled parameter, and set to 0.95 ~ 0.99 in our experiments.

2.3 Set  $S_i = \{f_s\}$ .

- 2.4 Expand flip-flop group  $S_i$  by iteratively including  $f_j \in \mathcal{F}$  such that (condition 1) the half perimeter on  $S_i \cup \{f_j\}$  is within  $D_{max}$  and (condition 2) its  $\nabla P(S_i, f_j)$ is the largest positive value.

- 2.5 Implement a clock gating logic for  $S_i$ .

- 2.6 Update i = i + 1,  $\mathcal{F} = \mathcal{F} S_i$ , and go to Step 2.2.

• Step 3 (*Toggling based clock gating*): Apply a conventional toggling based clock gating to the rest of flip-flops unprocessed in Step 2.

Fig. 2.8 shows an illustrative example of generating flip-flop group for clock gating in Step 2.4, in which starting from seed  $f_1$  picked in Step 2.2, flip-flops  $f_3$ ,  $f_2$ , and  $f_5$  are selected in the first, second, and third iterations, respectively.

#### 2.2.4 Cost Formulation

Let S be a group of flip-flops selected for state-0 driven clock gating in Step 2 and k = |S|. (The power saving cost in state-1 driven clock gating can be similarly formulated.) The amount of power consumption decreased by including flop-flop  $f_j$  to S for a clock gating with respect to a clock gating to S (without  $f_j$ ) is:

$$\nabla P_{saving}(S, f_j) = (P_g(S) + P_{ug}(f_j)) - P_g(S \cup \{f_j\})$$

(2.4)

$$P_g = \sum_{i=1}^{k} P_{gFF}(\rho^0(S)) + P_{GL}^k(\rho^0(S))$$

(2.5)

$$P_{GL}^{k}(\rho^{0}(S)) = P_{OR-tree}^{k}(\rho^{0}(S)) + P_{\sim const}$$

(2.6)

$$P_{\sim const} = P_{ICG}(\rho^0(S)) + P_{FF}(\rho^0(S)) + P_{OR}(\rho^0(S))$$

(2.7)

•  $P_{gFF}(\rho^0(S))$ : the total power consumed by the flip-flops when state-0 clock gating is applied to the group S of flip-flops including the power consumed by the internal clock inverters in the flip-flops.

| Grouping iteration (k)                  | $S_i$                    | $\nabla P(S_i, f_j)$       | Remark            |

|-----------------------------------------|--------------------------|----------------------------|-------------------|

|                                         |                          | $\nabla P(S_i, f_2) = 50$  |                   |

|                                         |                          | $\nabla P(S_i, f_3) = 150$ | Selected          |

| 1                                       | $\{f_s = f_1\}$          | $\nabla P(S_i, f_4) = 10$  |                   |

|                                         |                          | $\nabla P(S_i, f_5) = 80$  |                   |

|                                         |                          | $\nabla P(S_i, f_6) = 10$  |                   |

|                                         |                          | $\nabla P(S_i, f_2) = 30$  | Selected          |

| 2                                       | $\{f_1, f_3\}$           | $\nabla P(S_i, f_4) = 10$  |                   |

| 2                                       | $\{J_1, J_3\}$           | $\nabla P(S_i, f_5) = 20$  |                   |

|                                         |                          | $\nabla P(S_i, f_6) = 5$   |                   |

|                                         |                          | $\nabla P(S_i, f_4) = 2$   |                   |

| 3                                       | $\{f_1, f_2, f_3\}$      | $\nabla P(S_i, f_5) = 8$   | Selected          |

|                                         |                          | $\nabla P(S_i, f_6) = -5$  |                   |

| 4                                       | $\{f_1, f_2, f_3, f_5\}$ | $\nabla P(S_i, f_4) = -5$  | No positive value |

| <del>'1</del>                           | $\{J_1, J_2, J_3, J_5\}$ | $\nabla P(S_i, f_6) = -20$ |                   |

| $S_i = \{f_1, f_2, f_3, f_5\}$          |                          |                            |                   |

| $i = i + 1, \mathcal{F} = \{f_4, f_6\}$ | $\rightarrow$ Step 2.2   |                            |                   |

Figure 2.8: Example of generating a flip-flop group  $S_i$  for clock gating. The input flip-flop set  $\mathcal{F}$  is  $\{f_1, f_2, f_3, f_4, f_5\}$  and  $f_1$  is picked as a seed in Step 2.2.

- P<sup>k</sup><sub>GL</sub>(ρ<sup>0</sup>(S)): the total power consumed by the state-0 clock gating logic i.e., OR-tree, ICG, a signal stretcher (flip-flop and a 2-input OR gate) where the power consumed by OR-tree increases as the group size k increases whereas the power consumed by ICG and a stretcher is almost constant regardless of the value of k.

- $P_{ug}(f_j)$ : the power consumed by ungated flip-flop  $f_j$  including the power consumed by the internal clock inverters in the flip-flop.

Note that a fast calculation of the power costs, which will be iteratively required in Step 2.4, is enabled by simply referring the pre-computed data in a lookup table (LUT) forms.

## 2.3 Experiments

#### 2.3.1 Experimental Setup

To evaluate the effectiveness of our state driven clock gating, we tested our method and the conventional clock gating methods for circuits taken from IWLS benchmarks [22]. The benchmark circuits were synthesized and physically implemented by using Synopsys *Design Compiler* and *IC Compiler*. The operating clock frequency was set to 200 MHz for all circuits and the initial layout utilization was 70%. We used Synopsys 32/28 nm Generic Library and a slow PVT corner to guarantee the worst case performance. In addition, for power analysis we performed RTL simulations to get the switching activity information of the benchmark circuits and used *PrimeTime PX* for power estimation.

To compare our clock gating called State-driven CG with the existing clock gating methods, we used the conventional idle logic driven clock gating in RTL (Logicdriven CG) and toggle driven clock gating (Toggling-driven CG) provided by *Design Compiler* and *IC Compiler*. We tested three clock gating flows for the experiment as shown in Fig. 2.9. Those are (1) flow of Logic-driven CG only, (2) flow of Logic-driven CG followed by Toggling-driven CG, and (3) flow of Logic-driven CG followed by our State-driven CG and finally Toggling-driven CG as described in Sec. 2.2.3.

Figure 2.9: Tested clock gating flows. (a) Logic-driven CG only. (b) Logic-driven CG followed by Toggling-driven CG. (c) Logic-driven CG followed by our Statedriven CG and finally Toggling-driven CG.

Table 2.1 shows the information of benchmark circuits including the number of flip-flops, the number of gates, the percentage of the number of flip-flops whose state-1 probability is smaller than 0.05 over the total number of flip-flops (i.e., state-0 probability > 0.95), and the percentage of the number of flip-flops whose state-1 probability is bigger than 0.95. To extract the switching activity information, we performed simulations of typical operation modes for a sufficiently long period of time.

#### 2.3.2 Experimental Results

Table 2.2 summarizes the results produced by the conventional idle logic driven and toggling driven clock gating methods provided by a commercial electronic design automation (EDA) tool and our state driven clock gating method combined with the conventional methods. The Logic-driven CG, which has been commonly applied to practical low power designs, is used as a baseline for the comparison. We compared the

| Circuit   | # of FFs | # of gates | % of state-1 prob. < 0.05 | % of state-1 prob. > 0.95 |

|-----------|----------|------------|---------------------------|---------------------------|

| SPI       | 229      | 1612       | 27.90%                    | 12.20%                    |

| WB_DMA    | 523      | 2571       | 17.00%                    | 39.77%                    |

| AES_CORE  | 530      | 8422       | 7.74%                     | 6.42%                     |

| WB_CONMAX | 770      | 19600      | 39.61%                    | 10.39%                    |

| MEM_CTRL  | 1065     | 5078       | 31.74%                    | 19.34%                    |

| AC97_CTRL | 2199     | 8471       | 21.87%                    | 4.37%                     |

| VGA_LCD   | 17053    | 62187      | 14.95%                    | 43.47%                    |

Table 2.1: Benchmark circuit information.

clock gating ratio (i.e., the ratio of the number of gated flip-flops to the total number of flip-flops), the number of clock gating cells, and the power consumption of clock tree  $(P_{clk})$ , flip-flops  $(P_{ff})$ , combinational logics  $(P_{combi})$ , the total power consumption  $(P_{total})$ , the percentage of reduction of total power consumption <sup>3</sup>.

Compared with the conventional clock gatings, the flip-flop power  $P_{ff}$  was reduced consistently and effectively by our method for all test cases while there were fluctuations in the clock power  $P_{clk}$  due to the load changes on the driving buffers to the groups of gated flip-flops. In addition, the combinational logic power  $P_{combi}$  was increased because more flip-flops were gated by our method, which increased the corresponding supplemental clock gating logic. However, the flip-flop power  $P_{ff}$  and the clock power  $P_{clk}$  dominated the overall power, therefore decreasing the total power consumption over the conventional clock gating methods. In summary, our method reduced the total power consumption by 10.81% on average (up to 28.23%) while the conventional toggling driven clock gating reduced the total power consumption by 3.22% on average (up to 9.93%).

It is worthy to note that the power consumption of AES\_CORE was increased by

<sup>&</sup>lt;sup>3</sup>A negative sign indicates increase.

| Table 2.2: Comparison of the clock gating ratio, the number of clock gating cells (i.e., ICGs), the clock tree power $P_{clk}$ , the flip-flop  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

| power $P_{ff}$ , the combination logic power $P_{combi}$ including the power by clock gating logic, the total power $P_{total}$ produced (1) by |

| the conventional idle logic driven clock gating (Logic-driven CG), produced (2) by Logic-driven CG followed by the conventional                 |

| toggling driven clock gating (Toggling-driven CG), and produced (3) by Logic-driven CG followed by our state driven clock                       |

| gating (State-driven CG), finally applying Toggling-driven CG.                                                                                  |

|                                                                                                                                                 |

| s.                                                             |

|----------------------------------------------------------------|

| do                                                             |

| Ē                                                              |

| ĿĎ.                                                            |

| the flij                                                       |

| Je                                                             |

|                                                                |

| rs in                                                          |

| rs                                                             |

| rte                                                            |

| (e                                                             |

| È.                                                             |

| 4                                                              |

| S                                                              |

| č                                                              |

| al                                                             |

| Ë                                                              |

| e                                                              |

| he interna                                                     |

| е                                                              |

|                                                                |

| þ                                                              |

| d l                                                            |

| Je.                                                            |

| consume                                                        |

| JSI                                                            |

| ō                                                              |

| 0                                                              |

| lei                                                            |

| Š                                                              |

| ď                                                              |

| e                                                              |

| ÷                                                              |

| ы<br>В<br>П                                                    |

| ip                                                             |

| lu                                                             |

| <sup>o</sup>                                                   |

| Ŧ                                                              |

| s. ‡I                                                          |

| ğ                                                              |

|                                                                |

| Ē                                                              |

| p-fl                                                           |

| flip-fl                                                        |

| ie flip-fl                                                     |

| the flip-fl                                                    |

| in the flip-fl                                                 |

| rs in the flip-fl                                              |

| ters in                                                        |

| ters in                                                        |

| ters in                                                        |

| s inverters in the flip-fl                                     |

| ters in                                                        |

| lock inverters in                                              |

| l clock inverters in                                           |

| l clock inverters in                                           |

| l clock inverters in                                           |

| l clock inverters in                                           |

| internal clock inverters in                                    |

| internal clock inverters in                                    |

| internal clock inverters in                                    |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| the internal clock inverters in                                |

| xcluding the power consumed by the internal clock inverters in |

|                |       | Γοί       | Logic-driver        | ven CG              |             |              |       | Logic-driven + Toggling-driven CG | en + Tog(           | gling-driv          | en CG                   |             | Logic- | Logic-driven + our State-driven + Toggling-driven CG | State-dr            | iven + To           | ggling-dr               | iven CG     |

|----------------|-------|-----------|---------------------|---------------------|-------------|--------------|-------|-----------------------------------|---------------------|---------------------|-------------------------|-------------|--------|------------------------------------------------------|---------------------|---------------------|-------------------------|-------------|

| Circuit        |       |           |                     | Power (µW)          | (Mu).       |              |       |                                   |                     | Powe                | Power (µW)              |             |        | UUL J                                                |                     | Po                  | Power (µW)              |             |

|                |       | # 01 TCAS | $^{\dagger}P_{clk}$ | $^{\ddagger}P_{ff}$ | $P_{combi}$ | $P_{total}$  |       | # 01 ICGS                         | $^{\dagger}P_{clk}$ | $^{\ddagger}P_{ff}$ | $P_{combi}$ $P_{total}$ | $P_{total}$ |        |                                                      | $^{\dagger}P_{clk}$ | $^{\ddagger}P_{ff}$ | $P_{combi}$ $P_{total}$ | $P_{total}$ |

|                |       |           |                     |                     |             |              |       |                                   |                     |                     |                         | (Red.)      |        |                                                      |                     |                     |                         | (Red.)      |

| IdS            | 76.4% | 8         | 85.8                | 232.4               | 93.5        | 411.7        | 79.9% | 12                                | 82.3                | 212.0               | 96.7                    | 391.0       | 85.5%  | 15                                                   | 75.0                | 166.8               | 123.7                   | 365.5       |

|                |       |           |                     |                     |             |              |       |                                   |                     |                     |                         | (5.03%)     |        |                                                      |                     |                     |                         | (11.22%)    |

| WB_DMA         | 60.6% | 14        | 133.1               | 448.8               | 67.0        | 648.9        | 85.7% | 31                                | 168.1               | 380.1               | 77.5                    | 625.6       | 88.3%  | 43                                                   | 129.1               | 256.0               | 80.6                    | 465.7       |

|                |       |           |                     |                     |             |              |       |                                   |                     |                     |                         | (3.59%)     |        |                                                      |                     |                     |                         | (28.23%)    |

| AES_CORE       | 24.9% | 2         | 155.7               | 0.797.0             | 963.0       | 1916.0       | 26.0% | 20                                | 174.6               | 793.6               | 971.5                   | 1940.0      | 27.5%  | 7                                                    | 175.7               | 769.2               | 982.1                   | 1927.0      |

|                |       |           |                     |                     |             |              |       |                                   |                     |                     |                         | (-1.25%)    |        |                                                      |                     |                     |                         | (-0.57%)    |

| WB_CONMAX      | 49.9% | 24        | 317.2               | 643.4               | 875.3       | 1836.0 73.4% | 73.4% | 50                                | 370.0               | 559.7               | 894.7                   | 1824.0      | 76.1%  | 50                                                   | 355.4               | 462.5               | 913.6                   | 1731.0      |

|                |       |           |                     |                     |             |              |       |                                   |                     |                     |                         | (0.65%)     |        |                                                      |                     |                     |                         | (5.72%)     |

| MEM_CTRL       | 73.3% | 41        | 198.1               | 594.3               | 85.6        | 877.9        | 87.0% | 92                                | 252.4               | 438.5               | 7.66                    | 7.067       | 90.7%  | 93                                                   | 225.1               | 416.4               | 104.7                   | 746.2       |

|                |       |           |                     |                     |             |              |       |                                   |                     |                     |                         | (9.93%)     |        |                                                      |                     |                     |                         | (15.00%)    |

| AC97_CTRL      | 72.4% | 62        | 257.2               | 753.5               | 91.3        | 1102.0       | 91.4% | 118                               | 315.0               | 619.0               | 115.8                   | 1050.0      | 86.7%  | 106                                                  | 337.0               | 577.7               | 106.5                   | 1021.0      |

|                |       |           |                     |                     |             |              |       |                                   |                     |                     |                         | (4.72%)     |        |                                                      |                     |                     |                         | (7.35%)     |