#### 저작자표시-비영리-변경금지 2.0 대한민국

#### 이용자는 아래의 조건을 따르는 경우에 한하여 자유롭게

• 이 저작물을 복제, 배포, 전송, 전시, 공연 및 방송할 수 있습니다.

#### 다음과 같은 조건을 따라야 합니다:

저작자표시. 귀하는 원저작자를 표시하여야 합니다.

비영리. 귀하는 이 저작물을 영리 목적으로 이용할 수 없습니다.

변경금지. 귀하는 이 저작물을 개작, 변형 또는 가공할 수 없습니다.

- 귀하는, 이 저작물의 재이용이나 배포의 경우, 이 저작물에 적용된 이용허락조건 을 명확하게 나타내어야 합니다.

- 저작권자로부터 별도의 허가를 받으면 이러한 조건들은 적용되지 않습니다.

저작권법에 따른 이용자의 권리는 위의 내용에 의하여 영향을 받지 않습니다.

이것은 이용허락규약(Legal Code)을 이해하기 쉽게 요약한 것입니다.

### 이학박사 학위논문

# Highly integrated time-based data acquisition system using FPGA for PET scanners

FPGA를 이용한 시간 기반 고집적 PET 데이터 수집 장치

2019 년 7 월

서울대학교 대학원 의과학과

원 준 연

# Thesis for the Degree of Doctor of Philosophy in Science

# Highly integrated time-based data acquisition system using FPGA for PET scanners

FPGA를 이용한 시간 기반 고집적 PET 데이터 수집 장치

**July 2019**

Seoul National University Graduate School Major in Biomedical Sciences

**Jun Yeon Won**

#### **Abstract**

# Highly integrated time-based data acquisition system using FPGA for PET scanners

Jun Yeon Won

Major in Biomedical Sciences

Department of Biomedical Sciences

Seoul National University Graduate School

Positron emission tomography (PET) is a widely used functional imaging device for diagnosing cancer and neurodegenerative diseases. PET instrumentation studies focus on improving both spatial resolution and sensitivity to improve the lesion detectability while reducing radiation exposure to patients.

The silicon photomultiplier (SiPM) is a photosensor suitable for high-performance PET scanners owing to its compact size and fast response. However, the SiPM-based PET scanners require a large number of readout channels owing to a high level of granularity. For example, the typical whole-body PET scanners require more than 40,000 SiPM channels. Therefore, the highly integrated data acquisition (DAQ) system that can digitize a large number of SiPM signal with preserving its fast temporal response is required to develop the high-performance SiPM-based PET scanners.

Time-based signal digitization is a promising method to develop highly

integrated DAQ systems owing to its simple circuitry and fast temporal response. In this thesis, studies on developing highly integrated DAQ systems using a field-programmable gate array (FPGA) were presented.

Firstly, a 10-ps time-to-digital converter (TDC) implemented within the FPGA was developed. The FPGA-TDCs suffer from the non-linearity, because FPGAs are not originally designed to implement TDC. We proposed the dual-phase sampling architecture considering the FPGA clock distribution network to mitigate the TDC non-linearity. In addition, we developed the on-the-fly calibrator that compensated the innate bin width variations without introducing the dead time.

Secondly, the time-based SiPM multiplexing and readout method was developed using the principle of the global positioning system (GPS). The signal traces connecting every SiPM to four timing channels were used to encode the position information. The position information was obtained using the innate transit time differences measured by four FPGA-TDCs. In addition, the minimal signal distortion by multiplexing circuit allowed to use a time-over-threshold (ToT) method for energy measurement after multiplexing.

Thirdly, we proposed a new FPGA-only digitizer. The programmable FPGA input/output (I/O) port was configured with stub-series terminated logic (SSTL) input receiver, and each FPGA I/O port functioned as a high-performance voltage comparator with a fast temporal response. We demonstrated that the FPGA can be used as a high-performance DAQ system by directly digitizing the time-of-flight (TOF) PET detector signals using the FPGA without any front-end electronics.

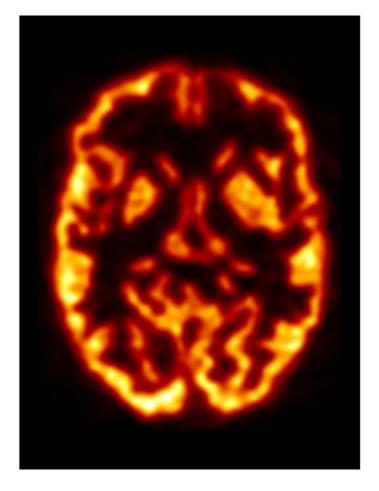

Lastly, we developed comparator-less charge-to-time converter (QTC) DAQ systems to collect data from a prototype high-resolution brain PET scanner. The energy channel consisted of a QTC combined with the SSTL input receiver of the

FPGA. The timing channel was a TDC implemented within the same FPGA. The

detailed structure of brain phantom was well-resolved using the developed high-

resolution brain PET scanner and the highly-integrated time-based DAQ systems.

**Keyword:** Data acquisition (DAQ) system, Field-programmable gate array (FPGA),

Positron Emission Tomography (PET), Silicon photomultiplier (SiPM), Time-of-

flight (TOF), Time-to-digital converter (TDC)

**Student Number: 2013-21782**

iii

## **Table of Contents**

| Chapter 1. Introduction                                   | 1  |

|-----------------------------------------------------------|----|

| 1.1. Background                                           | 1  |

| 1.1.1. Positron Emission Tomography                       | 1  |

| 1.1.2. Silicon Photomultiplier                            | 1  |

| 1.1.3. Data Acquisition System                            | 2  |

| 1.1.4. Time-based Signal Digitization Method              | 3  |

| 1.2. Purpose of Research                                  | 6  |

| Chapter 2. FPGA-based Time-to-Digital Converter           | 8  |

| 2.1. Background                                           | 8  |

| 2.2. Materials and Methods                                | 9  |

| 2.2.1. Tapped-Delay-Line TDC                              | 9  |

| 2.2.2. FPGA                                               | 11 |

| 2.2.3. Dual-Phase TDL TDC with On-the-Fly Calibrator      | 11 |

| 2.2.3.1. FPGA Clock Distribution Network                  | 11 |

| 2.2.3.2. The Principle of Dual-Phase TDL TDC              | 14 |

| 2.2.3.3. The Principle of Pipelined On-the-Fly Calibrator | 16 |

| 2.2.3.4. Implementation of Dual-Phase TDL TDC             |    |

| with On-the-Fly Calibrator                                | 18 |

| 2.2.4. Experimental Setups and Data Processing            | 20 |

| 2.2.4.1. TDC Characteristics                              | 21 |

| 2.2.4.2. Arrival Time Difference Measurements             | 22 |

| 2.3. Results                                              | 24 |

| 2.3.1. TDC Characteristics                                | 24 |

| 2.3.2. Arrival Time Difference Measurements               | 25 |

| 2.4. Discussion                                           | 28 |

| Chapter 3. Time-based Multiplexing Method              | 29 |

|--------------------------------------------------------|----|

| 3.1. Background                                        | 29 |

| 3.2. Materials and Methods                             | 30 |

| 3.2.1. Delay Grid Multiplexing                         | 30 |

| 3.2.2. Detector for Concept Verification               | 32 |

| 3.2.3. Front-end Electronics                           | 34 |

| 3.2.4. Experimental Setups                             | 35 |

| 3.2.4.1. Data Acquisition Using the Waveform Digitizer | 37 |

| 3.2.4.2. Data Acquisition Using the FPGA-TDC           | 37 |

| 3.2.5. Data Processing and Analysis                    | 38 |

| 3.2.5.1. Waveform Digitizer                            | 38 |

| 3.2.5.2. FPGA-TDC                                      | 41 |

| 3.3. Results                                           | 44 |

| 3.3.1. Waveform Digitizer                              | 44 |

| 3.3.1.1. Waveform, Rise Time, and Decay Time           | 44 |

| 3.3.1.2. Flood Map                                     | 46 |

| 3.3.1.3. Energy                                        | 48 |

| 3.3.1.4. CTR                                           | 49 |

| 3.3.2. FPGA-TDC                                        | 50 |

| 3.3.2.1. ToT and Energy                                | 50 |

| 3.3.2.2. Flood Map                                     | 51 |

| 3.3.2.3. CTR                                           | 52 |

| 3.4 Discussion                                         | 53 |

| Chapter 4. FPGA-Only Signal Digitization Method              | 54 |

|--------------------------------------------------------------|----|

| 4.1. Background                                              | 54 |

| 4.2. Materials and Methods                                   | 56 |

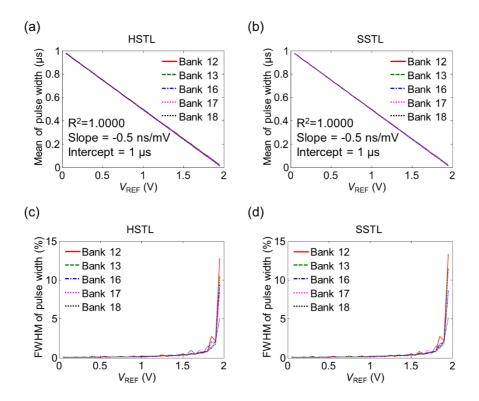

| 4.2.1. Single-ended Memory Interface Input Receiver          | 56 |

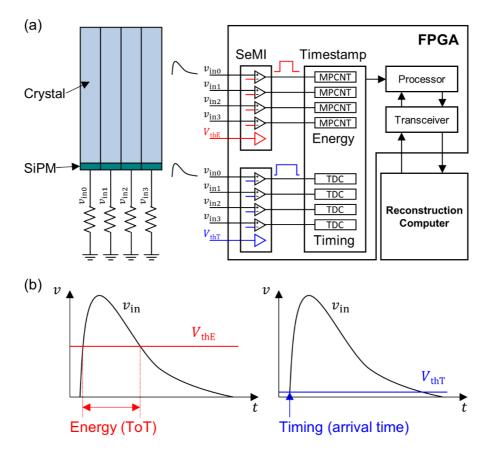

| 4.2.2. SeMI Digitizer                                        | 56 |

| 4.2.3. Experimental Setup for Intrinsic Performance          |    |

| Characterization                                             | 59 |

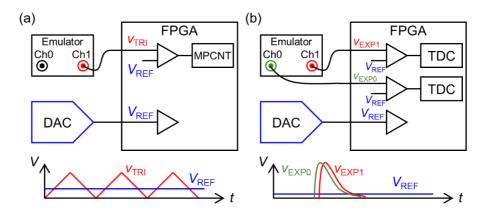

| 4.2.3.1. ToT                                                 | 59 |

| 4.2.3.2. Timing                                              | 60 |

| 4.2.4. Experimental Setup for Individual Signal Digitization | 60 |

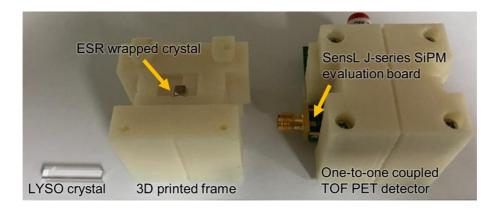

| 4.2.4.1. TOF PET Detector                                    | 60 |

| 4.2.4.2. Data Acquisition Using the Waveform Digitizer       | 61 |

| 4.2.4.3. Data Acquisition Using the SeMI Digitizer           | 63 |

| 4.2.4.4. Data Analysis                                       | 63 |

| 4.3. Results                                                 | 64 |

| 4.3.1. Results of Intrinsic Performance Characterization     | 64 |

| 4.3.1.1. ToT                                                 | 64 |

| 4.3.1.2. Timing                                              | 65 |

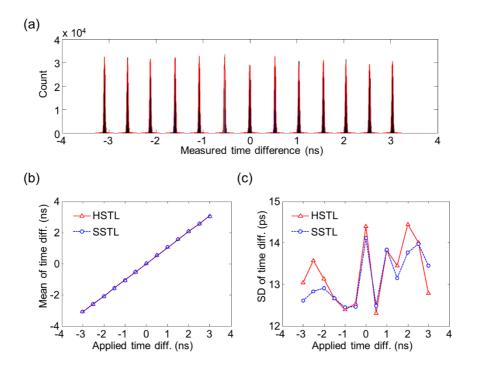

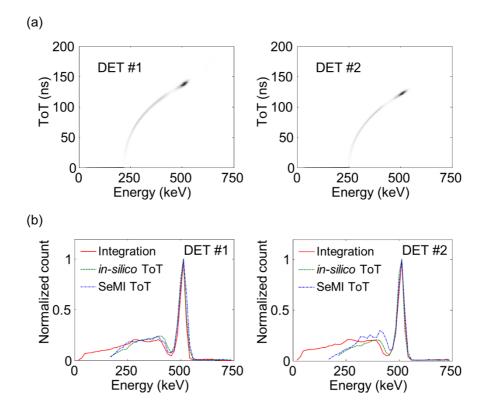

| 4.3.2. Results of Individual Signal Digitization             | 66 |

| 4.3.2.1. Energy                                              | 66 |

| 4.3.2.2. CTR                                                 | 67 |

| 4.4. Discussion                                              | 68 |

| Chapter 5. Comparator-less QTC DAQ Systems         |    |

|----------------------------------------------------|----|

| for High-Resolution Brain PET Scanners             | 70 |

| 5.1. Background                                    | 70 |

| 5.2. Materials and Methods                         | 72 |

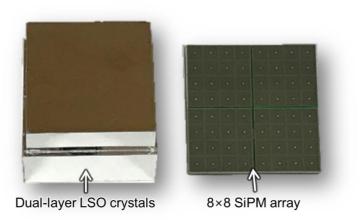

| 5.2.1. Brain PET Scanner                           | 72 |

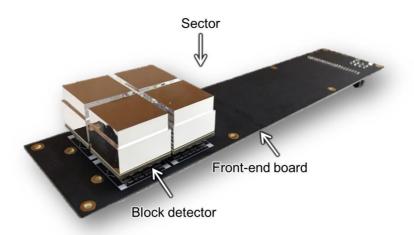

| 5.2.1.1. Block Detector                            | 72 |

| 5.2.1.2. Sector                                    | 73 |

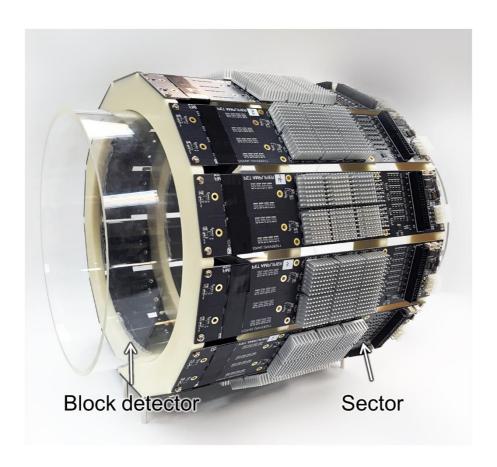

| 5.2.1.3. Scanner Geometry                          | 74 |

| 5.2.2. Comparator-less QTC DAQ System              | 75 |

| 5.2.3. Data Acquisition Chain of Brain PET Scanner | 79 |

| 5.2.4. Experimental Setups and Data Processing     | 79 |

| 5.2.4.1. Energy Linearity                          | 79 |

| 5.2.4.2. Performance Evaluation of Block Detector  | 80 |

| 5.2.4.3. Phantom Studies                           | 82 |

| 5.3. Results                                       | 83 |

| 5.3.1. Energy Linearity                            | 83 |

| 5.3.2. Performance Evaluation of Block Detector    | 83 |

| 5.3.3. Phantom Studies                             | 85 |

| 5.4. Discussion                                    | 87 |

| Chapter 6. Conclusions                             | 89 |

| Bibliography                                       | 90 |

| Abstract in Korean (국문 초록)                         | 94 |

## **Table of Figures**

| Figure 1-1.     | Conventional DAQ system2                                     |

|-----------------|--------------------------------------------------------------|

| Figure 1-2.     | Time-based signal digitization methods4                      |

| Figure 2-1.     | Tapped-delay-line TDC10                                      |

| Figure 2-2.     | The clock distribution network of the Virtex-6 FPGA12        |

| Figure 2-3.     | Timing diagrams and transfer functions of TDC in case of     |

| clock region of | erossing                                                     |

| Figure 2-4.     | The Principle of dual-phase TDL TDC15                        |

| Figure 2-5.     | The Principle of on-the-fly calibrator17                     |

| Figure 2-6.     | Prefix adder                                                 |

| Figure 2-7.     | Implementation of dual-phase TDL TDC with on-the-fly         |

| calibrator      | 19                                                           |

| Figure 2-8.     | The nonlinearity of dual-phase TDL TDC25                     |

| Figure 2-9.     | Time difference histograms obtained with online and offline  |

| calibration m   | ethods and without calibration26                             |

| Figure 2-10.    | Measurement uncertainty for the time differences with online |

| and offline ca  | libration methods and without calibration26                  |

| Figure 2-11.    | Time difference histograms with real-time calibration and    |

| non-real-time   | calibration                                                  |

| Figure 2-12.    | Measurement uncertainty of the time difference               |

| measurement     | s with real-time calibration and non-real-time calibration27 |

| Figure 3-1.     | Conceptual diagram for the delay grid multiplexing31         |

| Figure 3-2.     | LGSO/SiPM detector using the proposed multiplexing method    |

|                 | 33                                                           |

| Figure 3-3.     | Schematic of the front-end electronics for the LGSO/SiPM     |

| detector        | 34                                                           |

| Figure 3-4.     | Experimental setups                                          |

| Figure 3-5.     | Dual-threshold ToT                                           |

| Figure 3-6.     | Waveforms obtained at the four corner readout channels44     |

| Figure 3-7.                                                                                                                            | Rise and decay times                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

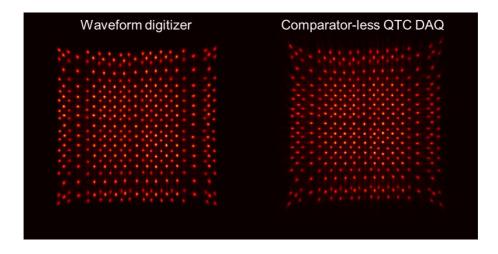

| Figure 3-8.                                                                                                                            | Flood maps obtained using the waveform digitizer47                        |

| Figure 3-9.                                                                                                                            | DWR values obtained using the waveform digitizer47                        |

| Figure 3-10.                                                                                                                           | Representative flood map and 1D profiles obtained using the               |

| waveform dig                                                                                                                           | gitizer47                                                                 |

| Figure 3-11.                                                                                                                           | Energy measurements for the LGSO/SiPM detector using the                  |

| waveform dig                                                                                                                           | gitizer48                                                                 |

| Figure 3-12.                                                                                                                           | CTR values using the waveform digitizer49                                 |

| Figure 3-13.                                                                                                                           | ToT measurements using the FPGA-TDC50                                     |

| Figure 3-14.                                                                                                                           | Representative flood map and 1D profiles obtained using the               |

| FPGA-TDC                                                                                                                               | 51                                                                        |

| Figure 3-15.                                                                                                                           | CTR measurements using the FPGA-TDC52                                     |

| Figure 4-1.                                                                                                                            | Time-based signal digitization55                                          |

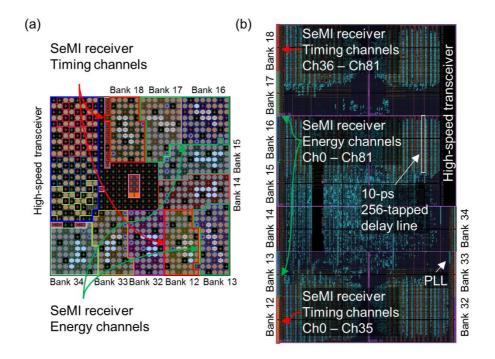

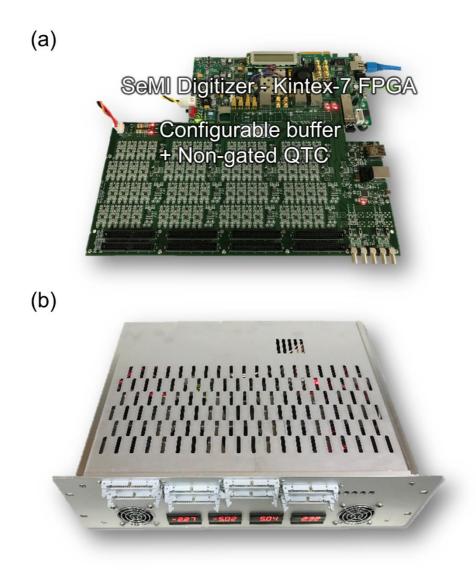

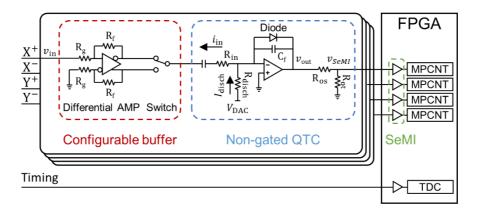

| Figure 4-2.                                                                                                                            | The layout of the SeMI digitizer using a Kintex-7 FPGA 57                 |

| Figure 4-3.                                                                                                                            | Conceptual diagram of the SeMI digitizer58                                |

|                                                                                                                                        |                                                                           |

| Figure 4-4.                                                                                                                            | Experimental setup for the intrinsic performance                          |

| C                                                                                                                                      | Experimental setup for the intrinsic performance on of the SeMI digitizer |

| characterizati                                                                                                                         |                                                                           |

| characterization Figure 4-5.                                                                                                           | on of the SeMI digitizer59                                                |

| characterization Figure 4-5. Figure 4-6.                                                                                               | on of the SeMI digitizer                                                  |

| characterization Figure 4-5. Figure 4-6. detector                                                                                      | on of the SeMI digitizer                                                  |

| characterization Figure 4-5. Figure 4-6. detector Figure 4-7.                                                                          | One-to-one coupled TOF PET detector                                       |

| characterization Figure 4-5. Figure 4-6. detector Figure 4-7.                                                                          | One-to-one coupled TOF PET detector                                       |

| characterization Figure 4-5. Figure 4-6. detector Figure 4-7. Figure 4-8.                                                              | One-to-one coupled TOF PET detector                                       |

| characterization Figure 4-5. Figure 4-6. detector Figure 4-7. Figure 4-8. Figure 4-9.                                                  | One-to-one coupled TOF PET detector                                       |

| characterization Figure 4-5. Figure 4-6. detector Figure 4-7. Figure 4-8. Figure 4-9. Figure 4-10.                                     | One-to-one coupled TOF PET detector                                       |

| characterization Figure 4-5. Figure 4-6. detector Figure 4-7. Figure 4-8. Figure 4-9. Figure 4-10. Figure 5-1.                         | One-to-one coupled TOF PET detector                                       |

| characterization Figure 4-5. Figure 4-6. detector Figure 4-7. Figure 4-8. Figure 4-9. Figure 4-10. Figure 5-1. Figure 5-2.             | One-to-one coupled TOF PET detector                                       |

| characterization Figure 4-5. Figure 4-6. detector Figure 4-7. Figure 4-8. Figure 4-9. Figure 4-10. Figure 5-1. Figure 5-2. Figure 5-3. | One-to-one coupled TOF PET detector                                       |

| Figure 5-6.    | Experimental setups for performance evaluation of block    |

|----------------|------------------------------------------------------------|

| detector       | 80                                                         |

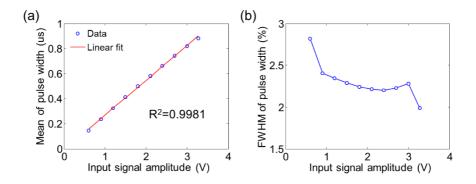

| Figure 5-7.    | Energy linearity of the comparator-less QTC DAQ83          |

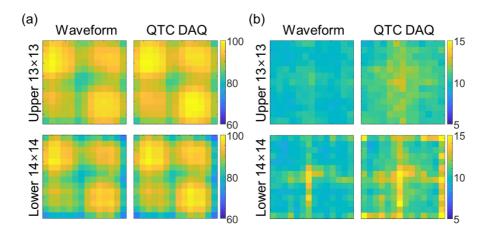

| Figure 5-8.    | Flood maps obtained using the waveform digitizer and the   |

| time-based Da  | AQ system84                                                |

| Figure 5-9.    | Normalized photopeak positions and energy resolutions      |

| obtained using | g the waveform digitizer and the time-based DAQ system .84 |

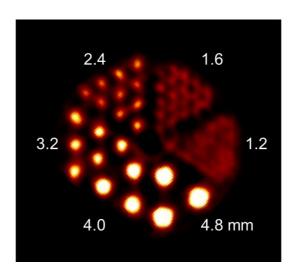

| Figure 5-10.   | Reconstructed hot-rod phantom image85                      |

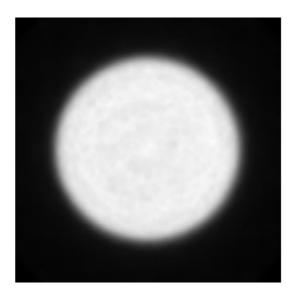

| Figure 5-11.   | Reconstructed uniform phantom image85                      |

| Figure 5-12.   | Reconstructed 2D Hoffman brain phantom image86             |

### **Table of Tables**

| <b>Table 2-1.</b> | TDC characteristics                                  | .24 |

|-------------------|------------------------------------------------------|-----|

| Table 3-1.        | Look-up table for decoding the position and the time |     |

| information       |                                                      | .31 |

#### **Chapter 1. Introduction**

#### 1.1. Background

#### 1.1.1. Positron Emission Tomography

Positron emission tomography (PET) is a functional imaging tool to visualize the distribution of the injected positron-emitting radiopharmaceutical, and thus widely used to diagnose cancer and neurodegenerative diseases. The studies on PET instrumentations have focused on improving spatial resolution, signal-to-noise ratio (SNR), and sensitivity to detect small lesion and to reduce radiation dose to patients. High spatial resolution can be achieved by using small-pitch scintillation crystal and photosensor [1-4]. High SNR can be achieved by measuring time-of-flight (TOF) information of annihilation photon pairs [5-7]. High sensitivity can be achieved by extending the axial length of the PET scanner [8, 9].

#### 1.1.2. Silicon Photomultiplier

The silicon photomultiplier (SiPM) is a photosensor suitable for high-performance PET scanners. Firstly, compact size enables not only the high-resolution scintillation crystal identification [3, 4] but also one-to-one coupling to improve timing resolution [10, 11]. Secondly, fast temporal response and high gain allow TOF measurement [10, 11]. Lastly, the SiPM is a cost-effective photosensor that can be used long-axial field-of-view (FOV) PET scanners owing to mass production using CMOS technology [9].

However, the high level of granularity in SiPM is a major challenge in developing SiPM-based PET scanners. Individual signal digitization requires the complex and large volume of data acquisition electronics.

#### 1.1.3. Data Acquisition System

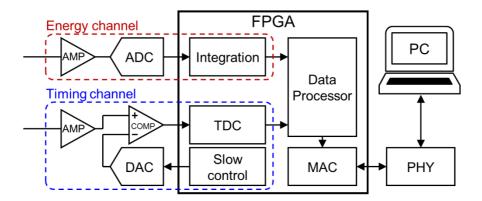

Typical data acquisition (DAQ) systems consist of energy, timing channels, field-programmable gate arrays (FPGAs), and auxiliary digital electronics [12, 13] as shown in Figure 1-1. The energy channel processes the energy and position information from the detectors with light sharing and/or charge division circuit. It consists of analog-to-digital converters (ADCs). The digitized values by ADCs are input into the FPGA that accumulates values for a predetermined period to obtain energy and position information. The timing channel processes the arrival time and thus TOF information of gamma-rays. It consists of high-speed amplifiers, comparators, and digital-to-analog converters (DACs). The comparator generates a digital timing pulse when the leading edge of the signal crosses the threshold voltage applied by a DAC. The digital timing pulse is input into a time-to-digital converter (TDC) that can measure the arrival time with precise time resolution. Currently, TDCs are usually implemented within the FPGA.

**Figure 1-1.** Conventional DAQ system.

#### 1.1.4. Time-based Signal Digitization Method

Time-based signal digitization methods that use timing channels to obtain both energy and timing information are widely used to simplify DAQ systems and further to increase the number of readout channels for SiPM-based PET scanners, because the timing channel is much smaller, simpler, and more power-efficient than the energy channel.

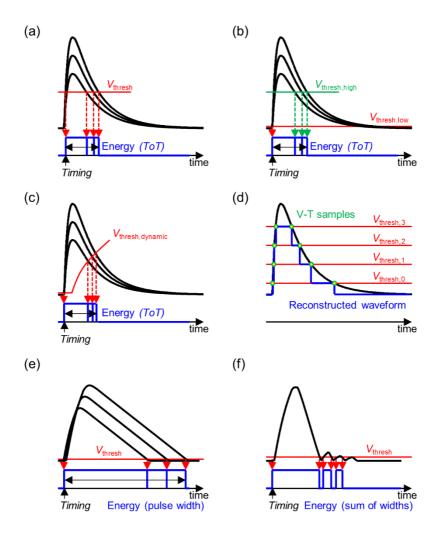

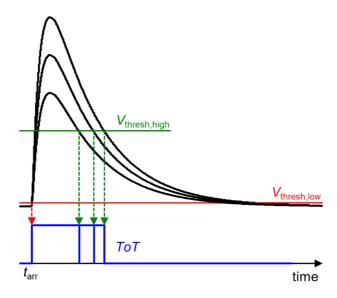

Time-over-threshold (ToT) method is a straightforward time-based signal digitization method by applying a single threshold to the signal and extract the energy and timing information from the pulse width and the transition time, respectively [14] as shown in Figure 1-2 (a). This method has the advantage that it requires only a single voltage comparator for both energy and timing measurements. However, the ToT method has the disadvantages of non-linear energy measurement and poor energy and/or timing resolutions. The low threshold to detect the early photons degrades the energy resolution and the high threshold for energy discrimination deteriorates the timing resolution. Thus, the dual-threshold method to apply low and high thresholds for the timing and energy channels, respectively, was developed to obtain good energy and timing resolutions for the TOF PET detectors [15, 16] as shown in Figure 1-2 (b).

A dynamic ToT method uses a single voltage comparator with an adaptive threshold to improve energy linearity and resolution as shown in Figure 1-2 (c). The threshold starts at a low level and increases gradually after the signal crosses the low threshold. This method can achieve both good energy and timing resolution because low and high thresholds are used for timing and energy measurements, respectively. However, the dynamic requires complex threshold circuits such as a monostable vibrator [17] or a DAC [18].

**Figure 1-2.** Time-based signal digitization methods. (a) Simple ToT with a single threshold. (b) Dual-threshold ToT. (c) Dynamic threshold ToT. (d) Multi-voltage-threshold. (e) Charge-to-time converter. (f) 1-bit sigma delta modulation.

The multi-voltage threshold (MVT) method uses multiple comparators and obtains multiple samples to reconstruct the analog signals [19, 20] as shown in Figure 1-2 (d). The energy and timing information is extracted from the reconstructed signals. However, the MVT method requires multiple comparators for each signal, thus degrading the level of integration.

The charge-to-time converter (QTC) involves the integrator [21, 22] as shown

in Figure 1-2 (e). This method collects the charge and provides a dual-slope pulse of which width is proportional to the input charge. The advantage of the non-gated QTC is a simple circuitry, because it automatically controls its idle, charge, and discharge phases using a diode. The gated QTC is complex to implement because it requires digitally controlled switches and associated digital controllers; however, has the advantage that it can modify the integration window [23]. In addition, a 1-bit sigmadelta modulator adaptively discharges the charges stored in the feedback capacitor in the integrator. It measures energy as the sum of the modulated pulse is greater than the threshold voltage [24, 25] as shown in Figure 1-2 (f).

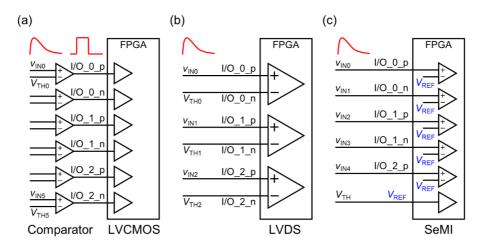

A new approach to using the FPGA as a digitizer significantly improves the level of integration of the time-based signal digitization method [20, 24-26]. The digital low-voltage differential signaling (LVDS) input receiver of FPGA can be used as a voltage comparator for signal digitization and the logic state of the receiver is directly processed by a TDC implemented within the same FPGA. However, each LVDS input receiver requires a pair of configurable input/output (I/O) ports of FPGA, and thus this method has the drawback that the number of readout channels is less than half the total number of available I/O ports.

Therefore, the FPGA-based time-based digitization is a promising method to implement the highly integrated DAQ systems for the SiPM-based PET scanners.

#### 1.2. Purpose of Research

The aim of this thesis is to develop highly-integrated time-based DAQ systems.

The time-based DAQ system is a device that collects energy, position and timing data using only time information.

In Chapter 2, the TDC implemented in the FPGA was presented. Two new architectures for FPGA-TDC were developed. The first architecture is a dual-phase sampling of delay-line considering the FPGA clock distribution network. The second architecture is an on-the-fly calibration method that measures bin-width fluctuations due to PVT variations and reflects updated bin widths in time measurements automatically.

In Chapter 3, a new time-based SiPM multiplexing method was presented. The crystal position was encoded using the innate transit times from each SiPM to readout channels. The crystal position can be identified using the time difference of arrival (TDOA) positioning method widely used in the global positioning system (GPS). Compared with the conventional multiplexing method that requires four ADCs, four TDCs were used.

In Chapter 4, the FPGA-only digitization method was presented. The SiPM signal was directly digitized by FPGA without any amplifiers. In addition, compared with the conventional DAQ system, no discrete comparator and ADC are required. The FPGA I/O port was configured with stub-series terminated logic (SSTL) that is widely used in the memory interface. The energy information was obtained using a ToT method and the timing information was obtained using the FPGA-TDC.

In Chapter 5, the highly integrated 165-channel comparator-less QTC DAQ system for high-resolution brain PET scanners was presented. The energy chain was

implemented by combining a QTC with the SSTL input receiver to improve energy linearity. The dual-slope output of QTC was directly digitized by an FPGA. The timing chain was a TDC implemented within the same FPGA. The detailed structure of the Hoffman brain phantom was clearly resolved using the developed time-based DAQ systems and the brain PET scanners.

### Chapter 2. FPGA-based Time-to-Digital Converter

#### 2.1. Background

TOF measurement of annihilation gamma pair can improve the image quality of the PET scanner [5-7, 27]. Because the gamma-ray propagates with the speed of light, the precise time measurement device is required to measure the TOF difference of gamma pairs.

The time-to-digital converter (TDC) is a precise time measurement device. The FPGA-TDC is widely used for TOF PET scanners, because the number of channels and the resolution can be configurable and TDC can be embedded into the data processing FPGA.

Most FPGA-TDCs use coarse-fine architecture [28-41]. The coarse counter operating the main clock frequency provides a coarse time with a resolution of the time period and covers a wide dynamic range. The fine time interpolator provides a sub-clock-period time with a fine resolution covers one clock period. The primitive carry chain for fast arithmetic operation is usually used to implement the delay line of the fine time interpolator. However, the carry chain is not originally designed for precise time measurement, most FPGA-TDCs suffer from the non-linearity. Non-linearity is all deviations from the ideal TDC with uniform resolution.

We developed the dual-phase tapped-delay-line architecture considering the clock distribution network [38] and the bin-width tuning method [39] to mitigate the bin width variations. In addition, we developed a fast on-the-fly bin width calibration method to measure the bin width variations and reflect them in the time measurement to reduce the uncertainty [38].

#### 2.2. Materials and Methods

#### 2.2.1. Tapped-Delay-Line TDC

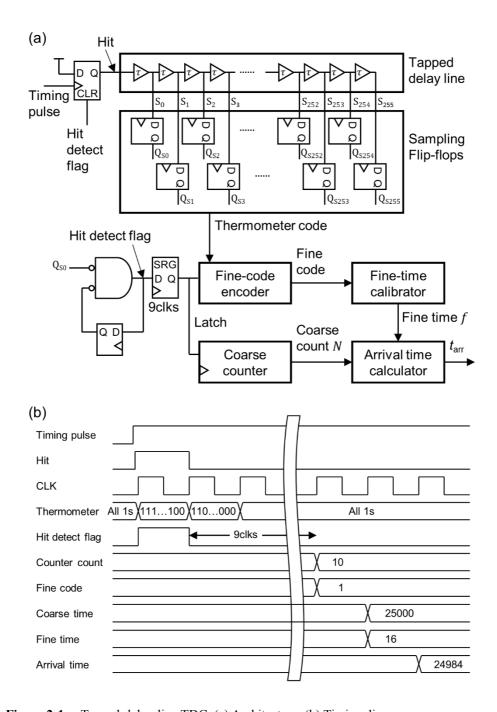

The tapped-delay-line (TDL) is a fundamental block to implement the fine time interpolator of the TDC [29-41] as shown in Figure 2-1. The asynchronous hit signal propagates along the TDL with changing the logic states of the delay elements until the hit signal synchronizes with the rising edge of the main clock signal. The flipflops operating at the main clock signal sample the propagation states of the TDL and provide a thermometer code. The fine-code encoder converts the thermometer code into a fine code in two steps. The thermometer code is converted into a one-hot code using multiple bubble suppressor [40]. The fat-tree encoder converts the onehot code to the binary code [39]. The coarse counter is a binary counter operating at the main clock period of  $T_0$ . The hit detect flag is generated during one clock period when the first logic state of the TDL is inverted. The hit detect flag is delayed by 9 clock periods using a shift register (SRG) and then latches the coarse count N and the fine code. The fine-time interpolator converts the fine code into the fine time f with a dynamic range of  $T_0$ . The code density test is used to measure the individual bin widths and reflect them into fine time measurements [38, 40]. The hit arrival time  $t_{\rm arr}$  is calculated as in (2.1).

$$t_{\rm arr} = N \times T_0 - f \tag{2.1}$$

The carry chain is widely used to implement the TDL and the total propagation time of the TDL should be greater than  $T_0$ .

Figure 2-1. Tapped-delay-line TDC. (a) Architecture. (b) Timing diagram.

#### 2.2.2. FPGA

The Virtex-6 evaluation kit (ML605, Xilinx) was used to implement TDC. The FPGA consists of the array of configurable logic blocks (CLBs) that can be driven by the clock buffers.

The CLB consists of look-up tables (LUTs), multiplexers, a carry logic, and distributed memories. Each carry logic is a carry look ahead logic and has four sums and four carry out. The carry logic can be cascaded to increase the total propagation time.

The global buffer located at the center of the FPGA can feed clock signals all the CLBs. In addition, the FPGA has multiple clock regions where the CLBs in the same clock region have the minimum clock skew.

#### 2.2.3. Dual-Phase TDL TDC with On-the-Fly Calibrator

#### 2.2.3.1. FPGA Clock Distribution Network

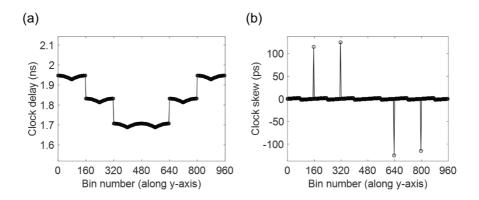

TDL implementation on the single clock region can mitigate the non-linearity, because the CLBs in the same clock region have the minimum clock skew. Figure 2-2 shows the clock delays and the clock skews for the TDL with 960 bins on the Virtex-6 evaluation kit. The Virtex-6 FPGA has 2×6 clock regions and each clock region is 40 CLBs high. The inter-clock-region clock skew was less than 2 ps; however, the intra-clock-region clock skew was greater than 100 ps.

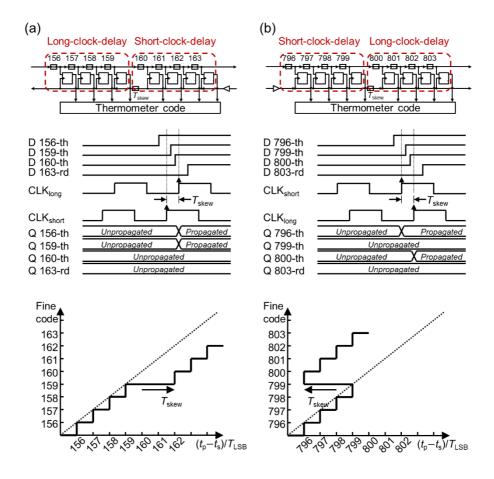

The clock region crossing of TDL can cause ultra-wide bin or several missing bins [38]. In the case where the TDL crosses from the long- to the short-clock-delay region as shown in Figure 2-3 (a), the last bin of the long-clock-delay region becomes the ultra-wide bin. There is a clock skew  $T_{\rm skew}$  when the flip-flops in the short-clock-

**Figure 2-2.** The clock distribution network of the Virtex-6 FPGA. (a) Clock delay. (b) Clock skew.

delay region sample the propagation states, but those in the long-clock-delay region do not sample the propagation states. If a transition propagates through the shortclock-region during this period, then the propagation states stored in the flip-flops in the short-clock-delay region are "unpropagated" sequences, although the transition has already propagated. After  $T_{\rm skew}$ , those in the long-clock-delay region sample the propagation states, in which the last bin of the long-clock-delay region is "propagated". Thus, T<sub>skew</sub> is added to the bin width of the last bin of the long-clockdelay region and the last bin becomes the ultra-wide bin. In contrast, in the case where the TDL crosses from the long- to the short-clock-delay region as shown in Figure 2-3 (b), the invalid thermometer code causes several missing bins. The flipflops of the short-clock-delay region near the boundary can sample the valid propagation pattern of "propagated, unpropagated". However, After  $T_{\text{skew}}$ , those in the long-clock-delay region also sample the propagation pattern of "propagated, unpropagated", because the transition continues to propagate along the TDL. Thus, the invalid thermometer pattern of "propagated, unpropagated, propagated, unpropagated" appears in the vicinity of the boundary between the short- and the

**Figure 2-3.** Timing diagrams and transfer functions of TDC in case of clock region crossing. (a) Clock region crossing from a long- to a short-clock-delay region. (b) Clock region crossing from a short- to a long-clock-delay region.

long-clock-delay region.

In the TDC transfer function, as shown in Figure 2-3, where  $t_p$  and  $t_s$  correspond to the propagation time along the delay line and the relative sampling time, respectively, early sampling shifts the transfer function of the short-clock-delay region to the right by  $T_{\rm skew}$ , and thus introduces the ultra-wide bin. On the other hand, late sampling shifts the transfer function of the long-clock-delay region to the left by  $T_{\rm skew}$ , causing the ambiguity in encoding of the corresponding fine code. Therefore, it is essential to implement the TDL in the single clock region to mitigate nonlinearity.

It is difficult to implement the TDL within a single clock region for the Virtex-6 FPGA. The minimum clock period for Virtex-6 FPGA fabric was 1.67 ns. At least 167 taps were required to implement the TDL considering the  $T_{LSB}$  was 10 ps, but the maximum number of taps in the single clock region was limited to 160. There was an interpolation loss of 70 ps when implementing the TDL TDC within a single clock region.

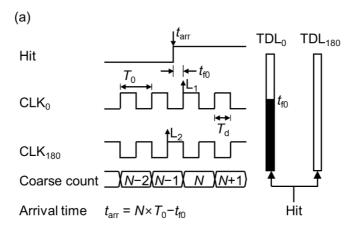

#### 2.2.3.2. The Principle of Dual-Phase TDL TDC

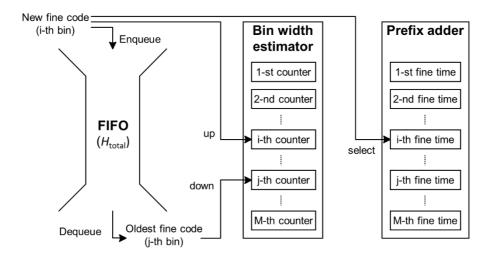

A new architecture using two TDLs of TDL<sub>0</sub> and TDL<sub>180</sub> sampled at the rising edges of the in-phase clock CLK<sub>0</sub> and the 180° out-of-phase clock CLK<sub>180</sub> was developed to implement TDC in the single clock region. The hit signal was split within the FPGA and fed into two TDLs. Each TDL covers a slightly longer period than half of  $T_0$ . In the case where the hit arrives at a TDC when CLK<sub>0</sub> is at a logic low, as shown in Figure 2-4 (a), the flip-flops of TDL<sub>0</sub> and TDL<sub>180</sub> are in the states sampled at L<sub>1</sub> and L<sub>2</sub>, respectively. Only the flip-flops of TDL<sub>0</sub> have the valid propagation states required to interpolate the fine time  $t_{f0}$ . The coarse count is obtained at the rising clock of CLK<sub>0</sub> immediately after the hit arrives, and the corresponding coarse count N yields the coarse time  $N \times T_0$ . The arrival time  $t_{arr}$  is therefore derived as in (2.2)

$$t_{\rm arr} = N \times T_0 - t_{\rm f0} \tag{2.2}$$

In the case where the hit arrives at a TDC when CLK<sub>0</sub> is at a logic high, as shown in Figure 2-4 (b), the flip-flops of TDL<sub>0</sub> and TDL<sub>180</sub> are in the states sampled

**Figure 2-4.** The principle of dual-phase TDL TDC. (a) In the case where the TDL<sub>0</sub> is selected to measure the fine time. (b) In the case where the TDL<sub>180</sub> is selected to measure the fine time.

at L<sub>3</sub> and L<sub>4</sub>, respectively. In this case, the sampled propagation states of TDL<sub>0</sub> are either valid or invalid because  $t_{f0}$  can be longer than the total delay time of a single TDL ( $T_P$ ), as shown in Figure 2-4 (b). However, the sampled propagation states of TDL<sub>180</sub> can be valid and provide a fine time  $t_{f180}$ . Therefore,  $t_{f180}$  is used when CLK<sub>0</sub> is at a logic high. The fine time is then derived as the sum of the period during which the CLK<sub>0</sub> is at a logic low ( $T_0 - T_d$ ) with  $t_{f180}$  where  $T_d$  is the duration when the CLK<sub>0</sub> is at a logic high. As per the previous case, the coarse count is obtained from the rising clock of CLK<sub>0</sub> immediately after the hit arrives, and the corresponding coarse

count N yields the coarse time  $N \times T_0$ . The  $t_{arr}$  is therefore derived as in (2.3)

$$t_{\rm arr} = N \times T_0 - (t_{\rm f180} + T_0 - T_{\rm d}) \tag{2.3}$$

#### 2.2.3.3. The Principle of Pipelined On-the-Fly Calibrator

The proposed on-the-fly calibration method is based on the code density test [40]. The code density test is a statistical method estimating every bin width. When the random hit signals are fed into the fine time interpolator, the portion of the number of collected hit signals into each fine code to the total number of hit signals is the same as the portion of the respective bin width to the clock period  $T_0$ . The i-th bin width  $w_i$  is estimated as in (2.4). The  $H_i$  and  $H_{\text{total}}$  are the measured number of hit signals collected into the i-th bin and a total number of hit signals, respectively. The i-th fine time  $f_i$  is calculated as in (2.5).

$$w_{\rm i} = \frac{H_{\rm i}}{H_{\rm total}} \times T_0 \tag{2.4}$$

$$f_{\rm i} = \frac{w_{\rm i}}{2} + \sum_{\rm k=0}^{\rm i-1} w_{\rm k} \tag{2.5}$$

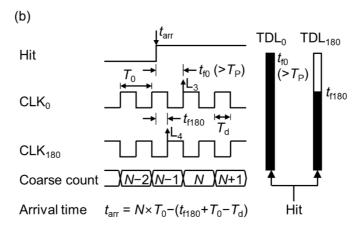

The proposed calibration method is conducted in two parallel steps as shown in Figure 2-5. The first step is the bin width identification based on the code density test; it is implemented using a fixed-depth FIFO (first in first out) memory and a set of binary counters serving as a bin width estimator. Each bin corresponds to one counter, the collected value of which is proportional to its own bin width. When the hit arrives at the TDC, the TDC yields the fine code. The new fine code is then

**Figure 2-5.** The principle of on-the-fly calibrator.

enqueued into a FIFO while increasing the value of the corresponding counter by one. Then, the oldest stored fine code is dequeued while decreasing the value of the corresponding counter by one. Using this process, the FIFO stores the most recent fine codes and the counters have up-to-date bin width information. Therefore, a  $H_{\text{total}}$ -depth FIFO and a  $H_{\text{i}}$ -count bin yield the  $w_{\text{i}}$  as in (2.4). For example, if the depth of the FIFO is 20,000 and the clock period is 2,500 ps, then the bin width of a 256-count bin is 256/20,000×2,500 ps = 32 ps. However, note that the bin width identification guarantees the calibration accuracy when a sufficient number of fine codes are booked in the FIFO.

The second step is the calibration information update, along with the continuous bin width identification. As shown in Figure 2-6, the pipelined and parallel prefix adder integrates bin widths, stored in a bin width estimator, to generate the calibration information. This process takes  $2 \times \log_2(\text{number of bins}) - 1$  clock cycles. The fine time  $f_1$  is then calibrated to the center of the TDC bins as in (2.5).

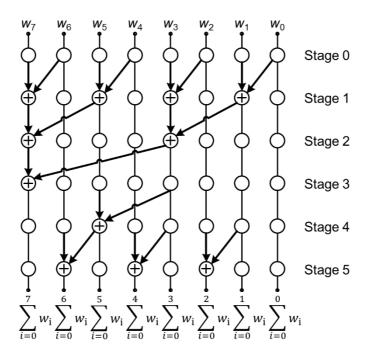

Figure 2-6. Prefix adder.

# 2.2.3.4. Implementation of Dual-Phase TDL TDC with On-the-Fly Calibrator

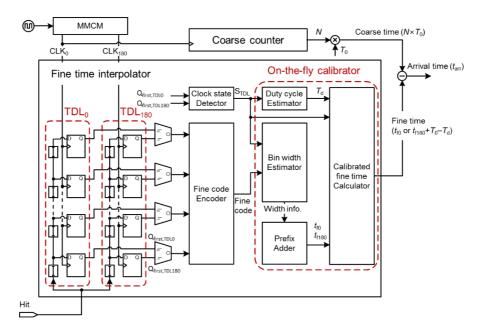

The dual-phase TDL TDC was implemented in the Virtex-6 evaluation kit. It consisted of the coarse counter and the fine time interpolator as shown in Figure 2-7. In the fine time interpolator, the TDL<sub>0</sub> was driven by a 400 MHz reference clock (CLK<sub>0</sub>) and TDL<sub>180</sub> is driven by a 180° out-of-phase clock (CLK<sub>180</sub>). A built-in 200 MHz differential oscillator (SiT9102, SiTime) provided the input clock to the mixed-mode clock manager (MMCM) that generated the high-performance clocks of CLK<sub>0</sub> and CLK<sub>180</sub>.

Each TDL consisted of 128 bins using 32 CLBs and two TDLs were located in parallel within the same clock region. When a hit was asserted into a TDC, the hit

**Figure 2-7.** Implementation of dual-phase TDL TDC with on-the-fly calibrator.

was split and fed into the two TDLs almost simultaneously. The flip-flops of TDL<sub>0</sub> and TDL<sub>180</sub> sampled the propagation states at the rising edges of CLK<sub>0</sub> and CLK<sub>180</sub>, respectively, and thus two different 128-bit thermometer codes were obtained for a single event. The  $S_{TDL}$  was used to select the TDL to interpolate the fine time and to measure the duty cycle  $T_d$ .

In the case where only the first bin of  $TDL_0$  was inverted as shown in Figure 2-4 (a), the  $S_{TDL}$  was at a logic low. In the case where both the first bins of  $TDL_0$  and  $TDL_{180}$  were inverted as shown in Figure 2-4 (b), the  $S_{TDL}$  was at a logic high. A set of multiplexers selected one of the propagation states from  $TDL_0$  or  $TDL_{180}$  depending on the  $S_{TDL}$ . The fine code encoder converted a selected 128-bit thermometer code into a 7-bit binary fine code.

The coarse counter driven by  $CLK_0$  generated the coarse time with 2.5 ns resolution. Therefore, in this architecture, the two 128-bin delay lines driven by

CLK<sub>0</sub> and CLK<sub>180</sub> provided the same effective dynamic range for the fine time as that of a 256-bin delay line without clock region crossing. The 10-ps delay bins and the effective 256-bin delay line allowed a dynamic range of 2,560 ps that covered the single clock period of 2.5 ns.

The on-the-fly calibrator consisted of a duty cycle estimator, a bin width estimator, a prefix adder, and a calibrated fine time calculator. It contained a fixeddepth FIFO, two sets of 128 binary counters used to store the bin width information of  $TDL_0$  and  $TDL_{180}$ , and one binary counter used for the duty cycle estimator. When a hit arrived at the TDC, the fine code encoder yielded the 7-bit fine code and the clock state detector yielded the S<sub>TDL</sub>. These new codes were concatenated as an 8-bit code and enqueued into the FIFO while the oldest code was dequeued. As stated above, these 8-bit codes corresponded to two sets of 128 binary counters and provided the up-to-date bin width information. In addition, S<sub>TDL</sub> was used to estimate the  $T_{\rm d}$ . If  $S_{\rm TDL}$  was at a logic high, it was involved in increasing or reducing the value of the duty cycle estimator. Using this process, the duty cycle estimator then provided up-to-date duty cycle information. Using the bin width information, two prefix adders can then generate the fine time either  $t_{f0}$  or  $t_{f180}$ . The calibrated fine time calculator yielded the calibrated fine time of either  $t_{f0}$  when  $S_{TDL}$  was at a logic low or  $t_{f180}+T_0-T_d$  when  $S_{TDL}$  was at a logic high. The  $t_{arr}$  was calculated as in (2.2) and (2.3)

#### 2.2.4. Experimental Setups and Data Processing

Two dual-phase TDL TDCs with on-the-fly calibrators were implemented in the Virtex-6 FPGA evaluation kit for arrival time difference measurements. The random hits were generated using a <sup>22</sup>Na point source, a scintillation detector, and the

auxiliary electronics. The <sup>22</sup>Na point source emitted radiation with a uniform time distribution. The scintillation detector, which consisted of a photomultiplier tube (R9800, Hamamatsu Photonics K. K.) coupled with an LYSO scintillation crystal, converted a gamma-ray into an electrical signal. The auxiliary electronics, which contained a timing discriminator (N840, CAEN), a fan-in/fan-out unit (N401, CAEN), and translator units (N89, CAEN) in order, converted an electrical signal to two copies of FPGA-compatible digital hits. Before two hits were asserted to two TDC channels, respectively, a dual delay unit (N108A, CAEN) was added to provide the known arrival time differences between two hits. The Virtex-6 FPGA evaluation kit was located in a temperature-controlled box when conducting the code density test and temperature drift test.

#### 2.2.4.1. TDC Characteristics

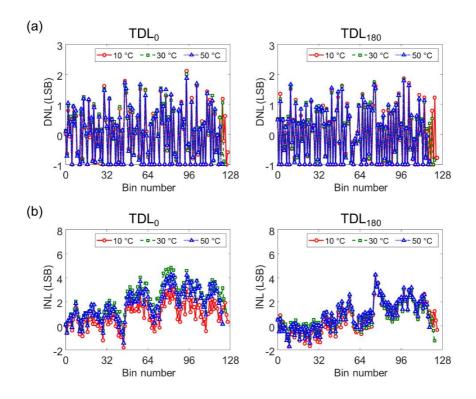

The TDC channel was characterized using the code density test with changing the ambient temperature from 10 to 50 °C in steps of 5 °C. The 102,400 samples were collected for the respective temperature.

The least significant bit (LSB)  $T_{LSB}$ , the differential non-linearity (DNL), and the integral non-linearity (INL) were characterized. The  $T_{LSB}$  was calculated by dividing  $T_0$  by the sum of the last bin numbers of TDL<sub>0</sub> and TDL<sub>180</sub>. The differential non-linearity (DNL) is a term describing the deviation of each bin width from its ideal value. The DNL of the i-th bin width  $w_i$  is calculated as in (2.6). The INL is a term describing the deviation of each fine time from the ideal TDC characteristics. The INL of the i-th bin is calculated as in (2.7)

$$DNL_{i} = \frac{w_{i} - T_{LSB}}{T_{LSB}}$$

(2.6)

$$INL_{i} = \sum_{k=0}^{i} DNL_{k}$$

(2.7)

The root-mean-square (RMS) quantization error  $\sigma_{\rm cal}$  of the ideal TDC with an LSB of  $T_{\rm LSB}$  is  $T_{\rm LSB}/\sqrt{12}$  [40]. However, the  $\sigma_{\rm cal}$  of FPGA-TDC is deteriorated because the bin width of the FPGA-TDC is non-uniform. The  $\sigma_{\rm cal}$  considering bin-width variations is calculated as in (2.8) [33, 40]. The equivalent bin width  $w_{\rm eq}$  is calculated as the bin width of the ideal TDC that has the RMS quantization error of  $\sigma_{\rm cal}$ .

$$\sigma_{\text{cal}} = \sqrt{\sum_{i=0}^{M} \frac{w_i^2}{12} \times \frac{w_i}{T_0}} = \frac{w_{\text{eq}}}{\sqrt{12}}$$

(2.8)

#### 2.2.4.2. Arrival Time Difference Measurements

The arrival time differences from 0 to 20 ns in steps of 0.5 ns were measured by two TDC channels in three conditions 'online calibration', 'offline calibration', and 'none'. The on-the-fly calibrator continuously updated the calibration information in the 'online calibration' measurements. The fine codes were used to generate the calibration information using the computer in the 'offline calibration'. All bin widths were considered equal to  $T_{\rm LSB}$  in the 'none' measurements. The 51,200 samples were collected for each measurement. The measurement uncertainty was evaluated using the maximum value of the standard deviation of the Gaussian fit.

In addition, the arrival time difference, fixed at zero, was measured in three different conditions. The first condition was with the active on-the-fly calibrator ('real-time calibration'). In this condition, the on-the-fly calibrator continuously compensated for the nonlinearity. The second and third conditions were with the on-the-fly calibrator disabled ('non-real-time calibration'). Under these conditions, the on-the-fly calibrator generated the calibration information at specific temperatures (10 and 50°C in the second and third sets of measurements, respectively) and did not update the calibration information, although the temperature changed. This calibrator operating mode conversion was performed by disabling the binary counters that serve as the duty estimator and the bin width estimator.

## 2.3. Results

#### 2.3.1. TDC Characteristics

The FPGA temperature was higher than the ambient temperature by  $8-9^{\circ}$ C. The core voltage was stabilized but decreased with the temperature increase, with values of 1.013 V at 10 °C, 1.011 V at 20 °C, 1.009 V at 30 °C, 1.006 V at 40 °C, and 1.004 V at 50 °C.

The TDC characteristics were summarized as shown in Table 2-1. The  $T_{LSB}$ , the  $\sigma_{cal}$ , and the  $w_{eq}$  slightly increased with the ambient temperature. The positive DNL and the negative DNL appear alternately as shown in Figure 2-8. However, the high positive DNL and the continuous negative DNL were not observed by implementing TDC in a single clock region. The patterns of the DNL and the INL were almost identical regardless of the ambient temperature; however, the INL values were significantly affected by the temperature drift.

**Table 2-1.** TDC characteristics.

|       | $T_{\rm LSB}$ (ps) | $T_{\rm d}({\rm ps})$ | $\sigma_{\rm cal}$ (ps) | w <sub>eq</sub> (ps) | DNL (LSB)      | INL (LSB)      |

|-------|--------------------|-----------------------|-------------------------|----------------------|----------------|----------------|

| 10 °C | 9.92               | 1,237                 | 5.33                    | 18.46                | [-1.00, +2.11] | [-1.81, +4.23] |

| 15 °C | 9.92               | 1,226                 | 5.33                    | 18.48                | [-1.00, +2.06] | [-1.55, +4.57] |

| 20 °C | 10.08              | 1,230                 | 5.34                    | 18.49                | [-1.00, +1.93] | [-1.86, +3.29] |

| 25 °C | 10.08              | 1,232                 | 5.41                    | 18.73                | [-1.00, +1.94] | [-1.63, +4.54] |

| 30 °C | 10.08              | 1,227                 | 5.38                    | 18.65                | [-1.00, +2.01] | [-1.27, +4.86] |

| 35 °C | 10.25              | 1,228                 | 5.42                    | 18.76                | [-1.00, +1.99] | [-1.69, +3.81] |

| 40 °C | 10.25              | 1,227                 | 5.47                    | 18.93                | [-1.00, +2.02] | [-1.62, +4.51] |

| 45 °C | 10.25              | 1,230                 | 5.51                    | 19.08                | [-1.00, +1.91] | [-1.70, +4.72] |

| 50 °C | 10.33              | 1,228                 | 5.51                    | 19.10                | [-1.00, +1.87] | [-1.74, +4.28] |

**Figure 2-8.** The nonlinearity of dual-phase TDL TDC. (a) DNL. (b) INL.

#### 2.3.2. Arrival Time Difference Measurements

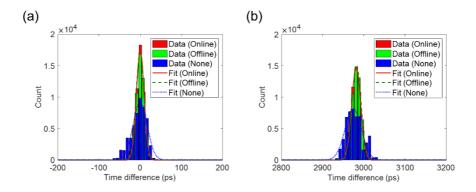

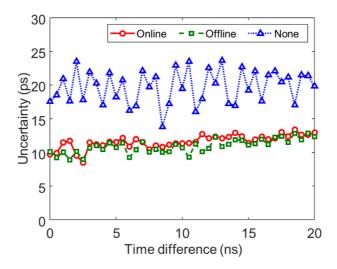

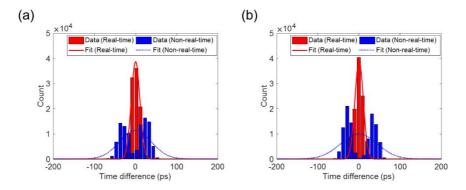

Figure 2-9 shows the time difference histograms for both hits arriving within a single clock period (Figure 2-9 (a)) and the second hit arriving a single clock period later (Figure 2-9 (b)). The propagation delay differences between the two TDC channels introduced by the external devices and cables were compensated. Figure 2-10 shows the measured uncertainty for time intervals. The measurement uncertainty values were 13.39, 12.87, and 23.65 ps with online and offline calibration methods and without calibration, respectively. The on-the-fly calibrator reduced the measurement uncertainty as well as had the comparable calibration performance with the offline calibration.

**Figure 2-9.** Time difference histograms obtained with online and offline calibration methods and without calibration. (a) Time difference of 0 ns. (b) Time difference of 3 ns.

**Figure 2-10.** Measurement uncertainty for the time differences with online and offline calibration methods and without calibration.

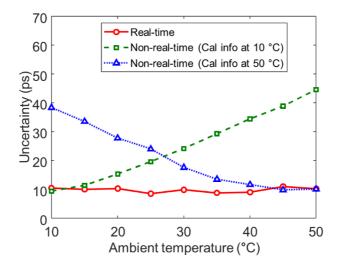

As shown in Figures 2-11 and 2-12, the measurement uncertainty for the time differences conducted with 'real-time calibration' was less than 11.07 ps. In contrast, the measurement uncertainty of the other measurements that were conducted with 'non-real-time calibration' increased up to 44.62 ps.

**Figure 2-11.** Time difference histograms with real-time calibration and non-real-time calibration. (a) In the second set of measurements with non-real-time calibration, the time differences were measured at 50 °C and the calibration information was obtained at 10 °C. (b) In the third set of measurements with non-real-time calibration, the time differences were measured at 10 °C and the calibration information was obtained at 50 °C.

**Figure 2-12.** Measurement uncertainty of the time difference measurements with real-time calibration and non-real-time calibration. The ambient temperature changed from  $10 \, ^{\circ}\text{C}$  to  $50 \, ^{\circ}\text{C}$  in steps of  $5 \, ^{\circ}\text{C}$ .

## 2.4. Discussion

The dual-phase TDL TDC enabled to implement the TDC in a single clock region with a moderate clock frequency of 400 MHz. Two 128-bin delay lines driven by CLK<sub>0</sub> and CLK<sub>180</sub> provided the same effective dynamic range for the fine time as that of a 256-bin delay line without clock region crossing. The 10-ps delay bins and the effective 256-bin delay line covered the single clock period of 2.5 ns.

Although the positive DNL and the negative DNL appeared alternately because of the unbalanced propagation delay of the carry chain, the ultra-wide bin and the continuous missing bins were not observed as shown in Figure 2-8 (a). The DNL values ranged from -1 to +2 LSB and the DNL can be improved using the bin width tuning method [39].

The INL ranged from -1.70 to +4.72 LSB and was affected by the temperature drift significantly as shown in Figure 2-8 (b); however, the on-the-fly calibrator can compensate for the INL without introducing the dead time.

The on-the-fly calibrator can improve the measurement uncertainty and showed comparable performance with the offline calibrator as shown in Figures 2-9 and 2-10. The on-the-fly calibrator with the pipelined structure can compensate for the INL variations under the temperature drifts, and thus the maintained the TDC performance as shown in Figures 2-11 and 2-12. In addition, the on-the-fly calibrator has the self-calibration capability because the gamma rays from the object obey Poisson statistics.

The FPGA-TDC is a fundamental block to implement the FPGA-based DAQ systems. The developed FPGA-TDC with the on-the-fly calibrator would improve the resolution and the performance of the highly integrated FPGA DAQ systems.

# **Chapter 3. Time-based Multiplexing Method**

## 3.1. Background

The SiPM signal multiplexing is a practical method to reduce the number of signals to handle a large number of output channels from the SiPM-based PET detectors. The most widely used multiplexing methods for the PET detectors are the charge division methods. In the charge division methods, the number of readout channels is reduced to four or five (usually, four channels for encoding the position information and one channel for timing measurement) using resistor [42, 43] or capacitor [44, 45] networks.

However, the charge division circuits have two main disadvantages. The first disadvantage is signal distortion. The shape of the signal is considerably depending on the SiPM position of the charge division network. In addition, the charge division methods demand energy measurement devices. Time pickoff devices are also required for timing measurement.

The waveform sampling method that uses a fast waveform digitizer provides both energy and timing information [46]. In addition, the time-based multiplexing method that uses a waveform digitizer can simplify the multiplexing circuits because the passive components required for charge division can be removed [47]. However, the waveform sampler should contain the ADC and a subsequent FPGA, thus the DAQ system cannot be fully simplified. Thus, a fully time-based multiplexing and readout method is required to simplify both multiplexing and DAQ systems

## 3.2. Materials and Methods

### 3.2.1. Delay Grid Multiplexing

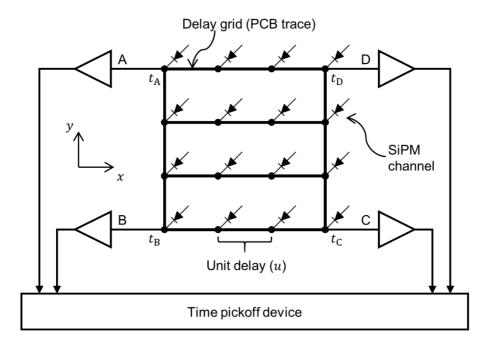

Fully time-based multiplexing and readout method consist of a delay grid that connects every SiPM output into the four timing pickoff channels [48]. The position of each SiPM within a multiplexing circuit (delay grid) is decoded using the principle of TDOA positioning. In the GPS that uses the TDOA positioning, the signal from the transmitter propagates through the medium and is received by multiple synchronized receivers. The position of the transmitter is localized using the known locations of the receivers and the TDOA information.

Similar to GPS, the position information on the fired SiPM can be decoded using the innate transit time differences from the SiPM channel to the readout channels. The transmitters, the medium, and the receivers in GPS correspond to the SiPM channels, the delay grid, and the time pickoff devices in the proposed multiplexing method. The delay grid consists of the traces in the row and column directions on a printed circuit board (PCB) where the SiPM channels of each row are connected and two column traces tie the ends of the row traces, as shown in Figure 3-1. Unit delay (*u*) is the transit time between the adjacent cathodes. The four corner nodes of the delay grid, referred to as the A, B, C, and D nodes in a counterclockwise direction, are connected into the amplifiers and the output of each amplifier is fed into the time pickoff device. When the SiPMs fire, the current signals from the SiPM flow into the delay grid and the identical signals are fed into the four corner nodes with the difference in transit times. As indicated in Table 3-1, the transit times from the SiPM channel to the readout channels are encoded uniquely.

**Figure 3-1.** Conceptual diagram for the delay grid multiplexing. Position for each SiPM channel is uniquely encoded using the innate transit times from a SiPM channel to the four corner nodes.

**Table 3-1.** Look-up table for decoding the position and the time information.

| Fir      | ing |                       | Corner node arrival time |                       |                       | Decoded       |               | Timing             |

|----------|-----|-----------------------|--------------------------|-----------------------|-----------------------|---------------|---------------|--------------------|

| position |     |                       | position                 |                       | Tilling               |               |               |                    |

| x        | у   | $t_{ m A}$            | $t_{ m B}$               | $t_{C}$               | $t_{ m D}$            | $\hat{x}$     | $\hat{y}$     | $t_{\gamma}$       |

| 0        | 0   | $3u + t_{\text{det}}$ | $0u + t_{\text{det}}$    | $3u + t_{\text{det}}$ | $6u + t_{\text{det}}$ | -1.5 <i>u</i> | -1.5 <i>u</i> |                    |

| 0        | 1   | $2u + t_{\text{det}}$ | $1u + t_{\text{det}}$    | $4u + t_{\text{det}}$ | $5u + t_{\text{det}}$ | -1.5u         | -0.5u         |                    |

| 0        | 2   | $1u + t_{\text{det}}$ | $2u + t_{\text{det}}$    | $5u + t_{\text{det}}$ | $4u + t_{\text{det}}$ | -1.5u         | 0.5 <i>u</i>  |                    |

| 0        | 3   | $0u + t_{\text{det}}$ | $3u + t_{\text{det}}$    | $6u + t_{\text{det}}$ | $3u + t_{\text{det}}$ | -1.5u         | 1.5 <i>u</i>  | 3u                 |

| 1        | 0   | $4u + t_{\text{det}}$ | $1u + t_{\text{det}}$    | $2u + t_{\text{det}}$ | $5u + t_{\text{det}}$ | -0.5u         | -1.5 <i>u</i> | $+ t_{\text{det}}$ |

| 1        | 1   | $3u + t_{\text{det}}$ | $2u + t_{\text{det}}$    | $3u + t_{\text{det}}$ | $4u + t_{\text{det}}$ | -0.5u         | -0.5u         |                    |

| :        | :   | :                     | :                        | :                     | :                     | ÷             | ÷             |                    |

| 3        | 3   | $3u + t_{\text{det}}$ | $6u + t_{\text{det}}$    | $3u + t_{\text{det}}$ | $0u + t_{\text{det}}$ | 1.5 <i>u</i>  | 1.5 <i>u</i>  |                    |

Using the TDOA measurements obtained at the A, B, C, and D nodes, the positions can be decoded as in (3.1) and (3.2). The values  $t_A$ ,  $t_B$ ,  $t_C$  and  $t_D$  are the corner node arrival times at the A, B, C, and D nodes, which are the sums of the transit times from the SiPM channel to the A, B, C, and D nodes and the gamma arrival time  $t_\gamma$ , respectively. The  $t_\gamma$  is the time when the gamma-ray interacts with the SiPM-based scintillation detector and calculated as in (3.3).

$$\hat{x} = \frac{+t_{A} + t_{B} - t_{C} - t_{D}}{4} \tag{3.1}$$

$$\hat{y} = \frac{-t_{A} + t_{B} + t_{C} - t_{D}}{4} \tag{3.2}$$

$$t_{\gamma} = \frac{+t_{A} + t_{B} + t_{C} + t_{D}}{4} \tag{3.3}$$

## 3.2.2. Detector for Concept Verification

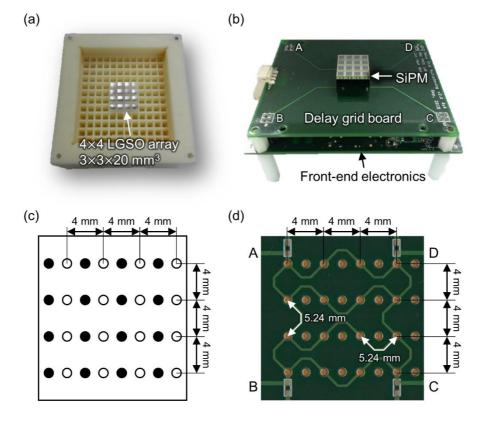

Figure 3-2 shows a SiPM-based detector assembled to show the feasibility of the proposed multiplexing method. The SiPM detector consisted of an array of  $4\times4$  LGSO crystals (Hitachi Chemical Ltd) and one-to-one coupled SiPM (S11064-050P; Hamamatsu Photonics. K.K.) as shown in Figures 3-2 (a) and (b). Each SiPM channel had an active area of  $3\times3$  mm<sup>2</sup> and both pitches of the cathode pins along the x and y directions were 4 mm as shown in Figure 3-2 (c). Each crystal had a dimension of  $3\times3\times20$  mm<sup>3</sup>. All crystal surfaces were chemically polished and wrapped with enhanced specular reflectors (ESR, 3M) with the exception of the exit face. Optical adhesive (Optically Clear Adhesive 8146-4, 3M) with a refractive index of 1.474 and a uniform thickness of 100  $\mu$ m was used to improve the optical coupling between the crystal and the SiPM.

**Figure 3-2.** LGSO/SiPM detector using the proposed multiplexing method. (a) LGSO crystal array assembled into the frame. (b) Mounted SiPM on a delay grid board and the front-end electronics. (c) Backside of the employed SiPM. The blank and the filled circles indicate the pinout of the cathodes and the anodes, respectively. (d) Detailed view of a delay grid board.

All the crystals were assembled into an in-house frame produced in our previous work [49] using a 3D printer (Mojo, Stratasys), as shown in Figure 3-2 (a). The crystal pitches along the x and y directions were 4.05 and 4.50 mm, respectively, which were equal to the SiPM pitches. As shown in figure 3-2 (b), the LGSO/SiPM detector was mounted on a delay grid board.

The delay grid is a planar array of the microstrips on an FR-4 substrate with the relative permittivity of 4.3 as shown in Figure 3-2 (d). The trace lengths between the cathode pins along the x and y directions were 5.24 mm. The width of the trace and the height with respect to the reference plane were 0.3 and 1.3 mm, respectively.

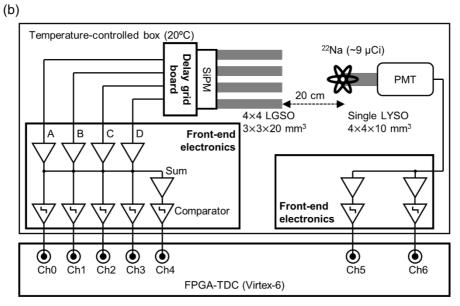

#### 3.2.3. Front-end Electronics

Front-end electronics provided either analog or digital signals containing the corner node arrival times with the time pickoff device. The signal chain was as follows. The four corner nodes of the delay grid board were connected to an in-house front-end electronics that contained the amplifiers and the comparators, as shown in Figure 3-2 (b).

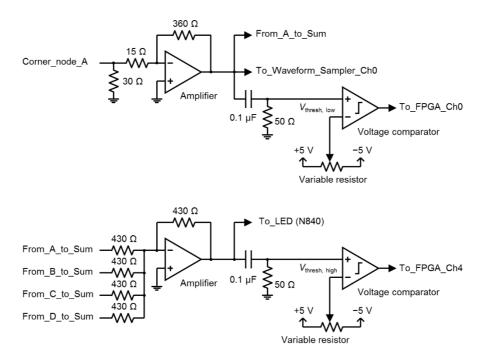

Figure 3-3 shows the detailed schematic of the front-end electronics for the LGSO/SiPM detector. The current signals that arrived at the A, B, C, and D nodes were converted into the voltage signals with an input impedance of 10  $\Omega$  and then amplified by -24 using inverting amplifiers. These signals were denoted as the A, B,

**Figure 3-3.** Schematic of the front-end electronics for the LGSO/SiPM detector. In the measurements using the waveform sampler, the bypass capacitors between the amplifiers and the comparators were detached. In the measurements using the FPGA-TDC, the cables connecting the front-end electronics to the waveform sampler and the leading edge discriminator (LED) module were detached.

C, and D signals, respectively. The summing amplifier added the A, B, C, and D signals and then provided the Sum signal. The traces from the A, B, C, and D amplifiers to the summing amplifier were designed to be the same lengths. Either analog A, B, C, and D signals or digital A, B, C, D, and Sum signals after discriminating the analog signals with the comparators were transmitted to the time pickoff device. The voltage threshold of the comparator was adjusted using a variable resistor and fixed during the measurement.

## 3.2.4. Experimental Setups

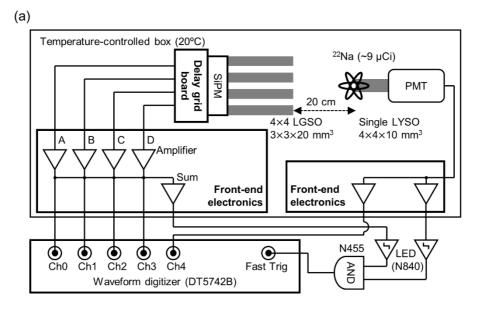

The LGSO/SiPM detector was evaluated in the coincidence detection mode with a reference detector, as shown in Figure 3-4. We used the PMT-based scintillation detector with a single timing resolution (STR) of 197 ps full width at half maximum (FWHM) as the reference detector [50]. A  $^{22}$ Na point source (approximately 9  $\mu$ Ci) was attached to the reference detector. The distance between the LGSO/SiPM and reference detectors was 20 cm. The ambient temperature was fixed at 20  $^{\circ}$ C using a temperature-controlled box.

We obtained 400,000 coincidence events for every measurement, with the exception of ToT nonlinearity calibration. In order to calibrate the nonlinearity of ToT, we acquired 1,024,000 coincidence events for a <sup>22</sup>Na and 1,024,000 singles events for <sup>131</sup>I and <sup>137</sup>Cs.

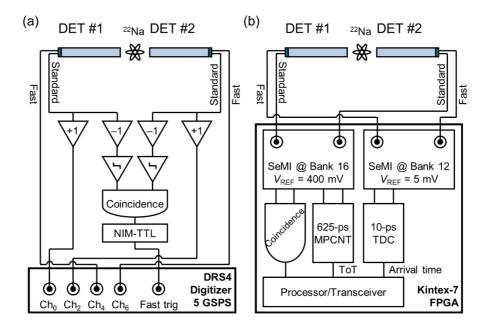

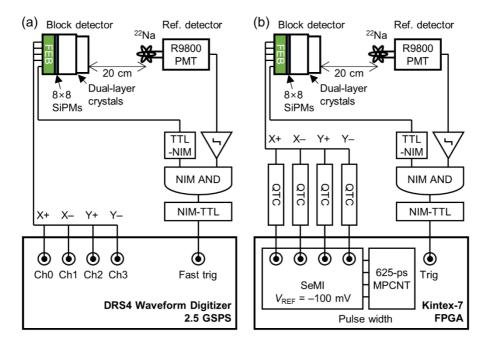

**Figure 3-4.** Experimental setups using (a) the waveform digitizer and (b) the FPGA-TDC.

#### 3.2.4.1. Data Acquisition Using the Waveform Digitizer

For the purpose of initial verification, we used a fast waveform digitizer (DT5742B, CAEN) based on switched capacitor arrays (SCAs). The SCA is the fourth version of the domino ring sampler (DRS4, PSI) and provides a resolution of 12 bits and a sampling rate of up to 5 Giga-samples/sec [46].

The leading edge discriminator (LED) modules (N840; CAEN) and a coincidence unit (N455; CAEN) were used to obtain only coincidence events, as shown in Figure 3-4 (a). The A, B, C, and D signals were acquired using a waveform digitizer at the respective readout channels. The output of the summing amplifier was used to generate a trigger, and instead, the Sum signal was obtained by adding the sampled A, B, C, and D waveforms. The time differences from the four corner nodes to the respective readout channels due to cable length differences were corrected before adding the sampled A, B, C, and D waveforms. The signal from the reference detector was also sampled.

The common bias voltage was applied to all SiPM channels where the breakdown voltages were -69.7 V. The overvoltage was swept from 2.1 to 3.6 V (bias voltages from -71.8 to -73.3 V) in steps of 0.3 V to find the optimal bias voltage where the SiPM provided the lowest coincidence timing resolution (CTR).

#### 3.2.4.2. Data Acquisition Using the FPGA-TDC

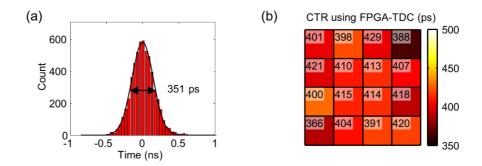

After verifying the concept of delay grid multiplexing using the waveform digitizer, we replaced the waveform digitizer with an FPGA-TDC to verify that the readout circuits can be further simplified. A multi-channel TDC with a 10-ps resolution and the sub-10-ps single-shot precision implemented in a Virtex-6 FPGA was used [38, 39].

In the front-end electronics for the LGSO/SiPM detector, the A, B, C, D, and Sum signals of the LGSO/SiPM detector were discriminated using the voltage comparators, and then the digital signals that contained the arrival times and ToT were transmitted to the FPGA-TDC. In the front-end electronics for the reference detector, the signal from the reference detector was discriminated by two comparators with different threshold levels. In the FPGA, either singles or coincidence events within the predetermined time window were obtained [51]. The overvoltage of 2.7 V at which the SiPM provided the lowest CTR in the measurements using the waveform digitizer was applied to the LGSO/SiPM detector when the FPGA-TDC was employed as a data acquisition system.

### 3.2.5. Data Processing and Analysis

#### 3.2.5.1. Waveform Digitizer

#### **Rise Time and Decay Time**

To show that the signal was not distorted by the multiplexing circuit, the rise and decay times of the A, B, C, D, and Sum signals were obtained. The rise time was evaluated using the time taken by a signal to change from 10% to 90% of its peak amplitude  $v_{\text{peak}}$ . The decay time  $\tau$  was obtained by fitting the trailing edge of the waveform to an exponential decay function  $v_{\text{peak}} \times \exp(-t/\tau)$ .

#### **Time Pickoff**

To obtain the position and the gamma arrival time  $t_{\gamma}$ , we sampled the signals at 5 Giga-samples/sec and interpolated the leading edge of the waveform using a cubic spline interpolation by a factor of 20 to obtain the resolution of 10 ps, and thus minimize the quantization error. We picked off the corner node arrival times by

applying either constant voltage discriminator (also known as LED) or constant fraction discriminator (CFD) to the leading edge of the interpolated waveforms where the baseline for time pickoff was determined at the onset of the signal with time window of 2 ns in order to minimize the effect of dark noise on time pickoff [52]. The threshold for time pickoff was determined as the percentage of peak amplitude of events within an energy window and denoted as the percentage (%) threshold hereinafter. For LED, the constant voltage threshold calculated by averaging the percentage thresholds of all the events within the energy window was applied to every signal. For CFD, the threshold was determined as a constant percentage of peak amplitude for each signal.

#### **Position**

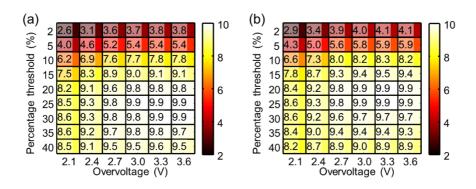

The position information was obtained from the corner node arrival times  $t_A$ ,  $t_B$ ,  $t_C$ , and  $t_D$  using equations (3.1) and (3.2). Both LED and CFD were employed and the percentage threshold used for obtaining the position information was swept from 2% to 40% in order to analyze the effect of threshold on the position.

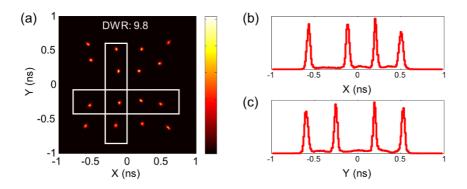

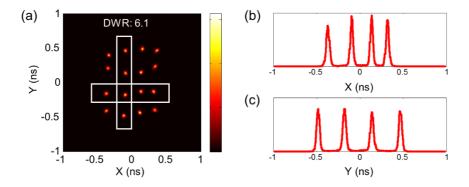

The flood map was used to display the position information, while the events within a 400–600 keV energy window were employed. Flood-map quality was evaluated using a distance-to-width ratio (DWR) in the flood map. The DWR is defined as the distance between the two adjacent spots in the flood map to the average FWHM of the two spots, and it is calculated as in (3.4).

$$DWR = \frac{2}{N_{adj}} \left( \sum_{i,j \in adj \text{ pair}}^{N_{adj}} \frac{x_i - x_j}{w_{x,i} + w_{x,j}} + \frac{y_i - y_j}{w_{y,i} + w_{y,j}} \right)$$

(3.4)

In equation (3.4),  $x_i$ ,  $y_i$  and  $x_j$ ,  $y_j$  are the x and y positions of the i-th and j-th crystals in the flood map, respectively. The  $w_{x,i}$ ,  $w_{y,i}$  and  $w_{x,j}$ ,  $w_{y,j}$  are the FWHM of 1D profiles along the x and y directions of the i-th and j-th crystals, respectively.  $N_{adj}$  is the number of adjacent crystal pairs. A larger DWR indicates that the crystals are more clearly resolved.

To perform a per-crystal analysis, the crystals in the flood map were identified using the k-means clustering, while the initial values of the iterations were determined as the peak positions of the flood map. All the results were represented as the mean  $\pm$  standard deviation of the measurements of resolved crystals.

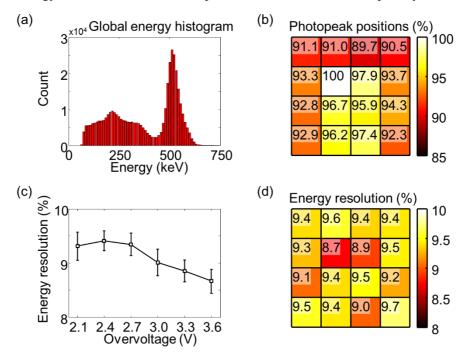

#### **Energy**

Energy information was calculated using the integration of sampled waveforms (sum of areas of the baseline-corrected A, B, C, and D waveforms). The baseline for energy integration was calculated using the mean value of the first 50 data points (10 ns) before the onset of the signal on an event-by-event basis. The energy integration window was 700 data points (140 ns).

The photopeak positions and the energy resolution were evaluated. The energy resolution was obtained by fitting the energy with a Gaussian function on a percrystal basis.

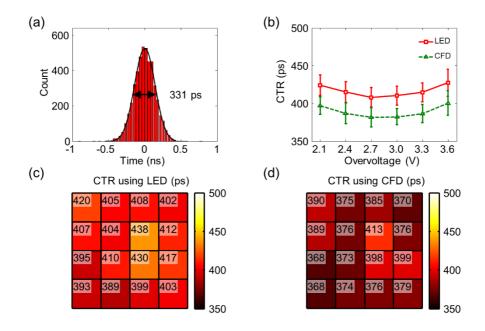

### **CTR**

The  $t_{\gamma}$  can be acquired using either digital LED or CFD. The percentage threshold used to pickoff  $t_{\gamma}$  was swept from 1% to 5% in steps of 0.5% and the 2% threshold yielded the lowest CTR values for both LED and CFD, and thus the 2% threshold was employed.

The events within the 400–600 keV energy windows of the LGSO/SiPM and reference detectors were employed to evaluate the CTR. The CTR between two identical LGSO/SiPM detectors  $CTR_{Test/Test}$  was calculated and notated hereinafter. From the FWHM of Gaussian fits applied to the time-difference histograms between the LGSO/SiPM and reference detectors  $CTR_{Test/Ref}$ , the STR of the reference detector of 197 ps FWHM was subtracted in the quadrature, and then that of the LGSO/SiPM detector was multiplied by  $\sqrt{2}$ , as in (3.5).

$$CTR_{Test/Test} = \sqrt{2} \times \sqrt{CTR_{Test/Ref}^2 - STR_{Ref}^2}$$

(3.5)

#### 3.2.5.2. FPGA-TDC

#### **Dual-threshold ToT**

Dual-threshold ToT was employed for both the LGSO/SiPM and reference detectors to extract the precise timing and energy information. As shown in Figure 3-5, the arrival time  $t_{arr}$  was obtained using the time when the signal crossed the low threshold  $V_{thresh,low}$  in its leading edge, while the ToT was calculated by subtracting this arrival time from the time when the signal crossed the high threshold  $V_{thresh,high}$  in its trailing edge. For the LGSO/SiPM detector, the  $V_{thresh,low}$  of 2% threshold and the  $V_{thresh,high}$  of 40% threshold were applied to the four corner readout channels and Sum readout channel, respectively; the ToT was calculated within an FPGA by subtracting  $t_{\gamma}$  from the time when the Sum signal crossed the  $V_{thresh,high}$  in its trailing edge. For the reference detector, the  $V_{thresh,low}$  of 5% threshold and the  $V_{thresh,high}$  of 30% threshold were applied to the respective channels. For both detectors, false

**Figure 3-5.** Dual-threshold ToT.

events with peak amplitudes lower than the  $V_{\text{thresh,high}}$  were rejected.

The ToT measurement was calibrated into the energy value using the calibration curve that compensated both nonlinearities of SiPM and ToT [15].

$$ToT(E) = c + a \times \ln[1 - \exp(-b \times E)]$$

(3.6)

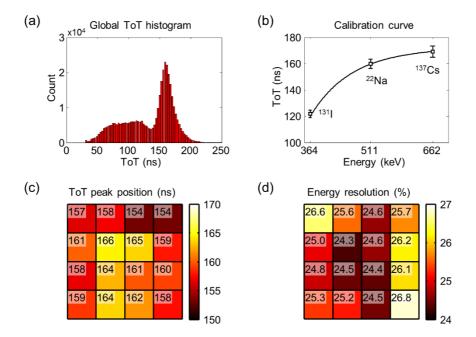

In equation (3.6), E indicates the energy of the incident gamma ray and a, b, and c are the constants to be determined for each crystal. Nonlinearity calibration was conducted in three steps. First, we obtained the photopeak positions of the ToT spectra for three radioisotopes with known energies:  $^{131}$ I (364 keV),  $^{22}$ Na (511 keV), and  $^{137}$ Cs (662 keV). Second, we solved equation (3.6) to acquire the calibration curve on a per-crystal basis. Third, we applied per-crystal calibration curves to the ToT measurements.

#### **Performance Evaluation**

The x and y positions and the  $t_{\gamma}$  were calculated from the corner node arrival times obtained by an FPGA-TDC using the equations (3.1), (3.2), and (3.3), respectively. Energy, DWR, and CTR were assessed using the same data analysis procedures conducted with the waveform digitizer.

## 3.3. Results

### 3.3.1. Waveform Digitizer

### 3.3.1.1. Waveform, Rise Time, and Decay Time

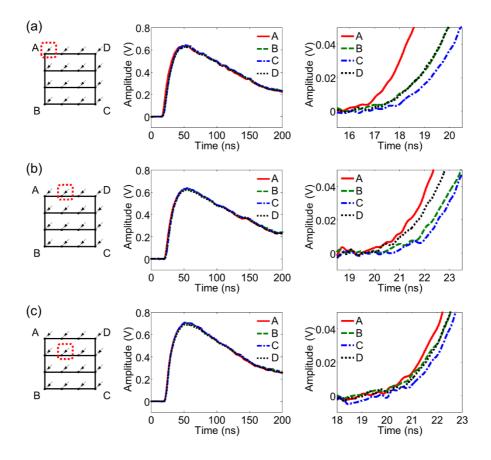

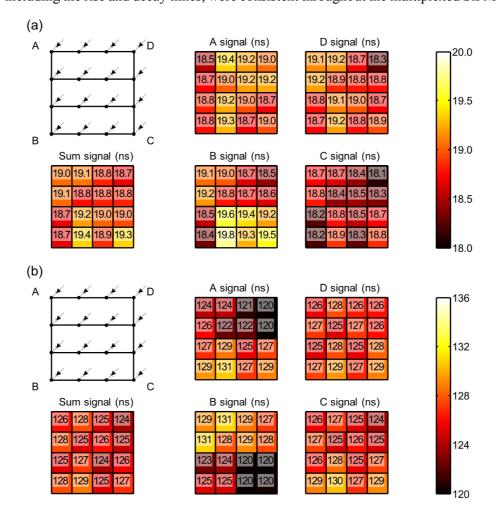

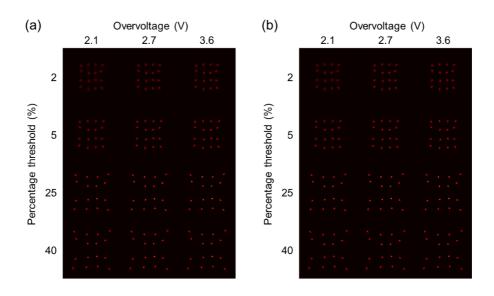

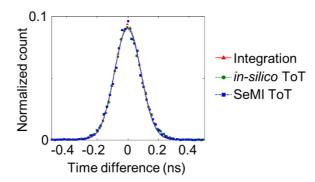

Figure 3-6 shows the A, B, C, and D signals that originated from the corner, edge, and center locations of the multiplexing circuit. For each event, the A, B, C, and D signals were almost identical, but with the TDOAs. The TDOAs described in Table 3-1 were measured as expected. The signal arrived at the four corner nodes in