# UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL INSTITUTO DE INFORMÁTICA PROGRAMA DE PÓS-GRADUAÇÃO EM MICROELETRÔNICA

# MATEUS SAQUETTI PEREIRA DE CARVALHO TIRONE

# Programmable virtual Switches: Design and Implementation of the Forwarding Engine and Supporting Features

Thesis presented in partial fulfillment of the requirements for the degree of Master of Microeletronics

Advisor: Prof. Dr. José Rodrigo Azambuja Coadvisor: Prof. Dr. Weverton Cordeiro

### **CIP** — **CATALOGING-IN-PUBLICATION**

Tirone, Mateus Saquetti Pereira de Carvalho

Programmable virtual Switches: Design and Implementation of the Forwarding Engine and Supporting Features / Mateus Saquetti Pereira de Carvalho Tirone. – Porto Alegre: PG-MICRO da UFRGS, 2020.

87 f.: il.

Thesis (Master) – Universidade Federal do Rio Grande do Sul. Programa de Pós-Graduação em Microeletrônica, Porto Alegre, BR–RS, 2020. Advisor: José Rodrigo Azambuja; Coadvisor: Weverton Cordeiro.

1. Programmable forwarding planes. 2. P4. 3. Virtualization. 4. NetFPGA SUME. I. Azambuja, José Rodrigo. II. Cordeiro, Weverton. III. Programmable virtual Switches: Designand Implementation of the ForwardingEngine and Supporting Features

#### UNIVERSIDADE FEDERAL DO RIO GRANDE DO SUL

Reitor: Prof. Rui Vicente Oppermann Vice-Reitora: Prof<sup>a</sup>. Jane Fraga Tutikian

Pró-Reitor de Pós-Graduação: Prof. Celso Giannetti Loureiro Chaves Diretora do Instituto de Informática: Prof<sup>a</sup>. Carla Maria Dal Sasso Freitas

Coordenadora do PGMICRO: Prof. Tiago Roberto Balen

Bibliotecária-chefe do Instituto de Informática: Beatriz Regina Bastos Haro

| "If I have seen farther than others,               |

|----------------------------------------------------|

| it is because I stood on the shoulders of giants." |

| — SIR ISAAC NEWTON                                 |

#### **ACKNOWLEDGMENT**

I would like to thanks my parents, Maria and Luis, that have always taken care of me. I am grateful for all support and learning that allowed me to be who I am. Thank you for believing in me even when I thought that I was not capable. Thank you for all unconditional love.

Mônica, thank you for all love and support, mainly on the hard days. Thank you for being my safe harbor, for being at my side and do not give up on me. You are so much more than a wife. You are my love, my partner, and my best friend, and I am so thankful for that. Thank you for making me so happy. I love you.

Many thanks to all my friends and family that even far supported me.

Finally, I would like to express my special thanks for gratitude to my advisors José and Weverton who allowed me to work on this project. Thank you for trusting in me and for all your dedication and guidance. You are an inspiration for me.

#### **ABSTRACT**

Virtualization has become the powerhouse for several networking concepts, from virtual local area networks (VLANs) to software switches, software-defined control plane, etc. Recent proposals like HyPer4, HyperVDP, and P4Visor brought the concept to the forwarding plane, by enabling *emulation* of several network contexts and/or composing several functions through a single program. In spite of the progress achieved, the real potential of forwarding plane virtualization remains untapped. In this work, we present PvS, a reconfigurable architecture for data plane virtualization. PvS provides parallel execution and hot-swapping of virtual switch instances, without requiring switch source code (for either emulation or program composition). We experimented PvS on a NetFPGA-SUME board with four virtual switches: a layer-2 switch, a simple router, a firewall, and an inband telemetry. Area occupation measurements evidence the feasibility of running up to eight virtual switches in parallel. Compared to existing work, performance data show an improvement of up to two orders of magnitude for bandwidth and six orders for latency.

Keywords: Programmable forwarding planes. P4. virtualization. NetFPGA SUME.

# Switches virtuais Programáveis: Projeto e Implementação do Mecanismo de Encaminhamento e Recursos de Suporte

### **RESUMO**

A virtualização se tornou a potência de vários conceitos de rede, de redes locais virtuais (VLANs) a switches definidos por software, plano de controle definido por software, etc. Propostas recentes como HyPer4, HyperVDP e P4Visor levaram o conceito ao plano de encaminhamento, permitindo *emulação* de vários contextos de rede e/ou compondo várias funções através de um único programa. Apesar do progresso alcançado, o verdadeiro potencial da virtualização do plano de encaminhamento permanece inexplorado. Neste trabalho, apresentamos PvS, uma arquitetura reconfigurável para virtualização do plano de dados. PvS fornece execução paralela e hot swap de instâncias de switches virtuais, sem a necessidade de código-fonte do switch (para emulação ou composição de programa). Experimentou-se PvS em uma placa NetFPGA-SUME com quatro switches virtuais: um switch de camada 2, um roteador simples, um firewall e um switch de telemetria de rede(*in-band telemetry*). As medições de ocupação da área evidenciam a viabilidade de executar até treze switches virtuais em paralelo. Comparado aos trabalhos existentes, os dados de desempenho mostram uma melhoria de até duas ordens de magnitude para largura de banda e seis ordens para latência.

**Palavras-chave:** plano de encaminhamento programável, P4, virtualização, NetFPGA SUME.

# LIST OF ABBREVIATIONS AND ACRONYMS

ASIC Application Specific Integrated Circuit

BEL Basic Element of Logic

BMv2 Behavioral Model version 2

BOQ BRAM Output Queues

BRAM Block Random Access Memory

CAM Content Addressable Memory

CDPI Control-Data-Plane Interface

CLB Configurable Logic Blocks

CLI Command Line Interface

CPLD Complex Programmable Logic Device

CvSI Control virtual Switch Interface

DMA Direct Memory Access

DSL Domain-Specific Language

FPGA Field-Programmable Gate Array

GTH Gigabyte Transceiver

HDL Hardware Description Language

HLIR High-Level Intermediate Representation

IA Input Arbiter

IP Intellectual Property

IvSI Input virtual Switch Interface

JTAG Joint Test Action Group

LAN Local Area Network

LUT Look-Up Table

NFV Network Function Virtualization

ONF Open Networking Foundation

OPL Output Port Lookup

OvSI Output virtual Switch Interface

P4 Programming Protocol-Independent Packet Processors

PCIe Peripheral Component Interconnect Express

POF Protocol-Oblivious Forwarding

PvS Programmable virtual Switches

PR Partial Reconfiguration

QSH High-Speed Socket

QTH High-Speed Terminal

RDMA Remote Direct Memory Access

RISC Reduced Instruction Set Computer

RMT Reconfigurable Match-action Tables

RM Reconfigurable Modules

SFP Small Form Factor Pluggable

SSS Simple Sume Switch

TCAM Ternary Content Addressable Memory

VI Virtual Internet

VSS Very Simple Switch

VLAN Virtual Local Area Network

VXLAN Virtual Extensible LAN

vS virtual Switch

WAN Wide Area Networks

# LIST OF FIGURES

| Figure 1.1    | PvS Overview                                                                                                                               | 20        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| Figure 2.1    | The Basic PISA Pipeline                                                                                                                    | 30        |

|               | Arrangement of Slices within the CLB of the FPGA Xilinx Virtex 7                                                                           |           |

|               | Canonical NetFPGA reference design.                                                                                                        |           |

| Figure 3.1    | PvS proposal in the literature                                                                                                             | 39        |

| Figure 3.2    | An overview of a conceptual architecture of a programmable virtual hypervisor, and its relationship with key elements that compose a high- |           |

| level S       | Software Defined Networking (SDN) architecture.                                                                                            | 43        |

| Figure 4.1    | NetFPGA SUME Board Peripherals Subsystems                                                                                                  | 47        |

|               | NetFPGA SUME Board Block Desig                                                                                                             |           |

|               | PvS Forwarding Engine Architecture                                                                                                         |           |

| Figure 5.1    | High-Level Synthesis flow overview                                                                                                         | 55        |

|               | Xilinx P4-SDNet compilation flow                                                                                                           |           |

| _             | Building a vS IP.                                                                                                                          |           |

| Figure 6.1    | FPGA Configuration with Full Bitstream                                                                                                     | 62        |

|               | FPGA Reconfiguration with Partial Bit File                                                                                                 |           |

| Figure 7.1    | Port saturation throughput measurement                                                                                                     | 70        |

| _             | FPGA saturation throughput and latency                                                                                                     |           |

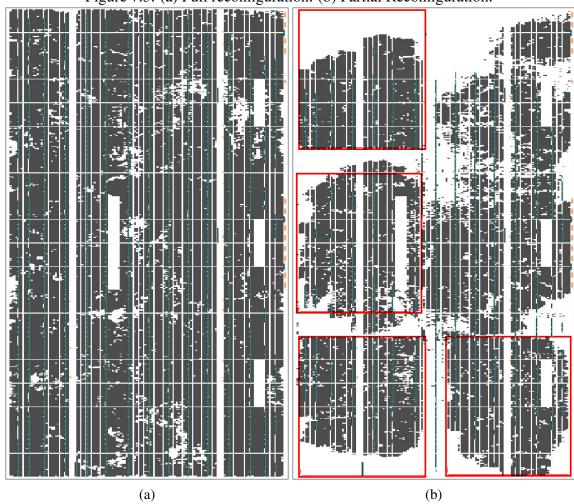

|               | (a) Full reconfiguration. (b) Partial Reconfiguration.                                                                                     |           |

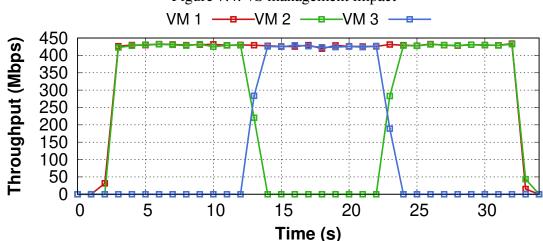

|               | vS management impact                                                                                                                       |           |

| 1 15010 / 1 1 | 10 1110110 A 11110 1111 A 1111 A 1 1 1 1                                                                                                   | • • • • • |

# LIST OF TABLES

| Table 2.1 | Simple Sume Switch sume_metadata Fields Description    | 36 |

|-----------|--------------------------------------------------------|----|

|           | Existing work on virtualization of forwarding elements |    |

| Table 7.1 | NetFPGA SUME resource usage                            | 68 |

|           | Match-action table usage                               |    |

| Table 7.3 | Simulated throughput and Latency                       | 69 |

# CONTENTS

| 1 INTRODUCTION                                                     | 19 |

|--------------------------------------------------------------------|----|

| 1.1 Motivation                                                     | 21 |

| 1.2 Contributions                                                  | 22 |

| 1.3 Outline                                                        | 23 |

| 2 BACKGROUND AND STATE OF THE ART                                  | 25 |

| 2.1 Domain-Specific Language (DSL)                                 | 25 |

| 2.1.1 Protocol-Oblivious Forwarding (POF)                          | 26 |

| 2.1.2 Programming Protocol-Independent Packet Processors (P4)      | 27 |

| 2.2 Virtualization                                                 |    |

| 2.3 Protocol Independent Switch Architecture (PISA)                | 30 |

| 2.4 Field-Programmable Gate Arrays (FPGA)                          | 31 |

| 2.5 Related Work                                                   | 33 |

| 2.5.1 Switch Program Emulation                                     | 34 |

| 2.5.2 Switch Program Composition and Parallel Execution            |    |

| 2.5.3 Software Switches                                            | 35 |

| 2.5.4 Canonical NetFPGA Reference Design Architecture              | 35 |

| 2.5.5 Summary                                                      |    |

| 3 PVS PROPOSAL                                                     | 39 |

| 3.1 Design Principles                                              | 39 |

| 3.2 PvS: Programmable virtual Switch Hypervisor for the Data Plane |    |

| 3.2.1 Memory slicing                                               | 43 |

| 3.2.2 Virtual ports                                                | 44 |

| 3.2.3 Management interfaces                                        |    |

| 4 FORWARDING ENGINE IMPLEMENTATION                                 |    |

| 4.1 Forwarding Engine Design Overview                              |    |

| 4.2 Tx/Rx Ports                                                    |    |

| 4.3 Input vS Interface (IvSI)                                      |    |

| 4.4 Virtual Switch Array (vS Array)                                |    |

| 4.5 Output vS Interface (OvSI)                                     |    |

| 4.6 Control vS Interface (CvSI)                                    |    |

| 5 HIGH-LEVEL SYNTHESIS FLOW                                        |    |

| 5.1 P4-to-HDL HLS flow                                             |    |

| 5.2 PvS Wrapper Generation Flow                                    | 58 |

| 5.3 Driver Generation Flow                                         |    |

| 6 RECONFIGURATION METHODOLOGY                                      |    |

| 6.1 Full Reconfiguration Methodology                               |    |

| 6.2 Partial Reconfiguration Methodology                            |    |

| 7 EVALUATION                                                       |    |

| 7.1 Resource Utilization and Performance                           |    |

| 7.1.1 Resource Utilization and Operating Frequency                 | 67 |

| 7.1.2 Scenario 1: Simulated Performance                            |    |

| 7.1.3 Scenario 2: Port Saturation Performance                      |    |

| 7.1.4 Scenario 3: FPGA Saturation Performance                      |    |

| 7.2 Reconfiguration Analysis                                       |    |

| 7.2.1 Resource Allocation                                          |    |

| 7.2.2 Reconfiguration Times                                        |    |

| 7.3 Impact of vS Management                                        |    |

| 7.4 Use Case: In-Band Telemetry                                    | 74 |

| 8 CONCLUSION                                  | 75 |

|-----------------------------------------------|----|

| 8.1 Future Work                               | 75 |

| 8.1.1 Network Segmentation                    |    |

| 8.1.2 Performance Guarantees                  |    |

| 8.1.3 Security Implications                   | 76 |

| 8.1.4 Community Development                   |    |

| REFERENCES                                    |    |

| APPENDIX A — PVS FORWARDING ENGINE TUTORIAL   |    |

| A.1 Preparing the Environment                 |    |

| A.2 Executing the HLS Flow                    |    |

| A.3 Downloading the Example to the FPGA Board |    |

| APPENDIX B — PUBLICATIONS                     |    |

#### 1 INTRODUCTION

The concept of programmable forwarding planes has seen a renewed interest by industry and academia with the advent of Domain-Specific Languages (DSL) like POF (SONG, 2013a) and P4 (BOSSHART et al., 2014). These languages unleashed innovation in the data plane (CORDEIRO; MARQUES; GASPARY, 2017), helping break further the "network ossification".

Resource sharing through virtualization has become commonplace in modern public and private clouds, powering virtual abstractions for servers (KOPONEN et al., 2014), network functions (MARTINS et al., 2014; HWANG; RAMAKRISHNAN; WOOD, 2015; LI et al., 2016; YI et al., 2018), forwarding devices (DOBRESCU et al., 2009; SHERWOOD et al., 2009; PFAFF et al., 2015; SHAHBAZ et al., 2016; KUMAR et al., 2019), and even entire control planes (JIN et al., 2015; BLENK et al., 2015; AFOLABI et al., 2018) running atop a shared infrastructure. These virtual abstractions are highly convenient, as they enable efficient resource usage for network providers and resource isolation for network tenants.

Thus the motivations for virtualization in the data plane are manifold, including network slicing and snapshotting, network function composition, and switch program profiling and debugging (HANCOCK; MERWE, 2016). Yet, existing "hypervisors" for P4-based switches have only enabled switch *emulation* (HANCOCK; MERWE, 2016; ZHANG et al., 2019) or composition of P4-based switch functions into a single program (ZHENG; BENSON; HU, 2018). As a result, they may pose a severe performance penalty and a large memory footprint. More importantly, they require access to switch source code for merging and custom compilation, thus violating the intellectual property of the programmable switches developers and vendors.

In this work, we argue in favor of a virtualization model for programmable forwarding elements that offers switch developers (and vendors) the possibility to distribute switch bytecode while preserving their intellectual property. In such a model, network operators would deploy on the hypervisor the same switch bytecode that otherwise would run directly on bare metal. For being a competitive model, the hypervisor should ensure that each virtual switch delivers the performance similarly, regardless of being run atop the switch hypervisor or hardware.

Delivering such a model is inherently challenging. The fundamental challenge is decoupling virtual switch instances from the hypervisor, while providing a virtual switch

abstraction that offers strict performance and isolation guarantees. Also, deploying a virtual switch should not interrupt other running virtual instances, and switch development/compilation should be agnostic of any particularities of the hypervisor. These requirements should be met while ensuring that virtual switch instances retain the same capabilities of a traditional programmable forwarding element. The approach taken is slicing the physical switch into a set of disjoint pipelines of match-action tables for independent control by distinct tenants. As a result, we become able to accommodate multiple switch pipelines running in parallel. One key advantage of this model is that any switch bytecode for the target architecture could be deployed on top of the switch hypervisor, regardless of its internal switching pipeline. It means, for example, that one could write a switch using P4 (BOSSHART et al., 2014), and deploy it in parallel to another switch written in POF (SONG, 2013a). Even a switch written in Hardware Description Language (HDL) could be deployed in the hypervisor, as long as it follows the Reconfigurable Match-action Tables (RMT) (BOSSHART et al., 2013) architecture.

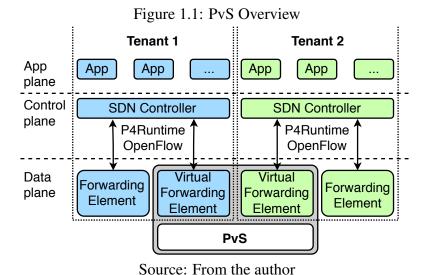

We realize this model in PvS, a system for running *Programmable virtual Switches* in a shared network environment. Figure 1.1 presents an overview of PvS containing two virtual switches from two different tenants. Each virtual switch has its pipeline of matchaction stages, along with separate control channel for secure management. Each tenant in the shared infrastructure can deploy its virtual switch and use the most convenient management interface (e.g., Openflow, P4Runtime, or command-line) for making network apps in the application plane operate it.

#### 1.1 Motivation

There are several motivations for bringing virtualization to the forwarding plane, as exhaustively discussed in prior work (HANCOCK; MERWE, 2016; ZHANG et al., 2019; KRUDE et al., 2019): networking slicing, multi-tenancy in private and public clouds, switch debugging, snapshotting, stateful switch migration, etc. Next we discuss some potential use cases.

**Network slicing.** Resource slicing is one main motivation for virtualization, and *per se* justifies the need for virtualization of programmable forwarding planes (AFOLABI et al., 2018). Consider for example the roll-out of novel communication technologies like 5G. In order to reduce risks with huge capital expenditure, telecommunication companies might opt to hire slices of radio-base stations (CABALLERO et al., 2017) on a pay-asyou-go basis. The radio-base service provider would need to offer not only the abstraction of a virtual radio-base station, but also abstractions of the networking hardware substrate – including programmable virtual switches – required for data communication between the provider and the telecom company network. A programmable virtual switch would make it easier to interface the provider network with that of the telecom company.

Multi-tenancy in cloud infrastructures. The deployment of a virtual networking infrastructure requires not only abstractions of servers and network functions, but also forwarding devices that will interconnect the virtual infrastructure. The use of software switches to materialize virtual forwarding devices might impose in some cases a performance penalty that violates defined service level objectives. An approach to overcome the performance penalty due to software switching is running programmable switches directly on a hypervisor that offers strict performance guarantees. A public cloud could even offer the notion of a "programmable switch as a service" (KRUDE et al., 2019), which could serve for interconnecting networks from different domains or running in various public cloud infrastructures.

**Switch profiling and debugging.** A network operator might want to evaluate a home-brewed switch in a semi-experimental scenario, using production workloads. A programmable switch hypervisor would enable that operator to instantiate a virtual switch, and steer (part of) the production traffic to it. The operator could run, for example, A/B acceptance testing, in which the performance of the home-brewed switch is compared with that of the production switch. The operator could also take advantage of such scenario to inspect switches for security vulnerabilities, for example, by replicating input traffic to

independently developed switch instances and comparing output packets.

Switch snapshotting and migration. A switch hypervisor, having privileged access to the virtual switch memory, could snapshot the switch state and configured set of match-action table entries. The network operator could then create a catalog of switch configurations, and quickly deploy virtual switch instances capable of handling network flows during peak and off-peak hours, for example. Switch snapshotting could also be useful in scenarios in which a switch must be migrated, along with its state and table configurations, for handling fluctuations in network traffic demands, just like any virtual network function migration (GEMBER-JACOBSON et al., 2014) as seen in the context of Network Function Virtualization (NFV).

#### 1.2 Contributions

This work presents PvS, discussing the approaches adopted to conceive a hypervisor capable of running multiple programmable virtual switches in a single hardware substrate with operation performance comparable to a single switch running as standalone. However, the main focus of this dissertation is the PvS's forwarding engine architecture, exposing its design, implementation, and supporting features. The main finding with this architecture is that it is possible to run virtual switch instances directly from switch bytecode while ensuring predictable performance and isolation. It does so by slicing physical switch resources into multiple pipelines and control. As a direct implication of this finding, we make the following contributions:

- The design and implementation of PvS's forwarding engine: Provides a virtual switch operation performance comparable to that of a single switch running as standalone directly on top of the physical programmable switch hardware. To achieve this goal, specific modules were designed and implemented to promote fair and efficient allocation of physical switch resources to virtual instances, in order to maximize the number of instances that can run in parallel, and prevent running instances interfere in the performance of each other;

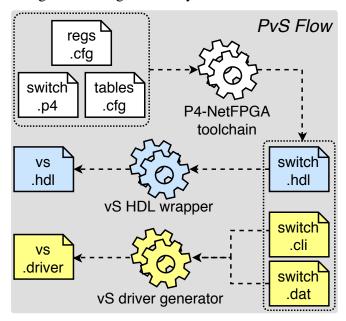

- **High-Level Synthesis (HLS) flow to virtual switch bytecode:** Enables deployment of a switch bytecode in a Field-Programmable Gate Arrays (FPGAs) board from a program code written in any Domain Specific Language (DSL) for programmable forwarding planes, like POF and P4. A framework to run the HLS flow

was developed, allowing generation and deployment of virtual switches described in P4. The proposed flow facilitates the development of virtualized switches with features to simulate and manage multiple switches in the hypervisor. Code changes are not necessary, which provides protection to the Intelectual Property (IP) and enables the support of the same switch bytecode compiled for the target without the hypervisor;

- The proposal of a methodology for switch reconfiguration for FPGA architectures: Enable virtual switch hot-swapping. In other words, a tenant should be able to (un)deploy switch bytecode from/to a programmable virtual switch assigned to that tenant. A methodology was developed to run partial and full FPGA reconfiguration. The partial reconfiguration provides a structure to replace virtual switches without affecting other running virtual switches, while the full methodology delivers the best optimization in terms of resource utilization and performance. Each approach has an optimal utilization case that can be explored to better adapt PvS to different scenarios;

- A public, open-source, implementation of PvS on GitHub<sup>1</sup>: PvS was built as a fork of the canonical NetFPGA reference design (IBANEZ et al., 2019). This repository contains the forwarding engine modules, the HLS program to build P4-based virtual switches, the supporting library to test virtual switches execution, examples of different virtual switches implementations, a demo to run the full and partial reconfiguration methodology, and tutorials to enable network operators to use our proposed architecture.

#### 1.3 Outline

The rest of this dissertation is organized as follows. Chapter 2 presents the background knowledge, including basics concepts of domain-specific languages, virtualization, and FPGAs. Also, it overviews switch program emulation, composition, and other reference architectures. Chapter 3 describes PvS, exposing the design principles and the system overview. Chapter 4 details the forwarding engine design and implementation with the modules that support switch virtualization. Chapter 5 describes the proposed HLS flow able to generate virtual switches from P4 descriptions. Chapter 6 explains our

<sup>&</sup>lt;sup>1</sup>PvS forwarding engine slicing GitHub repo: <a href="https://github.com/pvs-sigcomm/">https://github.com/pvs-sigcomm/</a>

pvs-forwarding-engine>

reconfiguration methodology with pros and cons of using full or partial reconfiguration. Chapter 7 discusses our evaluation in terms of resource usage and performance, measuring reconfiguration times and the impact of virtual switches management, and discussing the in-band telemetry case-study. Finally, Chapter 8 draws the final remarks and possible future works that can be done over the presented forwarding engine and features.

#### 2 BACKGROUND AND STATE OF THE ART

This Chapter discusses background on topics that are fundamental to understanding the work presented in this work, including DSLs, virtualization, Protocol Independent Switch Architecture (PISA), FPGA architectures, and related work addressing switch virtualization.

## 2.1 Domain-Specific Language (DSL)

A Domain-Specific Language (DSL) is a computer programming language of limited expressiveness focused on a particular domain. There are four key elements to this definition: *Computer programming language*: A DSL is used by humans to instruct a computer to do something. As with any modern programming language, its structure is designed to make it easy for humans to understand, but it should still be something executable by a computer. *Language nature*: A DSL is a programming language, and as such should have a sense of fluency where the expressiveness comes not just from individual expressions but also from the way they can be composed together. *Limited expressiveness*: A general-purpose programming language provides lots of capabilities: supporting varied data, control, and abstraction structures. All of this is useful but makes it harder to learn and use. A DSL supports a bare minimum of features needed to support its domain. You can not build an entire software system in a DSL; rather, you use a DSL for one particular aspect of a system. *Domain focus*: A limited language is only useful if it has a clear focus on a small domain. The domain focus is what makes a limited language worthwhile (FOWLER, 2010).

The adoption of a DSL involves pros and cons, working with this approach means finding the balance between these two. The benefits of DSLs include: DSLs allow solutions to be expressed in the idiom and at the level of abstraction of the problem domain. Consequently, domain experts themselves can understand, validate, modify, and often even develop DSL programs (DEURSEN; KLINT; VISSER, 2000); Programs are concise, self-documenting to a large extent, and can be reused for different purposes (LADD; RAMMING, 1994); DSLs enhance productivity, reliability, maintainability (KIEBURTZ et al., 1996); Allow validation and optimization at the domain level (BRUCE, 1997); DSLs improve testability following approaches such as (SIRER; BERSHAD, 1999); Still according to Deursen, Klint e Visser (2000), the disadvantages of the use of a DSL are:

The costs of designing, implementing and maintaining a DSL; The costs of education for DSL users; The difficulty of finding the proper scope for a DSL; The difficulty of balancing between domain-specificity and general-purpose programming language constructs; The potential loss of efficiency when compared with hand-coded software; And according Krueger (1992), the limited availability of DSLs;

Operators can use domain-specific languages to effectively program network behavior, from control plane applications to forwarding devices. In the following sections, we describe two prominent DSLs that enable data plane programmability: POF (SONG, 2013b) and P4 (BOSSHART et al., 2014). POF is designed to inter-operate with Open-Flow (MCKEOWN et al., 2008a) and enable greater flexibility in packet processing definition, whereas P4 provides higher-level abstractions to define protocol headers, header parsing logic and packet to achieve the same main goal as POF. Although there are other DSLs that enable data plane programmability, P4 and POF are the only that are recognized by the Open Networking Foundation<sup>1</sup> (ONF), responsible for fostering open networking standards.

#### 2.1.1 Protocol-Oblivious Forwarding (POF)

As one of the initial implementations of Software-Defined Networking (SDN), OpenFlow provides a powerful tool set for network operators to program and manage their networks adaptively (MCKEOWN et al., 2008b). However, its protocol-dependent nature still limits the programmability of the forwarding plane. Specifically, OpenFlow defines the matching fields in flow tables according to existing network protocols (e.g., Ethernet and Internet Protocol). Therefore, OpenFlow switches need to understand the protocol headers to parse packets and perform flow matching, which may cause serious compatibility issues when new protocols try to add or remove header fields. Hence, it is desirable that the network programmability can be further enhanced such that the forwarding plane is protocol-independent and can be dynamically reprogrammed to support new protocol stacks seamlessly. Following this idea, Protocol-Oblivious Forwarding (POF) was proposed, a new SDN technologies to try to decouple network protocols from packet forwarding and make the forwarding plane reconfigurable, programmable, and future-proof (LI et al., 2017).

More specifically, POF is an OpenFlow extension that introduces a protocol-inde-

<sup>&</sup>lt;sup>1</sup>https://www.opennetworking.org/

pendent instruction set, which allows a network operator to define the protocol stack and packet processing procedure in a much more flexible manner than that in the current OpenFlow specifications. This extension is designed to enable rules to reference arbitrary packet header fields and to control the table matching behavior. Header fields are referenced within table entries in POF using type, offset, length tuples, where type is set to 0 to indicate a header field or 1 to indicate a meta-data field. Meta-data fields may contain arbitrary data and serve the purpose of carrying packet information through the processing pipeline. The offset is the field starting position relative to the first bit of the header. The field length is specified in bits (SONG, 2013b).

Using POF to support new protocols, the operators need to download some flow rules with associated instructions into the network elements. This instruction set is named POF-FIS. POF-FIS is an enhancement and extension of the instructions and actions defined in OpenFlow 1.x. In the POF network element, network flows are handled by flow instructions in the form of POF Flow Instruction Blocks (POF-FIB). POF-FIBs are deployed by a controller through the POF southbound interface. All the flow instructions in POF-FIBs are defined in POF-FIS. The POF controller can use a Command-Line Interface (CLI), a Graphical User Interface (GUI), or a high-level programming language compiler as the northbound interfaces to users and applications (YU et al., 2014).

The packet parsing process is done through table redirection and specially defined decision tables. These tables match on header fields that indicate the next protocol type, for example, Ethernet *EtherType*, and their entries are populated to redirect the packet parsing appropriately. For example, suppose two decision tables dedicated to Internet Protocol version 4 (IPv4) and Internet Protocol version 6 (IPv6) routing, respectively. A third table could be defined to match the Ethernet *EtherType* field, and populated with two entries. One of them would have a matching value of 0x0800, and redirect the packet parsing, via Goto-Table instruction, to the IPv4 table. The other entry would have a matching value of 0x86DD, and redirect the parsing to the IPv6 table. The packet parsing is thus analogous to OpenFlow, but with the ability to match and modify arbitrary header fields (CORDEIRO; MARQUES; GASPARY, 2017).

# 2.1.2 Programming Protocol-Independent Packet Processors (P4)

Programming Protocol-Independent Packet Processors (P4) is a high-level language that provides an abstract model suitable for programming the network data plane

with the definition of its behavior (BOSSHART et al., 2014). Its main aspect goals are reconfigurability, protocol independence, and target independence. The reconfigurability proposes that packet parsing and processing may be redefined by the controller. The protocol independence suggests that the controller should be able to extract header fields by specifying the packet parser and a collection of header processing match-action tables. The target independence focuses on not getting irrelevant information about the switch.

A P4 program defines essentially six items: (i) headers, specify the names and width of the protocol fields which the program operates on; (ii) metadata, structures that provide specific information of the packet; (iii) parser, group of state machines to analyze headers and extract data for the metadata structures; (iv) match-action table, identifying packets fields and metadata that will be compared and the possible actions being executed in response; (v) execution pipeline, stage actions, determined control flow, to define how packets are processed; (vi) deparser, process to rebuild packets.

The task flow of the device definition with capacity for P4 starts with the operators writing and compiling a P4 program through a front-end compiler in a High-Level Intermediate Representation (HLIR). Then, a back-end compiler will adapt the program to different targets, including FPGAs. Finally, through an execution time controller, operators can fill entries in match-action tables in the data plane and make destination devices process packets like they are preset.

The main difference between these two DSLs is that POF is an extension of Open-Flow, and P4 is a protocol-independent language created to describe how the packets are processed. While POF is a more direct evolution of OpenFlow, designed to inter-operate with it and enable greater flexibility in packet processing definition, P4 provides higher-level abstractions to define protocol headers, header parsing logic, and packet processing. Both have the same main goal, to make the data plane programmable and reconfigurable.

#### 2.2 Virtualization

The work presented in (ANDERSON et al., 2005) conceptualizes virtualization as nothing more than a high-level abstraction that hides the underlying implementation details, for example, as used in virtual memory, virtual machines, and elsewhere. With virtualization, nodes can treat an overlay as if it is the native network, and multiple overlays can simultaneously use the same underlying infrastructure.

The application of virtualization has become common in modern public and pri-

vate clouds, powering virtual abstractions for servers. The high costs involved in the acquisition and maintenance of servers have caused the migration of local servers to remotely accessed virtualized servers. In the past fifteen years, server virtualization has become the dominant approach for managing computational infrastructures, with the number of virtual servers exceeding the number of physical servers globally (BITTMAN et al., 2013; KOPONEN et al., 2014). This approach shares resources to deliver a multi-tenant scheme, in which a user receives an individual software abstraction to run its processes.

The idea of a Virtual Internet (VI) presented by (TOUCH et al., 2003) is a network composed of tunneled links among a set of virtual routers and virtual hosts. The architecture provides an abstraction that hides the complexity of the underlying network and provides isolation-based protection that encourages resource sharing. The network virtualization completely decouples its component hosts and routers from the underlying network to support recursive VIs and to allow a node to participate multiple times in a single overlay, known as re-visitation. This architecture provides a consistent multihoming paradigm, including end-to-end overlays, naming and addressing, virtual host requirements, and virtual gateway requirements.

Network Function Virtualization (NFV) has been recently proposed to turn middle-boxes into software-based, virtualized entities (MARTINS et al., 2014; HWANG; RA-MAKRISHNAN; WOOD, 2015); provide high performance and flexible networking using virtualization on commodity platforms (HWANG; RAMAKRISHNAN; WOOD, 2015) and reconfigurable hardware (LI et al., 2016); and the comprehensive survey of network function virtualization (YI et al., 2018). These virtual abstractions are highly convenient, it provides virtualization, isolation and non-interrupted execution of network functions.

Resource sharing through virtualization in forwarding devices take the VI concept closer to reality. The research community has been proposing solutions to decouple hosts and routers from the underlying network. In the work of the authors DOBRESCU et al. is presented a software router architecture to parallelize router functionality across multiple cores within a single server. Different approaches using SDN hypervisor architectures, centralized and distributed also are presented to run on general-purpose computing platforms with special-purpose network elements (SHERWOOD et al., 2009). Forwarding systems with predictable performance have been proposed in the literature and are able to share resources efficiently, while rapidly reacting to ensure isolation in public and private clouds (KUMAR et al., 2019).

This work advocates in favor of network virtualization with the ability to run vir-

tual instances of routers, switches, links, and network functions on top of a physical network substrate. In addition to enabling experimentation with novel network architectures, this virtual networking also promotes the sharing of physical resources, powering a whole new class of networking-on-demand services.

# 2.3 Protocol Independent Switch Architecture (PISA)

Programmable switches enable the implementation of many complex network functions directly in the data plane. The Protocol Independent Switch Architecture (PISA) proposes the Reconfigurable Match Tables (RMT) model, a Reduced Instruction Set Computer (RISC) inspired pipelined architecture for switching chips, through the identification of the essential minimal set of action primitives to specify how headers are processed in hardware. RMT allows the forwarding plane to be changed on-the-fly without modifying the hardware. As in OpenFlow, the programmer can specify multiple match tables of arbitrary width and depth, subject only to an overall resource limit, with each table configurable for matching on arbitrary fields. (BOSSHART et al., 2013).

The PISA architecture consists of a large number of physical pipeline stages that a smaller number of logical RMT stages can be mapped to, depending on the resource needs of each logical stage. After entering a PISA switch, packets first go through an ingress pipeline, then enter the traffic manager that maintains multiple queues, and are finally processed by an egress pipeline (POKORNY et al., 2008).

Ingress Buffer Egress

Figure 2.1: The Basic PISA Pipeline

Source: Programming The Network Data Plane (KIM, 2017)

Figure 2.1 shows the processing pipeline stages in more detail. Note that there are three fundamental elements, the Ingress match-action, Buffer, and the Egress match-action. The Ingress and Egress match-action stages are composed of memory-implemented modules, such as lookup tables, counters, meters, and generic hash tables; and processing modules, such as standard boolean and arithmetic operations, header modification opera-

tions, hashing operations, etc. The packets are recirculated through these stages up until the processing is complete.

The implementation of the PISA is frequently prototyped in Application Specific Integrated Circuits (ASIC) - i.e. Barefoot Tofino ASIC (BAREFOOT, 2019). The ASIC provide their users the ability to manufacture products having a proprietary design without having to begin the design at the device level (CHAN; BIRKNER; CHUA, 1992). The main language used to program these devices is P4, that allows developers to describe how packets are processed by a programmable data plane, spanning ASICs and processors, implementing PISA (LUINAUD et al., 2020). However, the hardware implementation is non-trivial and imposes constraints on the number of bytes that can be examined in the packet header and on the number of match-action stages in a pipeline (JEPSEN et al., 2019).

# 2.4 Field-Programmable Gate Arrays (FPGA)

The use of hardware-accelerated network devices in switches and routers are enabling a rapid growth of the Internet. Today, gigabit ethernet switches are widely deployed to switch traffic within Local Area Networks (LAN) and route Internet Protocol packets across Wide Area Networks (WANs). Commercial vendors use ASICs and/or FPGAs to accelerate switching, routing, and processing of network data (LOCKWOOD et al., 2007). As elucidated in the previous sections, the newer generation of SDN-related solutions introduced the notion of data plane programmability - e.g., P4 and POF. They enable faster development/provisioning of novel and/or home-brewed protocols, as opposed to the long wait for the release of fixed-function ASIC switches supporting standardized protocols (SIVARAMAN et al., 2015). The intrinsic characteristics of Field-Programmable Gate Arrays (FPGAs) are aligned with the data plane programmability which can be a powerfully tool to network developers make the forwarding plane reconfigurable, programmable, and future-proof.

More specifically, the FPGAs are pre-fabricated silicon devices that can be electrically programmed to become almost any kind of digital circuit or system (KUON et al., 2008). They provide a number of compelling advantages over fixed-function ASICs, such as standard cells (CHINNERY; KEUTZER, 2002): ASICs typically take months to fabricate and cost hundreds of thousands to millions of dollars to obtain the first device; FPGAs are configured in less than a second (and can often be reconfigured if a mistake is

made) and cost anywhere from a few dollars to a few thousand dollars.

The flexible nature of FPGA comes at a significant cost in area, delay, and power consumption: an FPGA requires approximately 20 to 35 times more area than a standard cell ASIC, has a speed performance roughly 3 to 4 times slower than an ASIC, and consumes roughly 10 times as much dynamic power (KUON; ROSE, 2007). These disadvantages arise largely from an FPGA's programmable routing fabric that trades area, speed, and power for "instant" fabrication.

To create the circuit to be loaded into a FPGA board, a designer traditionally describes the circuit using Hardware Description Languages (HDL). HDLs describe the behavior of physical devices and processes, a task commonly called modeling. Models written in HDL are used as input to a suitable simulator to analyze the behavior of the devices before the design implementation (CHRISTEN; BAKALAR, 1999). Verilog and VHDL are hardware description languages that provide means of specifying a digital system at a wide range of levels of abstraction. Both languages support the early conceptual stages of design with its behavioral level of abstraction, and the later implementation stages with its structural level of abstraction. The hierarchical modeling of the system can be achieved with top-down and bottom-up design methodologies, and the system and its subsystems can be described at any level of abstraction ranging from the architecture level to gate level (BHASKER, 1999; THOMAS; MOORBY, 2008).

COUT COUT

CLB

Slice(1)

Switch

Matrix

Slice(0)

CIN

UG474\_cr\_01\_01\_071910

Figure 2.2: Arrangement of Slices within the CLB of the FPGA Xilinx Virtex 7

Source: Xilinx 7-Series Manual (XILINX, 2018)

The FPGA fabric is composed by fundamental building block named Configurable Logic Blocks (CLBs) that provide the physical support for an implemented and down-

loaded design. The CLB is the FPGA's main logic resource for implementing combinatorial and sequential logic functions. Each CLB is connected to the general routing fabric through a switch matrix (CHANDRAKAR; GAITONDE; BAUER, 2015). The Figure 2.2 shows how the arrangement of slices form the CLB structure of the Xilinx Virtex 7, the FPGA embedded in this work's target board. The slice is built from Basic Elements of Logic (BELs) such as Look up Tables (LUTs), flip-flops, carry logic, and wide-function multiplexers (XILINX, 2018).

The configuration data of a FPGA is stored in a file called bitstream (.bit), which defines the FPGA's logic functions and circuit connections. This configuration remains active in the FPGA until it is erased or overwritten. For the NetFPGA SUME board, erasing can be accomplished by resetting the board and overwriting can be accomplished by writing a new configuration file to the Joint Test Action Group (JTAG) port or by triggering the on-board Complex Programmable Logic Device (CPLD) to load a new bitstream from the parallel flash memory (Digilent Inc., Accessed: July 2019).

The use of FPGAs allows us not only to rapidly prototype PvS, but also to take advantage of its flexibility, high performance, and module reconfiguration. The main difference in the use of FPGAs, when compared to the use of microprocessors, is the ability to make substantial changes to the hardware, including modifications to the data and control flows (YANG et al., 2014), in addition of better efficiency in terms of performance and power consumption, since it implements a dedicated circuit. When compared to using a custom ASIC, the advantage of using FPGAs is the possibility of changing the hardware at run time by loading a different circuit in the reconfigurable matrix.

#### 2.5 Related Work

This work posit that a data plane hypervisor must allow network operators to deploy and hot-swap truly independent virtual P4-based switch instances, deliver a performance similar as if the virtual instances were running directly on hardware, and allow vendors to distribute switch byte-code while protecting their intellectual property. Although previous investigations partially fulfill some of these requirements, satisfying them simultaneously poses the following research challenges: (i) decouple virtual switch instances from the virtualization environment, (ii) provide network flow isolation, (iii) ensure hardware resource isolation, (iv) support virtual networking within the hypervisor, and (v) deliver an implementation with feasible performance and memory footprint. In

the following section, we discuss the state-of-the-art related works to elucidate our proposed approach.

### 2.5.1 Switch Program Emulation

Hancock and van der Merwe (HANCOCK; MERWE, 2016) were the first to propose the idea of a general purpose P4 switch program (called Hyper4) that exposes a set of match-action tables that can be configured in a way to emulate other P4 programs. The Hyper4 compiler is responsible for parsing switch programs and generating the necessary Hyper4 match-action table entries required to emulate them. Hyper4 makes extensive use of P4 packet recirculate primitive, which imposes high performance penalty to emulated switches. Zhang et al. (ZHANG et al., 2017; ZHANG et al., 2019) followed with HyperVDP, a solution that also emulates multiple P4 program switches using a single general purpose program. Similarly to Hyper4, HyperVDP also suffers from performance penalty due to emulation. In addition, both require several match-action stages to emulate a single match-action stage, thereby incurring in high memory footprint.

SR-PVX (LI et al., 2017) follows a similar approach to Hyper4, but focuses on POF (SONG, 2013a). SR-PVX enables instantiating virtual POF switches over designated substrate switches, and uses source routing to realize virtual links in virtual SDN slicing. The deployment flow of virtual switches involves (i) deployment of tenant-defined flow-table(s) in the substrate switch pipeline, and (ii) configuration of match tables in the substrate switch so that packets belonging to a specific SDN are processed by the corresponding tenant-defined flow-tables. In a follow-up work PVFlow (LI et al., 2018), the authors unify flow-tables that contain arbitrary matching fields with various lengths, enabling them to share the Ternary Content Addressable Memory (TCAM) of a matching stage in a substrate switch.

### 2.5.2 Switch Program Composition and Parallel Execution

P4Visor (ZHENG; BENSON; HU, 2018), Dejavu (WU et al., 2019), and P4SC (CHEN et al., 2019) are solutions that compose multiple switch codes into a single program, and that optimize resource usage through merging of similar switch program functionalities. The composed programs can then be configured in a way that emulates various

switch functions running in the substrate switch. However, they do not support switch isolation and interruption-free deployment of new switch instances.

Krude et al. (KRUDE et al., 2019) discussed research avenues towards providing *Programmable Switches as a Service*, including switch hot-pluggability in the data plane, which have been partially addressed in prior work like P4Visor (ZHENG; BENSON; HU, 2018), VirtP4 (SAQUETTI et al., 2019), and P4VBox (Saquetti et al., 2020). VirtP4 (SAQUETTI et al., 2019) and P4VBox (Saquetti et al., 2020) propose running multiple switch instances on a NetFPGA board, but lack management abstractions for controlling virtual switch instances. In our work, we show how the architectural requirements discussed in (KRUDE et al., 2019) are realized to deliver a hypervisor for programmable virtual switches running on a NetFPGA board.

#### 2.5.3 Software Switches

PISCES (SHAHBAZ et al., 2016) follows a best-of-breed approach for enabling customization of software switches through a high-level domain-specific language for programming packet parsing and processing logic. Derived from Open vSwitch (PFAFF et al., 2015), it provides a protocol-independent virtual switch whose behavior can be modified at will. Although multiple software switch instances could run in parallel, it is unclear whether each virtual switch instance would perform under intense competition for shared resources like CPU and physical switch ports. Still, such approach would require a supervisor program to steer packets between virtual switch instances and ensure network isolation.

## 2.5.4 Canonical NetFPGA Reference Design Architecture

The canonical NetFPGA design is based on the Simple Sume Switch (SSS) architecture, which supports a single switch description, its structure is showed in Figure 2.3. It consists of four 10Gbps and DMA I/O ports, Input Arbiter (IA), Output Port Lookup (OPL), and BRAM Output Queues(BOQ). The IA is responsible for serializing the packet frames received from the input ports and delivering them to the OPL module. The OPL is a placeholder to accommodate an implementation of an independent P4-based switch pipeline, which performs packet processing and determines the output port. The BOQ

buffers packets before they are copied to the output ports. The Control enables system monitoring and configuration.

10GMAC 10GMAC 10GMAC 10GMAC DMA RX 0 RX 1 RX 2 RX3 RX Control MicroBlaze UART Input Arbiter AXI MDIO Interconnect Output Port Lookup DMA/AXI4 Configuration Lite Master **BRAM Output** Queues

Figure 2.3: Canonical NetFPGA reference design Data Path

Source: From the author

$\mathsf{DMA}$

10GMAC

TX 3

10GMAC

10GMAC

TX 0

10GMAC

Table 2.1 describes the format of the SSS's *sume\_metadata* bus and the functionality of each field. The architecture could also be extended by more advanced users, or, for the most adventurous users, it could be completely replaced by writing a new architectural model (IBANEZ et al., 2019).

Table 2.1: Simple Sume Switch sume metadata Fields Description

| Field Name      | Ciga (hita) | Description                                                                              |

|-----------------|-------------|------------------------------------------------------------------------------------------|

| Field Name      | Size (bits) | Description                                                                              |

| pkt_len         | 16          | Size of the packet in bytes (not including the Ethernet preamble or FCS)                 |

| src_port        | 8           | Port on which the packet arrived (one-hot encoded)                                       |

| dst_port        | 8           | Set by the P4 program - which port(s) the packet should be sent out of (one-hot encoded) |

| send_dig_to_cpu | 8           | Set the least significant bit of this field to send the digest_data to the CPU           |

| *_q_size        | 16          | Size of each output queue at P4 processing start time, measured in of 32-byte words      |

Source: (IBANEZ et al., 2019)

For generating a switch implementation from a P4 description, the P4-NetFPGA uses a HLS methodology applied to a SSS architecture creating an OPL. The SSS is similar to the Very Simple Switch (VSS) reference model and supports switch logic composed of a single packet parser, match-action pipeline, and packet deparser.

# **2.5.5 Summary**

Most prior work have focused on *emulating* programmable switch pipelines through a single switch program, or *composing* several switch functions into a single program (see Table 2.2). Observe that prior work on virtualization of the forwarding plane lack mechanisms for ensuring predictable performance and tenant isolation. A common approach for virtualization has been using switch program composition, for example, through a merged packet parser and a set of match-action tables for emulating multiple pipelines.

Table 2.2: Existing work on virtualization of forwarding elements.

| Solution                          | Underlying hypervisor | Abstraction Model Target DSL Co |                | Compilation / Merging |             |

|-----------------------------------|-----------------------|---------------------------------|----------------|-----------------------|-------------|

| Hyper4 (HANCOCK; MERWE, 2016)     | Software switch       | Virtual switch                  | Emulation      | P4                    | Compilation |

| HyperVDP (ZHANG et al., 2019)     | Software switch       | Virtual switch                  | Emulation      | P4                    | Compilation |

| P4Visor (ZHENG; BENSON; HU, 2018) | Single switch program | Switch function                 | Emulation      | P4                    | Merging     |

| Dejavu (WU et al., 2019)          | Single switch program | Switch function                 | Emulation      | P4                    | Merging     |

| P4SC (CHEN et al., 2019)          | Single switch program | Switch function                 | Emulation      | P4                    | Merging     |

| SR-PVX (LI et al., 2017)          | Single switch program | Virtual switch                  | Emulation      | POF                   | Compilation |

| PV-Flow (LI et al., 2018)         | Single switch program | Virtual switch                  | Emulation      | POF                   | Compilation |

| PvS                               | Hard virtualization   | Virtual switch                  | Virtualization | Independent           | =           |

Source: From the author

The main drawbacks of these techniques are that: (i) they do not provide true switch isolation, as switch programs are merged into a single one, and therefore share physical resources, (ii) any modification to a switch program requires full recompilation, (iii) updating a single switch program requires full system halt, (iv) incur in performance degradation in terms of increased latency a decreased bandwidth, or (v) not provide a virtualization features.

### **3 PVS PROPOSAL**

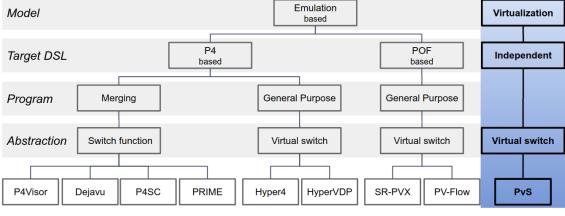

This Chapter presents an overview of PvS, a new solution of virtualization for programmable data planes that aims to fill the existing virtualization gap in the literature, as depicted in Figure 3.1. This system provides true virtualization running multiple pipelines of programmable virtual switches on top of the same hardware platform, providing performance comparable as a single switch running as standalone. The support to multiple DSLs allows the co-existence with legacy solutions and is capable of making the network infrastructure more extensible and reusable, while the hot-swapping process enables the easy (un)deploy of new virtual switches to do debugging or migration without interfering in the already running pipelines. In Section 3.1, we describe the design principles that a hypervisor should satisfy, which guided the PvS implementation, whereas Section 3.2 provides a PvS overview and define the main properties to programmable switch abstraction.

Figure 3.1: PvS proposal in the literature

Source: From the author

## 3.1 Design Principles

As a general goal, any hypervisor for the data plane should offer the network developer an abstraction of a programmable virtual switch. In other words, the hypervisor should enable the network developer to program a virtual switch placeholder as if the physical switch hardware itself were being programmed.

As a direct consequence of the goal above, any suitable hypervisor for the data plane should offer the following set of features:

- Promote fair and efficient allocation of physical switch resources to virtual instances, in order to maximize the number of instances that can run in parallel, and prevent running instances interfere in the performance of each other (Chapter 4);

- Provide virtual networking between virtual switch instances, enabling them to exchange flows between each other. This is the case for virtual networking within the hypervisor, a useful feature in a scenario where multiple switch instances belong to a same tenant, and are part of a same domain (Chapter 4).

- Ensure that virtual switch instances do not process network flows or read/write memory blocks or virtual ports beyond their control, e.g., from other virtual switches running in parallel. Such feature is essential for ensuring that a malicious virtual switch does not tamper with other running instances (Chapter 4 and 5);

- Enable the deployment of a switch bytecode compiled from a program written in any Domain Specific Language (DSL) for programmable forwarding planes, like POF and P4 (Chapter 5);

- Support the same switch bytecode compiled for the target it is running on. For example, if the hypervisor is running on NetFPGA, then it should run virtual switch instances from a switch bytecode compiled for a NetFPGA target (Chapter 5);

- Enable virtual switch hot-swapping. In other words, a tenant should be able to (un)deploy switch bytecode from/to a programmable virtual switch assigned to that tenant (Chapter 6);

- Provide a virtual switch operation performance comparable to that of a single switch running standalone directly on top of the physical programmable switch hardware (Chapter 7);

- Ensure that network apps running in the SDN application plane only gain any access to virtual switches if they provide valid access credentials. Such feature is critical for ensuring secure operation of virtual switch instances and tampering from a malicious tenant.

In addition to these features, the deployment of a virtual switch instance must not require access to switch source code or custom switch program compilation. Such feature is important for protecting the intellectual property of switch developers and vendors. In contrast, prior work require custom compilation or switch program composition for running it as a virtual switch instance.

To satisfy these features, we propose the following design principles for a pro-

grammable forwarding plane virtualization solution:

- P1 Forwarding engine slicing. For predictable performance and tenant isolation, physical switch resources should be sliced proportionally to the desired performance, and committed to virtual switch placeholders. In particular, resources like memory space for holding the switch bytecode, match-action table entries, and counters, as well as packet queues and buffers, should be allocated per deployed switch instance, to ensure their feasible operation.

- P2 *Control engine abstraction*. For ensuring secure management and compatibility with open control-data plane interfaces, the hypervisor should offer an abstraction of a single control engine and management channel to network apps running in the application plane.

The forwarding engine slicing (P1) enables accommodating virtual switch instances with predictable performance with regard to packet processing capabilities, and known storage capacity for handling match-action table entries and packet counters. In turn, the use of slicing requires accessory modules for ensuring that (i) incoming packets are steered to correct virtual switch instances, (ii) output packets are forwarded to the correct physical switch ports, and (iii) match-action table entry and register reading/writing operations do not overflow. More importantly, such modules should provide virtual port and ingress/egress buffer and queue abstractions for virtual switch placeholders, so that these placeholders can accommodate the same switch bytecode one would deploy directly on the physical switch. While P1 is necessary for predictable performance and enforce secure virtual switch operation at the forwarding engine, it does not cover control to data plane management channels, neither is capable of enforcing secure virtual switch management.

The control engine abstraction (P2) provides a proper abstraction of a virtual switch control engine and satisfies the last mentioned design principle. Such abstraction should intercept message requests sent through the control channel, and ensure that they are accepted and processed by the virtual switch only if proper credentials are supplied beforehand. It should also ensure that tenants do not perform read/write requests to match-action table entries and counters beyond their control. Observe also that regardless of the control engine abstraction used, the hypervisor must ensure that it is not reprogrammed by a malicious tenant so that these security properties are subverted, and a malicious tenant becomes able to access restricted memory regions in the forwarding

engine.

In this dissertation, we focus on the PvS Fowarding Engine, a programmable forwarding plane hypervisor that implements the forwarding engine slicing (P1) and all-but-the-last design principles. It enables compiled switch bytecode to run as virtual switch instances, with a performance comparable to what would be achieved if the switch bytecode were running directly on the physical programmable switch hardware. With the use of this virtualization system, we can have, for example, a layer-2 switch, a simple router, a firewall switch, and an in-band telemetry running on top of PvS. The control engine abstraction (P2), which satisfies the last design principle, is left out of the scope of this dissertation.

# 3.2 PvS: Programmable virtual Switch Hypervisor for the Data Plane

The PvS design is guided by the notion that a hypervisor for programmable forwarding planes should offer to network developers a proper abstraction of programmable virtual switches. Under such notion, and considering a scenario in which the hypervisor runs on top of a NetFPGA board, then the hypervisor should offer to each network developer the illusion of having their own dedicated NetFPGA board – which is, in practice, a slice of resources of the physical NetFPGA board. The hypervisor manager should be able to create as many slices for virtual switches as possible, and network developers should be able to instantiate any switch program on a slice. The operation of virtual switch instances should not interfere on switches running in other slices.

A physical switch may be characterized, for example, by (i) amount of memory available for storing the switch bytecode and table entries, (ii) number of network ports and their speed, (iii) switch throughput capacity, (iii) packet processing capacity per second, (iv) latency, and (v) number of dedicated management interfaces<sup>1</sup>. In this context, we define a programmable switch abstraction along properties like memory capacity, virtual switch ports, and dedicated management interfaces. The goal of PvS, as a programmable switch hypervisor, is supporting such abstractions while ensuring virtual switch performance and isolation.

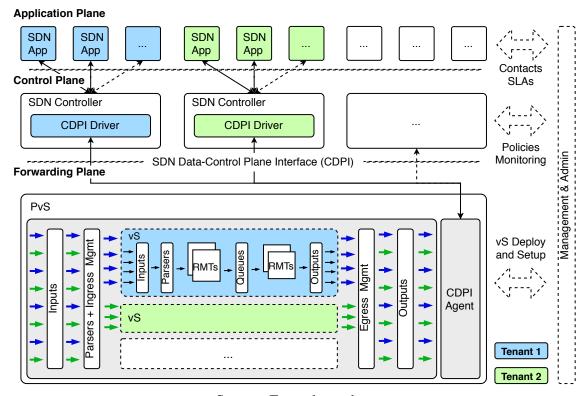

Figure 3.2 provides an overview of PvS, and its relationship with a software-

<sup>&</sup>lt;sup>1</sup>The physical switch characterization discussed in this paper is based on the datasheet of a STORDIS BF2556X-1T Barefoot Tofino-based programmable switch: <a href="https://www.stordis.com/wp-content/uploads/2019/12/STORDIS\_BF2556X-1T-A1F.pdf">https://www.stordis.com/wp-content/uploads/2019/12/STORDIS\_BF2556X-1T-A1F.pdf</a>

Figure 3.2: An overview of a conceptual architecture of a programmable virtual switch hypervisor, and its relationship with key elements that compose a high-level Software Defined Networking (SDN) architecture.

Source: From the author

defined networking architecture. PvS is composed of a *forwarding engine* and a *control engine*. The forwarding engine is responsible for accommodating virtual switch pipelines, whereas the control engine provisions the functionalities of a Control-Data-Plane Interface (CDPI) agent, as discussed in the SDN technical reference specification (FOUNDA-TION, 2013). The CDPI agent enables network applications, belonging to different tenants (colored in the figure for illustration purposes), interact with virtual switch instances through standard management interfaces like OpenFlow and P4Runtime.

## 3.2.1 Memory slicing

The network manager may define the amount of memory allocated to a virtual switch instance either considering the specific memory requirements of the switch bytecode to be deployed, or according to a desired arbitrary amount. The memory space allocated should consider both the required space to store the switch bytecode and the match-action table entries plus counters. The memory region belonging to a virtual switch

instance should be protected from unauthorized access, in order to ensure security and privacy of processed flows.

### 3.2.2 Virtual ports

After entering the physical switch input queue, network flows must be delivered to a virtual switch port. The network manager may define an arbitrary number of virtual ports for each switch instance, and a mapping of physical to virtual ports. The PvS parser and ingress management module is responsible for identifying the tenant associated to an incoming packet, and to which virtual switch pipeline an incoming packet must be steered to (note that a tenant may own multiple virtual switch instances). Such identification must be done based on the input physical port and values matched from the incoming packet header fields. Existing solutions considered custom packet tagging (HANCOCK; MERWE, 2016; ZHANG et al., 2017) to assist that identification; traditional protocols for network segmentation, like VLAN and Virtual Extensible LAN (VXLAN) may also be used to this end.

Once processed by a virtual switch, packet flows must be steered out of the switch (if not marked for drop). Similarly to input port mapping, the network manager must determine the virtual to physical output port mapping. The PvS egress management module is responsible for determining to which physical output port the packet must be copied to. To this end, it considers the virtual switch and port from which the packet is coming from. For ensuring secure packet steering, the egress management module should also check if the packet tag identifier (for example, VLAN/VXLAN id) matches the tenant that owns the virtual switch that forwarded the packet.

## 3.2.3 Management interfaces

The hypervisor must provide open management interfaces to virtual switches, so that they can be easily coupled to a software-defined network substrate. At the same time, the hypervisor must guarantee that the management interface is not subverted so that a malicious tenant gain unauthorized access to virtual switches. For this reason, PvS also implements the control engine abstraction, an abstraction of management channel to tenants, that is materialized through a single Control-Data-Plane Interface (CPDI) agent.

The agent receives requests from the CPDI driver, identifies the virtual switch target of the request, and then process it accordingly. Note that providing a management channel abstraction requires extending management specifications to support tenant authentication.

As previously mentioned, we focus on the forwarding engine slicing (P1) (Chapter 4), its supporting features (Chapter 5), and its reconfiguration capabilities (Chapter 6). Thus, we do not directly address the control engine abstraction (P2), only its interactions with the forwarding engine. The hypervisor seeks to accommodate the switch abstraction properties above, while ensuring that a network developer remains free to devise switch programs according to one's requirements and needs. More importantly, it seeks to deliver optimal memory occupancy per virtual switch instance and negligible overhead, both in terms of flow processing and operational management.

### 4 FORWARDING ENGINE IMPLEMENTATION

This work proposed a forwarding engine architecture for virtualization multiple virtual switch (vS) instances in a single hardware subtract. In typical switch system, only one switch can run on hardware and this system has a specific language supports. To make a target independent platform, this approach enable the portability to any FPGA-based architecture with minor adjustments in the Intellectual Property (IP) library. The real virtualization make the hardware target more flexible and reusable. So its can implement on FPGA cards or any other Verilog supported architecture, for example the 32-Port Programmable Switch from New Wave DV (DV, 2017).

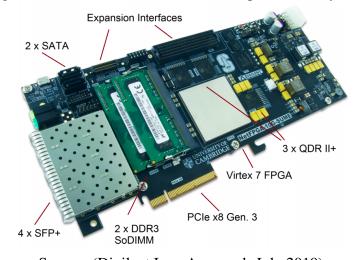

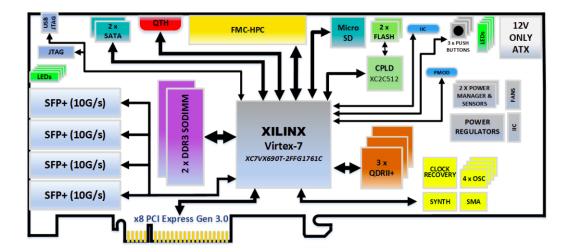

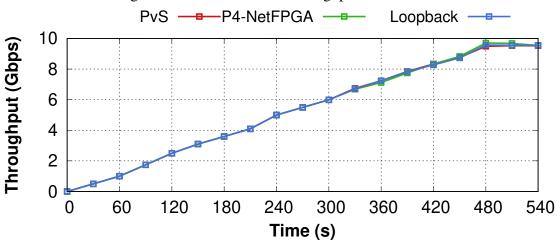

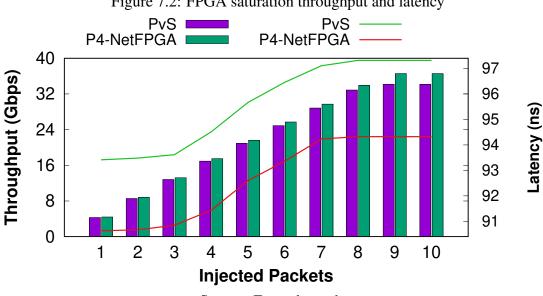

The FPGA-based architecture chosen to target the PvS prototype was the NetF-PGA SUME board. This is an FPGA-based PCI Express board with I/O capabilities for 10 and 100 Gbps operation, an x8 Gen3 PCIe adapter card incorporating Xilinx's FPGA with multiple memory and high-speed expansion interfaces (Digilent Inc., Accessed: July 2019). These attributes make SUME the ideal card for high-performance and high-density networking design.

Figure 4.1: NetFPGA SUME Board Peripherals Subsystems

Source: (Digilent Inc., Accessed: July 2019)

The board is manufactured by Digilent Inc and implemented as a dual slot, full-size PCIe adapter, that can operate as a stand-alone unit outside of a PCIe host presented. This operation mode use a microblaze soft-core processor, e.g. (WOODRUFF et al., 2014) considerable on-chip memory that can serve for onchip cache, the peripheral devices on board as a local RAM of between 8GB and 16GB running at 1866MT/s and two hard drives connected through SATA enable the card to operate as a powerful stand-alone computing unit. The Figure 4.1 show the NetFPGA SUME and expose its peripheral.

The core of the board is powered by Virtex-7 690T FPGA device. There are five peripheral subsystems that complement. A high speed serial interfaces subsystem composed of 30 serial links running at up to 13.1Gb/s. These connect four 10Gb/s SFP Ethernet interfaces, two expansion connectors and a PCIe edge connector directly to the FPGA. The second subsystem, the latest generation 3.0 of PCIe is used to interface between the card and the host device, allowing both register access and packet transfer between the platform and the motherboard. The memory subsystem combines both SRAM and DRAM devices. SRAM memory is devised from three 36-bit QDRII+ devices, running at 500MHz. In contrast, DRAM memory is composed of two 64-bit DDR3 memory modules running at 933MHz (1866MT/s). Storage subsystems of the design permit both a MicroSD card and external disks through two SATA interfaces. Finally, the FPGA configuration subsystem is concerned with use of the FLASH devices. A block diagram of the board is provided in Figure 4.2 (Zilberman et al., 2014).

The documentation support is provided by the NetFPGA project, a collaborative effort between Digilent, Xilinx, the University of Cambridge, and Stanford University. Its goal is provides software, hardware and community as a basic infrastructure to simplify design, simulation and testing, all around an open-source high-speed networking platform.

Figure 4.2: NetFPGA SUME Board Block Desig

Source: (Zilberman et al., 2014)

## **4.1 Forwarding Engine Design Overview**

The PvS forwarding engine is responsible for hosting virtual switch (vS) instances and performing flow steering between them. A conceptual view is shown in Figure 4.3. It contains five main elements: (4.2) Tx/Rx ports, which is the interface between the architecture and physical input and output layer, (4.3) Input vS Interface (IvSI), which receives incoming packets from the data plane, (4.4) vS Array, which hosts parallel vS instances, (4.5) Output vS Interface (OvSI), which outputs outgoing packets back to the data plane, and (4.6) Control vS Interface (CvSI), which provides access from the vS Array to the control engine.

**FPGA** vS Array TX RXvS Input vS Output vS RX TX Interface Interface ΤX RX (IvSI) (OvSI) vS Egress TΧ RX Ingress Table Table vS placevRX ٧TX holder Control vS Interface (CvSI)

Figure 4.3: PvS Forwarding Engine Architecture

Source: From the author

These modules have been developed in Verilog and implemented in the NetFPGA SUME board at 200 MHz. The communication interface with the control engine (at Host) occurs through PCI-e and USB interfaces. All design structures are based AXI4, released by ARM and later refined by Xilinx. The data flow transmission interface can be resumed as two AXI4 buses:

AXI Lite Control & Status Interface. The AXI Lite protocol is the control signals interface. It's basically a simple read/write interface, single beat access, with 32bit address and 32bit data. Implemented through Xilinx standardized AXI4 lite with 5 channels: read data, read address, write data, write address and write response. Components with AXI lite interface can be connected to each other via AXI interconnect module in which all peripherals reside within a slice address space. The master on this interconnect is both PCIe and microblaze, they can write and read all peripherals.