# Design and Characterization of the CLICTD Pixelated Monolithic Sensor Chip

I. Kremastiotis<sup>10</sup>, R. Ballabriga<sup>10</sup>, M. Campbell<sup>10</sup>, *Member, IEEE*, D. Dannheim, K. Dort, N. Egidos, *Student Member, IEEE*, J. Kröger, L. Linssen, X. Llopart,

M. Munker, A. Nürnberg, I. Peric, S. Spannagel, T. Vanat, and M. Williams<sup>D</sup>

Abstract-A novel monolithic pixelated sensor and readout chip, the compact linear collider tracker detector (CLICTD) chip, is presented. The CLICTD chip was designed targeting the requirements of the silicon tracker development for the experiment at the compact linear collider (CLIC) and has been fabricated in a modified 180 nm CMOS imaging process with charge collection on a high-resistivity p-type epitaxial layer. The chip features a matrix of 16 x 128 elongated channels, each measuring 300  $\times$  30  $\mu$ m<sup>2</sup>. Each channel contains 8 equidistant collection electrodes and analog readout circuits to ensure prompt signal formation. A simultaneous 8-bit time-of-arrival (with 10 ns time bins) and 5-bit time-over-threshold measurement is performed on the combined digital output of the 8 subpixels in every channel. The chip has been fabricated in two process variants and characterized in laboratory measurements using electrical test pulses and radiation sources. Results show a minimum threshold between 135 and 180 e<sup>-</sup> and a noise of about 14 e<sup>-</sup> rms. The design aspects and characterization results of the CLICTD chip are presented.

Index Terms—Monolithic CMOS sensors, silicon pixel detectors.

## I. INTRODUCTION

MONOLITHIC CMOS pixel technologies are considered for the tracking detector of the proposed future compact linear collider (CLIC) [1]–[3]. The requirements for the CLIC silicon tracker layers are summarized in Table I. For the large

Manuscript received June 11, 2020; revised July 29, 2020; accepted August 24, 2020. Date of publication August 27, 2020; date of current version October 16, 2020. This work was supported in part by the European Union's Horizon 2020 Research and Innovation Programme under Grant 654168 and in part by the Wolfgang Gentner Programme of the German Federal Ministry of Education and Research under Grant 05E15CHA.

I. Kremastiotis, R. Ballabriga, M. Campbell, D. Dannheim, L. Linssen, X. Llopart, M. Munker, and T. Vanat are with CERN, 1211 Geneva, Switzerland (e-mail: iraklis.kremastiotis@cern.ch).

K. Dort is with CERN, 1211 Geneva, Switzerland, and also with the Department of Experimental Physics II, Justus-Liebig-Universität Giessen, 35390 Giessen, Germany.

N. Egidos is with CERN, 1211 Geneva, Switzerland, and also with the Doctoral School of Engineering and Applied Sciences, University of Barcelona, 08007 Barcelona, Spain.

J. Kröger is with CERN, 1211 Geneva, Switzerland, and also with the Department of Physics and Astronomy, Ruprecht Karls Universität Heidelberg, 69117 Heidelberg, Germany.

A. Nürnberg and I. Peric are with the Karlsruhe Institute of Technology, 76131 Karlsruhe, Germany.

S. Spannagel is with CERN, 1211 Geneva, Switzerland, and also with DESY, 22607 Hamburg, Germany.

M. Williams is with CERN, 1211 Geneva, Switzerland, and also with the School of Physics and Astronomy, University of Glasgow, Glasgow G12 8QQ, U.K.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TNS.2020.3019887

TABLE I

Requirements for the Detectors in the CLIC Silicon Tracker

| Requirement               | Value                     |

|---------------------------|---------------------------|

| Single point resolution   | <7 µm (transverse plane)  |

| Max. cell size            | $0.05 - 0.5 \text{ mm}^2$ |

| Time resolution           | approx. 5 ns              |

| Hit detection efficiency  | > 99.7 - 99.9%            |

| Silicon thickness         | ≤ 200 µm                  |

| Average power consumption | $<150\mathrm{mW/cm^2}$    |

| Detector area             | $137 \mathrm{m}^2$        |

active area (137 m<sup>2</sup>) silicon tracker in the CLIC detector, this includes a material budget limited to 1-1.5% X<sub>0</sub> per detection layer (including sensor electronics, cables, mechanical supports, and cooling) and an average power consumption below 150 mW/cm<sup>2</sup>. A leak-less liquid cooling scheme is foreseen for the CLIC tracker. The material budget portion corresponding to the silicon sensor layers (including readout electronics) is approximately 200  $\mu$ m. In order to meet the required power consumption, the detector electronics can be operated in a power pulsed scheme where the main consuming parts of the circuitry are set to a standby power mode between subsequent bunch trains. Given the low duty cycle of the CLIC beam (156 ns long bunch trains repeated every 20 ms), the average power consumption can be significantly reduced by power pulsing and a trigger-less, frame-based readout at a frequency of 50 Hz can be employed. In addition, a  $\sim$  5-ns hit time resolution is required to suppress beaminduced background particles, along with a measurement of the energy deposited in the sensor to permit time walk correction and cluster position interpolation. A single point resolution of less than 7  $\mu$ m is required in the transverse direction of the barrel tracking detector, to achieve the required momentum measurement resolution in a magnetic field of 4 T. The granularity in the longitudinal direction, on the other hand, is limited by the occupancy from beam-induced background particles. Detector designs with long pixels or short strips (1–10 mm) can therefore be envisaged.

In this document, the design and characterization of a pixelated monolithic CMOS integrated circuit, the CLIC tracker detector (CLICTD) chip, are presented. The chip features an elongated readout channel geometry with an innovative subpixel segmentation scheme, to achieve a high measurement

This work is licensed under a Creative Commons Attribution 4.0 License. For more information, see https://creativecommons.org/licenses/by/4.0/

precision while limiting the amount of digital circuitry in the channel [4]. A simultaneous measurement of the timestamp and the energy deposited in the sensor is performed in each detecting channel (group of eight subpixels), while the collection electrodes, analog front-ends, and digital processing logic are all integrated in the channel.

Section II describes the process features and the design details of the CLICTD chip. Section III presents the performed characterization measurements.

#### II. CLICTD CHIP

The CLICTD chip was designed in the framework of the CLIC silicon tracker study and features a sensitive area of  $4.8 \times 3.84 \text{ mm}^2$ , with 16 columns by 128 rows of elongated channels, each measuring  $300 \times 30 \ \mu m^2$ . In order to minimize the detector capacitance while maintaining a fast signal formation time, the channel is segmented into eight subpixels, each with its own collection electrode, analog readout electronics, and discriminator. Minimizing the detector capacitance is beneficial for achieving a lower power consumption for a given signal-to-noise ratio [5]. The collection electrodes are, therefore, placed in the long channel dimension on a pitch of 37.5  $\mu$ m. Based on simulations, the 37.5  $\mu$ m pitch allows for having the minimum number of collection electrodes in the channel (in order to have an as low as possible detector capacitance) while maintaining a fast charge collection time (of the order of a few ns). Time-stamp and deposited energy information are stored for the combined output of all eight discriminators in the front-ends, as well as the hit pattern of the subpixels. In Sections II-A-II-E, a description of the fabrication process and the CLICTD chip design is presented.

#### A. Chip Fabrication Process

A modified 180-nm CMOS imaging process, with charge collection on a 30-µm-thick highly resistive epitaxial layer, was selected for the design of the CLICTD chip [6]. The epitaxial layer is placed on top of a thicker, low resistivity silicon substrate, resulting in a total silicon thickness of 300  $\mu$ m. This process offers a small n-type collection electrode (with a diameter of approximately 2  $\mu$ m) placed on top of the p-type high-resistivity epitaxial layer. The small detector capacitance allows for an important reduction of the analog power consumption and noise of the front-end electronics, compared to a detector of similar performance with larger detector capacitance. Taking advantage of the low noise in the front-end, a low detection threshold can be achieved. All analog and digital on-channel electronics are placed on a deep p-well, which offers an isolation between the electronics and the collection electrode, thus enabling the use of on-channel CMOS digital logic.

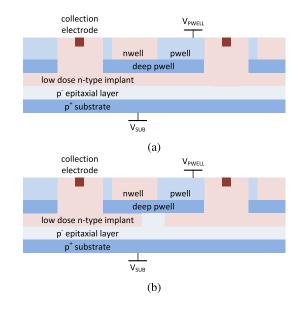

In order to fully deplete the epitaxial layer underneath the p-wells, a modification of this process has been developed, including an additional deep n-type implant. To speed up the charge collection for particles impinging between two collection electrodes and reduce the charge sharing within a detection channel, a further modification has been studied [7]. In this case, the deep n-type implant is segmented in the region

Fig. 1. Two CLICTD process variants. (a) Continuous n-implant and (b) gap in n-implant (not to scale). From [8].

between neighboring collection electrodes in order to increase the lateral electric field from the pixel edge to the collection electrode. The increased lateral field reduces the charge collection time, the loss of charges by recombination, and the amount of charge sharing between neighboring electrodes. The cross sections of the process variants with continuous and segmented deep n-implants are illustrated in Fig. 1(a) and (b), respectively.

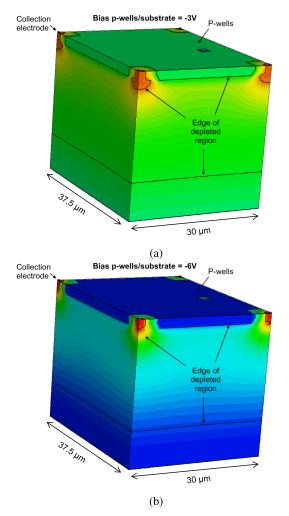

To enlarge the depleted region in the sensor volume, two nodes need to be reverse biased: the substrate, which is the physical bulk of the chip ( $V_{SUB}$  in Fig. 1), and the p-wells where the on-channel electronics are placed ( $V_{PWELL}$ in Fig. 1). According to simulations and measurements, the maximum reverse bias that can be applied to the p-wells and the substrate is -6 V, which is sufficient to deplete the epitaxial layer [9]. A TCAD simulation of the electrostatic potential, with the edges of the depleted region marked in black, for a reverse bias of -3 V at the p-wells and substrate is presented in Fig. 2(a). The same simulation, this time with the p-wells and substrate biased to -6 V, is presented in Fig. 2(b). From the simulations, it is shown that the volume around the collection electrode is further depleted by applying a higher reverse bias, thus minimizing the input capacitance [10].

The main contribution to the collected charge comes from the charge carriers that move by drift in the epitaxial layer. An additional diffusion component is collected from the un-depleted low-resistivity silicon substrate.

The CLICTD chip was fabricated in both process variants. In the case of the segmented n-implant, the segmentation was performed between subpixels only in the long channel dimension, in order to achieve a faster charge collection time and reduced charge sharing within a detection channel. No segmentation was performed along the short channel dimension, as charge sharing is desired for improving the spatial resolution in the transverse plane through hit position interpolation.

Fig. 2. Simulation of the electrostatic potential for a reverse bias of: (a) -3 V and (b) -6 V at the p-wells and substrate. The edges of the depleted region are marked in black. TCAD simulation for the process variant with continuous n-implant.

#### B. Analog Front-End

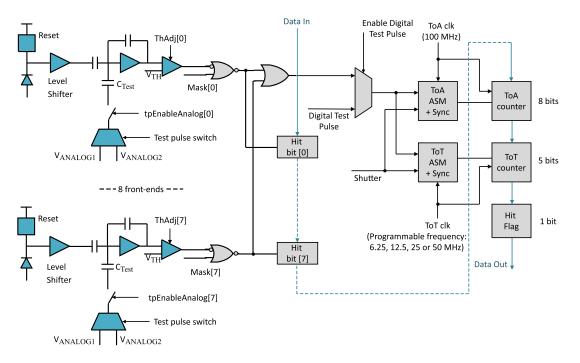

The CLICTD channel is segmented into eight collection electrodes, resulting in an electrode pitch of  $37.5 \times 30 \ \mu m^2$ . The segmentation in the long direction has been chosen in simulation to allow for a prompt charge collection, in view of the required time resolution. A block diagram of the analog front-end is shown on the left side of Fig. 3. A level shifter is placed close to the collection electrode in order to keep the input capacitance of the front-end as low as possible. The collection electrode is discharged by using a reset transistor. The voltage pulse at the output of the level shifter is amplified with a voltage amplifier. The amplifier includes a feedback loop with leakage current compensation, similar to the feedback architecture described in [11]. Amplifier parameters such as the dc output (baseline voltage), amplifier rise time, and slope for return to the baseline are controllable using biasing digitalto-analog converters (DACs) that are placed in the analog periphery of the chip. The amplified voltage pulse is connected to a discriminator where it is compared to a programmable threshold voltage that is common to the whole matrix. The signal at the output of the discriminator indicates whether a particle that deposited an energy above the applied threshold

was detected and is processed by the digital logic in order to store time-of-arrival (ToA) and time-over-threshold (ToT) information for the detected particle, as will be explained in Section II-C. To correct for variations in the baseline (and consequently the effective threshold) over the sensitive area, a threshold tuning DAC, implemented as a 3-bit binary weighted current source, is included in each analog subpixel. This DAC is connected to the discriminator and can be used to equalize the matrix by tuning the baseline voltage for each subpixel such that the threshold dispersion is minimized.

The eight discriminator outputs are connected to the inputs of the on-channel digital logic, where the signals are processed and stored during each acquisition.

Simulations show that the performance of the analog frontend depends on the value of the capacitance of the collection electrode, which is estimated to be between 1.5 and 2.5 fF for the nominal bias of -6 V at the p-wells and substrate. The capacitance value is strongly dependent on the bias voltage since the junction in the modified process is moved away from the collection electrode [10]. For a detector capacitance of 1.5 fF, the simulation predicts a gain up to 550 mV/ke<sup>-</sup> and a noise of 14 e<sup>-</sup> rms. For a detector capacitance of 2.5 fF, the corresponding simulated values are a gain of 380 mV/ke<sup>-</sup> and a noise of 18 e<sup>-</sup> rms. The expected signal rise time at the amplifier output is of the order of 100 ns. The simulated time walk is below 10 ns for a collected charge of 380 e<sup>-</sup> or above. A time walk correction can be applied using the energy measurement.

In order to electrically test the CLICTD channel, test pulses with programmable amplitude, simulating a signal induced by a particle, can be injected to individual subpixels. The amplitude of the test pulse injected to the analog front-end is set by the difference between the  $V_{ANALOG1}$  and  $V_{ANALOG2}$  voltages in Fig. 3, which are controlled by DACs in the chip periphery. The option to inject a digital pulse directly to the input of the digital logic in the channel is also foreseen. When a digital test pulse is injected, all analog front-ends are disconnected from the digital logic in order to decouple the two domains and test the functionality of the digital logic. A masking scheme, where any subpixels that malfunction or show higher noise can be excluded from further processing, is also implemented.

# C. Digital Logic

A block diagram of the circuitry in the CLICTD channel is presented in Fig. 3. In the on-channel digital logic, binary hit information is stored for each of the eight subpixels. The user can thus identify which, and how many, of the subpixels are hit during each acquisition. For the time and deposited energy measurement, all eight discriminator outputs are combined by means of an OR gate. The time-of-arrival (ToA) measurement is employed for determining the time of occurrence of the hit. Time bins of 10 ns are expected to be sufficient for achieving the required timing resolution. A 100-MHz clock is distributed along the channel columns, while a global shutter signal, defining the start and stop of the acquisition phase, is used as a time reference. The time-stamp is stored as the number of clock cycles from the moment when the OR of

Fig. 3. Block diagram of the analog front-end (in blue) and digital logic (in gray) in the CLICTD detector channel.

the discriminator outputs is set until the shutter is closed. The ToA counter has a depth of 8 bits, corresponding to a range of 2.54  $\mu$ s. As the time required for the signal to return to the baseline is proportional to the signal amplitude (and thus to the collected charge), the charge is determined by the time interval for which the discriminator output stays above the global threshold (ToT measurement). The ToT counter has a depth of 5 bits and a programmable range from 0.6 to 4.8  $\mu$ s. Asynchronous state machines are implemented in the CLICTD channel digital logic, in order to minimize the circuit area and the power consumption. In the layout, metal lines are used to shield the analog circuitry from the switching digital lines.

Since the information from the subpixels is combined using an OR gate in the CLICTD channel, the time-stamp is stored for the subpixel that first detected a hit. The energy information measures the OR of the ToT of all subpixels in the channel, in the case of overlapping signals from the subpixels. In the case of multiple, discrete hits in the same channel and within the same shutter frame, the sum of the measured ToT will be accumulated in the ToT counter.

During readout, the digital logic switches to a 40-MHz readout clock, and all channels in a column are connected as a long shift register, shifting the acquired data out of the chip serially. The readout clock frequency was selected as it is sufficient for shifting the acquired data out of the CLICTD matrix in a reasonable time (of the order of 1 ms). An optional compression algorithm is implemented to reduce the amount of data that are transmitted. The compression is based on a "hit flag" bit that is set to "high" once the channel detects a hit. For channels that detected a hit, all 22 bits of data (including hit flag, ToA, ToT, and binary hit information for the eight subpixels) are shifted out of the channel. In the case when the channel did not detect a hit, only the hit flag bit is shifted out.

The following 21 bits are skipped and the readout proceeds to the next channel. For the low expected occupancies in the CLIC tracker (of about 1% for the CLICTD channel size), this compression algorithm is expected to reduce the readout time by approximately a factor of 15.

## D. Periphery Electronics and Interface

In the analog periphery of the chip, 20 biasing DACs are included in order to bias the different front-end nodes. For testing and debugging purposes, the option to monitor or overwrite the output of each of the DACs is included. One of the DAC outputs can be monitored or overwritten at a time. In addition, the analog periphery comprises a bandgap circuit that internally generates a voltage reference for the chip.

In the digital periphery, a slow control interface based on a standard  $I^2C$  slave is implemented [12]. Through the slow control, the user can read and write all internal registers to control the biasing DACs, to configure the matrix, as well as to send test pulses, power pulsing, and readout commands. Along with the data output, a clock output and a signal indicating the start and end of the transmitted frame are sent during readout to facilitate the synchronization with the data acquisition (DAQ) system to sample the data.

## E. Chip Integration and Verification

The CLICTD chip was integrated using the digital-on-top approach. During the digital-on-top integration, the digital descriptions of all analog and digital building blocks are used to create a digital netlist that describes the connectivity among all instances. This approach allows for high-level digital simulations and verification of the design.

As a final step, the chip design was verified using the universal verification methodology (UVM) [13]. During the

Fig. 4. Photograph of a CLICTD sample, glued and wire-bonded on a PCB. Image credit: CLICdp.

verification stage, the postlayout chip netlist (including delays due to routing lines and parasitic capacitances) was simulated in different corners (power supply, temperature, and process variations). Extensive digital verification was proved essential for the CLICTD design, as several issues, including logic mistakes and timing violations, were detected and fixed before production. Two malfunctions of the digital logic were observed in the measurements of the prototype chips. The first was an issue in the configuration state machine and the second in the way the data are read out when the compression algorithm is enabled. Workarounds with negligible impact on the chip performance have been implemented for both issues.

A user's manual with a detailed description of the commands and operation of the CLICTD chip was compiled and made available online [14].

# **III. MEASUREMENT RESULTS**

First samples of the CLICTD chip were glued and wire-bonded on a custom-designed printed circuit board (PCB) and tested using the Caribou DAQ system [15]. A photo of a CLICTD sample, wire-bonded on the PCB, is presented in Fig. 4. First measurement results were presented in [16].

#### A. Electrical Characteristics

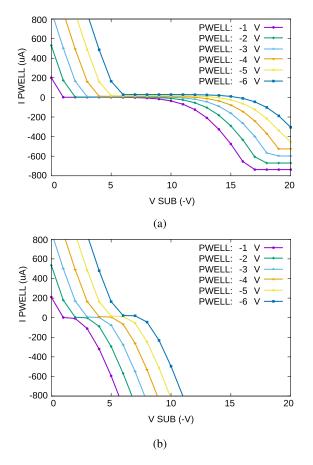

Studying the I-V characteristics of the sensor, and, in particular, the leakage current at the p-wells and substrate confirmed the differences between the two process variants, as expected from simulations. For the process variant with continuous n-type implant, the substrate can be biased to higher (in absolute value) voltages than the p-wells without significant increase in the leakage current. After the substrate voltage exceeds the p-wells voltage by about 10 V in absolute value, the current increases due to punchthrough between the p-wells and substrate. On the other hand, for the process variant with the gap in the n-type implant, a similar bias voltage should be applied to the two nodes such that the current is not dominated by the punchthrough current flowing between the p-wells and substrate. These differences are illustrated in Fig. 5(a) and (b) for the process variant with continuous n-type implant and with gap in the n-type implant, respectively. For this measurement, the p-well bias was set to values from -1 to -6 V and the substrate bias was scanned. The leakage current plotted in Fig. 5 was measured at the p-wells. For both process variants, the collection electrode is biased to about 0.8 V. The measurements were performed in

Fig. 5. Leakage current measured at the p-wells in the CLICTD matrix as a function of the substrate bias, for different values of the p-well bias. CLICTD sample with (a) continuous n-implant and (b) gap in n-implant [8].

room temperature. The saturation for higher absolute values of the reverse bias voltage in Fig. 5(a) is an effect of the current limit applied for this measurement. The reverse bias that can be applied at the p-wells is constrained to -6 V, to ensure reliable operation of the transistors in the sensitive area [9]. As the epitaxial layer is expected to be fully depleted at a bias of -6 V, both at the substrate and the p-wells, this was considered as the target operation point for the sensor. In contrast to the standard planar sensors, a higher negative reverse bias does not necessarily lead to a better performance, due to the complex field in the sensor [7]. As conclusion, although the sensor shows different I-V characteristics for the two process variants, it can be operated in both cases as long as the structure is properly biased. In order to have a straightforward comparison of the two process variants, for the majority of the performed measurements, the substrate was kept at the same bias as the p-wells for both process variants.

# B. Optimization of Operation Parameters

Due to the fact that the on-channel nMOS devices are laid out on the reverse-biased p-well, the transistors are expected to slow down when a higher negative bias is applied. Since the negative bias at the p-wells is not a standard feature of the fabrication process, the effects of the applied reverse bias on the nMOS devices are not well modeled in simulations.

Fig. 6. Baseline dispersion over the CLICTD matrix, before (red curve) and after (blue curve) equalization. Sample with a continuous n-type implant, with the substrate and p-wells biased to -6 V.

In order to correct for this effect, the operating point of several nodes of the circuit (e.g., the feedback loop in the analog front-end) had to be tuned after biasing the sensor to the nominal -6 V at the p-wells and substrate. Thereby, the nMOS transistors were set back to the desired operation point and the circuit could be operated successfully.

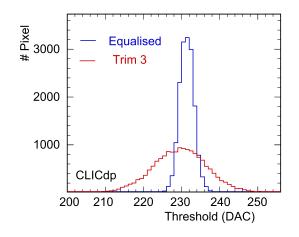

## C. Threshold Equalization

A threshold equalization algorithm was applied employing the 3-bit threshold tuning DAC in every subpixel. Threshold scans were performed for each of the eight codes of this DAC, while the number of detected hits for each applied threshold value was measured for each subpixel. The baseline was then extracted on a subpixel basis for every DAC code as the mean value of the curve resulting from the number of noise hits that were counted during the threshold scan. A target baseline was selected as the average of the mean values of the resulting baseline distributions for every DAC code. The matrix was then equalized by choosing the DAC code per subpixel such that its baseline is closest to the target.

Fig. 6 presents the measured baseline for all subpixels, before and after equalization, for a CLICTD sample from the process variant with a continuous n-layer, with the p-wells and substrate biased to -6 V. After applying the threshold equalization algorithm, the threshold dispersion over the CLICTD matrix, estimated as the rms of the baseline distribution, ranges from 33 to 39 e<sup>-</sup> rms, for the three different CLICTD samples that have been measured and calibrated. Before threshold equalization, the threshold dispersion is of the order of  $100 e^{-}$  rms. The conversion from DAC codes to electrons was done using the calibration presented in Section III-F.

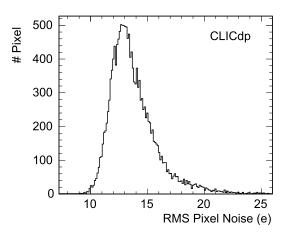

# D. Noise

The noise per subpixel was calculated as the rms value of the distribution of the measured noise hits in threshold scans. The mean value for the noise per subpixel was extracted to be approximately  $14 e^{-1}$  rms, for three measured assemblies from

Fig. 7. Histogram of noise rms per subpixel, extracted from threshold scans and measured in electrons. Sample with continuous n-type implant, with the substrate and p-wells biased to -6 V.

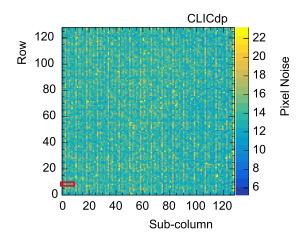

Fig. 8. Two-dimensional map of the noise rms per subpixel over the CLICTD matrix, extracted from threshold scans and measured in electrons. Sample with a continuous n-type implant, with the substrate and p-wells biased to -6 V. The position of one elongated channel in the matrix is marked in red.

both process variants, with the p-wells and substrate biased to -6 V. A histogram of the extracted noise rms values for all subpixels is presented in Fig. 7. Fig. 8 presents a 2-D map of the measured noise rms in electrons over the CLICTD matrix.

A regular pattern can be observed in Fig. 8, showing a dependence of the noise on the position of the tested subpixel. This pattern results from the regular structure of the layout in the CLICTD matrix. Although the layout of the analog front-end is identical for the eight subpixels, the shared digital logic is distributed along the channel. Due to this layout feature, differences in parasitic capacitances or sources of noise coupling can be expected, resulting in the observed pattern that repeats every eight subpixel columns in the horizontal direction. The tail in the right-hand side of the noise distribution in Fig. 7 results from the columns with higher noise that can be observed in Fig. 8. The higher noise in these subpixel columns is possibly a result of coupling with noise sources in the digital logic via parasitic capacitances. In the vertical direction, a similar pattern can be observed. The digital logic in one every eight rows includes additional buffers for distributing the clock and shutter signals from the periphery

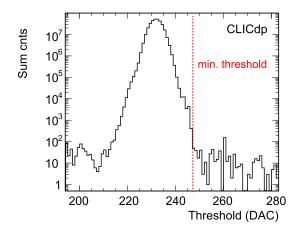

Fig. 9. Number of noise hits detected within a 1-ms shutter as a function of the threshold DAC code. Sample with a continuous n-type implant, with the substrate and p-wells biased to -6 V. The vertical line indicates the minimum operation threshold for this sample.

(which is located at the bottom of the matrix) to the top of the matrix. This results in a slightly modified layout for the digital logic in these rows and this structure is also observed in the noise plots.

#### E. Optimization of Operation Threshold

In order to identify the minimum operation threshold, the threshold was set to the lowest value that still ensures a noise-free operation. Fig. 9 presents the measured number of noise hits acquired within a 1-ms shutter as a function of the applied threshold DAC code. Subpixels that showed a non-Gaussian noise performance and were detecting noise hits even at higher threshold values were masked (thus excluded from further processing) in order to achieve a lower operation threshold. After equalization, the minimum operation threshold of the measured CLICTD samples is between 135 and 180 e<sup>-</sup> with an uncertainty of  $\pm 3$  e<sup>-</sup>, as extracted from the calibration measurements presented in Section III-F. At this threshold, the CLICTD matrix detects no noise hits. For the CLICTD sample used for this measurement, only 0.03% of the subpixels were masked.

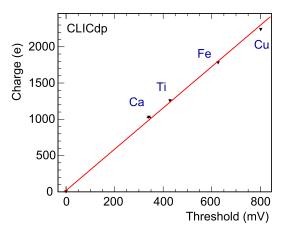

#### F. Calibration With Radiation Sources

In order to obtain physical units for the CLICTD performance parameters, samples were exposed to photons with known energies, using an X-ray machine and the fluorescence spectra of different targets. The  $K_{\alpha}$  peak of the fluorescence spectrum of iron is at 6.4 keV and, with a known mean electron-hole pair creation energy in silicon of 3.62 eV, the charge corresponding to the most probable value of the energy deposited in the sensor is 1.77 ke<sup>-</sup>. For the copper target, the equivalent value is 2.22 ke<sup>-</sup>, for an X-ray energy of 8.04 keV. Apart from the iron and copper targets, other materials such as calcium and titanium were used to verify the gain linearity of the CLICTD chip, as well as its ability to detect low energy photons.

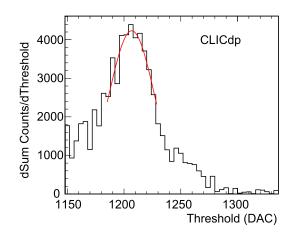

The calibration was performed by scanning the threshold voltage in the equalized CLICTD chip and counting the

Fig. 10. Fluorescence spectrum and Gaussian fit to the  $K_{\alpha}$  peak, resulting from a measurement with a titanium target. Sample with a continuous n-type implant, with the substrate and p-wells biased to -6 V.

Fig. 11. Gain calibration of the CLICTD amplifier response, extracted from fits of the  $K_{\alpha}$  peaks of the X-ray fluorescence spectra from different target materials. Sample with a continuous n-type implant, with the substrate and p-wells biased to -6 V. The error bars show the error on the mean of a Gaussian fit to the  $K_{\alpha}$  peaks.

number of X-rays detected for each voltage. By this scan, an occupancy curve showing the number of detected X-rays per threshold voltage is produced. The fluorescence spectrum is obtained by the derivative of this occupancy curve and the threshold voltage corresponding the  $K_{\alpha}$  peak is determined as the mean of a Gaussian function fitted to the spectrum. An example spectrum obtained measuring the fluorescence of a titanium target is presented in Fig. 10. The Gaussian distribution fitted to the observed  $K_{\alpha}$  peak is plotted in red.

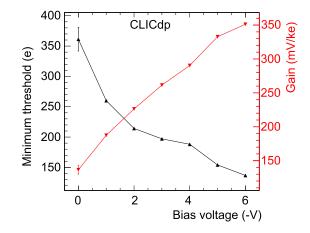

Fig. 11 shows the voltage amplitude at the output of the amplifier which corresponds to the  $K_{\alpha}$  peak of the fluorescent X-rays for each material, for a CLICTD sample with continuous n-type implant and with the substrate and p-wells biased at -6 V. The error bars correspond to the fit error of a Gaussian to the  $K_{\alpha}$  peaks. The amplifier gain is determined by the slope of the linear fit, which in this case is approximately 350 mV/ke<sup>-</sup>. Comparing this value to the simulated performance presented in Section II-B gives an indication for the input capacitance of the detector.

In addition, the conversion from threshold DAC steps to electrons, used for the results presented in Section III-C, was

Fig. 12. Amplifier gain, measured with X-ray calibration with different targets, as a function of the reverse bias applied to the p-wells and substrate. The error bars show the error on the mean of a Gaussian fit to the  $K_{\alpha}$  peaks.

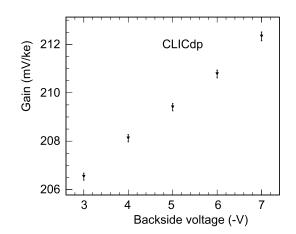

extracted from the X-ray calibration measurements. For a reverse bias of -6 V at the p-wells and the substrate, one LSB of the threshold DAC corresponds to a step of  $\sim 9 e^-$  (from 8.6 to 9.0 e<sup>-</sup> for the three measured assemblies). The fluorescence spectra from the various targets were measured for different values of the reverse bias voltages applied to the sensor, in order to study the effect of the bias voltage on the sensor and the performance of the front-end. Fig. 12 presents the measured amplifier gain and minimum operation threshold for different values of the sensor bias. This measurement confirms that with higher reverse bias voltage, the gain increases and lower minimum threshold can be achieved due to the reduced sensor capacitance (resulting from the larger depletion of the deep n-type implant around the collection electrode). For this measurement, both the p-wells and the substrate were biased at the same voltage level, indicated on the horizontal axis.

According to TCAD finite-element simulations, the reverse bias applied to the p-wells is expected to have the largest impact on the sensor performance [7]. In order to confirm this, similar calibration measurements were performed with the p-well bias kept at a fixed value, while the reverse bias at the substrate was scanned. The amplifier gain, measured from the fluorescence of an iron target for different values of the substrate bias, is plotted in Fig. 13. For this measurement, performed with a CLICTD sample with continuous n-type implant, the p-wells were constantly biased at -3 V. The gain increase of the amplifier is about 0.6% for a step of -1 V at the substrate bias. This confirms that the substrate bias has a negligible impact on the sensor performance, compared to when the two reverse bias nodes are operated at the same voltage.

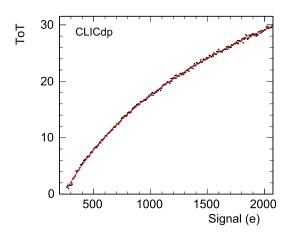

# G. ToT Calibration

A calibration of the ToT measurement with test pulses was performed for the CLICTD chip. Test pulses of different amplitudes were injected at the CLICTD front-end amplifier, in order to parameterize the relationship between the input signal amplitude and the measured ToT. Fig. 14 presents the measured ToT as a function of the injected test-pulse signal.

Fig. 13. Amplifier gain, measured with X-ray calibration with an iron target, as a function of the reverse bias applied to substrate, for a fixed bias value of -3 V at the p-wells. Sample with a continuous n-type implant. The error bars show the error on the mean of a Gaussian fit to the K<sub>a</sub> peaks.

Fig. 14. Measured ToT (in 160 ns bins) as a function of the injected test-pulse signal, for a single subpixel in the CLICTD matrix. Fitted with a surrogate function. Sample with a continuous n-type implant, with the substrate and p-wells biased to -6 V.

The ToT in this measurement is the mean measured ToT of 40 test pulses that were injected for each signal amplitude. A surrogate function, described by (1), was fitted to the measured data for each subpixel

$$ToT = ax + b - \frac{c}{x - t}.$$

(1)

The parameters a, b, c, and t are the fit parameters for the function and x is the injected pulse amplitude.

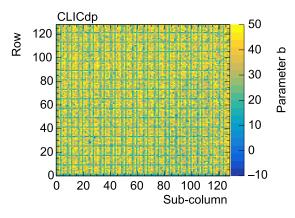

In Fig. 15, the value of one of the fit parameters for the surrogate function (parameter b) is plotted across the CLICTD matrix. A pattern that repeats every eight subpixels can be observed due to the regular structure of the layout in the CLICTD matrix, similar to the noise plots in Section III-D.

# H. Power Consumption

Taking advantage of the low duty cycle of the beam in the CLIC accelerator, introduced in Section I, a power pulsing scheme is implemented for setting parts of the CLICTD circuitry to a low power mode between bunch trains in order to minimize the average power consumption. In the analog

Fig. 15. Parameter *b* of the surrogate function fit to the measured ToT, plotted across the CLICTD matrix. Sample with a continuous n-type implant, with the substrate and p-wells biased to -6 V.

TABLE II POWER CONSUMPTION OF THE CLICTD CHIP

|                                        | Acquisition | $\mathbf{Readout}^1$ | Standby | Average <sup>2</sup> |

|----------------------------------------|-------------|----------------------|---------|----------------------|

| Analog - matrix [mW/cm <sup>2</sup> ]  | 524         | 2                    | 2       | 2.8                  |

| Analog - periphery [mW]                | 9           | 9                    | 9       | 9                    |

| Digital - matrix [mW/cm <sup>2</sup> ] | 279         | 112                  | 0.6     | 2.9                  |

| Digital - periphery [mW]               | 40          | 40                   | 40      | 40                   |

| Total - matrix [mW/cm <sup>2</sup> ]   | 803         | 114                  | 2.6     | 5.7                  |

| Total - periphery [mW]                 | 49          | 49                   | 49      | 49                   |

<sup>1</sup> Values extracted from simulations.

<sup>2</sup> Values extrapolated from simulations and static power consumption measurements, averaged assuming a CLIC duty cycle with an acquisition time of  $30 \,\mu$ s, a readout time of  $340 \,\mu$ s and a standby time of 20 ms.

domain, the main current consuming nodes of the front-end in the subpixel (level shifter, voltage amplifier, discriminator, and threshold tuning DAC) are set to standby between subsequent acquisitions. For the digital circuitry, the clock is gated in parts of the logic that only need to be active for short periods of time in order to reduce the number of switching gates. During acquisition, the on-channel state machines enable the clock in the counters only when a hit is detected in the channel. The 100-MHz measurement clock is distributed in the matrix only during the acquisition period. During readout, the 40-MHz readout clock is distributed to only one column at a time, since the data are shifted out on a column-by-column basis.

The CLICTD operation is divided into three distinct phases: acquisition, readout, and standby. The measured power consumption for the analog and digital circuitry for each phase, averaged over four measured assemblies, is presented in Table II. For the matrix electronics, the power consumption is noted in  $mW/cm^2$ . The CLICTD periphery electronics are continuously powered (no power pulsing is applied) and its power consumption is noted in milliwatt. In view of a future larger version of the CLICTD chip, the periphery is expected to be kept similar in terms of area and power consumption.

For estimating the average power consumption over the CLIC cycle, an acquisition duty cycle of 30  $\mu$ s/20 ms is assumed. The 30  $\mu$ s is expected from simulations to be sufficient for the front-end to settle after being set to the nominal power settings for acquisition. The readout time is

calculated as the time required for reading out a 1 cm<sup>2</sup> matrix, using a 40-MHz clock and the applied compression algorithm, with an occupancy of 1%. For measuring the power consumption, a current monitoring circuit was connected to the power supplies. However, communication with this circuit is established using the I<sup>2</sup>C slow control interface, which only allows for static measurements and is not sufficiently fast to measure the power consumption during the short time that the CLICTD readout is active. The values presented for the readout power in Table II are therefore extracted from simulations. The numbers presented for the average power consumption, after power pulsing, are extrapolated from simulated values and static measurements, using the aforementioned acquisition and readout times. Based on this measurement, the average power consumption over the CLIC cycle is expected to be dominated by the power consumption during the standby time. The value for the average power consumption is well within the detector requirements.

#### I. Detection of Minimum Ionizing Particles

First results from measurements in test beams have been presented in [17]. Preliminary analysis of the acquired data shows a performance close to the requirements for the CLIC silicon tracker. The full analysis is still ongoing.

#### IV. CONCLUSION AND OUTLOOK

The main design aspects and characterization results of the CLICTD chip have been presented. Slight variations have been observed within the eight subpixels in an elongated channel. Based on the measurement results so far, there is no indication of significant impact of these variations on the overall chip performance. Results from the three samples of the CLICTD chip show a minimum threshold between 135 and 180 e<sup>-</sup> and a noise of about 14 e<sup>-</sup> rms. Based on static power measurements, the expected power consumption, averaged over the cycle of the CLIC beam, is 5.7 mW/cm<sup>2</sup> for the sensitive area, plus about 50 mW for the periphery electronics.

Future studies will focus on a detailed comparison of the charge collection properties and the tracking performance of the two process variants, including test-beam measurements with inclined tracks and for samples thinned to  $40-100 \ \mu m$  total thickness.

#### ACKNOWLEDGMENT

The authors would like to thank T. Kugathasan and W. Snoeys (CERN, Geneva, Switzerland) for their valuable input on the technology and the design flow. The measurements leading to the results mentioned in Section III-I have been performed at the Test Beam Facility at DESY Hamburg (Germany), a member of the Helmholtz association (HGF).

#### REFERENCES

- D. Dannheim and A. Nürnberg, "Requirements for the CLIC tracker readout," CERN, Geneva, Switzerland, Tech. Rep. CLICdp-Note-2017-002, 2017.

- [2] D. Dannheim, K. Krüger, A. Levy, A. Nürnberg, and E. Sicking, Eds., "Detector technologies for CLIC," CERN, Geneva, Switzerland, Tech. Rep. CERN-2019-001, 2019.

- [3] L. Linssen, A. Miyamoto, M. Stanitzki, and H. Weerts, Eds., "Physics and detectors at CLIC: CLIC conceptual design report," CERN, Geneva, Switzerland, Tech. Rep. CERN-2012-003, 2012.

- [4] I. Kremastiotis *et al.*, "Design of a monolithic HR-CMOS sensor chip for the CLIC silicon tracker," in *Proc. Top. Workshop Electron. Particle Phys. (TWEPP)*, 2018, Art. no. PoS(TWEPP2018)072.

- [5] W. Snoeys, "Monolithic pixel detectors for high energy physics," Nucl. Instrum. Meth. Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 731, pp. 125–130, Dec. 2013.

- [6] W. Snoeys et al., "A process modification for CMOS monolithic active pixel sensors for enhanced depletion, timing performance and radiation tolerance," Nucl. Instrum. Meth. Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip., vol. 871, pp. 90–96, Nov. 2017.

- [7] M. Munker *et al.*, "Simulations of CMOS pixel sensors with a small collection electrode, improved for a faster charge collection and increased radiation tolerance," *J. Instrum.*, vol. 14, no. 5, May 2019, Art. no. C05013.

- [8] I. Kremastiotis, "Implementation and characterisation of monolithic CMOS pixel sensors for the CLIC vertex and tracking detectors," CERN, Geneva, Switzerland, Karlsruhe Inst. Technol., Karlsruhe, Germany, Tech. Rep. CERN-THESIS-2020-014, 2020.

- [9] J. W. van Hoorne, "Study and development of a novel silicon pixel detector for the upgrade of the ALICE inner tracking system," CERN, Geneva, Switzerland, Tech. Univ. Vienna, Vienna, Austria, Tech. Rep. CERN-THESIS-2015-255, 2015.

- [10] M. Munker, "Test beam and simulation studies on high resistivity CMOS pixel sensors," CERN, Geneva, Switzerland, Univ. Bonn, Bonn, Germany, Tech. Rep. CERN-THESIS-2018-202, 2018.

- [11] F. Krummenacher, "Pixel detectors with local intelligence: An IC designer point of view," *Nucl. Instrum. Meth. Phys. Res. A, Accel. Spectrom. Detect. Assoc. Equip.*, vol. 305, no. 3, pp. 527–532, Aug. 1991.

- [12] NXP. (2014). I<sup>2</sup>C-Bus Specification and User Manual. Accessed: Jun. 9, 2020. [Online]. Available: http://www.nxp.com/documents/ user\_manual/UM10204.pdf

- [13] A. Fiergolski, "Simulation environment based on the universal verification methodology," J. Instrum., vol. 12, Jan. 2017.

- [14] I. Kremastiotis et al. (2019). CLICTD Chip Description. Accessed: Jun. 9, 2020. [Online]. Available: https://edms.cern.ch/ document/2383095/1

- [15] A. Fiergolski, "A multi-chip data acquisition system based on a heterogeneous system-on-chip platform," in *Proc. Int. Conf. Technol. Instrum. Part. Phys.*, in Springer Proceedings in Physics, vol. 212, 2018, pp. 303–308.

- [16] I. Kremastiotis et al., "CLICTD: A monolithic HR-CMOS sensor chip for the CLIC silicon tracker," in Proc. Top. Workshop Electron. Part. Phys. (TWEPP), 2019, Art. no. PoS(TWEPP2019)039.

- [17] M. Munker, "Vertex and tracking setector R&D for CLIC," CERN, Geneva, Switzerland, Tech. Rep. CLICdp-Conf-2020-003, 2020.