## INVESTIGATION INTO RUNTIME WORKLOAD CLASSIFICATION AND MANAGEMENT

## FOR ENERGY-EFFICIENT MANY-CORE SYSTEMS

Ali Majeed M. Aalsaud

A Thesis Submitted for the Degree of Doctor of Philosophy at Newcastle University

School of Electrical and Electronic Engineering Faculty of Science, Agriculture and Engineering August 2019

Ali Aalsaud: Investigation into Runtime Workload Classification and Management for Energy-efficient Many-core Systems ©2019

#### DECLARATION

I hereby declare that this thesis is my own work and effort and that it has not been submitted anywhere for any award. Where other sources of information have been used, they have been acknowledged.

Newcastle upon Tyne August 2019

Ali Aalsaud

#### CERTIFICATE OF APPROVAL

I confirm that, to the best of my knowledge, this thesis is from the student's own work and effort, and all other sources of information used have been acknowledged. This thesis has been submitted with my approval.

ALEX YAKOVLEV FEI XIA RISHAD SHAFIK To my greatest supporters that is my wonderful parents, my beloved wife, Nouranse, my lovely daughters, and my lovely son Elia.

— Ali

#### ACKNOWLEDGEMENTS

I would like to express my sincere gratitude to my supervisors Prof. Alex Yakovlev, Dr. Fei Xia and Dr.Rishad Shafik for their support and guidance through my studies. They have been and always will be a source of inspiration and my role model as a researcher.

I am grateful to my sponsor Iraqi Ministry of Higher Education and Scientific Research and Mustansiriyah University for funding my Ph.D. study through their scholarship program.

I am also grateful to my colleagues and friends in the School of Electrical and Electonic Engineering, especially those in Microelectronic Systems research group, at Newcastle University for their assistance and guidance in my studies.

I would like to express my great thanks to (PRiME) project members for their support and useful discussions. I am thankful to Dr. Ashur Rafiev for his supporting through continues discussions, experimental works, and preparing mthread benchmark programs.

Finally, I would like to offer my special regards to all the staff of the school of Electrical and Electronic Engineering in Newcastle university.

Last but not least, I would like to thank my beautiful family for their continuous support and motivation throughout my Ph.D. journey.

Recent advances in semiconductor technology have facilitated placing many cores on a single chip. This has led to increases in system architecture complexity with diverse application workloads, with single or multiple applications running concurrently. Determining the most energy-efficient system configuration, i.e. the number of parallel threads, their core allocations and operating frequencies, tailored for each kind of workload and application concurrency scenario is extremely challenging because of the multifaceted relationships between these configuration knobs. Modelling and classifying the workloads can greatly simplify the runtime formulation of these relationships, delivering on energy efficiency, which is the key aim of this thesis.

This thesis is focused on the development of new models for classifying single- and multi-application workloads in relation to how these workloads depend on the aforementioned system configurations. Underpinning these models, we implement and practically validate low-cost runtime methodologies for energy-efficient many-core processors.

This thesis makes four major contributions. Firstly, a comprehensive study is presented that profiles the power consumption and performance characteristics of a multi-threaded many-core system workload, associating power consumption and performance with multiple concurrent applications. These applications are exercised on a heterogeneous platform generating varying system workloads, viz. CPU-intensive or memory-intensive or a combination of both. Fundamental to this study is an investigation of the tradeoffs between inter-application concurrency with performance and power consumption under different system configurations.

The second is a novel model-based runtime optimization approach with the aim of achieving maximized power normalized performance considering dynamic variations of workload and application scenarios. Using real experimental measurements on a heterogeneous platform with a number of PARSEC benchmark applications, we study power normalized performance (in terms of IPS/Watt) underpinned with analytical power and performance models, derived through multivariate linear regression (MLR). Using these models we show that CPU intensive applications behave differently in IPS/Watt compared to memory intensive applications in both sequential and concurrent application scenarios. Furthermore, this approach demonstrate that it is possible to continuously adapt system configuration through a per-application runtime optimization algorithm, which can improve the IPS/Watt compared to the existing approach. Runtime overheads are at least three cycles for each frequency to determine the control action.

To reduce overheads and complexity, a novel model-free runtime optimization approach with the aim of maximizing power-normalized performance considering dynamic workload variations has been proposed. This approach is the third contribution. This approach is based on workload classification. This classification is supported by analysis of data collected from a comprehensive study investigating the tradeoffs between inter-application concurrency with performance and power under different system configurations. Extensive experiments have been carried out on heterogeneous and homogeneous platforms with synthetic and standard benchmark applications to develop the control policies and validate our approach. These experiments show that workload classification into CPU-intensive and memory-intensive types provides the foundation for scalable energy minimization with low complexity.

The fourth contribution combines workload classification with model based multivariate linear regression. The first approach has been used to reduce the problem complexity, and the second approach has been used for optimization in a reduced decision space using linearregression. This approach further improves IPS/Watt significantly compared to existing approaches.

This thesis presents a new runtime governor framework which interfaces runtime management algorithms with system monitors and actuators. This tool is not tied down to the specific control algorithms presented in this thesis and therefore has much wider applications.

#### *List of publications:*

- Aalsaud, Ali, Rishad Shafik, Ashur Rafiev, Fie Xia, Sheng Yang, and Alex Yakovlev. "Power–Aware Performance Adaptation of Concurrent Applications in Heterogeneous Many-Core Systems." In Proceedings of the 2016 International Symposium on Low Power Electronics and Design, pp. 368-373. ACM, 2016.

- Aalsaud, Ali, Ashur Rafiev, Fei Xia, Rishad Shafik, and Alex Yakovlev. "Model-Free Runtime Management of Concurrent Workloads for Energy-Efficient Many-Core Heterogeneous Systems." In 2018 28th International Symposium on Power and Timing Modeling, Optimization and Simulation (PATMOS), pp. 206-213. IEEE, 2018.

- Aalsaud, Ali, Haider Alrudainv, Rishad Shafik, Fei Xia, and Alex Yakovlev. "MEMS-Based Runtime Idle Energy Minimization for Bursty Workloads in Heterogeneous Many-Core Systems." In 2018 28th International Symposium on Power and Timing Modeling, Optimization and Simulation (PATMOS), pp. 198-205. IEEE, 2018.

- 4. Aalsaud, Ali, Ashur Rafiev, Fei Xia, Rishad Shafik, and Alex Yakovlev. "Reduced-Complexity Runtime Management of Concurrent Workloads for Energy-Efficient Many-Core Systems." Journal paper under preparation.

- Gensh, Rem, Ali Aalsaud, Ashur Rafiev, Fei Xia, Alexei Iliasov, Alexander Romanovsky, and Alex Yakovlev. Experiments with odroid-xu3 board. Newcastle University, Computing Science, 2015.

#### I also contributed in the following works:

- Xia, Fei, Ashur Rafiev, Ali Aalsaud, Mohammed Al-Hayanni, James Davis, Joshua Levine, Andrey Mokhov et al. "Voltage, Throughput, Power, Reliability, and Multicore Scaling." Computer 50, no. 8 (2017): 34-45.

- 2. Rafiev, Aashur, Fei Xia, Alexei Iliasov, Rem Gensh, Ali Aalsaud, Alexander Romanovsky, and Alex Yakovlev. "Order graphs and

cross-layer parametric significance-driven modelling." In Application of Concurrency to System Design (ACSD), 2015 15th International Conference on, pp. 110-119. IEEE, 2015.

- 3. Rafiev, Ashur, F. Xia, Alexei Iliasov, Rem Gensh, Ali Aalsaud, Alexander Romanovsky, and Alexandre Yakovlev. "Selective abstraction and stochastic methods for scalable power modelling of heterogeneous systems." In Specification and Design Languages (FDL), 2016 Forum on, pp. 1-7. IEEE, 2016.

- 4. Rafiev, Ashur, Andrey Mokhov, Fei Xia, Alexei Iliasov, Rem Gensh, Ali Aalsaud, Alexander Romanovsky, and Alex Yakovlev. "Resource-Driven Modelling for Managing Model Fidelity." In Model-Implementation Fidelity in Cyber Physical System Design, pp. 25-55. Springer, Cham, 2017.

- Romanovsky, Alexander, and Alex Yakovlev. "Power-proportional modelling fidelity Ashur Rafiev, Fei Xia, Alexei Iliasov, Rem Gensh, Ali Aalsaud." (2015).

| I | Τł           | nesis Chapters                                  | 1  |

|---|--------------|-------------------------------------------------|----|

| 1 | INTRODUCTION |                                                 |    |

|   | 1.1          | Motivation                                      | 2  |

|   | 1.2          | Statement of originality                        | 4  |

|   | 1.3          | Thesis Organization                             | 5  |

| 2 | BAC          | KGROUND AND LITERATURE REVIEW                   | 7  |

|   | 2.1          | Introduction                                    | 7  |

|   | 2.2          | Power Consumption of CPU                        | 7  |

|   | 2.3          | Power management techniques                     | 8  |

|   |              | 2.3.1 Dynamic Voltage and Frequency Scaling     | 9  |

|   |              | 2.3.2 Many/multi-cores Systems                  | 10 |

|   |              | 2.3.3 Heterogeneous Many-core Systems           | 11 |

|   |              | 2.3.4 Power-aware dark silicon management       | 13 |

|   |              | 2.3.5 Workload scheduling and sharing resources | 13 |

|   | 2.4          | Literature Review                               | 14 |

|   |              | 2.4.1 Power Management Techniques During Design | 14 |

|   |              | 2.4.2 Runtime Power Management Techniques       | 17 |

| 3 | PLA          | TFORM EXPLORATION EXPERIMENTS                   | 31 |

|   | 3.1          | Introduction                                    | 31 |

|   | 3.2          | System Architecture and Platform description    | 32 |

|   |              | 3.2.1 Applications Workload                     | 33 |

|   |              | 3.2.2 Performance Counters                      | 37 |

|   | 3.3          | Characterization Experiments                    | 37 |

|   |              | 3.3.1 Dynamic voltage frequency scaling         | 38 |

|   |              | 3.3.2 CPU-power and number of active cores      | 41 |

|   |              | 3.3.3 Duty cycling with idle-wait state         | 43 |

|   |              | 3.3.4 Performance Evaluation                    | 44 |

|   | 3.4          | Summary and Conclusion                          | 44 |

| 4 | моі          | DEL-BASED RUNTIME MANAGEMENT OF CONCURRENT      |    |

|   | WORKLOADS    |                                                 | 47 |

|   | 4.1          | Introduction                                    | 47 |

|   | 4.2          | System Architecture and Applications            | 50 |

|   |              | 4.2.1 Heterogeneous System                      | 50 |

|   |              | 4.2.2 Applications Workload                     | 50 |

|   | 4.3          | Proposed Approach                               | 51 |

|   |              | 4.3.1 Modeling Power/Performance Tradeoffs      | 51 |

|   |              | 4.3.2 Modelling offline and online              | 65 |

|    |                                               | 4.3.3 Runtime Adaptation                        | 65  |

|----|-----------------------------------------------|-------------------------------------------------|-----|

|    | 4.4                                           | Experiment Results                              | 67  |

|    | 4.5                                           | Summary and Conclusion                          | 70  |

| 5  | 5 MODEL-FREE RUNTIME MANAGEMENT OF CONCURRENT |                                                 |     |

|    | WO                                            | RKLOADS                                         | 71  |

|    | 5.1                                           | Introduction and Motivation                     | 71  |

|    | 5.2                                           | Experimental Platform And Applications          | 74  |

|    | 5.3                                           | Workload Classification Taxonomy                | 76  |

|    | 5.4                                           | Runtime Management Method And Governor Design . | 77  |

|    |                                               | 5.4.1 Workload classification                   | 79  |

|    |                                               | 5.4.2 Control decision making                   | 83  |

|    |                                               | 5.4.3 runtime management (RTM) govenor design   | 87  |

|    | 5.5                                           | Experimental Results                            | 87  |

|    |                                               | 5.5.1 A Case Study of Concurrent Applications   | 87  |

|    |                                               | 5.5.2 Per-interval Re-classification            | 90  |

|    |                                               | 5.5.3 RTM stability, tobustness and complexity  | 95  |

|    |                                               | 5.5.4 Comparative evaluation of the RTM         | 95  |

|    | 5.6                                           | Summary and Conclusion                          | 97  |

| 6  | RED                                           | DUCED-COMPLEXITY RUNTIME MANAGEMENT OF CON-     | -   |

|    | CUR                                           | RRENT WORKLOADS                                 | 98  |

|    | 6.1                                           | Introduction                                    | 98  |

|    | 6.2                                           | State space analysis                            | 99  |

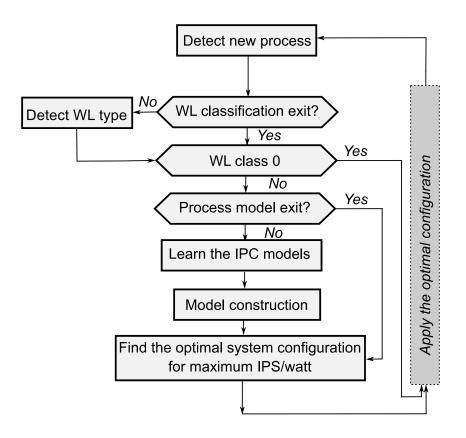

|    | 6.3                                           | Proposed Methodology                            | 99  |

|    | 6.4                                           | Power and Performance Related Models            | 101 |

|    | 6.5                                           | RTM Workload Classifications                    | 102 |

|    | 6.6                                           | Low-Complexity runtime                          | 102 |

|    | 6.7                                           | Proposed RunTime results                        | 104 |

|    | 6.8                                           | Summary and Conclusion                          | 105 |

| 7  | CON                                           | NCLUSIONS AND FUTURE WORK                       | 106 |

|    | 7.1                                           | Summary and Conclusion                          | 106 |

|    | 7.2                                           | Future Work                                     | 108 |

| 11 | Τł                                            | nesis Appendices                                | 109 |

|    | Tł                                            | nesis Bibliography                              | 126 |

| BI | BIBLIOGRAPHY 12                               |                                                 |     |

## LIST OF FIGURES

| Figure 1.1  | Processing element number is projected to scale    |    |

|-------------|----------------------------------------------------|----|

|             | exponentially according to ITRS [91]               | 2  |

| Figure 1.2  | Power trends until 2020 (Source: International     |    |

|             | Technology Roadmap for Semiconductors [92].        | 3  |

| Figure 1.3  | Thesis organization.                               | 6  |

| Figure 2.1  | Transister integration capacity [15]               | 8  |

| Figure 2.2  | Approaches To Power Management                     | 9  |

| Figure 2.3  | dynamic voltage frequency scaling with two         |    |

|             | voltage supply $[57]$                              | 9  |

| Figure 2.4  | A single-core microprocessor that runs at a lower  |    |

|             | clock speed can be made to operate at lower en-    |    |

|             | ergy per operation. Two single-core processors     |    |

|             | can be run in parallel to recover the overall sys- |    |

|             | tem performance [45]                               | 11 |

| Figure 2.5  | CPU-Power consumption relationship with num-       |    |

|             | ber of active cores [106]                          | 12 |

| Figure 2.6  | Flow of patterning, mapping, prediction (pmp) [37] | 13 |

| Figure 2.7  | Examples of thread-to-core mapping in chip-        |    |

|             | multiprocessor (CMP) configurations [132]          | 14 |

| Figure 2.8  | Three-layer power control architecture for a 16-   |    |

| C           | core chip multiprocessor [68]                      | 16 |

| Figure 2.9  | Proposed architecture of power delivery network    |    |

|             | (PDN) to support dynamic voltage scaling. The      |    |

|             | output voltage of each VRM is fixed [7]            | 17 |

| Figure 2.10 | Three power-supply configurations for a 4-core     |    |

|             | CMP [54]                                           | 18 |

| Figure 2.11 | A taxonomy of runtime power management tech-       |    |

|             | niques.                                            | 19 |

| Figure 2.12 | Block diagram of the proposed energy minimiza-     |    |

|             | tion approach [128]                                | 20 |

| Figure 2.13 | Proposed energy minimization approach [93] .       | 20 |

| Figure 2.14 | Agent-environment interaction Model                | 26 |

| Figure 2.15 | Overall flow of power management based on          |    |

| -           | multilevel reinforcement based learning [76]       | 27 |

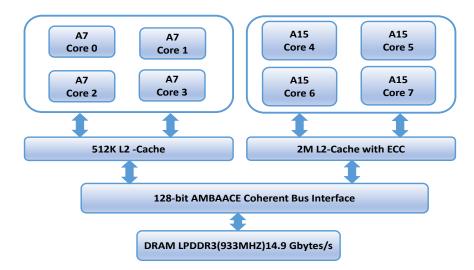

| Figure 3.1  | Exynos 5422 block diagram [2]                      | 33 |

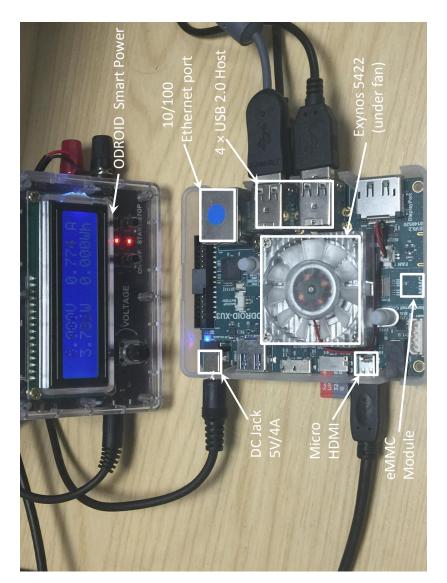

| Figure 3.2  | Exynos 5422 system set.                            | 34 |

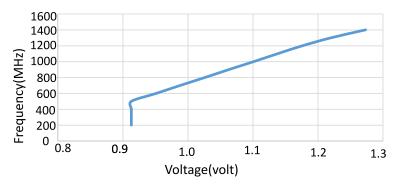

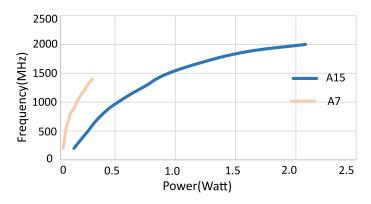

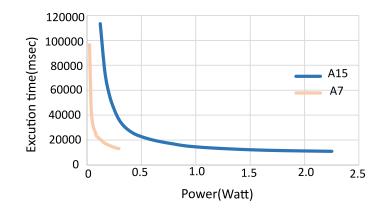

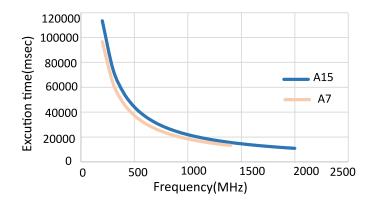

| Figure 3.3  | Cortex-A7 voltage-frequency characteristic         | 38 |

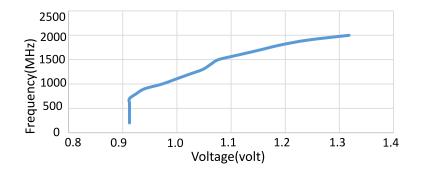

| Figure 3.4  | Cortex-A15 voltage-frequency characteristic        | 39 |

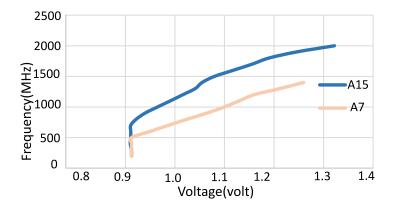

| Figure 3.5  | Cortex-A7 and Cortex-A15 voltage-frequency         |    |

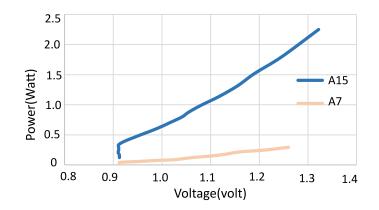

|             | characteristic under 100% workload                 | 39 |

| Figure 3.6  | Cortex-A7 and Cortex-A15 voltage–power char-<br>acteristic under 100% workload      | 40       |

|-------------|-------------------------------------------------------------------------------------|----------|

| Figure 3.7  | Cortex-A7 and Cortex-A15 power-frequency char-                                      | 40       |

|             | acteristic under 100% workload                                                      | 40       |

| Figure 3.8  | Cortex-A7 and Cortex-A15 power-execution time                                       |          |

|             | characteristic under 100% workload                                                  | 41       |

| Figure 3.9  | Cortex-A7 and Cortex-A15 frequency-execution                                        |          |

|             | time characteristic under 100% workload                                             | 41       |

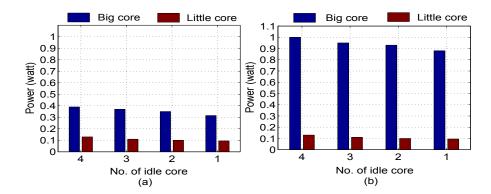

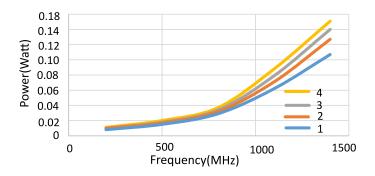

| Figure 3.10 | Experimental measurements of idle power by                                          |          |

|             | adopting Odroid-XU3 big.LITTLE platform (a)                                         |          |

|             | 1400MHz big.LITTLE; (b) 2000MHz big, 1400MHz                                        |          |

|             | LITTLE at 1400 MHz to 1 Watt at 2000 MHz                                            | 42       |

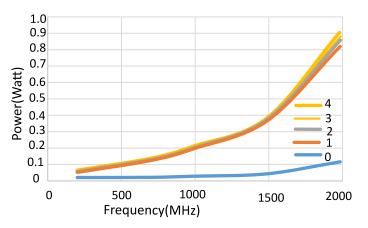

| Figure 3.11 | Power consumption of A7 domain with different                                       |          |

| 0           | number of active cores.                                                             | 42       |

| Figure 3.12 | Power consumption of A15 domain with differ-                                        |          |

| 0           | ent number of active cores.                                                         | 42       |

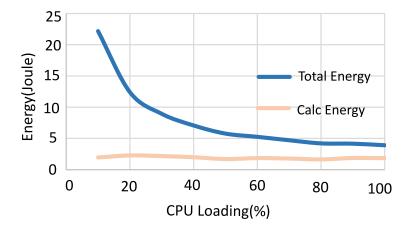

| Figure 3.13 | Dependence of total energy and calculation en-                                      |          |

| 0 9 9       | ergy on A7 CPU loading                                                              | 43       |

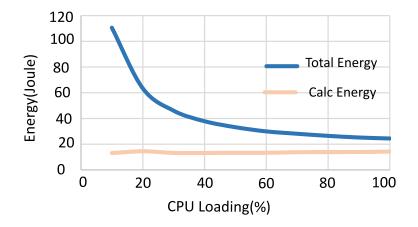

| Figure 3.14 | Dependence of total energy and calculation en-                                      |          |

| 0 9 1       | ergy on A15 CPU loading                                                             | 44       |

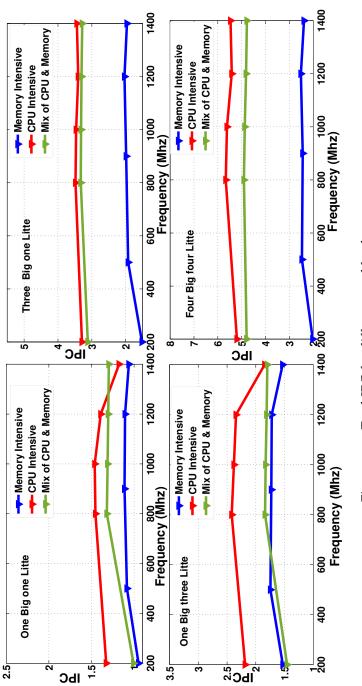

| Figure 3.15 | Total IPC for different workloads types                                             | 45       |

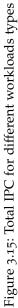

| Figure 4.1  | Total power for <i>ferret</i> and <i>bodytrack</i> applications                     |          |

|             | at 200 MHz and 1400 MHz frequencies.                                                | 53       |

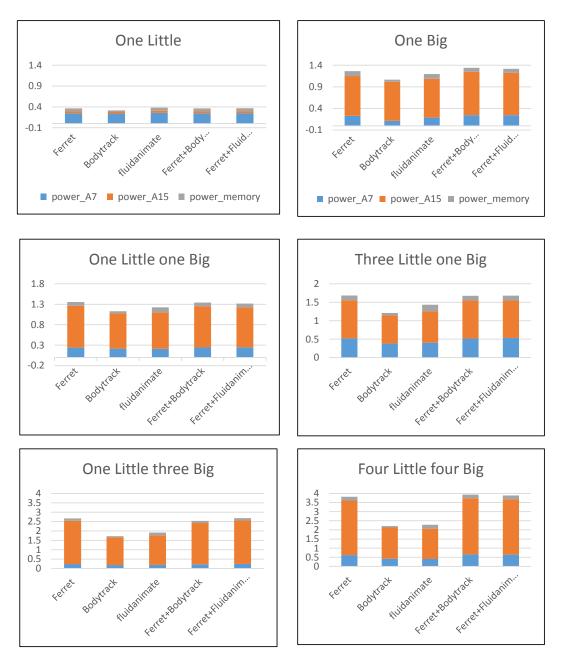

| Figure 4.2  | Total power for single and concurrent applica-                                      | <u> </u> |

| 1 iguie 4.2 | tions in different configuration running at 1400                                    |          |

|             | MHz                                                                                 | 54       |

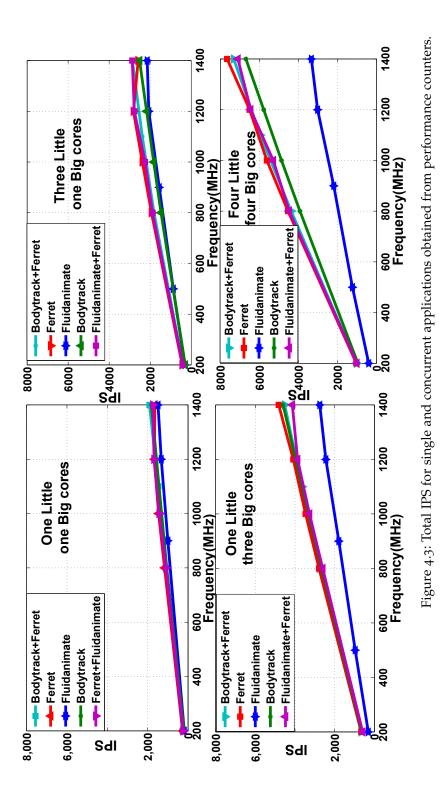

| Figure 4.3  | Total IPS for single and concurrent applications                                    | 94       |

| inguie 4.9  | obtained from performance counters                                                  | 58       |

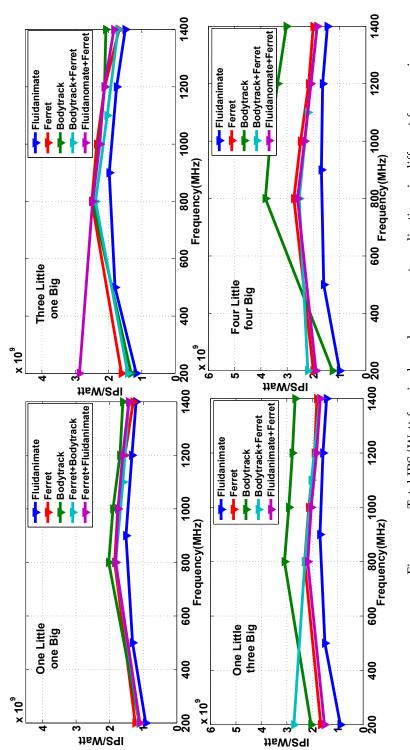

| Figure 4.4  | Total IPS/Watt for single and concurrent appli-                                     | 50       |

| 1 iguit 4.4 | cations in different frequencies.                                                   | 62       |

| Figure 4.5  | Total power normalized performance for differ-                                      | 02       |

| rigure 4.5  | ent core-allocations at 1400 MHz for <i>bodytrack</i> ,                             |          |

|             | ferret and bodytrack+ferret applications                                            | 62       |

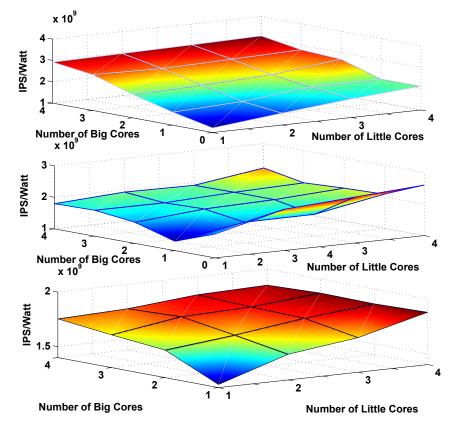

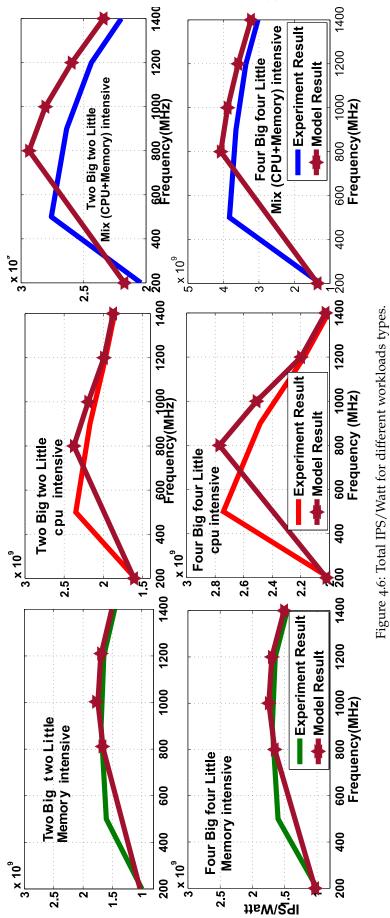

| Figure 4.6  | Total IPS/Watt for different workloads types.                                       | 63       |

| Figure 4.7  | Flowchart of the proposed runtime adaptation                                        | 64       |

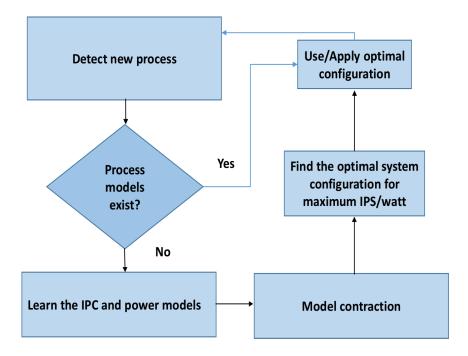

| rigure 4.7  | cycle                                                                               | 66       |

| Figuro 48   | Comparative IPS/Watt between the proposed                                           | 00       |

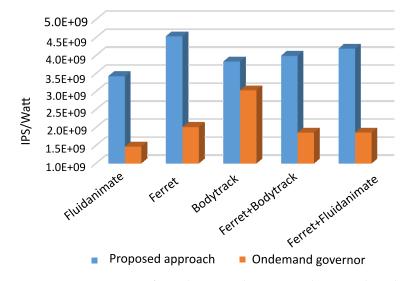

| Figure 4.8  |                                                                                     |          |

|             | approach and ondemand governor [75] with all 8 cores allocated to the applications. | 68       |

| Figure 4.0  |                                                                                     | 00       |

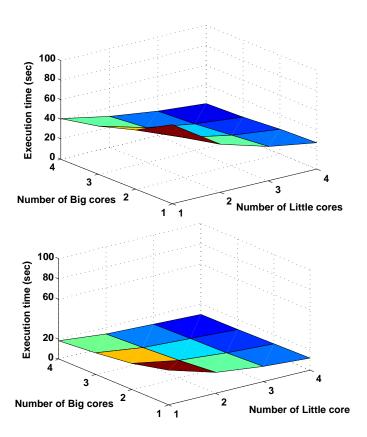

| Figure 4.9  | The execution time for different core allocation                                    |          |

|             | at 600 MHz and 1400 MHz respectively for <i>ferret</i>                              | 6        |

| Tionen      | application.                                                                        | 69       |

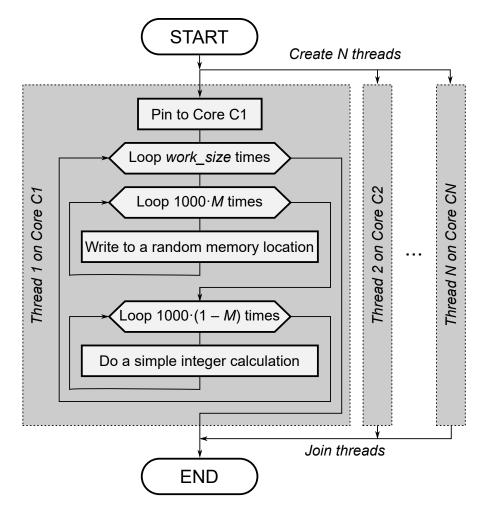

| Figure 5.1  | Flowchart of <i>mthreads</i> synthetic benchmark. M                                 |          |

| Tiouro      | and N are controlled parameters                                                     | 77       |

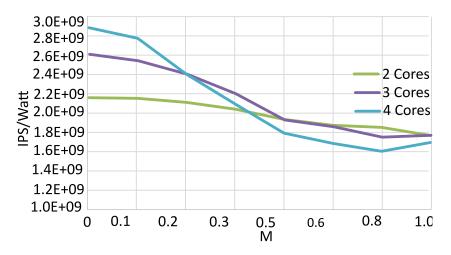

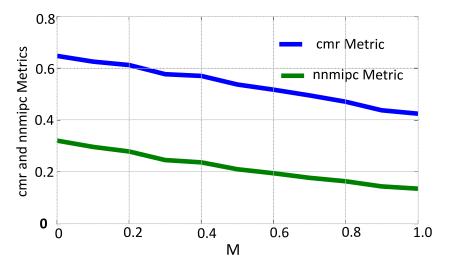

| Figure 5.2  | IPS/Watt for different memory use rates ( $0 \leq M \leq 1$ )                       | _0       |

|             | $M \leqslant 1$ )                                                                   | 78       |

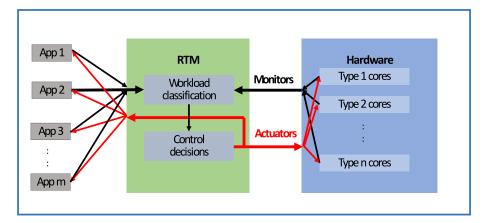

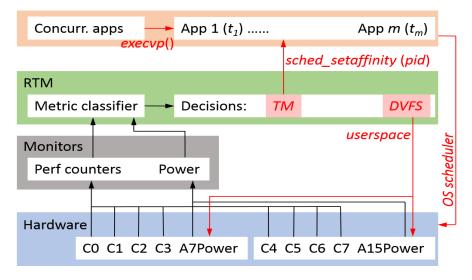

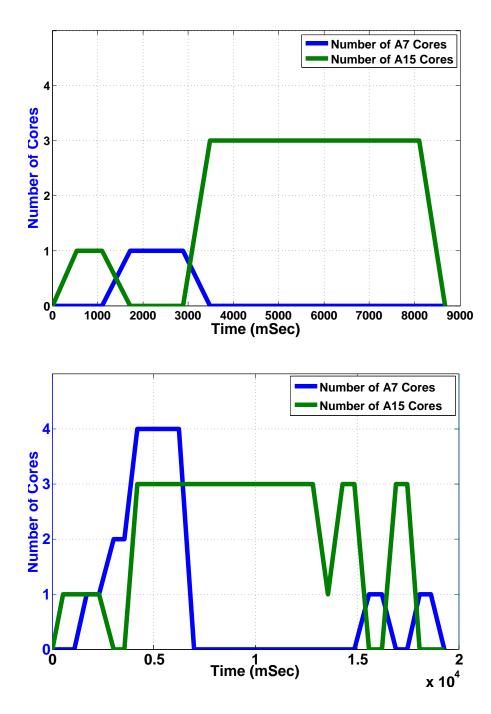

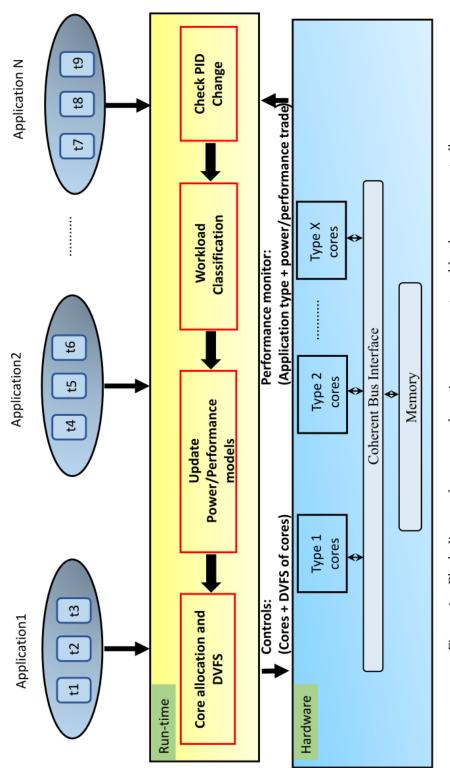

| Figure 5.3  | RTM architecture showing two-way interactions                      |     |

|-------------|--------------------------------------------------------------------|-----|

|             | between concurrent applications and hardware                       |     |

|             | cores                                                              | 78  |

| Figure 5.4  | mthreads and their Performance Counter Metrics                     |     |

|             | on Hetrogenous Many-core Systems                                   | 80  |

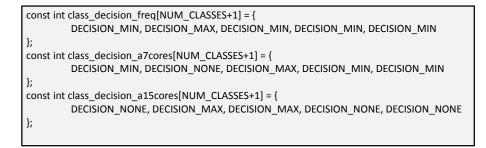

| Figure 5.5  | Code implementing Table 4                                          | 85  |

| Figure 5.6  | Governor implementation based on RTM                               | 87  |

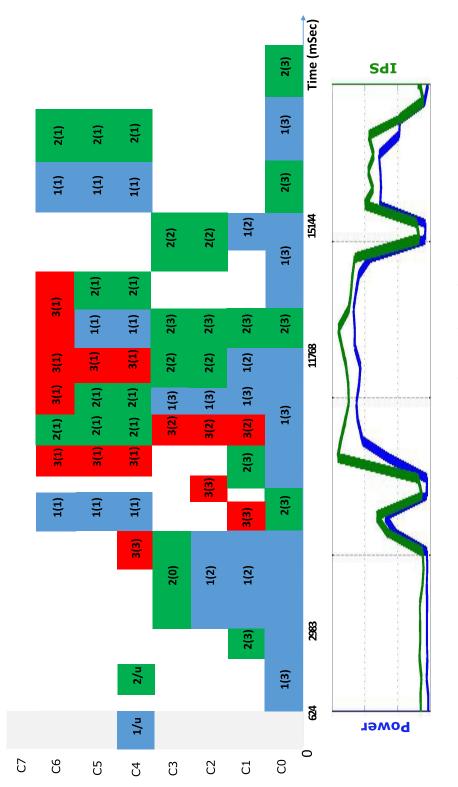

| Figure 5.7  | Execution trace with task mapping (TM) and                         |     |

|             | dynamic voltage frequency scaling (DVFS) de-                       |     |

|             | cisions                                                            | 91  |

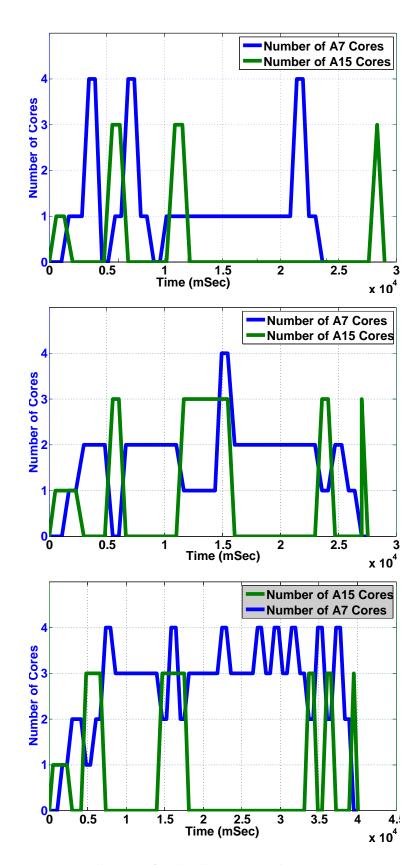

| Figure 5.8  | Core allocation for Fluidanimate application,                      |     |

|             | Two Memory concurrent applications , Three                         |     |

|             | Memory concurrent applications                                     | 92  |

| Figure 5.9  | Core allocation for Ferret application, Two CPU                    |     |

|             | concurrent applications                                            | 93  |

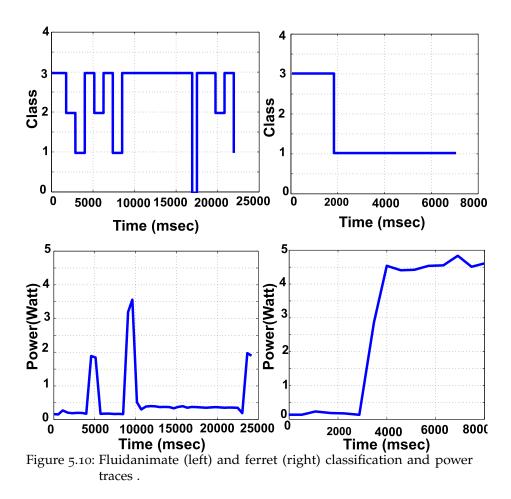

| Figure 5.10 | Fluidanimate (left) and ferret (right) classifica-                 |     |

|             | tion and power traces                                              | 94  |

| Figure 6.1  | Block diagram for proposed runtime concurrent                      |     |

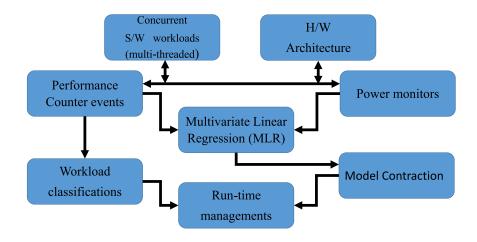

|             | workloads power controller                                         | 100 |

| Figure 6.2  | Simplified overview of proposed methodology.                       | 101 |

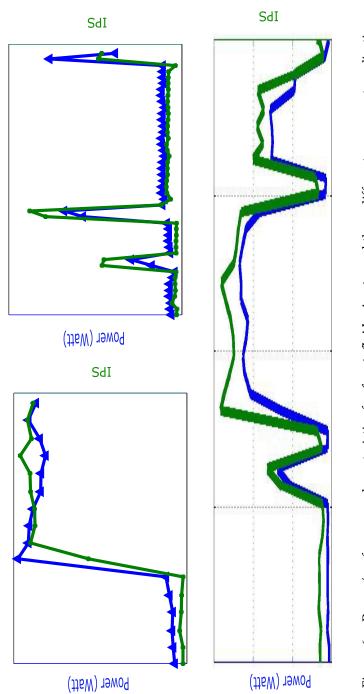

| Figure 6.3  | Power/performance characteristics for <i>ferret</i> , <i>flu</i> - |     |

|             | <i>idanimate</i> , and three different concurrent appli-           |     |

|             | cations                                                            | 103 |

| Figure 6.4  | Simulation flow to obtain the results                              | 104 |

## LIST OF TABLES

| Table 2.1 | Features and limitations of the supervised model-      |      |

|-----------|--------------------------------------------------------|------|

|           | based learning techniques approaches                   | 22   |

| Table 2.2 | Features and limitations of the supervised classificat | ion- |

|           | based and model-based learning techniques ap-          |      |

|           | proaches                                               | 25   |

| Table 2.3 | Features and limitations of the existing approaches    |      |

|           | of the model based Reinforcement learning (RL).        | 28   |

| Table 2.4 | Features and limitations of the existing model-        |      |

|           | free reinforcement approaches.                         | 30   |

| Table 3.1 | Qualitative summary of the inherent key char-          |      |

|           | acteristics of PARSEC benchmarks [10]                  | 36   |

| Table 3.2 | Performance Counter Events                             | 37   |

| Table 4.1 | Features and limitations of the existing approaches.   | 48   |

| Table 4.2 | Single Application Power Models.                       | 55   |

| Table 4.3 | Concurrent Application Power Models                    | 55   |

| Table 4.4 | Single Application Performance Models                  | 59   |

| Table 4.5  | Concurrent Application Performance Models         | 59 |

|------------|---------------------------------------------------|----|

| Table 5.1  | Features of existing approachs and this work      | 73 |

| Table 5.2  | Performance counter events                        | 75 |

| Table 5.3  | Metrics used to derive classification             | 79 |

| Table 5.4  | PARSEC applications and their performance counter |    |

|            | metrics on hetrogenous many-core systems          | 82 |

| Table 5.5  | PARSEC applications and their performance counter |    |

|            | metrics on Intel Core i7 Sandybridge CPU          | 82 |

| Table 5.6  | Classification details                            | 83 |

| Table 5.7  | RTM control decisions.                            | 84 |

| Table 5.8  | The Power, Frequency, Number of Cores, Classi-    |    |

|            | fication results for <i>ferret</i> Application    | 89 |

| Table 5.9  | Percentage IPS/WATT improvements of the RTM       |    |

|            | ovber the LINUX ONDEMAND Governor                 | 97 |

| Table 5.10 | Comparison of performance in terms of IPS of      |    |

|            | the proposed RTM with the LINUX ONDEMAND          |    |

|            | Governor.                                         | 97 |

| Table 6.1  | Nnmber of possible core allocations               | 99 |

| Table 6.2  | Percentage IPS/WATT Improvements of the RTM       |    |

|            | over the LINUX Ondemand Governor 1                | 05 |

|            |                                                   |    |

#### LIST OF ALGORITHMS

| 4.1 | Runtime system adaptation algorithm to generate maximum IPS/Watt. | 65 |

|-----|-------------------------------------------------------------------|----|

| 2   | Inside the RTM cycle                                              | -  |

## ACRONYMS

- OL offline

- RT runtime

- TM task mapping

- WLC workload classification

- **OS** operating system dark silicon management (DaSiM)

- DRAM Dynamic random-access memory

- **DVS** Dynamic voltage scaling

- DFS dynamic frequency scaling

- DCT dynamic concurrency throttling

- CMP chip-multiprocessor

- CMPs chip-multiprocessors

- CMOS complementary metal-oxide-semiconductor

- P polynomial

- NP non-polynomial

- SMDP semi-Markov decision process

- DaSiM dark silicon management

- LR linear regression

- DPM dynamic power management

- **DSP** Digital signal processing

- **DVFS** dynamic voltage frequency scaling

- **RL** Reinforcement learning

- TD temporal difference

- **RTM** runtime management

- **OH** overheads

- FPGA field-programmable gate array

- **MDP** Markov Decision Process

- GPU graphics processing unit

- LPM local power manager

- GPM global power manager

- MRPI Memory Reads Per Instruction linear programming (LP)

- LP linear programming

- **ITRS** international technology roadmap for semiconductors

- **PDN** power delivery network

- SoC system-on-chip

## Part I

# Thesis Chapters

#### 1.1 MOTIVATION

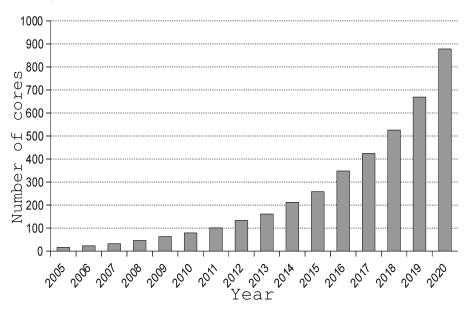

In the last four decades, contemporary computing systems, including embedded and high performance systems, are exhibiting increased complexities in two dimensions. In one dimension, the number and type of computing resources (cores) are growing in hardware platforms, and in the other, an increasing diversity of applications are being executed concurrently on these platforms [17, 81, 125]. In terms of system architecture, an important trend is to increase the number and type of cores on a chip while reducing their individual complexity. Figure 1.1 is from the international technology roadmap for semiconductors (ITRS) which expects that the overall number of cores that can be placed in a single chip will dramatically grow with technology scaling [91].

Figure 1.1: Processing element number is projected to scale exponentially according to ITRS [91].

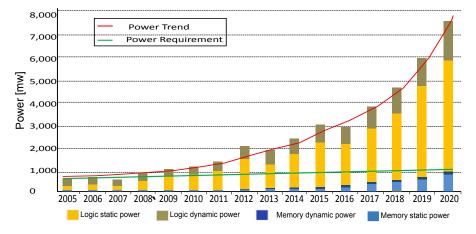

In the last decades, the clock frequencies of CPU have increased rapidly to meet growing performance needs [70]. Despite the rapidly increase in the recent technology scaling [15], the speed of transistor may not increase at the historic rate due to threshold leakage current, and supply voltage scaling described by Moore's Law [73, 94]. This results in power consumption not scaling with technology feature size reduction [85]. Moreover, according to the ITRS, by the year

2020, the semiconductor technology will see a consistent rise in chip power consumption as opposed to requirement as can be seen in Figure 1.2 [92]. Consequently, power and energy consumption has become a limiting factor to continued technology scaling and performance improvements.

Figure 1.2: Power trends until 2020 (Source: International Technology Roadmap for Semiconductors [92].

In terms of executing multiple applications, parallelization has been used to maintain a reasonable balance between energy consumption and performance in computing platforms [35].

On the other hand, managing hardware resources, to achieve energy efficiency, under different application scenarios (single or concurrent) is proving highly challenging due to runtime state-space expansion [14]. This has led to techniques for mitigating power consumption and performance degradation concerns. Power-aware platform design techniques including many-core architectures with the provision for dynamic task mapping and dynamic voltage frequency scaling (DVFS) have been the preferred tools for system designers over the years [79, 125].

Existing approaches for energy efficiency can be categorized into two types: offline (OL) and runtime (RT). In OL approaches, the system is extensively reasoned to derive energy and performance models [78, 4]. In RT approaches, the models are typically learnt using monitored information [128, 117]. Since RT modelling is costly in terms of resources, often OL and RT are complementarily coupled [4].

Modern applications exercise underline hardware in different ways, generating varying tradeoffs between power and performance. For example, CPU intensive applications tend to have higher computing workloads with less memory band-width. On the other hand memory intensive applications typically exercise higher memory bandwidth with low CPU workloads [111]. When these applications run concurrently the workloads generated by the hardware may vary significantly

compare to that of a single application. Hence, energy efficiency cannot be automatically guaranteed using the existing approaches that are agnostic of concurrent application workloads and behaviours [4].

This thesis opens a new research trend in the development of new framework design to dynamically select the number and type of cores with their frequencies for single and concurrent applications in heterogeneous many-core systems in order to improve energy efficiency. To achieve that we present new models, techniques and architectures.

#### **1.2 STATEMENT OF ORIGINALITY**

The major contributions of this thesis can be summarized as follows:

- A comprehensive literature study of power management techniques for many-core systems is presented. This study analyzes the advantages, disadvantages and limitations of the previous techniques of power management. The conclusions from this study can form a basis for any research aiming to utilize these management techniques' advantages and addressing their challenges.

- Experiments with the Odroid-XU<sub>3</sub> platform were carried out in order to examine the power management of heterogeneous systems using directly measured values from the performance counters and built-in monitors, these experiments include managing the number of big cores, number of LITTLE cores, different core allocation, and the operating frequencies as a function of workload type. Furthermore, other experiments were carried out to investigate the impact of the CPU duty cycle with idle-wait state power, and controlling the number of active cores on the CPU performance and power tradeoffs [30].

- Developing a new performance counter for measuring the onchip power consumption and performance caused by executing single and concurrent applications on heterogeneous many core systems. This performance counter can monitor system performance events (e.g. cache misses, cycles, instruction retired) and capturing the voltage, current, power, and temperature directly from the sensors of hardware platforms.

- Propose model-based runtime optimization approach for concurrent applications, practically implemented and demonstrated on a heterogeneous many-core system. Multivariate linear regression (MLR) is used to model power and performance tradeoffs expressed as IPS/Watt, determine the optimal system configuration (i.e. the number of parallel threads, their core allocations and operating frequencies) tailored for each kind of workload,

and maximize IPS/Watt for single and concurrent application scenarios using low-cost runtime adaptation algorithm [4].

- Propose a low-complexity, model-free and low-cost runtime approach for synergistic controls of dynamic voltage frequency scaling (DVFS) and task mapping (TM). Fundamental to this approach is an empirical and data-driven method, which classifies applications based on their memory and CPU requirements. The objective is to derive DVFS and TM policies, tailored to the classified workloads without requiring any explicit modelling at runtime. Due to simplified runtime classification, our approach can significantly reduce overheads. Furthermore, the model-free classification approach based RT enhances scalability for any concurrent application mix, platform, and metric having linear complexity which is not affected by the system heterogeneity, and the number of concurrent applications [6].

- To reduce overhead and complexity, workload classification is combined with model-based (multivariate linear regression technique) in a novel low-complexity runtime optimization approach with the aim of achieving maximized energy efficiency considering dynamic variations of workload and application scenarios.

- Implement the new approach for low-complexity runtime power adaptation as a Linux power governor to determine the hardware configuration knobs, such as the number and type of cores with their frequencies tailored to the workload type and application scenario. Validate this governor through extensive experimentation to demonstrate significant IPS/Watt improvements.

#### 1.3 THESIS ORGANIZATION

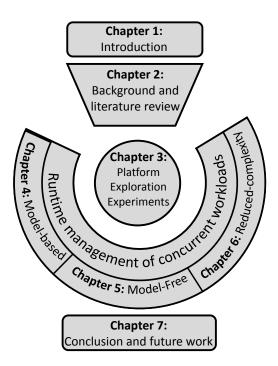

This thesis is organized into seven chapters, as shown in Figure 1.3.

Chapter 1 "Introduction": introduces the motivations, objectives, contributions and structure of this thesis.

Chapter 2 "Background and Literature Review": provides background information and summarizes the literature on topics relevant to this thesis. In addition, the emerging on-chip interconnects included in recent literature is reviewed and discussed in details.

Chapter 3 "Platform Exploration Experiments": presents several experiments with the Ordoid-XU3 board to reveal the impact of parallelism in different types of heterogeneous cores on performance, power consumption and idle power efficiency.

Chapter 4 "Model-based Runtime Management of Concurrent Workloads": proposes the novel runtime optimization approach for concurrent applications, practically implemented and demonstrated on a heterogeneous many-core system by using MLR to model power and performance tradeoffs expressed as IPS/Watt.

Figure 1.3: Thesis organization.

Chapter 5 "Model-free Runtime Management of Concurrent Workloads": proposes an runtime adaptation approach to improve the energy efficiency of a heterogeneous many-core system with concurrent workloads by using workload classification (WLC) techniques to derive DVFS and TM policies, tailored to the classified workloads.

Chapter 6 "Reduced-Complexity Runtime Management of Concurrent Workloads" develops the model-based runtime optimization approach by using the workload classification technique to reduce state-space size of the many-core heterogeneous system . Includes all possible core allocations and all possible DVFS combinations.

Chapter 7 "Conclusions and Future Work" summarizes the contributions of the thesis, discusses the implications of the presented research and draws the horizon for potential future work.

#### BACKGROUND AND LITERATURE REVIEW

This chapter presents the fundamental concepts involved in this thesis and gives a review of the existing work. The remainder of this chapter is organised as follows. Section 2.2 presents the principle of power consumption of complementary metal-oxide-semiconductor (CMOS) circuits of multiprocessors system on chip and Section 2.3 introduces the power management techniques which include dynamic voltage frequency scaling, many/multi-core architecture, heterogeneity of many core systems, dark silicon and workload scheduling. Finally, Section 2.4 gives an overview of the proposed techniques in the previous work relevant to the presented research.

#### 2.1 INTRODUCTION

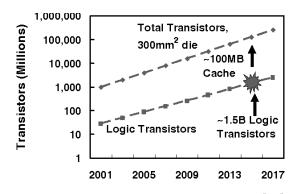

Over the last four decades, progress in information technology has changed every aspect of our lives - the ways we think, work, communicate, commute, and entertain ourselves. Modern computing systems, and especially mobile and embedded systems have had an enormous effect on our lives, including in areas such as the internet to consumer electronics, transporting, healthcare and manufacturing. However, these computing systems involve a performance-energy trade off as the current size of transistors is scaled down further [55]. This has led many researchers to investigate techniques to mitigate power consumption and performance degradation concerns. Such techniques include: power gating, dynamic voltage frequency scaling, emerging devices, and many-core architectures. The many-core technique has emerged as a consequence of recent advances in the integration density of transistors on a single chip, which has been achieved through the use of modern semiconductor processes [55]. However, despite the rapid recent increase in technology scaling [15], the speed of transistors may not increase at the historic rate due to threshold leakage current, with the supply voltage being scaled down, as shown in Figure 2.1.

#### 2.2 POWER CONSUMPTION OF CPU

The dynamic power consumption and the static power consumption are the two components of the power consumption in CMOS processors as can be seen in (2.1)

$$P_{total} = P_{dynamic} + P_{static}$$

(2.1)

Figure 2.1: Transister integration capacity [15].

where P<sub>dynamic</sub> is the dynamic power consumption due to charging and discharging activities of load capacitance whenever the CMOS circuit is running a useful application i.e active operation, and P<sub>static</sub> is the static power consumption due to several sources such as gate leakage and sub-threshold leakage whenever the CMOS circuits are not running useful computation i.e. idle mode [52][19].

Due to continued technology scaling the static power consumption is now a significant source of power consumption even in operation mode. The total power consumption (static and dynamic power) has to be optimized instead of simple dynamic power reduction. Design techniques exploration of the power consumption optimization need to work in a large dimension search space [46]. We discuss these in the subsections that follow.

#### 2.3 POWER MANAGEMENT TECHNIQUES

Over the past decades, advances in chip fabrication has continued at a steady stride and have yielded substantial improvements in the power efficiency of CMOS chips. Power and energy always had a significant impact on processor design. However, a few recent studies propose power control algorithms for many-core architectures [34]. A number of power management techniques for many- and multiple-core processors have been proposed and these techniques can be classified into two approaches: power management during design time and power management at runtime, as can be seen in Figure 2.2. These two approaches, including sets of hardware and software techniques, have been used to reduce the power consumption while meeting system performance requirements.

In this chapter, many techniques for the management of power consumption are discussed, such as dynamic voltage frequency scaling, CPU-power and number of active cores, power-aware dark silicon management, and workload scheduling plus sharing resources.

Figure 2.2: Approaches To Power Management

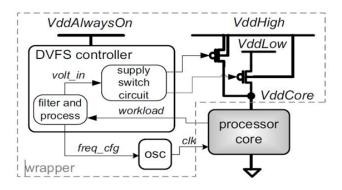

#### 2.3.1 Dynamic Voltage and Frequency Scaling

Many studies have recently been conducted aiming to reduce the power consumption of many-core processors based on various techniques. These techniques include varying the clock frequency, and supply voltage correspondingly while a task is being processed, called dynamic voltage frequency scaling (DVFS) control [39, 58, 53, 31], this technique was introduced in the 1990's. DVFS is able to help decrease the power dissipation of CMOS circuits by reducing the supply voltage and/or frequency as shown in the equation below:

$$P_{dynamic} = \alpha C_{switched} f V^2$$

(2.2)

where  $\alpha$  is the switching probability or activity,  $C_{switched}$  represents the effective switched capacitance of the transistor gates, f is the operating clock frequency, and V is the supply voltage [50, 57]. This equation shows that the  $P_{dynamic}$  is proportional to the product of the operating frequency and the square of supply voltage. DVFS is a hardware power minimization technique which has been developed for embedded systems where the frequency and supply voltage are dynamically changed depending on the workload variation.

Figure 2.3: dynamic voltage frequency scaling with two voltage supply [57]

For instance, LeSueur et al. [57] circuits designed for dynamic voltage frequency scaling using two individual power supply voltages of 1.3 v and 0.8 v on a nine core processor as shown in Figure 2.3 and this technique resulted in an average energy 52% of the original energy on a JPEG application.

DVFS may be controlled at the system software level. For instance, DVFS is controlled in Linux with power governors [14], such as ondemand, performance, conservative, userspace and powersave. These governors use DVFS control to manage system power according to the knowledge and prediction of workload and user preference. Current Linux governors are, however, not able to optimize energy consumption, primarily because they select only either the maximum or minimum frequency depending on whether the workload is higher or lower than a given threshold [14]. This coarse-grain approach is not capable of taking advantage of the different degrees of parallelizability of applications and producing the most efficient scheduling.

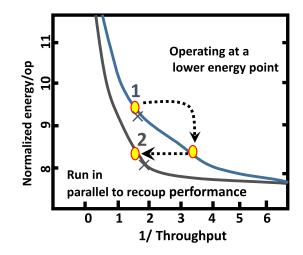

#### 2.3.2 Many/multi-cores Systems

In 1971, while microprocessors have been invented, performance enhancements from one era of processors to the following have been ruled via Pollack's regulation [15]. This states that the improvements in performance of the microprocessors is proportional to the square root of complexity (or area, assuming that the implementation makes use of the same CMOS technology). For instance, a dual-small core microprocessor can provide a performance improvement of 70-80 %, as compared to only 40% from a large monolithic core [15]. Each core is designed to run at a slower clock speed in order to reduce its energy per operation [45], while overall system performance can be recovered by operating both of the processors in parallel, as shown in Figure 2.4.

Despite the fact that, due to the generation scaling driven by Moore's law, a multi/many-core processor layout possibility has emerged which overcomes Pollack's regulation. This is because the use of multiple processors can offer close to-linear overall performance enhancement.

As the power consumption issue is becoming exacerbated with the newer micro-architecture design of microprocessors, parallel-computing has become widely employed in microprocessors. Therefore the multi/manycores systems can be considered for solving these problems:

- 1. Saving the power consumption can be possible by turning on or off for each core.

- It is possible to operate each core separately in reliable region (optimized voltage and clock frequency) depending on power budget.

Figure 2.4: A single-core microprocessor that runs at a lower clock speed can be made to operate at lower energy per operation. Two single-core processors can be run in parallel to recover the overall system performance [45].

- 3. It is possible to distribute the heat across the die by distributing the application workloads among processor cores.

- Establishing many core system which able to decide how and when to control the dynamic reconfiguration of processing cores with application needs.

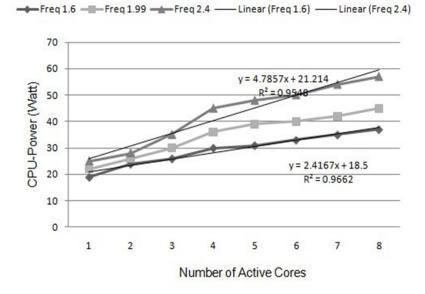

The connection between core-power and number of cores has been studied to calculate the power dissipation in many-cores systems. For example, Intel Xeon CPU E5540 processors are used to investigate the relationship between processor power and number of active cores, as can be seen in Figure 2.5 which has a linear trend line [106].

#### 2.3.3 Heterogeneous Many-core Systems

Advanced embedded systems such us mobile devises have enjoyed dramatic growth over the last decades, and their functionality has increased at a similar rate as they enable more immersive experiences. The expectations for more powerful features, greater flexibility, and high-performance are increasing dramatically [112].

Low power techniques have been used from clock power gating through dynamic voltage/frequency scaling, then the many cores which have been explained in previous sections. And most recently heterogeneous processing technology allows the use of multiple types of cores. There are many types of heterogeneity as shown below [88, 99]:

- 1. using different types of cores

- a) different types of CPU (such as ARM big.LITTLE)

Figure 2.5: CPU-Power consumption relationship with number of active cores [106].

- b) integrating graphics processing unit (GPU) with CPU

- c) using specific types of programmable core such as accelerators

- different types of hierarchies

- 3. using different types of software ( operating system (OS), tools,...)

ARM big.LITTLE is the latest in a series of innovations, that have allowed high improvements in embedded system performance within a constant power budget [23]. LITTLE refers to smaller high efficiency core on the system-on-chip (SoC) which has been used to low performance applications for example, e-mail, web browsing, etc. While big refers to bigger higher performance cores which have been used for high performance applications for example, gaming, multimedia, etc. These cores are connected by a coherent interconnect, rustling in an embedded system [1]. In such many core systems the big cores can produce peak performance, and the little cores can consume minimal power. To ensure that tasks are paired dynamically to the appropriate core type, the OS must be aware of the performance requirement for each application type. Global task mapping software adjusts the kernel scheduler to be aware of the performance requirements for each thread. As performance changes the tasks are switched between the big and LITTLE cores to maintain the most efficient performance. Global task scheduling provides the most flexibility for tuning the performance and power balance in an SoC [131]. With the efforts being

no more complex and for a standard DVFS based system. The other types of heterogeneity are out of scope of this thesis.

#### 2.3.4 Power-aware dark silicon management

In recent years, the dark silicon power management technique has been widely used in many-core systems. The dark silicon indicates that for a fixed power budget, only finite numbers of cores can be powered on (operating at high performance) in the reliable region while others remain unpowered (dark).

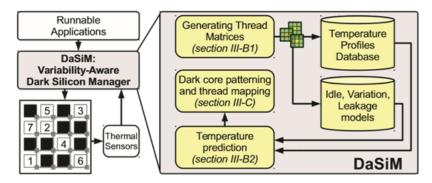

Shafique et al. [37] presented the basic flow of connections between the various elements of the dark silicon management (DaSiM) technique as can be seen in Figure 2.6. This technique is based on two concepts.

Figure 2.6: Flow of patterning, mapping, prediction (pmp) [37]

At first runtime application mapping and the dark cores technique is used to establish the power control of cores. Secondly, temperature prediction (section III-B2 in Figure 2.6) is used to establish the thermal matrix for each thread. A Gem 5 [11] simulator with McPAT [63] has been used in the experimental setup to demonstrate this technique.

#### 2.3.5 Workload scheduling and sharing resources

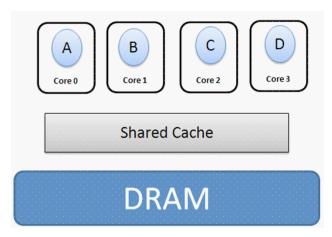

In recent embedded systems and chip-multiprocessors (CMPs), cores are not totally independent processors but rather share particular on/off chip resources. These resources are the last level cash L2-L3, interconnects (memory bus), pre-fetchers and the Dynamic randomaccess memory (DRAM) controller. The requests coming from different threads and different cores are treated as if they were all requested from one single source, as can be seen in Figure 2.7 [132].

Workload scheduling or mapping means how the running applications will be distributed on the cores in a particular period of time to minimize power consumption [126].

Figure 2.7: Examples of thread-to-core mapping in CMP configurations [132]

#### 2.4 LITERATURE REVIEW

Contemporary computing systems, including embedded and high performance systems, are exhibiting increased complexities in two dimensions. In one dimension, the number and type of computing resources (cores) are increasing in hardware platforms, and in the other, an increasing diversity of applications are being executed concurrently on these platforms [81], [79]. Managing hardware resources, to achieve energy efficiency, under different application scenarios (single or concurrent) is proving highly challenging due to runtime state-space expansion [36].

This section discusses a set of power management techniques carried out by different academic and industrial groups. This literature is by no means implies a total survey of power management research. Comprehensive survey studies have been presented in many papers for example, Mittal [71], Singh et al.[100], and Kallimani [49]. Specific work reviews related to the contributions of the thesis are presented in the appropriate chapters.

#### 2.4.1 Power Management Techniques During Design

As power and energy consumption has become a limiting factor to continued technology scaling and performance improvements [14], techniques for improving power and energy efficiency have emerged.

In the past few years, there have been various studies in power management of embedded systems during design or offline time.

Some of these techniques have been presented in Section 2.3. Mittal [71] and Kallimani et al. [49] classify power management techniques during design into four categories :

1. Dynamic voltage scaling (DVS), dynamic frequency scaling (DFS), and dynamic voltage frequency scaling DVFS techniques which

have been explained in Section 2.3 [16, 77, 54, 90, 29, 42, 22, 21, 130]

- Dynamic power management or sometimes called low power mode management [40].

- 3. Micro-architectural design techniques for specific components. For example, memory (cache, main, scratchpad) [72, 69, 104]

- 4. Digital signal processing (DSP) or GPUs or FPGAs have been used as unconventional-cores [109, 120, 12, 65]

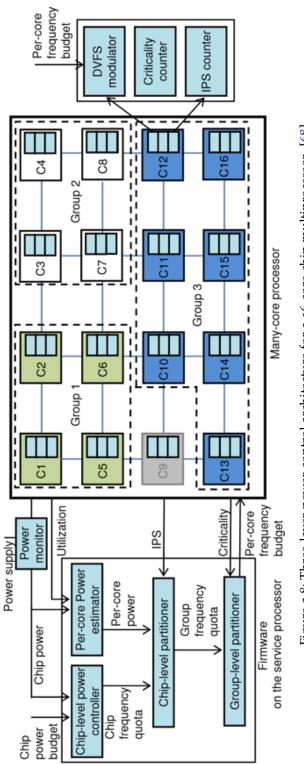

In terms of using DVFS technique, Ma et al. [68] proposed a low power control approach for many-core processors executing single applications. This approach has three layers of design features as shown in Figure 2.8: firstly, adjusting the clock frequency of the chip depending on the power budget; secondly, dynamically group cores to run-the same applications (as also shown in [127]), and finally, modify the frequency of each core group (as also shown in [123]).

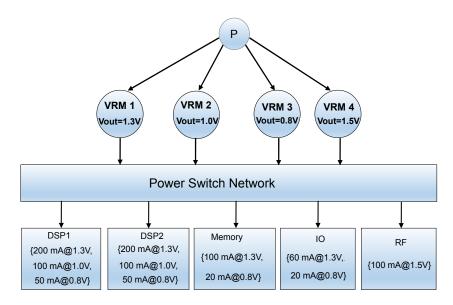

Beh et al. [7] suggested a new design for DVS for a complex systemon-chip SoC by dividing it into many blocks depending on suitable supply voltage levels and corresponding clock frequency to each processing element. These elements are CPU cores, IO, memory and DSP, which are called function blocks as can be seen in Figure 2.9.

Here the VRM represents a voltage regulator module, which is an electronic circuit designed to supply fixed voltage levels.

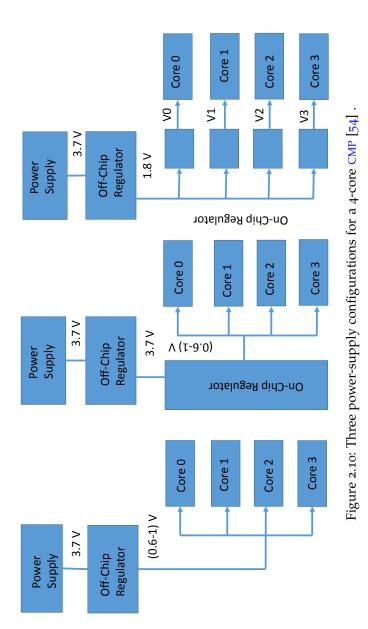

Per-core dynamic voltage frequency scaling DVFS is an effective power management technique to save power consumption. Kim et al. [54] designed a new power supply paradigm with an on/off regulator to implement DVFS per-core, as shown in Figure 2.10.

In this paradigm, many algorithms with different benchmarks have been adopted to implement per-core DVFS in an offline manner taking into account transition time and overheads effects.

The hardware designers of the embedded systems typically provide many operating modes to lower the power consumption. For example, a low power mode has been used to reduce the power consumption of the multi/many-core system when cores are idle. Hoeller et al. [40] presented a new paradigm for interfacing hardware and software components to manage the power consumption. Fundamental of this approach is that allowing applications to precise when some components are not being utilized and based on this data, particular components, cores or the entire system can be moved to low power mode.

In terms of using micro-architecture design techniques, Mittal and Zhang [72] presented a new cache memory design to save cache leakage power. This approach is based on software to predict the power efficiency and cache usage for multiple cache configuration and change cache configurations for reducing the cache power.

Figure 2.9: Proposed architecture of PDN to support dynamic voltage scaling. The output voltage of each VRM is fixed [7]

#### 2.4.2 Runtime Power Management Techniques

Modern embedded systems execute multiple applications, both sequentially and concurrently, on heterogeneous and homogeneous platforms. Determining the most energy-efficient system configuration (i.e. the number of parallel threads, their core allocations and operating frequencies) tailored for each kind of workload during execution is extremely challenging because the state space is very large and each application requires different optimization.

Recent years have witnessed various studies in power and energy optimization in embedded systems during execution time (i.e. runtime). These studies provide various methods of the ability to learn information without being clearly programmed, with regard to improve power and energy efficiency. The learned information during the operation is used to predict the appropriate task mapping and DVFS for future execution. In general, runtime power management techniques policies have three objectives [9];

- 1. The total power saving ought to be maximized.

- 2. The latency penalty is reduced.

- 3. The runtime overhead ought to be reduced to prevent prolonging of the kernel time.

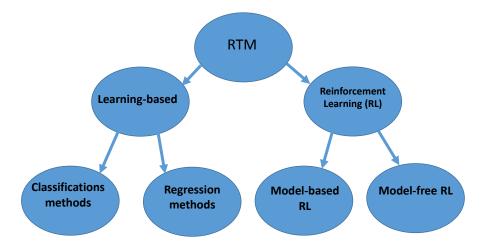

Based on the principles they employ, existing studies can be largely categorised into two approaches: learning based and reinforcement learning, as can be seen in Figure 2.11.

Figure 2.11: A taxonomy of runtime power management techniques.

#### 2.4.2.1 Learning based runtime management

Many strategies have been adopted in this approach, which can be classified based on learning principle into two taxonomies i.e. classifications techniques and regression techniques. The first one has been used for predicting application response based on the applications type such us email, medical imaging, and games or based on application behaviour ( CPU-intensive, memory-intensive, or both).

On the other hand, learning based regression techniques have been used for predicting continuous response for instance, changing in temperature or fluctuating in voltage or frequency. Regression techniques are used to learn model parameters from data collected at runtime, and the resulting models are used to derive next step control decisions. Existing work that proposed the use of regression in the runtime management are those by Sheng et al. [128], Shafik et al. [93], and [18, 41, 44, 62]. Sheng et al. presented an adaptive power minimization approach using practical implementation on heterogeneous platforms. Fundamental to this approach is the use of runtime linear regression (LR)-based modelling of the power and performance tradeoffs as can be seen in Figure 2.12. Using the model, the task mapping and DVFS are suitably chosen to meet the specified performance requirements.

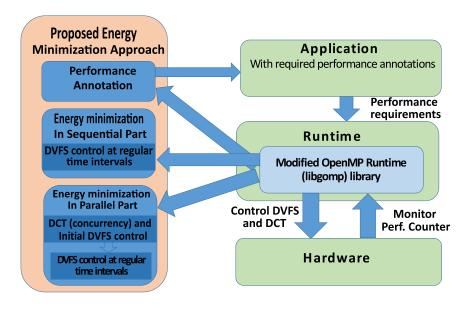

Shafik et al.[93] proposed a new runtime adaptation approach for modern many core systems to reduce the power consumption based on parallel application. This approach depend on workload prediction with DVFS technique in runtime as can be seen in Figure 2.13. This adaptation is easy to adjust through performance annotations in sequential and parallel parts of workloads. This approach has been validated on Intel Xeon E5-2630 platform , which consist of 24 cores. NAS benchmark has been demonstrated on this platform based on OpenMP library. Furthermore, this approach shows that the energy

| Application<br>ta:                              | sks<br>.   tn                          |

|-------------------------------------------------|----------------------------------------|

| Performance req.                                |                                        |

| Runtime                                         |                                        |

| 2 Runtime Manager<br>2a Task mapping<br>2b DVFS | 1 Runtime Energy/<br>Performance Model |

|                                                 |                                        |

| Mapping/VFS controls                            | Energy/Perf. statistics                |

| Mapping/VFS controls<br>Hardware                | Energy/Perf. statistics                |

|                                                 | Energy/Perf. statistics                |

Figure 2.12: Block diagram of the proposed energy minimization approach [128].

consumption can be minimized significantly compared to existing approaches.

Figure 2.13: Proposed energy minimization approach [93]

Another runtime approach for homogeneous many core systems has been adopted by Leech et al. [59], realizing power-aware performance adaptation for homogeneous many cores systems. This approach is based on power and performance models that can be determined during runtime by linear regression learning based on low complexity hypotheses of power and performance for a given operating frequency. The approach is extensively demonstrated using stereo vision applications running on a 61-core Intel Xeon Phi platform. DVFS with multi thread techniques have been used in runtime to achieve significant improvement in energy efficiency compared to existing approaches.

Juan et al. [48] proposed a new runtime approach based on using a model selection from machine learning. Using the adaptation model to determine the optimal dynamic voltage frequency operating points under-extend threshold, nominal, or turbo-mode conditions. The approach is demonstrated by Sniper and McPAT simulations running PARSEC and SPLASH-2 benchmarks at different operating frequencies. In this approach two types of experiments are carried out. Firstly: investigation of energy minimization under frequency requirements; secondly, investigation of performance maximizing under power budget. The experimental results show that the improvements in performance under power budget is less than the reduction in energy consumption under the performance condition.

The method of combining DVFS with dynamic concurrency throttling at runtime have been investigated recently. For instance, Jian Li and Jose F. Martinez [62] proposed a new runtime optimization approach for heterogeneous many core systems, fundamental to this study is that runtime optimization of concurrency with DVFS for parallel applications can achieve energy-efficient execution and high performance. This runtime optimization occurs in two-dimensional scenario, firstly; task mapping of active cores, secondly; the various frequency/voltage levels available.

Another prediction model for power/performance optimization in runtime for homogeneous systems has been proposed by Curtis et al. [26]. In this approach two knobs DVFS and dynamic concurrency throttling (DCT) have been used to reduce the dynamic power consumption. Using experimental measurements on two Intel Xeon E5320 quad-core processors platform with seven benchmarks from the OpenMP version of the NAS Parallel Benchmark suite to validate this approach. Multivariate linear regression is used to establish multi-dimensional empirical prediction model coefficients offline.

|                           | labl                          | e 2.1: Features and | a limitations c | Table 2.1: Features and limitations of the supervised model-based learning techniques approaches. | ed learnin | ig techniques appri            | oaches.                                        |

|---------------------------|-------------------------------|---------------------|-----------------|---------------------------------------------------------------------------------------------------|------------|--------------------------------|------------------------------------------------|

| Approach                  | Approach Application Platform | Platform            | Validation      | Validation Runtime type                                                                           | WLC        | Control<br>Knobs               | Optimization                                   |

| Juan et<br>al. [48]       | Single                        | Homogeneous         | Simulation      | Homogeneous Simulation Model-based learning                                                       | No         | DVFS                           | Energy saving+<br>Performace improvement       |

| Sridharan<br>et al. [103] | Single                        | Homegenous          | Simulation      | Simulation Model-based learning                                                                   | No         | Task<br>mapping                | Energy saving+<br>Energy efficincy improvement |

| Ma et<br>al.[67]          | Single                        | Heterogenous        | Simulation      | Model-based learning<br>(offline regression)                                                      | No         | DVFS+Task<br>mapping           | Power saving+Performace<br>improvement         |

| Curtis et<br>al. [25]     | Concurrent                    | Homegenous          | Practical       | Model-based learning<br>(offline regression)                                                      | No         | DVFS+DCT                       | Power saving+Performace<br>improvement         |

| Sasaki et<br>al. [89]     | Single                        | Homegenous          | Practical       | Model-based learning<br>(Multivarate linear<br>regression)                                        | No         | DVFS+Number<br>of active cores | Performace improvement                         |

| Wu et<br>al. [124]        | Single                        | Heterogenous        | Practical       | Model-based learning<br>(linear regression)                                                       | No         | DVFS                           | Performace improvement                         |

|                           |                               |                     |                 |                                                                                                   |            |                                |                                                |

roaches modal-based learning tachniques head 4112 and limitations of the Table 2.1: Features Recently, numerous studies have focused on workload type with using mixture of two technique to optimize the power/performance for many core embedded systems [24, 102, 27, 28, 131]. For instant, the technique proposed in [27] first derives energy and cycles-perinstruction models. Then, these models have been used to characterize the workload at runtime by selecting the best dynamic power management (DPM) scenario together with DVFS setting for each core.

Sozzo et al. [102] proposed a new runtime Linux scheduler using practical implementation of their approaches on heterogeneous platforms. Fundamental of this approach is that optimize voltage/frequency under performance constraint, manages the task mapping of application threads among heterogeneous cores, and uses performance counters to monitor the varying in workload characteristics. The approach is demonstrated by Odroid XU<sub>3</sub> running the Black and Scholes parallel model application of OpenMP. Moreover, The experimental results of this approach show a significant improvements in power consumption and performance compared to current Linux governors. Similarly, the work in [131] proposed a practical implementation approach on a set of web-browsing applications running on ARM big.LITTLE heterogeneous many core systems. In this approach linear regression technique is used to build power/performance models, and then use these models to determine the optimal core allocation for minimum power consumption.

Table 2.1 shows the most features and limitations of the existing approaches which employ supervised model-based learning techniques. It is clear that the researchers did not include the workload classification in these approaches.

In terms of using classification-based techniques, numerous studies have focused on using these techniques in dynamic power management with DVFS together at runtime [36, 56, 87, 24, 13, 113, 122]. For instance, Gupta et al.[36] proposed a new runtime approach based on workload classification. To build this classifier extensive offline experiments are made on heterogeneous many core platforms and Matlab is used to determine the classifier parameters offline. Pareto function is used to determine the optimal configuration. However, this classification is heavily based on offline analysis results, and assigns an application a fixed type, regardless of its operating context. It also requires the annotation of applications by application programmers through using a special API.

Another runtime workload classification approach for heterogeneous multi-core systems is proposed by Reddy et al. [87]. Memory Reads Per Instruction (MRPI) metric has been used to perform workload classification. This metric uses performance counters to determine the performance in terms of instruction per second (IPS) during application execution. The workload classification aims to determine the optimal voltage/frequency without any loss of performance. Using experimental measurements on ARM big.LITTLE Odroid-XU<sub>3</sub> platform with five applications from SPEC CPU2006 benchmarks and two applications from PARSEC to validate this approach. However, this work does not merge DVFS with task mapping techniques for workload on heterogeneous platform.

Table 2.2 shows the most features and limitations of the existing approaches based on supervised classification-based and model-based learning techniques.

|                            |                                                                                  | F                                           | 2.4                                               |                               | IUKE KEVIEW                                                                    |

|----------------------------|----------------------------------------------------------------------------------|---------------------------------------------|---------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------|

| Optimization               | Performanc<br>optimization                                                       | Performace<br>improvement                   | Performace<br>improvement                         | Power/Performance<br>tradeoff | Energy efficincy<br>improvement                                                |

| Control<br>Knobs           | Task<br>mapping                                                                  | Task<br>mapping                             | Task<br>mapping                                   | DVFS+Task<br>mapping          | DVFS+<br>Number of<br>active cores                                             |

| Workload<br>Classification | Offline classification<br>based on memory<br>bound                               | Partial WLC to<br>big or small cores        | Offline classification for<br>OpenCL applications | Offline classification        | Partial classification<br>(offline determining<br>the<br>classifier parameters |

| Validation Runtime type    | Model-based<br>learning (machine<br>learning to<br>predict performance<br>model) | classification+<br>performance<br>modelling | Model-based<br>learning                           | Model-based<br>learning       | Model-based<br>learning<br>(Pareto)                                            |

| Validation                 | Practical                                                                        | Simulation                                  | Practical                                         | Practical                     | Practical                                                                      |

| Platform                   | Homegenous                                                                       | Heterogenous                                | Heterogenous<br>CPU/GPU                           | Homegenous                    | Heterogenous                                                                   |

| Application                | Single                                                                           | Single                                      | Concurrent                                        | Single                        | Single                                                                         |

| Approach                   | Bitirgen<br>et al. [13]                                                          | Van et<br>al. [113]                         | Wen et<br>al. [122]                               | Cochran<br>et al.[24]         | Gupta et<br>al. [36, 34]                                                       |

Table 2.2: Features and limitations of the supervised classification-based and model-based learning techniques approaches.

25

# 2.4.2.2 Reinforcement learning (RL)

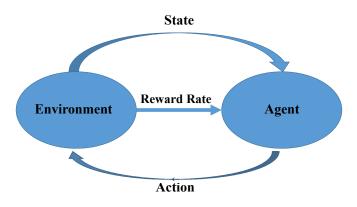

Reinforcement learning RL methods are a set of arrangements for ideal long-term activity choice such that activities take under consideration both immediate and delayed results [43]. Figure 2.14 shows the general description of the RL model which comprises of a finite state space S, an agent, a set of available actions A, and a reward function R [118]. Mathematically, RL [105] describes some kind of solution to the problems of the Markov Decision Process (MDP) identified by the group *S*, *A*, *T*, *R*, and  $\pi$  where:

- 1. S: a set of states  $s \in S$

- **2**. *A*: a set of actions  $a \in A$

- 3. *T*: the transition function maps each state-action combine to a dissemination over successor states

- 4. *R* : the reinforcement function set three times the state-actionsuccessor state to a stander return *r* maximizing the overall predicted future

Figure 2.14: Agent-environment interaction Model.

The objective is to specify  $a \rightarrow \pi(x)$  policy that sets each state to the action maximizing the entire anticipated future return of activities a in state s. RL methods can be classified into two types model-based and model-free. Model-based techniques evaluate a clear model of the environment and the agent which mean that the applies descriptions based on model decision, in options that reflect current preferences regarding results. While, Model-free approaches do without any explicit information of the elements of the environment or the results of actions and assess how good actions are implemented through trial and error learning [43].

In other words, model-based RL assume knowledge of the transition matrix T, the reward function R, the state S, and action spaces A which define the model. And, model-free RL strategies are used in

circumstances where agents do not know *T* and *R* where the choice trees are too complicated to assess.

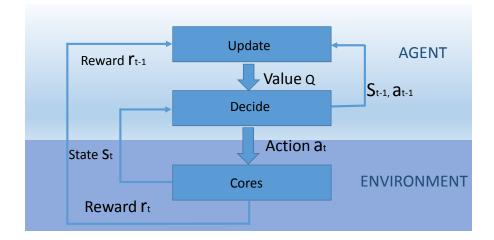

# 2.4.2.3 Model-Based RL

Over the years substantial research has been carried out addressing runtime energy minimization and/or performance improvement approaches. The technique of learning reinforcement has been used for many core systems by Tan et al. [107] and Ye et al. [129]. There are a few solid similarities between dynamic power management and reinforcement learning: the next decision in DPM based on the current status and the previous statistics, while in the RL technique the agent monitors the state environment  $s_t$  at t time, tacking action  $a_t$ , and therefore gets a  $r_t$  reward. Because of the similarities in the trial and error operation, power management can be performed using reinforcement learning techniques [76].