## Old Dominion University

# **ODU Digital Commons**

Electrical & Computer Engineering Theses & Dissertations

**Electrical & Computer Engineering**

Spring 2020

# Comprehensive Designs of Innovate Secure Hardware Devices against Machine Learning Attacks and Power Analysis Attacks

Yiming Wen Old Dominion University, ywen001@odu.edu

Follow this and additional works at: https://digitalcommons.odu.edu/ece\_etds

Part of the Electrical and Computer Engineering Commons

#### **Recommended Citation**

Wen, Yiming. "Comprehensive Designs of Innovate Secure Hardware Devices against Machine Learning Attacks and Power Analysis Attacks" (2020). Doctor of Philosophy (PhD), Dissertation, Electrical & Computer Engineering, Old Dominion University, DOI: 10.25777/999a-wk88 https://digitalcommons.odu.edu/ece\_etds/210

This Dissertation is brought to you for free and open access by the Electrical & Computer Engineering at ODU Digital Commons. It has been accepted for inclusion in Electrical & Computer Engineering Theses & Dissertations by an authorized administrator of ODU Digital Commons. For more information, please contact digitalcommons@odu.edu.

# COMPREHENSIVE DESIGNS OF INNOVATE SECURE HARDWARE DEVICES AGAINST MACHINE LEARNING ATTACKS AND POWER ANALYSIS ATTACKS

by

Yiming Wen B.S. June 2013, Central South University (China) M.S. June 2016, University of South Florida

A Dissertation Submitted to the Faculty of Old Dominion University in Partial Fulfillment of the Requirements for the Degree of

# DOCTOR OF PHILOSOPHY

### ELECTRICAL AND COMPUTER ENGINEERING

OLD DOMINION UNIVERSITY February 2020

Approved by:

Weize Yu (Director)

Chung-Hao Chen (Member)

Cong Wang (Member)

Jiang Li (Member)

### ABSTRACT

# COMPREHENSIVE DESIGNS OF INNOVATE SECURE HARDWARE DEVICES AGAINST MACHINE LEARNING ATTACKS AND POWER ANALYSIS ATTACKS

Yiming Wen Old Dominion University, 2020 Director: Dr. Weize Yu

Hardware security is an innovate subject oriented from growing demands of cybersecurity and new information vulnerabilities from physical leakages on hardware devices. However, the mainstream of hardware manufacturing industry is still taking benefits of products and the performance of chips as priority, restricting the design of hardware secure countermeasures under a compromise to a finite expense of overheads. Consider the development trend of hardware industries and state-of-the-art researches of architecture designs, this dissertation proposes some new physical unclonable function (PUF) designs as countermeasures to side-channel attacks (SCA) and machine learning (ML) attacks simultaneously. Except for the joint consideration of hardware and software vulnerabilities, those designs also take efficiencies and overhead problems into consideration, making the new-style of PUF more possible to be merged into current chips as well as their design concepts. While the growth of artificial intelligence and machine-learning techniques dominate the researching trends of Internet of things (IoT) industry, some mainstream architectures of neural networks are implemented as hypothetical attacking model, whose results are used as references for further lifting the performance, the security level, and the efficiency in lateral studies. In addition, a study of implementation of neural networks on hardware designs is proposed, this realized the initial attempt to introduce AI techniques to the designs of voltage regulation (VR). All

aforementioned works are demonstrated to be of robustness to threats with corresponding power attack tests or ML attack tests. Some conceptional models are proposed in the last of the dissertation as future plans so as to realize secure on-chip ML models and hardware countermeasures to hybrid threats. Copyright, 2020, by Yiming Wen, All Rights Reserved.

Dedicated to my mom who gives me encouragement as well as my best friends who give me company throughout my fascinating learning experience in United States

### ACKNOWLEDGEMENTS

Thanks to unpredictable life and sparks of human nature. Ten years ago, when I was first out for a journey to the society, never did I imagine I would find a career that I would love so much and a life goal that I would fully devote myself to. Thanks to those stories as well as characters included that make me who I am today.

My first special appreciation is devoted to my advisor Dr. Weize Yu. It must be written in my fate to find an eminent mentor like him. His unfailing instruction helps me overcome difficulties one after another. Your accompany beyond academics released my loneliness and we are just like family throughout three years in Norfolk. No words can express my grateful thanks to your patience as my advisor.

Special thanks to all members in my dissertation committee: Dr. Chung-Hao Chen, Dr. Jiang Li, and Dr. Cong Wang. It is my great honor to invite them in my last trip as a Ph.D student and the origin as an engineer. Their rigorous attitude to research and teaching inspires me a lot. I would like to thank them for their invaluable time, patience, comments, and encouragement.

Thanks to my friends, Youwen Min, Zheng Qu, Xushi Wang, and Hongbo Pan. It is already 15 years since we first met. Although we hardly have time to gossip, it is always a great experience to share collected stories every time when I am back home. Their en-couragement and suggestion help me stand firmly for my convictions, and I will treasure our friendship as wealth for a lifetime.

Finally, thanks for the supports and accompany of my mother. I first thought my invitation of your helps you to escape trifles of life. However, when I finish my final word in this work, I realize it is because you are here, that I can focus fully on my work and find a goal to struggle for. I love you, mom!

# TABLE OF CONTENTS

Page

| LIST OF TABLES ix                                                                                                                                                                                                                                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LIST OF FIGURES xiii                                                                                                                                                                                                                                                                              |

| Chapter                                                                                                                                                                                                                                                                                           |

| CHAPTER 1INTRODUCTION11.1HARDWARE SECURITY11.2SIDE-CHANNEL ATTACKS31.3PHYSICAL UNCLONABLE FUNCTION DEVICES51.4MACHINE LEARNING71.5HARDWARE TROJANS111.6OUR CONTRIBUTION13                                                                                                                         |

| CHAPTER 2DESIGN AN INNOVATE PHYSICAL UNCLONABLE FUNCTIONDEVICE WITH VOLTAGE REGULATOR152.1MOTIVATION152.2BACKGROUND172.3ARCHITECTURE DESIGN172.4EVALUATION212.5CIRCUIT LEVEL SIMULATION352.6CONCLUSION36                                                                                          |

| CHAPTER 3USING BALANCED LOGIC GATES TO DESIGN AN INNOVATESTRONG PUF IN IOT SECURITY373.1MOTIVATION3.2ARCHITECTURE DESIGN3.3PERFORMANCE EVALUATION3.4ROBUSTNESS AGAINST POWER ATTACKS3.5RESILIENCE AGAINST MACHINE-LEARNING ATTACKS3.6CONCLUSION63                                                 |

| CHAPTER 4A NOVEL PUF PRIMITIVE FOR GENERAL PROTECTIONAGAINST NON-INVASIVE ATTACKS ON IOT DEVICES644.1MOTIVATION644.2WORKING PRINCIPLE OF THE PROPOSED PUF654.3ROBUSTNESS AGAINST MACHINE LEARNING ATTACKS674.4RESILIENCE AGAINST SIDE-CHANNEL ATTACKS744.5PERFORMANCE EVALUATION774.6CONCLUSION77 |

| CHAPTER 5 HARDWARE TROJAN-BASED MALICIOUS ATTACKS ON PHY | SIC- |

|----------------------------------------------------------|------|

| AL UNCLONABLE FUNCTION SENSORS                           | 79   |

| 5.1 MOTIVATION                                           | 79   |

| 5.2 REVIEW OF RING OSCILLATOR PUF (ROPUF) SENSOR         | 81   |

| 5.3 DESIGN OF TROJAN-INFECTED ROPUF                      | 84   |

| 5.4 RETRIEVAL OF CONFIDENTIAL DATA                       | 87   |

| 5.5 TROJAN DETECTION                                     | 96   |

| 5.6 CONCLUSION                                           |      |

| CHAPTER 6 COMBINING SIDE-CHANNEL ANALYSIS AND MACHINE    |      |

| LEARNING MODELS IN EFFICIENT ATTACKS ON XOR PUFS         | 99   |

| 6.1 MOTIVATION                                           | 99   |

| 6.2 PRINCIPLE OF SC-ASSISTED CNN ATTACK                  | 100  |

| 6.3 COMPARISON BETWEEN THE PROPOSED ATTACK AND A REGU-   | -    |

| LAR CNN ATTACK                                           | 103  |

| 6.4 CONCLUSION                                           | 106  |

| CHAPTER 7 CONCLUSION                                     | 108  |

| CHAPTER 8 FUTURE WORK                                    | 110  |

| 8.1 MACHINE LEARNING-BASED PHYSICAL UNCLONABLE FUNCTION  | [    |

| (PUF)-LIKE MODULES                                       | 110  |

| 8.2 LOW/REDUCED OVERHEAD PHYSICAL UNCLONABLE FUNCTION    | [    |

| DEVÍCES                                                  |      |

|                                                          |      |

| REFERENCES                                               | 125  |

| APPENDICES                                               |      |

| VITA                                                     | 126  |

# LIST OF TABLES

| Tabl | e                                                                                                                                                         | Page |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 3.1  | Four different transient current signatures: $I_1^*$ , $I_2^*$ , $I_3^*$ , and $I_4^*$ induced by four different output logic transitions of Fig. 3.5(b). | . 52 |

| 4.1  | A CNN structure for modeling PUF primitives                                                                                                               | . 70 |

| 4.2  | Training Results of the CNN structure for modeling the MSB of the 128-bit KU AES-embedded PUF (number of epochs is 20).                                   | . 72 |

| 4.3  | Training results of the new CNN attack for modeling the MSB of the 128-bit KU AES-embedded PUF (number of epochs is 20).                                  | . 74 |

| 5.1  | Training results of the CNNs with different number of training data (number of epochs is 60 and batch_size is 100)                                        | . 92 |

# LIST OF FIGURES

| Figu | Figure                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

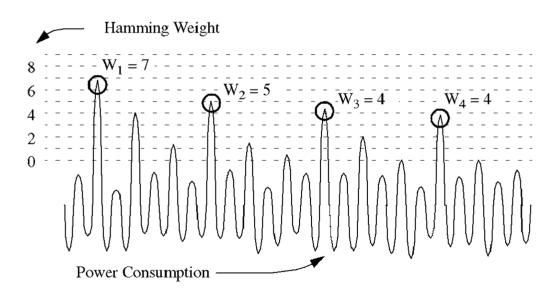

| 1.1  | Hamming weight information can be extracted from leaked signal of power con-<br>sumption [1]                                                                                                                                                                                                                                                                                                                                                               | 5  |

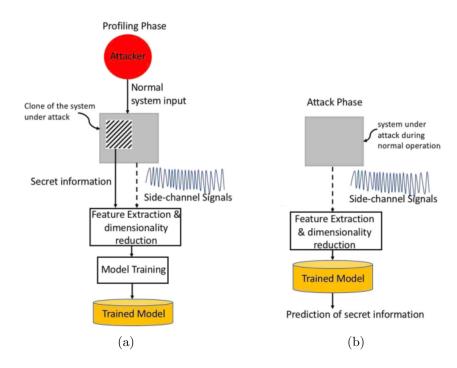

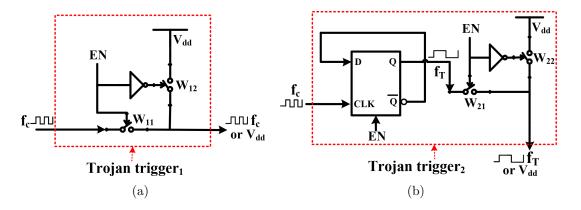

| 1.2  | Profiling-based side-channel analysis attack using machine learning as modeling tools: (a) profiling phase; (b) attack phase [2]                                                                                                                                                                                                                                                                                                                           | 9  |

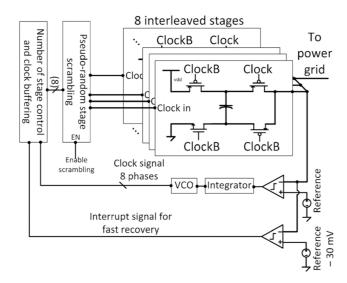

| 2.1  | CoGa regulator in [3] (8-phase) introduces PRNG to realize the mitigation of output power profiles.                                                                                                                                                                                                                                                                                                                                                        | 16 |

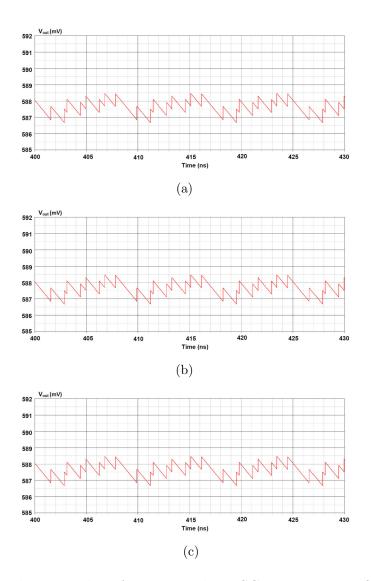

| 2.2  | Output voltage ripples of a 2:1 32-phase SC converter. a Case 1: Sequence of activation pattern (8 active phases): (7, 12, 13, 18, 20, 25, 27, 31). b Case 2: Sequence of activation pattern (16 active phases): (1, 2, 3, 4, 6, 8, 9, 14, 15, 16, 22, 23, 26, 28, 29, 30). c Case 3: Sequence of activation pattern (16 active phases): (2, 5, 6, 9, 10, 11, 14, 16, 19, 23, 24, 26, 28, 29, 30, 32)                                                      | 18 |

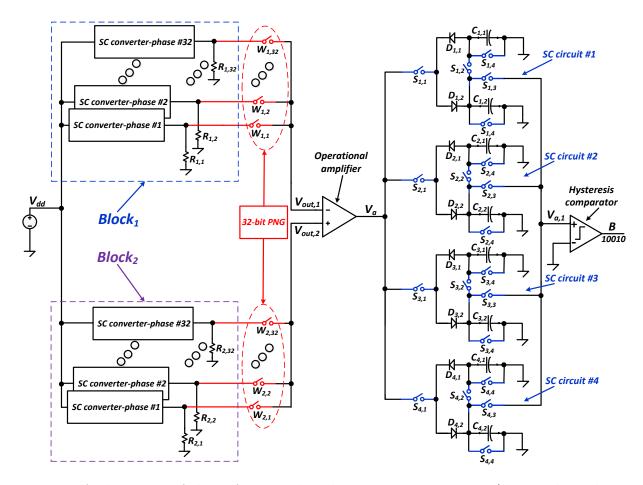

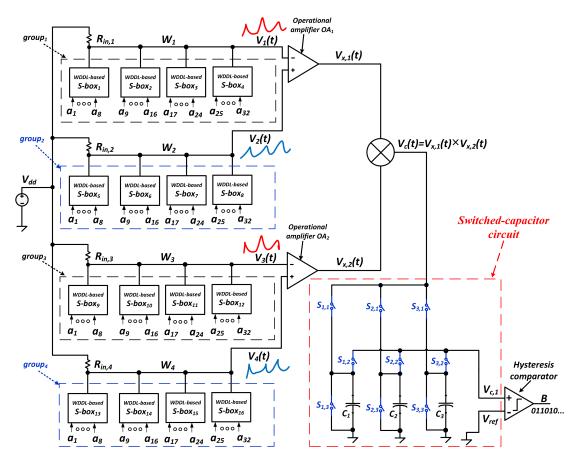

| 2.3  | Architecture of the WAMPVR-based strong PUF primitive (the total number $X$ of phases in the original WAMPVR is 64, the resistors $R_{1,1}$ , $R_{2,1}$ , $R_{1,2}$ , $\cdots$ , and $R_{2,32}$ are designed with the same resistance $R$ , and the capacitors $C_{1,1}$ , $C_{1,2}$ , $C_{2,1}$ , $\cdots$ , and $C_{4,2}$ are also designed with the same capacitance $C$ ).                                                                             | 20 |

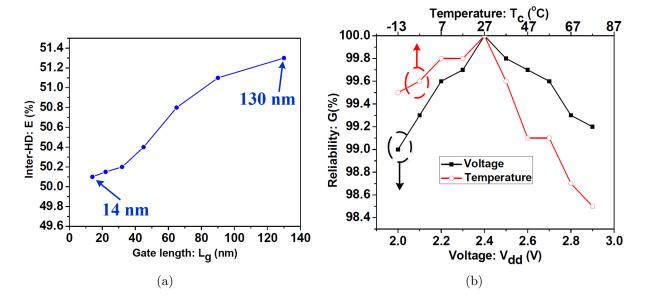

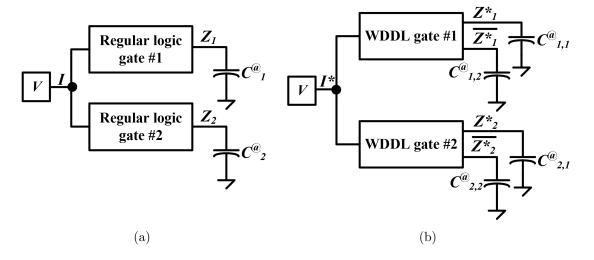

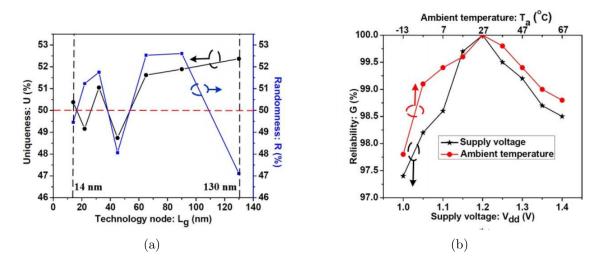

| 2.4  | Performance evaluation for the designed strong PUF primitive. (a) Inter-HD $E$ versus gate length $L_g$ ( $K = 100$ and $N = 32$ ). (b) Reliability $G$ versus supply voltage $V_{dd}$ and environmental temperature $T_c$ ( $M = 50$ and $N = 32$ )                                                                                                                                                                                                       | 26 |

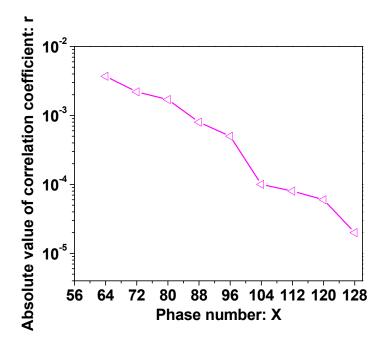

| 2.5  | Absolute value $r$ of correlation coefficient between $P_{in}$ and $\Delta C$ versus phase number $X$ against side-channel attacks                                                                                                                                                                                                                                                                                                                         | 27 |

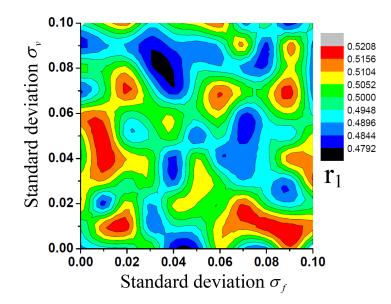

| 2.6  | Prediction accuracy $r_1$ of power attacks versus standard deviations $\delta_f$ and $\delta_v$<br>after analyzing 1 million input power and output response pairs (The colors and<br>contours represent the variation values of the prediction accuracy $r_1$ . Since the<br>variation values of the prediction accuracy $r_1$ are around 0.5 and random, that<br>reflects power attacks are unable to leak critical information on the proposed<br>PUF). | 30 |

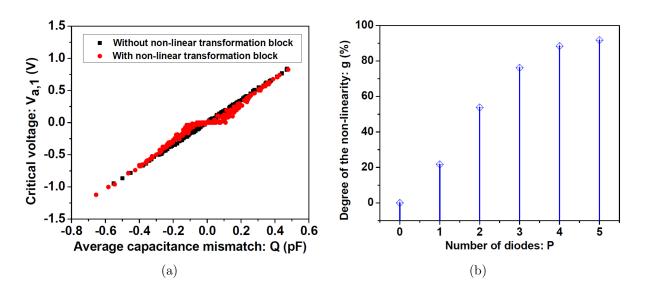

| 2.7  | (a) Critical voltage $V_{a,1}$ versus average capacitance mismatch $Q$ against ML attacks. (b) Number of diodes $P$ between the switch $S_{h,1}$ and the capacitor $C_{h,x}$ in Fig. 2.3 versus degree $g$ of the non-linearity of the WAMPVR-based strong PUF primitive.                                                                                                                                                                                  | 31 |

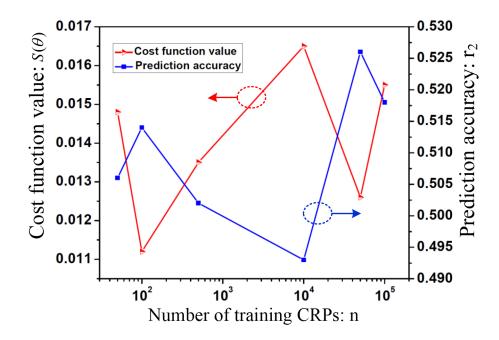

| 2.8  | Cost function value $S(\theta)$ and prediction accuracy $r_2$ versus number of train-<br>ing CRPs $n$ for the WAMPVR-based strong PUF primitive under LR attacks<br>(number of diodes $P = 3$ )                                                                      | 34 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

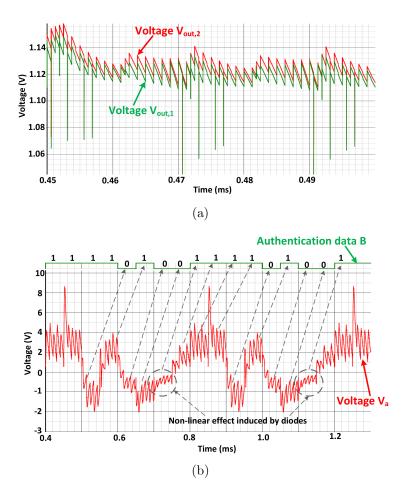

| 2.9  | Simulated waveforms of the WAMPVR-based strong PUF primitive $(X = 32)$ .<br>(a) Voltages $V_{out,1}$ and $V_{out,2}$ versus time. (b) Voltage $V_{out,1}$ and binary authentication data $B$ versus time                                                            | 35 |

| 3.1  | Architecture of a WDDL-based AES strong PUF primitive (the total number $N$ of digital input bits of the AES cryptographic circuit is 128)                                                                                                                           | 39 |

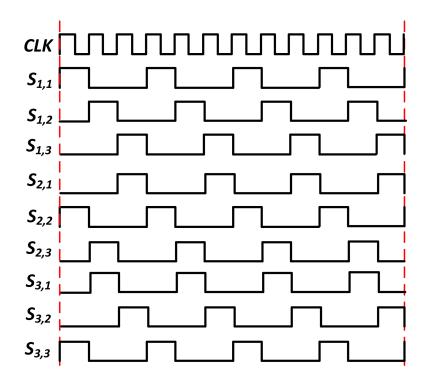

| 3.2  | Waveform of control signal of the switch $S_{i_{1,j}}$ ( <i>CLK</i> is the clock signal of the input data <i>A</i> . $S_{i_{1,j}} = 1$ represents the switch $S_{i_{1,j}}$ is in on-state, and <i>vice versa</i> ).                                                  | 40 |

| 3.3  | Dynamic current profile of $group_1$ (Four number of WDDL-based S-boxes are used. $A_1, A_2$ , and $A_3$ are three different 32-bit binary data)                                                                                                                     | 46 |

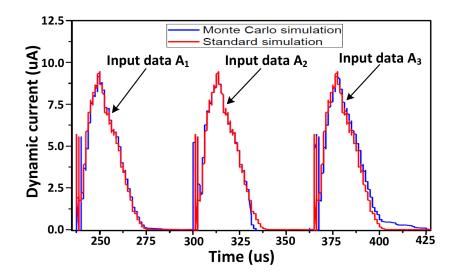

| 3.4  | Performance evaluation for the WDDL-based AES strong PUF. (a) Inter-HD $H$ versus identically designed resistance $R_0$ ( $M = 100$ and $K = 10$ ). (b) Reliability $G$ versus supply voltage $V_{dd}$ and environmental temperature $T_e$ ( $M = 50$ and $K = 10$ ) | 47 |

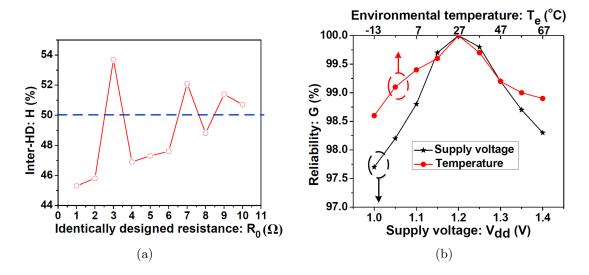

| 3.5  | Two logic gates share the same power supply. (a) Regular logic gates. (b) WDDL gates.                                                                                                                                                                                | 49 |

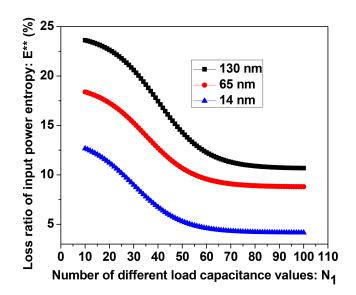

| 3.6  | Loss ratio $E^{**}$ of input power entropy versus number of different load capacitance values $N_1$ for the WDDL-based AES strong PUF against the power attack                                                                                                       | 53 |

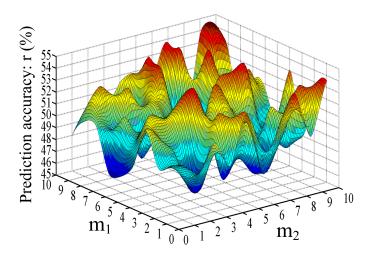

| 3.7  | Prediction accuracy $r$ of the power attack under the parameters $B^*$ and $B^{**}$ versus degrees $m_1$ and $m_2$ of the series $(n_3 = 1, 000, 000)$ .                                                                                                             | 56 |

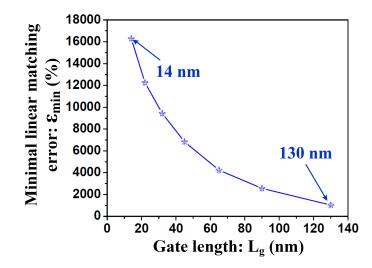

| 3.8  | Minimal linear matching error $\varepsilon_{min}$ versus gate length $L_g$ for the WDDL-based AES strong PUF against machine-learning attacks ( $Y = 100,000$ )                                                                                                      | 60 |

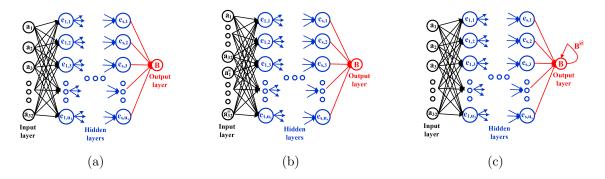

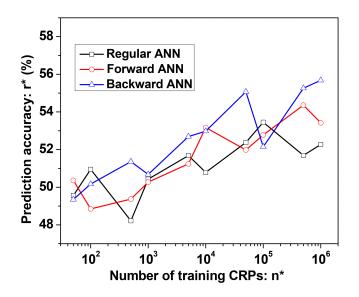

| 3.9  | Three different artificial neural network (ANN) architectures for performing deep-learning attacks on the WDDL-based AES strong PUF. (a) Regular ANN. (b) Forward ANN. (c) Backward ANN.                                                                             | 61 |

| 3.10 | Prediction accuracy $r^*$ versus number of training CRPs $n^*$ for the WDDL-based AES strong PUF under thee different deep-learning attacks ( $s = 3, u_1 = 15, u_2 = 30$ , and $u_3 = 20$ )                                                                         | 62 |

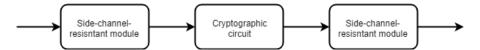

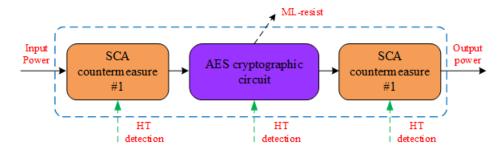

| 4.1  | Conceptual model of proposed comprehensive countermeasure to ML attacks and SCA attacks. Both ends of the cryptographic circuit is protected by a ML model. The uncertainty is retained by the keys stored/inserted on the cryptographic circuit.                    | 65 |

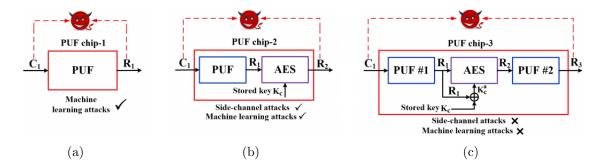

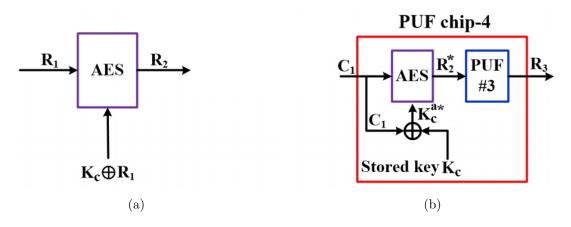

| 4.2 | Three different PUF chips under machine learning or side-channel attacks. (a)<br>Conventional PUF (PUF chip-1). (b) Hybrid PUF (PUF chip-2). (c) Key-<br>updating (KU) AES-embedded PUF (PUF chip-3)                                                                                                                                                                                                        | 66 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

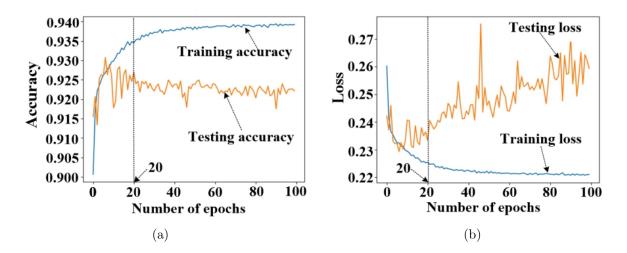

| 4.3 | Training result of the CNN structure in Table 4.1 for modeling the MSB of the 128-bit arbiter PUF (100,000 number of CRPs are enabled for training). (a) Accuracy versus number of epochs. (b) Loss versus number of epochs                                                                                                                                                                                 | 72 |

| 4.4 | (a) AES in the KU AES-embedded PUF. (b) Equivalent PUF architecture for the KU AES-embedded PUF                                                                                                                                                                                                                                                                                                             | 73 |

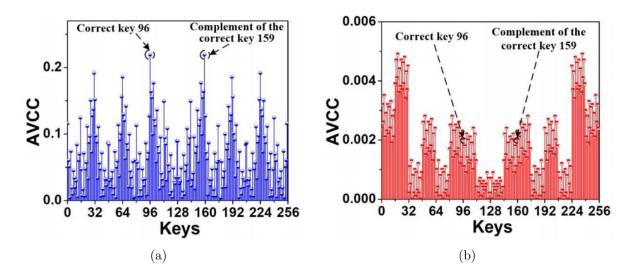

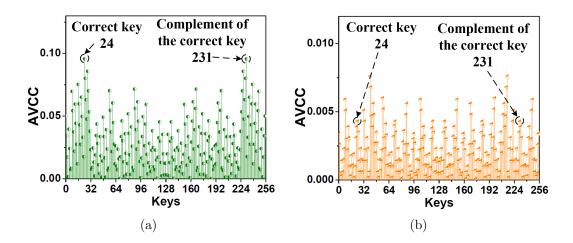

| 4.5 | Simulations of power attacks (hamming-weight (HW) model is used). (a) Absolute value of correlation coefficient (AVCC) versus possible keys for leaking an 8-bit sub-key of the 128-bit unprotected AES cryptographic circuit after inputting 1,000 number of data. (b) AVCC versus possible keys for leaking an 8-bit sub-key of the 128-bit KU AES-embedded PUF after inputting 1 million number of data. | 76 |

| 4.6 | Performance evaluation for the 128-bit KU AES-embedded PUF. (a) Uniqueness $U$ and randomness $R$ versus technology node $L_g$ . (b) Reliability $G$ versus supply voltage $V_{dd}$ and ambient temperature $T_a$ ( $L_g = 130$ nm)                                                                                                                                                                         | 77 |

| 5.1 | A conceptual sketch of a hardware system that is well protected by countermeasures to ML attacks, SCA attacks, and HT attacks.                                                                                                                                                                                                                                                                              | 80 |

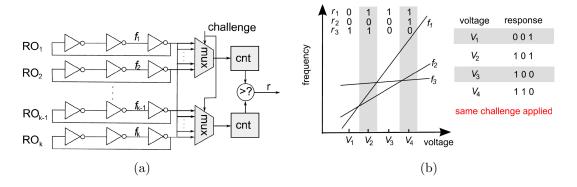

| 5.2 | (a) Architecture of a ROPUF [4]. (b) Oscillating frequencies versus supply volt-<br>age for a ROPUF under the same input challenge [4]                                                                                                                                                                                                                                                                      | 81 |

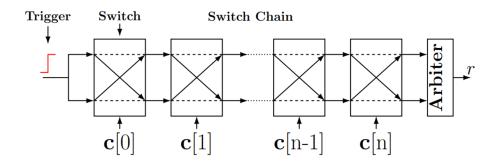

| 5.3 | Classic Arbiter PUF using path-swapping switches [5]                                                                                                                                                                                                                                                                                                                                                        | 82 |

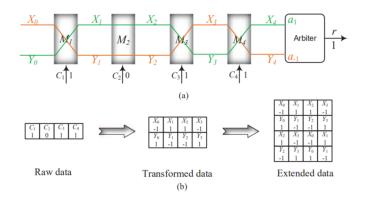

| 5.4 | CRPs data transformation and extension [6]                                                                                                                                                                                                                                                                                                                                                                  | 83 |

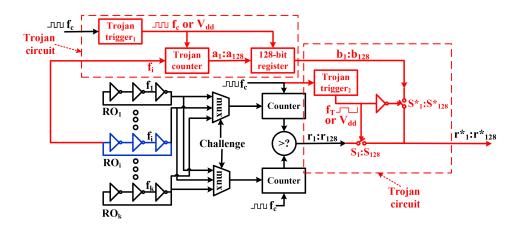

| 5.5 | Basic architecture of a 128-bit Trojan-infected ROPUF                                                                                                                                                                                                                                                                                                                                                       | 84 |

| 5.6 | (a) Architecture of the Trojan trigger 1. (b) Architecture of the Trojan trigger $_2$ .                                                                                                                                                                                                                                                                                                                     | 85 |

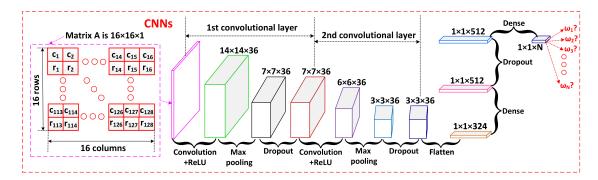

| 5.7 | Detailed structure of the CNNs with two convolutional layers for cracking the 128-bit Trojan-infected ROPUF                                                                                                                                                                                                                                                                                                 | 88 |

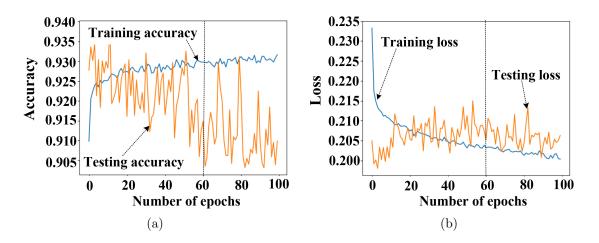

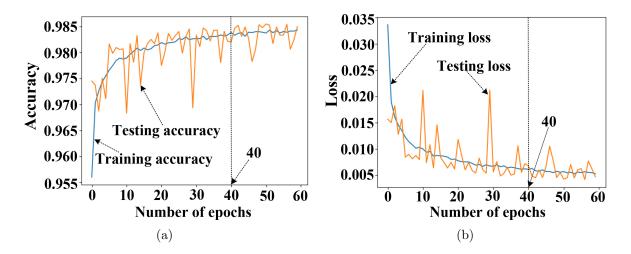

| 5.8 | Training result of the devised CNNs with 100,000 number of training data (the batch_size of the training is set as 100 and $N$ is chosen as 10). (a) Accuracy versus number of epochs. (b) Loss versus number of epochs                                                                                                                                                                                     | 90 |

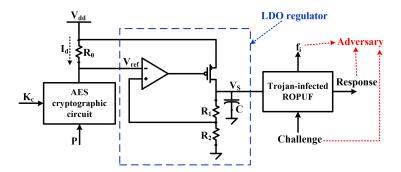

| 5.9 | Architecture of the Trojan-infected ROPUF sensor for sensing the dynamic cur-<br>rent of an AES cryptographic circuit                                                                                                                                                                                                                                                                                       | 91 |

| 5.10 | Absolute value of correlation coefficient (AVCC) versus all the possible keys for<br>the ROPUF sensors under the side-channel analysis (Hamming-weight model<br>is used). (a) Trojan-infected ROPUF sensor with 3,000 input plaintexts. (b)<br>Trojan-free ROPUF sensor with 1 million input plaintexts                                                                                     | 95  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

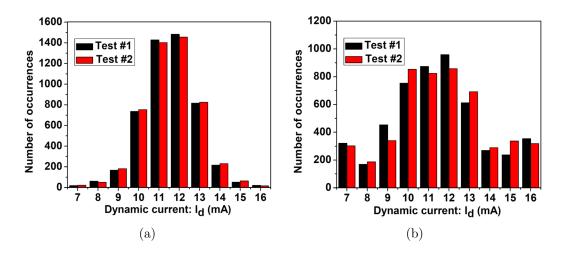

| 5.11 | Distributions of the sensed data after executing two independent tests (each test contains 5,000 sensed data). (a) An AES cryptographic circuit with a Trojan-free ROPUF sensor. (b) An AES cryptographic circuit with a Trojan infected ROPUF sensor                                                                                                                                       | 97  |

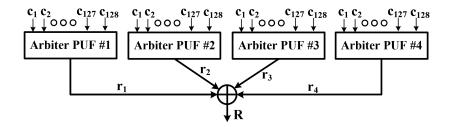

| 6.1  | Basic architecture of a 128-bit XOR arbiter PUF $(r_1, r_2, r_3, r_4, \text{ and } R \text{ are single bit data})$                                                                                                                                                                                                                                                                          | 102 |

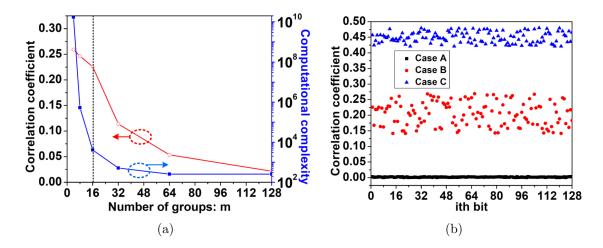

| 6.2  | Correlation analyses for the original input challenge $(c_1, c_2,, c_{128})_2$ and new<br>input challenge $(c_1^*, c_2^*,, c_{128}^*)_2$ . (a) Correlation coefficient (between $c_1^*$ and<br>$\sum_{i=1}^{128} c_i^*$ ) and computational complexity versus number of group $m$ . (b) Cor-<br>relation coefficient versus $i_{th}$ bit for Case A, Case B, and Case C $(m = 16) \ldots 1$ | 102 |

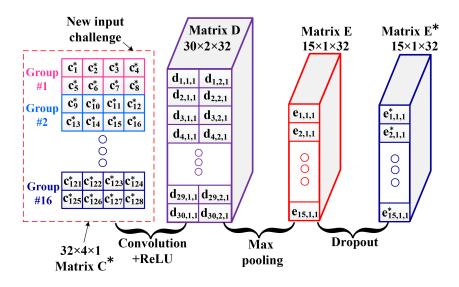

| 6.3  | Convolutional layer of the SC-assisted CNN attack for modeling the 128-bit XOR arbiter PUF                                                                                                                                                                                                                                                                                                  | 104 |

| 6.4  | Training result of the SC-assisted CNN attack on the 128-bit XOR arbiter PUF.<br>(a) Accuracy versus number of epochs. (b) Loss versus number of epochs 1                                                                                                                                                                                                                                   | 105 |

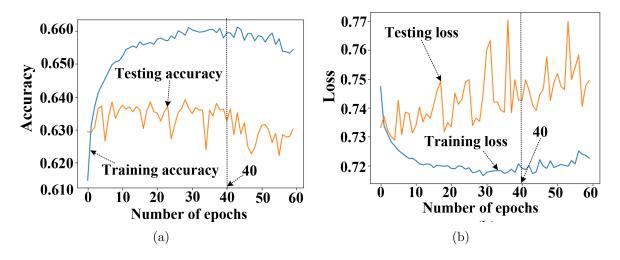

| 6.5  | Training result of the regular CNN attack on the 128-bit XOR arbiter PUF. (a)<br>Accuracy versus number of epochs. (b) Loss versus number of epochs                                                                                                                                                                                                                                         | 106 |

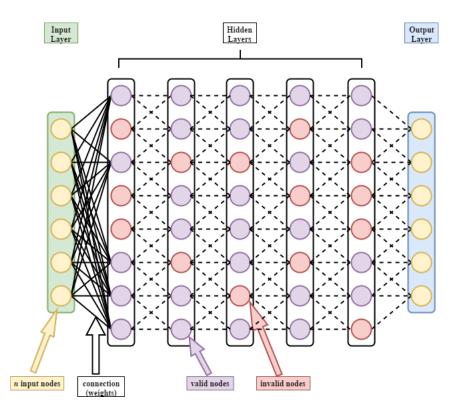

| 8.1  | Conceptual floorplan of neural network PUF-like module 1                                                                                                                                                                                                                                                                                                                                    | 11  |

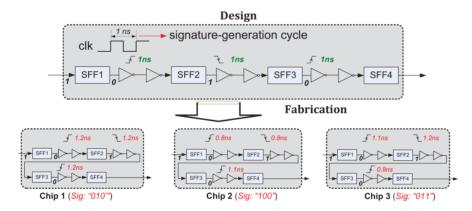

| 8.2  | Illustration of PUF realization using on-chip scan structure [7] 1                                                                                                                                                                                                                                                                                                                          | 14  |

### CHAPTER 1

# INTRODUCTION

#### 1.1 HARDWARE SECURITY

What is the trend of computer technology in the next decade? This holds a big question mark for researchers for almost a century. The answer changes dramatically: from a huge monster ENIAC to a cute Alexa set, from the rising of Moore's Law to the prototype of quantum computer, and even from an Intel 4004 with frequency at 104 kHz to an AMD Threadripper 3970 with frequency at 4.6GHz. Questions come and go. The secure system, however, holds its extraordinary vitality in every generation and grows up to a prosperous subject, cybersecurity, today. Except for traditional software secure methods that are still under updating to meet our current Internet environment, some innovate hardware-based threats are recently proposed and request higher demands on hardware designs. Due to the new hardware attacking methods and the increasing distribution of Internet of things (IoT) devices, hardware security is proposed as an extended protection solution of conventional software-based cryptographic system.

Different from conventional software-based threats, hardware threats aim at seeking for vulnerabilities in signal leakage, design defects, and/or insert malicious hardware devices to bypass software countermeasures in higher network layers. Due to the design demand for better performance, most current chip designs tend to think little of protections of hardware signals. Those physical leakages, in return, can be used for mathematical analysis and for further extraction of confidential information. Consequently, some countermeasures are proposed to hide/encrypt those secrets in physical designs.

Although some models of threats and their countermeasures are presented and proved to be of potential research value to cybersecurity studies, the industries are still not aware of the importance of hardware protections in some ways. First of all, the investmentyield ratio is still the prior consideration of the market. The pursuit of Moore's law is not just for the need of higher performance but also for the commercial competition in the chip market. If a secure hardware design consumes too much system source such as area, power, heating, etc, the reduction of performance will drive consumers to select other brands. Moreover, hardware threats have not caused severe secure information panic. This is mainly because hardware-based attacks are usually stealthy and requires ancillary equipment to extract and analyze physical signals, which makes information stealing from hardware difficult to ordinary people. In addition, some hardware attacks like hardware Trojan can only be implemented during fabrications. This means the reveal of vulnerabilities can only be achieved by designers. The detection of the information leakage would cause excess costs.

Opposite to the sluggish reaction of the market, hardware threats develop greatly due to the growth of advanced technologies. On the one hand, some work already proved that physical threats combined with high-level anti-detection designs are more aggressive to confidential information [8, 9, 10]. On the other hand, machine learning (ML) introduces some innovate vulnerabilities, giving even more challenges to secure hardware designs [11, 12]. As a result, comprehensive hardware security designs with considerations of both hardware and software attacks would be the final solution to cater to the market. Limited by those conditions, it can be foreseen that future secure hardware devices should be of features that include but not limit to:

- Design on existing functional devices instead of independent secure hardware modules. Although independent hardware modules provide more secure protection mechanisms, the overheads of speed, power, and area require hardware designers to sacrifice some hardware performance to achieve the encryption standard.

- Considerations of jointly resisting side-channel attacks (SCA) and ML attacks. With more IoT devices applied and distributed under unsupervised, leaked physical signal can be targeted and extracted more easily. With the growth of ML technologies, traditional countermeasures to SCA need to be redesigned to confront ML attacks.

- Detection of hardware Trojan need to be aware. Some pre-implemented hardware Trojans tend to negate cryptographic modules.

#### **1.2 SIDE-CHANNEL ATTACKS**

Oriented from the natural flaws of switching characteristics in modern complementary metal oxide semiconductors (CMOS), some features or functionality can be analyzed with leaked physical signals. Depending on measurement equipment that is used by attackers, heat, power, time delay, and many more measurement dimensions can be monitored by attackers. Many published papers have proved that side channel attacks are of higher efficiency to modern encryption systems [13, 14, 15, 16]. Among all attacking techniques of side channel attacks, power analysis attacks are most referred and studied. Depending on complexity of attacks and types of analyzed power, power analysis attacks can be categorized as simple power analysis, differential power analysis (DPA), and leakage power analysis (LPA). Fig. 1.1 shows an experimental result of simple power analysis attacks [1]. In this early study, it has been proved that the Hamming weight of the byte being processed is proportional to the height of the power consumption pulse. However, due to the awareness of power analysis attacks, current hardware designs are usually attached with SCA-resistant designs at either circuit level and architecture level [17]. As a result, DPA and LPA are mainstream researches of current side-channel attacks in which the former focuses on analysis of relationship between confidential information and dynamic power consumption while the latter cares more on mathematical analysis on static power traces. Comparing to DPA attacks, LPA attacks are more dangerous to our cryptographic systems. Djukanovic *et al.* [18] perform LPA attacks on various DPA-resistant logic styles and reveal LPA attacks are effective in extracting confidential information in both CMOS bit sliced circuits and CMOS combinational circuits (e.g., S-boxes).

Conventional countermeasures to power analysis attacks emphasize the reduction of dependency of side-channel leakage and power consumption profile. The power consumption, first of all, can be mitigated by redesigning on CMOS devices. A well designed magnetic tunnel junction CMOS can produce uniform power consumption during operation [19]. By introducing user-defined security metric using constrained state assignment, the power footprint can be encoded [20], making it impossible to reveal the correlation between confidential information and leaked power. A multi-core processor combining Random Dynamic Task Scheduling, Random Dynamic Frequency Scaling, and Random Dynamic Phase Adjustment

Fig. 1.1: Hamming weight information can be extracted from leaked signal of power consumption [1].

is proved to be of resistance to DPA attacks [21]. Although randomized input can be utilized to arbitrary initial input values on an AES circuit [22], innovate power analysis methods using convolutional neural networks [23, 24, 25] are still challenging hardware designers to push the complexity of secure designs to a higher level. Other than the competition to advanced attacking approaches, another straits in designing countermeasures to SCA is the limitation of power budget and area restriction. Some researchers raise their ideas on low-overhead secure designs to particular side-channel attack method [26, 27]. However, to design an architecture to obstruct all potential physical leakages is still expensive.

#### **1.3 PHYSICAL UNCLONABLE FUNCTION DEVICES**

Physical Unclonable Function (PUF) devices are innovate circuit primitives that exploit inherent manufacturing profess variations as natural random variables to realize some secure functions in physical level [28]. According to the specific architecture design, different physical parameters, such as voltage, time delay, frequency, etc., can be utilized as referred variables in comparison. In this way, binary input sequences drive the designed PUF primitive to generate random outputs, which form the core security parameter called challenge response pairs (CRPs). On the basis of the scale of generated CRPs, a weak PUF is defined as a PUF that generates a countable set of obtainable CRPs, while a PUF primitive that generate relative infinite CRPs is called strong PUF. With their inherent random feature, the internal arithmetic logic and characteristic parameter are usually unpredictable until the measurement collection after fabrication. Thus, each PUF is unique to its circuit layout and is hard to replicate in practice. This makes PUF devices excellent candidacy in security applications such as authentication, key generation, and noise generation [28, 29].

Up to date, variant PUF primitives are invented to meet the demand of different scenarios. Arbiter PUF [30] utilize delay features in logic gates and realize early strong PUF. A SRAM-PUF uses the power-up states of a SRAM cell to realize logical PUF design, making it a practical ID/key generator in micro-controllers. Besides, ring-oscillator (RO) PUFs are inspired by its multi-input and lightweight features. It is also widely used as protection mechanisms in distributed wireless sensor networks.

Nonetheless, associating with the spreading application of PUFs and the design of new PUF primitives, what we cannot ignore are potential risks under attacks and the demand of market. Initially, most proposed PUF designs rely on highly linear comparing logic, which is usually vulnerable to machine learning attacks. Moreover, PUF devices are always implemented as an independent security unit instead of a functional module that promote performance of devices. This will obviously introduce considerable overhead and occupy system resources. Consider the contradiction to the pursuit of profits, only devices that requires special protection or are exposed to a vulnerable environment will be allocated with protections of PUFs. With the quickening spreading of IoT devices, more intelligent devices will become preys of potential malicious attacks. Consequently, there is an urgent need for a bran-new design standard for PUFs to accommodate the demand of security and overhead.

#### **1.4 MACHINE LEARNING**

Machine learning (ML) is an interdisciplinary subject that exploits theories of probability, statistics, approximation, convex analysis, etc. to endow computers machines to imitate human's learning process from prior experience in order to obtain new knowledge or desired functions. As a cutting edge technology in artificial intelligence, ML has been proved to be beneficial in applications of medicine, genetics, data mining, and more promising research fields [31, 32, 33]. According to the demand of tasks, data analysts are capable to design their own neural networks and inject validating learning data that leads our machines to achieve particular functions. Those learning processes are usually categorized as supervised learning and unsupervised learning that are practical in classification, regression, data description, etc [34]. With the massive advent of software development environment/kits [35, 36, 37], to design a customized network is no longer a monopoly to data researchers and engineers. More educational resources are infused into this field, making ML a booming industry and the hottest topic today.

However, just like every story that we learned from our history, a rising technology is a double bladed sword. Except for the excellent performance in the technology revolution, we can never ignore potential risks since ML is also a dangerous tool for attackers. As hardware security engineers, we know more about this. In this section, more details will be highlighted in how ML is applied in defense and attack mechanisms.

#### 1.4.1 MACHINE LEARNING ATTACKS IN HARDWARE SYSTEM

Early investigations of malicious hardware-based attacks tend to hypothesize that attackers extract physical signals from defects of designs and perform mathematical analysis according to collected information. Recent studies [38, 39] demonstrate machine learning models exhibit extensive potentials in data mining and analysis, extensively reducing the time cost in extracting confidential information from physical signals. Owing to the cruel environment of competition, devices' resistance against machine learning attacks is proposed as a new design criterion to all new secure hardware design. At present, the application of machine learning attacks are usually categorized into two main aspects. One direction of attacks attempts to adopt machine learning as auxiliary tools of mathematical analysis in revealing secret information.

Fig. 1.2 shows an example of profiling attack using ML learning as its modeling tool. The side-channel signals are initially collected from targeted hardware devices. By injecting adequate number of input data and objective physical signals which contains potential correlation to confidential information, a training data set is thus established. In this case, the constructed neural network is regarded as a black box whose learning results may describe the relationship in given training samples. If the training dataset is large enough and the network model is well constructed, the trained model should be capable in imitating the inner logic of the cryptographic chip. By means of ML, attackers will no longer bother to

Fig. 1.2: Profiling-based side-channel analysis attack using machine learning as modeling tools: (a) profiling phase; (b) attack phase [2]

attempt different secret keys or build specific mathematical models. A well-trained model is sufficient for attackers to manipulate the hardware system as desired.

Another malicious ML attack model that we have to face today is IC overbuilding, a modeling attack that aims to crack the authentication system of PUF devices. The operation of data extraction and model training are similar to aforementioned side-channel attacks. In practice, SVM, logistic regression, and more advanced DNN architectures are used as cracking models to PUF primitives.

# 1.4.2 MACHINE LEARNING COUNTERMEASURES IN HARDWARE SE-CURITY

By contrast, ML possess more extraordinary capabilities in designs of hardware security.

One remarkable application is the detection of hardware Trojans. By implementing secret extracting hardware part, hardware Trojans forms malicious inclusions in hardware system that result in the degradation of performance or the failure of functions in hardware systems [2]. Due to the increasing globalization of industry have been increasing, more third-party manufacturers take part in the production of chips, raising risks that malicious inclusions to be embedded onto the primary design. Hence, the detection of malicious inclusions comes to be a pivotal mechanism in current hardware manufacture. On the basis of the dependence of the usage of golden-chips, fabricated chips that is validated as free of the infection of hardware Trojans, countermeasures to hardware Trojans can be classified as golden-chip methods and golden-chip free methods. Benefiting from machine learning, the workload of data analysis and feature extraction is greatly reduced. By using the divergences in power consumption, [40] exploits support vector machine as a golden-chip based method. An ASIC based implementation method of hardware Trojans is proposed in [41]. Simultaneously, a comprehensive detection using SVM, PCA, and side-channel extraction is introduced by the same team. In addition, more advanced researches of deep neural networks (DNN) participate in the wrestle of confidential information. [42] introduces a method that optimize non-linearity after an initial PCA analysis on hardware Trojans. A BP network is demonstrated to be efficient in accomplishing multiple Trojan detection works individually [43]. This also proves neural networks have satisfying performances in self-learning and data adaptions.

#### 1.5 HARDWARE TROJANS

Hardware Trojans are malicious hardware inclusions that leak secret information, degrade the performance of the system, or cause denial-of-service [2]. With the promotion of globalization and industrial cooperation, the production of a single chip may always involve the engagement of third-party companies. Since the confidential information is always of great appeal to attackers, commercial spies and alike information thieves tend to exploit state-of-the-art technologies and seek unusual attack approaches and vulnerabilities to steal confidential information. Under this background, hardware Trojans and their corresponding detection theories are thus proposed.

Unlike aforementioned non-invasive attack models, like ML attacks and SCA attacks, hardware Trojans is always implemented during fabrication process. For any ML attack models or SCA attack models, approaches of data extraction, methods/tools of analysis, targets of vulnerable architectures are mostly transcendental to designers or security engineers. Based on investigated vulnerabilities or accidents that happens, there are always countermeasures that obstruct the attack procedure. The detection and removal of hardware Trojans, however, is extremely difficult and troublesome. First of all, those malicious components can be very small comparing to the whole layout. Liu et al. propose two malicious inclusion designs that only introduce several diodes to achieve effective data extraction [44]. The scale of Trojans means attackers do not greatly change the function or physical signals. Thus, it is always difficult to be aware of the existence of Trojans.

Current studies of hardware Trojans pay more attention to detection of particular Trojan types. And according to usage of golden chips, chips that are free from Trojan infection, detection approaches can be categorized as golden chip-based methods and golden chip-free methods. As the name implies, golden chip-based methods require a bunch of chips that are validated free from infection. By using secure reference group, the differences between Trojan-infected chips and golden chips can be easily extracted when comparing physical divergence in between. [40] utilize the frequency domain components of power consumption traces as their reference variable and use support vector machine (SVM) to filter infected chips. A Bayesian method is used to analyze current divergences in two groups [45]. The execution path delay can also be used as examining variable. By using principle component analysis (PCA), a divergence in time delay can be detected to categorize Trojan-infected chips [46]. As for golden chip-free methods, the detection is mostly based on a known parameter dimension that physical parameters may vary between/among target groups. [44] utilize PCA as analyzing tool to map transmission power into three dimensional points and finally classify chip samples into three groups (one Trojan-free and two Trojan infected). Although a great number of papers are proposed on detection approaches of Trojan chips, some defects still exist in their detection procedures. First of all, most Trojan detection methods are proposed with a new Trojan design. Those methods are mostly valid only for the proposed Trojan chips. Moreover, some Trojan detection method only focus on one or two physical parameters. And that is under an assumption that attackers are using the particular Trojan types. As for golden chip-free methods, most proposed work only use PCA or SVM as feature extraction tools. Those methods do not specify the rationality that uses ML models. And in reality, if the Trojan type is unknown, there is no guarantee that the divergence signal can be truly extracted and used for further Trojan detection. Therefore, a general golden chip-free detection approach is still the ultimate goal in the research domain of hardware Trojans.

#### **1.6 OUR CONTRIBUTION**

Consider the current development and bottlenecks of PUF devices illustrated in Section 1.1. The trends of future secure hardware devices should manage to elevate security performance against potential attacks by means of hardware and software simultaneously. In the meantime, the reduction of excess overhead is also an essential consideration. Therefore, we propose our improved designs of secure hardware devices. Our contribution in this work is summarized as follows:

- *Chapter 2* proposes an innovate design of physical unclonable function device against machine learning attacks and side channel attacks.

- *Chapter 3* investigates features of wave dynamic differential logic (WDDL) and propose our design of a new PUF primitive against machine learning attacks and power attacks.

- *Chapter 4* reviews drawbacks of two former designs and introduces a new floorplan for PUF primitives, aiming at giving an ultimate solution to non-invasive attacks.

- *Chapter 6* designs an innovate hardware Trojan for conventional PUF primitive. A statistical method is proposed as new golden chip-free detection approach.

- *Chapter 5* aims at vulnerabilities in profiling attacks and examine the effectiveness of a new attack model that jointly use ML models and SCA models.

- *Chapter 7* summarizes all previous chapters and systematically integrates concepts of designs, vulnerability detection, and performance evaluation into a whole.

- *Chapter 8* exhibits reviews of our current work and future research plans after graduation are mapped out.

#### CHAPTER 2

# DESIGN AN INNOVATE PHYSICAL UNCLONABLE FUNCTION DEVICE WITH VOLTAGE REGULATOR

### 2.1 MOTIVATION

On-chip workload-aware multi-phase voltage regulators (WAMPVRs) is a countermeasure to power attacks<sup>1</sup>. Oriented from voltage regulation techniques, WAMPVRs aims at mitigating output power profiles while keeping small, fast efficient, high power density, and robust features of initial voltage regulators [48, 49]. By introducing random sequence control scheme, the leakage power can be mitigated to an acceptable level as well as keep a high power conversion efficiency. Converter-gating (CoGa) regulator [3] and converter-reshuffling (CoRe) regulators [50] are two typical regulating techniques. Fig. 2.1 exhibits the base architecture design of CoGa regulator and CoRe regulator. Both architectures adopt similar layout designs. In CoGa regulation scheme, the pseudo-random number generator (PRNG) will act according to the change of output power. When the power demand does not change dramatically, the control signal from the PRNG tends to remain unchanged to maintain a stable output power profile. In CoRe regulators, however, the PRNG will take former control signal as references. By keeping changing the input control sequence, the entropy value of the input sequence is elevated and more randomness can be introduced to protect the output power to be extracted and analyzed.

<sup>&</sup>lt;sup>1</sup>The content of this Chapter partially has been published in [47].

Fig. 2.1: CoGa regulator in [3] (8-phase) introduces PRNG to realize the mitigation of output power profiles.

In the aforementioned architecture of CoRe voltage regulator, the input sequence is under controlled by a PRNG, which can be served as a binary sequence input. Besides, all flying capacitors are interleaved with shifted clocks. If we take flying capacitors in each stage as random outcomes of manufacturing fabrication and the capacitance discrimination can be detected and compared, the output power should produce a sensible difference even two identical input sequences are applied on two CoRe voltage regulators. Consequently, CoRe voltage regulator can be easily redesigned as a new PUF. Since the new PUF is designed on a functional device, the overhead of the PUF is greatly reduced compared to traditional SRAM PUF, arbiter PUF, or ring-oscillator (RO) PUF. Those traditional PUF primitives only provide security features which introduce losses in power and area. In this research, we would like to provide an innovate thinking of PUF design, by which we can consider whether we can design and implement PUF primitives on an existing device in our current computer architecture.

#### 2.2 BACKGROUND

The workload-aware multi-phase voltage regulators (WAMPVRs) like converter-gating (CoGa) voltage regulator [3] and converter-reshuffling (CoRe) voltage regulator [50] are designed based on multi-phase switched capacitor (SC) voltage converters. Integrating WAMPVRs fully on-chip is an efficient solution for reducing the power conversion loss and strengthening the robustness of modern ICs against power attacks [3, 50]. As demonstrated in [3, 50], increasing the total number of phases for the WAMPVRs can result in significant improvements of the power conversion efficiency and the security against power attacks. Accordingly, the designs of on-chip voltage regulators with more than 120 phases have been frequently reported in the recent literatures [51, 52].

In the design of a 2:1 (Input voltage/output voltage = 2:1) 32-phase on-chip SC voltage converter, the simulated output voltage ripples are shown in Fig. 2.2. Case 1 (as shown in Fig. 2.2(a)) and Case 2 (as shown in Fig. 2.2(b)) indicate that different number of activated phases can generate different output voltage ripple signatures. Furthermore, when we compare Case 2 with Case 3 in Fig. 2.2(b) and 2.2(c), under the same number of active phases, the output voltage ripples are also different if the sequences of activation pattern are different.

In a multi-phase SC voltage converter, the output voltage ripple is extremely sensitive to the flying capacitance in each sub-phase [3]. Since the flying capacitor in each subphase is identically designed, the physical randomness of the flying capacitor induced by the fabrication process enables the multi-phase SC converter to be eligible for building PUF architectures.

Fig. 2.2: Output voltage ripples of a 2:1 32-phase SC converter. a Case 1: Sequence of activation pattern (8 active phases): (7, 12, 13, 18, 20, 25, 27, 31). b Case 2: Sequence of activation pattern (16 active phases): (1, 2, 3, 4, 6, 8, 9, 14, 15, 16, 22, 23, 26, 28, 29, 30). c Case 3: Sequence of activation pattern (16 active phases): (2, 5, 6, 9, 10, 11, 14, 16, 19, 23, 24, 26, 28, 29, 30, 32)

#### 2.3 ARCHITECTURE DESIGN

The architecture of a workload-aware multi-phase voltage regulator (WAMPVR)-based strong PUF primitive is devised in Fig. 2.2. Two identically designed 32-phase switchedcapacitor (SC) voltage converters:  $Block_1$  and  $Block_2$  are utilized to build the strong PUF architecture. The output port of the  $j^{th}$   $(j = 1, 2, \dots, 32)$  phase of the SC converter in Block<sub>i</sub> (i = 1, 2) connects with the switch  $W_{i,j}$ . Moreover, a 32-bit phase number generator (PNG) is utilized to control the activation behaviors of the switches  $W_{i,1}, W_{i,2}, \dots, W_{i,32}$ to determine the sequences of active phases that are used for building the strong PUF. For example, if only the switches  $W_{i,2}, W_{i,5}, W_{i,12}$ , and  $W_{i,18}$  are turned on by the PNG, the output voltage ripples of phase #2, phase #5, phase #12, and phase #18 of the SC converters are selected for generating the PUF response. Since a 32-bit PNG can generate  $\binom{32}{0} + \binom{32}{1} + \binom{32}{2} + \cdots + \binom{32}{32} = 2^{32}$  different activation patterns, therefore, the total number of raw challenge-to-response pairs (CRPs) of the WAMPVR-based strong PUF primitive are  $2^{32}$ .

As shown in Fig. 2.3, the mismatches of voltage ripple between  $V_{out,1}$  and  $V_{out,2}$  are magnified through employing an operational amplifier. Four pipelined SC circuits (*SC circuit* #1, ..., and *SC circuit* #4, as shown in Fig. 2.3) are utilized to convert the high-frequency voltage ripple mismatch  $V_a$  into the critical voltage  $V_{a,1}$  for generating the secret authentication data B. Furthermore, each SC circuit has four independent working phases: *charging* phase, *charge-sharing* phase, *output* phase, and *discharging* phase. For example, as shown in Fig. 2.3, if *SC circuit* #1 is in *charging* phase, the switch  $S_{1,1}$  will be turned on. Then the positive component of  $V_a$  will charge the capacitor  $C_{1,2}$  while the negative component of  $V_a$  will charge the capacitor  $C_{1,1}$ . Once the *charging* phase ends, the switch  $S_{1,1}$  will be turned off while the switch  $S_{1,2}$  will be activated to balance the charge of the capacitors  $C_{1,1}$  and  $C_{1,2}$ . After the *charge-sharing* phase, the *SC circuit* #1 will output the sampled critical voltage  $V_{a,1}$  to generate the binary authentication data *B* by activating the switch

Fig. 2.3: Architecture of the WAMPVR-based strong PUF primitive (the total number X of phases in the original WAMPVR is 64, the resistors  $R_{1,1}$ ,  $R_{2,1}$ ,  $R_{1,2}$ ,  $\cdots$ , and  $R_{2,32}$  are designed with the same resistance R, and the capacitors  $C_{1,1}$ ,  $C_{1,2}$ ,  $C_{2,1}$ ,  $\cdots$ , and  $C_{4,2}$  are also designed with the same capacitance C).

$S_{1,3}$ . If the voltage  $V_{a,1} \ge 0$  V, the authentication data *B* outputs logic value "1". Otherwise, B = 0. In the final stage (*discharging* phase), the residual charge in the capacitors  $C_{1,1}$  and  $C_{1,2}$  will be cleared to initialize the next data sampling through turning on the  $S_{1,4}$  switches. The main intention of employing *discharging* phase is to break the correlation between the current data and the history data against machine-learning attacks. Please note that in each SC circuit, the behaviors of the switches  $S_{h,1}$ , (h = 1, 2, 3, 4),  $S_{h,2}$ ,  $S_{h,3}$ , and  $S_{h,4}$  are mutually exclusive. Additionally, as shown in Fig. 2.3, there are two different

kinds of diodes: back-biased diode  $D_{h,1}$  and forward-biased diode  $D_{h,2}$  exist in each SC circuit. The main role of these diodes is working as a non-linear transformation block to generate the non-linear output response B against machine-learning attacks, which will be fully discussed in Section 2.4.

#### 2.4 EVALUATION

#### 2.4.1 PERFORMANCE EVALUATION

Two most significant metrics that are selected to evaluate the PUF characterization are the inter-Hamming distance (HD) and the intra-HD (reliability) [53, 51, 54]. Inter-HD measures the distinctness between two different PUF devices while intra-HD (reliability) represents the stability of a single PUF device under different temperatures and supply voltages.

In Fig. 2.3, assume the resistors  $R_{1,1}$ ,  $R_{2,1}$ ,  $R_{1,2}$ ,  $\cdots$ , and  $R_{2,32}$  are designed with a high resistance R to reduce the overall power consumption of the WAMPVR-based strong PUF primitive. As a result, under the same process variation, the mismatch rate of these resistors  $R_{1,1}$ ,  $\cdots$ , and  $R_{2,32}$  will be negligible as compared to the mismatch rate of the flying capacitors in the SC converters. Hence, in Fig. 2.3, the output voltage  $V_{out,i,j}$  of the  $j^{th}$   $(j = 1, 2, \cdots, 32)$  phase of the SC converter in  $Block_i$ , (i = 1, 2) can be denoted by a function F, as shown below

$$V_{out,i,j} = F\left(C_{i,j}^{s}, V_{dd}, T_{C}, t + (j-1)\frac{T_{S}}{32}\right)$$

(2.1)

where  $C_s$  is the flying capacitance of the  $j^{th}$  phase of the SC converter in  $Block_i$ .  $V_{dd}$ ,  $T_C$ ,  $T_S$ ,

and t, respectively, are the supply voltage, the environmental temperature, the switching period of the SC converters, and the timing of the 1<sup>st</sup> phase of the SC converters. Let us assume the supply voltage  $V_{dd}$  and the environmental temperature  $T_C$  are time invariant. As a result, the critical parameters:  $C_S, V_{dd}, T_C$ , and t are mutually independent. Then the output voltage  $V_{out,i,j}$  can be approximated as<sup>2</sup>

$$V_{out,i,j} = F\left(C_{i,j}^{s}, V_{dd}, T_{c}, t + (j-1)\frac{T_{s}}{32}\right)$$

$$= F_{1}\left(C_{i,j}^{s}\right) \times F_{2}\left(V_{dd}\right) \times F_{3}\left(T_{c}\right) \times F_{4}\left(t + (j-1)\frac{T_{s}}{32}\right)$$

$$\approx \left(\sum_{i_{1}=0}^{m_{1}} a_{i_{1}}(C_{i,j})^{i_{1}}\right) \times \left(\sum_{i_{2}=0}^{m_{2}} b_{i_{2}}(V_{dd})^{i_{2}}\right) \times \left(\sum_{i_{3}=0}^{m_{3}} c_{i_{3}}(T_{c})^{i_{3}}\right)$$

$$\times \left(\frac{d_{0}}{2} + \sum_{i_{4}=1}^{m_{4}} d_{i_{4}}\cos\left(\frac{2\pi i_{4}}{T_{S}}\left(t + (j-1)\frac{T_{s}}{32}\right)\right)\right)$$

$$+ \sum_{i_{4}=1}^{m_{4}} e_{i_{4}}\sin\left(\frac{2\pi i_{4}}{T_{S}}\left(t + (j-1)\frac{T_{s}}{32}\right)\right)$$

(2.2)

where  $F_1(C_{i,j}^S)$ ,  $F_2(V_{dd})$ ,  $F_3(T_C)$ , and  $F_4(t + (j - 1)\frac{T_s}{32})$ , respectively, are the voltage components of  $V_{out,i,j}$  that are determined by  $C_{i,j}^S$ ,  $V_{dd}$ ,  $T_C$ , and  $(t + (j - 1)\frac{T_s}{32})$ .  $\sum_{i_1=0}^{m_1} a_{i_1}(C_{i,j})^{i_1}$ ,  $\sum_{i_2=0}^{m_2} b_{i_2}(V_{dd})^{i_2}$ , and  $\sum_{i_3=0}^{m_3} c_{i_3}(T_C)^{i_3}$  are the approximated polynomial expansions of  $F_1(C_{i,j}^S)$ ,  $F_2(V_{dd})$ , and  $F_3(T_C)$ , respectively.  $a_{i_1}(i_1 = 0, 1, \cdots, m_1)$ ,  $b_{i_2}(i_2 = 0, 1, \cdots, m_2)$ , and  $c_{i_3}(i_3 = 0, 1, \cdots, m_3)$ , respectively, are the coefficients of  $(C_{i,j})^{i_1}$ ,  $(V_{dd})^{i_2}$ , and  $(T_C)^{i_3}$ .  $m_1$ ,  $m_2$ , and  $m_3$  are the degrees of the approximated polynomials of  $F_1(C_{i,j}^S)$ ,  $F_2(V_{dd})$ , and  $F_3(T_C)$  respectively.  $d_0, d_1, \cdots, m_4, e_1, e_2, \cdots, e_{m_4}(m_4)$  are the coefficients (degree) of the

<sup>&</sup>lt;sup>2</sup>As demonstrated in Fig. 2.2, the output voltage of an SC converter is a periodical signal. Therefore, the voltage component of  $V_{out,i,j}$  related with the timing t can be unfolded with Fourier series.

approximated Fourier series of  $F_4(t + (j-1)\frac{T_s}{32})$ . If the supply voltage  $V_{dd}$ , the environmental temperature  $T_C$ , and het timing t are fixed, through matching the relationship curve between the capacitance  $C_{i,j}^s$  and the output voltage  $V_{out,i,j}$ , the coefficients  $a_0, a_1, \dots$ , and the degree  $m_1$  for  $F_1(C_{i,j}^S)$  can be unriddled. The coefficients and the degrees of  $F_2(V_{dd})$ ,  $F_3(T_C)$ , and  $F_4(t + (j-1)\frac{T_s}{32})$  can also be estimated in a similar way.

Once the complete expression of the output voltage  $V_{out,i,j}$  is obtained, the following step is to model the mismatches of output voltage ripple between  $Block_1$  and  $Block_2$  in Fig. 2.3. Assume the 32-bit PNG in Fig. 2.3 generates the 32-bit binary data  $W = (w_1, w_2, \dots, w_{32})_2$ to select a certain number of active phases of the SC converters for building a strong PUF for authentication by controlling the activation patterns of the corresponding switches.<sup>3</sup> As a result, by using the Kirchhoff's law, the voltages  $V_{out,1}$  and  $V_{out,2}$  in Fig. 2.3 can, respectively, be derived as

$$V_{out,1} = \frac{\sum_{j=1}^{32} w_j V_{out,i,j}}{R} \times \frac{R}{\sum_{j=1}^{32} w_j}$$

$$= \frac{\sum_{j=1}^{32} w_j V_{out,i,j}}{\sum_{j=1}^{32} w_j}$$

(2.3)

$$V_{out,1} = \frac{\sum_{j=1}^{32} w_j V_{out,2,j}}{R} \times \frac{R}{\sum_{j=1}^{32} w_j}$$

$$= \frac{\sum_{j=1}^{32} w_j V_{out,2,j}}{\sum_{j=1}^{32} w_j}$$

(2.4)

$<sup>\</sup>overline{{}^{3}w_{1}, w_{2}, \cdots, w_{32}}$  control the activation behaviors of the switches  $W_{1}, W_{2}, \cdots, W_{32}$  respectively. If  $w_{j} = 1$ , the switches  $W_{1,j}$  and  $W_{2,j}$  are turned on, and vice versa.

Then the voltage ripple mismatch  $V_a$  in Fig. 2.3 is

$$V_a = A_v \left( V_{out,2} - V_{out,1} \right) = A_V \frac{\sum_{j=1}^{32} w_j \left( V_{out,2,j} - V_{out,1,j} \right)}{\sum_{j=1}^{32} w_j}$$

(2.5)

For the WAMPVR-based strong PUF primitive in Fig. 2.3, assume the switching period of the SC circuits is designed equal to four times of the switching period of the SC converters and the pulse width of all the switches  $S_{1,1}, S_{1,2}, \dots, S_{4,4}$  in SC circuits is 25%. If *SCcircuit*1 is in *charging* phase, the switch  $S_{1,1}$  is in on-state. The voltages  $V_a^*$  and  $V_a^{**}$  of the capacitors  $C_{1,1}$  and  $C_{1,2}$  in Fig. 2.3, respectively, are

$$V_{a}^{*} = \begin{cases} V_{a} - V_{b} , V_{a} \ge V_{b} \\ 0 , V_{a} < V_{b}, \end{cases}$$

$$V_{a}^{*} = \begin{cases} V_{a} + V_{b} , V_{a} \le V_{b} \\ 0 , V_{a} > V_{b}, \end{cases}$$

$$(2.6)$$

$$(2.7)$$

where  $V_b$  is the forward-biased threshold voltage of the diodes  $D_{1,1}$  and  $D_{1,2}$  in Fig. 2.3. When *SCcircuit* 1 enters into *output* phase, since the capacitors  $C_{1,1}$  and  $C_{1,2}$  are designed with the same capacitance C, the critical voltage  $V_{c,1}$  in Fig. 2.3 can be denoted as

$$V_{a,1} = \frac{\int_{t}^{t+T_s} C_{1,1} \frac{dV_a^*}{dt} dt + \int_{t}^{t+T_s} C_{1,2} \frac{dV_a^{**}}{dt} dt}{C_{1,1} + C_{1,2}}$$

$$= \frac{\int_{t}^{t+T_s} \left(\frac{dV_a^*}{dt} + \frac{dV_a^{**}}{dt}\right) dt}{2}$$

(2.8)

Therefore, if the critical voltage  $V_{a,1} \ge 0$  V, the output binary data B = 1. Otherwise,

B = 0.

Assume N number of WAMPVRs are utilized for building a strong PUF primitive to generate the N-bit binary authentication data  $\overline{B}$ . As a result, if K strong PUF primitives are selected for evaluating the uniqueness, the inter-HD E is written as [55]

$$E = \frac{2}{K(K-1)} \sum_{k_1=1}^{K-1} \sum_{k_2=k_1+1}^{K} \frac{\bar{B}_{k_1} \oplus \bar{B}_{k_2}}{N} \times 100\%$$

(2.9)

where  $\bar{B}_{k_1}$   $(k_1 = 1, 2, \dots, K-1)$  and  $\bar{B}_{k_2}$   $(k_2 = k_1 + 1, k_1 + 2, \dots, K)$ , respectively, are the *N*-bit binary authentication data generated by the  $k_1^{th}$  and  $k_2^{th}$  strong PUF primitives.

Similarly, for a single PUF primitive, if M number of different environmental settings are considered, the reliability of the strong PUF primitive G can be expressed as [55]

$$G = \left(1 - \frac{1}{M} \sum_{l=1}^{M} \frac{\bar{B}_{0}^{*} \oplus \bar{B}_{l}^{*}}{N}\right)$$

(2.10)

where  $\bar{B}_0^*$  and  $\bar{B}_l^*$  are the *N*-bit binary authentication data generated by the single PUF primitive under the ideal and  $l^{th}$   $(l = 1, 2, \dots, M)$  environmental setting, respectively.

All of the aforementioned parameters in the mathematical model of the designed WAMPVRbased strong PUF primitive are extracted from the 130 nm CMOS technology kits in Cadence. As shown in Fig. 2.4, by applying the Monte Carlo simulation into the aforementioned mathematical model, the inter-HD E of the WAMPVR-based strong PUF primitive is about 51.3% ( $L_g = 130$  nm). Furthermore, if the scaling of CMOS technology is considered, through utilizing the mismatch rates of capacitors under different CMOS technologies from [17], the inter-HD E of the technology-scaled WAMPVR-based strong PUF primitive

Fig. 2.4: Performance evaluation for the designed strong PUF primitive. (a) Inter-HD E versus gate length  $L_g$  (K = 100 and N = 32). (b) Reliability G versus supply voltage  $V_{dd}$  and environmental temperature  $T_c$  (M = 50 and N = 32).

can also be predicted. Related experiment results are as shown in Fig. 2.4(a). When the CMOS technology is scaled from 130 nm to 14 nm, the inter-HD, E is improved from 51.3% to 50.1%. That indicates a larger capacitance mismatch rate induced by a shorter gate length enables the WAMPVR-based strong PUF primitive to achieve a better uniqueness. Additionally, the reliability G of the designed WAMPVR-based strong PUF primitive is assessed in Fig. 2.4(b). Concluded from results above, the ideal environmental setting for the strong PUF primitive is: the ambient temperature  $T_c = 27$ . As shown in Fig. 2.4(b), the worst reliability of the designed WAMPVR-based strong PUF primitive is 98.5% when  $V_{dd} = 2.9$  V.

Fig. 2.5: Absolute value r of correlation coefficient between  $P_{in}$  and  $\Delta C$  versus phase number X against side-channel attacks.

# 2.4.2 SECURITY AGAINST SIDE-CHANNEL ATTACKS

### Side-Channel Leakage Analysis

If an X-phase (assume X is even) WAMPVR is utilized for devising a strong PUF architecture, the number of phases in  $Block_1$  and  $Block_2$  in Fig. 2.3 is X/2. Since all the phases in  $Block_1$  and  $Block_2$  are active all the time, the input power of the WAMPVR-based strong PUF primitive is a constant within a switching period  $T_s$  regardless the variations of process, voltage, and temperature (PVT). However, if the mismatches of the flying capacitors in the SC converters induced by the random fabrication process are considered, the total input power  $P_{in}$  of the WAMPVR-based strong PUF primitive within a switching period  $T_s$

can be expressed as

$$P_{in} = \sum_{i=1}^{2} \sum_{j=1}^{X/2} C_{i,j}^{S} f_s V_{dd}^2$$

(2.11)

where  $f_s$  is the switching frequency of the SC converters.

Since the attacker may leak the mismatches of the flying capacitors in the SC converters through analyzing the input power  $P_{in}$ , the absolute value r of correlation coefficient between the input power  $P_{in}$  and the capacitance mismatch  $\Delta C = C_{2,j}^S - C_{1,j}^S$  is studied against sidechannel attacks. As shown in Fig. 2.5, the correlation coefficient between  $P_{in}$  and  $\Delta C$  is about 0.0037 when the phase number X = 64, which indicates a good robustness against side-channel attacks. Moreover, if the phase number X increases, the correlation coefficient between  $P_{in}$  and  $\Delta C$  will be further reduced against side-channel attacks.

## **Implementation of Side-Channel Attacks**

The main intention of implementation of implementing side-channel attacks on the WAMPVR-based strong PUF primitive is unriddling the output response B by analyzing the critical side-channel leakage. If the input power  $P_{in}$  of the proposed strong PUF device is tailored as the critical side-channel leakage, the relationship between the input power  $P_{in}$  and the output response B needs to be studied when side-channel attacks are executed. Since the random fabrication process and circuit noise conform to normal distributions [55, 56], if the variations of PVT are considered, the input power  $P_{in}$  can be further derived as

$$P_{in} = \sum_{i=1}^{2} \sum_{j=1}^{X/2} C_{i,j}^{S} f_{s} V_{dd}^{2}$$

$$= \frac{1}{\sqrt{2\pi X} \sigma_{c}} \exp\left(-\frac{\left(\sum_{i=1}^{2} \sum_{j=1}^{X/2} C_{i,j}^{S} - X \mu_{C}\right)^{2}}{2X \sigma_{c}^{2}}\right)$$

$$\times \frac{1}{\sqrt{2\pi} \sigma_{f}} \exp\left(-\frac{\left(f_{s} - \mu_{f}\right)^{2}}{2X \sigma_{c}^{2}}\right)$$

$$\times \left(\frac{1}{\sqrt{2\pi}] \sigma_{c}} \exp\left(-\frac{\left(V_{dd} - \mu_{v}\right)^{2}}{2\sigma_{v}^{2}}\right)\right)^{2}$$

(2.12)

where  $\mu_c(\sigma_c)$ ,  $\mu_f(\sigma_f)$ , and  $\mu_v(\sigma_v)$  are the means (standard deviations) of the flying capacitance, switching frequency, and supply voltage of the proposed strong PUF device, respectively.

So as to model the relationship between the input power  $P_{in}$  and the output response B, let us define a function  $F^*(P_{in})$  and approximate the function  $F^*(P_{in})$  with a polynomial expansion  $F^{**}(P_{in})$  as shown below

$$F^*(P_{in}) \approx \sum_{k=0}^{K^*} f_k^* \times (P_{in})^k = F^{**}(P_{in})$$

(2.13)

where  $K^*$  is the degree of the approximated polynomial and  $f_k^*$  is the coefficient of  $(P_{in})^k$ . Assume that Z is the number of input power and output response pairs:  $(P_{in,1}, B_1), (P_{in,2}, B_2),$  $\cdots$ , and  $(P_{in,Z}, B_Z)$  of the proposed strong PUF primitive are selected for analysis, then the matching error  $\Delta L$  between the input power  $P_{in}$  and the output response B with the polynomial expansion  $F^{**}(P_{in})$  can be expressed as

Fig. 2.6: Prediction accuracy  $r_1$  of power attacks versus standard deviations  $\delta_f$  and  $\delta_v$  after analyzing 1 million input power and output response pairs (The colors and contours represent the variation values of the prediction accuracy  $r_1$ . Since the variation values of the prediction accuracy  $r_1$  are around 0.5 and random, that reflects power attacks are unable to leak critical information on the proposed PUF).

$$\Delta L = \sum_{z=1}^{Z} \left( \sum_{k=0}^{K^*} f_k^* \times (P_{in,z})^k - B_z \right)^2$$

(2.14)

By minimizing the matching error  $\Delta L$  with

$$\frac{\partial \Delta L}{\partial f_k^*} = \left( 2\sum \left( \sum_{k=0}^{k^*} f_k^* \times (P_{in,z})^k - B_z \right) \right) \times \sum_{k=0}^{K^*} (P_{in,z})^k = 0, \quad (2.15)$$

the optimal  $K^*$ ,  $f_0^*$ ,  $f_1^*$ ,  $\cdots$ ,  $f_{K^*}^*$  can be determined.

The Z number of input power and output response pairs:  $(P_{in,1}, B_1), (P_{in,2}, B_2), \cdots$ , and  $(P_{in,z}, B_z)$  of the WAMPVR-based strong PUF primitive with the 130 nm CMOS technology under the standard deviations  $\sigma_f$  and  $\sigma_v$  is simulated in Cadence. As shown in Fig. 2.6, if power attacks are implemented on the WAMPVR-based strong PUF primitive by exploring

Fig. 2.7: (a) Critical voltage  $V_{a,1}$  versus average capacitance mismatch Q against ML attacks. (b) Number of diodes P between the switch  $S_{h,1}$  and the capacitor  $C_{h,x}$  in Fig. 2.3 versus degree g of the non-linearity of the WAMPVR-based strong PUF primitive.

the input power  $P_{in}$  as the critical side-channel leakage, the maximum prediction accuracy of the power attacks is about 0.52 even if 1 million input power and output response pairs are analyzed. That indicates the proposed strong PUF primitive is adequately secure against the advanced power attacks.

# 2.4.3 SECURITY AGAINST MACHINE-LEARNING (ML) ATTACKS

### **Non-Linearity Analysis**

The degree of the non-linearity between the input challenges and the output response is a critical parameter that affects the robustness of a strong PUF against machine-learning (ML) attacks [57]. For the WAMPVR-based strong PUF primitive in Fig. 2.3, the relationship between the average capacitance mismatch Q and the critical voltage  $V_{a,1}$  is studied. The definition of the average capacitance mismatch Q in Fig. 2.3 is

$$Q = \sum_{j=1}^{32} w_j \left( C_{2,j}^S - C_{1,j}^S \right)$$

(2.16)

The non-linear relationship between Q and  $V_{a,1}$  can be observed in Fig. 2.7(a) when the non-linear transformation block that is consist of diodes  $D_{1,1}, D_{1,2}, D_{2,1}, \dots, D_{4,2}$  (as shown in Fig. 2.3) is enabled. By contrast, a strong linear relationship exists between Q and  $V_{a,1}$ if the non-linear transformation block is removed.

If Y number of different Q values:  $Q_1, Q_2, \dots, Q_Y$  are studied, assume the corresponding value of the critical voltage  $V_{a,1}$  is:  $V_{a,1,1}, V_{a,2,1}, \dots, V_{a,2,Y}$   $(V'_{a,1,1}, V'_{a,2,1}, \dots, V'_{a,2,Y})$  for the strong PUF with (without) the non-linear transformation block. As a result, the degree g of the non-linearity of the designed WAMPVR-based strong PUF primitive can be estimated as [58]

$$g = \frac{\frac{1}{2Y} \sum_{j_1=1}^{Y} \left( V_{a,1,j_1} - V'_{a,1,j_1} \right)^2}{\left( \frac{\sum_{j_1=1}^{Y} V'_{a,1,j_1}}{Y} \right)^2} \times 100\%$$

(2.17)

To enhance the degree of the non-linearity of the proposed strong PUF device, we can increase the number of diodes in the non-linear transformation block. For instance, in Fig. 2.3, only one diode  $D_{h,x}$  (h = 1, 2, 3, 4 and x = 1, 2) exists between the switch  $S_{h,1}$ and the capacitor  $C_{h,x}$ . If larger number of diodes can be inserted, the degree g of the non-linearity of the WAMPVR-based strong PUF primitive will be improved (g = 91.79%when p = 5), as shown in Fig. 2.7(b).

### Linear Regression (LR) Attacks