# Investigation of potential induced degradation as a performance limiting defect in photovoltaic modules

# Isaac Morko Kwembur

Submitted in fulfilment of the requirements for the degree of

# PHILOSOPHIAE DOCTOR

# IN THE FACULTY OF SCIENCE AT THE NELSON MANDELA UNIVERSITY

April 2020

Promotor: Prof E.E. van Dyk Co- Promotor: Dr J.L. Crozier Co- Promotor: Dr F.J. Vorster

# Declaration

Full name: Isaac Morko Kwembur Student Number: 215379446 Qualification: PHILOSOPHIAE DOCTOR Title of the Project: "Investigation of potential induced degradation as a performance limiting defect in photovoltaic modules"

In accordance with Rule G4.6.3, I hereby declare that the above-mentioned thesis is my own work and that it has not previously been submitted for assessment to another University or for another qualification.

| SIGNATURE: | SARE |  |

|------------|------|--|

| -          |      |  |

DATE: \_\_\_\_\_\_24/03/2020\_\_\_\_\_

# DEDICATION

To my parents the late Richard Chepoto Kwembur and Beatrice Tamnai

# ACKNOWLEDGEMENTS

Sincere thanks to:

- My promoter **Prof E.E van Dyk** for his support, guidance and encouragements.

- My co promoter **Dr. J Crozier** and **Dr. F.J. Vorster** for their unwavering support and guidance.

- Mr. Johan Wessels, Mr. Marius Claassen and Mr. Len Compton for their technical assistance.

- Ms. Chanie Neveling, Ms. Mariska Müller and Ms. Jualine Ferreira for their exceptional administrative help.

- Fellow students at the PGRG and physics department especially **Mr. Ross Dix-Peek** for image analysis and **Mr. Monphias Vumbugwa** for the help during experimentation and **Dr. Ross Schultz** from the help on the experimental work.

- Dr. M. K. Munji for introducing me to Photovoltaics and Dr. E. Tennyson for help with articles for literature.

- South African National Research Foundation (NRF), PVinsight (Pty) Ltd, National Laser Centre (NLC), African Laser Centre (ALC), the South African Department of Science and Technology (DST), ESKOM and Nelson Mandela University (NMU) for the financial support and providing necessary facilities for research.

- A special thanks to my wife **Caren Mining`wa**, family and friends for their support.

- I`m grateful to The Almighty God for good health and provision thought out the years of my study

# ABSTRACT

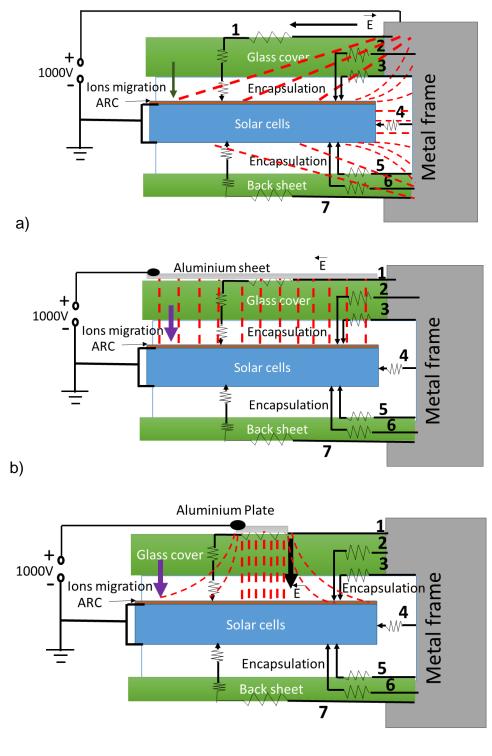

Potential Induced Degradation (PID) impacts negatively on photovoltaic (PV) module durability because it significantly affects the output of PV modules and systems. Unless detected at infancy, PID progression can be catastrophic. This study involved systematic PID stressing of PV modules using a custom-built environmental chamber that can achieve suitable environmental conditions, viz., of the 35 °C  $\pm$  1 °C and relative humidity of 75 %  $\pm$  5 %. The first part of this work was to induce PID using three approaches: climate chamber testing, inducing PID using a conductive aluminium plate on the surface of the module without touching the frame and a localised PID induction on one cell in a module. The second part is to detect induced PID using Electroluminescence (EL) images taken at current corresponding to 10% I<sub>sc</sub>, EL histograms analysis and V<sub>oc</sub> ratio taken at 1000 W/m<sup>2</sup> to 200 W/m<sup>2</sup>. The third part is to study module regeneration after PID shunting degradation in two ways, viz., forced reverse polarization and natural recovery.

The PID detection tools used in this work are well known module characterization techniques such as EL imaging, Infrared imaging, and light and dark current-voltage measurements. These characterisation tools are used in combination to detect defects such as optical losses, cracks, breakage, electric circuit degradation and PID. Under normal testing PID was detected and in some cases, modules were able to recover, while for advanced stage PID regeneration or PID reversal was difficult. This thesis focuses on PID detection at infancy using three approaches; EL imaging at current corresponding to 10% of  $I_{sc}$ . Light and dark current – voltage measurements (L-IV & D-IV) and open circuit voltage (Voc) ratios at low irradiance.

The early detection procedures are essential in reversing the degradation caused by PID which is reversible. The time taken to reverse the PID degradation will depend on the extent of the degradation. If detected early, it will take a short period of time to completely reverse lost power. Infrared thermography is a non-contact characteristic tool that can be deployed in large scale plants using drones to detect the presence of PID in PV plants.

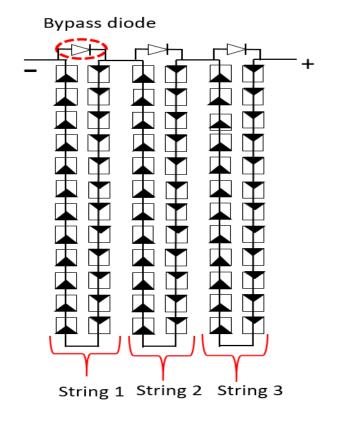

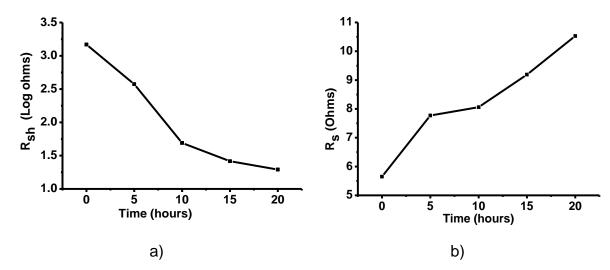

Module performance and device parameters extracted from the L-IV curves on a module before and after PID stress, such as  $P_{mpp}$ ,  $V_{oc}$ ,  $I_{sc}$  Fill Factor (FF), shunt resistance ( $R_{sh}$ ) and series resistance ( $R_s$ ) and ideality (*n*) are sensitive to PID shunting.  $V_{oc}$  and  $R_{sh}$  drop significantly with the onset of PID, while  $R_s$  increases. The decrease in  $V_{oc}$  and  $R_{sh}$  is due to heavy shunting on the module resulting in increased carrier recombination, while the increase in  $R_s$  is due to increased shunting paths leading to decreased photocurrent. When substantial degradation on a module occurs  $P_{mpp}$ , FF and *n* will drop and at very advanced stage of PID degradation  $I_{sc}$  may drop excessively.

# TABLE OF CONTENTS

| Dedicat | dicationii                                                       |    |  |  |  |

|---------|------------------------------------------------------------------|----|--|--|--|

| Acknow  | cknowledgementsiv                                                |    |  |  |  |

| Abstrac | actv                                                             |    |  |  |  |

| Table o | able of Contentsvi                                               |    |  |  |  |

| LIST O  | ST OF FIGURES                                                    |    |  |  |  |

| Chapte  | Chapter 1                                                        |    |  |  |  |

| 1. Intr | oduction                                                         | 15 |  |  |  |

| 1.1     | Background and motivation                                        |    |  |  |  |

| 1.1     | .1.1 Status of the PV industry                                   |    |  |  |  |

| 1.2     | Summary of possible module degradation modes crystalline modules |    |  |  |  |

| 1.3     | Potential Induced Degradation (PID) and module reliability       |    |  |  |  |

| 1.4     | Research problem                                                 |    |  |  |  |

|         | hesis outline summary                                            |    |  |  |  |

| Chapte  | r Two                                                            | 23 |  |  |  |

| 2. Sei  | miconductor Devices                                              | 23 |  |  |  |

| 2.1     | Introduction                                                     | 23 |  |  |  |

| 2.2     | PV devices                                                       | 23 |  |  |  |

| 2.3     | The PN junction                                                  | 24 |  |  |  |

| 2.4     | Mobility of charge carriers                                      |    |  |  |  |

| 2.5     | Recombination                                                    |    |  |  |  |

| 2.5     | .1 Radiative recombination                                       | 26 |  |  |  |

| 2.5     | .2 Auger Recombination                                           | 27 |  |  |  |

| 2.5     | .3 Shockley-Read Hall (SRH) recombination                        | 27 |  |  |  |

| 2.6     | Carrier properties                                               | 28 |  |  |  |

| 2.7     | Charge carrier transportation                                    | 28 |  |  |  |

| 2.8     | Collection probability                                           | 29 |  |  |  |

| 2.9     | Quantum efficiency                                               | 30 |  |  |  |

| 2.10    | Diode Under forward bias                                         | 30 |  |  |  |

| 2.11    | Basic principles of electroluminescence (EL) imaging             | 31 |  |  |  |

| 2.12    | Solar cell models                                                | 32 |  |  |  |

| 2.1     | 2.1 Single exponential model                                     | 33 |  |  |  |

| 2.1     | 2.12.2 Two diode model                                           |    |  |  |  |

| 2.13    | 2.13 Module I-V curves and Solar cell parameters                 |    |  |  |  |

| 2.14 Summary and conclusion                                            | 36 |  |

|------------------------------------------------------------------------|----|--|

| CHAPTER 3                                                              |    |  |

| 3. POTENTIAL INDUCED DEGRADATION – MECHANISMS, DETECTION AN PREVENTION |    |  |

| 3.1 Introduction                                                       | 40 |  |

| 3.2 PV cell technologies                                               | 40 |  |

| 3.2.1 Monocrystalline cells                                            | 40 |  |

| 3.2.2 Multi-crystalline cells                                          | 40 |  |

| 3.3 Module construction                                                | 41 |  |

| 3.3.1 Cell preparation                                                 | 41 |  |

| 3.3.2 Crystalline Silicon module construction                          | 42 |  |

| 3.4 Potential Induced Degradation (PID)                                | 44 |  |

| 3.4.1 PID overview                                                     | 44 |  |

| 3.4.2 PID at system, module and cell level                             | 45 |  |

| 3.4.2.1 String level                                                   | 46 |  |

| 3.4.2.1.1 String characterization methods                              | 48 |  |

| 3.4.2.1.2 PID prevention measures at a system level                    | 48 |  |

| 3.4.2.2 Module level                                                   | 49 |  |

| 3.4.2.3 Cell Level                                                     | 51 |  |

| 3.4.2.3.1 PID prevention at cell level                                 | 53 |  |

| 3.4.3 PID module regeneration modelling                                | 53 |  |

| 3.4.4 Test methods for the detection of PID                            | 55 |  |

| 3.4.4.1 PID Stress Induction                                           | 55 |  |

| 3.4.4.2 Module Characterisation Tools effective for PID detection      | 58 |  |

| 3.5 Summary and conclusions                                            | 60 |  |

| Chapter 4                                                              | 68 |  |

| 4. Experimental Materials and Details                                  | 68 |  |

| 4.1 Introduction                                                       | 68 |  |

| 4.2 Modules used in this study                                         | 68 |  |

| 4.3 PV module characterization techniques                              | 69 |  |

| 4.3.1 Light Current-Voltage (L-IV) measurements                        | 69 |  |

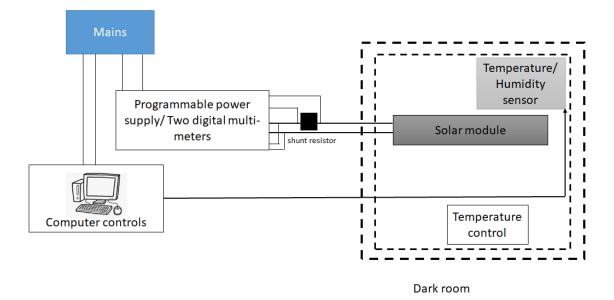

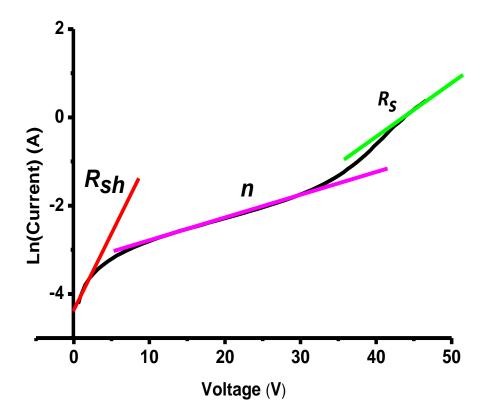

| 4.3.2 Dark Current-Voltage (D-IV) measurements                         | 70 |  |

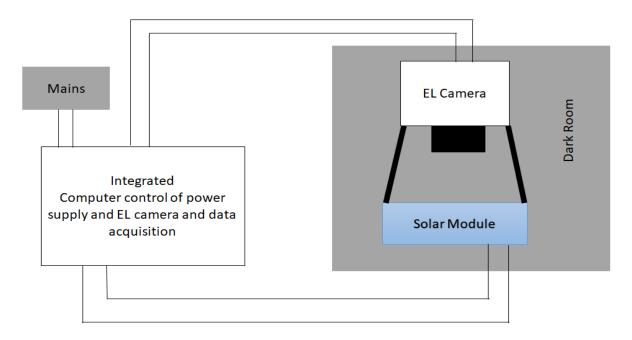

| 4.3.3 Electroluminescence (EL) measurements                            | 72 |  |

| 4.3.4 Wet leakage current76                                            |    |  |

| 4.3.5 Thermal Infrared (TIR) imaging                                   | 77 |  |

|     | 4.3.                                   | 6 W   | orst case cell determination/ cell mismatch investigation                                   | . 78 |

|-----|----------------------------------------|-------|---------------------------------------------------------------------------------------------|------|

| 4.  | 4 PI                                   | D In  | duction and Recovery                                                                        | . 78 |

|     | 4.4.                                   | 1 PI  | D Induction Methods                                                                         | . 78 |

|     | 4.4.                                   | 2 PI  | D recovery Methods                                                                          | . 80 |

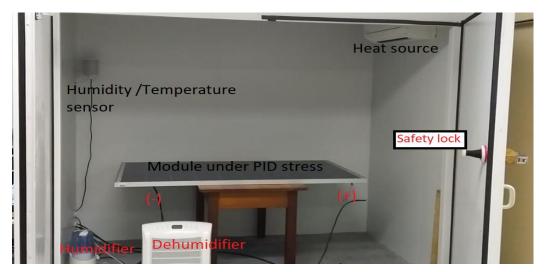

|     | 4.4.                                   | 3 Th  | ne environmental chamber construction                                                       | . 81 |

| 4.  | 5 Sı                                   | umm   | nary and conclusion                                                                         | . 82 |

| Cha | pter                                   | 5     |                                                                                             | . 84 |

| 5.  | Results and discussion8                |       |                                                                                             | . 84 |

| 5.  | 1                                      | Intro | oduction                                                                                    | . 84 |

| 5.  | 2                                      | PID   | detection                                                                                   | . 85 |

|     | 5.2.<br>of I₅                          |       | EL images taken at a current corresponding to the specified $I_{sc}$ and 1 the module       |      |

|     | 5.2.                                   | 2     | Light-IV and Dark-IV curve measurements                                                     | . 91 |

|     | 5.2.                                   | 3     | Comparison of open circuit voltage (Voc) at 1000 $W.m^{\text{-}2}$ to 200 $W.m^{\text{-}2}$ | . 94 |

| 5.  | 3                                      | PID   | stress induction methods                                                                    | . 95 |

|     | 5.3.                                   | 1     | Method 1: PID stress by environmental conditioning                                          | . 95 |

|     | 5.3.                                   | 2     | Method 2: Aluminium sheet cover method                                                      | . 97 |

|     | 5.3.                                   | 3     | Method 3: A case localised PID                                                              | 100  |

| 5.  | 4                                      | Мос   | dule power recovery after PID stress by way of natural and forced                           |      |

| re  | vers                                   |       | as                                                                                          |      |

| 5.  | 5                                      | PID   | cell mismatch analysis                                                                      | 107  |

| 5.  | 6                                      |       | kage current analysis                                                                       |      |

| 5.  | 7                                      | The   | rmal Infrared (IR) imaging (TIR)                                                            | 112  |

| 5.  | 8                                      | Cor   | nclusion                                                                                    | 115  |

|     |                                        |       |                                                                                             |      |

| 6.  | Sun                                    | nma   | ry and Conclusion                                                                           | 118  |

| 6.  | 1 Sı                                   | umm   | nary                                                                                        | 118  |

| Арр | end                                    | ix A  |                                                                                             | 121  |

| 1.  | 1. JOURNALS/ REFEREED PUBLICATIONS 121 |       |                                                                                             |      |

| 2.  | 2. PUBLISHED PROCEEDINGS 121           |       |                                                                                             |      |

| 3.  | RES                                    | SEA   | RCH PAPERS AT CONFERENCES                                                                   | 122  |

# LIST OF FIGURES

Figure 2. 2: Isolated p- and n- type semiconductor material energy band structure [9]

Figure 2. 3: The PN junction structure with band gap diagram at thermal equilibrium [9]

Figure 2. 5: The diffusion length in the emitter and in the base respectively [16] .... 29

Figure 2. 6: Silicon quantum efficiency [17]

30

Figure 2. 8: Emission of light associated with electroluminescence in PV modules [20]

**Figure 2. 11**: Characteristic IV curve of a PV module; I<sub>sc</sub>-Module short circuit current, I<sub>mpp</sub>- current at maximum power point, V<sub>mpp</sub>-Voltage at maximum power point, V<sub>oc</sub>- open circuit voltage. R<sub>s</sub>- Series resistance region and R<sub>sh</sub>-shunt resistance [6]......35

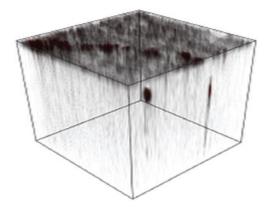

**Figure 3. 6:** Time of Flight -SIMS 3-D representation showing sodium ions distribution on 200  $\mu$ m by 200  $\mu$ m by 2.2  $\mu$ m Volume after PID stress [46]......51

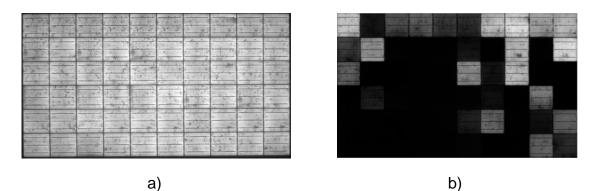

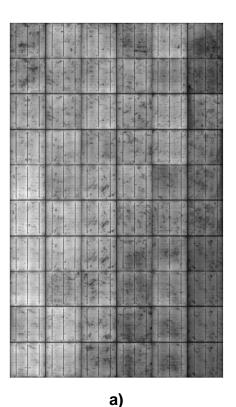

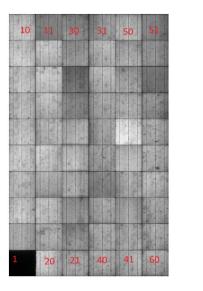

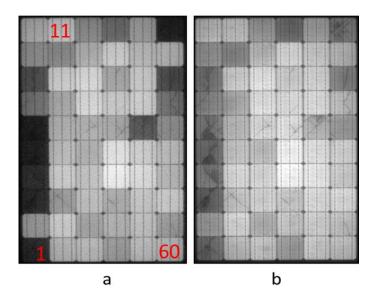

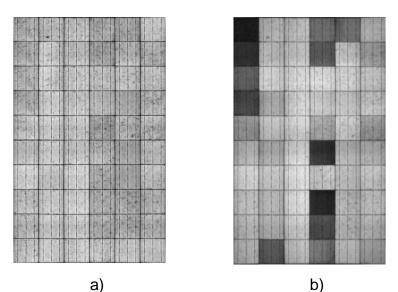

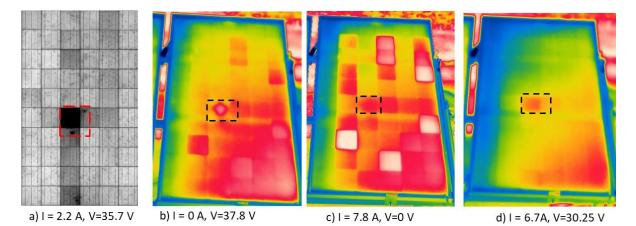

**Figure 3. 12:** Module K, EL images taken at of  $I_{sc}$  (7.8 A), a) Initial EL image, b) EL image after 20 hours of PID stress. The module lost 36.4% of its initial maximum power.

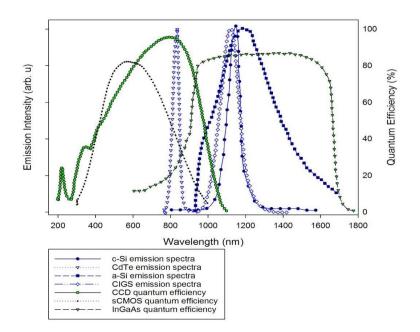

**Figure 4. 4:** Emission spectra from a range of solar cell technologies and the quantum efficiency of silicon CCD, CMOS and InGaAs CMOS cameras [5]......74

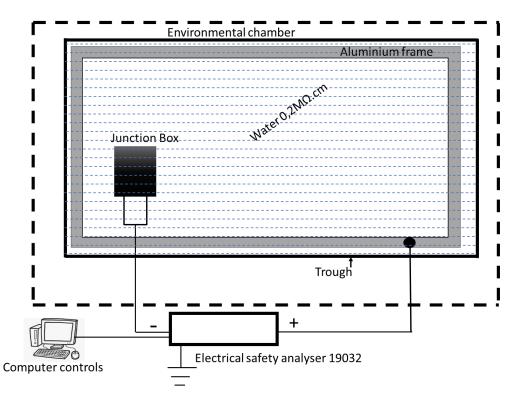

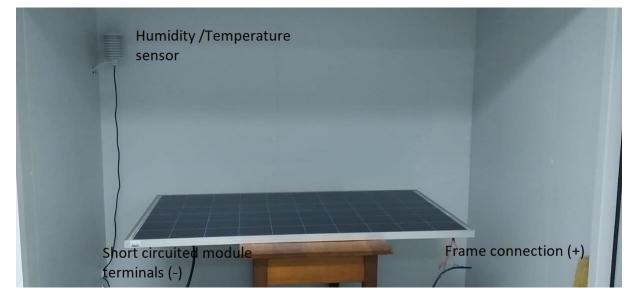

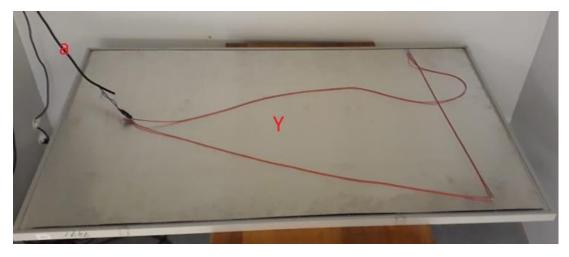

**Figure 4. 9:** PID stress procedure method 2; Y is Aluminium plate measuring 1625 mm by 955 mm by 3 mm; a is the positive terminal biased to the power supply source. 80

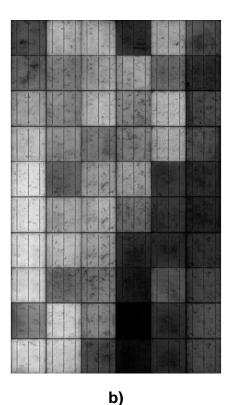

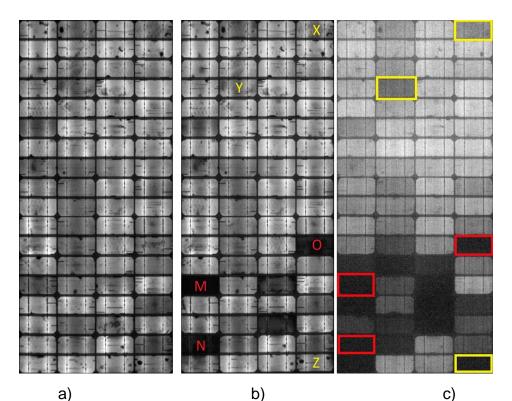

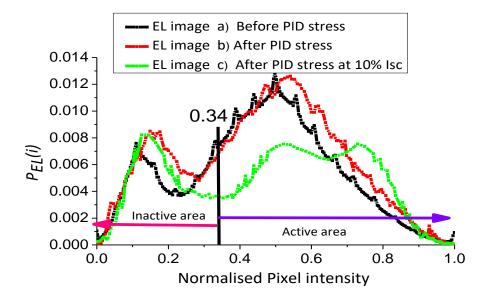

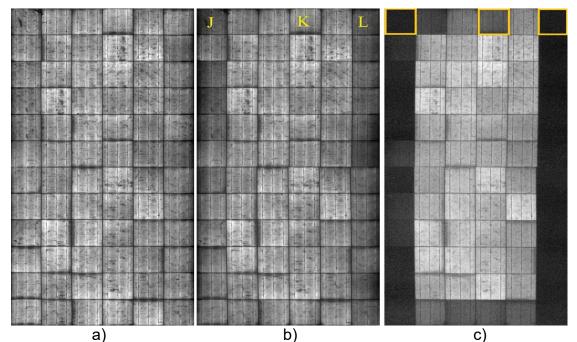

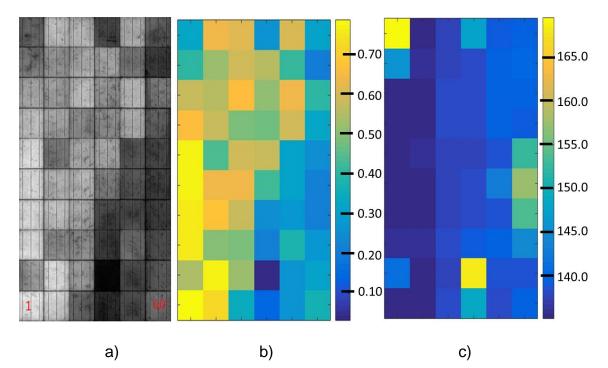

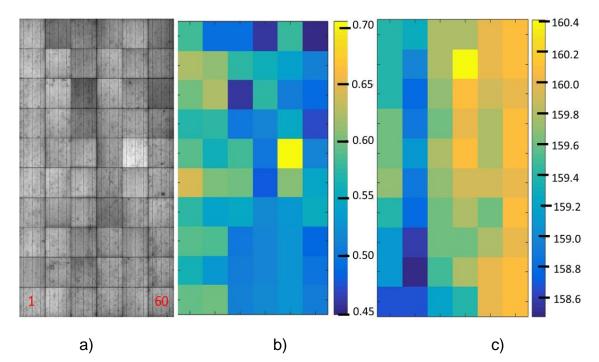

**Figure 5. 2:** EL images of Module A. The EL images were obtained as follows: a) and b) EL at  $I_{sc}$ , 3.61A, and c) EL at 10%  $I_{sc}$ , 0.361A, cells M, N, O are heavily shunted hence visibly dark on figure b) while cells X, Y, Z are less shunted and only observable in figure c).

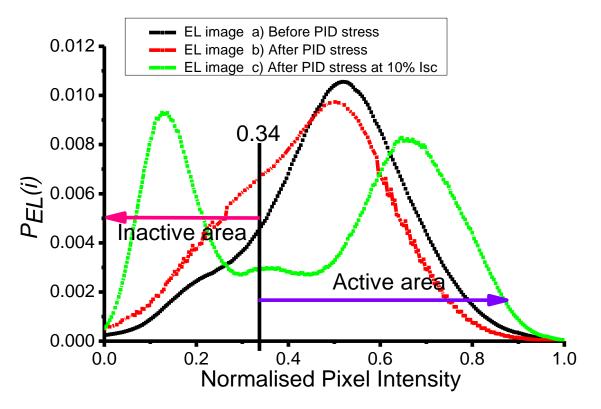

**Figure 5. 6:** I-V characteristics of modules before and after PID Stress: a) L-IV Curve of Module A. b) D-IV Curve Module A. c) L-IV Curve of Module B. d) D-IV Curve of Module B. The values indicated are reciprocals of the respective tangents in  $\Omega$ . .... 93

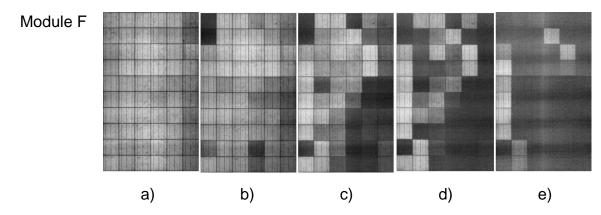

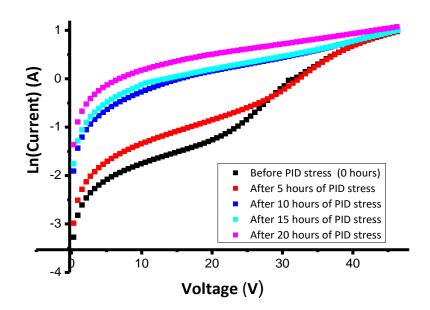

**Figure 5. 9:** The dark-IV measurements taken on module sample F, the plotted measurements are for before PID stress and after every five hours of PID stress...98

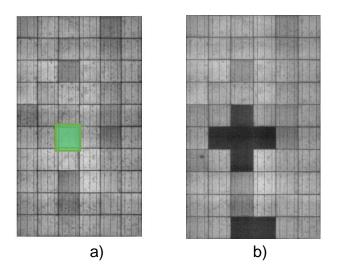

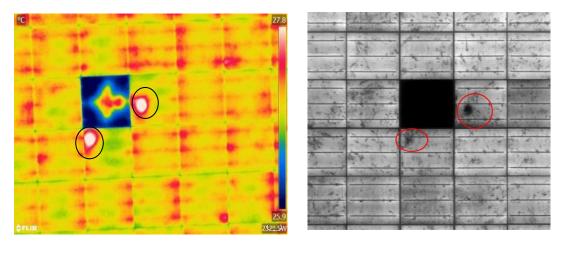

**Figure 5. 19**: EL and IR thermography of a PID affected Module I under sunlight conditions (approx. 700 W/m<sup>2</sup>): a) The EL image taken at low Current to optimise

# LIST OF TABLES

| Table 4. 1: List of module specification used in this study.         69                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 5. 1: List of modules used in this study with Initial Power and Power after PID stress                                                                                                                                                                       |

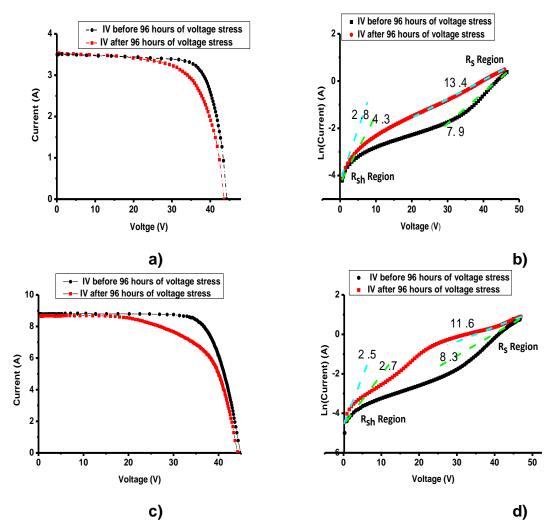

| <b>Table 5. 2:</b> Standard deviation (STD) of The PEL distributions and [%] of module inactive area [MIA], calculated from EL images of Module A and Module B                                                                                                     |

| <b>Table 5. 3:</b> Module A and B extracted solar parameters; $V_{oc}$ (open circuit voltage); $I_{sc}$ (short circuit current; $P_{mpp}$ (maximum power point), FF (Fill Factor), $R_{sh}$ (Shuntresistance), $R_s$ (series resistance and Ideality factor (n).93 |

| Table 5. 4: Table of $V_{oc}$ and $P_{mpp}$ taken at 1000 W.m <sup>-2</sup> and 200 W.m <sup>-2</sup> irradiance94                                                                                                                                                 |

| Table 5. 5: Modules power measurements comparison table before and after PID stress                                                                                                                                                                                |

| <b>Table 5. 6</b> : List of the extracted $R_{sh}$ and $R_s$ for the Module F at time intervals of 5 hoursfrom the D-IV measurements in Figure 5.9.                                                                                                                |

| Table 5. 7: Power measurements on modules before and after PID stress in listed modules                                                                                                                                                                            |

| Table 5.8: List of modules power measurement before and after PID stress 101                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                    |

| Table 5. 9: List of modules used for PID stress and recovery investigation                                                                                                                                                                                         |

| <b>Table 5. 9</b> : List of modules used for PID stress and recovery investigation                                                                                                                                                                                 |

# CHAPTER 1

# **1. INTRODUCTION**

# 1.1 Background and motivation

# 1.1.1 Status of the PV industry

Photovoltaic (PV) modules convert solar energy to electrical energy and are a proven reliable and sustainable energy source. Over the past decade the number of photovoltaic installations has increased substantially. By the end of 2018 the global PV solar Electricity generation exceeded 0.5 TW contributing 2.6 % of global electricity needs [1]. It is estimated that by 2050, the total PV installed capacity is projected to reach 4.7 TW contributing 16.0% of the global electricity needs [2][3]. Attainment of 16 % by 2050 seems possible with the current record module efficiency of 26.1% and 22.8% for mono and multi- crystalline modules, respectively [4]. This is attributed to the effort of both the industry and academic research.

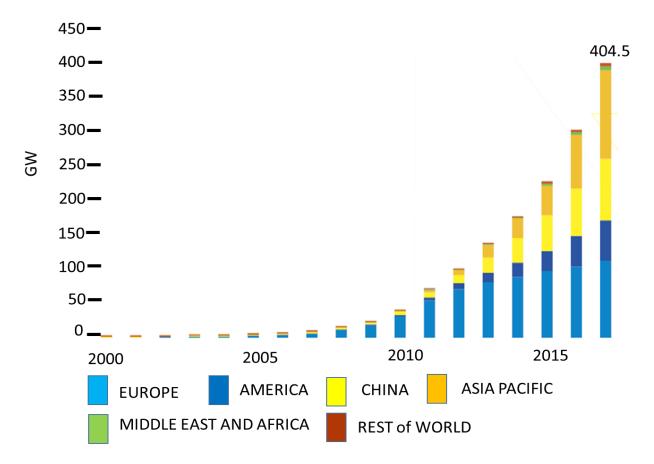

Photovoltaics (PV) is an important form of renewable energy that has attracted the attention of the world's leading economies with a global cumulative installed capacity of 404.5 GW [5]. The annual installation for 2017 stood at 99.1 GW [5]. Figure 1.1 show the exponential growth of PV industry over the years up to 2017, the growth has been made possible by favourable support policies in renewable energy sector. In 2011, the South African government introduced Renewable Energy Independent Power Producer Procurement Programme (REIPPPP) with grid contribution of 1,474 MW against the set goal of 8, 400 MW from PV [6]. The total cumulative installation in South Africa stood at 1.8 GW at end of 2017 [7]

### Figure 1. 1: Annual worldwide PV installations according to EPIA [5]

Silicon crystalline modules dominate the world market with about 95% of the market being silicon-based wafers with multi-crystalline accounting for 62% of modules produced in 2017. Multi-crystalline modules have a laboratory efficiency of about 22.3% and commercial efficiency increasing from 12% to 17% from 2007 to 2017 [8]

PV modules have a warranty of up to 30 years [9] and allowable degradation rate of 0.8% per annum based on long term photovoltaic data analysis, financial and statistical modelling undertaken on old modules [9]. Module's initial performance would be expected to drop within 72 hours of deployment due to Light Induced degradation (LID) [10].

Ordinarily modules undergo design qualification test such as IEC 61215, IEC 61730 for module safety and IEC TS 60904-13 for Electroluminescence. The aim of the qualification test is to help detect flaws the PV module may have suffered right from the factory processes, handling during transportation, storage and installation. Module degradation in the field varies greatly depending on climatic conditions (temperatures and humidity levels), PV power plant cleaning routine and surrounding human activity

[11]. Most crystalline modules located in high temperature regions suffer degradation due to discoloration of the encapsulate which promotes a higher degradation as compared to those at moderate cool environment [12]. Unprecedented degradation rates on a PV power plant over a long period of time may pose a risk of the generation of the power plant and may, in the long term, affect plant lifetime power generation and its reliability.

### **1.2** Summary of possible module degradation modes crystalline modules.

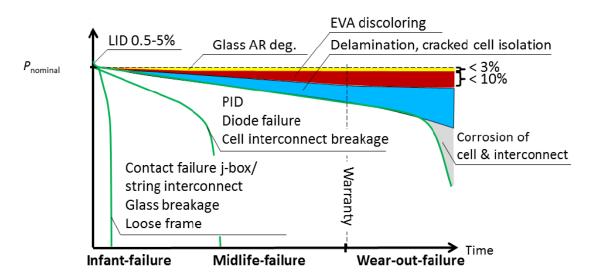

Figure 1.2 shows possible degradation that PV modules suffer in the course of their lifetime in the field. Modules suffer LID (Light Induced Degradation) immediately after deployment losing between 0.5-5.0 percent of the module power [13]. At infancy common module defects such as contact failures, string interconnect, glass breakage and loose frame are caused by during transportation, storage and installation [11]. At mid - life modules may suffer degradation such as Potential Induced Degradation (PID), diode failure and cell interconnect breakage [14], caused by system issues, thermo - cycling and moisture ingress. Some of the degradation modes such as EVA discoloration, delamination, cracked cells are exacerbated with module aging, leading to wear-out failure [11].

#### 1.3 Potential Induced Degradation (PID) and module reliability

Performance limiting defects such as PID in the modules are being managed by adjustment on the structural orientation of the module and by developing new materials to be used in module fabrication. Module reliability has attracted the attention of different PV industry players such as researchers, manufacturers, financers, insurers and investors [15]. Ordinarily PV modules of different technologies and manufactures are considered reliable and can attract insurance guarantees of up to 30 years of general liability, property and environmental risk [16].

Whereas modules are assumed to be reliable, they may be susceptibility to failures such as corrosion, delamination, cracks discoloration and PID. PID in some cases has resulted in losses of up to 30% of the initial power at string level [13]. In a PV power plant several modules are connected in series to form a string whose string voltage is the sum of voltages of individual module voltage. Modules in a string are also required to be grounded for safety reasons depending on the type of the inverter used, a high potential may develop between the frame and string's electrically active string circuitry. The potential difference can cause a leakage current to flow either from the cells to the module ground or from module ground to the cells depending whether it is n- or p-type. The consequence of PID may get worse with plans to increase string voltage to 1500 V.

PID has been an issue for a while in modules, at least during reliability test in laboratories. In 1978 Jet Propulsion Laboratory (JPL) observed PID in both crystalline and amorphous Si modules [17], and in 2005, at the SunPower Laboratory reported PID in n-type modules [18]. From 2009 much research has been undertaken, especially on conventional p-type modules [19][20]. Mitigating PID in modules has been elusive because of the complexity of causes which touches on environmental conditions (temperature and humidity), system topologies (grounding) and properties of module components such as encapsulation, ARC (Anti Reflecting Coating) and glass cover [15]. While complete elimination may be possible in future with continued research as significant proposals have been implemented to manage PID progression in strings, modules and cells. The measures are implemented to remain relevant in the cost competitive renewable energy market. This work proposes techniques to

detect PID at infancy which will play a big role in managing power failures that are associated with PID, especially at PV plant level.

# 1.4 Research problem

The general objective is to induce, detect and monitor PID as a PV performance limiting defect using tools such as Electroluminescence (EL), Power measurements and dark current-voltage measurement. Specific objectives are:

- (i) To Induce PID using three different approaches and quantify the PV module power degradation

- (ii) To use EL imaging to detect the onset of PID

- (iii) To utilise EL image histogram distributions to analyse PID

- (iv) To monitor power regeneration of PID degraded PV modules, naturally and by way of reverse polarity.

### 1.5 Thesis outline summary

This section outlines the summary overview of each of the chapters

**Chapter 2:** This chapter describes the basic operational principles of the semiconductor devices. The chapter describes p-type and n-type semiconductors and the formation of PN junction devices. Basic device operation that pertains to this study such as charge transport, recombination, charge collection probability, quantum efficiency and module parameters are introduced and explained. Device modelling utilises both the single- and two-diode model for device parameter extraction is also introduced.

**Chapter 3:** This chapter describes the cell ingot growth for multi and mono crystalline modules, the development of p- and n- type's cells, and fabrication of the modules. Description of causes, detection and prevention measures of PID are also covered. The three PID stress method used in this work are introduced and explained, as well as PID regeneration modelling.

**Chapter 4:** This chapter introduces physical characteristics of modules used in this investigation, the experimental details and procedures are explained in detail. The module characterization tools such as EL imaging, IR thermography, Light and Dark current-voltage (I-V) characteristics are introduced, including the type of the equipment

used. EL imaging histograms are introduced, and the formulas used in calculation of active/inactive areas and the standard deviation calculations are also presented

**Chapter 5:** This chapter presents results and analysis obtained from the experiments. PID detection using Electroluminescence imaging recorded at 10% of I<sub>sc</sub> and normalised EL image histograms. Other PID detection tools include use of open circuit voltage under low irradiance and I-V measurements in the dark and under illumination. The PID stress results from the three methods are explained in detail. PID regeneration for both natural and forced recovery are discussed in detail including deriving an empirical function to estimate regeneration with the aim of projecting estimated performance regeneration.

**Chapter 6:** This chapter gives a conclusion of this study and proposes some work for future investigations on PID in PV modules.

#### Reference

- [1] IEA PVPS, "PVPS 2019 Snapshot of global PV Markets" *lea Pvps T1-35:2019*, pp. 1–18, 2019.

- S. Vergura, "A Complete and Simplified Datasheet-Based Model of PV Cells in Variable Environmental Conditions for Circuit Simulation," *Energies*, vol. 9, no. 5, p. 326, 2016.

- [3] M. Köntges, S. Kurtz, C. Packard, U. Jahn, K. A. Berger, K. Kato, T. Friesen, *et al.*, *Review of Failures of Photovoltaic Modules*. IEA, 2014.

- [4] NREL, "Best Research-Cell Efficiency Chart.pdf," NREL, 2019. [Internet] available from: https://www.nrel.gov/pv/assets/pdfs/best-research-cellefficiencies.20191105.pdf. [Accessed: 02-10-2019]

- [5] M. Gaetan, O. Sinead, and R. Manoel, "Global market outlook," EPIA Eur. Photovolt. Ind. Assoc., p. 60, 2018.

- [6] Department of Energy, Department of National Treasury, and Development Bank of Southern Africa, "Independent Power Producers Procurement

Programme (IPPPP), An Overview," p. 76, 2015.

- [7] G. Masson and M. Brunisholz, "2018 Snapshot of global photovoltaic markets," *lea Pvps T1-292016*, pp. 1–19, 2018.

- [8] V. V. Tyagi, N. A. A. Rahim, N. A. Rahim, and J. A. L. Selvaraj, "Progress in solar PV technology: Research and achievement," *Renew. Sustain. Energy Rev.*, vol. 20, pp. 443–461, 2013.

- [9] D. L. King, M. A. Quintana, J. A. Kratochvil, D. E. Ellibee, and B. R. Hansen, "Photovoltaic module performance and durability following long-term field exposure," *Prog. Photovoltaics Res. Appl.*, vol. 8, pp. 241–256, 2000.

- [10] B. Sopori, P. Basnyat, S. Devayajanam, S. Shet, V. Mehta, J. Binns, and J. Appel, "Understanding light-induced degradation of c-Si solar cells," in 2012 38th IEEE Photovoltaic Specialists Conference, pp. 1115–1120, 2012.

- [11] D. Quansah, M. Adaramola, G. Takyi, and I. Edwin, "Reliability and Degradation of Solar PV Modules—Case Study of 19-Year-Old Polycrystalline Modules in Ghana," *Technologies*, vol. 5, no. 2, p. 22, 2017.

- [12] E. Coronel and A. Hultqvist, "The Effect of Zn 1-x Mg x O Buffer Layer Deposition Temperature on Cu (In, Ga) Se 2 Solar Cells : A Study of the Buffer / Absorber Interface," *Prog. Photovolt Res. Appl.*, pp. 115–125, 2009.

- [13] K. Marc, G. Oreski, U. Jahn, M. Herz, P. Hacke, K.-A. Weiss, R. Guillaume, et al., "Assessment of PV Module Failures in the Field," IEA, 2017.

- [14] S. Ahsan, K. A. K. Niazi, H. A. Khan, and Y. Yang, "Hotspots and performance evaluation of crystalline-silicon and thin-film photovoltaic modules," *Microelectron. Reliab.*, vol. 88–90, pp. 1014–1018, 2018.

- [15] W. Luo, Y. S. Khoo, P. Hacke, V. Naumann, D. Lausch, S. P. Harvey, J. P. Singh, *et al.*, "Potential-induced degradation in photovoltaic modules: a critical review," *Energy Environ. Sci.*, vol. **10**, no. 1, pp. 43–68, 2017.

- [16] Bethany Speer, Michael Mendelsohn, and Karlynn Cory, *Insuring Solar Photovoltaics: Challenges and Possible Solutions*. 2010.

- [17] G. R. Mon, R. Ross, G. Whitla, and J. Orehotsky, "Predicting electrochemical

breakdown in terrestrial photovoltaic modules," in *Photovoltaic Specialists Conference, 17th, Kissimmee*, pp. 682–692, 1984.

- [18] R. M. Swanson, M. Cudzinovic, D. Deceuster, V. Desai, J. Jürgens, N. Kaminar,

W. Mulligan, *et al.*, "The surface polarization effect in high-efficiency silicon solar cells," in *15th Asian PVSEC*, 2005, pp. 410–411.

- [19] F. Martínez-Moreno, G. Figueiredo, and E. Lorenzo, "In-the-field PID related experiences," *Sol. Energy Mater. Sol. Cells*, vol. **174**, pp. 485–493, 2018.

- [20] S. Pingel, S. Janke, and O. Frank, "Recovery Methods for Modules Affected by Potential Induced Degradation (PID)," in 27th European Photovoltaic Solar Energy Conference and Exhibition, 2012, pp. 3379–3383.

# CHAPTER TWO 2. SEMICONDUCTOR DEVICES

# 2.1 Introduction

Photovoltaics devices use the principle of photoelectric effect to convert sunlight into electricity. The physics behind the semiconductor materials and diodes are discussed in this chapter. A solar cell and PV modules behave as diodes, and utilizing some of the operational principles of diodes, crystalline based modules can be characterised. The basic characterisation techniques include current-voltage (I-V) measurements and forward bias electroluminescence imaging.

### 2.2 PV devices

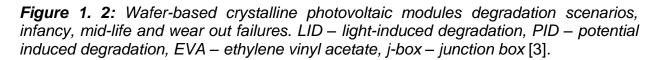

Atoms consist of a nucleus and electrons orbiting the nucleus [1]. Electrons orbit around the nucleus on allowed orbits and only exist in specific discrete levels, called the energy levels. A large number of atoms normally gather together to form a crystal [2]. The energy levels may become closely packed to form energy band. The energy bands are of two types the valance band and the conduction band [3][4]. In metals the conduction and valence bands overlap, while in semiconductors there exists a small energy gap, E<sub>g</sub>, which separates occupied valence band from unoccupied conduction band [4].

For a semiconductor to conduct electrons in the valance band must be excited by either increase in temperature or from interaction with photons [5]. For semiconductor materials to conduct at room temperature introduction of additional energy levels through doping must be done [6]. Doping is the introduction of a group III (trivalent) atom for example boron or introduction of group V element (pentavalent) for example phosphorous into the silicon crystal structure [2]. When silicon is doped with a trivalent the three electrons will participate in covalent bonding leaving a free hole to conduct, resulting in p-type semiconductor as shown in Figure 2.1a) [1]. On the other hand, if silicon is doped with a pentavalent four electrons will participate in covalent bonding with four from the doping element the excess electron be free to conduct at room temperature hence an n-type semiconductor shown in Figure 1.2b). The band gap of pure silicon is about 1.12 eV while doped silicon has band gap of as low as 0.02 eV, the dopant introduces donor and acceptor levels within the band gap [5]. In p-type

semiconductors holes are the majority charge carriers while electrons are minority charge carries. In n-type semiconductors electrons are majority charge carriers while holes are minority charge carriers [7].

**Figure 2. 1**: The band gap structure of doped p- and n-type semiconductors: a) p-type doped semiconductor. b) n-type doped semiconductor [5][6]

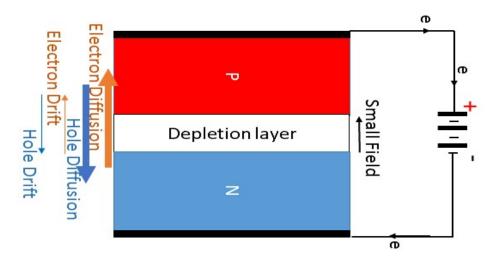

### 2.3 The PN junction

When a p-type and n-type semiconductors are combined they create an electron hole concentration gradient. The p-type has high concentration of holes while n-type has high concentration of electrons [4]. The concentration gradient between the p-type and n-type causes electrons to diffuse from the n-side to p-side while holes diffuse from p-side to n-side [6]. When electrons and holes move to either sides of the junctions the fixed ions in the crystal lattice become activated within what is to become a depletion region resulting in a built in electric field. The built-in electric field is responsible for causing the transition zone or what is called depletion region [6].

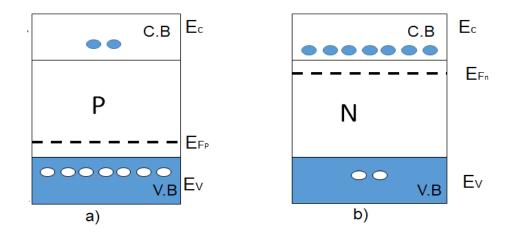

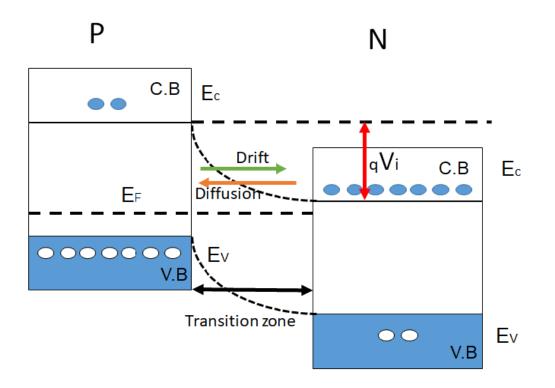

In a p-conductor semiconductor the Fermi energy level  $E_{Fp}$  is closer to the valance band (V.B) as shown in Figure 2.2a) while in Figure 2.2b) n-type semiconductor the Fermi energy level  $E_{Fn}$  is closer to conduction band (C.B). At thermal and chemical equilibrium, the Fermi level  $E_F$  must be constant hence the V.B and C.B must adjust accordingly. V<sub>i</sub> is the built potential, resulting from the requirement to keep the Fermi level constant in the material Figure 2.3. The energy difference between V.B and C.B is qV<sub>i</sub>, where q is the elementary charge of an electron. The mobility of charge carriers is made possible only through drift and diffusion currents [7][8].

Figure 2. 2: Isolated p- and n- type semiconductor material energy band structure [9]

### 2.4 Mobility of charge carriers

In semiconductor material charge carriers are forced to move either by way of an electric field (drifting) or by carrier concentration gradient (diffusion). The charges in a semiconductor can be fixed ions or mobile, for example in n-type semiconductors positive ions are fixed while majority of mobile charges are electrons *viz.* in p-type negative ions are fixed while majority of charge carriers are positive [9]. Mobile ions

are free to move from one contact device while fixed ions may only distribute within its equilibrium position. The mobility of charge carriers in a semiconductor may be determined by the strength of the electric field, doping levels in the semiconductor material and temperature [2]. In a semiconductor material charge equilibrium is reached through charge flow from a region of high concentration to regions of low concentration. The charge flow to equilibrium is governed by velocity and scattering events in the bulk of the material. The diffusion allows carriers induced by absorption and recombination to reach an equilibrium without application of external force [10].

#### 2.5 Recombination

When electrons lose energy, they fall from conduction band to valence band where they recombine with the holes. There are three types of recombination namely Radiative, Shockley – Read – Hole (SRH) and Auger recombination [9]. In silicon solar cells Auger and SRH recombination are dominant. Any electron in the conduction band will eventually stabilize into the valence band filling in the hole that was empty this process is called recombination [11].

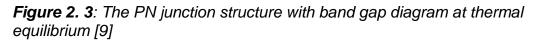

#### 2.5.1 Radiative recombination

Radiative recombination is the dominant recombination mechanism in direct band gap semiconductors [12]. Most common places of radiative recombination devices include Light Emitting Diodes (LED), concentrators and space solar cell application made from gallium arsenide (GaAs), Gallium Indium Phosphide (GaInP) and Cadmium Telluride (CdTe) [9]. In direct recombination an electron from the conduction band directly recombines with a hole in the valence band and release a photon with energy equivalent to band gap hence weakly absorbed as it exits the semiconductor device as shown in Figure 2.4a) [13]. In Indirect recombination the conservation of momentum dictates that photon absorption should involve additional particles. The process of light emission involves either phonon absorption or emission. Radiative recombination in indirect recombination such as Silicon (Si) based cells and Gallium (Ge) as shown in Figure 2.4b) have a very small coefficient of recombination compared to direct recombination enabling greater penetration of light making indirect band gap unique with electroluminescence techniques used ion silicon based degradation detection technique [14][6].

*Figure 2. 4*: The energy-momentum diagram of radiative recombination [13]. a) Direct band gap. b) Indirect band gap.

#### 2.5.2 Auger Recombination

Auger recombination involves three carriers, when an electron and a hole recombine instead of emitting energy as thermal or a photon. It transfers the energy to a third carrier, which is an electron in the conduction band [9]. The third electron then thermalizes to the edges of conduction band [6]. Auger recombination is most prevalent in high carrier concentration due to heavy doping and injection levels [6]. In silicon-based semiconductors, auger recombination limits the lifetime and efficiency. Heavily doped materials have a shorter Auger recombination lifetime [13].

### 2.5.3 Shockley-Read Hall (SRH) recombination

SRH recombination occurs through defects, it takes place in two steps. In the first case an electron or a hole is trapped by an energy state in the depletion region which is introduced through introducing a dopant into the crystal lattice structure [9]. In the second case an electron moves up to the same energy state before the electron is thermally re-emitted into the conduction band which then recombines [13]. The rate of electron movement into the depletion region depends on distance of introduced energy state from the either conduction or valence band. This implies that energy state introduced closer to the either bands recombines less since the electron is likely to be re-emitted to the conduction band than recombine with a hole which moves into the same energy state. This implies that energy levels near the mid-gap (Fermi level) are very effective recombination sites [2].

### 2.6 Carrier properties

In a PN junction the forbidden or the depletion layer separates the n-type and p-type. Electrons are majority charge carriers while the holes are minority charge carriers on the n-type side [13]. On the p-type material minority charge carriers are the electrons while holes are minority charge carriers on the n- type material. For a solar cell to work optimally photo generated carriers on the either side must be collected by external circuit before electron-holes recombine, this is made possible by the forbidden region. To ensure status quo the carrier lifetime or the diffusion length must be made sufficiently long to ensure carrier collection [12].

When diode is not biased, there is equilibrium in carrier generation, carrier recombination, diffusion and drift currents due to the depletion at the PN junction. The electric field due to fixed ions prevents majority charge carriers from crossing the junction. Minority charge carriers which are thermally generated exist on either side of the PN junction [9]. Recombination takes place when charge carriers travel a distance, known as the diffusion length ( $L_x$ ). The diffusion length relates to the carrier lifetime  $\tau$  and diffusivity, D, as expressed in equation 2.1. In silicon-based PV module the carrier lifetime is large for high efficiency solar cells [15].

$$L_{x} = \sqrt{D\tau}$$

(2.1)

### 2.7 Charge carrier transportation

In a semiconductor material electrons and holes behave as free particles, hence subject to drift or diffusion [12]. Drift is a response of charged particles to an electric field, when an electric field is applied across a uniformly doped semiconductor, the bands bend in the direction of the electric field. The electrons in conduction band are then forced to move in the opposite direction to the field, while holes would move along the electric field i.e. electrons sink while holes float. During the drift carriers may scatter if they collide with crystals in the atom, dopant ions, crystal defects and even other holes and electrons [2]. Due to random thermal excitations, electrons and hole may move or diffuse from regions of high concentration to regions of low concentration until an equilibrium is reached, where there is no net electron current flow [13].

#### 2.8 Collection probability

Collection probability describes the chances that photo generated electron-holes (e - h) will be collected as photo current before they recombine. The probability depends on the distance the carrier should travel in relation with the diffusion length. The probability of charge collection drops away from the PN junction, the e - h generated at the PN junction is almost guaranteed since they are collected immediately upon generation. The surface properties of the material also play an important role. Generated e - h at the surface of the emitter often surface surface recombination hence needs for surface passivation [16].

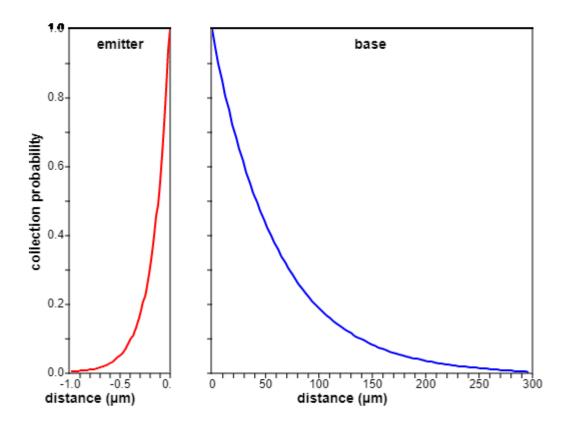

Figure 2. 5: The diffusion length in the emitter and in the base respectively [16]

The lifetime of minority charge carriers will be the determinant for collection to take place. For high efficiency in silicon based solar cells with indirect band gap, the diffusion length and minority lifetime must be long enough to avoid recombination as shown in Figure 2.5 [16].

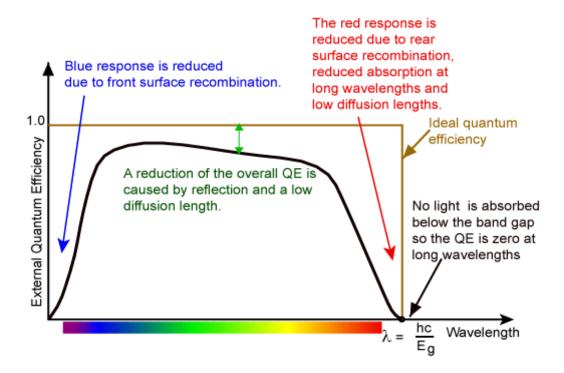

### 2.9 Quantum efficiency

External quantum efficiency (EQE) is the ratio of collected carriers to the number of photons of certain wavelength incident on the surface of the cell [9]. EQE increases with decrease in recombination both in surface recombination and bulk [9]. Silicon for example has very low EQE in blue light region, because blue light is absorbed within few microns hence photo generated e - h generated closer to the surface hence high likelihood of surface recombination. Quantum efficiency is mainly affected by the minority carrier diffusion length and recombination velocity. Internal Quantum efficiency (IQE) refers to photons that are reflected or transmitted out of the cells capable of generating collectable carriers. By quantifying devices reflectance and transmission, IQE can be derived from the EQE efficiency as shown in figure 2.6 [17].

Figure 2. 6: Silicon quantum efficiency [17]

### 2.10 Diode Under forward bias

A diode is in forward bias when voltage is applied on the device in a manner that the electric field developed reduces the depletion layer [2]. The p-type is connected to the positive while the n-type is connected to the negative terminal of the power source. The electric current will flow in the opposite direction to the electric field in the depletion layer [1]. Reducing the electric field disturbs the junction equilibrium hence decreasing

the potential barrier at the junction resulting in increased diffusion current. The drift current would remain unchanged because it depends on carriers generated by diffusion from one side of the junction to another [1]. The number of minority charge carriers remains the same on either side of the PN junction since the reduction in depletion layer width is small as shown in Figure 2.7 [7].

Figure 2. 7: Behaviour of solar cell in forward bias [7]

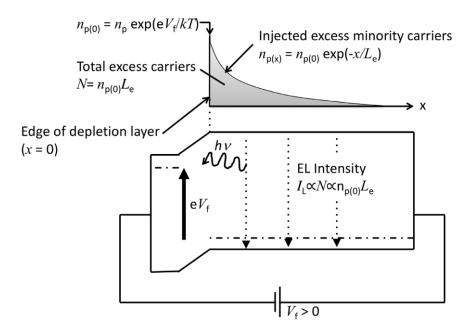

# 2.11 Basic principles of electroluminescence (EL) imaging

EL imaging depends on the principle of radiative/non radiative recombination. During EL imaging the module is connected in forward bias. Minority charge carriers are then injected into the p-side of the PN junction where they undergo radiative recombination. The emitted EL spectrum is between 900 nm to 1300 nm[18]. The number of minority charge carriers in a cell will determine the intensity of EL signal. Regions within the cells which appear darker undergo undetectable recombination. Such regions are potential defect areas in a cell [19]. The minority carrier concentration at the junction is given by equation 2.2

Under forward bias, electrons are injected at the p-side of the p-n junction and the distribution of these minority carriers (electrons) in the p-side of the p-n junction is discussed in this section.

The minority carrier concentration,  $n_p$ , at the junction (x=0) is given in equation 2.2 and is dependent on the intrinsic carrier concentration,  $n_i$ , the doping concentration of the base, N<sub>A</sub>, applied junction voltage, V, the Boltzmann's constant, k, the temperature , T and the electron charge, e [18].

$$n_p(0) = \frac{n_i^2}{N_A} \exp\left(\frac{eV}{kT}\right)$$

2.2

The injected excess minority carrier concentration at a distance x, from the junction is given in equation 2.3 and is determined by the equilibrium minority carrier density at the junction  $n_{p(0)}$  and the Diffusion Length (L<sub>e</sub>).

$$n_{p(x)} = n_{p(o)} \exp\left(\frac{-x}{L_e}\right)$$

2.3

*Figure 2. 8*: Emission of light associated with electroluminescence in PV modules [20]

Figure 2.8 describes the number of minority charge carriers at the junction and the change in the number of charge carriers as distance increases away from the PN junction [20].

#### 2.12 Solar cell models

Behaviour of solar cells of solar cells have been modelled using a two-part system i.e under solar illumination and in the dark. The model under solar illumination has photo current generation, while the model in the dark has no photo currents. Under illumination the solar cell is assumed to act under direct PN junction carrier injection whereas the solar cell in the dark operate in charge recombination with small diffusion currents. Two models are discussed in this section that is single diode model and two diode model which accounts for solar cell recombination processes in the dark and in the light [9].

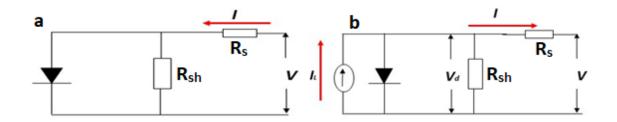

#### 2.12.1 Single exponential model

The single model consists of a photo current, a diode, a parallel resistor representing leakage current and a series resistance representing internal resistance to current flow. The one diode solar cell dark equation is given in 2.4 and illustrated in Figure 2.9a).

$$I = I_L - I_0 \left[ \exp\left(\frac{q(V - IR_s)}{nkT} - 1\right) \right] - \left(\frac{(V - IR_s)}{R_{sh}}\right)$$

2.4

Where  $I_o$  represents the diode dark saturation current, n is the ideality factor, T is the PN junction temperature, k is the Boltzmann constant, V is the applied voltage and  $IR_s$  is the voltage measured across the series resistor [21].

Under illumination the diode expression introduced the photo current term is introduced and its *I-V* characteristics is as expressed in the Equation 2.5

$$I = I_o \left[ \exp\left(\frac{q(V_d)}{nkT} - 1\right) \right] - \left(\frac{V_d}{R_{sh}}\right) - I_L$$

2.5

Where;  $I_L$  is photo-induced current with direction opposite to that of the dark current and  $V_d$  is the diode voltage. Since  $I_L$  is greater than the dark current, the net current generated by the cell is in the direction of  $I_L$ . Hence, the diode voltage expressed with respect to measured voltage, V was given as  $V + IR_S$  and the light-IV characteristics can be written as shown in Equation 2.6 and illustrated in Figure 2.9b)

$$I = I_L - I_0 \left[ \exp\left(\frac{q(V+IR_s)}{nkT} - 1\right) \right] - \left(\frac{V+IR_s}{R_{sh}}\right)$$

2.6

The Equation 2.4 is useful when analysing dark-IV characteristics while Equation 2.5 gives light-IV characteristics that are used to define, calculate and analyse solar cell device and performance parameters. Figure 2.9 shows one diode equivalent solar cell under illumination and in the dark.

*Figure 2. 9*: The schematic illustration of a single diode equivalent solar cell circuit when a) in the dark environment b) under illumination.

#### 2.12.2 Two diode model

Single diode equation assumes single ideality factor *n*. In reality the ideality factor is influenced by voltage across the devices. At high voltages surface recombination dominates while at lower voltages the bulk recombination dominates hence two diode model gives  $n_1 \approx 1$ , while  $n_2$  is a value  $\approx 2$ . The two diodes also describe two saturation currents  $I_{01}$  and  $I_{02}$ . The dark-IV equation is as shown in equation 2.7

$$I = I_{01} \left[ \exp\left(\frac{q(V - IR_s)}{n_1 kT} - 1\right) \right] + I_{02} \left[ \exp\left(\frac{q(V - IR_s)}{n_2 kT} - 1\right) \right] - \left(\frac{V - IR_s}{R_{sh}}\right)$$

2.7

Where  $I_{01}$  and  $I_{02}$  are saturation currents which depend on processes corresponding to diode quality factors  $n_1$  and  $n_2$  and the voltage *V* measured or applied in the dark. The Illuminated light-IV characteristics can be expressed as equation 2.8.

$$I = I_{01} \left[ \exp\left(\frac{q(V_d)}{n_1 k T} - 1\right) \right] + I_{02} \left[ \exp\left(\frac{q(V_d)}{n_2 k T} - 1\right) \right] + \left(\frac{V_d}{R_{sh}}\right) - I_L$$

2.8

In this equation the diode voltage ( $V_d$ ) can be expressed as  $V + IR_s$  and the inverted light-IV characteristics will be as represented in equation 2.9.

*Figure 2. 10*: The two-diode model schematic representation a) two diode equivalent solar cell circuit when in the dark environment b) when under illumination.

$$I = I_{01} \left[ \exp\left(\frac{q(V+IR_s)}{n_1 k T} - 1\right) \right] + I_{02} \left[ \exp\left(\frac{q(V+IR_s)}{n_2 k T} - 1\right) \right] - \left(\frac{V+IR_s}{R_{sh}}\right)$$

2.9

The two-diode equation has a limitation at higher efficiency because the number of charge carriers increase with the applied voltage, resulting in a dramatic change in rear surface recombination, complicating ideality factors in two diode model which depend on surface and bulk recombination. In this work the single diode model parameter equation was used to extract light-IV module parameters, using particle swarm optimization algorithm (PSO) to extract the module light-IV characteristics before and after PID stress [22]. The comparison is essential in estimating the severity PID degradation on module performance of parameters such as open circuit voltage V<sub>oc</sub>, maximum power point, shunt resistance (R<sub>sh</sub>) and series resistance (R<sub>s</sub>) [22][23].

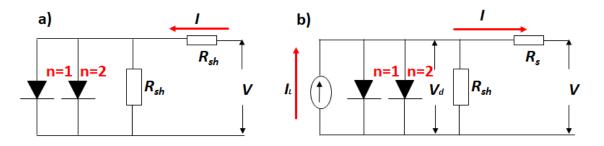

#### 2.13 Module I-V curves and Solar cell parameters

The electrical characteristics of a module are obtained when a curve of current against applied voltage is plotted under illumination. The curve normally occurs at the fourth quadrant, but it is inverted to the first quadrant. In a light-IV curve maximum power point  $P_{mpp}$  is found at a point when the product of current ( $I_{mpp}$ ) and voltage ( $V_{mpp}$ ) is maximum. When Voltage is zero (*V=0*), the current is at short circuit current ( $I_{sc}$ ), similarly when the current is zero (I=0), the voltage is at open circuit voltage ( $V_{oc}$ ).

**Figure 2. 11**: Characteristic IV curve of a PV module;  $I_{sc}$ -Module short circuit current,  $I_{mpp}$ - current at maximum power point,  $V_{mpp}$ -Voltage at maximum power point,  $V_{oc}$ - open circuit voltage.  $R_{s}$ - Series resistance region and  $R_{sh}$ -shunt resistance [6]

Light-IV curve measurements are done using indoor solar simulator measurements system. The standard test condition (STC) for power measurement are 1000 W/m<sup>2</sup> and 25 °C and A.M 1.5. The I<sub>sc</sub> may be equivalent to photo generated current (I<sub>L</sub>) under ideal condition but may decrease with increase in R<sub>s</sub> or leakage current. The V<sub>oc</sub> is the measure of strength of the bias at the PN junction caused by I<sub>L</sub>. Fill Factor (FF) is obtained as a measure of the ratio between maximum power to the product of I<sub>sc</sub> and V<sub>oc</sub>. FF gives an indication of the impact of series R<sub>s</sub> and shunt resistance R<sub>sh</sub> on the I-V curve shape. R<sub>s</sub> may occur along the metallization and external cabling, bulk, emitter, contacts and bus bars. The net impact of R<sub>s</sub> is to limit current output and cause a drop in voltage. The increased R<sub>s</sub> is observed as flatted I-V at the 'knee' and at very high resistance the light-IV curve would resemble an Ohmic graph (a linear graph from I<sub>sc</sub> to V<sub>oc</sub>).

The module current output is directly linked to irradiance levels. Lower irradiance levels or shading decreases the current output of the module. The decrease can also be occasioned by module encapsulant discoloration or if cells in multiple strings are badly damaged. Damage to a section of the cell(s) would impact negatively on the current levels since the effective area of photo current generation is reduced.

Solar power plants are constructed using solar PV modules comprising of either 60 or 72 cells connected in series. The total voltage output of a solar PV module is the sum of the individual cell's V<sub>oc</sub>. Modules that output a lower than expected V<sub>oc</sub> may be due to shunting, faulty interconnection or bypass diodes and increased temperatures. Light-IV curves may have steps especially at lower voltages, this may be caused by mismatch of current in the strings resulting in bypass diode activation. Multiple cracks on a cell my lead to localised heating on a cell activating the bypass diode. The gradient taken at low voltages near I<sub>sc</sub> represents R<sub>sh</sub>. A decrease in R<sub>sh</sub> results in a steeper gradient. At high voltages the slope represents R<sub>s</sub>. A less steep slope represents the undesired high series resistance which may be as result of poor soldering, soiling or bad contacts and junction box [25].

### 2.14 Summary and conclusion

This chapter discusses the theoretical processes and mechanisms that describe basic solar PV module operation. The solar PV module is a diode whose operation is governed by single diode or two diode model. The recombination mechanism inside

the module is of significance especially in techniques such as electroluminescence measurements when the module is connected in forward bias. Charge transportation mechanism is crucial in understanding the module operation especially under illumination. Processes such as charge transport, recombination, collection probability and quantum efficiency summaries e - h generation in a solar PV device and determines device efficiency. Module parameters such as FF, Isc, Voc, Pmpp, Impp, Rsh and Rs are introduced and explained in the last section. It's imperative to note that PID defects, affects parameter such Voc (especially at low irradiance), Pmpp, FF, Rsh and Rs.

#### References

- A. Sproul, "Understanding the p-n Junction," in Solar Cells: Resource for the Secondary Science Teacher, vol. 1, UNSW, pp. 13–34, 2003.

- K. Leaver, "Conduction in Semiconductors," *Microelectronic Devices*, 2012.

[Online]. Available: http://leachlegacy.ece.gatech.edu/ece3040/notes/chap01.pdf. [Accessed: 20-Nov-2019].

- [3] P. Zhang, W. Li, S. Li, Y. Wang, and W. Xiao, "Reliability assessment of photovoltaic power systems: Review of current status and future perspectives," *Applied Energy*, vol. **104**. pp. 822–833, 2013.

- [4] J. Olafsen, "Electrons and Holes in Semiconductors," Sturge's Statistical and Thermal Physics, 2019. [Online]. Available: https://www.coursehero.com/file/11896888/Chenming-Hu-ch1/. [Accessed: 25-Nov-2019].

- [5] G. Cook, L. Billman, and R. Adcock, *Photovoltaic Fundamental*. Solar Energy Research In- stitute (SERI) for the U.S. Department of Energy (DOE)., 1995.

- [6] S. O. Kasap, *Principles of Electronic Materials and Devices*, Third Edit. Suzanne Jeans, 2006.

- [7] C. Honsberg and S. Bowden, "Bias of PN Junctions," 2018. [Online]. Available:

https://www.pveducation.org/pvcdrom/pn-junctions/bias-of-pn-junctions. [Accessed: 18-Jun-2019].

- [8] C. Honsberg and S. Bowden, "Applying the Basic Equations to a PN Junction," *PVEducation*, 2014. [Online]. Available https://www.pveducation.org/pvcdrom/applying-the-basic-equations-to-a-pn-junction [Accessed: 18-Jun-2019].

- [9] K. Mertens, *Photovoltaics Fundamentals Technology and Practice*, First Edit. John Wiley & Sons Ltd, 2014.

- [10] G. Paasch, T. Lindner, and S. Scheinert, "Variable range hopping as possible origin of a universal relation between conductivity and mobility in disordered organic semiconductors," *Synth. Met.*, vol. **132**, no. 1, pp. 97–104, 2002.

- T. O. M. Tiedje, E. L. I. Yablonovitch, G. D. G. D. Cody, and B. G. Brooks,

"Limiting Efficiency of Silicon," *IEEE Trans. Electron Devices*, vol. **31**, no. 5, pp. 711–716, 1984.

- [12] U. K. Mishra and J. Singh, *Electronic levels in semiconductors*. AA Dordrecht: Springer, 2007.

- [13] J. L. Gray, "The Physics of the Solar Cell," in *Handbook of Photovoltaic Science and Engineering*, Indiana, USA: John Wiley & Sons Ltd, , pp. 82–129, 2011.

- [14] C. Honsberg and B. Stuart, "Types of Recombination," *PV education*, 2016.

[Online]. Available: http://www.pveducation.org/pvcdrom/pn-junction/types-of-recombination. [Accessed: 18-Jun-2019].

- [15] P. Würfel, T. Trupke, T. Puzzer, E. Schäffer, W. Warta, and S. W. Glunz,

"Diffusion lengths of silicon solar cells from luminescence images," *J. Appl. Phys.*, vol. **101**, no. 12, 2007.

- [16] C. Honsberg and S. Bowden, "Collection probability," *PVEducation*, 2017.

[Online]. Available: https://www.pveducation.org/pvcdrom/collection-probability-0. [Accessed: 17-Jun-2019].

- [17] M. H. Weik and M. H. Weik, "Quantum Efficiency," Computer Science and Communications Dictionary, 2006. [Online]. Available: https://www.pveducation.org/pvcdrom/solar-cell-operation/quantum-efficiency.

[Accessed: 18-Jun-2019].

- [18] T. Fuyuki and A. Kitiyanan, "Electroluminescence Characterization of Crystalline Silicon Solar Cells," *Appl. Phys. A Mater. Sci. Process.*, vol. **96**, no. 1, pp. 189– 196, 2009.

- [19] T. Fuyuki, H. Kondo, Y. Kaji, A. Ogane, and Y. Takahashi, "Analytic findings in the electroluminescence characterization of crystalline silicon solar cells," *J. Appl. Phys.*, vol. **101**, no. 2, 2007.

- [20] International Electrotechnical Commission, "Electroluminescence of photovoltaic modules," Geneva, IEC TS 60904-13, 2019.

- [21] G. Marius, *The Physics of Semiconductors.*, Second Edi. 2010.

- [22] M. K. Munji, W. Okullo, E. E. Van Dyk, and F. J. Vorster, "Local device parameter extraction of a concentrator photovoltaic cell under solar spot illumination," *Sol. Energy Mater. Sol. Cells*, vol. **94**, no. 12, pp. 2129–2136, 2010.

- [23] K. Ishaque, Z. Salam, and H. Taheri, "Simple, fast and accurate two-diode model for photovoltaic modules," *Sol. Energy Mater. Sol. Cells*, vol. **95**, no. 2, pp. 586– 594, 2011.

- [24] F. González-Longatt, "Model of photovoltaic module in Matlab," 2° Congr. Iberoam. Estud. Ing. Eléctrica, Electrónica y Comput. (II Cibelec 2005), pp. 1– 5, 2005.

- [25] I. Bodnar, B. Csehi, B. Sukaly, and A. C. Gaspar, "Examination of power loss and voltage drop of a solar panel as a function of environmental factors," in *IEEE International Reliability Physics Symposium Proceedings*, 2019, pp. 1–5.

# **CHAPTER 3**

# 3. POTENTIAL INDUCED DEGRADATION – MECHANISMS, DETECTION AND PREVENTION

### 3.1 Introduction

Potential Induced Degradation (PID) is a form of module degradation that occurs due to the high system voltages experienced by modules in PV plants. PID susceptibility is determined by the cell technology, module construction and string configuration. This chapter starts with an introduction into these concepts. Manufacturers have made structural adjustments to the cells, modules and system topologies in order to manage the power drop caused by PID. This chapter discusses the manufacturing process of silicon-based modules and PID as performance limiting defects in detail.

### 3.2 PV cell technologies

### 3.2.1 Monocrystalline cells

Monocrystalline silicon has an ordered crystal lattice structure that is assumed to be defect free [1]. The cells are of high quality and are better performing than multicrystalline under optimum controlled conditions. The disadvantage associated with monocrystalline solar cells is the cost of the complicated manufacturing process. Two of the most common methods used in growth of single crystalline silicon are; the Czochralski (CZ) and the floating zone (FZ) methods. The processes involve growing monocrystalline material by way of seed contact with molten silicon [1][2]. In CZ method a monocrystalline seed crystal is brought in contact with molten silicon allowing crystalline lattice to propagate as the seed is pulled up gradually while undergoing slow rotary motion [3][4]. The monocrystalline boule growth condition would determine the quality and energy efficiency of the resulting monocrystalline cell [5]. The single crystalline boule is sliced into thin wafers of less than 400  $\mu$ m [6], after which they are processed to fabricate solar cells for integration into a PV module.

# 3.2.2 Multi-crystalline cells

The multi-crystalline silicon (m-Si) cells are cast from pure molten multi-crystalline silicon material into square shaped block ingot [3]. The ingot is sliced into thin wafers

using a diamond infused wire [6]. The m-Si are formed in square wafer cells implying that there is less material wastage [3]. Lack of additional crystal growth steps reduces the cost of production; however, this implies that the m-Si cell has more imperfection (defects) which may limit charge carrier mobility resulting in reduced cell performance and conversion efficiency. The imperfection in m-Si cells manifest itself as grain boundaries and crystal dislocations. Grain boundaries create possible regions of local carrier recombination, reduced carrier lifetime and increased local diffusion current densities [3].

In the lattice structure the grain boundaries are visualised as the interface between two different crystal orientations [3]. Dislocations may result from mechanical or thermal stress gradients during ingot growth and wafer slicing [5]. The dislocation and grain boundary defects in cells may have a compounded effect of reducing the  $I_{sc}$  and  $V_{oc}$  of m-Si modules. Multi-crystalline modules are made from cell material with large and unequal grains in the crystal structure oriented at different planes. This gives m-Si a heterogeneous appearance with a blue hue depending on the grain's crystal orientation [3].

# 3.3 Module construction

# 3.3.1 Cell preparation

The wafers are processed into either p-type or n-type cells for use in a module. For ptype cells the wafer is doped with phosphorous, then boron is diffused from one side until its concentration exceeds the phosphorus [2] [3]. Similarly, for n-type the wafer is doped with boron, then phosphorous is diffused into the wafer from one side until its concentration exceeds that of boron [1][3]. P-type cells have the advantage of being resistant to space radiation and degradation hence modules fabricated from it can be deployed for outer space exploration [3]. Alternatively, n-type cells are immune to boron-oxygen defects which decreases the efficiency in p-type modules. The n-type modules are more efficient and are immune to light induced degradation (LID) [3]. Fingers and busbars are then screen printed on the front surface of the cell and then annealed. The back of the cell has an aluminium alloy applied on as the base [3].

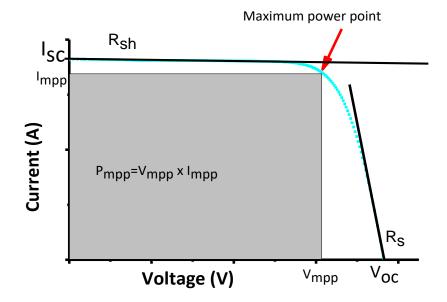

# 3.3.2 Crystalline Silicon module construction

A PV module comprises of cells soldered in series connected strings, as shown in Figure 3.1. Each of the strings has a bypass diode connected across it, so that in an event of cell mismatch the bypass diode will be activated and minimise the power losses.

*Figure 3. 1:* PV module configuration, for a 72 cell modules arranged in 3 string each of 2 cells. Three bypass diodes are connected across each string.

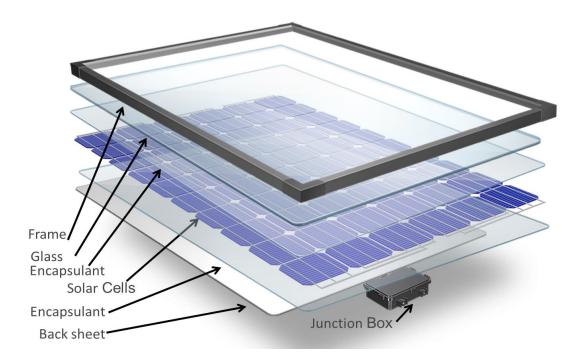

Most PV modules in use today comprise of a glass surface, the solar cells that are sandwiched between two polymeric encapsulation layers and the back sheet shown in Figure 3.2 [7]. The glass surface provides mechanical stability, high transparency, good spectral response and environmental protection of the cells and metallization from external impacts [8]. The encapsulation provides mechanical stability to silicon cells which are brittle in nature. In many modules, EVA (ethylene vinyl acetate) is chosen due to its good UV stability and better glass adhesion to minimise chances of delamination. The back sheet which is generally a permeable polymer, provides mechanical stability and electrical safety. The ARC increases photon absorption and prevents surface reflection [9].

*Figure 3. 2:* A sample structure of a 60 cell monocrystalline module; comprising of the frame, glass cover, encapsulant, back sheet and junction box [7]

In order to produce a required system string voltage, PV modules are connected in series. The number of modules and thus the magnitude of the string voltage, vary from one PV power plant to another. A large string has the advantage of mobilizing a higher system voltage leading to low yield losses, efficient power transmission and the potential for reduced installation and maintenance cost [10][11]. PV power plants are capital intensive and as such the modules deployed should be durable and reliable enough for the duration of the contract which falls between 25-30 years [12]. Figure 3.3 below shows a string with 14 modules (3.5 kW system), with a total output voltage of 516.6 V and current of 8.25 A.

*Figure 3. 3:* A 3.5 kW module string at Outdoor Research Facility at Nelson Mandela University, string Voltage 516.6 V and current of 8.25 A.

# 3.4 Potential Induced Degradation (PID)

### 3.4.1 PID overview

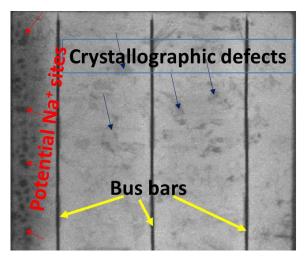

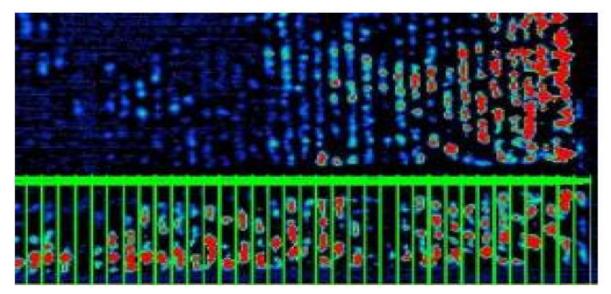

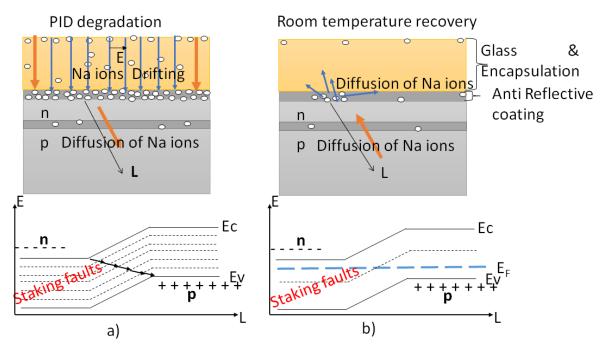

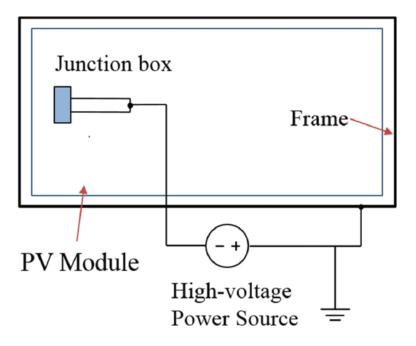

In 1978 at the Jet Propulsion Laboratory PID stress factors was first observed [13]. The degradation was as a result of voltage stress exerted between the frame and the cells. In 2005, a similar effect was observed on n-type modules at SunPower laboratories [14], as the number of large solar power grid tied systems became a reality with reduction in module prices there was increased interest in PID stress [9]. The degradation was associated with negative potential which gave rise to PV module cell current shunting due to positive ions accumulation and forming a layer beneath the ARC resulting in decreased R<sub>sh</sub> and increased R<sub>s</sub>, of the affected modules [15]. These results were confirmed when shunting regions showed Na<sup>+</sup> accumulation and other alkali ions such as potassium (K<sup>+</sup>) within the ARC and stacking faults across the PN junction which provide Na<sup>+</sup> diffusion channels [16]. Drifting Na<sup>+</sup> from glass surface to the ARC require a large electric potential of nearly 1000 V. Upon reaching the cell-ARC interface they spontaneously diffuse into the stalking faults creating an electrically conductive layer which causes the PN junction to behave like it had short circuits [17].

Hara *at el.*, 2015 [18] reported PID in n-type modules where positive charge (K<sup>+</sup>) centres are trapped within the ARC as opposed to Na<sup>+</sup> which accumulate for the case of p-type modules. This kind of PID shunting was found to be reversible and may be avoided by grounding the negative terminal of the PV array, which would automatically impose positive potential to all modules in a string [9] [18] [19]. In a PV module PID

progresses as a dynamic process because the size of leakage current flowing between the ground and cells causing displacement of ions depends on the applied voltage and the resistance in the path between individual affected cells and the grounded frame. Under outdoor PV operating conditions, the surface of the glass plays the role of a major leakage current pathway. In the morning, the glass is more conductive due to dew accumulation on the glass surface, this can be replicated on rainy days where the glass bulk and encapsulation become more conductive than on dry days [20].

Surface soiling may play a significant role by creating a humidity matrix which behaves like a sponge which extend to the grounding resulting in increased leakage currents [9]. As the day progresses the dew evaporates and the resistance to leakage current increases to very high value halting the leakage current [21]. As the temperature increases, PID recovery takes place at the module operating temperature and high solar irradiance [22]. At night the module PID recovery may still be possible even with the presence of dew on the module's glass surface [23]. Module recovery during the day at higher temperatures is much higher than PID recovery during the night at low temperatures [9]. Accelerated PID recovery can be done at night on a power plant using reverse polarity using commercial anti-PID devices. PID lowers energy yield output of a power plant and increases the mismatch losses which if uncorrected my quickly develop into hot spots especially shunted cells.

PID will not develop in a PV system where recovery surpasses the PID stress. The balance between module PID recovery and PID stress become evident with time as the module is deployed to the field for continued operation under harsh environmental conditions [21]. The PID degradation may be influenced by intrinsic characteristic of PV module technology, PV array grounding scheme and system operation voltage which can be up to 1500 V on multi-megawatt PV plants [23]. If PID continues for a long period of time, irreversible electrical corrosion might take place which may require module replacement [4].

#### 3.4.2 PID at system, module and cell level

PID defects are observed in modules with both n-type and p-type cells at cell, module and string level. The polarization is caused when a high potential develops between the cells and the module frame. Many factors contribute to PID progression which may include environmental factors (temperature and humidity), at module level the type of glass, encapsulation, ARC and cells may determine module PID susceptibility. At string or system level the string voltage and type of earthing would play a role.

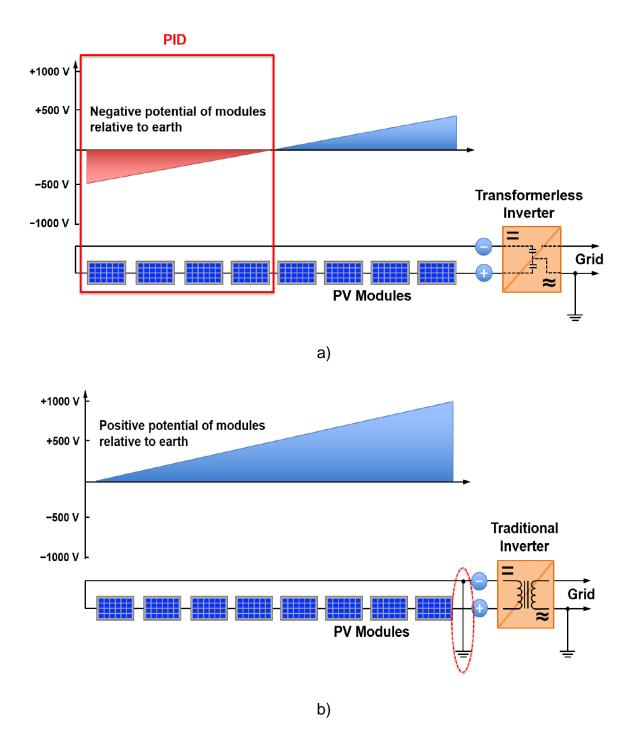

# 3.4.2.1 String level

The size of system voltage is determined by the number of modules connected in series on a string [17]. The string voltage should be designed not to exceed the allowed module system voltage currently set at 1000 V or 1500 V [24]. The type of grounding of the string plays an important role in deterring PID. Three common grounding configurations are used; positive pole grounding, negative pole grounding and no grounding (floating) are used in PV systems depending on inverter capabilities. Whenever a string is not grounded its potential is said to be floating and half of the system is at positive potential while the other half is at negative potential as shown in Figure 3.4. PID affects modules only on the negative potential end of the string[25], [26]. Floating potential is observed when a transformerless inverter without grounding capability is used in a string as shown in Figure 3.4 a). For either positive or negative grounding the naming depends on grounding pole and the type of modules used either n-type or p-type. Figure 3.4b) shows a string of 8 modules that are well grounded. The inverter used isolates the string circuit and the grid circuit hence minimizing chances of high potential developing between the frame and the string circuitry.

*Figure 3. 4:* Comparison of Transformerless Inverter with Transformer Inverter in a PV System a) Transformerless inverter, b) Traditional inverter [25].

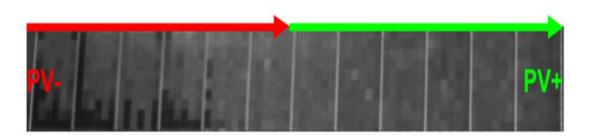

In a floating string affected by PID, the string p-type modules on the negative end will be the most affected as shown in EL image shown in Figure 3.5 [26].

*Figure 3. 5: EL image of PID affected string, modules on the negative side are affected by PID* [26].

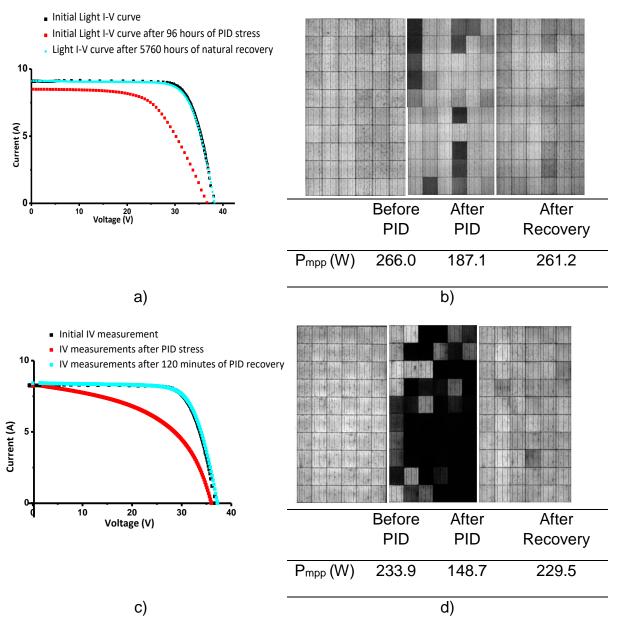

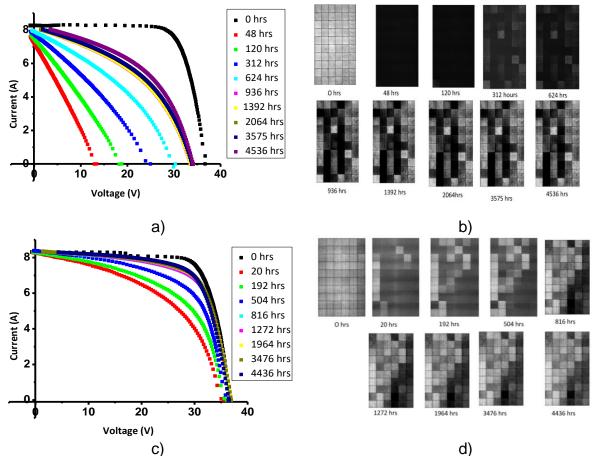

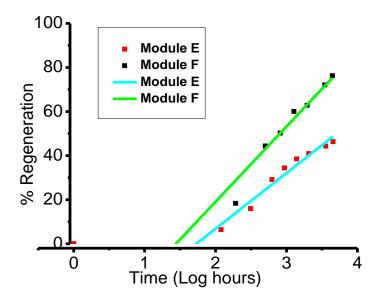

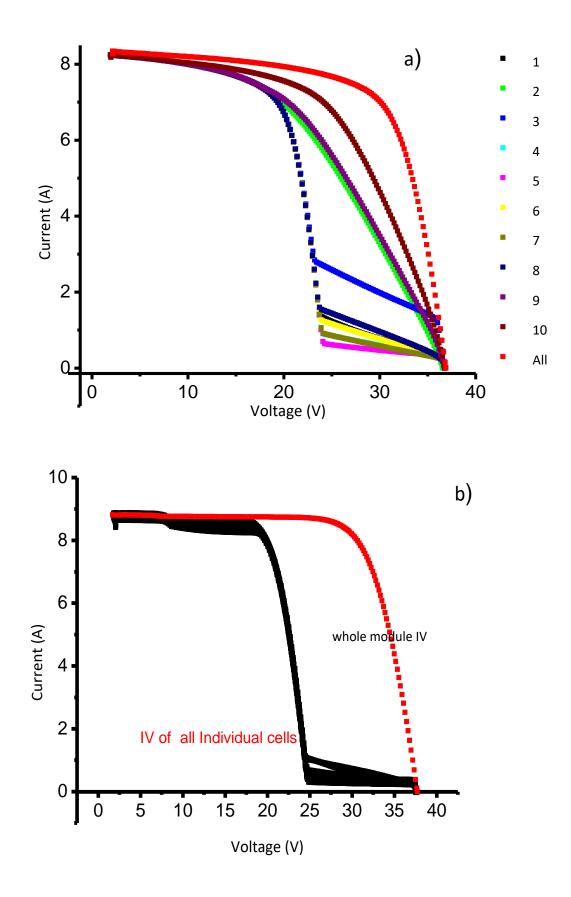

# 3.4.2.1.1 String characterization methods