# ANALYSIS OF FAILURE MECHANISMS THAT IMPACT SAFE OPERATION OF ALGAN/GAN HEMTS

by

Michael David Hodge

A dissertation submitted to the faculty of The University of North Carolina at Charlotte in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

Charlotte

2014

Approved by:

Dr. Ryan Adams

Dr. Ramakrishna Vetury

Dr. Robert Cox

Dr. Edward Stokes

Dr. Stuart Smith

© 2014 Michael David Hodge ALL RIGHTS RESERVED

#### ABSTRACT

# MICHAEL DAVID HODGE. Analysis of failure mechanisms that impact safe operation of AlGaN/GaN HEMTs. (Under the direction of DR. RYAN ADAMS)

The reliability of AlGaN/GaN high electron mobility transistors (HEMTs) is traditionally determined via thermal lifetime acceleration stress tests. More recently it has been proposed that electric field has a prominent role in limiting lifetimes. Multiple failure mechanisms have been proposed as a result of device degradation observed when stressed under high applied electric fields, as typical when the device is biased into the OFF-state. One potential reason for multiple mechanisms could be due to varying levels of quality and maturity of the GaN processes in the reported literature.

The work presented in this dissertation seeks to provide clarity and understanding into the failure mechanism of AlGaN/GaN HEMT devices under high electric fields. The devices in this study were fabricated in a commercial GaN process, notable for exceptional ruggedness and industry leading 65V qualified operational bias for RF power amplifiers. A series of OFF-state, high electric field step-stress experiments, as described in literature, were performed to assess if any were applicable to this process.

It was discovered that device degradation could only be induced when stressed close to the breakdown limits. This lead to the development of a unique stress method that enables the device to be held close to catastrophic breakdown, while avoiding an over stress event that would prevent the device from being studied at the conclusion of the experiment. It was discovered via careful electrical and optical analysis that failure was due to a localized degradation of the Schottky gate diode properties. The physical analysis found the failure inconsistent with the widely reported inverse piezoelectric effect. Instead the failures resemble recently proposed time dependent dielectric breakdown of the AlGaN barrier layer.

#### ACKNOWLEDGMENTS

As my Ph.D. studies come to a close it is important to recognize everyone that has supported me during the journey. The path I chose was unconventional, as I decided to pursue my doctoral work after accepting a position within industry at RF Micro Devices (RFMD). Therefore, these studies required support from both the University of North Carolina at Charlotte (UNCC) and RFMD. At RFMD I must thank Dan Green for pushing me to pursue a Ph.D. and giving me the confidence that such a task was possible while employed at RFMD. A huge thanks goes to my manager at RFMD, Rama Vetury, who advised and guided me the entire process. Rama introduced me to the reliability challenges that were present in modern gallium nitride technology and inspired me to research and seek answers related to this topic that would become the focus of my doctoral work. Without the encouragement, guidance, and discussions with Rama this would have never been possible. Another special thanks to Jeff Shealy who was the general manager for my group at RFMD and also provided his technical expertise and made sure my work and position was funded through the duration of my studies.

I also want to give special thanks to individuals at RFMD that provided insightful technical discussions with regards to GaN devices and reliability. Haldane Henry in the RFMD fab for discussions related to GaN technology and process details. Brian Trabert in the RFMD GaN product line for discussion into reliability of GaN at the product level and collaboration of reliability on projects. Saulius Smetona in RFMD GaN quality group for insight in state of the art reliability and theories of III-V semiconductor technology. I also want to acknowledge the support from Terry Stark and David Shuttleworth in the failure analysis lab for their support and diligence in study of the devices in this work.

At UNCC I want to give a special thanks to my academic adviser, Ryan Adams, for his insight and technical discussion along with guiding me through the process from the academic side and accepting the challenge of advising a student working in industry. I also want to give thanks to my departmental committee members Ed Stokes and Rob Cox for their support and insight into GaN technology and power electronics.

A very special thanks and acknowledgment of the insightful discussion, significant contributions, and funding of this work provided by the United States Air Force Research Lab (AFRL) team led by Chris Bozada. Especially, I want to acknowledge Eric Heller, who worked in collaboration with me during my entire time at RFMD. The quality of the results in this work was greatly enhanced by Eric's contribution. I also want to recognize Dave Via and Don Dorsey at AFRL for their support over the years. I want to thank the Office of Naval Research (ONR) and Paul Maki for funding that was used to support the work in this dissertation. Acknowledgment and thanks to Megarel/NanoTEM, specifically Fred Shapuur for his work in failure analysis of the parts in this study.

Thanks for support to all of my colleagues at RFMD for their encouragement over the years. Specifically, I would like to acknowledge the following individuals: David Aichele, Kevin Bogacki, Eric Carpenter, Mark Everhart, Jon Ferrell, Phil Garber, Joe Gering, Shawn Gibb, Ekatrina Harvard, Brook Hosse, David Hepper, Carl Hinshaw, Cheng-Hui Lin, Kevin Kobayashi, Karthik Krishnamurthy, Sushil Kumar, Jason Martin, James Martin, Pinal Patel, Matthew Poulton, David Runton, Kent Story, Bruce Thompson, and anyone else I have collaborated with professionally.

Finally, I would like to thank my fiancé Nicole for her love, patience and willingness to share time with my studies over the years. I would like to thank my family Athena, Megan, and JoAnne for their love and encouragement while I embarked on my long academic journey. Without my loved ones supporting me, none of this work would have been possible and I dedicate this dissertation to all of them.

# TABLE OF CONTENTS

| LIST            | LIST OF TABLES in       |                                                                   |    |  |

|-----------------|-------------------------|-------------------------------------------------------------------|----|--|

| LIST OF FIGURES |                         |                                                                   |    |  |

| CHA             | CHAPTER 1: INTRODUCTION |                                                                   |    |  |

| 1               | 1.1                     | Gallium Nitride History and Advancements                          | 1  |  |

| 1               | 1.2                     | Applications of AlGaN/GaN HEMT Devices                            | 3  |  |

|                 |                         | 1.2.1 RF Power Applications                                       | 3  |  |

|                 |                         | 1.2.2 Power Switching Applications                                | 7  |  |

| 1               | 1.3                     | Objectives of this Dissertation                                   | 11 |  |

| CHA             | АРТ                     | ER 2: ALGAN/GAN HIGH ELECTRON MOBILITY TRANSISTORS                | 13 |  |

| 2               | 2.1                     | Substrates                                                        | 13 |  |

| 2               | 2.2                     | Bulk Material and Heterojunction Properties                       | 15 |  |

|                 |                         | 2.2.1 GaN and AlGaN Material Properties                           | 15 |  |

|                 |                         | 2.2.2 AlGaN/GaN Spontaneous and Piezoelectric Polarization Fields | 16 |  |

|                 |                         | 2.2.3 Two Dimensional Electron Gas (2DEG) Formation               | 18 |  |

| 2               | 2.3                     | AlGaN/GaN High Electron Mobility HEMT Operation                   | 23 |  |

|                 |                         | 2.3.1 Ohmic Contacts                                              | 24 |  |

|                 |                         | 2.3.2 Schottky Contacts                                           | 25 |  |

|                 |                         | 2.3.3 AlGaN/GaN HEMT Traps and Surface Passivation                | 32 |  |

| 2               | 2.4                     | Summary                                                           | 35 |  |

| CHA             | АРТ                     | ER 3: ALGAN/GAN HEMT RELIABILITY OVERVIEW                         | 36 |  |

|                 | 3.1                     | AlGaN/GaN HEMT Operation and Resulting Stresses                   | 36 |  |

| 9               | 3.2                     | Motivations of AlGaN/GaN HEMT Reliability Studies                 | 39 |  |

|                 | 3.3                     | Reliability Studies of OFF-state Stressed AlGaN/GaN HEMTs         | 44 |  |

|                 |                         | 3.3.1 The Inverse Piezoelectric Effect Degradation Mechanism      | 44 |  |

|                 |                         | 3.3.2 Time Dependent OFF-state Degradation                        | 51 |  |

|    |      |        |                                                   | vii |

|----|------|--------|---------------------------------------------------|-----|

|    | 3.4  | Summ   | ary                                               | 53  |

| CF | IAPJ | TER 4: | RELIABILITY OF COMMERCIAL ALGAN/GAN HEMTS         | 55  |

|    | 4.1  | Step-S | Stress Study of Commercial AlGaN/GaN HEMTs        | 55  |

|    |      | 4.1.1  | Device Details                                    | 55  |

|    |      | 4.1.2  | Step-Stress Experimental Details                  | 57  |

|    |      | 4.1.3  | Step-Stress Study Results                         | 59  |

|    | 4.2  | Const  | ant OFF-State Stress Experiment Details           | 64  |

|    |      | 4.2.1  | Device Details                                    | 65  |

|    |      | 4.2.2  | Stress Method                                     | 65  |

|    | 4.3  | Const  | ant OFF-state Stress Results and Discussion       | 68  |

|    |      | 4.3.1  | Observations                                      | 68  |

|    |      | 4.3.2  | Walk-out                                          | 70  |

|    |      | 4.3.3  | Walk-in                                           | 72  |

|    |      | 4.3.4  | ON-State Characterization                         | 74  |

|    |      | 4.3.5  | Failure Analysis                                  | 76  |

|    | 4.4  | Applie | ed Electric Field Simulation                      | 78  |

|    | 4.5  | Safe C | Operating Voltage                                 | 79  |

|    | 4.6  | Summ   | ary                                               | 81  |

| CF | IAPI | TER 5: | ANALYSIS OF TIME DEPENDENT E-FIELD DEGRADATION    | 83  |

|    | 5.1  | Time   | Dependent Degradation Analysis Experiment Details | 83  |

|    |      | 5.1.1  | Device Details                                    | 84  |

|    |      | 5.1.2  | Breakdown Characterization                        | 84  |

|    |      | 5.1.3  | Electrical Stress                                 | 87  |

|    |      | 5.1.4  | Electrical Degradation                            | 88  |

|    | 5.2  | Electr | ical Analysis                                     | 91  |

|    |      | 5.2.1  | Drain Current Injection Characterization          | 91  |

|    |      | 5.2.2  | Gate Diode Characterization                       | 94  |

|                                   | viii |

|-----------------------------------|------|

| 5.3 Optical Analysis              | 97   |

| 5.3.1 Electroluminescence         | 97   |

| 5.3.2 Thermal Infrared (IR)       | 102  |

| 5.4 Summary                       | 103  |

| CHAPTER 6: REVIEW AND CONCLUSIONS | 106  |

| 6.0.1 Future Work                 | 111  |

| REFERENCES                        | 113  |

# LIST OF TABLES

| TABLE 1.1:    | Comparison of semiconductor material parameters.                      | 4  |

|---------------|-----------------------------------------------------------------------|----|

| TABLE 1.2:    | Comparison of semiconductor Johnson figures of merit.                 | 5  |

| TABLE 2.1:    | Material parameters of Typical GaN Substrates.                        | 14 |

| TABLE 2.2:    | Lattice Constants and Piezo Coefficients for AlGaN and GaN.           | 18 |

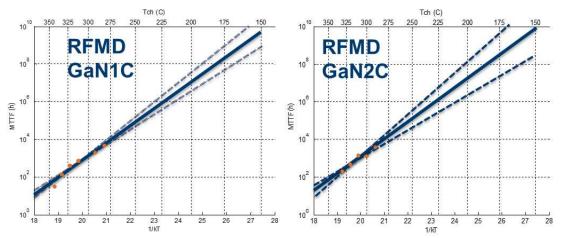

| TABLE 3.1:    | Summary of US domestic foundry GaN reliability data.                  | 43 |

| TABLE 3.2:    | Material parameters used in the inverse piezoelectric effect model.   | 46 |

| TABLE $4.1$ : | Step-stress conditions used in this study for both devices A and B.   | 58 |

| TABLE 4.2:    | Sequence of stress for constant high electric field stress.           | 70 |

| TABLE 4.3:    | ON-state parametric shifts observed under high electric field stress. | 76 |

| TABLE 5.1:    | Stress and analysis plan for second constant stress experiment.       | 84 |

# LIST OF FIGURES

| FIGURE 1.1:  | Theoretical limits of semiconductor materials.                           | 9  |

|--------------|--------------------------------------------------------------------------|----|

| FIGURE 2.1:  | Polarization Fields in the AlGaN/GaN Heterostructure.                    | 16 |

| FIGURE 2.2:  | Polarization fields in AlGaN and GaN epitaxial layers.                   | 17 |

| FIGURE 2.3:  | Polarization sheet charge density as a function of Al content.           | 19 |

| FIGURE 2.4:  | Conduction band diagram for the AlGaN/GaN heterointerface.               | 20 |

| FIGURE 2.5:  | Band diagram comparison of AlGaN barrier thickness.                      | 21 |

| FIGURE 2.6:  | 2DEG charge density as a function of AlGaN barrier thickness.            | 22 |

| FIGURE 2.7:  | Illustration of basic operation of AlGaN/GaN HEMT.                       | 23 |

| FIGURE 2.8:  | Band diagrams for a Schottky metal-semiconductor junction                | 26 |

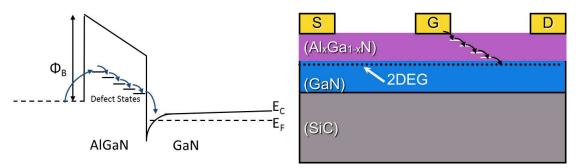

| FIGURE 2.9:  | Gate leakage conduction paths in AlGaN/GaN HEMT.                         | 28 |

| FIGURE 2.10: | Illustration of trap-assisted tunneling mechanisms.                      | 30 |

| FIGURE 2.11: | Illustration of the virtual gating effect in AlGaN/GaN HEMTs.            | 33 |

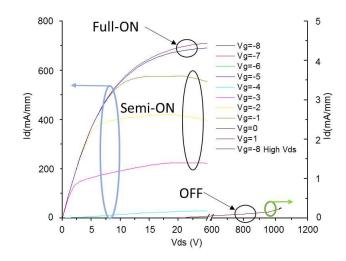

| FIGURE 3.1:  | Various states of operation of the device current vs voltage plot.       | 37 |

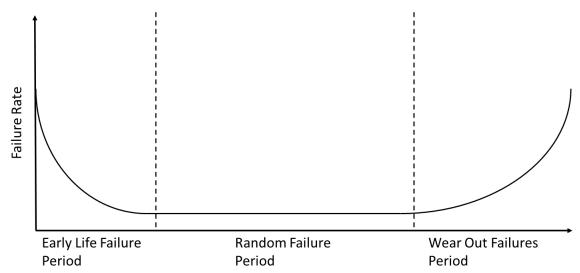

| FIGURE 3.2:  | Illustration of "bathtub curve" related to failure rates.                | 40 |

| FIGURE 3.3:  | GaN process lifetime from three temperature reliability test.            | 43 |

| FIGURE 3.4:  | Proposed gate leakage path due to inverse piezoelectric effect.          | 46 |

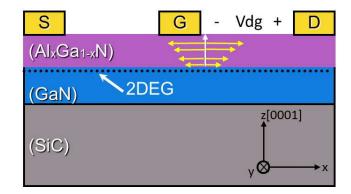

| FIGURE 3.5:  | Tensile strain induced by the applied electric field during stress.      | 47 |

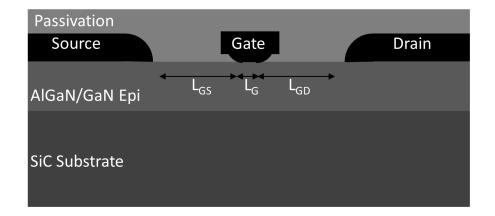

| FIGURE 4.1:  | AlGaN/GaN HEMT device cross section schematic.                           | 56 |

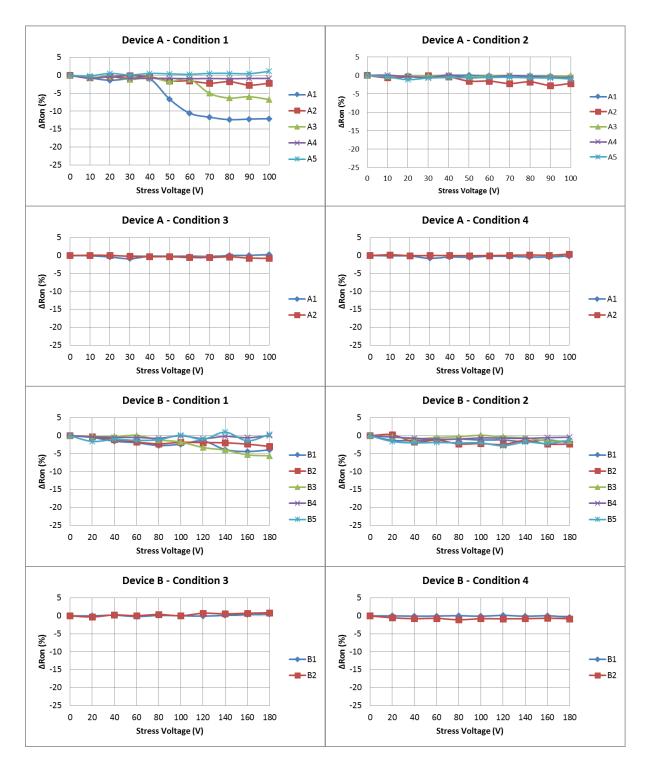

| FIGURE 4.2:  | Parametric shift of $R_{on}$ during the step-stress experiment.          | 60 |

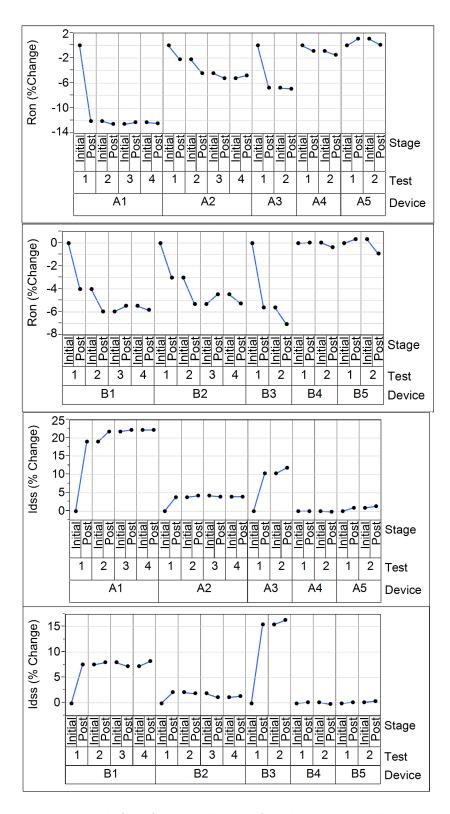

| FIGURE 4.3:  | Parametric shifts of $R_{on}$ and $I_{dss}$ of each device after stress. | 61 |

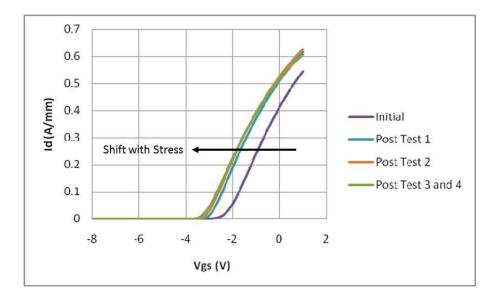

| FIGURE 4.4:  | Shift in threshold voltage observed after stress.                        | 62 |

| FIGURE 4.5:  | Gate leakage current during condition 1 of step-stress study.            | 63 |

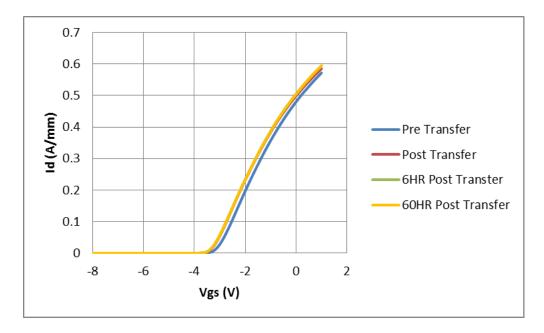

| FIGURE 4.6:  | Transfers curves showing stability up to 60 hours of stress.             | 64 |

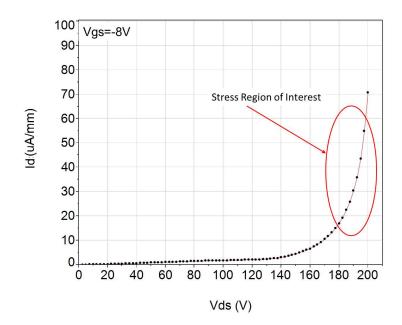

| FIGURE 4.7:  | $I_{ds}$ vs $V_{ds}$ breakdown sweep from a device in this study.        | 66 |

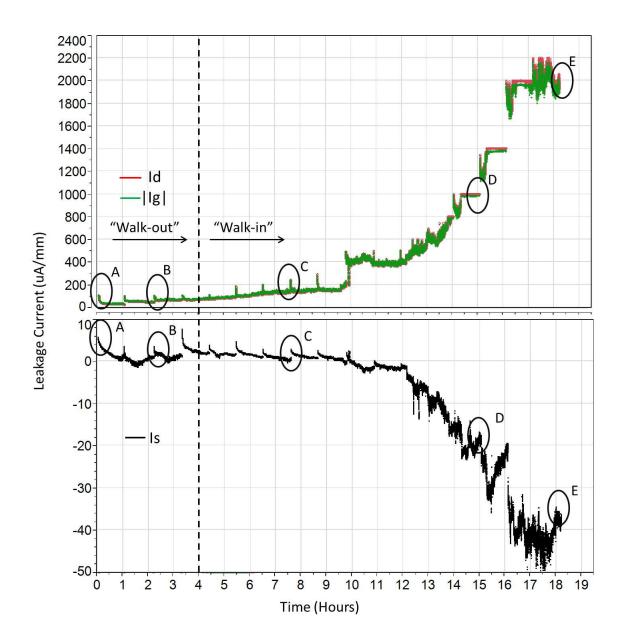

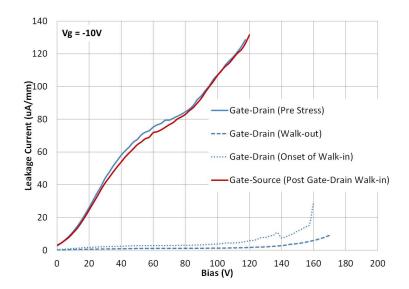

| FIGURE 4.8:  | In-situ stress leakage data during the constant stress study.            | 69 |

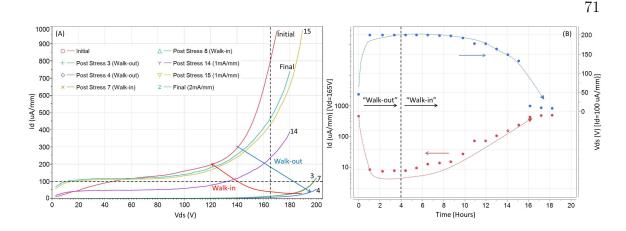

| FIGURE 4.9:  | Three terminal breakdown curves collected during stress.               | 71  |

|--------------|------------------------------------------------------------------------|-----|

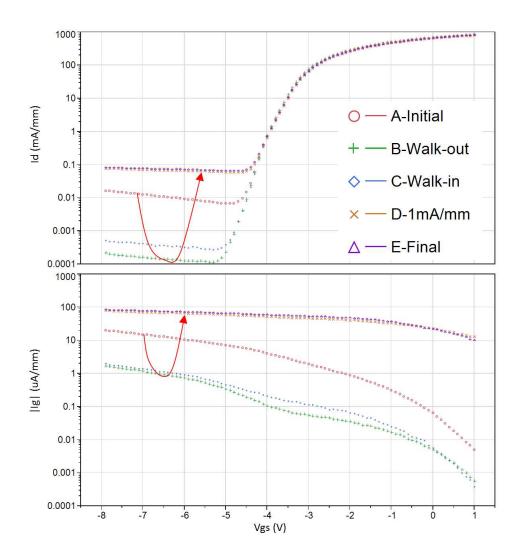

| FIGURE 4.10: | Breakdown characterization from source and drain side.                 | 73  |

| FIGURE 4.11: | Transfer curves from the ON-state characterization during stress.      | 75  |

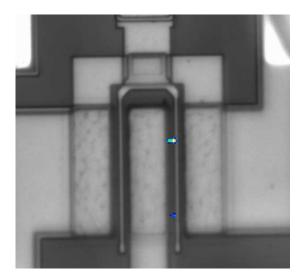

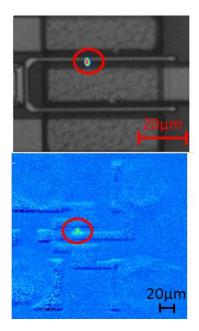

| FIGURE 4.12: | Evidence of localized EL after stress in this study.                   | 76  |

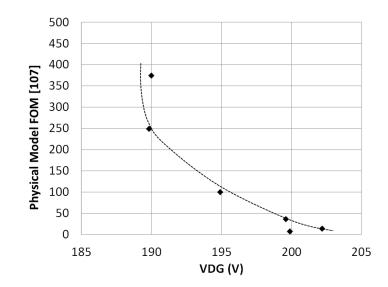

| FIGURE 4.13: | Simulation of stored elastic energy in the AlGaN barrier.              | 78  |

| FIGURE 4.14: | Fit of constant stress data to a field acceleration law.               | 80  |

| FIGURE 5.1:  | Schematic of the drain current injection method.                       | 85  |

| FIGURE 5.2:  | Drain current injection characterization on a AlGaN/GaN HEMT.          | 86  |

| FIGURE 5.3:  | Stress currents measured at both the drain and gate terminals.         | 89  |

| FIGURE 5.4:  | Breakdown characterization at multiple intervals during stress.        | 90  |

| FIGURE 5.5:  | $I_d$ injection characterization with temperature at stress intervals. | 91  |

| FIGURE 5.6:  | Comparison of $I_D$ injection characterization at room temperature.    | 92  |

| FIGURE 5.7:  | Gate diode characterization with temperature during stress.            | 95  |

| FIGURE 5.8:  | Quantified ideality factor and Schottky barrier height with stress.    | 96  |

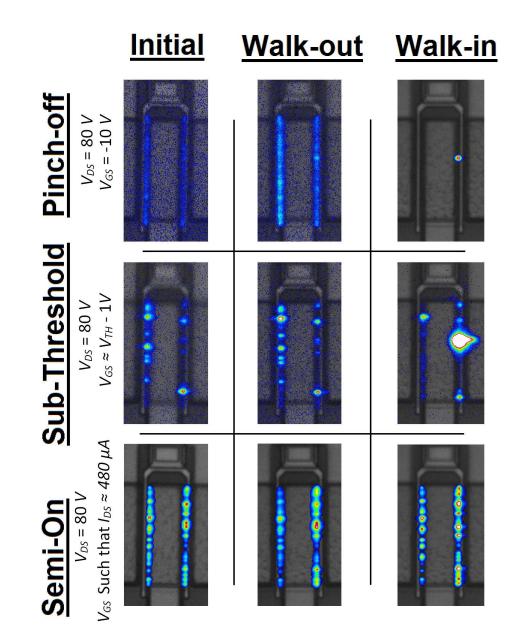

| FIGURE 5.9:  | EL with bias and stress of a representative device.                    | 98  |

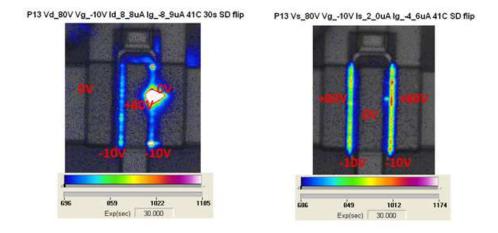

| FIGURE 5.10: | EL when biased from either the drain and source contacts.              | 100 |

| FIGURE 5.11: | Evolution of localized EL with degradation state.                      | 101 |

| FIGURE 5.12: | Comparison of EL and IR imaging after walk-in.                         | 103 |

xi

# CHAPTER 1: INTRODUCTION

This dissertation details a study on semiconductor devices using modern III-V materials and fabrication processes. The semiconductor material system in these devices was the compound gallium nitride (GaN) and it's ternary alloy aluminum gallium nitride (AlGaN). GaN has several attractive properties that make it ideally suited for a wide variety of applications. These include a wide bandgap, enabling the device to sustain high electric fields, a direct bandgap that enables light emission, high charge density and mobility conducting channel, and high mechanical/thermal stability combined with good thermal conductivity.

This chapter will provide a background on GaN materials and advancements. This will be followed by a review of the primary applications suited for GaN based devices. The chapter will conclude with a motivation of work to be detailed in the remainder of the dissertation.

#### 1.1 Gallium Nitride History and Advancements

The earliest reports of gallium nitride formation was in 1932, in publication by Johnson et. al. [1]. However, it wasn't until 1968, when Radio Corporation of America (RCA) began investigations into the feasibility of flat panel displays, did GaN research truly begin. A researcher at RCA, H. Maruska, reported successful epitaxial growth of GaN on sapphire substrates [2], also that GaN was natively ntype material. Additional work from the RCA group proved that GaN would emit light when excited by a laser, a property of direct bandgap materials [3]. Furthermore, it was possible to make GaN p-type by doping the material with magnesium (Mg) [4] and so it was possible to generate electroluminescence [5]. However, while this work Up until the early 1990s, research involved improving the crystal quality and finding a shallow p-type dopant to enable the manufacture of GaN light emitting diodes (LEDs). The breakthroughs in crystal quality were initially published by Yoshida et al. [6], describing high quality GaN epitaxy, via molecular beam epitaxy (MBE), on sapphire substrates by first growing an aluminum nitride interlayer between the GaN and non-native substrate. This was due to the fact that AlN had a much better lattice match to GaN than the traditional substrates. These findings were eventually applied to growth of GaN epitaxy via metal organic chemical vapor deposition (MOCVD) by Amano et. al. [8]. In this article the two step growth method, widely used in MOCVD growth, was introduced that consists of first growing the AlN buffer layer at lower temperature and then growing the GaN epitaxy at higher temperatures. This work was extended to growth of p-type GaN by demonstrating successful growth via the use of low energy electron beam irradiation (LEEBI) of Mg [9].

devices, the material quality was not sufficient for practical applications.

These advancements in the growth quality of GaN greatly accelerated research into the feasibility of a wide range of semiconductor devices in power applications in order to harness the many advantages offered by this material system. These applications ranged from optical, power switching, and RF power applications. The possibility of GaN based transistors was realized by Khan et al. [10] in 1990, when it was demonstrated that a high carrier mobility conducting channel could be formed by growing a thin layer of aluminum gallium nitride (AlGaN) on top of the GaN epitaxy forming a highly conductive channel at the interface. Two years after this result the group was able to successfully report on the first AlGaN/GaN high electron mobility transistor (HEMT)[11].

The demonstration of a GaN HEMT enabled the material system to play a significant role in the semiconductor industry. This was solidified further when Nakamura et. al. [14] was able to report the first high brightness, double heterostructure blue LED in 1994. This same group extended their work to include multi-quantum well structures in 1996 and was able to demonstrate the first GaN laser diode in the same year [15]. The breakthroughs in discovery of both a transistor and LED for GaN would set in motion a torrent of research and publications in the subsequent years exploring the capabilities of the material.

The adoption of GaN into optical applications has been swift with many commercial items from media players to lighting that now include GaN light emitting devices. Despite the progress reported in GaN power and RF electronic devices in the years since Khan demonstrated the GaN transistor, there still remains a vast amount of potential to be unlocked. Nevertheless, even operating at a fraction of it capability these devices offer enhanced performance when compared to competing semiconductor technologies such as silicon (Si) or other III-V based devices.

## 1.2 Applications of AlGaN/GaN HEMT Devices

The advancements in AlGaN/GaN HEMTs and LEDs has enabled many applications to utilize the unique properties offered by this technology. As was mentioned in the previous section, GaN LEDs and laser diodes have had tremendous success in penetrating the consumer market for a wide range of applications. The push for green energy will continue to enable adoption in the solid state lighting markets. The work presented in this dissertation will focus on the HEMT side of the technology and as a consequence the LED applications are outside of the scope of this work. In this section the applications for GaN transistors will be presented and discussed.

## 1.2.1 RF Power Applications

As the world increasingly relies on wireless technology the requirements of microwave systems are more demanding. On the consumer side, system bandwidth requirements have become increasingly taxing with the growing popularity of smart phones, tablets, and other mobile media devices. Furthermore in emerging markets there is a desire for wireless infrastructure for media connectivity in base station applications that further increase demands for bandwidth and power.

The military industry is also a major driver of RF power devices. Applications include phased array RADARs, electronic warfare such as jamming and surveillance, and communications. More recently mechanized warfare and surveillance through the use of unmanned aerial vehicles (UAV) or drones have placed a high demand on cutting edge RF power devices.

Table 1.1: Comparison of material parameters for competing semiconductor technologies in the RF and power electronic markets. Semiconductor materials shown are gallium nitride (GaN), silicon (Si), gallium arsenide (GaAs), and silicon carbide (SiC) [12] [13]

|                         | $\operatorname{GaN}$ | $\mathrm{Si}$ | GaAs         | $\operatorname{SiC}$ |

|-------------------------|----------------------|---------------|--------------|----------------------|

| $E_g \ (eV)$            | 3.4                  | 1.1           | 1.4          | 3.2                  |

| $E_c \ (MV/cm)$         | 3.3                  | 0.4           | 0.4          | 3                    |

| $\epsilon_r$            | 9                    | 11.9          | 12.9         | 10                   |

| $n_i \ (cm^{-3})$       | $1.9X10^{-10}$       | $9.6X10^{9}$  | $2.1X10^{6}$ | $8.2X10^{-9}$        |

| $\mu_n \ (cm^2/Vs)$     | 900                  | 1450          | 8000         | 600                  |

| $v_{sat} \ (10^7 cm/s)$ | 2.5                  | 1             | 1.2          | 2                    |

| $\Theta_K (W/cmK)$      | 1.3                  | 1.5           | 0.4          | 3.3                  |

A comparison of intrinsic material parameters for competing semiconductor materials in the RF and power electronics application space is shown in Table 1.1. The incumbent materials in the field are Si and GaAs. In lower frequency RF applications, such as L-band and S-band, the primary choice has historically been Si. The dominant RF power device in silicon is the lateral double-diffused-metal-oxidesemiconductor field-effect-transistors (LDMOS FETs). However, LDMOS FETs are limited to operation up to 3.5 GHz [16] due to intrinsic material properties.

Beyond S-band, the choice has typically been GaAs due to superior performance for high frequency operation. This may be attributed to the material high carrier mobility as shown in Table 1.1. One drawback to this choice of material is that high power densities are not possible in conjunction with the frequency performance. From Table 1.1, GaAs has the lowest critical field of the listed semiconductors, limiting the electric field that can be applied to the device. The maximum power density for GaAs devices when operated in S-band has been reported to be 3.4 W/mm [17].

For next generation applications, RF power devices need to offer a combination of high frequency of operation while providing high power densities. This requires that the intrinsic properties have both high electron velocity and high critical electric fields. Wide bandgap materials offer the possibility of achieving this desired combination. The semiconductors of interest from Table 1.1 are GaN and SiC. The superiority of these materials may be demonstrated by applying the Johnson figure of merit (JM) which was published by Johnson et al. [18] as a means of comparing semiconductor technologies as RF power devices based on intrinsic properties. The figure of merit is given by the following equation.

$$JM = \frac{E_c \cdot v_{sat}}{2\pi} \tag{1.1}$$

A plot of the JM for each of the semiconductors in Table 1.1 is shown in Table 1.2, normalized to the JM of Si. This clearly illustrates the potential of GaN and SiC to displace Si and GaAs as the choice semiconductors for RF power applications.

Table 1.2: Johnson figure of merit (JM), normalized to silicon (Si), for the semiconductor materials shown in Table 1.1. This illustrates that wide bandgap semiconductors SiC and GaN have the potential to displace Si and GaAs and the choice semiconductors for RF power applications.

| 1             |                |                |                |                |

|---------------|----------------|----------------|----------------|----------------|

|               | Si             | GaAs           | SiC            | GaN            |

| JM            | $6.37X10^{11}$ | $7.64X10^{11}$ | $9.55X10^{12}$ | $1.31X10^{13}$ |

| Normalized JM | 1              | 1.2            | 15             | 20.6           |

The intrinsic material properties of GaN and SiC may suggest similar performance. However, in practice this is not the case since GaN HEMTs have been demonstrated while the same cannot be said for SiC. The high mobility channel provided by the HEMT structure yields superior performance under high frequency operation. In fact, the main advantage of SiC when compared to GaN is the high thermal conductivity by more than a factor of 2. As mentioned in the previous section, GaN is grown on non-native substrates via epitaxial growth processes. Because of this GaN may be epitaxially grown on SiC substrates so that the thermal advantages of SiC may be combined with the frequency and power capabilities of GaN.

The high power density allows GaN to match or exceed GaAs power amplifiers with much smaller transistors and less cooling due to thermal properties. This allows for a reduction in both size and weight of a RF module. The record power density for GaN on SiC substrates was reported as 41.4 W/mm at 4GHz [19] and represents an order of magnitude advantage over other semiconductor technologies. In the realm of mm-wave frequencies, GaN has demonstrated a power density of 10 W/mm at 40 GHz [20].

Recently there has been a push to integrate GaN into an array of RF applications beyond power amplifiers. Commercially available GaN RF switches have been offered in recent years [21] and [22]. The intrinsic properties of GaN make it attractive for switches, such as high carrier mobility resulting in low insertion loss (IL), low dielectric constant that minimizes off capacitance and therefore increases isolation (ISO), and the high critical field enables high power operation. The incumbent semiconductor technologies in this space are Si and GaAs. In terms of providing high linearity and broadband performance, GaAs and silicon-on-insulator (SOI) are the primary choices with the limitation being power handling, limited to power levels <10 W. Si PIN diode switches are used in high power applications with the drawback of high bias currents needed to achieve low loss and high isolation. This required bias circuitry adds to system cost, size, and power requirements.

GaN switches have demonstrated marked improvement over the incumbent technologies. Broadband switches have been demonstrated, with frequency of operation as wide as DC-18GHz while maintaining IL < 1.5 dB and ISO > 30 dB [23]. High power switches have been reported with a 0.1 dB compression in IL up to 100 W at 2 GHz [24] demonstrating an order of magnitude improvement over the existing technologies. The only parasitic power draw of GaN switches is associated with the gate leakage current under OFF-state gate bias that typically is on the order of micro amps, resulting in very little power consumption.

#### 1.2.2 Power Switching Applications

Power switching devices are used in an array of power conversion applications that involves transforming a DC voltage to a lower value (buck converter) or to a higher value (boost converter). This may also be extended to converting a power source from AC to DC and vice versa. The critical feature of power conversion devices is the efficiency at which these transformations take place. Two primary losses impact efficiency, conduction and switching losses. Conduction losses occur when the switch is in the ON state and are due to the parasitic resistance of the device, typically referred to as the on-resistance  $(R_{ON})$ . The switching losses manifest when the device is transitioning from OFF to ON state and vice versa. The power losses are the product of the current from source to drain and voltage present across the source and drain terminals. In the ON-state the voltage is low (limited by  $R_{ON}$ ) and the current is high. In the OFF-state, the voltage is high and current is low (limited by small leakage current in the FET). During the transition there is a short period of time where moderate amounts of voltage and current are present that represents a large loss in power. Switching losses may be minimized by reducing the switching times  $(t_{ON} \text{ and } t_{OFF}).$

Switching losses play a significant role in normal operation and as a consequence, the frequency at which the converter operates (i.e. ON and OFF cycles) is minimized. The penalty is that the lower the switching frequency, the larger the passive components required in the converter. This in turn leads to increases in size and weight. One of the drawbacks of incumbent silicon technology is due to the low current density. This requires large area devices to source high currents. As the chip area increases so does parasitic capacitances that lead to increased switching times, resulting in larger switching losses. Therefore, a technology that minimizes switching losses, via increases in switching speed, could greatly reduce size, weight, and cost of a power system by simply operating at higher switching frequencies.

The other limitation of incumbent silicon technology is that operation temperature is normally limited to around  $80^{\circ}C$ . The heat generated in the device due to the losses combined with the high ambient temperatures may require the system to have additional cooling capabilities for the power converter system. An example of this would be hybrid electric vehicles, that has separate cooling systems for both the combustion engine and the power inverter system. Wide bandgap technologies can operate at much higher junction temperatures,  $250^{\circ}C$  is typical for GaN and the higher thermal conductivity means removal of heat from the power device is easier. This has the potential to either greatly reduce or even eliminate the cooling systems from some applications greatly reducing weight and increasing range in the electric vehicle example.

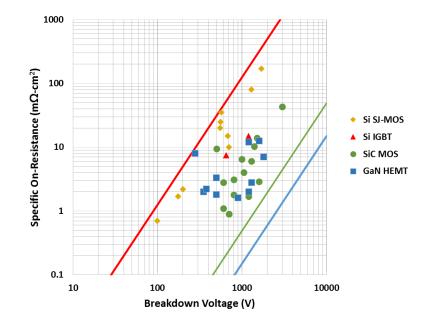

When comparing switch devices, a first order comparison is called the power device figure of merit, which is simply  $V_{BD}^2/R_{ON}$ . Where  $V_{BD}$  is the breakdown voltage of a device. When designing a power device these parameters have an inverse relation to one another, so this tradeoff must be optimized for a given application. Figure 1.1 is a plot of specific on-resistance versus breakdown voltage, with the data points showing reported achieved performance and the lines represent the theoretical limits. It has been demonstrated by silicon that these theoretical limits may be surpassed via optimization in FET architecture. The super-junction architecture [25] is one such way and as seen in Figure 1.1, the work utilizing this approach is already at the theoretical limit. Also, beyond the SJ-MOS limit is the silicon insulated gate bipolar transistor which has been the incumbent device for high voltage switching applications

Figure 1.1: Theoretical limits and reported results comparing power switching devices. Resistance is shown as specific on-resistance  $R_{sp}$  plotted versus breakdown voltage. Semiconductor technologies compared are silicon (Si), Super-Junction silicon MOSFET (SJ-MOSFET), silicon insulated gate bi-polar transistors (IGBT), silicon carbide (SiC), and gallium nitride (GaN) [26] [28].

in the 600 V and 1200 V range. However, these devices suffer long switching times leading to drops in efficiency due to switching losses.

GaN is a formidable contender to these incumbent Si technologies due to superior critical electric field as was shown in Table 1.1 combined with the low resistance two dimensional electron gas (2DEG) channel, that will be detailed in Chapter 2. This highly conductive, low resistance channel enables for GaN devices to source the same current levels offered by Si technology with much smaller chip area. These small chip sizes not only provide compact solutions but also minimize parasitic capacitances that limit switching speed and, by extension, switching losses. These advantages are represented in Figure 1.1 as the theoretical limit of GaN is well ahead of the competing technologies. The closest semiconductor technology would be SiC. However, it should be noted that this chart does not account for additional performance metrics such as switching losses, power density, frequency capability, and cost. In all of these metrics GaN has an advantage over SiC except for cost which is on the same order if SiC substrates are used. However, cost can become yet another advantage for GaN by using alternative, cheaper substrates such as Si.

The final challenge that GaN must overcome in power applications to increase adoption and further displace silicon is the development of an enhancement mode (Emode) (normally off) AlGaN/GaN HEMT without sacrificing performance. Normally OFF devices are preferred and sometimes required in power electronics applications for safety reasons. GaN HEMTs are by nature depletion mode devices (D-mode) (normally on) since the conducting channel is spontaneously created as a consequence of material growth.

There exists a variety of reported methods in literature shown to demonstrate E-mode AlGaN/GaN HEMTs. One common method involves etching a recess in the AlGaN barrier under the gate contact to deplete the underlying channel under the gate contact [29], [30], [31], [32]. Another method involves implantation of negatively charged ions in the gate region, such as fluorine [33]. Also proposed is the growth of additional epitaxial layers above the AlGaN layer, such as InGaN [34], to induce a polarization field to shift the threshold voltage positive. Generally the performance of E-mode AlGaN/HEMTs has been demonstrated as inferior when compared to the D-mode counterparts. This has been attributed to a reduction in the gate voltage swing during operation. To counteract this effect, the use of epitaxial barrier layers, on top of the AlGaN/GaN layers, have been shown to overcome these limitations [34], [35], [36]. Another practical method of achieving normally off operation is by placing a normally OFF FET, such as Si, in cascode with a D-mode GaN HEMT [28]. E-mode GaN power devices have recently been made commercially available, with operation up to 600 V [37].

#### 1.3 Objectives of this Dissertation

AlGaN/GaN devices have made major strides in recent years to displace many incumbent semiconductor technologies in a wide array of power electronics applications. The role of the applied electric field in accelerating device lifetimes and their exact failure mechanisms are not completely understood in literature. As a consequence, this may be seen as limit on GaN technology achieving it's true potential. For example many AlGaN/GaN HEMTs in the market have listed breakdown voltage more than a factor of three higher than the operating bias voltage. The same may also be said of power switching devices, that also show much higher breakdown voltages than specified by the intended application. This suggests that the parts are over designed to meet reliability requirements and that some optimization in the performance vs reliability tradeoff may be better achieved if failure mechanisms due to high applied electric fields are better understood.

Recently there has been discussion in literature about the reliability impacts, especially when switching devices are biased in the OFF-state blocking high RF and DC voltages. These publications have reported a wide variety of results that have led to debate on the actual failure mechanism and their root causes. Because of these varying results there is no clearly understood method of stressing and characterizing devices in the OFF-state.

In this research work the scope was to perform a reliability study on a commercially available and qualified AlGaN/GaN HEMT process that is notable for high breakdown voltage and state of the art power density. The goal was to understand how these devices degrade in the presence of high electric fields. Once degradation is observed it becomes imperative to identify the symptoms of this degradation and how it impacts the device electrically via detailed characterization. From this characterization and analysis a root cause failure mechanism is determined. Any advancement in understanding of device failure could then be used to better assess safe operating conditions of AlGaN/GaN devices, allowing them to be optimally designed for their intended applications.

# CHAPTER 2: ALGAN/GAN HIGH ELECTRON MOBILITY TRANSISTORS

This chapter will focus on the details of AlGaN/GaN HEMT fabrication and the physics behind the operation of these devices. It begins with an overview of the intrinsic material properties of Gallium Nitride (GaN). This is followed with a description of the heteroepitaxy of GaN and the alloy, Alumnium Gallium Nitride (AlGaN), and how this leads to the formation of a conductive two-dimensional electron gas (2DEG). Following a discussion on the principles of operations of AlGaN/GaN HEMT devices, the chapter concludes with the fabrication process used to form an AlGaN/GaN high electron mobility transistor (HEMT) as well as an overview of contact formation and properties along with surface passivation.

#### 2.1 Substrates

Ideally, gallium nitride based devices would be grown via homo-epitaxy on native GaN substrates. Recently bulk GaN substrates in 4 to 6 inch diameter wafers have been realized but are still cost prohibitive for large scale manufacturing. As an alternative, cost efficient non-native substrates are used so that GaN HEMTs are grown via hetero-epitaxy. Typical materials for GaN substrates are silicon (Si), sapphire  $(Al_2O_3)$ , and silicon carbide (SiC).

Table 2.1 shows the mechanical properties of GaN compared to the three most popular materials used as the substrate. The disadvantages of growth on non-native substrates are derived from the inherent lattice mismatch that leads to the formation of threading dislocations in the epitaxial layers. In modern GaN devices, dislocation densities number in the range of  $10^{-7} - 10^{-10} cm^{-2}$ .

Early in the development of GaN devices, sapphire was the substrate of choice

|                  | 51                          |                                                       |

|------------------|-----------------------------|-------------------------------------------------------|

| Lattice Constant | Coefficient of Thermal      | Thermal Conductivity                                  |

| (Å)              | Expansion $(10^{-6}K^{-1})$ | (W/cmK)                                               |

| 3.19             | 5.45                        | 1.3                                                   |

| 3.08             | 4.46                        | 5                                                     |

| 5.43             | 3.59                        | 1.5                                                   |

| 4.76             | 7.5                         | 0.5                                                   |

|                  | (Å)<br>3.19<br>3.08<br>5.43 | 3.19     5.45       3.08     4.46       5.43     3.59 |

Table 2.1: Material Parameters of Typical GaN Substrates [41] [42]

due to its low cost and mechanically stable properties; sapphire substrates are still popular for GaN optoelectronic applications. However, alternatives to this material are needed for high power devices due to poor thermal conductivity.

Silicon is another low cost substrate option that provides an improvement in thermal conductivity over sapphire. One principle drawback is the large lattice mismatch with GaN that degrades the quality of the GaN epitaxy. Despite this mismatch, additional buffer layers and growth techniques have been developed to improve GaN epitaxy layers grown on silicon. GaN power devices grown on silicon wafers with diameters up to 8 inches have been demonstrated [39]. For large scale manufacturing, at low cost, and reasonable device performance, silicon is an attractive option for GaN power devices. The final substrate commonly used for GaN power devices is silicon carbide and is by far the best choice from a performance perspective. SiC has a minimal lattice mismatch with GaN (<5%) which provides for high quality epitaxial GaN films to be achieved during growth without the need of intermediate buffer layers. SiC has an extremely high thermal conductivity that is ten times higher than sapphire and three times higher than silicon or gallium nitride, making it the premier choice for high power devices. SiC wafer sizes lag behind Si as state of the art GaN-on-SiC wafers have been demonstrated up to 6 inches in diameter. Additionally, SiC wafers are substantially more expansive than both Si or sapphire, which currently prevents SiC from becoming the clear substrate choice for GaN devices.

#### 2.2 Bulk Material and Heterojunction Properties

#### 2.2.1 GaN and AlGaN Material Properties

Gallium nitride can be synthesized in two different crystal structures. The first type is a zinc blend structure with a cubic shaped lattice; the second type is a wurtzite structure utilizing a hexagonal shaped lattice. Both crystal types incorporate mechanical strain in the growth process which gives rise to piezoelectric properties that have a large impact on the charge density and electric field distribution within the material[40][43]. In addition to piezoelectric effects, wurtzite materials also possess a very large spontaneous polarization field due lattice charge transfer between the highly electronegative nitrogen atoms and the less electronegative gallium atoms. Depending on the growth method the crystal may be orientated either Ga-face or N-face as shown in Figure 2-1, which determines the polarity of the spontaneous electric field[44]. The devices used in this study were fabricated from Ga-face wurtzite crystal.

GaN crystal growth is achieved via one of two different methods, metalorganic chemical vapor deposition (MOCVD) or molecular beam epitaxy (MBE). MBE growth occurs at lower temperatures in the 600-900°C range. The process is highly controlled as the crystal is deposited one atomic layer at a time. However, this means that growth is very slow. The MOCVD method has several advantages over MBE. MOCVD growth is fast, at a rate of a few micrometers per hour, with multi-wafer capability easy to integrate. MOCVD growth temperatures are high, on the range of 1000-1100°C, which is thermodynamically favorable. Finally, the overall quality of GaN epitaxy layers is high when compared to MBE. Due to these numerous advantages MOCVD is the dominant growth method for commercial GaN devices.

Both GaN and the alloy AlGaN are wide bandgap materials with high critical electric fields. The bandgap of GaN is 3.4 eV and the bandgap of Al<sub>x</sub>Ga<sub>1-x</sub>N depends on the ratio of Al to Ga in the alloy. This can be determined from equation 2.1[44].

| Aluminum Gallium Nitride (AlxGa1-xN) | ↓ P <sub>SP</sub> | ↓ P <sub>PE</sub> | Tensile Strained |

|--------------------------------------|-------------------|-------------------|------------------|

| Gallium Nitride (GaN)                |                   | Р <sub>SP</sub>   | Relaxed          |

| Silicon Carbide (SiC)                |                   |                   |                  |

Figure 2.1: Polarization fields in typical AlGaN/GaN heterostructure.  $P_{SP}$  represents the spontaneous polarization that is inherently present in all III-N compounds.  $P_{PZ}$ denotes the piezoelectric polarization that is present in the strained epitaxial layer.

$$E_g(x) = x6.13eV + (1-x)3.42eV - x(1-x)1.0eV$$

(2.1)

Both GaN and AlGaN have very high critical electric fields of 3 MV/cm for GaN and up to 11 MV/cm for AlGaN depending on the ratio of Al and Ga. Both GaN and AlGaN are very stable materials both mechanically and electrically over a wide range of temperatures. Electrical stability with temperature may be illustrated by defining the temperature at which the intrinsic carrier concentration reaches  $10^{15}cm^{-3}$ as the threshold which the semiconductor becomes as conductor. Silicon reaches this intrinsic carrier concentration at  $315^{\circ}C$  while GaN retains its semiconducting properties up to  $1300^{\circ}C$ . [13] [45].

## 2.2.2 AlGaN/GaN Spontaneous and Piezoelectric Polarization Fields

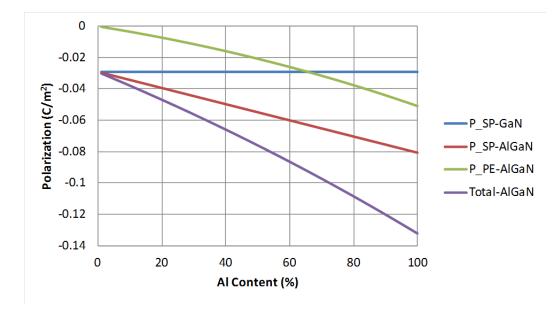

AlGaN/GaN HEMT formation starts with the growth of a thin layer of AlGaN (~ 20 nm) on top of a thick layer of GaN (~  $1 \mu m$ ). An example of the epitaxial stack and the polarization fields is shown in Figure 2.1. The spontaneous polarization is present in both layers due to inherent properties described in the previous section. The spontaneous polarization in GaN is  $-0.029 C/m^2$ , while the spontaneous polarization in the AlGaN layer can be calculated from equation 2.2.

$$P_{SP}(x) = (-0.052x - 0.029)C/m^2$$

(2.2)

Figure 2.2: Calculated polarization fields in AlGaN and GaN epitaxial layers in a AlGaN/GaN heterostructure as a function of Al content. Since  $P_{SP}$  and  $P_{PZ}$  in the AlGaN layer have the same polarity, the total magnitude is the sum of both fields.

The second polarization field present in the heterostructure is the piezoelectric polarization due to strain present in the epitaxial layers. The lattice constant of AlGaN is smaller than that of GaN so the epitaxial AlGaN layer is tensile strained when grown on top of GaN. No piezoelectric polarization is present in the GaN layer due to its relaxed state. The piezoelectric polarization field can be calculated by using equation 2.3.

$$P_{PE} = 2\left(\frac{a-a_0}{a_0}\right)\left(e_{31} - \frac{e_{33}C_{13}}{C_{33}}\right)$$

(2.3)

In this equation the  $2(a - a_0)/a_0$  term represents the in-plane strain,  $a_0$  is the intrinsic lattice constant, and a is the deformation lattice constant due to strain. The terms  $e_{13}$  and  $e_{33}$  represent the piezoelectric coefficients while  $C_{13}$  and  $C_{33}$  represent the elastic coefficients. A summary of the these terms for both GaN and AlGaN are given in Table 2.2.

A plot of the calculated polarization fields in both AlGaN and GaN epitaxial

|                 | GaN  | AlGaN           |

|-----------------|------|-----------------|

| $a_0(A)$        | 3.19 | -0.077x + 3.189 |

| $C_{13}(GPa)$   | 103  | 5x + 103        |

| $C_{33}(GPa)$   | 405  | -32x + 405      |

| $e_{13}(C/m^2)$ | 3.08 | -0.11x - 0.49   |

| $e_{33}(C/m^2)$ | 5.43 | 0.73x + 0.73    |

Table 2.2: Lattice Constants and Piezoelectric Coefficients for AlGaN and GaN [44].

layers versus Al content is shown in Figure 2.2. Note that as Al content increases so does the spontaneous and piezoelectric fields in the AlGaN layer. Also, since the polarity of both of the spontaneous and piezoelectric fields are the same they combine to increase the magnitude of the total field.

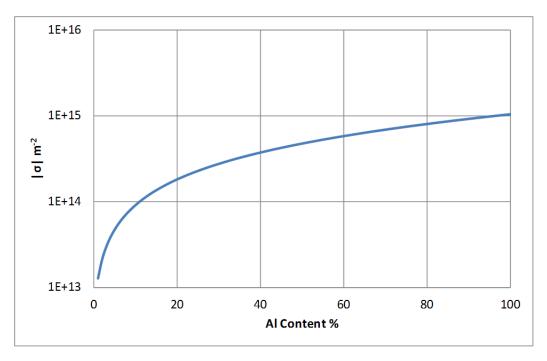

A polarization gradiant gives rise to a sheet charge density given by  $\rho_P = \nabla P$ . As seen in Figure 2.3 there exists an abrupt change in polarization at the AlGaN/GaN interface. The polarization sheet charge is generally defined as:

$$\sigma = (P_{SP_{top}} + P_{PE_{top}}) - (P_{SP_{top}} + P_{PE_{bottom}})$$

(2.4)

In the typical case of tensile strained AlGaN epitaxially grown on top of relaxed GaN, the equation becomes:

$$\sigma = (P_{SP_{AlGaN}} + P_{PE_{AlGaN}}) - (P_{SP_{GaN}})$$

(2.5)

This indicates that at the AlGaN/GaN heterointerface there exists a permanent fixed polarization sheet charge. As the Al content of AlGaN increases, so does the magnitude of the sheet charge at the interface.

## 2.2.3 Two Dimensional Electron Gas (2DEG) Formation

As shown earlier in the chapter, both GaN and AlGaN are inherently electrical insulators. Therefore, the material system relies on the polarization fields detailed in the previous section to form a conductive channel at the hetero-interface. The

Figure 2.3: Calculated polarization sheet charge density as a function of Al content in the AlGaN barrier layer [44].

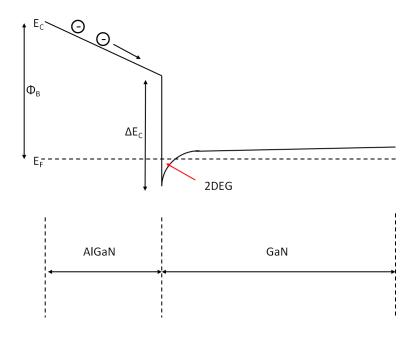

polarization fields in both the AlGaN/GaN epitaxy (Ga-face) give rise to a highly positive sheet charge density. Electrons are then attracted by this positive sheet charge so that the electrons become spatially confined at the hetero interface as shown in Figure 2.4. These confined electrons are quantized in two dimensions, leading to the formation of a two dimensional electron gas (2DEG) on the GaN side of the interface.[44]

Electrons in the 2DEG are sourced by the donor-like states at the surface of the AlGaN epitaxy according to the following. First, spatial charge within the structure must sum to zero, meaning the structure is charge neutral. Second, the polarization induced charge constitutes a dipole, meaning that the net contribution to the space charge is zero. Third, the buffer charge must be negative or charge will not remain confined to the hetero interface; the buffer charge is intentionally minimized so that it may considered negligible [46]. If the AlGaN barrier layer is undoped, as is typical in modern GaN heterostructures, the charge in the AlGaN can be considered to be

Figure 2.4: Conduction band diagram for the AlGaN/GaN heterointerface.

zero. Therefore the final charge balance equation that must be satisfied is:

$$\sigma_{Surface} - qn_s = \sigma_{Surface} - \sigma_{2DEG} = 0 \tag{2.6}$$

Where  $qn_s$  is the charge in the 2DEG. The maximum sheet carrier concentration in the 2DEG in an undoped structure is given by [46]:

$$n_s(x) = \left(\frac{\sigma(x)}{e}\right) - \left(\frac{\epsilon_0 \epsilon(x)}{de^2}\right) \left[e\phi_b(x) + E_F(x) - \Delta E_C(x)\right]$$

(2.7)

In this equation, d is the width of the AlGaN barrier and  $e\Phi_b$  is the Schottky-Barrier height of the gate contact. The Fermi level with respect to the GaN conduction band is given by  $E_F$  and the conduction band offset between AlGaN/GaN is given by  $\Delta E_C$ . [44]

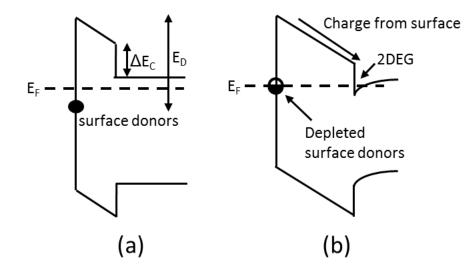

Equation 2.7 shows that the number of carriers in the 2DEG must be equal to the number of positive charges on the AlGaN surface in an undoped heterostructure. Therefore, the surface states can be considered donor-like such that they are neutral when occupied by an electron and positively charged when ionized. The donor-like

Figure 2.5: Band diagram in an undoped AlGaN/GaN heterostructure. (a) Band diagram when the AlGaN barrier thickness is not sufficient thickness to induce a 2DEG. (b) Band diagram in the case of the AlGaN thickness surpassing the critical thickness necessary to induce a 2DEG. [46].

surface states then have an energy,  $E_D$ , below the conduction band when filled as shown in Figure 2.5a. The occupancy of the surface states and by extension the charge, in the 2DEG depends on the  $E_D$  relative to the Fermi level  $E_F$ . If  $E_D$  is sufficiently deep and below the Fermi level, then no 2DEG will form since  $\sigma_{Surface} =$  $\sigma_{2DEG} = 0$ . At a critical AlGaN barrier thickness the surface donor-like states will reach the Fermi level and begin to ionize by transfer electrons to the empty conduction band states at the AlGaN/GaN interface, thus forming the 2DEG.

The critical thickness,  $t_{CR}$ , necessary to induce a 2DEG is given by the following equation.

$$t_{CR} = (E_D - \Delta E_C) \frac{\epsilon}{q\sigma_{PZ}} \tag{2.8}$$

Where  $\epsilon$  is the AlGaN relative dielectric constant and  $\Delta E_C$  is the AlGaN/GaN conduction band offset. The 2DEG density as a function of barrier thickness is given by the following equation.

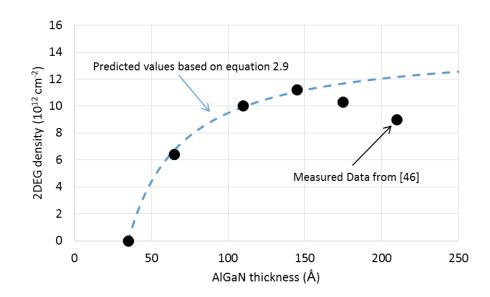

Figure 2.6: Experimentally measured room temperature 2DEG density as a function of  $Al_{0.34}Ga_{0.66}N$  barrier thickness. The solid line is calculated from Equation 1.9.[46].

$$qn_s = \sigma_{PZ} \left( 1 - \frac{t_{CR}}{t} \right) \tag{2.9}$$

As can be seen in Figure 2.6,  $n_s$  rapidly increases once the critical thickness is exceeded as the surface states  $E_D$  crosses the Fermi level before finally saturating at  $\sigma_{PZ}/q$  for  $t \gg t_{CR}$  once all of the donor-like surface states have been emptied [46].

The formation of the conducting channel in AlGaN/GaN HEMTs is shown to be primarily dependent on two factors. These factors are the Al mole fraction in the AlGaN barrier layer and thickness of the AlGaN barrier layer. An upper limit to AlGaN barrier thickness does exist due to epitaxial strain caused by the lattice mismatch between GaN and AlGaN. Since the lattice mismatch is a function of Al mole fraction, higher Al concentrations come at the expense of a reduced upper limit to the critical thickness. Once this thickness is exceeded, the AlGaN barrier layer will relax via cracking which in turn reduces the piezoelectric component to polarization and thus degrades the 2DEG charge density.

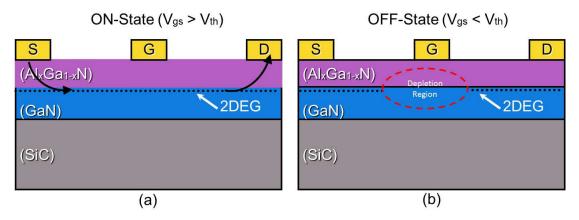

Figure 2.7: Basic operation principles of a AlGaN/GaN HEMT. (a) ON-state condition, when gate bias is more positive than the threshold voltage. (b) OFF-state condition when the gate bias is more negative than the threshold voltage.

#### 2.3 AlGaN/GaN High Electron Mobility HEMT Operation

Previous sections have described how the AlGaN/GaN epitaxy layers generate a sheet of highly mobile electrons that are ideally suited to act as a conducting channel for a three terminal FET device as shown in Figure 2.7. The AlGaN/GaN HEMT has the traditional gate, source, and drain contacts found in the classical metal-oxide-semiconductor field effect transistor (MOSFET). Operation consists of the device operating in the ON-state when gate bias is more positive than the threshold voltage. In this state, the device 2DEG remains continuous allowing the flow of electrons from the source ohmic terminal to the drain ohmic terminal as seen in Figure 2.7a. The device OFF-state is induced when the gate bias is more negative than the threshold voltage. The negative bias in this case is sufficient to deplete the electrons in the 2DEG below the gate terminal leading to an electrical discontinuity between the source and drain terminals, shown in Figure 2.7b.

Since the 2DEG is present as a consequence of the epitaxial growth, the device is in the ON-state when no bias is applied. This makes all AlGaN/GaN HEMTs natively depletion mode devices. This is in contrast to traditional MOSFET devices that are enhancement mode devices, requiring a positive gate bias to be applied to turn the device ON.

#### 2.3.1 Ohmic Contacts

The source and drain contacts on an AlGaN/GaN HEMT are ohmic, meaning that the metal-semiconductor junction has a linear current-voltage behavior as described by Ohm's law. These contacts provide access to the conductive channel of the device providing a path for electrical current to flow.

Ohmic contacts are formed through the deposition of thin metals on the semiconductor surface that are then rapidly annealed at high temperature to alter the metal semiconductor interface and make the junction ohmic. In AlGaN/GaN semiconductors thin layers of Ti/Al were initially discovered to provide reasonable contact resistances [47]. Subsequent studies introduced additional metal layers to the ohmic stack while demonstrating improved contact resistances. These additional layers on top of the Ti/Al layers consist of a diffusion barrier such as titanium (Ti), nickel (Ni), molybdenum (Mo), or platnium (Pt) before completing the stack with a final gold (Au) layer [48] [49] [50].

Typical AlGaN/GaN semiconductor processes deposit the metals via electron beam evaporation under vacuum to maximize the quality and maintain a high degree of control on the final metal thickness. Contacts are defined via a metal photoresist liftoff process. The deposited contacts are then alloyed in a rapid thermal anneal oven at temperatures that depend on the specific process and can range from  $650^{\circ}C$ to  $850^{\circ}C$ . During the anneal an inert gas such as Ar or N is forced into the oven to prevent oxidation of the contact.

The physical mechanism that leads to the formation of low resistance contacts is understood as follows. During the anneal process, the Ti layer in contact with the semiconductor surface diffuses into the semiconductor forming a TiN alloy that is metallic in nature and has a low work function. The formation of TiN at the semiconductor surface directly leads to the generation of nitrogen vacancies. These vacancies lead to heavy doping of the GaN, effectively thinning the barrier, and provides for a low impedance path to the device 2DEG [51]. The layers at the top of the stack alloy into a stable composite for high temperature applications.

#### 2.3.2 Schottky Contacts

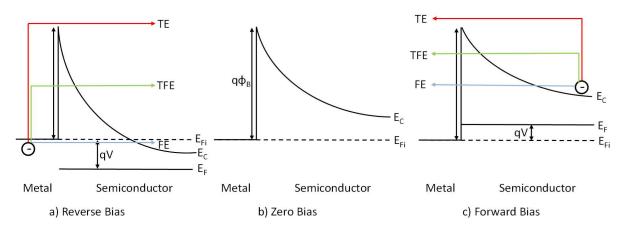

The gate contact on an AlGaN/GaN HEMT acts to modulate the device channel and sets the state of operation. To accomplish this task, the gate contact must have rectifying properties similar to that of a diode. Therefore, unlike the ohmic drain and source contacts, the gate contact is engineered to have a Schottky barrier at the metal-semiconductor junction. An illustration of the band diagram of a metalsemiconductor Schottky junction is shown in Figure 2.8. The gate contact plays a significant role in device performance and reliability as will be discussed in detail in subsequent chapters.

Fabrication of Schottky contacts is similar to the ohmic contact process. A metal stack is deposited on the semiconductor surface, typically via electron beam deposition under high vacuum. Contacts are defined via metal liftoff. Unlike ohmic contacts, no metal annealing is performed after deposition. Several metals have been found to form a Schottky barrier on GaN. The classical metals and their respective metal work functions ( $\phi_m$ ) are gold (5.1 eV), palladium (5.12 eV), nickel (5.15 eV), and platinum (5.65 eV) [52]. The contact is then completed with a layer of Au on the top to minimize impedance with an appropriate Au diffusion barrier in the middle to prevent Au from mixing with the Schottky metal.

When the gate is either reverse or forward biased, it is possible for electrons to overcome the Schottky barrier ( $\Phi_B$ ) and transport across the junction. Electron transport is not desired under ideal operating conditions and should be minimized to maximize both performance and reliability. In the presence of low to medium electric fields, transport across the junction is dominated by thermionic emission [12] and is generally the most common emission observed during normal operation

Figure 2.8: Band diagram illustrating the metal-semiconductor junction of Schottky contact. a) Junction is reverse biased. b) Zero bias on the metal-semiconductor junction. c) Forward bias Junction. The colored arrows in the reverse and forward bias show schematically how the electron transport across the barrier could occur. These mechanisms are thermionic emission (TE), thermionic field emission (TFE), and field emission (FE).

of AlGaN/GaN devices. The thermionic emission equation for total current density across the Schottky barrier is given by

$$J_n = \left[A^* T^2 exp\left(\frac{-q\phi_B}{kT}\right)\right] \left[exp\left(\frac{qV}{kT}\right)\right]$$

(2.10)

Where  $A^*$  is the Richardson constant for thermionic emission and is material specific, T is the ambient temperature of the device, k is the Boltzmann constant, and  $\phi_B$  is the Schottky barrier height [12].

In operation at low temperatures, other transport mechanisms which involve the electron tunneling through the barrier to arrive at the opposite side of the metalsemiconductor junction are dominant. When the electron tunnels directly across the Schottky barrier, aided only by the applied electric field, it is called field emission. Transport across the junction via a combination of both applied electric field and thermal energy is called thermionic field emission[12].

The current density due to field emission transport is given by the following equation.

$$J_{FE} = A^* \left(\frac{E_{00}}{k}\right)^2 \left(\frac{\phi_B + V_R}{\phi_B}\right) exp\left(\frac{2q\phi_B^{3/2}}{3E_{00}\sqrt{\phi_B + V_R}}\right)$$

(2.11)

The current density due thermionic field emission is given by the following equation.

$$J_{TFE} = \frac{A^*T}{k} \sqrt{\pi E_{00} q \left[ V_R + \frac{\phi_B}{\cosh^2\left(E_{00}/kT\right)} \right]} \left( exp \frac{-q\phi_B}{E_0} \right) \left( exp \frac{qV_R}{\epsilon'} \right)$$

(2.12)

where

$$\epsilon' = \frac{E_{00}}{(E_{00}/kT) - tanh(E_{00}/kT)}$$

(2.13)

$$E_{00} = \frac{h}{2} \sqrt{\frac{N_D}{m^* \epsilon_S \epsilon_0}} \tag{2.14}$$

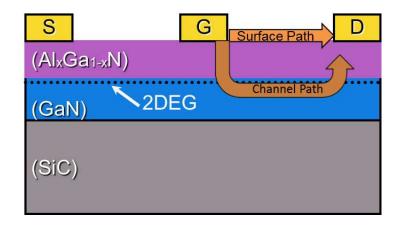

When fabricated as a lateral device, meaning the gate, source, and drain contacts are all on the same surface of the device, electrical current may flow between the gate and ohmic contacts under bias. When the gate diode is forward biased with respect to the drain and the source, electrons may be thought of as flowing from the ohmic contacts to the gate contact. Under reverse bias conditions the opposite would be true with the electrons flowing from the gate contact to the ohmic contacts. Two paths for conduction are possible and both are illustrated in Figure 2.9. The first path is across the AlGaN barrier to the device 2DEG and from there the electrons may travel to the source or drain contact through a low impedance path. The second path follows the AlGaN surface from the gate contact to the ohmic contact.

In the forward bias case the electrical current fits the thermionic emission model and is understood to be the physical mechanism by which current flows under typical operating conditions and temperatures of an AlGaN/GaN device. The mechanism by which current flows in the device when the gate diode is reverse biased with respect

Figure 2.9: Schematic cross section of the device showing the two conduction paths available for electrical current to flow from the gate contact to either ohmic contact. Current flow from gate to drain is pictured.

to the ohmic contacts is still a subject for debate that has not been completely understood in literature.

The field emission (FE) and thermionic field emission (TFE) mechanisms in Al-GaN/GaN HEMTs assume that the metal-semiconductor junction is heavily doped  $(N_D > 10^{17} cm^{-3})$  [53]. However, this doping concentration typically does not exist as the 2DEG can formed without doping the AlGaN layer. Despite this fact there exist publications that have shown the reverse leakage characteristics can be fitted to the FE/TFE models. In these works the authors fit the model to measured values by assuming the barrier doping as  $N_d = 1X10^{17} cm^{-3}$  in [54] and  $N_d = 1.4X10^{19} cm^{-3}$ in [55]. The high doping assumptions in the AlGaN barrier are rationalized by the introduction of the "thin surface barrier" model [56]. This thin surface barrier model states that a high density of defect donors are present at the AlGaN surface due to nitrogen vacancies. This acts to reduce the width of the Schottky barrier to enable the probability of electron tunneling to occur under reverse bias conditions. The precise mechanism in this model is dependent on ambient temperature with FE transport said to occur below 250K and TFE above this temperature.

Similar to the FE transport is Fowler-Nordheim tunneling which has been shown

to fit reverse Schottky diode leakage at low temperatures [58]. The current density due to Fowler-Nordheim is given by the following equation.

$$J = E_b^2 \left( \frac{q^2 (m_e/m_n^*)}{8\pi h \phi_b} \right) exp \left( -\frac{8\pi E_b \sqrt{2m_n^* (q\phi_b)^3}}{3qh} \right)$$

(2.15)

Where  $E_b$  is the electric field in the AlGaN barrier layer, q is the charge of an electron,  $m_e$  is the free electron mass,  $m_n^*$  is the conduction band effective mass in the semiconductor, h is Planck's constant, and  $\phi_b$  is the effective barrier height at the Schottky contact [58]. Experimentally, the data in [58] shows that a very weak temperature dependence is present in reverse leakage current measured from 110K to 130K and was shown to fit the Fowler-Nordheim model.

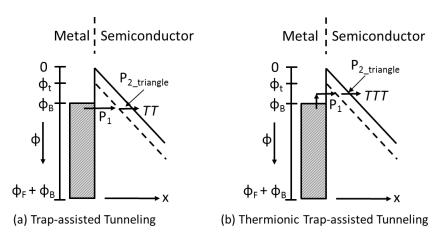

An alternative model proposed to explain reverse leakage current are the trapassisted tunneling and thermionic trap assisted tunneling models and have been shown to match the reverse leakage observed in AlGaN/GaN Schottky diodes [57]. In these models the trap-assisted tunneling model suggests that an electron may tunnel through the Schottky barrier by hopping to an intermediate trap state available in the bandgap and then continue traveling to the conduction band of the AlGaN from this trap state. The thermionic trap assisted tunneling model is identical except that it proposes that the electron is thermally excited prior to entering the bandgap trap state and crossing the AlGaN barrier in a region of triangular barrier that is thinner. An illustration of these mechanisms is shown in Figure 2.10.

An extension of trap assisted tunneling methods that has also been utilized to explain gate leakage current is the Poole-Frenkel mechanism [58], [59]. Poole-Frenkel conduction is explained as the emission of trapped electrons, from a continuum of trap states, into the conduction band via thermal excitation and may be enhanced by the applied electric field [60]. Poole-Frenkel has been referenced to explain both vertical [58] and lateral [59] conduction paths, in observed leakage from studies in literature, that are illustrated in Figure 2.9.

Figure 2.10: (a) Illustration of trap-assisted tunneling mechanism. (b) Thermionic trap-assisted tunneling mechanism. [57]

The total current density due to Poole-Frenkel emission is given by the following equation [58]

$$J = CE_b \left[ -\frac{q \left( \phi_t - \sqrt{q E_b / \pi \epsilon_0 \epsilon_s} \right)}{kT} \right]$$

(2.16)

Where  $E_b$  is the electric field in the semiconductor barrier at the metal-semiconductor junction,  $\phi_t$  is the barrier height for electron emission from the traps state,  $\epsilon_0$  is the permittivity of free space,  $\epsilon_s$  is the relative dielectric permittivity of the AlGaN barrier at high frequency, T is the temperature and k is Boltzmann's constant.

The expression for current density as a function of applied bias may be written as:

$$J = V exp\left(\frac{2a\sqrt{V}}{T} - \frac{q\phi_t}{kT}\right) \tag{2.17}$$

where

$$a = \sqrt{\frac{q}{\pi\epsilon_0 d}} \tag{2.18}$$

In this equation V is the bias that is applied to the gate terminal and d is the thickness

of the AlGaN barrier. Reverse current leakage experimentally measured is then fitted to the above equations. Such fits have been demonstrated in literature and is typically shown on a log scale versus the square of the applied voltage or electric field so that a linear trend may be observed. Examples in literature exist that show a fit to Poole-Frenkel as both a function of applied electric field and temperature [58], and fitting both vertical and lateral gate diode leakage current[59]. By extrapolating the fit data back to the zero bias condition on the gate ( $V_{gs} = 0V$ ) a trap barrier height ( $\phi_t$ ) may be extracted from the model. In the cited works, the trap barrier height was estimated to be 0.26 eV for conduction along the AlGaN surface [59] and 0.30 eVfor leakage across the AlGaN barrier [58]. Furthermore it was suggested in the latter study that the emission of electrons from the trap state was due to a continuum of electrical states, not in the AlGaN barrier.

If the continuum of trap states were to be located in the AlGaN barrier then it would require that the trap states be located 0.30eV below the conduction band in the AlGaN. If this were true, then the trap level would be located 0.8 - 0.9eV above the metal Fermi level, in which case the thermal emission of carriers from the metal into the trap state would be the key mechanism allowing the flow of leakage current. This is an unlikely process under reverse bias conditions [58]. Therefore, the authors explain that the reverse leakage current occurs through Poole-Frenkel emission from a state within the AlGaN such as a trap state near the metal-semiconductor interface into a continuum of states associated with conductive dislocation, such as nitrogen vacancies. Another study found the magnitude reverse leakage current to be correlated to the threading dislocation density in the AlGaN barrier layer. In this work it was reported that by reducing the threading dislocation density from  $2X10^{10} cm^{-2}$ to  $5X10^7 cm^{-2}$  led to a decrease in mean reverse leakage by a factor of 45 [62].

In summary, the forward conduction of a Schottky gate contact on an AlGaN/GaN HEMT may be sufficiently described by the thermionic emission theory. The reverse

leakage current is still a subject for debate and not completely understood. Several different works have found that the reverse leakage may be sufficiently described by a variety of mechanisms which may mean that the dominant mechanism is dependent on the specific material that is studied.

## 2.3.3 AlGaN/GaN HEMT Traps and Surface Passivation

Carrier trapping in AlGaN/GaN HEMTs has been identified in literature as a performance limiting phenomena and leads to a variety of observations which include current dispersion, compression, and power slump. In a power semiconductor device the output power may be estimated by the following equation.

$$P_{out} = \frac{I_{max}(V_{BD} - V_{knee})}{8}$$

(2.19)

In this equation  $I_{max}$  is the max current output by the device in the saturation region,  $V_{knee}$  is the voltage at which the device transitions from the linear region to the saturation region on the I-V curve. The term  $V_{BD}$  is defined as the breakdown voltage of the device. When operated under RF or pulsed conditions the DC I-V parameters for a device have been observed to dynamically change and therefore lead to a reduction of output power that is achieved by the device. This observation is wide spread in the literature and is revealed by characterizing the device with a pulsed-IV system. In a pulsed I-V test, the device is DC pulsed from a quiescent bias point, typically chosen for a desired RF power operating condition. The device is then pulsed to various points on the I-V plane. With each pulsed the I-V curve collapses so that max current is continuously reduced along with an increase in knee voltage, and as a result the output power drops. The reduction is due to filling of trap states in the device, so the reduction in drain current is used to quantify the trap state density. This test is used as a proxy for behavior that happens to the device under RF drive.

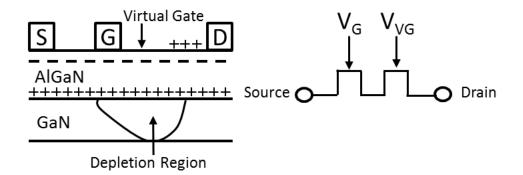

Figure 2.11: Illustration of the virtual gate mechanism described in [63] used to explain the trapping phenomena observed during RF operations and pulsed IV characterization.

The virtual gate phenomena has been used to explain the mechanism by which trapping leads to degradation effects observed during RF operation [63]. As detailed earlier in this chapter, during the growth of the AlGaN/GaN epitaxial layers, the formation of the channel 2DEG gives rise to a sheet of positive surface charge so that charge balance may be achieved in the heterostructure. This positive sheet can arise from ionized donor states at the surface. The virtual gate mechanism states that electrons sourced from the gate metal may be trapped by the ionized donor states that are present on the surface of the semiconductor. These trapped charges on the surface act as a second "virtual gate" and exert a negative potential on the underlying 2DEG and in turn depletes charge from the channel.

The mechanism by which trapping occurs also has been shown to have an opposite de-trapping mechanism by which charge is removed from the virtual gate and restored to the gate metal. Trapping was shown to occur under off-state conditions with high bias applied to the device, while de-trapping occurs when the device was biased into open channel conditions  $V_{gs} = 0V$  [63]. This implies that the trapping is heavily dependent on the electric field that is present between the gate and drain contacts. As charge is collected in the virtual gate, it acts to deplete the underlying charge in the 2DEG which leads to a reduction of the electric field at the drain edge of the gate contact and therefore reducing the rate by which electrons are trapped in the surface states.

The concept of virtual gating may also be extended to the GaN buffer layer below the device 2DEG [64]. These trap states are shown to be deep states and physically far from the AlGaN/GaN interface [65]. The time constants associated with these trap states in the bulk GaN of the semiconductor have been demonstrated to be very long, on the order of minutes to hours. As a consequence they can have similar impacts on performance due to surface trapping [66]. However, advancements in substrate quality and epitaxial growth techniques have greatly mitigated the effects of bulk trap states.

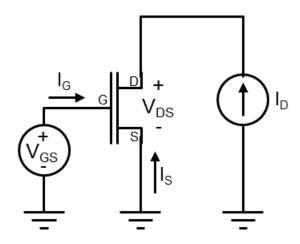

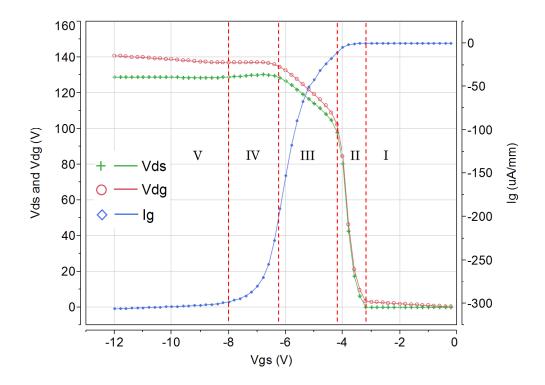

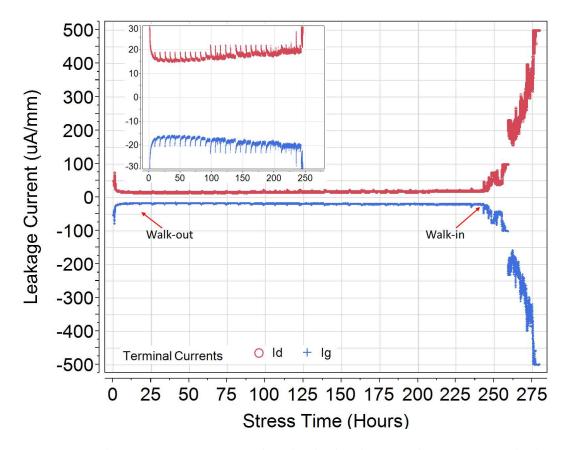

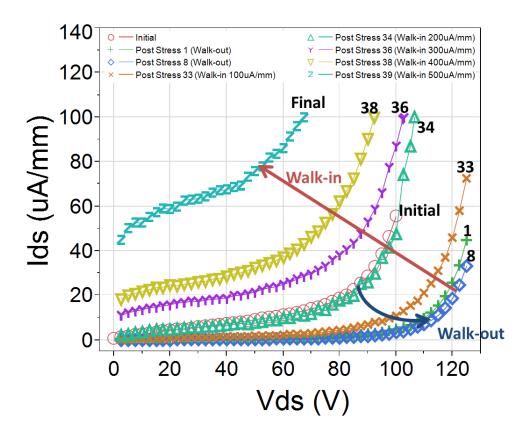

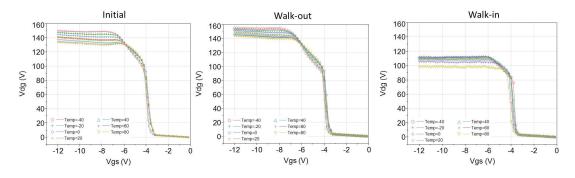

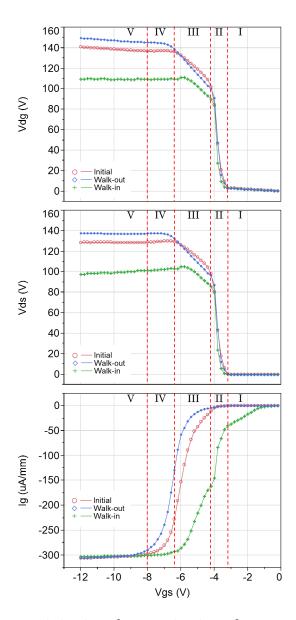

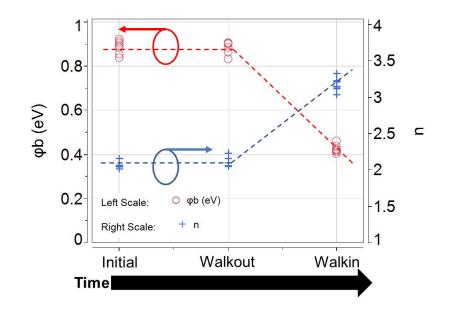

In order to mitigate the effects of surface trapping, surface passivation was introduced and becomes a critical process step in the fabrication of AlGaN/GaN HEMTs. Experimentally, it has been shown that proper passivation with silicon nitride  $(Si_3N_4)$ , mitigates effects such as dispersion, current degradation, and power droop [63], [64]. Even with surface passivation there still exist states at the AlGaN/SiN interface that may trap charge and therefore lead to virtual gating effects. So high quality passivation with minimal interface states is crucial during device fabrication. This means that surface passivation recipes and materials may vary significantly in different GaN processes, but SiN passivation is by far the most widely used. Deposition of the passivation layer is recommended to occur as early in device processing as possible as the deposition techniques, typically plasma enhanced chemical vapor deposition (PECVD), exposes the surface to ions and other potential contaminants [67].